# RITOKO

### **ERROR SIGNAL ISOLATOR**

#### **FEATURES**

- **■** Eliminates Opto-coupler from Feedback Loop

- Replaces TL431 and Eliminates Parasitic Zero

- Pulse Transformer Driver

- Same Transformer for Any Output Voltage

- Peak Current Controlled

- Automatic Volt-Second Balancing

- Self-running Oscillator

- Hi-performance Op-amp & Bandgap Reference

- Functionally Integrated & Simplified 5-pin Design

#### **APPLICATIONS**

- **■** Power Supplies with Primary-Side Controller

- **■** Low Isolation-Barrier Capacitance Equipment

- **■** Instrumentation

- Industrial Process Control

- **■** Test Equipment

- Data Acquisition

#### DESCRIPTION

The TK75002 monitors the output voltage of a power supply, generates an error signal, and transmits the error signal across an isolation barrier using a small pulse transformer. In conjunction with the pulse transformer, it replaces the TL431/opto-coupler combination and eliminates the undesirable zero created in the feedback loop by that combination. The transformer is driven with pulse amplitude modulation in a free-running oscillator configuration. The period of oscillation is proportional to the inductance of the pulse transformer. The magnitude of the voltage pulse is internally limited so that the pulse transformer design need not be changed for various output voltages.

The TK75002 is available in an 8-pin DIP package.

## **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage 7 V                      | Extended Temperature Range (I)40 to +85 °C |

|-----------------------------------------|--------------------------------------------|

| Power Dissipation (Note 1) 825 mW       | Operating Voltage Range 1.6 to 12 V        |

| Storage Temperature Range55 to +150 °C  | Junction Temperature 150 °C                |

| Operating Temperature Range20 to +70 °C | Lead Soldering Temperature (10 s) 235 °C   |

# **TK75002 ELECTRICAL CHARACTERISTICS**

$Test \ conditions: \ V_{CC} = 5 \ V, \ T_A = Full \ Operating \ Range. \ Typical \ numbers \ apply \ at \ T_A = 25 \ ^{\circ}C, \ unless \ otherwise \ specified.$

| SYMBOL                                  | PARAMETER                                        | TEST CONDITIONS                                 | MIN   | TYP   | MAX   | UNITS |

|-----------------------------------------|--------------------------------------------------|-------------------------------------------------|-------|-------|-------|-------|

| I <sub>CC(OFF)</sub>                    | Standby Supply Current                           | V <sub>CC</sub> = 3.5 V                         | 100   | 600   | 1000  | μA    |

| I <sub>CC(ON)</sub>                     | Operating Supply Current                         | DRV Pin Open                                    |       | 9.5   | 15    | mA    |

| V <sub>cc</sub>                         | Operating Voltage Range                          |                                                 | 4.7   |       | 7     | V     |

| V <sub>CC(ON)</sub>                     | UVLO High Threshold                              | $V_{COMP} = V_{ref(EA)}$                        | 3.5   | 4.1   | 4.7   | V     |

| V <sub>CC(HYST)</sub>                   | UVLO Hysteresis                                  | $V_{COMP} = V_{ref(EA)}$                        | 15    | 120   | 300   | mV    |

|                                         | LIFIER SECTION (INV AND CON                      | IP PINS)                                        |       | •     | •     | •     |

| V <sub>ref(EA)</sub>                    | Equivalent Internal Reference<br>Voltage         | T <sub>A</sub> = 25 ° C                         | 1.330 | 1.350 | 1.370 | V     |

|                                         |                                                  | T <sub>A</sub> = Full Range                     | 1.31  |       | 1.39  | V     |

| A <sub>OL</sub>                         | Open Loop Gain                                   |                                                 | 53    | 65    |       | dB    |

| GBW                                     | Gain-Bandwidth Product                           |                                                 |       | 4.5   |       | MHz   |

| PSSR                                    | Power Supply Rejection Ratio                     |                                                 | 50    | 70    |       | dB    |

| COMP(SINK)                              | Maximum Sink Current                             | $V_{COMP}$ = Short to $V_{CC}$                  | 2     | 4     | 6     | mA    |

| I <sub>COMP(SRC)</sub>                  | Maximum Source Current                           | V <sub>COMP</sub> = Short to GND                | -25   | -18   | -5    | mA    |

| I <sub>INV</sub>                        | Bias Current                                     | $V_{INV} = V_{COMP}$                            | -2    | 0.2   | 2     | μA    |

| PULSE AMPL                              | ITUDE MODULATOR SECTION                          | (DRV PIN)                                       |       |       |       |       |

| I <sub>DRV(PK)</sub>                    | Peak Drive Current Threshold                     |                                                 | 30    | 55    | 75    | mA    |

| t <sub>OFF,D</sub>                      | Turn-off Delay from Peak<br>Detection to DRV Pin | L = 5 μH                                        | 50    | 175   | 350   | ns    |

| V <sub>CC</sub> - V <sub>DRV(ON)</sub>  | Peak Voltage Across Pulse<br>Transformer         | $I_{DRV} = I_{DRV(PK)}, V_{CC} \ge 5 \text{ V}$ | 2.8   | 3.5   | 4.8   | V     |

| V <sub>DRV(OFF)</sub> - V <sub>CC</sub> | Peak Voltage Across Clamp<br>Diode               | I <sub>DRV</sub> = 50 mA                        | 0.6   | 0.8   | 1.2   | V     |

| $V_{TRD,TH}$                            | Transformer Reset Detector<br>Threshold          |                                                 | 290   | 650   | 950   | mV    |

| k                                       | Gain of Level Shifter Stage                      |                                                 | 1.00  | 1.25  | 1.45  | V/V   |

|                                         |                                                  |                                                 |       |       |       |       |

Note 1: Power dissipation is 825 mW when mounted as recommended. Derate at 6.6 mW/°C for operation above 25 °C.

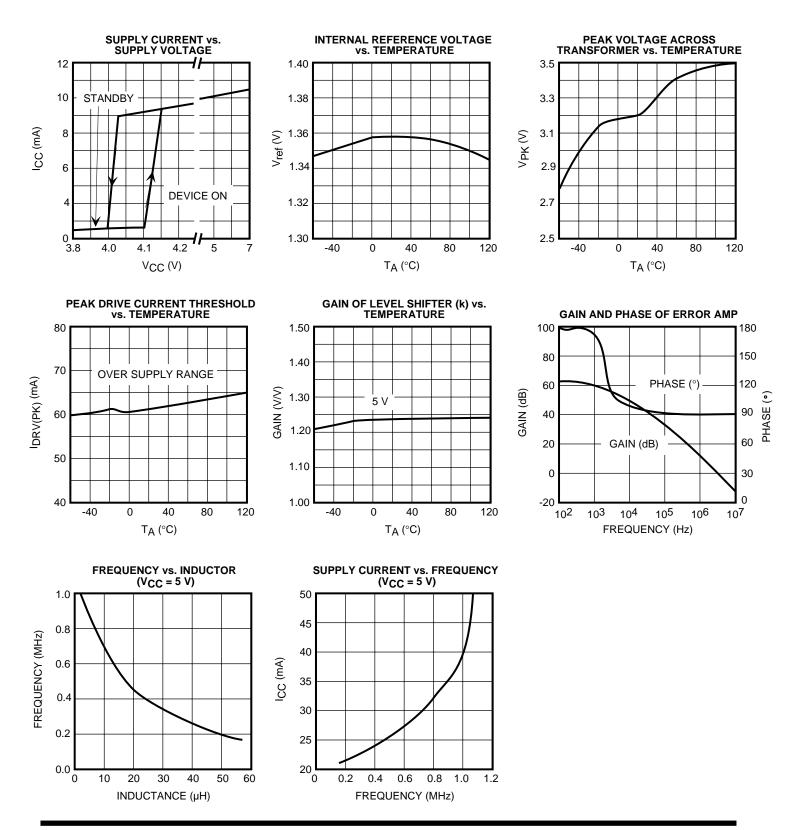

## TYPICAL PERFORMANCE CHARACTERISTICS

#### THEORY OF OPERATION

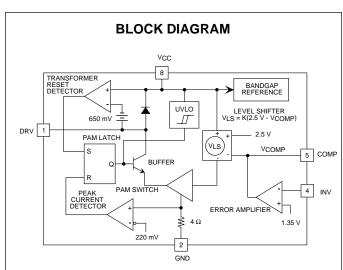

The TK75002 can be used in conjunction with either an opto-coupler or a pulse transformer to isolate an error signal developed by its internal op-amp. The op-amp can be externally compensated and features a precision reference voltage at the non-inverting input. When configured to drive a pulse transformer, the TK75002 will automatically oscillate to drive the pulse transformer in a pulse-amplitude-modulation (PAM) mode.

When  $V_{CC}$  is below the UVLO threshold (~4.1V) the TK75002 does not operate and the DRV pin remains in a high-impedance state. When  $V_{CC}$  is above the UVLO threshold, the PAM switch turns on and forces  $V_{DRV}$  with respect to  $V_{CC}$  to be equal to a gain constant times the opamp output voltage,  $V_{COMP}$ , with respect to 2.5 V. Essentially, then, the inverse of the error voltage (referenced to 2.5 V, a virtual ground) times a small gain constant is what appears between the DRV and  $V_{CC}$  pins. Note that this is only valid when  $V_{COMP}$  is less than 2.5 V, which also implies that  $V_{DRV}$  is less than  $V_{CC}$ .

If an opto-coupler and series resistor are hooked between the DRV and  $V_{\rm CC}$  pins, an error current is transmitted across the opto-coupler which is free from the characteristic of having the zero that is a sort of parasitic effect of the standard configuration of driving an opto-coupler with a TL431.

If a pulse transformer is connected between the DRV and V<sub>CC</sub> pins, the magnetizing current will begin to increase until it reaches a threshold of ~ 55 mA, as detected by the Peak Current Detector. After an internal turnoff delay, the PAM switch turns off and the magnetizing current forces the DRV-pin voltage above  $V_{CC}$ . An internal clamp diode between the DRV pin and the  $V_{CC}$  pin clamps the voltage and then essentially compares it to a  $V_{CC}$ -referenced voltage which corresponds to ~ 1 mA of current flow in the clamp diode (i.e., ~ 650 mV at room temperature). When the magnetizing current has decayed to nearly zero (i.e., ~ 1 mA) and after an internal turn-on delay, the Transformer Reset Detector turns on the PAM switch to initiate the process all over again. By using peak rectification on the secondary side of the pulse transformer, the error signal can be recovered. The time constant of the peak detection circuit is chosen to yield negligible ripple but also an acceptable response time. The magnetizing inductance of the pulse transformer is chosen to yield an acceptable peak current overshoot and/or power dissipation when the switching frequency is at a maximum (maximum switching frequency occurs when the op-amp output is low).

The TK75002 has a saturation limiter in the feedback loop. For either the opto-coupler or pulse transformer configurations, the error voltage which is transmitted across the isolation device by the TK75002 is limited to less than 5 V. This limiting occurs regardless of the applied  $V_{\rm CC}$  (generally, it is  $V_{\rm CC}$  which is being regulated by the feedback loop for which the TK75002 transmits the error signal). Thus, when the TK75002 is used in a variable output voltage power supply or in a standard line of various fixed output power supplies, no supplemental signal-limiting circuitry is required in the feedback loop.

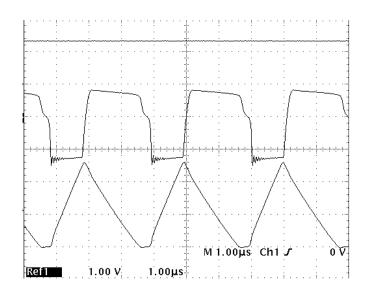

The characteristic waveforms of the TK75002 driving a pulse transformer are shown in Figure 1. The top trace shows the error voltage (@ 1 V / div.) referenced two divisions below the top; it is equal to approximately 1.3 V. The middle trace shows the DRV Pin voltage with respect to  $V_{CC}$  (@ 1 V / div.) referenced three divisions below the top. The bottom trace shows the DRV Pin current (@ 20 mA / div.) referenced one division above the bottom.

FIGURE 1: CHARACTERISTIC WAVEFORMS OF THE TK75002

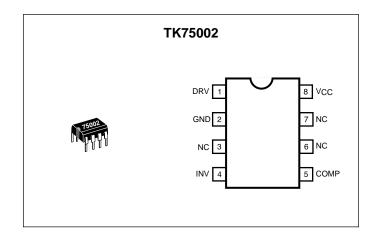

#### PIN DESCRIPTION

### $V_{CC}PIN$

This pin is connected to the supply voltage. The operation of the IC is enabled when the supply voltage exceeds 4.1 V, which is the upper threshold of the undervoltage lockout circuit. The operation is disabled when the supply voltage drops below 3.98 V.

#### **GND PIN**

This pin provides ground return for the IC.

#### **DRV PIN**

This pin drives the first terminal of the primary winding of the external pulse transformer using pulse-amplitude modulation (PAM). The second terminal of the primary winding is connected to the V<sub>CC</sub> pin. When the DRV pin is low, an internal NPN transistor (the PAM switch) is turned on and sinks an increasing current from the supply voltage through the primary winding. The PAM switch is turned off when the current reaches approximately 55 mA. The PAM switch is turned on again when the transformer is reset through the internal free-wheeling diode.

#### **INV PIN**

The INV pin is the inverting input of the error amplifier. The non-inverting input of the error amplifier is connected to an internal 1.35 V precision reference source.

#### **COMP PIN**

The COMP pin is the output of the error amplifier. The frequency compensation feedback network is connected between the COMP and INV pins. Internally, the COMP pin drives the inverting input of a level shifter stage. The roles of the level shifter are to change (1) the reference point of the error signal from the GND pin to the  $\rm V_{\rm CC}$  pin (necessary to avoid the parasitic zero in the transfer function caused by feed-forward through the supply) and (2) the signal polarity (necessary for start-up of the converter system in case the reference point was changed). The parasitic zero is discussed in the "Application Information" section.

#### APPLICATION INFORMATION

# THE PARASITIC ZERO AND HOW IT IS ELIMINATED IN THE TK75002

In a feedback-regulated isolated power supply, isolation is usually provided by an opto-coupler whose photodiode section is connected between the output of the power supply and the output of the error amplifier (in series with a resistor that converts the voltage difference between the two outputs into a current). Due to the feed-forward path established by that connection, the transfer function of the error amplifier is significantly modified (the modification in the transfer function appears also if the opto-coupler is replaced by the combination of a transformer and peak detector driven by a pulse amplitude modulator).

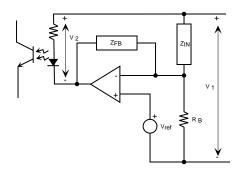

Figure 2 shows the error amplifier/opto-coupler combination. The output voltage V<sub>2</sub> (that is the voltage measured across the photodiode and the series resistor) can be written as:

$$V_2 = V_1 - [-(Z_{FB} / Z_{IN}) \times V_1]$$

(1)

From (1), the transfer function of the error amplifier (from the supply voltage  $V_1$ , to the voltage  $V_2$ ) is:

$$H(s) = V_2(s) / V_1(s) = 1 + (Z_{FB} / Z_{IN})$$

(2)

In the case when the feedback impedance is a capacitor C and the input impedance is a resistor R, the transfer function becomes:

$$H(s) = (1 + SRC) / SRC$$

(3)

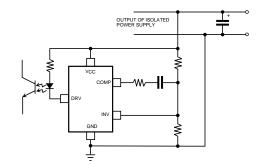

FIGURE 2: ERROR AMPLIFIER / OPTO-COUPLER COMBINATION

Figure 3 shows the magnitude and phase diagram of the transfer function. As can be seen, the feed-forward path adds a left half-plane zero (sometimes called a "parasitic" zero) to the transfer function of the ideal integrator. The parasitic zero is undesirable because it increases the high frequency loop gain of the system, potentially leading to subharmonic instability or chaotic behavior. To avoid the effect of the zero, either a low pass (decoupling) filter must be added to the supply rail of the opto-coupler, or an additional pole must be introduced around the frequency of the zero, or the loop gain must be reduced. (Note that reducing the loop gain slows down the transient response of the system.)

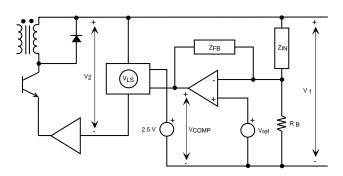

The TK75002 eliminates the parasitic zero by changing the reference point of the error signal from the GND pin to the  $V_{CC}$  pin. That is achieved by inserting a level shifter circuit between the output of the error amplifier and the buffer of the pulse-amplitude modulator (see Figure 4). The output voltage of the level shifter is proportional to the error signal (i.e., the voltage of the COMP pin) and is conveyed relative to the supply voltage  $V_1$ . The end result is that the transfer function becomes:

$$H(s) = Z_{FB} / Z_{IN}$$

(4)

In the case of a capacitive feedback impedance and resistive input impedance, the transfer function will be that of an ideal integrator, without the parasitic zero.

FIGURE 3: MAGNITUDE AND PHASE VS.

FREQUENCY OF AN ERROR AMPLIFIER / OPTOCOUPLER COMBINATION

# **APPLICATION INFORMATION (CONT.)**

FIGURE 4: ELIMINATING THE Feed-forward OF THE SUPPLY VOLTAGE IN THE TK75002

#### ISOLATION WITH PULSE TRANSFORMER

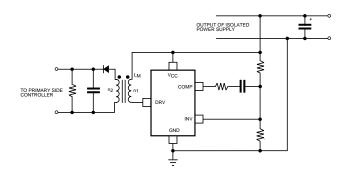

Figure 5 shows an application where the error signal is isolated with a pulse transformer. The signal is recovered at the primary side with a peak detector. The circuit is self-oscillating. The frequency of operation is:

$$\mathsf{f} = \mathsf{V}_\mathsf{F} \, / \, [[(\mathsf{I}_\mathsf{DRV(PK)} \, \mathsf{x} \, \, \mathsf{L}_\mathsf{M}) \, / \, \mathsf{kV}_\mathsf{COMP} + \mathsf{t}_\mathsf{OFF(D)}] \, \mathsf{x} \, \, (\mathsf{kV}_\mathsf{COMP} + \mathsf{V}_\mathsf{F})]$$

(5)

where the various quantities are:

$m V_F$  forward voltage drop of the internal clamp diode  $m I_{DRV(PK)}$  peak drive current threshold

L<sub>M</sub> magnetizing inductance of the pulse transformer

k gain of level shifter stage

${\it t}_{\rm OFF,D}$  turnoff delay from peak detection to DRV pin  ${\it V}_{\rm COMP}$  error signal (voltage at the COMP pin)

A  $20\,\mu\text{H}$  magnetizing inductance, with the typical parameter values of the TK75002 and an error signal of 1.4 V yields about 500 kHz oscillation frequency. Such an inductance can be obtained with three to five turns on a small ferrite toroid core of 5 to 10 mm external diameter.

FIGURE 5: ISOLATING THE ERROR SIGNAL WITH A PULSE TRANSFORMER

#### **ISOLATION WITH OPTO-COUPLER**

Figure 6 shows how the TK75002 can be used together with an opto-coupler. The oscillation is automatically disabled because the peak current will never reach the nominal 50 mA peak drive current threshold. A resistor must be connected in series with the photodiode of the opto-coupler to limit the maximum current. The main advantage of the TK75002 over the TL431 is the left-half-plane zero is avoided. Another advantage is that the error amplifier in the TK75002 has higher bandwidth than the TL431.

FIGURE 6: ISOLATING THE ERROR SIGNAL WITH AN OPTO-COUPLER

# **APPLICATION INFORMATION (CONT.)**

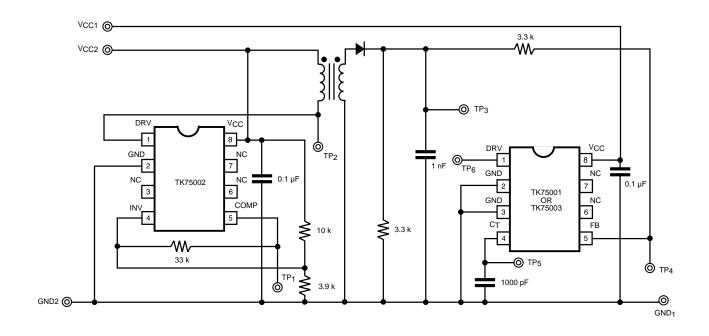

#### **TEST CIRCUIT EXAMPLE**

This simple circuit shown in Figure 7 is designed to allow the user to probe and observe the characteristic performance and behavior of either a TK75001 or a TK75003 operating with a TK75002. Also, either IC can be characterized independently in the circuit. The TK75001/TK75003 are pulse width modulated (PWM) controllers. The TK75002 is a pulse-amplitude-modulated (PAM) controller.

In all of the following text, the TK75003 can be substituted for the TK75001, depending on which of those two ICs is used in the characterization circuit. Ground is common to both the TK75001 and the TK75002.

$V_{CC1}$  provides power to the TK75001.  $V_{CC1}$  must be brought up to around 15 V to turn on the TK75001. Turn-on can be determined by any of the following events: a) current from the  $V_{CC1}$  supply jumps from ~ 1 mA to ~ 20 mA as the supply voltage is raised, b) a timing waveform appears at  $TP_5$ , or c) a drive signal appears at  $TP_6$  (assuming that  $TP_3$ or TP<sub>4</sub> is held low). TP<sub>5</sub> is the timing pin of the TK75001, which has a sawtooth voltage waveform across the 1000 pF timing capacitor. TP₄ is the feedback pin. The user can force a voltage there directly (for example, to measure the threshold voltage of the PWM,  $V_{CCD}$ , which is approximately 0.92 V) or voltage can be applied at TP<sub>3</sub>. Applying the voltage at TP<sub>3</sub> allows a voltage ramp to form and the PWM characteristic to be observed. The modulation range from zero to maximum PWM is approximately 0 to 1 V of voltage applied to TP3. The higher the applied voltage, the narrower the pulse width. Finally, in order to see the TK75001 operating with the TK75002, the voltage at TP<sub>3</sub> can be applied by causing the TK75002 to operate, as described next.

$V_{CC2}$  provides power to the TK75002. The TK75002 is configured with a resistor-feedback limited DC gain from  $V_{CC2}$  so that a gradual PAM change can be easily observed as  $V_{CC2}$  is changed. The modulation range from zero to maximum PAM is approximately 5 to 6 V of applied  $V_{CC2}$ . The higher the  $V_{CC}$  the higher the PAM signal magnitude. The PAM signal can be observed by probing  $TP_2$ , although it is more easily understood when connecting the probe ground to  $V_{CC2}$  since PAM is with respect to the supply voltage in the TK75002. The peak-rectified transformer-coupled output of the TK75002 can be observed at  $TP_3$ .

# **APPLICATION INFORMATION (CONT.)**

FIGURE 7: TEST CIRCUIT SCHEMATIC

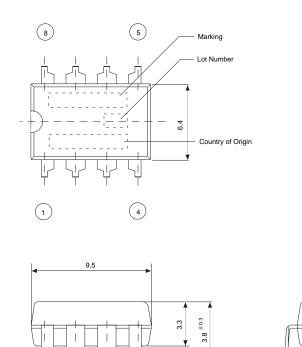

### **PACKAGE OUTLINE**

### DIP-8

#### **Marking Information**

TK75002

Marking 75002

# RITOKO

2.54

Toko America, Inc. Headquarters 1250 Feehanville Drive, Mount Prospect, Illinois 60056 Tel: (847) 297-0070 Fax: (847) 699-7864

#### TOKO AMERICA REGIONAL OFFICES

Dimensions are shown in millimeters Tolerance:  $x.x = \pm 0.2$  mm (unless otherwise specified)

Midwest Regional Office Toko America, Inc. 1250 Feehanville Drive Mount Prospect, IL 60056 Tel: (847) 297-0070 Fax: (847) 699-7864 Western Regional Office Toko America, Inc. 2480 North First Street , Suite 260 San Jose, CA 95131 Tel: (408) 432-8281

0.5 min

+ 0.15

(M)

0.25

0.25

e1 7.62

Eastern Regional Office Toko America, Inc. 107 Mill Plain Road Danbury, CT 06811 Tel: (203) 748-6871 Fax: (203) 797-1223 Semiconductor Technical Support Toko Design Center 4755 Forge Road Colorado Springs, CO 80907 Tel: (719) 528-2200 Fax: (719) 528-2375

#### Visit our Internet site at http://www.tokoam.com

Fax: (408) 943-9790

The information furnished by TOKO, Inc. is believed to be accurate and reliable. However, TOKO reserves the right to make changes or improvements in the design, specification or manufacture of its products without further notice. TOKO does not assume any liability arising from the application or use of any product or circuit described herein, nor for any infringements of patents or other rights of third parties which may result from the use of its products. No license is granted by implication or otherwise under any patent or patent rights of TOKO, Inc.