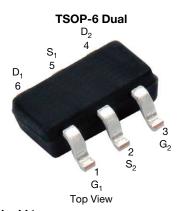

# Dual P-Channel 30 V (D-S) MOSFET

Marking code: MJ

| PRODUCT SUMMARY                                             |       |  |  |  |  |

|-------------------------------------------------------------|-------|--|--|--|--|

| V <sub>DS</sub> (V)                                         | -30   |  |  |  |  |

| $R_{DS(on)}$ max. ( $\Omega$ ) at $V_{GS} = -10 \text{ V}$  | 0.111 |  |  |  |  |

| $R_{DS(on)}$ max. ( $\Omega$ ) at $V_{GS} = -4.5 \text{ V}$ | 0.188 |  |  |  |  |

| Q <sub>g</sub> typ. (nC)                                    | 2.7   |  |  |  |  |

| I <sub>D</sub> (A) <sup>a</sup>                             | -2.9  |  |  |  |  |

| Configuration                                               | Dual  |  |  |  |  |

#### **FEATURES**

- TrenchFET® power MOSFET

- 100 % R<sub>g</sub> tested

• Material categorization: for definitions of compliance please see www.vishay.com/doc?99912

RoHS COMPLIANT HALOGEN FREE

#### **APPLICATIONS**

- Load switch portable applications

- Battery switch for portable devices

- Computers

- Bus switch

- Load switch

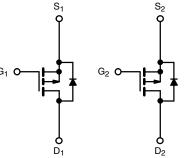

P-Channel MOSFET P-Channel MOSFET

| ORDERING INFORMATION            |                  |

|---------------------------------|------------------|

| Package                         | TSOP-6           |

| Lead (Pb)-free and halogen-free | Si3993CDV-T1-GE3 |

| <b>ABSOLUTE MAXIMUM RATINGS</b> (T <sub>A</sub> = 25 °C, unless otherwise noted) |                        |                                   |                       |      |  |

|----------------------------------------------------------------------------------|------------------------|-----------------------------------|-----------------------|------|--|

| PARAMETER                                                                        |                        | SYMBOL LIMIT                      |                       | UNIT |  |

| Drain-source voltage                                                             |                        | V <sub>DS</sub>                   | -30                   | V    |  |

| Gate-source voltage                                                              |                        | V <sub>GS</sub>                   | ± 20                  | V    |  |

|                                                                                  | T <sub>C</sub> = 25 °C |                                   | -2.9                  |      |  |

| Continuous drain surrent /T 150 °C\                                              | T <sub>C</sub> = 70 °C | 1 .                               | -2.3                  |      |  |

| Continuous drain current (T <sub>J</sub> = 150 °C)                               | T <sub>A</sub> = 25 °C | I <sub>D</sub>                    | -2.6 <sup>b, c</sup>  |      |  |

|                                                                                  | T <sub>A</sub> = 70 °C |                                   | -2.1 <sup>b, c</sup>  | Α    |  |

| Pulsed drain current                                                             |                        | I <sub>DM</sub>                   | -8                    |      |  |

| Continuous source drain diada surrent                                            | T <sub>C</sub> = 25 °C |                                   | -1.17                 |      |  |

| Continuous source-drain diode current                                            | T <sub>A</sub> = 25 °C | l <sub>S</sub>                    | -0.95 <sup>b, c</sup> |      |  |

|                                                                                  | T <sub>C</sub> = 25 °C |                                   | 1.4                   |      |  |

| Maximum power dissipation                                                        | T <sub>C</sub> = 70 °C |                                   | 0.9                   | 10/  |  |

|                                                                                  | T <sub>A</sub> = 25 °C | P <sub>D</sub>                    | 1.14 <sup>b, c</sup>  | W    |  |

|                                                                                  | T <sub>A</sub> = 70 °C |                                   | 0.73 <sup>b, c</sup>  |      |  |

| Operating junction and storage temperature range                                 |                        | T <sub>J</sub> , T <sub>stq</sub> | -55 to +150           | °C   |  |

| THERMAL RESISTANCE RATINGS       |              |                   |         |         |      |  |

|----------------------------------|--------------|-------------------|---------|---------|------|--|

| PARAMETER                        |              | SYMBOL            | TYPICAL | MAXIMUM | UNIT |  |

| Maximum junction-to-ambient b, d | t ≤ 5 s      | R <sub>thJA</sub> | 93      | 110     | °C/W |  |

| Maximum junction-to-foot         | Steady state | $R_{th,JF}$       | 75      | 90      | C/VV |  |

#### Notes

- a.  $T_C = 25$  °C

- b. Surface mounted on 1" x 1" FR4 board

- d. Maximum under steady state conditions is 150 °C/W

# Vishay Siliconix

| PARAMETER                                     | SYMBOL                               | TEST CONDITIONS                                                           | MIN. | TYP.  | MAX.      | UNIT     |  |

|-----------------------------------------------|--------------------------------------|---------------------------------------------------------------------------|------|-------|-----------|----------|--|

| Static                                        |                                      |                                                                           | •    | •     |           | •        |  |

| Drain-source breakdown voltage                | $V_{DS}$                             | $V_{GS} = 0 \text{ V}, I_D = -250 \mu\text{A}$                            | -30  | -     | -         | V        |  |

| V <sub>DS</sub> temperature coefficient       | $\Delta V_{DS}/T_{J}$                | L 050 A                                                                   | -    | -17   | -         |          |  |

| V <sub>GS(th)</sub> temperature coefficient   | ΔV <sub>GS(th)</sub> /T <sub>J</sub> | I <sub>D</sub> = -250 μA                                                  | -    | 3.5   | -         | mV/°C    |  |

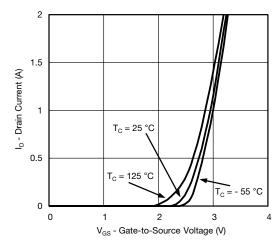

| Gate-source threshold voltage                 | V <sub>GS(th)</sub>                  | $V_{DS} = V_{GS}$ , $I_D = -250 \mu A$                                    | -1.2 | -     | -2.2      | V        |  |

| Gate-source leakage                           | I <sub>GSS</sub>                     | $V_{DS} = 0 \text{ V}, V_{GS} = \pm 20 \text{ V}$                         | -    | -     | ± 100     | nA       |  |

| 7                                             | I <sub>DSS</sub>                     | V <sub>DS</sub> = -30 V, V <sub>GS</sub> = 0 V                            | -    | -     | 1         |          |  |

| Zero gate voltage drain current               |                                      | V <sub>DS</sub> = -30 V, V <sub>GS</sub> = 0 V, T <sub>J</sub> = 55 °C    | -    | -     | 10        | μA       |  |

| On-state drain current <sup>a</sup>           | I <sub>D(on)</sub>                   | $V_{DS} \le -5 \text{ V}, V_{GS} = -10 \text{ V}$                         | -8   | -     | -         | Α        |  |

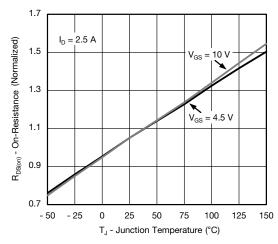

| Drain acuras an atata registance 3            | В                                    | V <sub>GS</sub> = -10 V, I <sub>D</sub> = -2.5 A                          | -    | 0.092 | 092 0.111 |          |  |

| Drain-source on-state resistance <sup>a</sup> | R <sub>DS(on)</sub>                  | V <sub>GS</sub> = -4.5 V, I <sub>D</sub> = -1 A                           | -    | 0.156 | 0.188     | $\Omega$ |  |

| Forward transconductance a                    | 9 <sub>fs</sub>                      | $V_{DS} = -15 \text{ V}, I_D = -2.6 \text{ A}$                            | -    | 5     | -         | S        |  |

| Dynamic <sup>b</sup>                          |                                      |                                                                           |      |       |           |          |  |

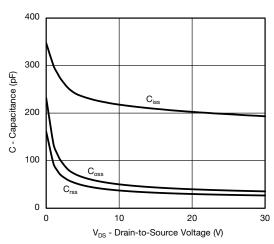

| Input capacitance                             | C <sub>iss</sub>                     |                                                                           | -    | 210   | -         |          |  |

| Output capacitance                            | C <sub>oss</sub>                     | $V_{DS} = -15 \text{ V}, V_{GS} = 0 \text{ V}, f = 1 \text{ MHz}$         | -    | 45    | -         | pF       |  |

| Reverse transfer capacitance                  | C <sub>rss</sub>                     |                                                                           | -    | 33    | -         |          |  |

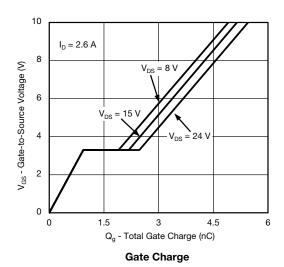

| Total gate charge                             | Qg                                   | $V_{DS} = -15 \text{ V}, V_{GS} = -10 \text{ V}, I_D = -2.6 \text{ A}$    | -    | 5.2   | 8         |          |  |

|                                               |                                      |                                                                           | -    | 2.7   | 4         |          |  |

| Gate-source charge                            | Q <sub>gs</sub>                      | $V_{DS} = -15 \text{ V}, V_{GS} = -4.5 \text{ V}, I_{D} = -2.6 \text{ A}$ | -    | 0.94  | -         | nC       |  |

| Gate-drain charge                             | Q <sub>gd</sub>                      |                                                                           | -    | 1.3   | -         |          |  |

| Gate resistance                               | $R_g$                                | f = 1 MHz                                                                 | 2    | 7     | 14        | Ω        |  |

| Turn-on delay time                            | t <sub>d(on)</sub>                   |                                                                           | -    | 39    | 59        |          |  |

| Rise time                                     | t <sub>r</sub>                       | $V_{DD}$ = -15 V, $R_L$ = 7.1 $\Omega$                                    | -    | 25    | 38        |          |  |

| Turn-off delay time                           | t <sub>d(off)</sub>                  | $I_D\cong$ -2.1 A, $V_{GEN}$ = -4.5 V, $R_g$ = 1 $\Omega$                 | -    | 13    | 20        |          |  |

| Fall time                                     | t <sub>f</sub>                       |                                                                           | -    | 9     | 18        |          |  |

| Turn-on delay time                            | t <sub>d(on)</sub>                   |                                                                           | -    | 5     | 10        | ns       |  |

| Rise time                                     | t <sub>r</sub>                       | $V_{DD}$ = -15 V, $R_L$ = 7.1 $\Omega$                                    | -    | 10    | 20        | 1        |  |

| Turn-off delay time                           | t <sub>d(off)</sub>                  | $I_D\cong$ -2.1 A, $V_{GEN}$ = -10 V, $R_g$ = 1 $\Omega$                  | -    | 14    | 21        |          |  |

| Fall time                                     | t <sub>f</sub>                       |                                                                           | -    | 7     | 14        |          |  |

| Drain-Source Body Diode Characteristic        | s                                    |                                                                           | •    | •     |           |          |  |

| Continuous source-drain diode current         | Is                                   | T <sub>C</sub> = 25 °C                                                    | -    | -     | 1.17      | ^        |  |

| Pulse diode forward current                   | I <sub>SM</sub>                      |                                                                           | -    | -     | 8         | A        |  |

| Body diode voltage                            | V <sub>SD</sub>                      | $I_S = -2.1 \text{ A}, V_{GS} = 0 \text{ V}$                              | -    | 0.85  | 1.2       | V        |  |

| Body diode reverse recovery time              | t <sub>rr</sub>                      |                                                                           | -    | 13    | 20        | ns       |  |

| Body diode reverse recovery charge            | Q <sub>rr</sub>                      | $I_F = -2.1 \text{ A}, \text{ di/dt} = 100 \text{ A/}\mu\text{s},$        | -    | 6     | 12        | nC       |  |

| Reverse recovery fall time                    | t <sub>a</sub>                       | T <sub>J</sub> = 25 °C                                                    | -    | 9     | -         |          |  |

| Reverse recovery rise time                    | t <sub>b</sub>                       |                                                                           | _    | 4     | _         | ns       |  |

#### Notes

- a. Pulse test; pulse width  $\leq$  300 µs, duty cycle  $\leq$  2 %

- b. Guaranteed by design, not subject to production testing

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

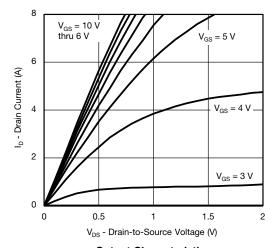

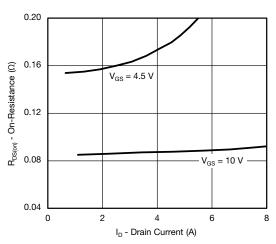

## TYPICAL CHARACTERISTICS (25 °C, unless otherwise noted)

## **Output Characteristics**

On-Resistance vs. Drain Current and Gate Voltage

**Transfer Characteristics**

Capacitance

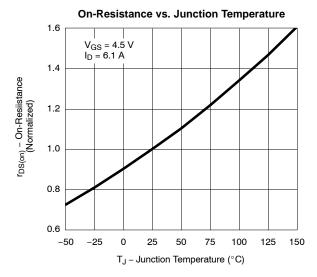

On-Resistance vs. Junction Temperature

# TYPICAL CHARACTERISTICS (25 °C, unless otherwise noted)

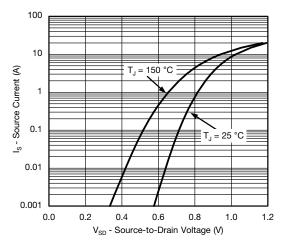

#### Source-Drain Diode Forward Voltage

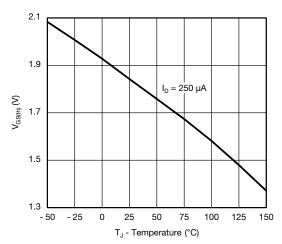

**Threshold Voltage**

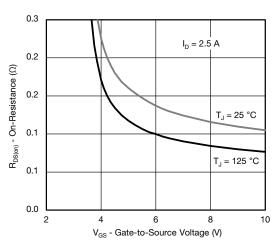

On-Resistance vs. Gate-to-Source Voltage

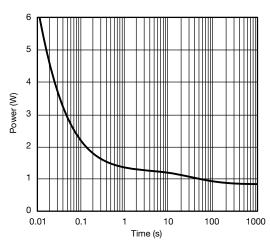

Single Pulse Power (Junction-to-Ambient)

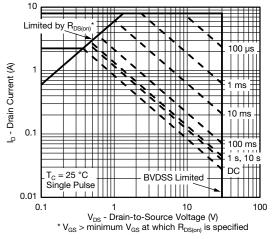

Safe Operating Area, Junction-to-Ambient

# Vishay Siliconix

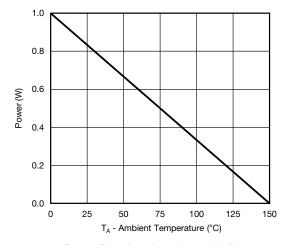

## TYPICAL CHARACTERISTICS (25 °C, unless otherwise noted)

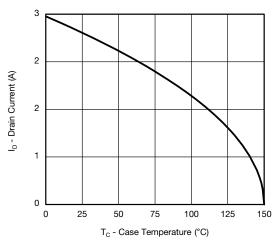

Current Derating a

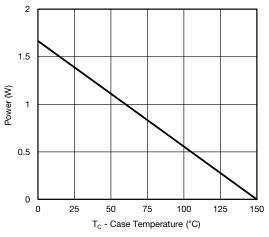

Power Derating, Junction-to-Ambient

#### Note

a. The power dissipation P<sub>D</sub> is based on T<sub>J</sub> max. = 150 °C, using junction-to-case thermal resistance, and is more useful in settling the upper dissipation limit for cases where additional heatsinking is used. It is used to determine the current rating, when this rating falls below the package limit

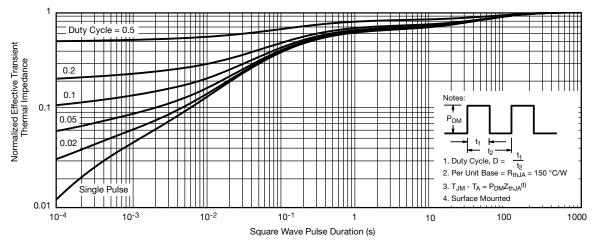

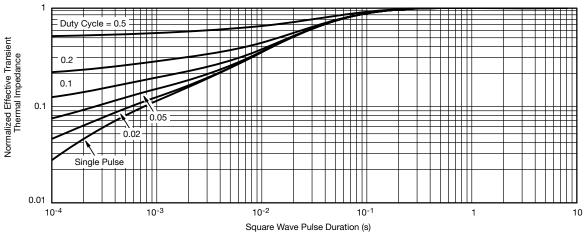

# TYPICAL CHARACTERISTICS (25 °C, unless otherwise noted)

Normalized Thermal Transient Impedance, Junction-to-Ambient

Normalized Thermal Transient Impedance, Junction-to-Foot

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package / tape drawings, part marking, and reliability data, see <a href="https://www.vishay.com/ppg?67331">www.vishay.com/ppg?67331</a>.

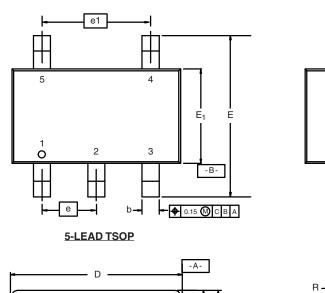

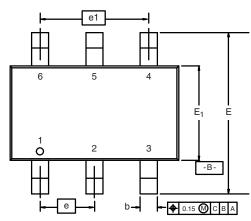

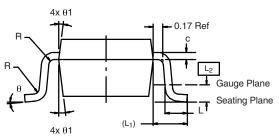

TSOP: 5/6-LEAD

**JEDEC Part Number: MO-193C**

**6-LEAD TSOP**

D A<sub>2</sub> A

Seating Plane

|                                             | MILLIMETERS |          |      | ı         | NCHES      |       |

|---------------------------------------------|-------------|----------|------|-----------|------------|-------|

| Dim                                         | Min         | Nom      | Max  | Min       | Nom        | Max   |

| Α                                           | 0.91        | -        | 1.10 | 0.036     | -          | 0.043 |

| A <sub>1</sub>                              | 0.01        | -        | 0.10 | 0.0004    | -          | 0.004 |

| A <sub>2</sub>                              | 0.90        | -        | 1.00 | 0.035     | 0.038      | 0.039 |

| b                                           | 0.30        | 0.32     | 0.45 | 0.012     | 0.013      | 0.018 |

| С                                           | 0.10        | 0.15     | 0.20 | 0.004     | 0.006      | 0.008 |

| D                                           | 2.95        | 3.05     | 3.10 | 0.116     | 0.120      | 0.122 |

| Е                                           | 2.70        | 2.85     | 2.98 | 0.106     | 0.112      | 0.117 |

| E <sub>1</sub>                              | 1.55        | 1.65     | 1.70 | 0.061     | 0.065      | 0.067 |

| е                                           |             | 0.95 BSC |      | (         | 0.0374 BSC | ;     |

| e <sub>1</sub>                              | 1.80        | 1.90     | 2.00 | 0.071     | 0.075      | 0.079 |

| L                                           | 0.32        | -        | 0.50 | 0.012     | -          | 0.020 |

| L <sub>1</sub>                              | 0.60 Ref    |          |      | 0.024 Ref |            |       |

| L <sub>2</sub>                              | 0.25 BSC    |          |      | 0.010 BSC |            |       |

| R                                           | 0.10        | -        | -    | 0.004     | -          | -     |

| θ                                           | 0°          | 4°       | 8°   | 0°        | 4°         | 8°    |

| $\theta_1$                                  | 7° Nom      |          |      |           | 7° Nom     |       |

| ECN: C-06593-Rev. I, 18-Dec-06<br>DWG: 5540 |             |          |      |           |            |       |

Document Number: 71200 www.vishay.com 18-Dec-06 uww.vishay.com

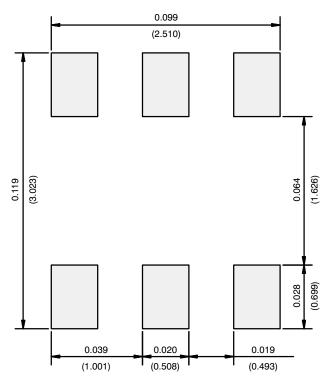

# Mounting LITTLE FOOT® TSOP-6 Power MOSFETs

Surface mounted power MOSFET packaging has been based on integrated circuit and small signal packages. Those packages have been modified to provide the improvements in heat transfer required by power MOSFETs. Leadframe materials and design, molding compounds, and die attach materials have been changed. What has remained the same is the footprint of the packages.

The basis of the pad design for surface mounted power MOSFET is the basic footprint for the package. For the TSOP-6 package outline drawing see http://www.vishay.com/doc?71200 and see http://www.vishay.com/doc?72610 for the minimum pad footprint. In converting the footprint to the pad set for a power MOSFET, you must remember that not only do you want to make electrical connection to the package, but you must made thermal connection and provide a means to draw heat from the package, and move it away from the package.

In the case of the TSOP-6 package, the electrical connections are very simple. Pins 1, 2, 5, and 6 are the drain of the MOSFET and are connected together. For a small signal device or integrated circuit, typical connections would be made with traces that are 0.020 inches wide. Since the drain pins serve the additional function of providing the thermal connection to the package, this level of connection is inadequate. The total cross section of the copper may be adequate to carry the current required for the application, but it presents a large thermal impedance. Also, heat spreads in a circular fashion from the heat source. In this case the drain pins are the heat sources when looking at heat spread on the PC board.

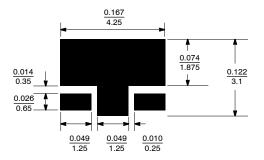

Figure 1 shows the copper spreading recommended footprint for the TSOP-6 package. This pattern shows the starting point for utilizing the board area available for the heat spreading copper. To create this pattern, a plane of copper overlays the basic pattern on pins 1,2,5, and 6. The copper plane connects the drain pins electrically, but more importantly provides planar copper to draw heat from the drain leads and start the process of spreading the heat so it can be dissipated into the ambient air. Notice that the planar copper is shaped like a "T" to move heat away from the drain leads in all directions. This pattern uses all the available area underneath the body for this purpose.

FIGURE 1. Recommended Copper Spreading Footprint

Since surface mounted packages are small, and reflow soldering is the most common form of soldering for surface mount components, "thermal" connections from the planar copper to the pads have not been used. Even if additional planar copper area is used, there should be no problems in the soldering process. The actual solder connections are defined by the solder mask openings. By combining the basic footprint with the copper plane on the drain pins, the solder mask generation occurs automatically.

A final item to keep in mind is the width of the power traces. The absolute minimum power trace width must be determined by the amount of current it has to carry. For thermal reasons, this minimum width should be at least 0.020 inches. The use of wide traces connected to the drain plane provides a low impedance path for heat to move away from the device.

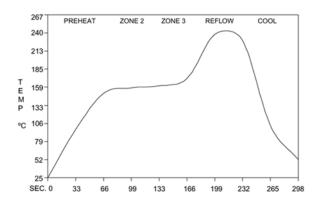

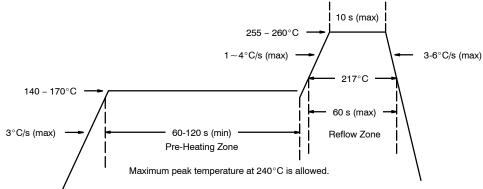

#### **REFLOW SOLDERING**

Vishay Siliconix surface-mount packages meet solder reflow reliability requirements. Devices are subjected to solder reflow as a test preconditioning and are then reliability-tested using temperature cycle, bias humidity, HAST, or pressure pot. The solder reflow temperature profile used, and the temperatures and time duration, are shown in Figures 2 and 3.

| Ramp-Up Rate                | +6°C/Second Maximum |

|-----------------------------|---------------------|

| Temperature @ 155 ± 15°C    | 120 Seconds Maximum |

| Temperature Above 180°C     | 70 – 180 Seconds    |

| Maximum Temperature         | 240 +5/-0°C         |

| Time at Maximum Temperature | 20 - 40 Seconds     |

| Ramp-Down Rate              | +6°C/Second Maximum |

FIGURE 2. Solder Reflow Temperature Profile

Document Number: 71743 www.vishay.com 27-Feb-04

# **Vishay Siliconix**

FIGURE 3. Solder Reflow Temperature and Time Durations

## **THERMAL PERFORMANCE**

A basic measure of a device's thermal performance is the junction-to-case thermal resistance,  $R\theta_{jc},$  or the junction-to-foot thermal resistance,  $R\theta_{\mbox{\scriptsize if}}.$  This parameter is measured for the device mounted to an infinite heat sink and is therefore a characterization of the device only, in other words, independent of the properties of the object to which the device is mounted. Table 1 shows the thermal performance of the TSOP-6.

| TABLE 1.                                   |        |  |  |  |

|--------------------------------------------|--------|--|--|--|

| Equivalent Steady State Performance—TSOP-6 |        |  |  |  |

| Thermal Resistance $R\theta_{jf}$          | 30°C/W |  |  |  |

# SYSTEM AND ELECTRICAL IMPACT OF TSOP-6

In any design, one must take into account the change in MOSFET r<sub>DS(on)</sub> with temperature (Figure 4).

FIGURE 4. Si3434DV

www.vishay.com Document Number: 71743 27-Feb-04

# VISHAY.

## **RECOMMENDED MINIMUM PADS FOR TSOP-6**

Recommended Minimum Pads Dimensions in Inches/(mm)

Return to Index

# **Legal Disclaimer Notice**

Vishay

# **Disclaimer**

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and / or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.