# SY88403BL

# 3.3V 4.25 Gbps CML Low-Power Limiting Post Amplifier with TTL LOS

#### Features

- Multi-Rate up to 4.25 Gbps Operation

- 5 mV<sub>PP</sub> Input Sensitivity

- Low Noise 50Ω CML Data Outputs

- 800 mV<sub>PP</sub> Output Swing

- 60 ps Edge Rates

- 1ps<sub>RMS</sub> Typ. Random Jitter

- 10ps<sub>PP</sub> Typ. Deterministic Jitter

- Chatter-Free Loss-of-Signal (LOS) Output

- 3.5 dB Electrical Hysteresis

- OC-TTL Output with Internal 4.75 k $\Omega$  Pull-Up Resistor

- Programmable LOS Sensitivity Using Single External Resistor

- Internal 50Ω Data Input Termination

- TTL /EN Input Allows Feedback from LOS

- Wide Operating Range:

- Single 3.3V ±10% Power Supply

- Industrial Temperature Range: -40°C to +85°C

- Available in a 16-pin QFN Package

#### Applications

- 1.062 Gbps, 2.125 Gbps, and 4.25 Gbps Fibre Channel

- Cable Driver

- Small Form Factor (SFF) and Small Form Factor Pluggable (SFP) Transceivers

- High-Gain Line Driver and Line Receiver

#### **General Description**

The SY88403BL is a low-power limiting post amplifier optimized for copper applications. The device connects to typical transimpedance amplifiers (TIAs). The linear signal output from TIAs can contain significant amounts of noise and may vary in amplitude over time. The SY88403BL quantizes these signals and outputs typically 800 mV<sub>PP</sub> voltage-limited waveforms.

The SY88403BL operates from a single +3.3V  $\pm 10\%$  power supply, over an industrial temperature range of  $-40^{\circ}$ C to +85°C. With its wide bandwidth and high gain, signals with data rates up to 4.25 Gbps and as small as 5 mV<sub>PP</sub> can be amplified to drive devices with CML inputs or AC-coupled PECL inputs.

The SY88403BL incorporates a loss-of-signal (LOS) open-collector TTL output with internal 4.75 k $\Omega$  pull-up resistor. A programmable loss-of-signal level set pin (LOSLVL) sets the sensitivity of the input amplitude detection.

LOS asserts high if the input amplitude falls below the threshold set by LOSLVL and de-asserts low otherwise. LOS can be fed back to the enable bar (/EN) input to maintain output stability under a loss of signal condition. /EN de-asserts the true output signal without removing the input signal. Typically, 3.5 dB LOS hysteresis is provided to prevent chattering.

#### Markets

- Copper Interconnect

- Datacom and Telecom

- Storage Area Network (SAN)

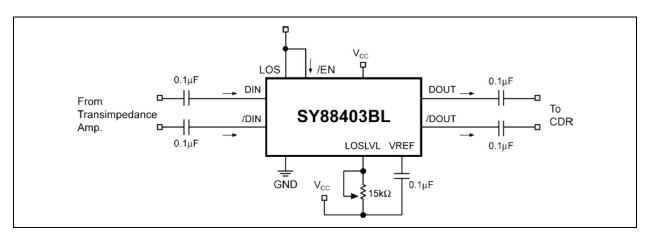

# **Typical Application Circuit**

# 1.0 ELECTRICAL CHARACTERISTICS

#### Absolute Maximum Ratings †

| Supply Voltage (V <sub>CC</sub> ) |        |

|-----------------------------------|--------|

| /EN, LOSLVL Voltage               |        |

| REF Current                       | ±1 mA  |

| LOS Current                       |        |

| DOUT, /DOUT Current               | ±25 mA |

| DIN, /DIN Current                 | ±10 mA |

# Operating Ratings ‡

**† Notice:** Permanent device damage may occur if ratings in the absolute maximum ratings section are exceeded. This is a stress rating only and functional operation is not implied for conditions other than those detailed in the operational sections of this data sheet. Exposure to absolute maximum ratings conditions for extended periods may affect device reliability.

**‡** Notice: The data sheet limits are not guaranteed if the device is operated beyond the operating ratings.

# DC ELECTRICAL CHARACTERISTICS

$V_{CC}$  = +3.0V to +3.6V;  $R_L$  = 50 $\Omega$  to  $V_{CC}$ ;  $T_A$  = -40°C to +85°C; typical values at  $V_{CC}$  = +3.3V,  $T_A$  = +25°C.

| Parameter                      | Symbol              | Min.                    | Тур.                  | Max.             | Units | Conditions   |

|--------------------------------|---------------------|-------------------------|-----------------------|------------------|-------|--------------|

| Power Supply Current           |                     | _                       | 25                    | 42               | mA    | 3.3V, Note 1 |

| Power Supply Current           | I <sub>CC</sub>     | _                       | 41                    | 62               | mA    | 3.3V, Note 2 |

| REF Voltage                    | V <sub>REF</sub>    | —                       | V <sub>CC</sub> – 1.3 | —                | V     | —            |

| LOSLVL Voltage Range           | V <sub>LOSLVL</sub> | VREF                    | _                     | V <sub>CC</sub>  | V     | —            |

| DOUT, /DOUT HIGH Voltage       | V <sub>OH</sub>     | $V_{CC} - 0.020$        | $V_{CC} - 0.005$      | V <sub>CC</sub>  | V     | Note 3       |

| DOUT, /DOUT LOW Voltage        | V <sub>OL</sub>     | V <sub>CC</sub> – 0.475 | $V_{CC} - 0.400$      | $V_{CC} - 0.350$ | V     | 3.3V, Note 3 |

| DC Differential Output Voltage | V <sub>OD_DC</sub>  | 700                     | 800                   | 950              | mV    | Note 3       |

| Differential Output Offset     | V <sub>OFFSET</sub> | —                       | _                     | ±80              | mV    | —            |

| Single-Ended Output Impedance  | ZO                  | 40                      | 50                    | 60               | Ω     | —            |

| Single-Ended Input Impedance   | ZI                  | 40                      | 50                    | 60               | Ω     | —            |

# TTL DC ELECTRICAL CHARACTERISTICS

$V_{CC}$  = 3.0V to 3.6V;  $T_A$  = -40°C to +85°C.

| Parameter              | Symbol          | Min. | Тур. | Max.            | Units | Conditions             |

|------------------------|-----------------|------|------|-----------------|-------|------------------------|

| LOS Output HIGH Level  | V <sub>OH</sub> | 2.4  | _    | V <sub>CC</sub> | V     | Sourcing 100 µA        |

| LOS Output LOW Level   | V <sub>OL</sub> | _    | _    | 0.5             | V     | Sinking 2 mA           |

| /EN Input HIGH Voltage | V <sub>IH</sub> | 2.0  |      | -               | V     | —                      |

| /EN Input LOW Voltage  | V <sub>IL</sub> | _    | _    | 0.8             | V     | —                      |

| /EN Input HIGH Current | IIH             | _    | _    | 20              | μA    | V <sub>IN</sub> = 2.7V |

|                        |                 |      |      | 100             | μA    | $V_{IN} = V_{CC}$      |

| /EN Input LOW Current  | ۱ <sub>IL</sub> | -0.3 | _    | _               | mA    | V <sub>IN</sub> = 0.5V |

**Note 1:** Excludes current of CML output stage. See "Detailed Description."

2: Total device current with no output load.

3: Output levels are based on a 50 $\Omega$  to V<sub>CC</sub> load impedance. If the load impedance is different, the output level will be changed. Amplifier is in limiting mode. Measured at 155 Mbps with 20 mV<sub>PP</sub> input and PRBS-23 data pattern and 50 $\Omega$  load.

# AC ELECTRICAL CHARACTERISTICS

$V_{CC}$  = +3.0V to +3.6V;  $T_A$  = -40°C to +85°C;  $R_L$  = 50 $\Omega$  to  $V_{CC}$ ; typical values at  $V_{CC}$  = +3.3V,  $T_A$  = 25°C.

| Parameter                             | Symbol                          | Min. | Тур. | Max. | Units             | Conditions                                        |

|---------------------------------------|---------------------------------|------|------|------|-------------------|---------------------------------------------------|

| Output Rise/Fall Time<br>(20% to 80%) | t <sub>r</sub> , t <sub>f</sub> | _    | 60   | 120  | ps                | Note 1                                            |

| Deterministic Jitter                  | +                               | -    | 10   | —    | ps <sub>PP</sub>  | Note 2                                            |

| Random Jitter                         | t <sub>JITTER</sub>             | _    | 1    | —    | ps <sub>RMS</sub> | Note 3                                            |

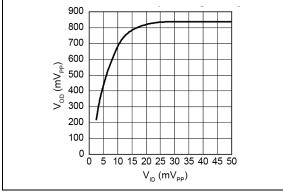

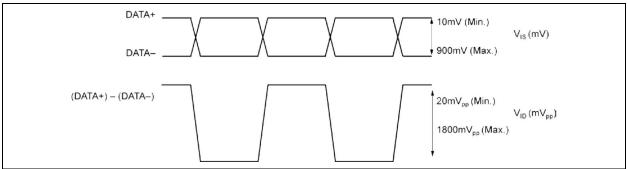

| Differential Input Voltage Swing      | V <sub>ID</sub>                 | 5    | _    | 1800 | mV <sub>PP</sub>  | See Figure 1                                      |

| AC Differential Output Voltage        | V <sub>OD_AC</sub>              | 600  | 800  | 950  | mV <sub>PP</sub>  | Note 4                                            |

| LOS Release Time                      | t <sub>OFF</sub>                | _    | 2    | 10   | μs                | —                                                 |

| LOS Assert Time                       | t <sub>ON</sub>                 | _    | 2    | 10   | μs                | —                                                 |

| Low LOS Assert Level                  | LOS <sub>AL</sub>               | —    | 8    | —    | mV <sub>PP</sub>  | $R_{LOSLVL}$ = 15 k $\Omega$ , Note 5             |

| Low LOS De-assert Level               | LOS <sub>DL</sub>               | _    | 12   | _    | mV <sub>PP</sub>  | $R_{LOSLVL} = 15 \text{ k}\Omega, \text{ Note 5}$ |

| Low LOS Hysteresis                    | HYSL                            | 2    | 3.5  | 4.5  | dB                | $R_{LOSLVL} = 15 \text{ k}\Omega$ , Note 6        |

| Medium LOS Assert Level               | LOS <sub>AM</sub>               | 12   | 17   | —    | mV <sub>PP</sub>  | $R_{LOSLVL} = 5 k\Omega$ , Note 5                 |

| Medium LOS De-assert Level            | LOS <sub>DM</sub>               | _    | 25   | 33   | mV <sub>PP</sub>  | $R_{LOSLVL} = 5 k\Omega$ , Note 5                 |

| LOS Hysteresis                        | HYS <sub>M</sub>                | 2    | 3.5  | 4.5  | dB                | $R_{LOSLVL} = 5 k\Omega$ , Note 6                 |

| High LOS Assert Level                 | LOS <sub>AH</sub>               | 34   | 47   | —    | mV <sub>PP</sub>  | $R_{LOSLVL} = 100\Omega$ , Note 5                 |

| High LOS De-assert Level              | LOS <sub>DH</sub>               | _    | 70   | 83   | mV <sub>PP</sub>  | $R_{LOSLVL} = 100\Omega$ , Note 5                 |

| High LOS Hysteresis                   | HYS <sub>H</sub>                | 2    | 3.5  | 4.5  | dB                | $R_{LOSLVL} = 100\Omega$ , Note 6                 |

| LOS Sensitivity Range                 | V <sub>SR</sub>                 | 20   | _    | 35   | mV <sub>PP</sub>  | —                                                 |

| Differential Voltage Gain             | A <sub>V(DIFF)</sub>            | 32   | 38   |      | dB                | —                                                 |

| Single-Ended Small-Signal Gain        | S <sub>21</sub>                 | 26   | 32   | _    | dB                | —                                                 |

Note 1: Amplifier in limiting mode. Input is a 200 MHz square wave.

**2:** Deterministic jitter measured using 4.25 Gbps K28.5 pattern,  $V_{ID}$  = 20 mV<sub>PP</sub>.

3: Random jitter measured using 4.25 Gbps K28.7 pattern, V<sub>ID</sub> = 20 mV<sub>PP</sub>.

- **4:** Differential output swing measured at 4.25 Gbps with 20 mV<sub>PP</sub> input and PRBS-23 data pattern and 50Ω load.

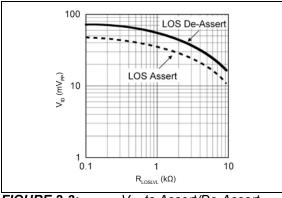

- **5:** See "Typical Operating Characteristics" for a graph showing how to choose a particular R<sub>LOSLVL</sub> for a particular LOS assert and its associated de-assert amplitude.

- 6: This specification defines electrical hysteresis as 20log(LOS De-assert/LOS Assert). The ratio between optical hysteresis and electrical hysteresis is found to vary between 1.5 and 2 depending on the level of received optical power and ROSA characteristics. Based on that ratio, the optical hysteresis corresponding to the electrical hysteresis range 2 dB to 4.5 dB shown in the AC characteristics table will be 0.5 dB to 3 dB Optical Hysteresis.

## **TEMPERATURE SPECIFICATIONS (Note 1)**

| Parameters                          | Sym.           | Min. | Тур. | Max. | Units | Conditions         |  |  |

|-------------------------------------|----------------|------|------|------|-------|--------------------|--|--|

| Temperature Ranges                  |                |      |      |      |       |                    |  |  |

| Junction Temperature Range          | ТJ             | -40  | _    | +120 | °C    | —                  |  |  |

| Ambient Temperature                 | Τ <sub>Α</sub> | -40  | _    | +85  | °C    | —                  |  |  |

| Lead Temperature                    | _              |      | _    | +260 | °C    | Soldering, 10 sec. |  |  |

| Storage Temperature                 | Τ <sub>S</sub> | -65  | —    | +150 | °C    | —                  |  |  |

| Package Thermal Resistance (Note 2) |                |      |      |      |       |                    |  |  |

| QFN (Still-Air)                     | $\theta_{JA}$  |      | 61   | _    | °C/W  | —                  |  |  |

| QFN                                 | $\Psi_{JB}$    |      | 38   | _    | °C/W  | —                  |  |  |

**Note 1:** The maximum allowable power dissipation is a function of ambient temperature, the maximum allowable junction temperature and the thermal resistance from junction to air (i.e., T<sub>A</sub>, T<sub>J</sub>, θ<sub>JA</sub>). Exceeding the maximum allowable power dissipation will cause the device operating junction temperature to exceed the maximum +85°C rating. Sustained junction temperatures above +85°C can impact the device reliability.

**2:** Thermal performance assumes the use of a 4-layer PCB. Exposed pad must be soldered (or equivalent) to the device's most negative potential on the PCB.

#### 2.0 TYPICAL PERFORMANCE CURVES

Note: The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

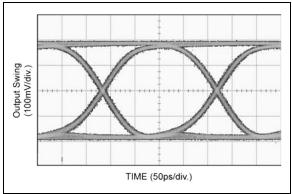

3.3V, 25°C 20 mV<sub>PP</sub> Input FIGURE 2-1: @4.25 Gbps  $2^{23} - 1$  PRBS,  $R_{LOAD} = 50$  to  $V_{CC}$ .

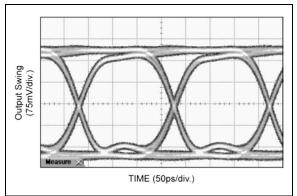

FIGURE 2-2: 1800 mV<sub>PP</sub> Input @4.25 Gbps 2<sup>23</sup> – 1 PRBS.

FIGURE 2-3: V<sub>ID</sub> to Assert/De-Assert LOS vs. RLOSLVL.

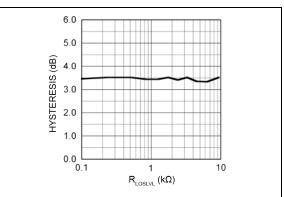

FIGURE 2-4: R<sub>LOSLVL</sub>.

LOS Hysteresis vs.

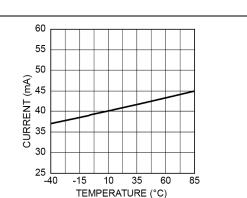

FIGURE 2-5: Power Supply Current vs. Temperature.

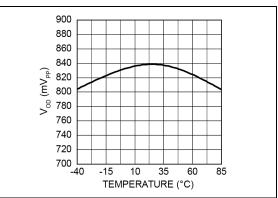

FIGURE 2-6: Differential Output Voltage Swing vs. Temperature (Amplifier in Limiting Mode).

**FIGURE 2-7:** Differential Output Voltage Swing vs. Differential Input Voltage Swing.

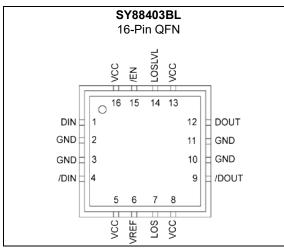

# 3.0 PIN DESCRIPTIONS

#### Package Type

The descriptions of the pins are listed in Table 3-1.

#### TABLE 3-1: PIN FUNCTION TABLE

| QFN Pin<br>Number          | Pin Name       | Туре                                                                 | Description                                                                                                                                         |

|----------------------------|----------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 4                       | DIN, /DIN      | Differential Data Input                                              | Differential Data Input. Each pin internally terminates to REF through $50\Omega$ .                                                                 |

| 2, 3,10, 11<br>Exposed Pad | GND            | Ground                                                               | Device Ground. Exposed pad must be soldered (or equivalent) to the same potential as the ground pins.                                               |

| 5, 8, 13, 16               | VCC            | Power Supply                                                         | Positive Power Supply. Bypass with 0.1 $\mu$ F  0.01 $\mu$ F low ESR capacitors. 0.01 $\mu$ F capacitors should be as close as possible to VCC pin. |

| 6                          | VREF           | _                                                                    | Reference Voltage. Bypass with 0.01 $\mu$ F low ESR capacitor from VREF to VCC to stabilize LOS <sub>LVL</sub> and V <sub>REF</sub> .               |

| 7                          | LOS            | Open Collector TTL<br>Ouput with Internal<br>4.75kΩ Pull-Up Resistor | Loss-of-Signal: Asserts high when the data input amplitude falls below the threshold set by LOSLVL.                                                 |

| 9, 12                      | DOUT,<br>/DOUT | Differential CML Output                                              | Differential Data Output.                                                                                                                           |

| 14                         | LOSLVL         | Input: Default is maxi-<br>mum sensitivity.                          | Loss-of-Signal Level Set: A resistor from this pin to VCC sets the threshold for the data input amplitude at which the LOS output will be asserted. |

| 15                         | /EN            | TTL Input: Default is<br>high.                                       | Enable Bar: De-asserts true data output when high. Incorporates 25 k $\Omega$ pull-up to VCC.                                                       |

# 4.0 FUNCTIONAL DESCRIPTION

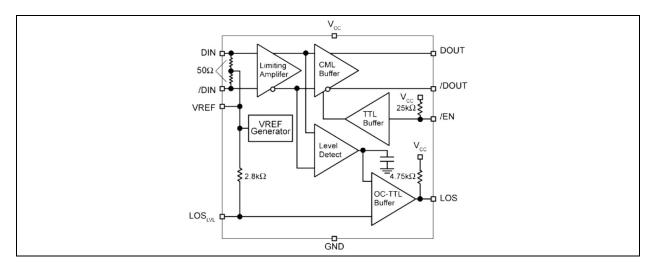

#### 4.1 Functional Block Diagram

#### 4.2 Detailed Description

The SY88403BL low-power limiting post amplifier operates from a single +3.3V power supply, over temperatures from  $-40^{\circ}$ C to +85°C. Signals with data rates up to 4.25Gbps and as small as 5 mV<sub>PP</sub> can be amplified. Figure 4-1 shows the allowed input voltage swing. The SY88403BL generates an LOS output, allowing feedback to /EN for output stability. LOSLVL sets the sensitivity of the input amplitude detection.

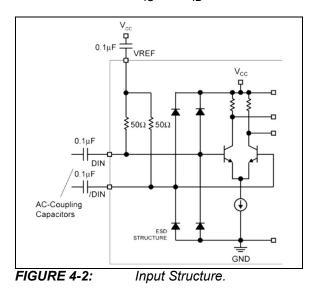

#### 4.2.1 INPUT AMPLIFIER/BUFFER

The SY88403BL's inputs are internally terminated with  $50\Omega$  to REF. If not affected by this internal termination scheme, upstream devices need to be AC-coupled to the SY88403BL's inputs. Figure 4-2 shows a simplified schematic of the input stage.

The high-sensitivity of the input amplifier allows signals as small as 5 mV<sub>PP</sub> to be detected and amplified. The input amplifier allows input signals as large as 1800 mV<sub>PP</sub>. Input signals are linearly amplified with a typically 38 dB differential voltage gain. Since it is a limiting amplifier, the SY88403BL outputs typically 800 mV<sub>PP</sub> voltage-limited waveforms for input signals that are greater than 20 mV<sub>PP</sub>. Applications requiring the SY88403BL to operate with high-gain should have the upstream TIA placed as close as possible to the SY88403BL's input pins to ensure the best performance of the device.

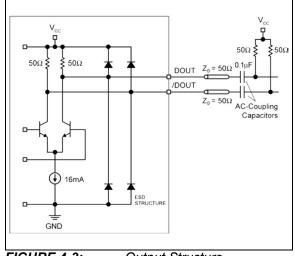

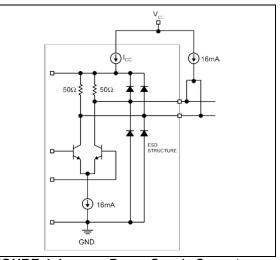

#### 4.2.2 OUTPUT BUFFER

The SY88403BL's CML output buffer is designed to drive 50 $\Omega$  lines. The output buffer requires appropriate termination for proper operation. An external 50 $\Omega$  resistor to V<sub>CC</sub> or equivalent for each output pin provides this. Figure 4-3 shows a simplified schematic of the output stage and includes an appropriate

termination method. Of course, driving a downstream device with a CML input that is internally terminated with 50 $\Omega$  to V<sub>CC</sub> eliminates the need for external termination. As noted in the previous section, the amplifier outputs typically 800 mV<sub>PP</sub> waveforms across 25 $\Omega$  total loads. The output buffer thus switches typically 16 mA tail-current. Figure 4-4 shows the power supply current measurement, which excludes the 16 mA tail-current.

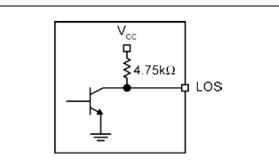

#### 4.2.3 LOSS-OF-SIGNAL

SY88403BL The incorporates а chatter-free loss-of-signal (LOS) open-collector TTL output with internal 4.75 kΩ pull-up resistor as shown in Figure 4-5. LOS is used to determine that the input amplitude is too small to be considered a valid input. LOS asserts high if the input amplitude falls below the threshold set by LOSLVL and de-asserts low otherwise. LOS can be fed back to the enable (/EN) input to maintain output stability under a loss of signal condition. /EN de-asserts low the true output signal without removing the input signals. Typically 3.5 dB LOS hysteresis is provided to prevent chattering.

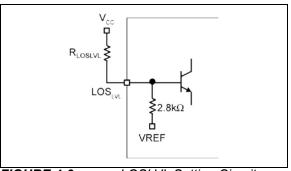

#### 4.2.4 LOSS-OF-SIGNAL LEVEL SET

A programmable loss-of-signal level set pin (LOSLVL) sets the threshold of the input amplitude detection. Connecting an external resistor between VCC and LOSLVL sets the voltage at LOSLVL. This voltage ranges from  $V_{CC}$  to  $V_{REF}$ . The external resistor creates a voltage divider between  $V_{CC}$  and  $V_{REF}$  as shown in Figure 4-6. If desired, an appropriate external voltage may be applied rather than using a resistor. The relationship between  $V_{LOSLVL}$  and  $R_{LOSLVL}$  is given by:

#### **EQUATION 4-1:**

$$V_{LOSLVL} = V_{CC} - \left(1.3 \frac{R_{LOSLVL}}{R_{LOSLVL} + 2.8}\right)$$

Where:

Voltages are in volts and resistances are in  $k\Omega$ .

The smaller the external resistor, implying a smaller voltage difference from LOSLVL to VCC, lowers the LOS sensitivity. Hence, larger input amplitude is required to de-assert LOS. "Typical Operating Characteristics" contains graphs showing the relationship between the input amplitude detection sensitivity and  $R_{LOSLVL}$ .

#### 4.2.5 HYSTERESIS

The SY88403BL provides typically 3.5 dB LOS electrical hysteresis. By definition, a power ratio measured in dB is 10log (power ratio). Power is calculated as  $V_{IN}^{2}/R$  for an electrical signal. Hence the same ratio can be stated as 20log (voltage ratio). While in linear mode, the electrical voltage input changes linearly with the optical power and hence the ratios change linearly. Therefore, the optical hysteresis in dB is half the electrical hysteresis in dB given in the datasheet. The SY88403BL provides typically 1.75 dB LOS optical hysteresis. As the SY88403BL is an electrical device, this datasheet refers to hysteresis in electrical terms. With 3.5 dB LOS hysteresis, a voltage factor of 1.5 is required to de-assert LOS.

# SY88403BL

V<sub>IS</sub> and V<sub>ID</sub> Definition.

FIGURE 4-3:

Output Structure.

FIGURE 4-4: Power Supply Current Measurement.

LOS Output Structure.

FIGURE 4-6:

LOSLVL Setting Circuit.

# 5.0 PACKAGING INFORMATION

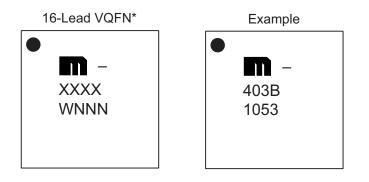

## 5.1 Package Marking Information

| Legend: | Y<br>YY<br>WW<br>NNN<br>@3<br>*        | Product code or customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC <sup>®</sup> designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |

|---------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| t d     | be carried<br>characters<br>the corpor | nt the full Microchip part number cannot be marked on one line, it will<br>d over to the next line, thus limiting the number of available<br>for customer-specific information. Package may or may not include<br>ate logo.<br>(_) and/or Overbar ( <sup>-</sup> ) symbol may not be to scale.                                                                                                              |

|         |                                        |                                                                                                                                                                                                                                                                                                                                                                                                             |

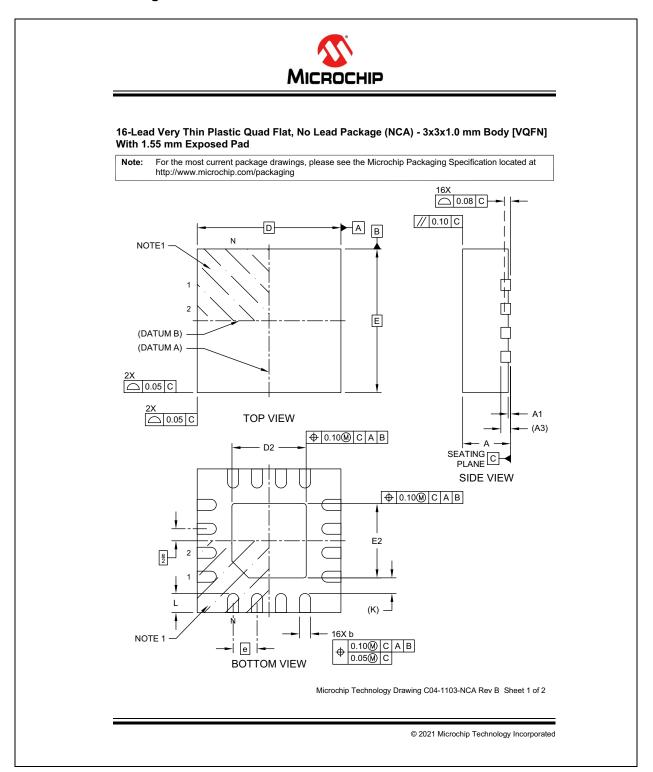

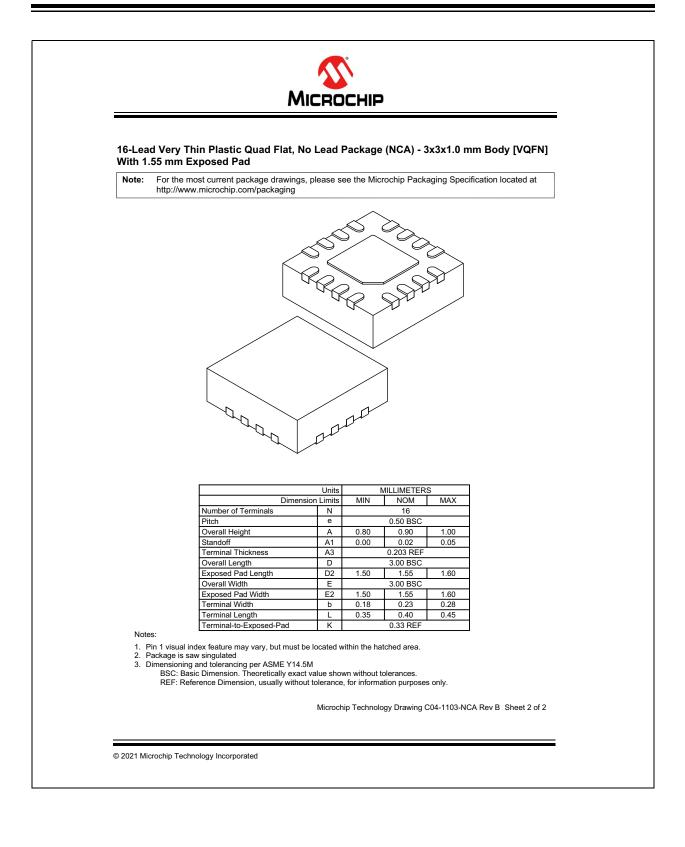

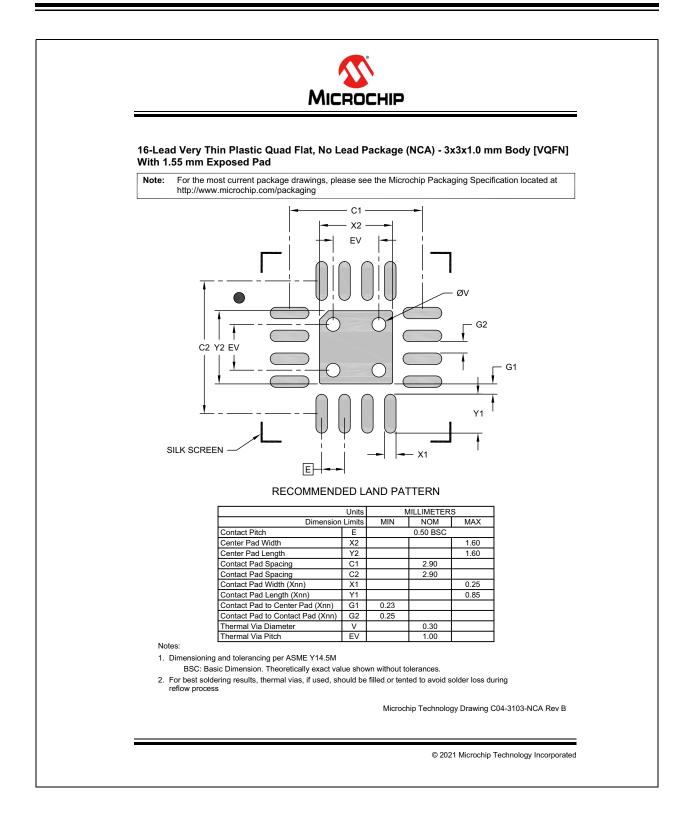

#### 16-Lead QFN Package Outline and Recommended Land Pattern

NOTES:

# APPENDIX A: REVISION HISTORY

#### **Revision A (February 2022)**

- Converted Micrel document SY88403BL to Microchip data sheet DS20006650A.

- The MSOP package was removed as part of a recent update that happened prior to the document conversion.

- Minor text changes throughout.

NOTES:

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, contact your local Microchip representative or sales office.

| PART No.              | <u>x</u>          | <u>x</u>             | <u>x</u>                                    | - <u>XX</u> | Example | es:            |                                                                                                                    |

|-----------------------|-------------------|----------------------|---------------------------------------------|-------------|---------|----------------|--------------------------------------------------------------------------------------------------------------------|

|                       | Supply<br>Voltage | Package              | Temperature<br>Range                        | Media Type  | a) SY88 | 403BLMG:       | SY88403B, 3.3V Supply Volt-<br>age, 16-Lead 3x3 VQFN,<br>-40°C to +85°C Temp. Range,                               |

| Device:               | SY88403B          |                      | CML Limiting Post A<br>s-of-Signal Detectio |             | b) SY88 | 403BLMG-TR:    | 100/Tube<br>SY88403B, 3.3V Supply Volt-<br>age, 16-Lead 3x3 VQFN,                                                  |

| Supply Voltage:       | L =               | 3.3V                 |                                             |             |         |                | -40°C to +85°C Temp. Range,<br>1,000/Reel                                                                          |

| Package:              | M =               | 16-Lead 3 mm >       | x 3 mm VQFN                                 |             | Note 1: |                | identifier only appears in the<br>mber description. This identifier is                                             |

| Temperature<br>Range: | G =               | –40°C to +85°C       |                                             |             |         | the device pac | ng purposes and is not printed on<br>kage. Check with your Microchip<br>r package availability with the<br>option. |

| Media Type:           |                   | 00/Tube<br>,000/Reel |                                             |             |         |                | -                                                                                                                  |

NOTES:

#### Note the following details of the code protection feature on Microchip products:

- · Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip product is strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not

mean that we are guaranteeing the product is "unbreakable". Code protection is constantly evolving. Microchip is committed to

continuously improving the code protection features of our products.

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at https:// www.microchip.com/en-us/support/design-help/client-supportservices.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WAR-RANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDI-RECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSE-QUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### Trademarks

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPIC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, TrueTime, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, GridTime, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, Inter-Chip Connectivity, JitterBlocker, Knob-on-Display, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, NVM Express, NVMe, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, Symmcom, and Trusted Time are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2022, Microchip Technology Incorporated and its subsidiaries.

All Rights Reserved.

ISBN: 978-1-5224-9777-6

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

# **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support

Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510

New York, NY Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110 Tel: 408-436-4270

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

China - Beijing Tel: 86-10-8569-7000 China - Chengdu

Tel: 86-28-8665-5511 China - Chongqing Tel: 86-23-8980-9588

**China - Dongguan** Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

China - Nanjing Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

China - Shanghai Tel: 86-21-3326-8000

China - Shenyang Tel: 86-24-2334-2829

China - Shenzhen Tel: 86-755-8864-2200

China - Suzhou Tel: 86-186-6233-1526

**China - Wuhan** Tel: 86-27-5980-5300

China - Xian Tel: 86-29-8833-7252

China - Xiamen Tel: 86-592-2388138 China - Zhuhai

Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631 India - Pune

Tel: 91-20-4121-0141

**Japan - Osaka** Tel: 81-6-6152-7160

Japan - Tokyo Tel: 81-3-6880- 3770

Korea - Daegu Tel: 82-53-744-4301

Korea - Seoul Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

Singapore Tel: 65-6334-8870

Taiwan - Hsin Chu Tel: 886-3-577-8366

Taiwan - Kaohsiung Tel: 886-7-213-7830

Taiwan - Taipei Tel: 886-2-2508-8600

Thailand - Bangkok Tel: 66-2-694-1351

Vietnam - Ho Chi Minh Tel: 84-28-5448-2100 Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

EUROPE

**Denmark - Copenhagen** Tel: 45-4485-5910 Fax: 45-4485-2829

Finland - Espoo Tel: 358-9-4520-820

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Garching Tel: 49-8931-9700

Germany - Haan Tel: 49-2129-3766400

Germany - Heilbronn Tel: 49-7131-72400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Germany - Rosenheim** Tel: 49-8031-354-560

Israel - Ra'anana Tel: 972-9-744-7705

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

**Italy - Padova** Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7288-4388

Poland - Warsaw Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Gothenberg Tel: 46-31-704-60-40

**Sweden - Stockholm** Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820