Single-channel, Adjustable Voltage Monitor in Ultra-small Package

# **General Description**

The SY6370F device is a very small supervisory circuit that monitor voltage greater than 500mV with a 0.25% threshold accuracy and offer adjustable delay time using external capacitor. The SY6370F has a logic enable pin to power on and off the output.

The SY6370F operates from 1.7V to 6.5V and has a typical quiescent current of  $9\mu$ A with an open drain output rated at 18V. The SY6370F is available in an ultra-small DFN package.

## **Ordering Information**

| SY6370 |      | ☐<br>└─ Tempera<br>── Package<br>── Optional |   |      |

|--------|------|----------------------------------------------|---|------|

| 0.1.1  | NY 1 | <b>D</b> 1                                   | 1 | NT . |

| Ordering Number | Package type | Note |

|-----------------|--------------|------|

| SY6370FDTC      | DFN1.45×1-6  |      |

#### Features

- Adjustable Threshold Down to 500mV

- Threshold Accuracy: 1% Over temperature

- Capacitor-adjustable Delay Time

- Low Quiescent Current: 9µA (typ.)

- External Enable Input

- Open Drain Output (Rated at 18V)

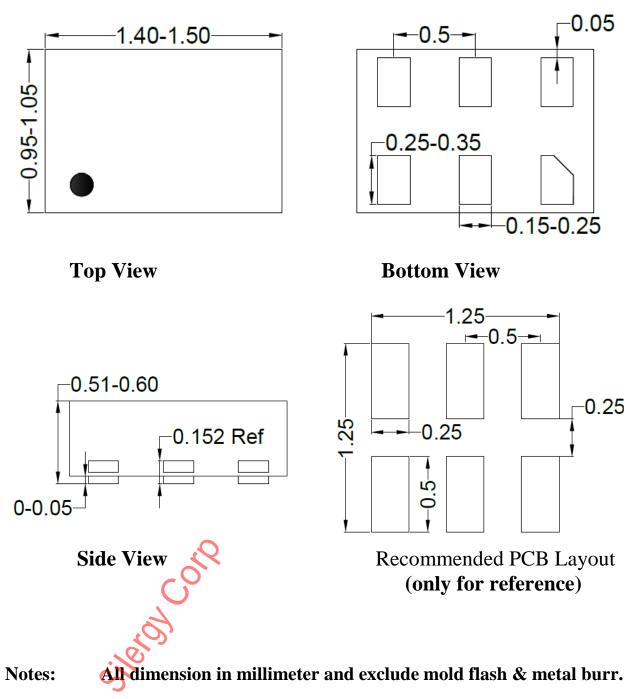

- Compact Package Minimizes Board Space: DFN1.45mm×1.0mm - 6

#### Applications

- DSPs, Microcontrollers, and Microprocessors

- Notebook and Desktop Computers

- PDAs and Handheld Products

- Portable and Battery-powered Products

- FPGAs and ASICs

**Top Mark:** Vxyz (device code: V, x=year code, y=week code, z= lot number code)

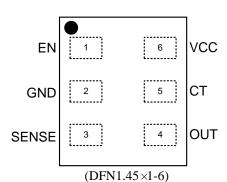

| Pin Name | Pin NO. | I/O | Pin Description                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|---------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| СТ       | 5       | Ι   | Capacitor-adjustable delay. The CT pin offers a user-adjustable delay time.<br>Connecting this pin to a ground referenced capacitor sets the delay time for SENSE rising above 0.5V to OUT asserting.<br>$t_{pd(r)}(s) = [C_{CT}(\mu F) \times 4] + 40\mu s$                                                                                                                                       |

| EN       | 1       | Ι   | Active high input. Driving EN low immediately makes OUT go low, independent of $V_{SENSE}$ . With $V_{SENSE}$ already above $V_{IT+}$ , drive EN high to make OUT go high after 0.2 $\mu$ s.                                                                                                                                                                                                       |

| GND      | 2       |     | Ground.                                                                                                                                                                                                                                                                                                                                                                                            |

| SENSE    | 3       | Ι   | This pin is connected to the voltage that is monitored with the use of an external resister. The output asserts after the capacitor-adjustable delay time when VSENSE rises above 0.5V and EN is asserted. The output de-asserts after a minimal propagation delay (16 $\mu$ s) when VSENSE falls below V <sub>IT+</sub> - V <sub>HYS</sub> .                                                      |

| OUT      | 4       | 0   | OUT is an open drain output that is immediately driven low after $V_{SENSE}$ falls<br>below ( $V_{IT+}$ - $V_{HYS}$ ) or the EN input is low. OUT goes high after the capacitor-<br>adjustable delay time when $V_{SENSE}$ is greater than $V_{IT+}$ and the EN pin is high. Open<br>drain device can be pulled up to 18V independent of VCC; Pull-up resisters are<br>required for these devices. |

| VCC      | 6       | Ι   | Supply Voltage Input. Connect a 1.7V to 6.5V supply to VCC to power the device. It is good analog design practice to place a $0.1 \mu$ F ceramic capacitor close to this pin.                                                                                                                                                                                                                      |

|          | S:      | 60  | -orR.                                                                                                                                                                                                                                                                                                                                                                                              |

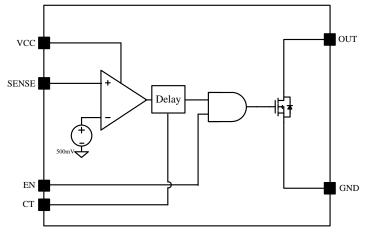

### **Block Diagram**

Figure2. Block Diagram

#### Absolute Maximum Ratings (Note 1)

|                                        | 8 7                |

|----------------------------------------|--------------------|

| VCC                                    |                    |

| СТ                                     | 0.3V to VCC + 0.3V |

| EN, SENSE                              | -0.3V to 7V        |

| OUT (Open Drain)                       |                    |

| OUT Current                            | ±10mA              |

| Power Dissipation, PD @ $T_A = 25 $ °C | 0.34W              |

| Package Thermal Resistance (Note 2)    |                    |

| $\theta_{JA}$                          | 293.8 °C/W         |

| θ <sub>JC</sub>                        | 165.1 °C/W         |

| Junction Temperature Range             | 40 °C to 125 °C    |

|                                        | 260 °C             |

| Storage Temperature Range              |                    |

### Recommended Operating Conditions (Note 3)

| VCC       | 1.7V to 6.5V    |

|-----------|-----------------|

| СТ        | 0V to 6.5V      |

| EN, SENSE | 0V to 6.5V      |

|           | 0V to 18V       |

|           | 0.0003mA to 1mA |

|           |                 |

|           |                 |

#### **Electrical Characteristics**

(1.7V <  $V_{CC}$  < 6.5V, typical values are at  $T_J$  = 25  $^\circ\!\!C$  and  $V_{CC}$  = 3.3V, unless otherwise noted.)

| Parameter                              | Symbol               | Test Conditions $\frac{1}{25}$                       | Min  | Тур   | Max   | Unit |

|----------------------------------------|----------------------|------------------------------------------------------|------|-------|-------|------|

| Input Voltage Range                    | V <sub>CC</sub>      |                                                      | 1.7  |       | 6.5   | V    |

| Power on Reset Voltage                 | V <sub>POR</sub>     | $V_{OL}$ (max) =0.2V, $I_{OUT}$ =15 $\mu$ A (Note 4) |      | 0.72  |       | V    |

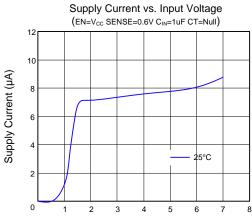

| Supply Current                         | т                    | $V_{CC}$ =3.3V, $T_A$ =25 °C, no load                |      | 9     | 12    | μA   |

| (into VCC pin)                         | I <sub>CC</sub>      | $V_{CC}=6.5V, T_A=25$ °C, no load                    |      | 11    | 13.5  | μΑ   |

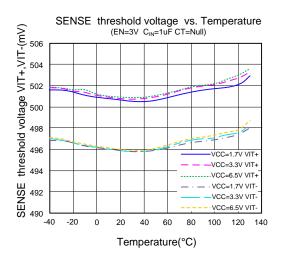

| Hysteresis Voltage                     | V <sub>HYS</sub>     | V <sub>SENSE</sub> falling                           |      | 5     |       | mV   |

| SENSE Input Current                    | I <sub>SENSE</sub>   | $V_{\text{SENSE}} = 0V$ to $V_{\text{CC}}$ (Note 5)  | -15  |       | 15    | nA   |

| CT Pin Charge Current                  | I <sub>CT</sub>      |                                                      | 260  | 310   | 360   | nA   |

| CT Pin Comparator<br>Threshold Voltage | V <sub>CT</sub>      |                                                      | 1.18 | 1.238 | 1.299 | v    |

| CT Pin Down Resistance                 | R <sub>CT</sub>      |                                                      |      | 200   |       | Ω    |

| Low-level Input Voltage                | V <sub>IL</sub>      |                                                      |      |       | 0.4   | V    |

| High-level Input Voltage               | V <sub>IH</sub>      |                                                      | 1.4  |       |       | V    |

| Under Voltage Lockout                  | V <sub>UVLO</sub>    | V <sub>CC</sub> falling, (Note 6)                    | 1.3  |       | 1.7   | V    |

| EN Leakage                             |                      | $EN/#EN = V_{CC}$ or $GND$                           | -100 |       | 100   | nA   |

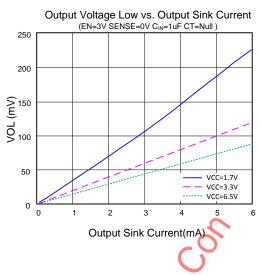

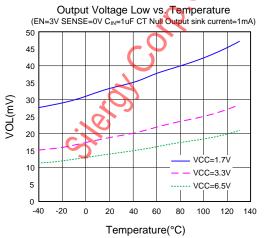

|                                        |                      | $V_{CC} \ge 1.2 V, \ I_{SINK} = 90 \mu A$            |      |       | 0.3   | V    |

| Low-level Output Voltage               | V <sub>OL</sub>      | $V_{CC} \ge 2.25 V,  I_{SINK} = 0.5 mA$              |      |       | 0.3   | V    |

|                                        |                      | $V_{CC} \ge 4.5V, I_{SINK} = 1mA$                    |      |       | 0.4   | V    |

| Open-drain Output Leakage<br>Current   | I <sub>LKG(OD)</sub> | $V_{OUT}$ high impedance = 18V                       |      | 20    |       | nA   |

### **Timing Requirements**

| Parameter                                   | Symbol              | Test Condition                                    | Min | Тур | Max | Unit |

|---------------------------------------------|---------------------|---------------------------------------------------|-----|-----|-----|------|

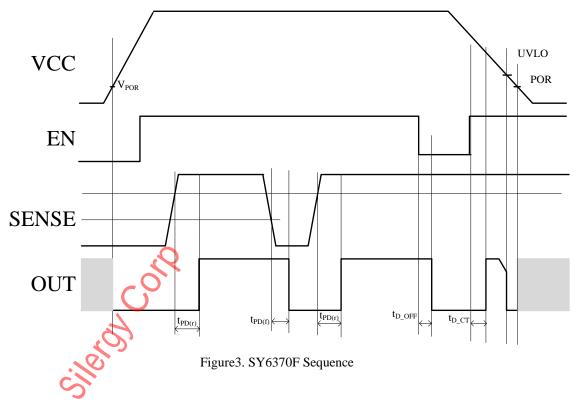

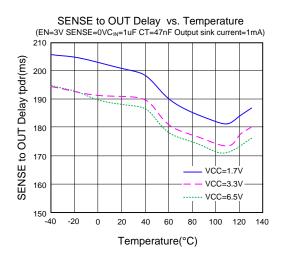

| SENSE (rising) to OUT                       | +                   | $V_{\text{SENSE}}$ rising, $C_{\text{CT}}$ = open |     | 40  |     | μs   |

| Propagation Delay                           | t <sub>PD(r)</sub>  | $V_{SESNE}$ rising, $C_{CT} = 0.047 \mu F$        |     | 190 |     | ms   |

| SENSE (falling) to OUT<br>Propagation Delay | t <sub>PD(f)</sub>  | Sense falling                                     |     | 16  |     | μs   |

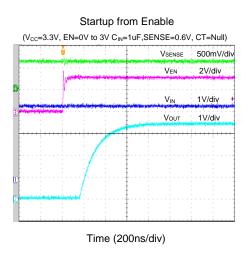

| Start-up Delay                              |                     | (Note 7)                                          |     | 50  |     | μs   |

| EN Pin Minimum Pulse<br>Duration            | tw                  |                                                   | 1   |     |     | μs   |

| EN Glitch Rejection                         | t <sub>EN_GLH</sub> |                                                   |     | 100 |     | ns   |

| EN to OUT Delay Time<br>(Output Disable)    | t <sub>d_off</sub>  | EN de-asserted to output de-asserted              |     | 200 |     | ns   |

| EN to VOUT Delay Time                       | t <sub>d_fix</sub>  | EN asserted to output asserted delay              |     | 200 |     | ns   |

|                                             |                     |                                                   |     |     |     |      |

**Note 1**: Stresses beyond the "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note 2:  $\Theta_{JA}$  is measured in the natural convection at  $T_A = 25$  °C on a low effective single layer thermal conductivity test board of JEDEC 51-3 thermal measurement standard.

Note 3: The device is not guaranteed to function outside its operating conditions

Note 4: The lowest supply voltage (VCC) at which output is active (OUT is low);  $t_{r-VCC} > 15\mu s/V$ . below  $V_{POR}$ , the output cannot be determined.

Note 5: Specified by design.

Note 6: When VCC falls below the UVLO threshold, the output de-asserts (OUT goes low). Below  $V_{POR}$ , the output cannot be determined

Note 7: During power on,  $V_{CC}$  must exceed 1.7 V for at least 50µs (plus propagation delay time,  $t_{PD(r)}$ ) before output is in the correct state.

### Sequence:

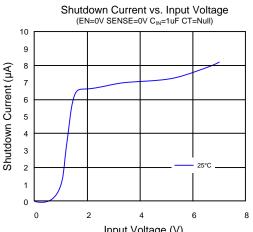

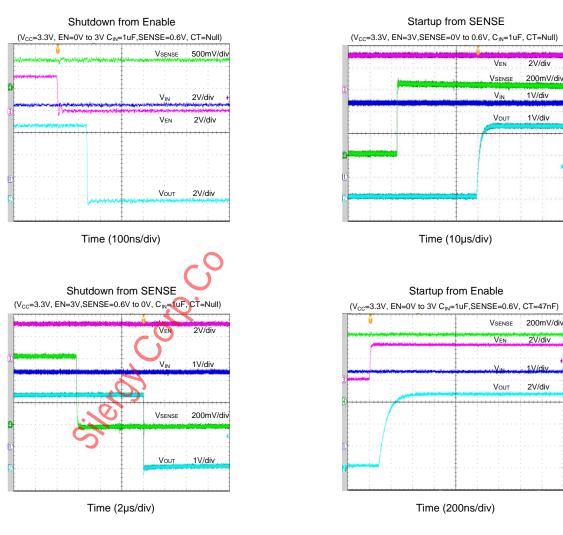

### **Typical Operating Characteristics**

Input Voltage (V)

SENSE to OUT Delay vs. C<sub>CT</sub> (V<sub>CC</sub>=3.3V EN=3V SENSE=0.6V C<sub>IN</sub>=1uF) 9000 8000 7000 OUT Delay(ms) 6000 5000 4000 300 2000 1000 0  $200 \quad 400 \quad 600 \quad 800 \quad 1000 \ 1200 \ 1400 \ 1600 \ 1800 \ 2000$

$C_{CT}$  (nF)

AN\_SY6370F Rev. 0.9 © 2020 Silergy Corp.

Silergy Corp. Confidential-prepared for Customer Use Only 6 All Rights Reserved.

2V/div

2V/div

1\//d

AN\_SY6370F Rev. 0.9 © 2020 Silergy Corp.

Silergy Corp. Confidential-prepared for Customer Use Only 7 All Rights Reserved.

# SY6370F

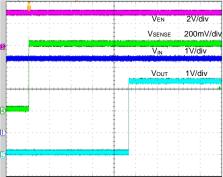

#### Shutdown from Enable

Time (400ns/div)

Startup from SENSE

(V<sub>CC</sub>=3.3V, EN=3V,SENSE=0V to 0.6V, C<sub>IN</sub>=1uF, CT=47nF)

Time (40ms/div)

| -   |      | Ű |                 |           |

|-----|------|---|-----------------|-----------|

| E   | <br> |   | Ven             | 2V/div    |

|     |      |   | ‡ : :           |           |

|     |      |   | V <sub>IN</sub> | 1V/div    |

|     |      |   |                 |           |

|     |      |   |                 | +         |

| -   |      |   | VSENSE          | 200mV/div |

| -   |      |   | 1 : :           |           |

| t i |      |   | +               |           |

|     |      |   | •               |           |

Time (4µs/div)

### **General Description**

The SY6370F is a very small supervisory circuit that monitors voltage greater than 500mVwith a 0.25% threshold accuracy and offer adjustable delay time using external capacitor. The SY6370F has a logic enable pin to power on and off the output.

The SY6370F operates from 1.7V to 6.5V and has a typical quiescent current of  $9\mu A$  with an open drain output rated at 18V.

The SY6370F is available in an ultra-small DFN package.

#### Overview

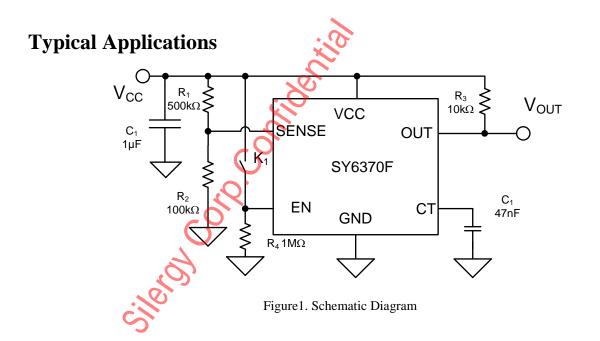

The SY6370FDTC is an ultra-small supervisory circuit. The SY6370F is designed to assert the SENSE\_OUT or SENSE\_OUT signal, as shown in Table 1. When the SENSE pin rises above 0.5 V and the enable input is asserted (ENABLE = high or ENABLE = low), the output asserts (OUT goes high or OUT goes low) after the capacitor-adjustable delay time. The SENSE pin can be set to any voltage threshold above 0.5V using an external resistor divider. A broad range of output delay times and voltage thresholds can be supported, allowing these devices to be used in wide array of applications.

Table1. SY6370F Truth Table

| Conditions    |                                               | Output     | Status                      |

|---------------|-----------------------------------------------|------------|-----------------------------|

| ENABLE = high | gh SENSE < VIT+ OUT = low Output not asserted |            | Output not asserted         |

| ENABLE = low  | SENSE < VIT+                                  | OUT = low  | Output not asserted         |

| ENABLE = low  | SENSE > VIT+                                  | OUT = low  | Output not asserted         |

| ENABLE = high | SENSE > VIT+                                  | OUT = high | Output asserted after delay |

#### **Applications Information**

#### Input Pin (SENSE)

The SENSE input pin allows any system voltage above 0.5 V to be monitored. If the voltage at the SENSE pin exceeds VIT+, and provided that the enable pin is asserted (ENABLE=high), then the output is asserted after the capacitor-adjustable delay time elapses. When the voltage at the SENSE pin drops below (VIT+ Phys), the output is de-asserted. The comparator has a built-in hysteresis to ensure smooth output assertions and de-assertions. Although not required in most cases, for extremely noisy applications, it is good analog design practice to place a 1nF to 10nF bypass capacitor at the SENSE input in order to reduce sensitivity to transients and layout parasitic. The target threshold voltage can be calculated by using Equation 1:

$VTARGET = (1 + R_1 / R_2) \times 0.5(V)$ (1)

#### **Output Delay Time Pin (CT)**

To program a user-defined, adjustable delay time, an external capacitor must be connected between the CT pin and GND. If the CT pin is left open, there will be a delay of  $40\mu s$ . The adjustable delay time can be calculated through Equation 2:

$tpd(r)(s) = [CCT(\mu F) \times 4] + 40 \ \mu s$  (2)

The reset delay time is determined by the time it takes an on-chip, precision 310nA current source to charge the external capacitor to 1.24 V. When SENSE > VIT+ and with ENABLE high, the internal current sources are enabled and begin to charge the external capacitors. When the CT voltage on a capacitor reaches 1.24 V, the corresponding OUT is asserted. Note that a low-leakage type capacitor (such as ceramic) should be used and that stray capacitance around this pin may cause errors in the reset delay time.

#### Output Pin (OUT)

In a typical SY6370F application, the OUT outputs is connected to a reset/enable input of the processor (DSP, CPU, FPGA, ASIC, and so on) or connected to enable input of a voltage regulator. the The SY6370F provide open-drain outputs. Pull up resistors must be used to hold these lines high when OUT is asserted. By connecting the pull up resistors to the proper voltage rails, OUT can be connected to other devices at the correct interface voltage levels. The outputs can be pulled up to 18 V independent of the supply voltage (VCC). To ensure proper voltage levels, some thought should be given to choosing the correct pull up resistor values. The ability to sink current is determined by the supply voltage; therefore, if VCC = 5V and the desired output pull up is 18 V, then to obtain a sink current of 1mA or less (as mentioned in the Electrical Characteristics), the pull up resistor value should be greater than  $18k\Omega$ . By using wired-OR logic, any combination of OUT can be merged into one logic signal.

#### **Enable Function**

The enable input allows an external logic signal from other processors, logic circuits, and/or discrete sensors to turn on or turn off the output. The SY6370FDTC offer an active-high enable input (ENABLE).Driving ENABLE high forces OUT to go high. The 0.4V (maximum) low and 1.4V (minimum) high allow ENABLE to be driven with a 1.5V or

Silergy Corp. Confidential-prepared for Customer Use Only 9 All Rights Reserved.

greater system supply. Active high input. Driving EN low immediately makes OUT go low. With VSENSE already above VIT+, drive EN high to make OUT go high after  $0.2\mu$ s.

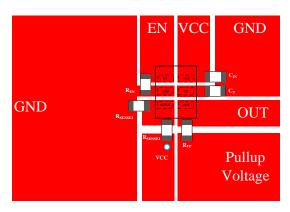

#### PCB Layout Guide

For best performance of the SY6370F, the following guidelines must be strictly followed:

1. Place the VCC decoupling capacitor close to the device.

2. Input and output capacitors should be placed closed to the IC and connected to ground plane to reduce noise coupling.

3. SENSE pin is a sensitive pin. Keep SENSE trace far away from the trace or plane that has large dv/dt. The divider resistor should be placed as close as possible to the SENSE pin.

Figure 4. PCB Layout Suggestion

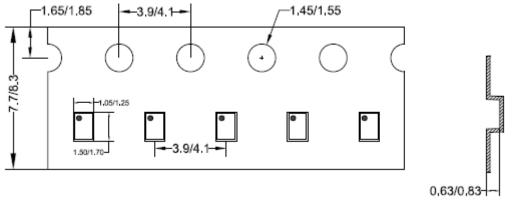

### **Taping & Reel Specification**

#### 1. Taping orientation

2. Carrier Tape & Reel specification for packages

| Package   | Tape width | Pocket    | Reel size | Trailer    | Leader length | Qty per |

|-----------|------------|-----------|-----------|------------|---------------|---------|

| types     | (mm)       | pitch(mm) | (Inch)    | length(mm) | (mm)          | reel    |

| DFN1.45×1 | 8          | 4         | 7''       | 400        | 160           | 3000    |

#### **IMPORTANT NOTICE**

1. **Right to make changes.** Silergy and its subsidiaries (hereafter Silergy) reserve the right to change any information published in this document, including but not limited to circuitry, specification and/or product design, manufacturing or descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products are sold subject to Silergy's standard terms and conditions of sale.

2. Applications. Application examples that are described herein for any of these products are for illustrative purposes only. Silergy makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Buyers are responsible for the design and operation of their applications and products using Silergy products. Silergy or its subsidiaries assume no liability for any application assistance or designs of customer products. It is customer's sole responsibility to determine whether the Silergy product is suitable and fit for the customer's applications and products planned. To minimize the risks associated with customer's products and applications, customer should provide adequate design and operating safeguards. Customer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Silergy assumes no liability related to any default, damage, costs or problem in the customer's applications or products, or the application or use by customer's third-party buyers. Customer will fully indemnify Silergy, its subsidiaries, and their representatives against any damages arising out of the use of any Silergy components in safety-critical applications. It is also buyers' sole responsibility to warrant and guarantee that any intellectual property rights of a third party are not infringed upon when integrating Silergy products into any application. Silergy assumes no responsibility for any said applications or for any use of any circuitry other than circuitry entirely embodied in a Silergy product.

3. Limited warranty and liability. Information furnished by Silergy in this document is believed to be accurate and reliable. However, Silergy makes no representation or warranty, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. In no event shall Silergy be liable for any indirect, incidental, punitive, special or consequential damages, including but not limited to lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges, whether or not such damages are based on tort or negligence, warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, Silergy' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Standard Terms and Conditions of Sale of Silergy.

4. **Suitability for use.** Customer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of Silergy components in its applications, notwithstanding any applications-related information or support that may be provided by Silergy. Silergy products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an Silergy product can reasonably be expected to result in personal injury, death or severe property or environmental damage. Silergy assumes no liability for inclusion and/or use of Silergy products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

5. **Terms and conditions of commercial sale**. Silergy products are sold subject to the standard terms and conditions of commercial sale, as published at http://www.silergy.com/stdterms, unless otherwise agreed in a valid written individual agreement specifically agreed to in writing by an authorized officer of Silergy. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. Silergy hereby expressly objects to and denies the application of any customer's general terms and conditions with regard to the purchase of Silergy products by the customer.

6. No offer to sell or license Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights. Silergy makes no representation or warranty that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right. Information published by Silergy regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of Silergy.

For more information, please visit: www.silergy.com

© 2020 Silergy Corp.

All Rights Reserved.