# STPS60A150CHR

Datasheet

# Rad-Hard 2 x 30 A - 150 V Schottky rectifier

SMD.5

The upper metallic lid is not internally connected to any pin, nor to the IC die inside the package

| Product status link                         |        |  |  |  |

|---------------------------------------------|--------|--|--|--|

| STPS60A150CHR                               |        |  |  |  |

| Product summary                             |        |  |  |  |

| I <sub>F(AV)</sub> 2 x 30 A                 |        |  |  |  |

| V <sub>RRM</sub>                            | 150 V  |  |  |  |

| T <sub>j</sub> (max)                        | 175 °C |  |  |  |

| V <sub>F(max)</sub> at 2 x 30<br>A / 125 °C | 0.83 V |  |  |  |

## **Features**

- Forward current: 2 x 30 A

- Repetitive peak reverse voltage: 150 V

- Low forward voltage drop

- dV/dt up to 10 kV/µs

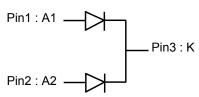

- Monolithic dual die common cathode

- Hermetic package

- TID and SEE characterized

- Package mass: 0.92 g

- ESCC qualified : 5106/023

## Description

The STPS60A150CHR is package and screened to comply with the ESCC5000 specification for aerospace products. It is a dual monolithic Schottky rectifier assembled in an SMD.5 hermetic package and characterized in total dose at high dose rate and in single event effect to be used in aerospace applications. It is ESCC qualified.

The complete ESCC specification for this device is available from the European Space Agency web site. ST guarantees full compliance of qualified parts with the ESCC detailed specification.

## 1 Characteristics

57/

## **1.1** Absolute maximum ratings

The absolute maximum ratings are limiting values at 25°C, per diode unless otherwise notified. Values provided in Table 1 shall not be exceeded at any time during use or storage

| Symbol                          | Parameter                                                    | Value       | Unit  |

|---------------------------------|--------------------------------------------------------------|-------------|-------|

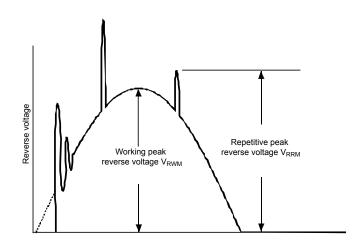

| V <sub>RWM</sub> <sup>(1)</sup> | Working peak reverse voltage                                 | 150         | V     |

| V <sub>RRM</sub> <sup>(1)</sup> | Repetitive peak reverse voltage                              | 150         | V     |

| I <sub>O</sub> <sup>(2)</sup>   | Average output rectified current<br>per diode<br>per package | 30<br>60    | A     |

| I <sub>FSM</sub>                | Forward surge current                                        | 190         | А     |

| dV/dt <sup>(3)</sup>            | Reverse voltage maximum rise rate (4)                        | 10          | kV/µs |

| T <sub>op</sub>                 | Operating temperature range (case temperature)               | -65 to +175 | °C    |

| T <sub>j</sub> <sup>(5)</sup>   | Maximum junction temperature                                 | +175        | °C    |

| T <sub>stg</sub>                | Storage temperature range                                    | -65 to +175 | °C    |

| T <sub>sol</sub> <sup>(6)</sup> | Soldering temperature                                        | +245        | °C    |

| Table ' | 1. Absolute | maximum | ratings |

|---------|-------------|---------|---------|

|---------|-------------|---------|---------|

- 1. See Figure 1. V<sub>RRM</sub> and V<sub>WRM</sub> definition Schematics.

- Per diode: for T<sub>case</sub> > +74 °C, derate linearly to 0 A at +175 °C. Per device: for case > +44 °C, derate linearly to 0 A at +175 °C.

- 3. Evaluated by characterization. Tested in production at 25 °C on 5 parts per wafer lot.

- 4.  $V_{RRM}$  from stationary no-conduction state to  $V_{RRM} < V_{RRM}$  max

- 5.  $(dP_{tot'}/dT_j) < (1/R_{th(j-a)})$  condition to avoid thermal runaway for a diode on its own heatsink.

- 6. Duration 5 seconds maximum with at least 3 minutes between consecutive temperature peaks.

#### Figure 1. V<sub>RRM</sub> and V<sub>WRM</sub> definition - Schematics

## **1.2** Thermal parameters

#### Table 2. Thermal parameters

| Symbol                                                                   | Parameter   |           | Typ. value | Max. value | Unit |

|--------------------------------------------------------------------------|-------------|-----------|------------|------------|------|

| <b>R</b>                                                                 |             | Per diode | -          | 3.4        | °C/W |

| R <sub>th(j-c)</sub> Thermal resistance, junction to case <sup>(1)</sup> | Per package | -         | 2.2        | C/W        |      |

1. When only 1 diode is used, the dissipation is made from a part of the die, hence to a higher thermal resistance.

## 1.3 Electrical characteristics

Limiting value per diodes, unless otherwise specified.

| Symbol                            | Parameter               | MIL-STD-750 test<br>method | Test condition                    | Test conditions         |   | Тур. | Max.  | Unit |

|-----------------------------------|-------------------------|----------------------------|-----------------------------------|-------------------------|---|------|-------|------|

| I <sub>R</sub> <sup>(1)</sup>     | Poverao lookago gurrent | 4016                       | DC method, V <sub>R</sub> = 150 V | T <sub>j</sub> = 25 °C  | - |      | 14    | μA   |

| 'R'                               | Reverse leakage current | 4010                       | De memou, $v_{\rm R}$ = 150 v     | T <sub>j</sub> = 125 °C | - | 2.0  | 8     | mA   |

|                                   |                         |                            |                                   | T <sub>j</sub> = -55 °C | - | 0.77 | 0.84  |      |

|                                   |                         | orward voltage drop 4011   | I <sub>F</sub> = 5 A              | T <sub>j</sub> = 25 °C  | - | 0.70 | 0.78  | -    |

|                                   |                         |                            |                                   | T <sub>j</sub> = 125 °C | - | 0.56 | 0.62  |      |

|                                   |                         |                            | I <sub>F</sub> = 10 A             | T <sub>j</sub> = -55 °C | - | 0.92 | 1.03  |      |

|                                   |                         |                            |                                   | T <sub>j</sub> = 25 °C  | - | 0.77 | 0.85  |      |

| <b>V</b> (2)(3)                   |                         |                            |                                   | T <sub>j</sub> = 125 °C | - | 0.62 | 0.69  |      |

| V <sub>F1</sub> <sup>(2)(3)</sup> | Forward voltage drop    |                            | I <sub>F</sub> = 20 A             | T <sub>j</sub> = -55 °C | - | 1.27 | 1.435 | V    |

|                                   |                         |                            |                                   | T <sub>j</sub> = 25 °C  | - | 0.85 | 0.93  |      |

|                                   |                         |                            |                                   | T <sub>j</sub> = 125 °C | - | 0.70 | 0.78  |      |

|                                   |                         |                            | I <sub>F</sub> = 30 A             | T <sub>j</sub> = -55 °C | - | 1.65 | 1.87  |      |

|                                   |                         |                            |                                   | T <sub>j</sub> = 25 °C  | - | 0.90 | 0.99  |      |

|                                   |                         |                            |                                   | T <sub>j</sub> = 125 °C | - | 0.76 | 0.83  |      |

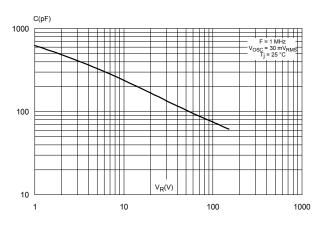

| C <sup>(3)</sup>                  | Junction capacitance    | 4001                       | V <sub>R</sub> = 10 V, F = 1 MHz  | T <sub>j</sub> = 25 °C  | - | 237  | 310   | pF   |

#### Table 3. Static electrical characteristics

1. 100% tested at 25 °C. Compliance with the 125 °C specification is supported by simulation, characterization and, as per STMicroelectronics wafer lot acceptance procedure, by sampling on 5 parts per wafer lot, with an acceptance criteria of 0. In case of fail, a 100% test is performed.

2. Pulse width 680  $\mu$ s, duty cycle  $\leq 2\%$

Compliance with the specification is supported by simulation, characterization and, as per STMicroelectronics wafer lot acceptance procedure, by sampling on 5 parts per wafer lot, with an acceptance criteria of 0. In case of fail, a 100% test is performed.

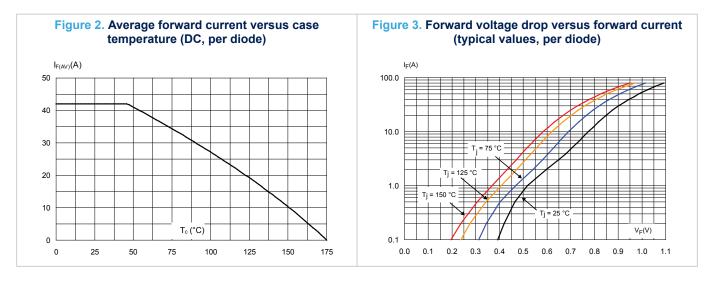

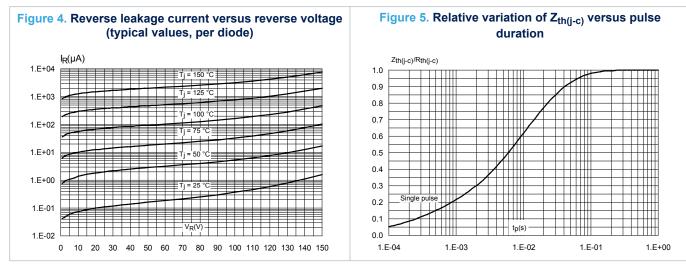

## 1.4 Characteristics (curves)

## 2 Radiation

The technology of the STMicroelectronics Rad-Hard rectifier's diodes is intrinsically highly resistant to radiative environments.

The product radiation hardness assurance is supported by a total ionisation dose (TID) test at high dose rate and a single effect event (SEE) characterization.

## 2.1 Total dose radiation (TID) testing

The part has been characterized in total ionizing dose at high dose rate on 12 parts packaged in SMD.5, 4 parts unbiased, 4 parts reverse biased and 4 parts forward biased. All parts were from the same wafer lot.

The irradiation has been done according to the ESCC 22900 specification, standard window.

Both pre-irradiation and post-irradiation performances have been tested using the same circuitry and test conditions for a direct comparison can be done ( $T_{amb}$  = 22 ±3 °C unless otherwise specified).

The following parameters were measured :

- Before irradiation

- After irradiation at final dose 3 Mrad (Si)

- After 168 hrs at room temperature

- after 168 hrs at 100 °C anneal

Based on this characterization, the device is deemed able to sustain 3 Mrad(Si) while maintaining all its parameters within its specifications.

### 2.2 Single event effect

The Single Event Effect (SEE) relevant to power rectifiers are characterized, i.e. the Single Event Burnout (SEB). The tests are performed as per ESCC 25100, each one on 3 pieces from 1 wafer at room temperature. The accept/reject criteria are :

SEB (Destructive mode):

The diode is reverse biased during irradiation. The test is stopped as soon as a SEB occurs or when the reverse leakage current is above the specification or when the overall fluency on the component reaches 1E7 cm<sup>2</sup>.

Post irradiation stress test (PIST):

After the irradiation, a stress is applied to the diode in order to reveal any latent damage on the irradiated devices.

The reverse voltage value is increased from 0 V to 100% of V<sub>R</sub>max. and then decreased from 100% of the V<sub>R</sub>max. to 0 V. At each step, the reverse leakage current value is measured.

| Туре                  | Conditions                                                                                                                                     | Result                                                                                                           |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| Total ionisation dose | High dose rate 4 reverse biased + 4 forward biased + 4 unbiased                                                                                | Immune up to 3 Mrad(Si)                                                                                          |

| Single effect burnout | LET : 62.5 MeV.cm <sup>2</sup> /mg: $V_r \le 100\% V_{Rmax}$                                                                                   | No burnout                                                                                                       |

| PIST                  | $\label{eq:LET: 62.5 MeV.cm^2/mg:} $$ V_r \le 85\% \ V_{Rmax}$$ V_r \le 55\% \ V_{Rmax}$$ LET: 32.4 MeV.cm^2/mg: \ V_r \le 100\% \ V_{Rmax}$$$ | Part functional <sup>(1)</sup><br>Part fully compliant to specification<br>Part fully compliant to specification |

#### Table 4. Radiation hardness assurance summary

1. Ir gets above its max specification during the test without recovery.

# **3** Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

## 3.1 SMD.5 package information

# $b^{3} + b^{2} + b^{2$

#### Figure 7. Surface mount SMD.5 package outline (3-terminal)

#### Table 5. SMD.5 package mechanical data

| Symbole           | Dimensions (mm) |          | Dir   | es)   |       |       |

|-------------------|-----------------|----------|-------|-------|-------|-------|

| Symbols           | Min.            | Тур.     | Max.  | Min.  | Тур.  | Max.  |

| A                 | 2.84            |          | 3.15  | 0.112 |       | 0.124 |

| A1                | 0.25            |          | 0.51  | 0.010 |       | 0.200 |

| b                 | 7.13            |          | 7.39  | 0.281 |       | 0.291 |

| b1                | 5.58            |          | 5.84  | 0.220 |       | 0.230 |

| b2 <sup>(1)</sup> | 2.28            |          | 2.54  | 0.090 |       | 0.100 |

| b3                | 2.92            |          | 3.18  | 0.115 |       | 0.125 |

| D                 | 10.03           |          | 10.28 | 0.395 |       | 0.405 |

| D1                | 0.76            |          |       | 0.030 |       |       |

| E                 | 7.39            |          | 7.64  | 0.291 |       | 0.301 |

| e                 |                 | 1.91 BSC |       |       | 0.075 |       |

1. 2 locations

DS12256 - Rev 6

# 4 Ordering information

57

| Order codes   | ESCC detail specification | Quality level        | Package | Lead<br>finishing | Marking <sup>(1)</sup> | Weight | Packing    |

|---------------|---------------------------|----------------------|---------|-------------------|------------------------|--------|------------|

| STPS60A150CS1 | -                         | engineering<br>model | Gold    |                   |                        |        |            |

| STPS60A150CSG | 5106/023/02               | Flight model         | SMD.5   |                   | 510602302              | 0.92 g | Strip pack |

| STPS60A150CST | 5106/023/06               | Flight Model         |         | Solder dip        | 510602306              |        |            |

#### Table 6. Ordering information

1. Specific marking only. The full marking includes in addition:

• For the Engineering Models: ST logo, date code, country of origin (FR)

• For flight parts: ST logo, date code, country of origin (FR), ESA logo, serial number of the part within the assembly lot

## 5 Other information

51

## 5.1 Traceability information

The date code in formation is structured as described in the table below.

#### Table 7. Date codes

| Model | Date code <sup>(1)</sup> |

|-------|--------------------------|

| EM    | ЗуууwW                   |

| ESCC  | yywwN                    |

1. *yy* = *year*, *ww* = *week number*, *N* = *lot index in the week*.

## 5.2 Documentation

Each product shipment includes a set of associated documentation within the shipment box. This documentation depends on the quality level of the products, as detailed in the table below. The documentation is provided on printed paper in a dedicated envelop.

| Quality level     | Documentation                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Engineering Model | Certificate of Conformance including :<br>Customer name<br>Customer purchase order number<br>ST sales order number and item<br>ST part number<br>Quantity delivered<br>Date code<br>Reference data sheet<br>Reference to TN1181 on engineering models<br>ST Rennes assembly lot ID                                                                                            |

| ESCC Flight       | Certificate of Conformance including:   Customer name   Customer purchase order number   ST sales order number and item   ST part number   Quantity delivered   Date code   Serial numbers   Diffusion line (plant + wafer size)   Diffusion run (wafer lot number) and wafer ID   Reference of the applicable ESCC Qualification maintenance lot   ST Rennes assembly lot ID |

#### Table 8. Default documentation provided with the parts

# **Revision history**

| Date        | Revision | Changes                                                                        |

|-------------|----------|--------------------------------------------------------------------------------|

| 06-Dec-2018 | 1        | First issue.                                                                   |

| 18-Sep-2019 | 2        | Added Section 1.4 .Updated Section 1.3 Electrical characteristics and Table 7. |

| 24-Sep-2019 | 3        | Updated Table 1, Figure 4 and Figure 5.                                        |

| 24-Sep-2020 | 4        | Updated title description and Table 8.                                         |

| 03-Nov-2020 | 5        | Updated Features, Table 1 and Table 4.                                         |

| 26-Jan-2022 | 6        | Updated Table 1 and Table 8. Added Figure 1.                                   |

#### Table 9. Document revision history

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2022 STMicroelectronics - All rights reserved