## **PS/2 3D Mouse Controller**

AUG 05, 2004 Version 1.4

SUNPLUS TECHNOLOGY CO. reserves the right to change this documentation without prior notice. Information provided by SUNPLUS TECHNOLOGY CO. is believed to be accurate and reliable. However, SUNPLUS TECHNOLOGY CO. makes no warranty for any errors which may appear in this document. Contact SUNPLUS TECHNOLOGY CO. to obtain the latest version of device specifications before placing your order. No responsibility is assumed by SUNPLUS TECHNOLOGY CO. for any infringement of patent or other rights of third parties which may result from its use. In addition, SUNPLUS products are not authorized for use as critical components in life support devices/ systems or aviation devices/systems, where a malfunction or failure of the product may reasonably be expected to result in significant injury to the user, without the express written approval of Sunplus.

### **Table of Contents**

### **PAGE**

| 1. | GENERAL DESCRIPTION                                                                   | 3  |

|----|---------------------------------------------------------------------------------------|----|

| 2. | FEATURES                                                                              | 3  |

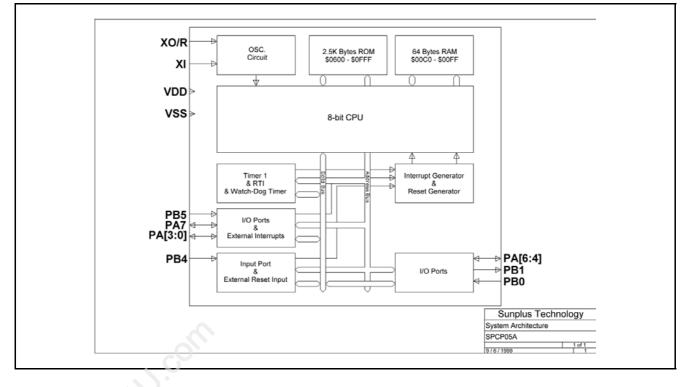

| 3. | BLOCK DIAGRAM                                                                         | 3  |

|    | 3.1. FUNCTIONAL BLOCK DIAGRAM                                                         | 4  |

|    | 3.1.1. CPU                                                                            | 4  |

|    | 3.1.2. Register summary                                                               | 5  |

| 4. | SIGNAL DESCRIPTIONS                                                                   |    |

|    | 4.1. PIN Assignment & Package Outline                                                 |    |

|    | 4.2. PORT A REGISTERS & PINS                                                          | 7  |

|    | 4.3. PORT B REGISTERS & PINS                                                          | 9  |

|    | 4.4. INTERRUPT                                                                        | 11 |

|    | 4.5. WDT, TIMER1 & REAL TIME INTERRUPT                                                | 13 |

|    | 4.5.1. RT1: RT0 - Real time interrupt rate select                                     | 14 |

|    | 4.6. RESET                                                                            | 15 |

|    | 4.7. OPTION TABLE                                                                     | 16 |

| 5. | ELECTRICAL SPECIFICATIONS                                                             | 17 |

|    | 5.1. ITEM DEFINITION                                                                  | 17 |

|    | 5.2. ABSOLUTE MAXIMUM RATING                                                          | 17 |

|    | 5.3. RECOMMENDED OPERATING CONDITIONS                                                 | 17 |

|    | 5.4. PIN ATTRIBUTE DESCRIPTION (VDD = 5.0V) TEMPERATURE = 25°C)                       |    |

|    | 5.5. TIMING DIAGRAM (VDD = 4.5V TO 5.5V, TEMPERATURE = 0°C TO 40°C OR 70°C)           | 18 |

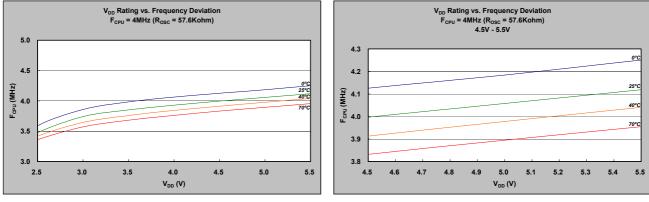

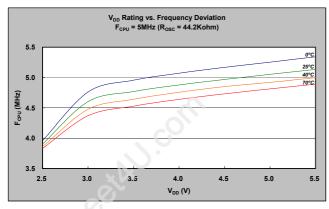

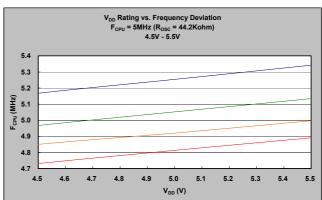

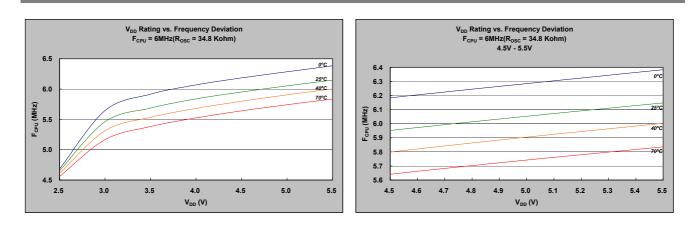

|    | 5.6. R-OSC MODE FREQUENCY CURVE (NORMALIZED DATA)                                     |    |

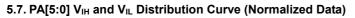

|    | 5.7. PA[5:0] V <sub>IH</sub> AND V <sub>IL</sub> DISTRIBUTION CURVE (NORMALIZED DATA) |    |

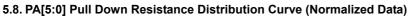

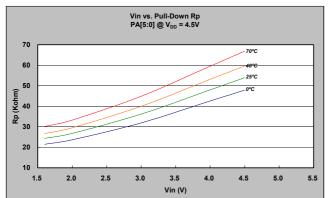

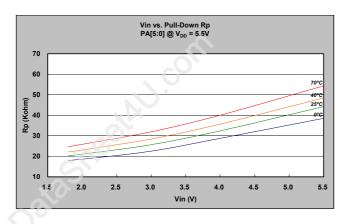

|    | 5.8. PA[5:0] PULL DOWN RESISTANCE DISTRIBUTION CURVE (NORMALIZED DATA)                | 19 |

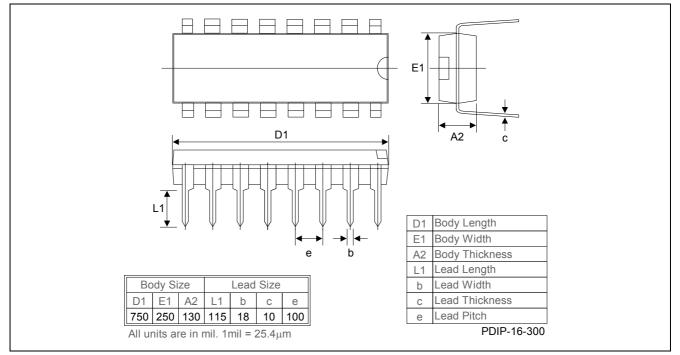

| 6. | PACKAGE/PAD LOCATIONS                                                                 | 20 |

|    | 6.1. PACKAGE INFORMATION                                                              | 20 |

|    | 6.1.1. PDIP 16                                                                        |    |

|    | 6.2. ORDERING INFORMATION                                                             | 20 |

| 7. | DISCLAIMER                                                                            | 21 |

| 8. | REVISION HISTORY                                                                      | 22 |

### **PS/2 3D MOUSE CONTROLLER**

#### **1. GENERAL DESCRIPTION**

SPCP05A is a solution on functional improvement from SPMC01. It enhances the slew rate control and reduces the output current from 8mA to 4mA on PA port for EMI improvement. In addition, the I/O attribute of PB port is specified for the application. The memory size is similar to SPMC01: 2.5K bytes of ROM and 64 bytes of RAM.

#### 2. FEATURES

- Built-in 8-bit Sunplus CPU core and up to 6.0MHz clock operation.

- Eight general-purpose I/O channels that are grouped as PA port, three pure input channels and one pure output channel are grouped as PB port.

- Three interrupt groups in external.

- External Reset input option on PB4.

- An 8-bit Timer with Real Time Interrupt control.

- A watchdog timer for program control.

- 2.5K bytes of ROM with 64 bytes of RAM.

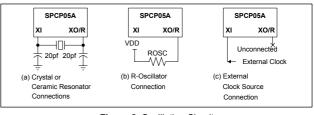

- R-Oscillation or Crystal input options for system clock.

- Slow Power On Reset respond to the power on slew rate at least 5V/50ms.

- Slew Rate controlled outputs and Balanced Power distribution for EMI improvement.

- Operation voltage 2.5V 5.5V.

#### 3. BLOCK DIAGRAM

#### 3.1. Functional Block Diagram

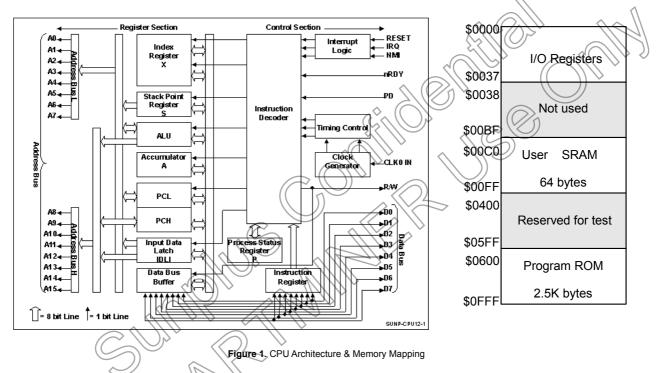

#### 3.1.1. CPU

The 8-bit high performance Micro-Controller of SPCP05A is a SUNPLUS processor equipped with the following essential registers: Accumulator, Program Counter, X Register, Stack Pointer and Processor Status Register (The same as 6502 instruction's structure). SPCP05A is a fully static CMOS design. The oscillation frequency could be varied from 100KHz up to 6.0MHz and depends on the application needs. The SPCP05A

Development System includes a SUNPLUS ICE, Evaluation Chip and Engineering Development Board.

The content of processor Status Register is:

| Bit  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------|---|---|---|---|---|---|---|---|

| Flag | Ν | V | - | В | - | Ι | Z | С |

N: Negative, V: Overflow, B: Brk command, I: IRQ disable, Z: Zero, C: Carry

Sixty-four bytes of RAM (including the stack) are available from \$00C0 to \$00FF. The stack begins at address \$00FF and proceeds down to \$00C0. Total of 3072 bytes of ROM on chip includes 2560 bytes of user ROM located from \$0600 through \$0FFF and 512 bytes of internal test ROM located from \$0400 through \$05FF. Users' program can only be allocated from \$0600 through \$0FFF (2.5K).

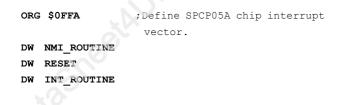

The address of NMI (not provided in this chip), RESET and IRQ are located from \$0FFA to \$0FFF. The interrupt vectors should be specified in the program as follows:

When using Evaluation board with EPROM (for 27C256), the address of \$7FFA must be defined as follows:

| ORG \$7FFA     | ;interrupt vector for EPROM |

|----------------|-----------------------------|

|                | with                        |

| DW NMI_ROUTINE | ;Evaluation Board.          |

| DW RESET       |                             |

| DW INT_ROUTINE |                             |

When using Evaluation board with Sunplus ICE, users fill the **ORG** address of \$0FFFA as follows:

| ORG | \$0FFFA     | ; interrupt vector for SUNPLUS |

|-----|-------------|--------------------------------|

|     |             | ICE.                           |

| DW  | NMI_ROUTINE |                                |

| DW  | RESET       |                                |

| DW  | INT_ROUTINE |                                |

The SPCP05A supports AT-cut parallel resonant oscillated Crystal /Resonator or RC oscillator or external clock sources by mask option (select one out of three types). The design of application circuit should follow the vendors' specifications or recommendations. The diagram listed below is typical X'TAL/ROSC circuits for most applications:

Figure 2. Oscillation Circuit

#### 3.1.2. Register summary

All of the function registers will be set to 0 (except *rt1* and *rt0* in **TCS1**) when a reset signal occurred. The bits *rt1* and *rt0* will be set to '1' when a reset signal occurred.

| Abbr.  | Register              | bit 7     | bit 6         | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 | Enable |

|--------|-----------------------|-----------|---------------|-------|-------|-------|-------|-------|-------|--------|

| Addr.  | R/W Control           |           | Default Value |       |       |       |       |       |       |        |

| PA     | Port A Data           | а7        | a6            | a5    | a4    | a3    | a2    | a1    | a0    |        |

| \$0000 | a a a a a a a a       | 0         | 0             | 0     | 0     | 0     | 0     | 0     | 0     |        |

| PB     | Port B Data           |           |               | b5    | b4    |       |       | b1    | b0    |        |

| \$0001 | r r a r               | -         | -             | 0     | 0     | -     | -     | 0     | 0     |        |

| DPA    | Port A Data Direction | dpa7      | dpa6          | dpa5  | dpa4  | dpa3  | dpa2  | dpa1  | dpa0  | 0=IN   |

| \$0002 | w w w w w w w         | (0)       | (0)           | (0)   | (0)   | (0)   | (0)   | (0)   | (0)   | 1=OUT  |

| DPB    | Port B Data Direction | sle       |               | dpb5  | dpb4  |       |       | dpb1  | dpb0  | 0=IN   |

| \$0003 |                       | 1         | -             | 0     | 0     | -     | -     | 1     | 0     | 1=OUT  |

| TCS1   | Timer Ctl. & Status 1 | tof1      | rtif          | tofe1 | rtie  | tofr1 | rtifr | rt1   | rt0   |        |

| \$0004 | r r a a w w a a       | 0         | 0             | 0     | 0     | (0)   | (0)   | 1     | 1     | 1=SET  |

| TCR1   | Timer Counter Reg. 1  | tm1r[7:0] |               |       |       |       |       |       |       |        |

| \$0005 | r r r r r r r r       | 0         | 0             | 0     | 0     | 0     | 0     | 0     | 0     |        |

| IRQS   | IRQ Control & Status  | irqr1     | irqr          |       |       | irqf  | irqf1 | irqe1 | irqe  |        |

| \$0006 | w w r r a a           | (0)       | (0)           | -     | -     | 0     | 0     | 0     | 0     |        |

| CPWD   | CMP & WDT Status      |           |               |       |       |       |       |       | wdt   |        |

| \$0007 | w                     | -         | -             | -     | -     | -     | -     | -     | 0     | 1=CLR  |

| RPA    | Port A Pull-up/down   |           |               | rpa5  | rpa4  | rpa3  | rpa2  | rpa1  | rpa0  |        |

| \$0009 | w w w w w w           | -         | -             | (0)   | (0)   | (0)   | (0)   | (0)   | (0)   |        |

| RPB    | Port B Pull-up        |           |               | rpb5  | rpb4  |       |       |       | rpb0  |        |

| \$000A | w w w                 | -         | -             | (0)   | (0)   | -     | -     | -     | (0)   |        |

#### 4. SIGNAL DESCRIPTIONS

| Mnemonic | PIN No.  | Description                                                                                                |

|----------|----------|------------------------------------------------------------------------------------------------------------|

| хо       | 1        | Crystal In Or Resistor In. An external resistive pull-up is connected with internal OSC circuitry for      |

|          |          | generating the internal clock in R-Oscillation mode. It will be connected with external crystal            |

|          |          | for crystal oscillation circuitry in crystal mode.                                                         |

| XI       | 2        | Crystal Output or External Clock Input. External clock input is connected with internal clock circuitry to |

|          |          | generate the internal clock for crystal oscillation circuitry in crystal mode.                             |

| PB4      | 3        | Port B4 Input. General-purpose input. It also can be used as the Main nRESET input.                        |

| PA[7:6]  | 4,5      | GPIO Port A Bit [7:6]. General-purpose inputs/outputs with EMI output control. Use DPA to configure        |

|          |          | it. In addition, PA7 can be used as the external interrupt inputs.                                         |

| PA[5:0]  | 6:7,9:12 | GPIO Port A Bit [5:0]. General-purpose inputs/outputs with EMI output control. Use DPA to configure        |

|          |          | it.                                                                                                        |

| PB0      | 8        | Port B0 Input. General-purpose input.                                                                      |

| PB5      | 13       | Port B5 Input. General-purpose input. It also can be used as the external Main IRQ input.                  |

| VSS      | 14       | System Ground.                                                                                             |

| VDD      | 15       | System Power Supply.                                                                                       |

| PB1      | 16       | Port B1 Output. General-purpose output with EMI output control.                                            |

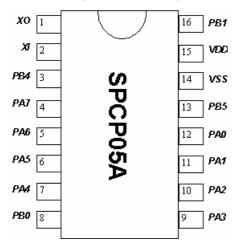

#### 4.1. PIN Assignment & Package Outline

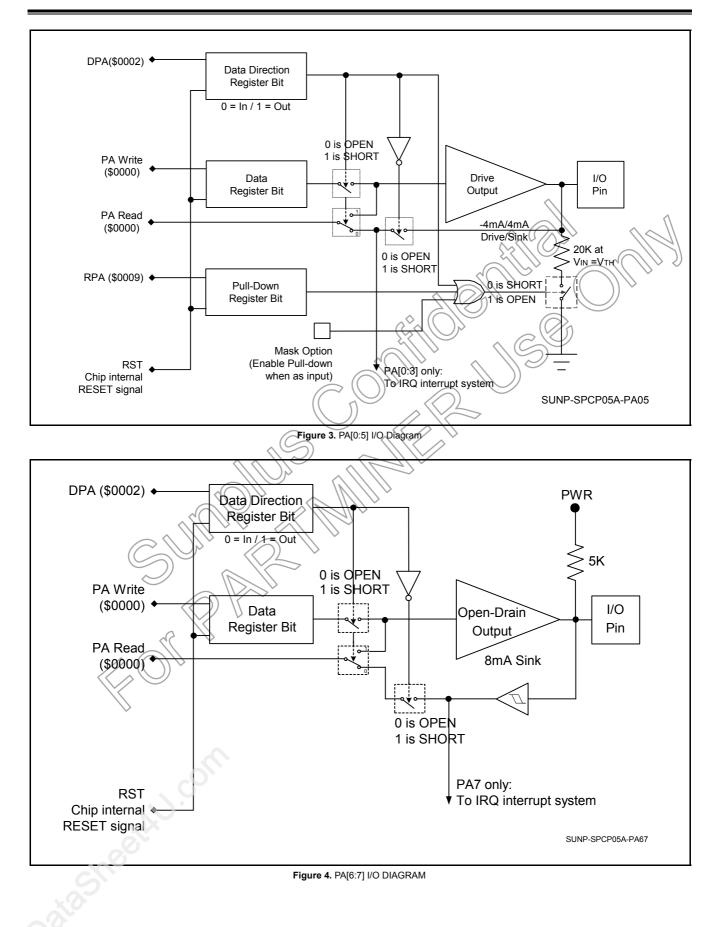

#### 4.2. Port A Registers & PINs

There are data register, direction control register, and pull up-down control register built in for PortA access and control. The port A pins are controlled by these registers. Data register (PA) is a read/write accessible register. The Direction Control Register

(DPA) and the Pull Up-Down Register (RPA) just can be written and read as "0". All of the output pins are slew rate controlled cell for EMI improvement. The detail description is shown below:

| PA     | Port A Data Register              |   |    |                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|--------|-----------------------------------|---|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Name   | Bit RW Dft Functional Description |   |    |                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| a[7:0] | [7:0]                             | A | 0h | Port A Data. When Port A is programmed as output pin, the output data on Port pins are determined by PA data register. When Port A is programmed as input pin, any "read" command on Port A Data Register will reflect the logic status of those I/O pins. PA data register will be set to "0" when RESET occurred. |  |  |  |  |  |  |

| DPA      |       |    |     | Port A Data Direction Register \$0002                                                                                                                                                                                                                                           |  |  |  |  |

|----------|-------|----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Name     | Bit   | RW | Dft | Functional Description                                                                                                                                                                                                                                                          |  |  |  |  |

| dpa[7:0] | [7:0] | W  | 0h  | <u>Port A Data Direction.</u> Port A can be programmed as input or outputs by DPA register. When dpan="1", the corresponding pins are programmed as outputs. When dpan="0", the corresponding pins are programmed as inputs. DPA will be set to "0"(input) when RESET occurred. |  |  |  |  |

|          |       |    |     |                                                                                                                                                                                                                                                                                 |  |  |  |  |

| RPA      |       |    |     | Port A Pull Up-Down Register \$0009                                                                                                                                                                                                                                                               |

|----------|-------|----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name     | Bit   | RW | Dft | Functional Description                                                                                                                                                                                                                                                                            |

| resv.    | [7:6] | -  |     | Reserved                                                                                                                                                                                                                                                                                          |

| rpa[5:0] | [5:0] | W  | 0h  | <u>Port A Pull Down Disable.</u> When the bit is '0', the build in pull down resistor of the corresponding pins at input mode will be enabled. When it is '1', the pull down resistor will be disabled. Pull down resistors is invalid during output mode. RPA will be set to "0"(enable mode) by |

|          |       | Ĉ  |     | RESET.                                                                                                                                                                                                                                                                                            |

|      | here information of the port A pinster showing dealer. |         |    |     |             |                                                       |  |  |  |  |  |  |  |

|------|--------------------------------------------------------|---------|----|-----|-------------|-------------------------------------------------------|--|--|--|--|--|--|--|

| Pins | Pull Up-Down                                           | R Value | In | Out | Source/Sink | Special Function                                      |  |  |  |  |  |  |  |

| PA7  | Always Pull Up                                         | 5ΚΩ     | IS | OD  | -/8mA       | <u>Ext. IRQ1.</u> Refer to Interrupt for more detail. |  |  |  |  |  |  |  |

| PA6  | Always Putl Up                                         | 5ΚΩ     | IS | OD  | -/8mA       | -                                                     |  |  |  |  |  |  |  |

| PA5  | Pull Down @ rpa5                                       | 20ΚΩ    | -  | 0   | 4/4mA       | -                                                     |  |  |  |  |  |  |  |

| PA4  | Pull Down @ rpa4                                       | 20ΚΩ    | -  | 0   | 4/4mA       | -                                                     |  |  |  |  |  |  |  |

| PA3  | Pull Down @ rpa3                                       | 20ΚΩ    | -  | 0   | 4/4mA       | Ext. IRQ0. Refer to Interrupt for more detail.        |  |  |  |  |  |  |  |

| PA2  | Pull Down @ rpa2                                       | 20ΚΩ    | -  | 0   | 4/4mA       | Ext. IRQ0. Refer to Interrupt for more detail.        |  |  |  |  |  |  |  |

| PA1  | Pull Down @ rpa1                                       | 20ΚΩ    | I  | 0   | 4/4mA       | Ext. IRQ0. Refer to Interrupt for more detail.        |  |  |  |  |  |  |  |

| PA0  | Pull Down @ rpa0                                       | 20ΚΩ    |    | 0   | 4/4mA       | Ext. IRQ0. Refer to Interrupt for more detail.        |  |  |  |  |  |  |  |

#### More information of the port A pins is shown below:

Note: Equivalent Pull down resistance on PA[5:0] is measured at  $V_{IN} = V_{TH}$ .

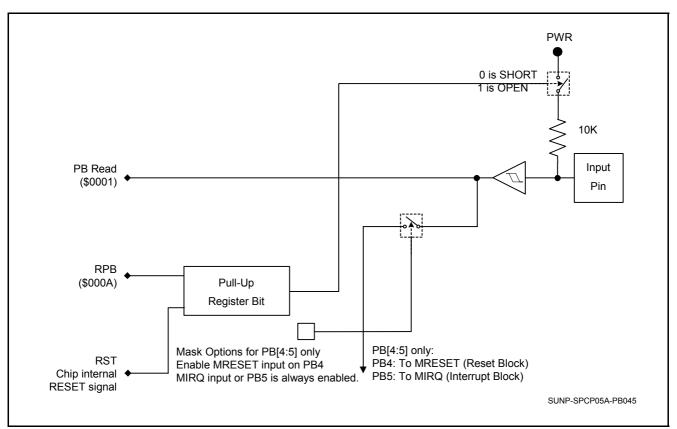

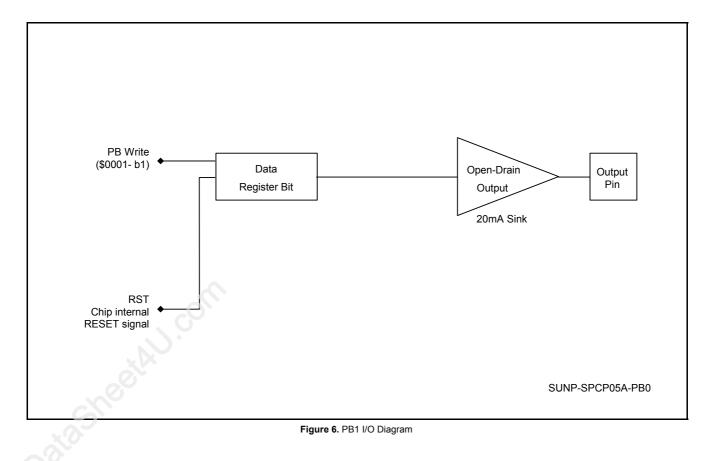

#### 4.3. Port B Registers & PINs

There are data register, direction control register, and pull up-down control register built in for port B accesses and control. The port B pins are controlled by these registers. Data register (PB) is a read/write accessible register. The Direction Control Register

(DPB) and the Pull Up-Down Register (RPB) just can be written and read as "0". The output pin, PB1, is slew rate controlled cell for EMI improvement. The detail description is shown below:

| PB        |                                   |   |   | Port B Data Register \$0001                                                                     |  |  |  |  |  |

|-----------|-----------------------------------|---|---|-------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Name      | Bit RW Dft Functional Description |   |   |                                                                                                 |  |  |  |  |  |

| resv.     | [7:6], [3:2]                      | - |   | Reserved.                                                                                       |  |  |  |  |  |

| b[5:4],b0 | [5:4], 0                          | R | 0 | Port B Data on PB[5:4], or PB0. The pure input pins, PB[5:4] and PB0, reflect the data to these |  |  |  |  |  |

|           |                                   |   |   | bits. Any "read" command on Port B Data Register will reflect the logic status of those I/O     |  |  |  |  |  |

|           |                                   |   |   | pins. PB data register will be set to "0" when RESET occurred.                                  |  |  |  |  |  |

| b1        | 1                                 | А | 0 | Port B Data on PB1. PB1 is a pure output pin. The output data on PB1 pin is determined by this  |  |  |  |  |  |

|           |                                   |   |   | bit. PB data register will be set to "0" when RESET occurred.                                   |  |  |  |  |  |

| RPB       | Port B Pull Up-Down Register \$000A |   |    |                                                                                             |            |  |  |  |  |  |

|-----------|-------------------------------------|---|----|---------------------------------------------------------------------------------------------|------------|--|--|--|--|--|

| Name      | Bit RW Dft Functional Description   |   |    |                                                                                             |            |  |  |  |  |  |

| resv.     | [7:6], [3:1]                        | - |    | Reserved.                                                                                   |            |  |  |  |  |  |

| rpb[5:4], | [5:4], 0                            | W | 0h | Port B Pull Up Disable. When the bit is 0 the build in pull up resistor of the correspondir | ng pins at |  |  |  |  |  |

| rpb0      |                                     |   |    | input mod will be enabled. When it is 1, the pull up resistor will be disabled.             | Pull up    |  |  |  |  |  |

|           |                                     |   |    | resistors is invalid during output mode. RPB will be set to "0"(enable mode) by RE          | ESET.      |  |  |  |  |  |

More information of the port B pins is shown below:

| PINs | Pull Up-Down   | R Value | In | Out | Source/Sink | Special Function                                                                        |

|------|----------------|---------|----|-----|-------------|-----------------------------------------------------------------------------------------|

| PB5  | Pull Up @ rpb5 | 10KΩ    | IS | -   |             | Ext. IRQ0. Refer to Interrupt for more detail.                                          |

| PB4  | Pull Up @ rpb4 | 10KΩ    | IS | -   |             | <u>nRESET.</u> Use as the external reset input with the Schmitt trigger negative logic. |

| PB1  | No             |         |    | OD  | -/20mA      | -                                                                                       |

| PB0  | Pull Up @ rpb0 | 10KΩ    | IS | -   |             | -                                                                                       |

Figure 5. PB[0,4:5] I/O Diagram

#### 4.4. Interrupt

There are three types of interrupt, Software Interrupt, External Interrupt, and Timer Interrupt. Software interrupt is generated by the instruction BRK. External interrupt is come from IRQ0 and IRQ1. These IRQ signals are combined with the specific function to generate the interrupt. Timer interrupt is generated by the Timer1 that will be described in detail in section *WDT*, *Timer1* & *Real Time Interrupt*.

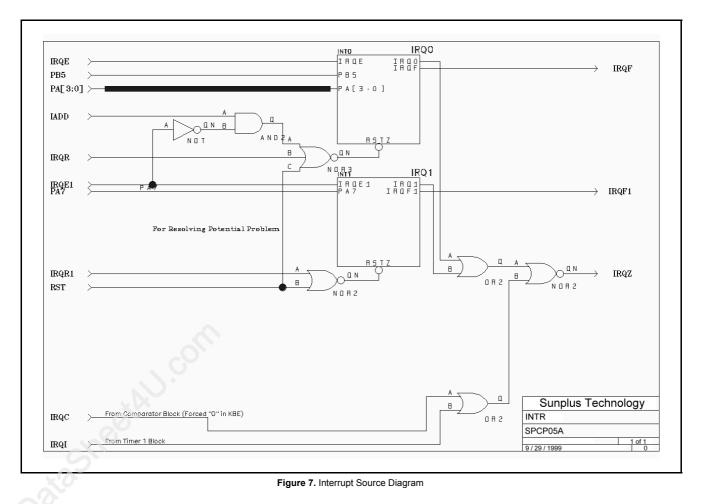

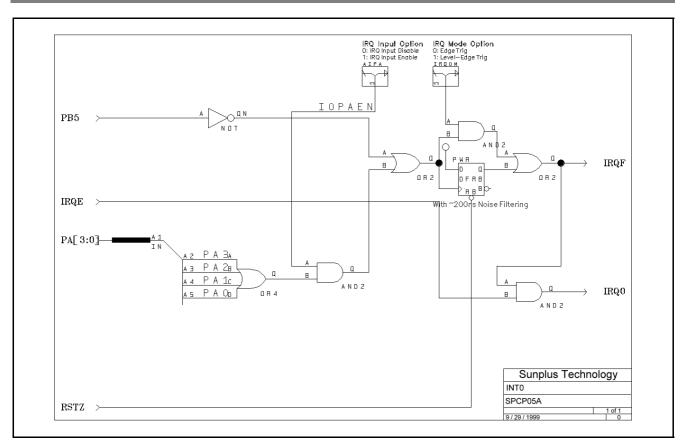

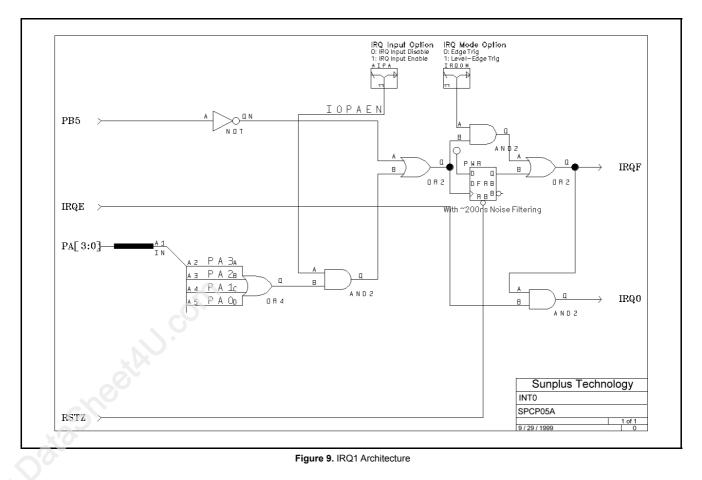

The interrupt source diagram is shown in Figure 7-9. The control register for external interrupts is defined in detail as below:

| IRQS  |       |    |     | IRQ Control & Status Register \$0006                                                             | 6   |

|-------|-------|----|-----|--------------------------------------------------------------------------------------------------|-----|

| Name  | Bit   | RW | Dft | Functional Description                                                                           |     |

| irqr1 | 7     | W  |     | irgf1 Clear bit. It is used to clear the irqf1 flag. 0: no clear, 1: clear irqf1.                |     |

| irqr  | 6     | W  |     | irgf Clear bit. It is used to clear the irqf flag. 0: no clear, 1: clear irqf.                   |     |

| resv. | [5:4] | -  |     | Reserved.                                                                                        |     |

| irqf  | 3     | R  | 0   | Interrupt Flag bit of PB5 or PA[0:3] IRQ0 Input. It is the flag of interrupt requests coming fro | om  |

|       |       |    |     | PB5 or PA[0:3]. 0: no interrupt, 1: interrupt requested.                                         |     |

| irqf1 | 2     | R  | 0   | Interrupt Flag bit of PA7 IRQ1 Input. It is the flag of interrupt requests coming from PA7. 0: r | no  |

|       |       |    |     | interrupt, 1: interrupt requested.                                                               |     |

| irqe1 | 1     | А  | 0   | Interrupt Control bit of PA7 IRQ1 Input. It is used to control the interrupt requests coming fro | om  |

|       |       |    |     | PA7. 0: disable, 1: enable.                                                                      |     |

| irqe  | 0     | А  | 0   | Interrupt Control bit of PB5 or PA[0:3] IRQ0 Input. It is used to control the interrupt reques   | sts |

|       |       |    |     | coming from PB5 or PA[0:3]. 0: disable, 1: enable.                                               |     |

#### Figure 8. IRQ0 Architecture

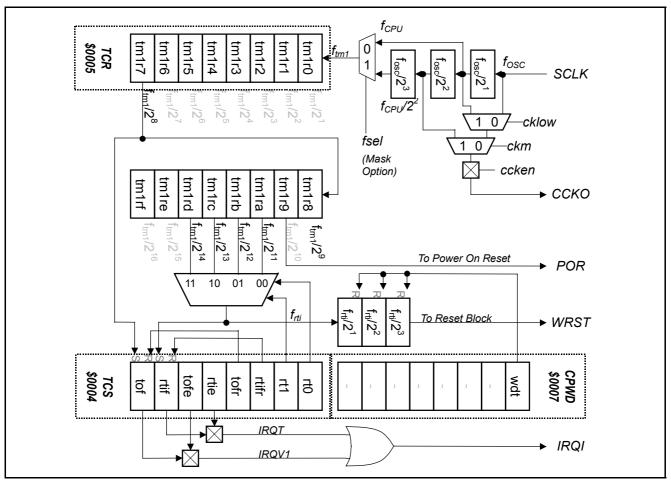

#### 4.5. WDT, TIMER1 & Real Time Interrupt

There is an 8-bit timer in Timer 1 with Real Time Interrupt. In addition, a watchdog Timer is built in for the time out reset. It can be enabled or disabled by the mask option. The function of

watchdog timer will be described in detail in next section. The related information of Timer is shown below:

| TCR1      | Timer Counter Register 1 |                                   |   |                                                                                        |                |  |  |  |  |

|-----------|--------------------------|-----------------------------------|---|----------------------------------------------------------------------------------------|----------------|--|--|--|--|

| Name      | Bit                      | Bit RW Dft Functional Description |   |                                                                                        |                |  |  |  |  |

| tm1r[7:0] | [7:0]                    | R                                 | 0 | Timer Counter Register 1. This register is a read-only register. It reports the curren | t value of the |  |  |  |  |

|           |                          |                                   |   | beginning 8-bit of timer chain. It is cleared by reset.                                |                |  |  |  |  |

| TCS1    |       | -  | -   | Timer Control/Status Register 1 \$0004                                                                                                                                                                                                              |

|---------|-------|----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name    | Bit   | RW | Dft | Functional Description                                                                                                                                                                                                                              |

| tof1    | 7     | R  | 0   | <u>Overflow Flag bit of Timer 1</u> . It is used to indicate the TCR1 rolls over from \$FF to \$00. 0: no overflow, 1: overflow is set. It can be cleared by writing "1" to tofr1.                                                                  |

| rtif    | 6     | R  | 0   | <u>Real Time Interrupt Flag bit of Timer 1</u> . It is used to indicate the status of selected Real Time<br>Interrupt Event of TCR1. 0: no event, 1: event is set. It can be cleared by writing "1" to<br>rtifr.                                    |

| tofe1   | 5     | A  | 0   | <u>Overflow Interrupt Control bit of Timer 1</u> . It is used to control the interrupt event being generated by tof1 is set. 0: disable, 1: enable.                                                                                                 |

| rtie    | 4     | A  | 0   | <u>Real Time Interrupt Control bit of Timer 1</u> . It is used to control the interrupt event of selected Real<br>Time being generated by rtif is set. 0: no event, 1: event is set. It can be cleared by<br>writing "1" to. 0: disable, 1: enable. |

| tofr1   | 3     | W  |     | <u>Overflow Interrupt Clear bit of Timer 1</u> . It is used to clear tof1 by writing "1" to this bit. 0: not cleared, 1: clear.                                                                                                                     |

| rtifr   | 2     | W  |     | <u>Real Time Interrupt Clear bit of Timer 1</u> . It is used to clear rtif by writing "1" to this bit. 0: not cleared, 1: clear.                                                                                                                    |

| rt[1:0] | [1:0] | А  | 00  | Selection of Real Time Interrupt Rate. It is used to select the Interrupt rate for Timer 1. The related rate is shown below.                                                                                                                        |

| CPWD  |       | Comparator & WDT Status \$0007 |     |                                                                                         |  |  |  |  |  |  |

|-------|-------|--------------------------------|-----|-----------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Name  | Bit   | RW                             | Dft | Functional Description                                                                  |  |  |  |  |  |  |

| resv. | [7:1] | -                              |     | Reserved.                                                                               |  |  |  |  |  |  |

| wdt   | 0     | W                              | 0   | Watch Dog Timer Time Out Reset. It is used to reset Watchdog Timer by writing it as "1" |  |  |  |  |  |  |

Figure 10. Block Diagram of WDT and Timer 1

#### 4.5.1. RT1: RT0 - Real time interrupt rate select

The RT0 & RT1 control bits select one of four types to let the Real Time Interrupt circuit run. The following table shows an example on interrupt period and WDT reset period on different options for Timer 1 clock input.

| E       | Example: CPU Clock $f_{CPU}$ = 1.0MHz (Oscillation Frequency = 2.0MHz) with two options for Timer 1 clock |                            |                            |                         |                            |                            |  |  |  |  |  |  |  |

|---------|-----------------------------------------------------------------------------------------------------------|----------------------------|----------------------------|-------------------------|----------------------------|----------------------------|--|--|--|--|--|--|--|

| RT1:RT0 |                                                                                                           | <b>RTI RATES</b>           |                            | MIN. WDT RESET (=RTI/8) |                            |                            |  |  |  |  |  |  |  |

|         | Divider                                                                                                   | option f <sub>CPU</sub> /4 | option f <sub>CPU</sub> /1 | Divider                 | option f <sub>CPU</sub> /4 | option f <sub>CPU</sub> /1 |  |  |  |  |  |  |  |

| 00      | 2048                                                                                                      | 8.192ms                    | 2.048ms                    | 16384                   | 65.536ms                   | 16.384ms                   |  |  |  |  |  |  |  |

| 01      | 4096                                                                                                      | 16.384ms                   | 4.096ms                    | 32768                   | 131ms                      | 32.768ms                   |  |  |  |  |  |  |  |

| 10      | 8192                                                                                                      | 32.768ms                   | 8.192ms                    | 65536                   | 262ms                      | 66ms                       |  |  |  |  |  |  |  |

| 11      | 16384                                                                                                     | 65.536ms                   | 16.384ms                   | 131072                  | 524ms                      | 131ms                      |  |  |  |  |  |  |  |

(RT1, RT0) for RTI & WDT Reset Frequency Table at f<sub>CPU</sub> = 1.0 MHz

#### 4.6. RESET

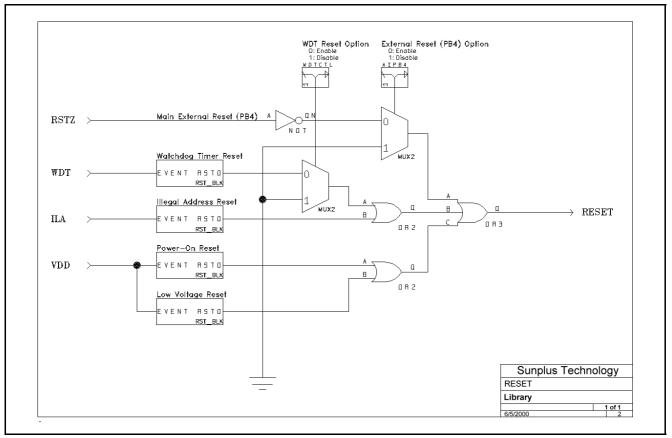

There are five types of the reset resources implemented for system reset: Power-On Reset, Low Voltage Reset, Illegal Address Reset, Main External Reset and Watchdog Timer Reset.

The last two are optional by mask for customers' configuration. Below shown is the block diagram of Reset.

Figure 11. Block Diagram of Reset

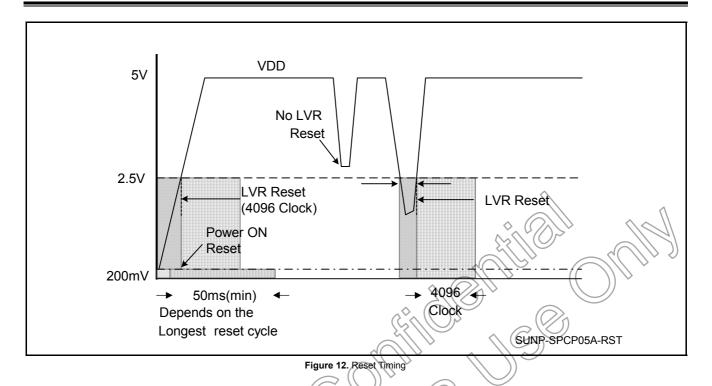

Power on Reset is an internal reset. The Power-on-Reset will generate the reset signal that will reset the CPU until oscillator stabilized. The CPU will become active after 50ms in minimum from system reset. To confirm the Power on Reset is generated properly, the system VDD should be held at a zero potential with respect to ground. Improper initial setting of the VDD might cause the Power on Reset to be failed and then the internal can not be initialized properly. In such case, the system is unexpected to work properly.

The Watchdog Timer (WDT) can be disabled or enabled through mask option. The internal reset of WDT will be generated by a time-out of the WDT automatically when watchdog is enabled. It is implemented on this device using the output of the RTI circuit and further dividing it by eight (RT1, RT0 timing times 8). This time out generates reset if the WDT register is not cleared. An internal reset is generated and reset vector fetched. Preventing a WDT time-out reset is done by writing a '1' to WDT (\$0007 b0) within a specific time. The min. WDT reset times listed in (RT1, RT0) & WDT Interrupt Frequency Table.

The internal reset of IAR generated when an instruction op-code fetch occurs from an address not implemented in the RAM (\$00C0-\$00FF) nor ROM (\$0400-\$0FFF). The IAR will generate the reset signal that will reset the CPU and other peripherals.

#### 4.7. Option Table

| No. | Name   | Relation    | Function                                                                                                                |

|-----|--------|-------------|-------------------------------------------------------------------------------------------------------------------------|

| 1   | aipa   | PA[3:0] Pin | <u>Alternative Input Option on PA[3:0] for IRQ0.</u> 0: Alternative Input is Disabled. 1: Alternative Input is Enabled. |

| 2   | aipb4  | PB4 Pin     | Alternative Input Option on PB4 for nRESET. 0: Alternative Input is Enabled. 1: Alternative Input is Disabled.          |

| 3   | clkext | XI/XO pins  | External Clock Input Option. 0: Internal clock mode, depended on OSC mode option, oscm.                                 |

|     | C      |             | 1) External clock mode. XO is used to feed in external clock.                                                           |

| 4   | oscm   | XI/XO pins  | Oscillation Mode Option. 0: Crystal mode, A crystal circuitry is connected to XI and XO for                             |

|     |        |             | clock generating. 1: R-OSC mode, A Pull up Resistor is placed on XI for internal                                        |

|     |        |             | OSC circuitry to generate the clock.                                                                                    |

| 5   | irq0m  | IRQ0        | IRQ Trig Mode Option on IRQ0. 0: Edge Trig. 1: Level-Edge Trig.                                                         |

| 6   | fsel   | Clock       | <u>CPU Clock Divisor Option.</u> 0: f <sub>CPU</sub> . 1: f <sub>CPU</sub> /4.                                          |

| 7   | wdłctl | WDT         | Option of Function Control on Watchdog Timer Reset. 0: Function is enabled. 1: Function is                              |

|     |        | $ \ge $     | disabled.                                                                                                               |

#### 5. ELECTRICAL SPECIFICATIONS

#### 5.1. Item Definition

| Item            | Definition              | ltem            | Definition                      |

|-----------------|-------------------------|-----------------|---------------------------------|

| V <sub>IH</sub> | Input High Voltage      | I <sub>он</sub> | Output High Current (Source)    |

| V <sub>IL</sub> | Input Low Voltage       | I <sub>OL</sub> | Output Low Current (Sink)       |

| V <sub>TH</sub> | Input Threshold Voltage | Iz              | Output Leakage Current (Source) |

| $SF_{V}$        | Frequency Stability     | R <sub>P</sub>  | Pull-up/down Resistance         |

| $DF_{V}$        | Frequency Deviation     |                 |                                 |

#### 5.2. Absolute Maximum Rating

| Characteristics               | ltem             | Min. | Тур. | Max.     | Unit | Condition    |

|-------------------------------|------------------|------|------|----------|------|--------------|

| Storage Temperature           | T <sub>STR</sub> | -40  | -    | 125      | °C   | Package Type |

| Operating Ambient Temperature | T <sub>OPR</sub> | 0    | -    | 70       | °C   |              |

| Voltage Rating on Input       | V <sub>IN</sub>  | -0.3 | -    | VDD +0.3 | V    |              |

| Voltage Rating on VDD         |                  | -0.3 | -    | 7.0      | V    |              |

| Output Voltage                | V <sub>OUT</sub> | 0    | -    | VDD      | V    |              |

Note: Stresses beyond those given in the Absolute Maximum Rating table may cause operational errors or damage to the device. For normal operational conditions see AC/DC Electrical Characteristics.

#### 5.3. Recommended Operating Conditions

| Characteristics                | Item              | Min. | Тур. | Max. | Unit | Condition                              |

|--------------------------------|-------------------|------|------|------|------|----------------------------------------|

| Operating Supply Voltage       | VDD               | 2.4  | -    | 5.5  | V    |                                        |

| CPU Clock (Internal CPU clock) | f <sub>CPU</sub>  | 200K | -    | 6.0M | Hz   | VDD = 5.0V                             |

| Power Consumption              | I <sub>DD</sub>   | -    | 3.7  | -    | mA   | f <sub>CPU</sub> = 6.0MHz @ VDD = 5.0V |

| Power Up Initial Voltage       | V <sub>INIT</sub> | -    | -    | 1.5  | V    |                                        |

| LVR Trigger Voltage            | V <sub>LVR</sub>  | 2.4  | -    | -    | V    |                                        |

#### 5.4. PIN Attribute Description (VDD = 5.0V, Temperature = 25°C)

| Mnemonic | Description                     | Item            | Min. | Тур. | Max. | Unit | Condition                                                 |

|----------|---------------------------------|-----------------|------|------|------|------|-----------------------------------------------------------|

| PA[5:0]  | Input TTL level with Pull Down  | VIH             | 2.0  | -    | -    | V    |                                                           |

|          | R option                        | V <sub>IL</sub> | -    | -    | 0.8  | V    |                                                           |

|          | 4mA Output with Slew Rate       | $V_{TH}$        | 1.3  | -    | 2.0  | V    | 0°℃ to 40°℃                                               |

|          | Control.                        | I <sub>OH</sub> | 4.0  | -    | -    | mA   | V <sub>OH</sub> = 2.4V                                    |

|          |                                 | I <sub>OL</sub> | 4.0  | -    | -    | mA   | V <sub>OL</sub> = 0.5V                                    |

|          |                                 | Iz              | -    | -    | 10   | μA   |                                                           |

|          |                                 | $R_{P}$         | 16   | 20   | 24   | KΩ   | $V_{IN}$ = $V_{TH}$ , 0°C to 40°C                         |

|          | <u></u>                         |                 | 40   | 50   | 60   | KΩ   | $V_{IN} = VDD = 5V$                                       |

| XI, XO   | Special Input Cell Pair for RC  | $SF_V$          | -    | -    | ±5   | %    | (f <sub>5.5V</sub> -f <sub>4.5V</sub> )/f <sub>5V</sub> * |

|          | oscillation                     | $DF_v$          | -    | -    | ±10  | %    | VDD = 5V                                                  |

|          |                                 | R₽              | -    | 45.3 | -    | KΩ   | f <sub>5V</sub> = 5.15MHz                                 |

| PA[7:6]  | Input TTL level with Pull Up R, | VIH             | 2.4  | -    | -    | V    |                                                           |

|          | Schmitt-Triger                  | V <sub>IL</sub> | -    | -    | 0.8  | V    |                                                           |

|          | 8mA Open Drain Output with      | I <sub>OL</sub> | 8.0  | -    | -    | mA   | V <sub>OL</sub> = 0.5V                                    |

| 2        | Slew Rate Control.              | R₽              | 4.0  | 5.0  | 6.0  | KΩ   | V <sub>IN</sub> = VSS                                     |

| Mnemonic     | Description                   | ltem            | Min. | Тур. | Max. | Unit | Condition              |

|--------------|-------------------------------|-----------------|------|------|------|------|------------------------|

| PB[5:4], PB0 | Input CMOS level with Pull Up | VIH             | 3.5  | -    | -    | V    |                        |

|              | R, Schmitt-Triger             | VIL             | -    | -    | 1.2  | V    |                        |

|              |                               | R <sub>P</sub>  | 8.0  | 10   | 12   | KΩ   | V <sub>IN</sub> = VSS  |

| PB1          | 20mA Open Drain Output with   | I <sub>OL</sub> | 20   | -    | -    | mA   | V <sub>OL</sub> = 0.5V |

|              | Slew Rate Control.            | Iz              | -    | -    | 10   | μA   |                        |

Note: \*The frequency defined in this item is based on the CPU frequency. It is one-half of the oscillation frequency.

#### 5.5. Timing Diagram (VDD = 4.5V to 5.5V, Temperature = 0°C to 40°C or 70°C)

| Characteristics                          | ltem             | Min. | Тур. | Max. | Unit | Condition                      |

|------------------------------------------|------------------|------|------|------|------|--------------------------------|

| Power On Reset (Ensure POR)              | t <sub>POR</sub> | -    | -    | 120  | ms   | Option for t <sub>POR</sub> /2 |

| Output Falling Edge Transition (PA[7:6]) | t <sub>R</sub>   | 12   | 15   | 18   | ns   | C <sub>L</sub> = 10pf, 90%-10% |

|                                          |                  | -    | -    | 20   |      | 40°C / 70°C                    |

| Output Falling Edge Transition (PB1)     | t <sub>R</sub>   | 12   | 15   | 18   | ns   | C <sub>L</sub> = 10pf, 90%-10% |

|                                          |                  | -    | -    | 20   |      | 40°C / 70°C                    |

| Output Rising Edge Transition (PA[5:0])  | t <sub>R</sub>   | 17   | 22   | 27   | ns   | C <sub>L</sub> = 10pf, 10%-90% |

|                                          |                  | -    | -    | 29   |      | 40℃/ 70℃                       |

| Output Falling Edge Transition (PA[5:0]) | t <sub>F</sub>   | 14   | 17   | 20   | ns   | C∟= 10pf, 90%-10%              |

|                                          |                  | -    | -    | 22   |      | 40℃/ 70℃                       |

#### 5.6. R-Osc Mode Frequency Curve (Normalized Data)

© Sunplus Technology Co., Ltd. Proprietary & Confidential

© Sunplus Technology Co., Ltd. Proprietary & Confidential AUG. 05, 2004 Version: 1.4

#### 6. PACKAGE/PAD LOCATIONS

#### 6.1. Package Information

#### 6.1.1. PDIP 16

#### 6.2. Ordering Information

| Product Number    | Package Type            |

|-------------------|-------------------------|

| SPCP05A-NnnV-C    | Chip form               |

| SPCP05A-NnnV-PD03 | Package form - PDIP16   |

| SPCP05A-NnnV-FD03 | Lead free form - PDIP16 |

#### 7. DISCLAIMER

The information appearing in this publication is believed to be accurate.

Integrated circuits sold by Sunplus Technology are covered by the warranty and patent indemnification provisions stipulated in the terms of sale only. SUNPLUS makes no warranty, express, statutory implied or by description regarding the information in this publication or regarding the freedom of the described chip(s) from patent infringement. FURTHERMORE, SUNPLUS MAKES NO WARRANTY OF MERCHANTABILITY OR FITNESS FOR ANY PURPOSE. SUNPLUS reserves the right to halt production or alter the specifications and prices at any time without notice. Accordingly, the reader is cautioned to verify that the data sheets and other information in this publications. Applications involving unusual environmental or reliability requirements, e.g. military equipment or medical life support equipment, are specifically not recommended without additional processing by SUNPLUS for such applications. Please note that application circuits illustrated in this document are for reference purposes only.

#### 8. REVISION HISTORY

| Date          | Revision # | Description                                                                                                                                        | Page     |

|---------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| AUG. 05, 2004 | 1.4        | Correct ordering information                                                                                                                       | 20       |

| JAN. 29, 2003 | 1.3        | Incorrect format section 5.4                                                                                                                       | 17 - 18  |

| SEP. 04, 2002 | 1.2        | <ol> <li>Revise the storage temperature in section "<u>5.2. Absolute Maximum Rating</u>"</li> <li>Add "<u>6. PACKAGE/PAD LOCATIONS</u>"</li> </ol> | 17<br>20 |

| OCT. 17, 2001 | 1.1        | <ol> <li>Revise Timer1 Block Diagram and I/O attribute on Port B Data Register</li> <li>Renew to a new document format</li> </ol>                  |          |

| SEP. 05, 2001 | 1.0        | Original                                                                                                                                           |          |