## SP8400

### Very Low Phase Noise Synthesiser Divider

The SP8400 is a very low phase noise programmable divider which is based on a divide by 8/9 dual modulus prescaler and a 12 stage control counter. This gives a minimum division ratio of 56 (64 for fractional - N synthesis applications), and a maximum division ratio of 4103. Special circuit techniques have been used to reduce the phase noise considerably below that produced by standard dividers.The data inputs are CMOS or TTL compatible.

The SP8400 is packaged in a 28 pin plastic SO package.

#### **FEATURES**

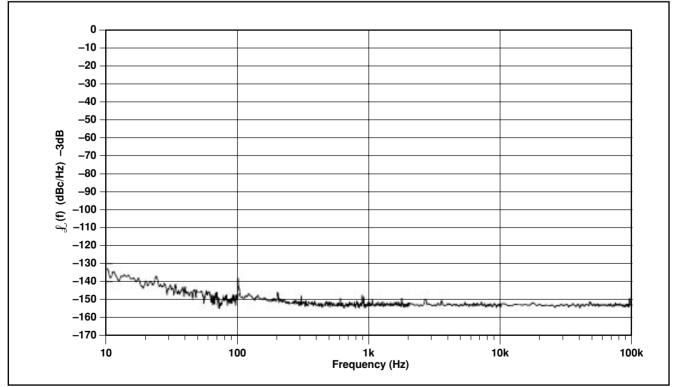

- Very low Phase Noise (Typically -156dBc/Hz at 1kHz offset)

- Supply Voltage 5V

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage              | 6.5V            |

|-----------------------------|-----------------|

| Output Current              | 20mA            |

| Storage Temperature Range   | -55°C to +125°C |

| Maximum Clock Input Voltage | 2.5V p-p        |

| Septembe                                                                                    | r 2005 |  |

|---------------------------------------------------------------------------------------------|--------|--|

| Ordering Information                                                                        |        |  |

| SP8400/KG/MPES 28 Pin SOIC Tubes<br>SP8400/KG/MPFP 28 Pin SOIC* Tubes<br>*Pb Free Matte Tin |        |  |

|                                                                                             |        |  |

| M2 H 1 28 H M3<br>M1 H 2 27 H M4                                                            |        |  |

|                                                                                             |        |  |

| V <sub>CC +</sub> 5V 🖽 4 25 🖽 M6                                                            |        |  |

| GND - 5 24 - M7                                                                             |        |  |

|                                                                                             |        |  |

|                                                                                             |        |  |

|                                                                                             |        |  |

|                                                                                             |        |  |

|                                                                                             |        |  |

| $V_{CC} + 5V$ $L$ 11 18 $L$ $V_{CC} + 5V$<br>$V_{CC} + 5V$ $L$ 12 17 $L$ N/C                |        |  |

|                                                                                             |        |  |

|                                                                                             |        |  |

| M                                                                                           | P28    |  |

Fig.1 Pin connections - top view

Fig.2 Typical single sideband phase noise measured at 300MHz

Zarlink Semiconductor Inc. Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc. Copyright 1997-2005, Zarlink Semiconductor Inc. All Rights Reserved.

#### **ELECTRICAL CHARACTERISTICS**

Guaranteed over: Supply voltage V<sub>CC</sub> = +4.75V to +5.25V Temperature T<sub>amb</sub> = -10°C to +75°C Tested at +4.75V and +5.25V at T<sub>amb</sub> = +25°C

| Characteristic                                                               | Pin                             | Value      |            |                    | Units                 | Conditions                                                                                                                                 |

|------------------------------------------------------------------------------|---------------------------------|------------|------------|--------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Characteristic                                                               |                                 | Min.       | Тур.       | Max.               |                       | Conditions                                                                                                                                 |

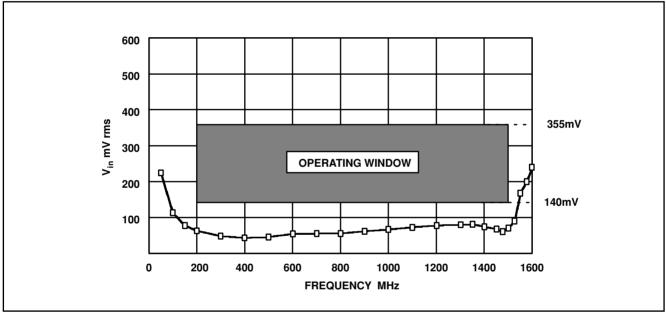

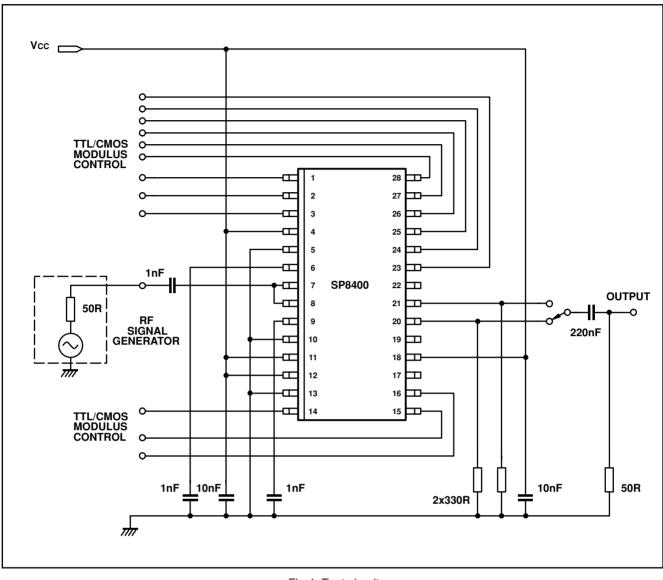

| Supply current<br>Output voltage swing<br>Input sensitivity 200MHz to 1.5GHz | 4, 11, 12, 18<br>20, 21<br>7, 8 | 122<br>320 | 137<br>410 | 152<br>140<br>(-4) | mA<br>mV<br>mV<br>dBm | Output loaded with 300R See Fig.4<br>p-p @ 1.5GHz input ÷ 71 mode<br>See Fig.4<br>RMS Sine wave into 50 Ohms<br>(dBm equivalent) See Fig.3 |

| Data Inputs<br>Logic high voltage<br>Low low voltage<br>Input current        |                                 | 2.2        |            | 0.8<br>180         | V<br>V<br>μA          | 5V Data input voltage                                                                                                                      |

Fig.3 Typical input sensitivity

Fig.4 Test circuit

#### APPLICATIONS INFORMATION

#### Circuit description, synthesiser divider

The divider is based on a divide by 8/9 modulus prescaler, and a 12 stage control counter. This gives minimum fractional – N division ratio of 64 (56 for general division), and a maximum division ratio of 4103. The inputs to the control counter are TTL/CMOS compatible. There is a fixed offset of 8 between the number on the data lines and the actual division ratio.

The output is one transition only per divide cycle. This eliminates the problem of where to put the redundant edge when the divider is used in a fractional–N system, and also avoids the problem of how to define the output pulse width. This means that the overall division ratio conventionally defined in terms of the rate of edges of the same polarity is twice the selected division ratio.

#### Equations for division

The M and A data inputs form a 12 bit number with A0 being the least significant bit and M8 being the most significant bit.

| Definition 1: | Division ratio – (input frequency to out put edges, positive or negative). |  |  |  |  |

|---------------|----------------------------------------------------------------------------|--|--|--|--|

|               | = Number loaded + 8                                                        |  |  |  |  |

| Definition 2: | Division ratio – (input frequency to out put frequency).                   |  |  |  |  |

|               | = (Number loaded + 8) x 2                                                  |  |  |  |  |

#### Available division ratio

All division ratios of 64 to 4103 (Definition 1) will return the divider to the same internal state at the end of the count and hence these are the only divisional ratios to be used for fractional–N synthesiser application.

All division ratios of 56 to 4103 are available for general division purposes. Additional division ratios available for general division are:-

8,9 16, 17, 18 24, 25, 26, 27 32, 33, 34, 35, 36 40, 41, 42, 43, 44, 45 48, 49, 50, 51, 52, 53, 54

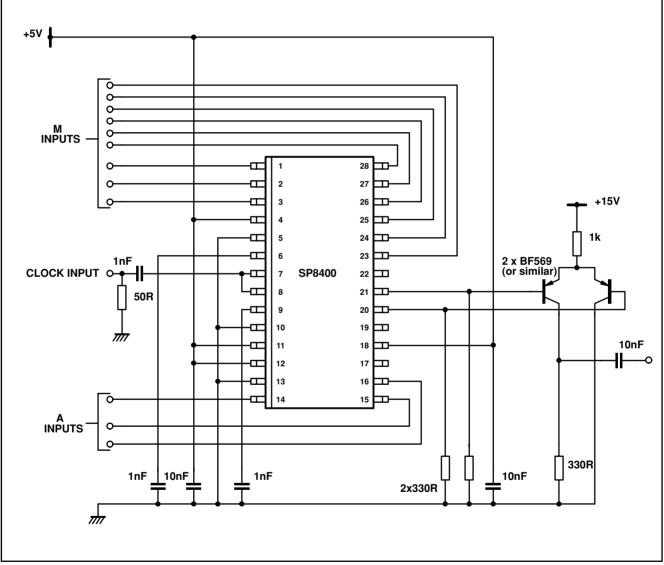

Fig.5 Typical application combining output to increase signal and retain low phase noise

# For more information about all Zarlink products visit our Web Site at

#### www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's I<sup>2</sup>C components conveys a licence under the Philips I<sup>2</sup>C Patent rights to use these components in and I<sup>2</sup>C System, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright Zarlink Semiconductor Inc. All Rights Reserved.

TECHNICAL DOCUMENTATION - NOT FOR RESALE