## **Ethernet System Controller**

• 83C795

Data Book

#### **TABLE OF CONTENTS**

| 1.0. GENERAL DESCRIPTION                                             | 1  |

|----------------------------------------------------------------------|----|

| 2.0. FEATURES                                                        | 1  |

| 3.0. FUNCTIONAL DESCRIPTION                                          | 3  |

| 3.1. DESCRIPTION OF DATA PATH                                        | 3  |

| 3.2. CONVENTIONS                                                     | 3  |

| 4.0. PIN LIST                                                        | 5  |

| 4.1. SPECIAL INPUT-TO-OUTPUT PIN MAPPING                             | 10 |

| 5.0. ETHERNET SYSTEM CONTROLLER REGISTERS                            | 12 |

| 5.1. HOST INTERFACE INTERNAL REGISTERS                               | 14 |

| 5.1.1. CR - Control Register                                         | 14 |

| 5.1.2. EER - EEROM Register                                          | 14 |

| 5.1.3. IOPL - I/O Pipe Data Location Low                             | 15 |

| 5.1.4. IOPH - I/O Pipe Data Location High                            | 15 |

| 5.1.5. HWR - Hardware Support Register                               | 16 |

| 5.1.6. BPR - BIOS Page Register                                      | 17 |

| 5.1.7. ICR - Interrupt Control Register                              | 17 |

| 5.1.8. REV/IOPA - Revision/I/O Pipe Address Register                 | 18 |

| 5.1.9. LAN0 - LAN5 - LAN Address Registers                           |    |

| 5.1.10. BDID - Board ID Register                                     |    |

| 5.1.11. CKSM - Checksum Register                                     |    |

| 5.1.11. GCR2 - General Control Register 2                            |    |

| 5.1.13. IAR - I/O Address Register.                                  |    |

| 5.1.14. RAR - RAM Address Register                                   |    |

| 5.1.15. BIO - ROM Control Register                                   |    |

| 5.1.16. GCR - General Control Register                               |    |

| 5.1.17. ERFAL - Early Receive Fail Address Low Register              |    |

| 5.1.18. ERFAH - Early Receive Fail Address High Register             |    |

| 5.2. LAN CONTROLLER REGISTER DESCRIPTIONS                            |    |

| 5.2.1. ALICNT - Alignment Error Counter Register                     |    |

| 5.2.2. BOUND - Receive Boundary Page Register                        |    |

| 5.2.3. CMD - Command Register.                                       |    |

| 5.2.4. COLCNT - Collision Count Register                             |    |

| 5.2.5. CRCCNT - CRC Error Counter                                    |    |

| 5.2.6. CURR - Current Frame Buffer Pointer Register.                 |    |

| 5.2.7. CURRH - Current Frame Buffer Descriptor Pointer Register High |    |

| 5.2.8. CURRL - Current Frame Buffer Descriptor Pointer Register Low  | 25 |

| 5.2.9. DCON - Data Configuration Register                     |

|---------------------------------------------------------------|

| 5.2.10. ENH - Enhancement Register                            |

| 5.2.11. ERWCNT - Early Receive Warning Threshold Register     |

| 5.2.12. GROUP0-GROUP7 - Multicast Filter Table Registers      |

| 5.2.13. INTMASK - Interrupt Mask Register                     |

| 5.2.14. INTSTAT - Interrupt Status Register                   |

| 5.2.15. MANCH - Manchester Management Register                |

| 5.2.16. MPCNT - Missed Packet Error Counter Register          |

| 5.2.17. NEXT - DMA Controller Next Buffer Register            |

| 5.2.18. RADDH - Receive Burst Starting Address High Register  |

| 5.2.19. RADDL - Receive Burst Starting Address Low Register   |

| 5.2.20. RBEGIN - Receive Buffer Starting Address Register     |

| 5.2.21. RCNTH - Receive Byte Count High Register              |

| 5.2.22. RCNTL - Receive Byte Count Low Register               |

| 5.2.23. RCON - Receive Configuration Register                 |

| 5.2.24. RDOWNH - Buffer Room Remaining High Register          |

| 5.2.25. RDOWNL - Buffer Room Remaining Low Register           |

| 5.2.26. REND - Receive Buffer End Register                    |

| 5.2.27. RSTART - Receive Start Page Register                  |

| 5.2.28. RSTAT - Receive Packet Status Register                |

| 5.2.29. RSTOP - Receive Stop Page Register                    |

| 5.2.30. RTABH - Receive Buffer Table Pointer High Register    |

| 5.2.31. RTABL - Receive Buffer Table Pointer Low Register     |

| 5.2.32. STA0-STA5 - Station Address Registers                 |

| 5.2.33. TADDH - Transmit Burst Starting Address High Register |

| 5.2.34. TADDL - Transmit Burst Starting Address Low Register  |

| 5.2.35. TBEGIN - Transmit Buffer Starting Address Register    |

| 5.2.36. TCNTH - Transmit Frame Length High Register           |

| 5.2.37. TCNTL - Transmit Frame Length Low Register            |

| 5.2.38. TCON - Transmit Configuration Register                |

| 5.2.39. TDOWNH - Transfer Count High Register                 |

| 5.2.40. TDOWNL - Transfer Count Low Register                  |

| 5.2.41. TEND - Transfer Buffer End Register                   |

| 5.2.42. TLEVEL - Transmit FIFO Track Register                 |

| 5.2.43. TSTARTH - Transmit Start Page High Register           |

| 5.2.44. TSTARTL - Transmit Start Page Low Register            |

| 5.2.45. TSTAT - Transmit Status Register                      |

| 5.2.46. TTABH - Transmit Buffer Pointer High Register         |

| 5.2.47. TTABL - Transmit Buffer Pointer Low Register          |

| 5.2.48. UBRCV - Ultra Board Receive Register                 | 40 |

|--------------------------------------------------------------|----|

| 6.0. HOST INTERFACE SECTION                                  | 44 |

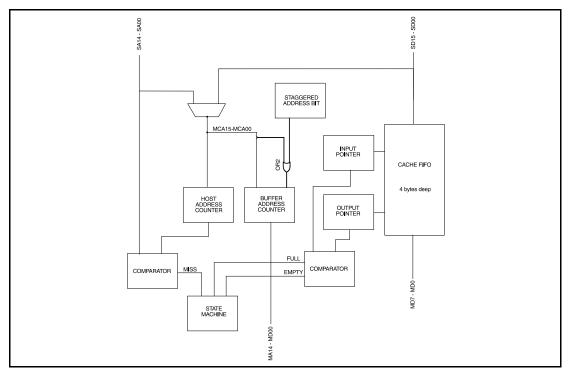

| 6.1. MEMORY CACHE                                            | 44 |

| 6.1.1. Zero Wait State Response to Host                      | 45 |

| 6.1.2. Staggered Address Transfers                           | 45 |

| 6.1.3. Operation on Micro-Channel Adapters                   | 46 |

| 6.2. I/O-MAPPED PIPE                                         | 46 |

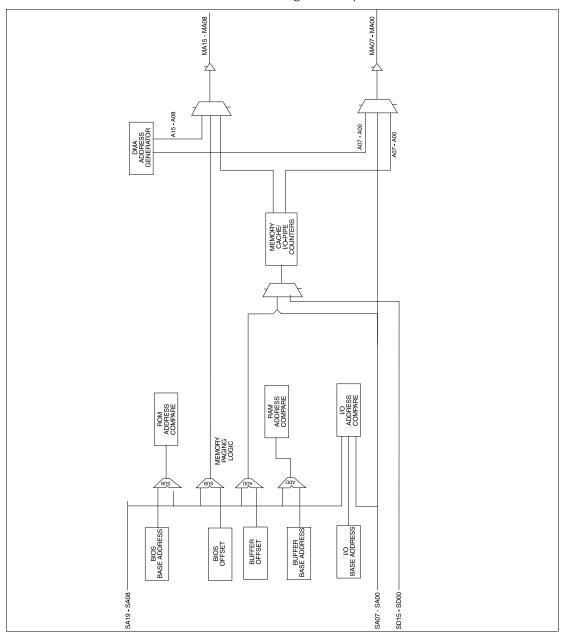

| 6.3. ADDRESS DECODERS                                        | 46 |

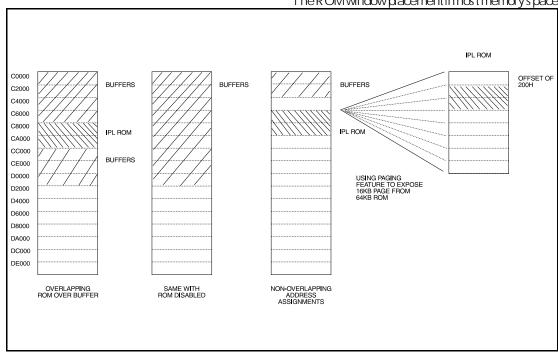

| 6.3.1. Memory Address Generation                             | 48 |

| 6.3.2. I/O Address Decode                                    | 50 |

| 6.3.2.1. PC-98 Bus Support                                   | 50 |

| 6.4. BUS CONTROL SIGNALS                                     | 50 |

| 6.4.1. IORDY                                                 | 50 |

| 6.4.2. Zero Wait State Response To Host                      | 50 |

| 6.5. MEMORY BUS STRUCTURE AND CONFIGURATION                  | 51 |

| 6.5.1. Memory Bus Width Control                              | 51 |

| 6.5.2. 16-Bit Response To Host Access                        | 51 |

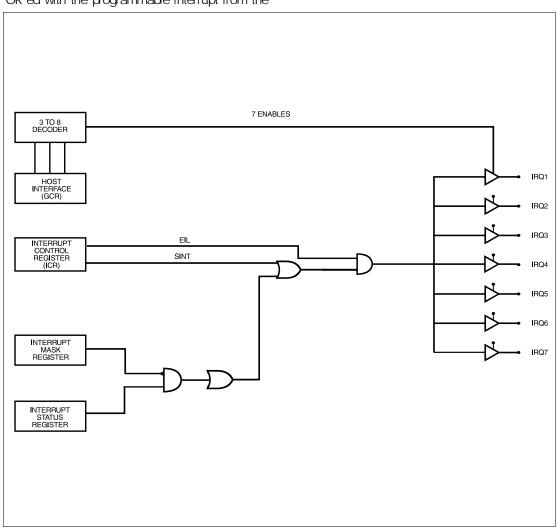

| 6.6. INTERRUPT REQUEST CONTROL LOGIC                         | 52 |

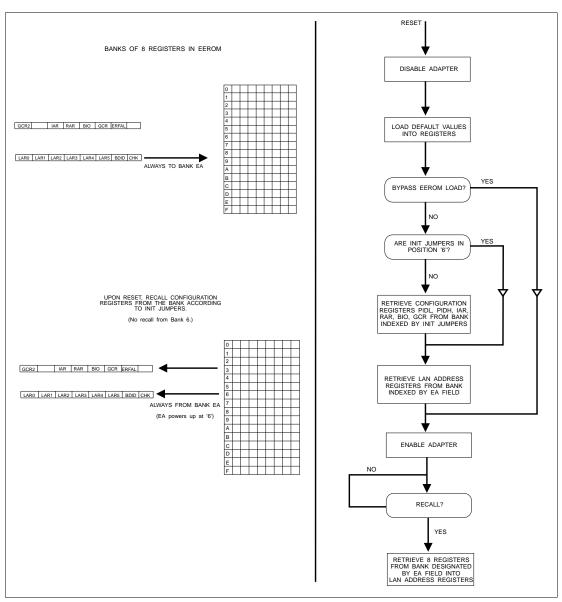

| 6.7. EEROM CONTROLLER AND ITS UTILIZATION                    | 53 |

| 6.7.1. Initialization Of 83C795                              | 53 |

| 6.7.2. Retrieval And Storage Of Host Configuration Registers | 54 |

| 6.7.2.1. EEROM Interface Overview                            | 54 |

| 6.7.2.2. EEROM Recall Operation Details                      | 54 |

| 6.7.2.3. Storage Operations                                  | 56 |

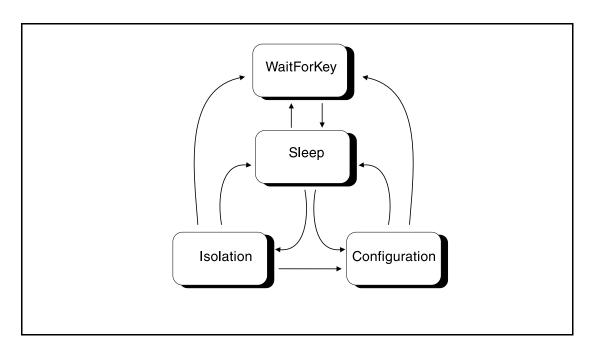

| 6.8. PLUG AND PLAY                                           | 57 |

| 6.8.1. Auto-Configuration Ports                              | 57 |

| 6.8.2. Plug And Play States                                  | 58 |

| 6.8.2.1. Isolation                                           | 59 |

| 6.8.2.2. Configuration And Activation                        | 59 |

| 6.8.3. Configuration Registers                               | 59 |

| 6.8.4. Resource String                                       | 62 |

| 6.8.5. Configuring As A Boot Card                            | 64 |

| 6.8.6. Configuring With An I/O-Mapped Pipe                   | 64 |

| 6.8.7. Buffer Memory Limitations                             | 64 |

| 6.9. EXTERNAL POWER SUPPLY CONTROL                           | 64 |

| 7.0. LAN CONTROLLER OVERVIEW                                 |    |

| 7.1. DMA CONTROLLER                                          | 65 |

| 7.1.1. Assembly and Disassembly Latches                      | 65 |

| 7.1.2. Memory Interface Unit                                 | 65 |

|                                                              |    |

| 7.1.3. LAN Controller Internal Bus Arbitration                   | 67 |

|------------------------------------------------------------------|----|

| 7.1.4. DMA Microcontroller                                       | 67 |

| 7.1.5. How to Access Registers                                   | 67 |

| 7.1.6. Memory Interface                                          | 67 |

| 7.2. FIFOS                                                       | 68 |

| 7.3. RECEIVER NETWORK INTERFACE (PHY-TO-MAC)                     | 68 |

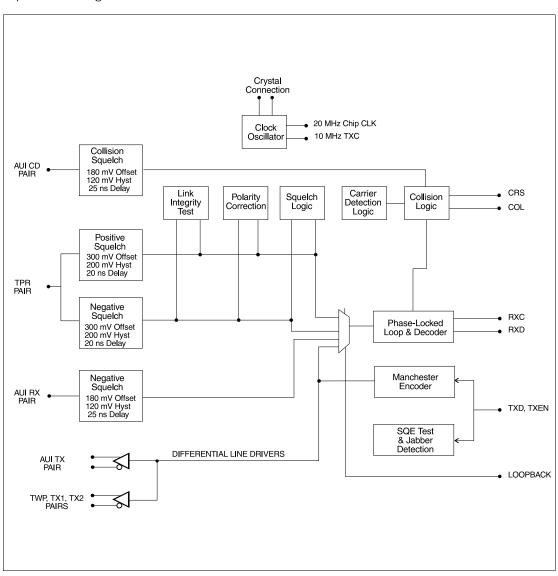

| 7.3.1. AUI Differential Receiver                                 | 69 |

| 7.3.2. Twisted-Pair Differential Receiver                        | 69 |

| 7.3.2.1. Extended Length For Twisted-Pair                        | 69 |

| 7.3.3. Manchester Decoder                                        | 69 |

| 7.3.4. Carrier Sense                                             | 69 |

| 7.3.5. Collision Detect                                          | 69 |

| 7.3.6. Loopback Mode                                             | 69 |

| 7.4. MAC RECEIVER                                                | 70 |

| 7.4.1. Basic Functions                                           | 70 |

| 7.4.2. Interface to the MAC Receiver                             | 70 |

| 7.4.3. Loopback Paths                                            | 70 |

| 7.4.4. Receive Deserialization                                   | 70 |

| 7.4.5. CRC Checker                                               | 71 |

| 7.4.6. Address Recognition Logic                                 | 71 |

| 7.4.7. Received Byte Counter and Early Receive Warning Interrupt | 71 |

| 7.4.7.1. Early Receive Failure Detection                         | 72 |

| 7.4.8. Receive Protocol FSM                                      | 72 |

| 7.4.9. Reception Process                                         | 72 |

| 7.4.9.1. Start of Frame                                          | 73 |

| 7.4.9.2. End of Frame                                            | 73 |

| 7.4.10. Receiver Blinding                                        | 73 |

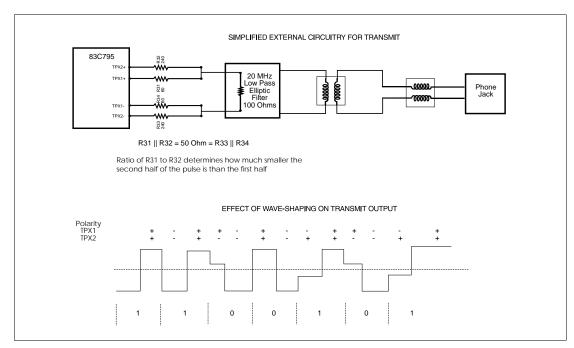

| 7.5. TRANSMITTER NETWORK INTERFACE (MAC-TO-PHY)                  | 74 |

| 7.5.1. Oscillator                                                | 74 |

| 7.5.2. Manchester Encoder                                        | 74 |

| 7.5.3. AUI Differential Driver                                   | 74 |

| 7.5.4. Collision Translator                                      | 74 |

| 7.5.5. Twisted-Pair Differential Driver                          | 74 |

| 7.5.6. Link Integrity Test Function                              | 75 |

| 7.5.7. Jabber Protection                                         | 75 |

| 7.5.8. SQE Test (Heartbeat Test)                                 | 75 |

| 7.5.9. Status Indications                                        | 75 |

| 7.6. TRANSMITTER SECTION                                         | 76 |

| 7.6.1 Rasic Function                                             | 76 |

| 7.6.2. Preamble Generator                           | 76 |

|-----------------------------------------------------|----|

| 7.6.3. Transmit Serializer                          | 76 |

| 7.6.4. CRC Generator                                | 76 |

| 7.6.5. Transmit Protocol FSM                        | 76 |

| 7.6.5.1. Interframe Gap and Deference               | 76 |

| 7.6.5.2. Collision Handling Logic                   | 76 |

| 7.6.6. Timers                                       | 77 |

| 7.6.6.1. Slot Timer                                 | 77 |

| 7.6.6.2. Backoff Timer                              | 77 |

| 7.6.6.3. Collision Counter                          | 77 |

| 7.6.6.4. Heartbeat Detection                        | 77 |

| 7.6.7. Transmitter Operation                        | 77 |

| 7.6.7.1. Transmission Initialization                | 77 |

| 7.6.7.2. Transmission Process                       | 77 |

| 7.6.7.3. Transmit Underrun.                         | 78 |

| 7.6.7.4. Early Transmit Underrun Protection         | 78 |

| 7.6.7.5. Collisions                                 |    |

| 7.6.7.6. Extensions Beyond 802.3 10Base5 Protocol   | 79 |

| 7.6.7.7 Extended Length                             | 79 |

| 8.0. BUFFER STRUCTURING AND DATA MOVEMENT PROCESSES | 80 |

| 8.1. TRANSMIT PACKETS                               | 80 |

| 8.1.1. Single Packet Transmission                   | 80 |

| 8.1.2. Multiple Packet Transmissions                |    |

| 8.1.2.1. Ownership of Buffers                       |    |

| 8.1.2.2. Modifying the Transmit Queue               |    |

| 8.2. RECEIVE PACKET BUFFERING                       |    |

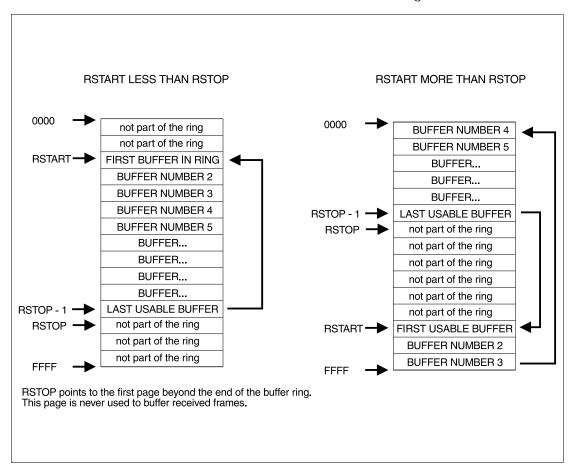

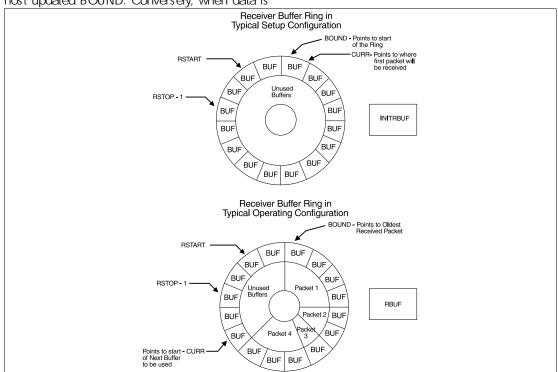

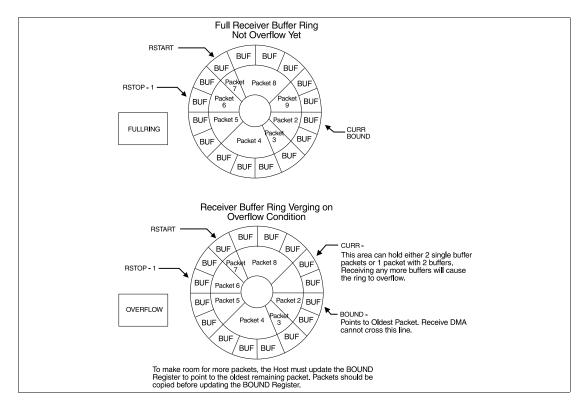

| 8.2.1. Ring of Buffers                              | 83 |

| 8.2.1.1. Automatic Ring Wrapping                    |    |

| 8.2.1.2. Ring-Empty Bit                             | 87 |

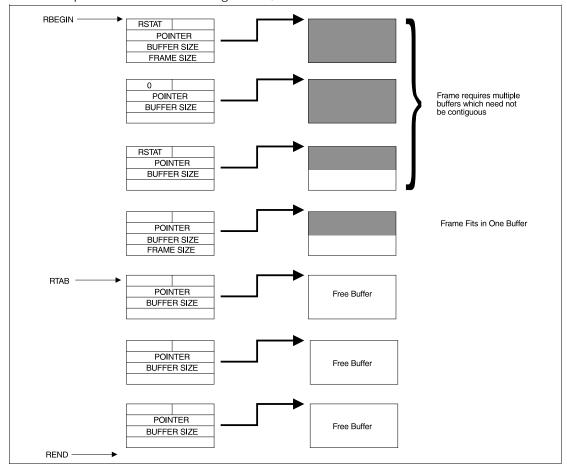

| 8.2.2. Linked-List Receiver Buffering               |    |

| 9.0. ELECTRICAL SPECIFICATIONS                      |    |

| 9.1. ABSOLUTE MAXIMUM RATINGS                       | 90 |

| 9.2. RECOMMENDED OPERATING CONDITIONS               | 90 |

| 9.3. DC OPERATING CHARACTERISTICS                   | 90 |

| 9.3.1. Input Pins                                   | 90 |

| 9.3.2. Output Pins.                                 |    |

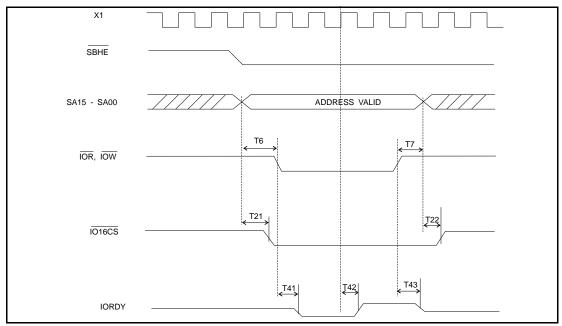

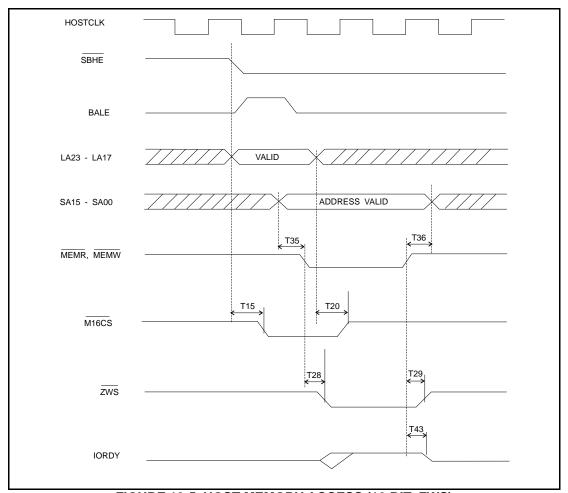

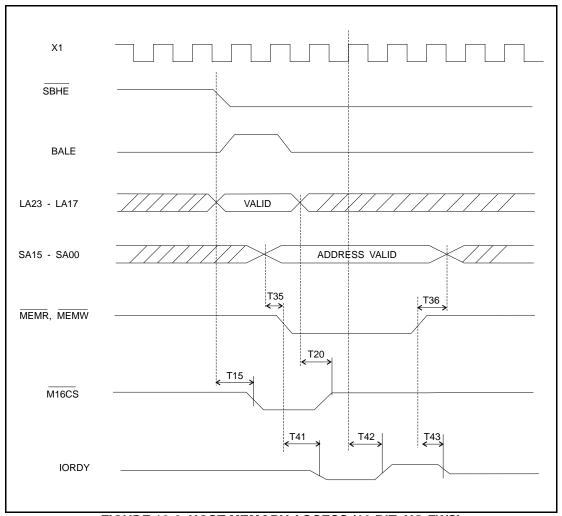

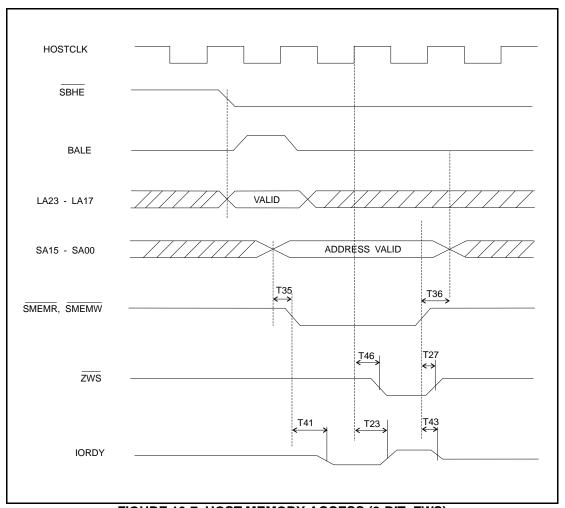

| 10.0. AC OPERATING CHARACTERISTICS AND TIMING       |    |

| 11.0. PACKAGE DIMENSIONS                            |    |

| INDEX                                               |    |

#### **LIST OF FIGURES**

| FIGURE 1-1. 83C795 BLOCK DIAGRAM                      |     |

|-------------------------------------------------------|-----|

| FIGURE 3-1. 83C790 DATA PATH FLOW                     | 4   |

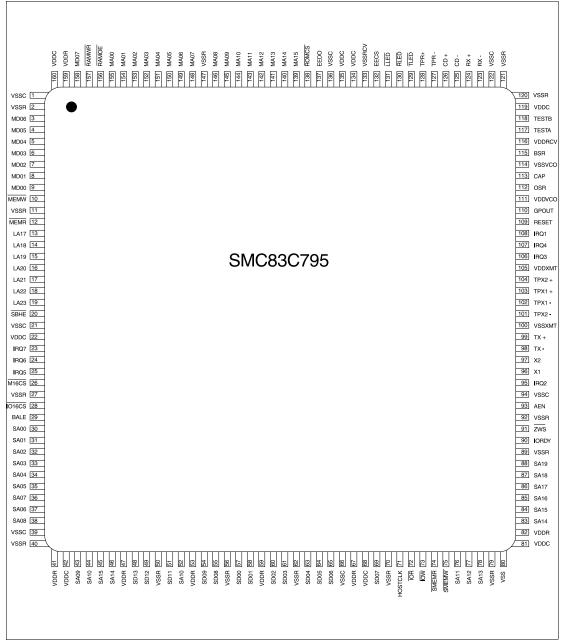

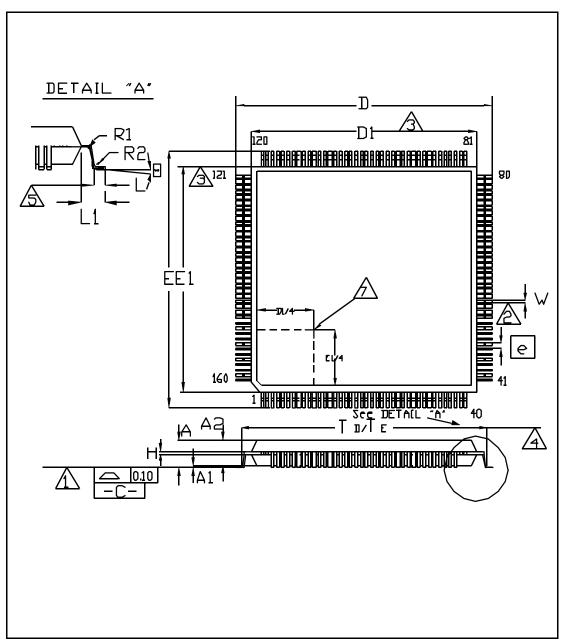

| FIGURE 4-1. 83C790 PIN OUT DIAGRAM (160 PINS)         | 5   |

| FIGURE 6-1. MEMORY CACHE ARRANGEMENT                  | 45  |

| FIGURE 6-2. OVERLAPPING ADDRESS STRUCTURE             | 47  |

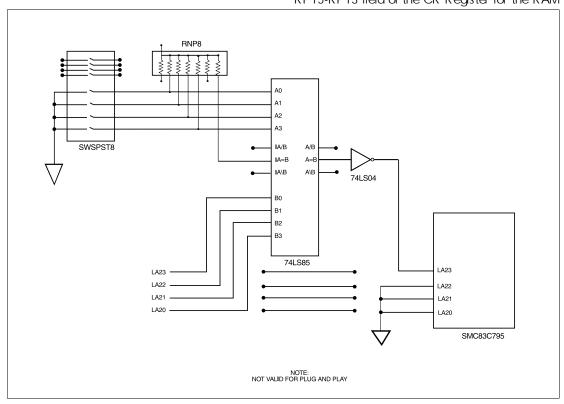

| FIGURE 6-3. EXTERNAL CASCADED ADDRESS DECODER         | 48  |

| FIGURE 6-4. ADDRESS GENERATION PATH                   | 49  |

| FIGURE 6-5. INTERRUPT CONTROL LOGIC                   | 52  |

| FIGURE 6-6. EEROM REGISTER LOGIC                      | 55  |

| FIGURE 6-7. PLUG AND PLAY STATE MACHINE               | 58  |

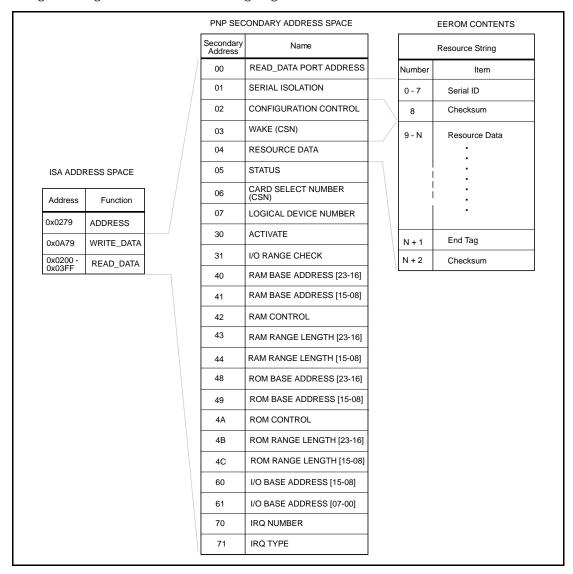

| FIGURE 6-8. PLUG AND PLAY CONFIGURATION REGISTERS     | 60  |

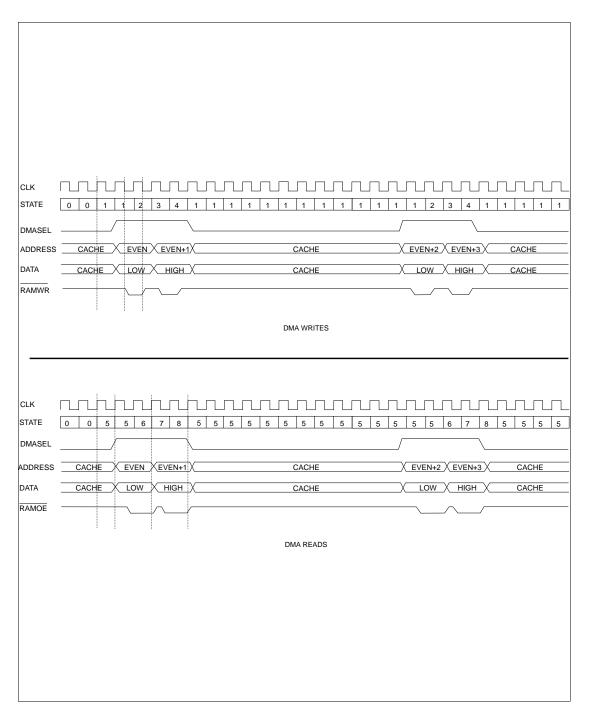

| FIGURE 7-1. BASIC DMA CYCLES                          |     |

| FIGURE 7-2. AUI/TWISTED-PAIR INTERFACE                |     |

| FIGURE 7-3. SIMPLIFIED TRANSMIT CIRCUITRY             | 75  |

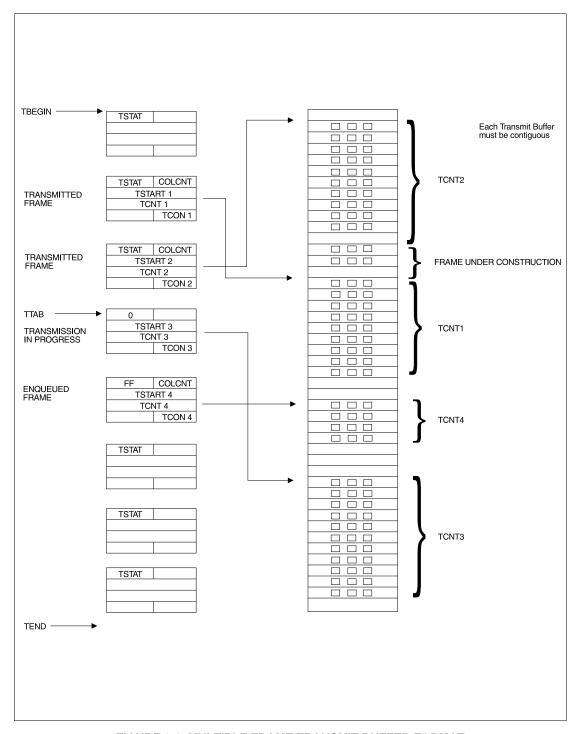

| FIGURE 8-1. MULTIPLE FRAME TRANSMIT BUFFER FORMAT     | 81  |

| FIGURE 8-2. RECEIVER BUFFER FORMAT                    | 84  |

| FIGURE 8-3. RING BUFFER STRUCTURE                     | 85  |

| FIGURE 8-4. RECEIVER BUFFER RING 1                    |     |

| FIGURE 8-5. RECEIVER BUFFER RING 2                    |     |

| FIGURE 8-6. LINKED-LIST BUFFER FORMAT                 |     |

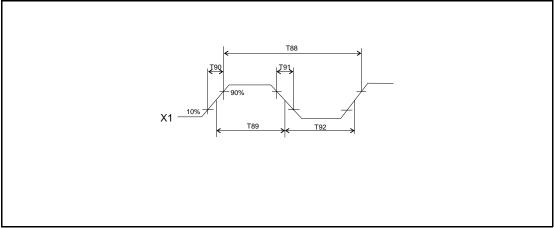

| FIGURE 10-1. SYSTEM CLOCK TIMING                      |     |

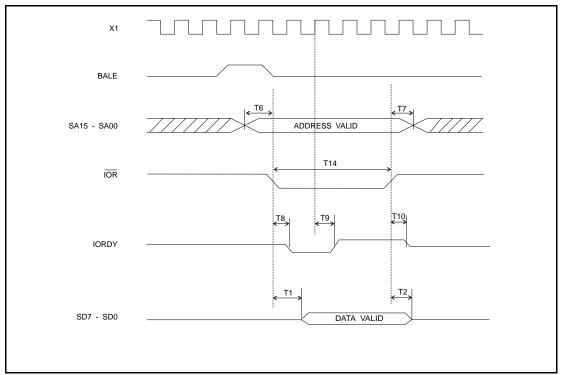

| FIGURE 10-2. REGISTER ACCESS TIMING - READ            |     |

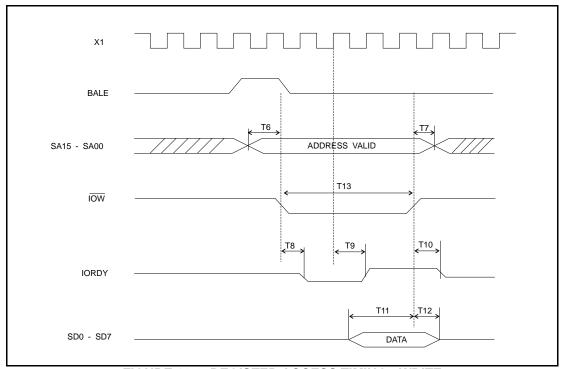

| FIGURE 10-3. REGISTER ACCESS TIMING - WRITE           | 98  |

| FIGURE 10-4. 16-BIT REGISTER ACCESS (I/O PIPE ONLY)   |     |

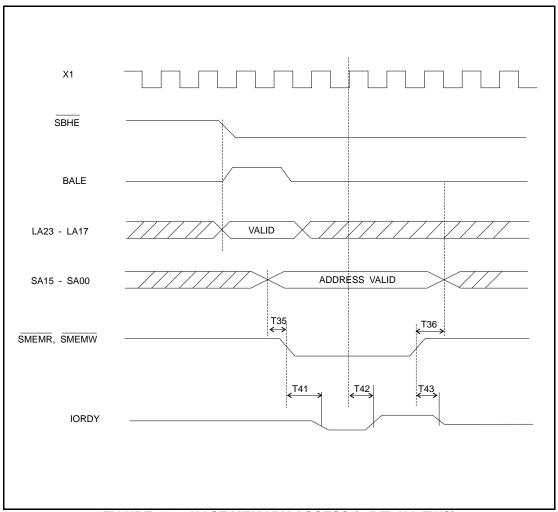

| FIGURE 10-5. HOST MEMORY ACCESS (16-BIT, ZWS)         |     |

| FIGURE 10-6. HOST MEMORY ACCESS (16-BIT, NO ZWS)      |     |

| FIGURE 10-7. HOST MEMORY ACCESS (8-BIT, ZWS)          |     |

| FIGURE 10-8. HOST MEMORY ACCESS (8-BIT, NO ZWS)       |     |

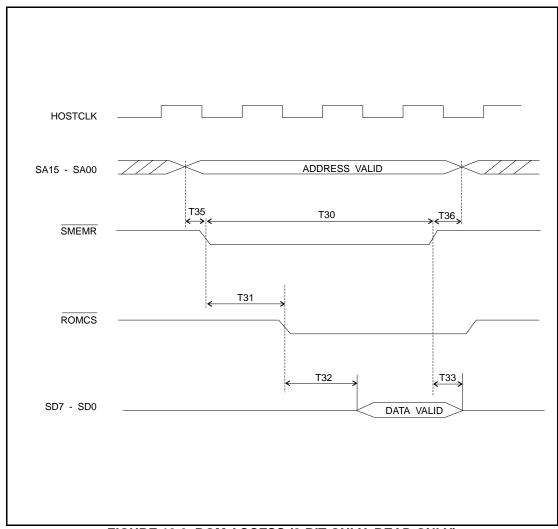

| FIGURE 10-9. ROM ACCESS (8-BIT ONLY, READ ONLY)       |     |

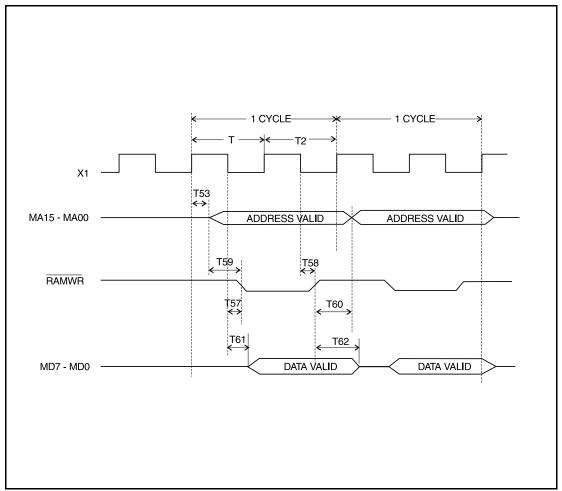

| FIGURE 10-10. DMA OR MEMORY CACHE WRITES              |     |

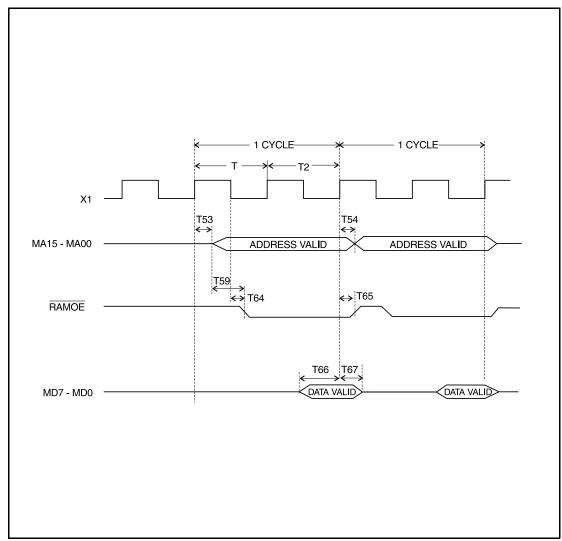

| FIGURE 10-11. DMA OR MEMORY CACHE READS               |     |

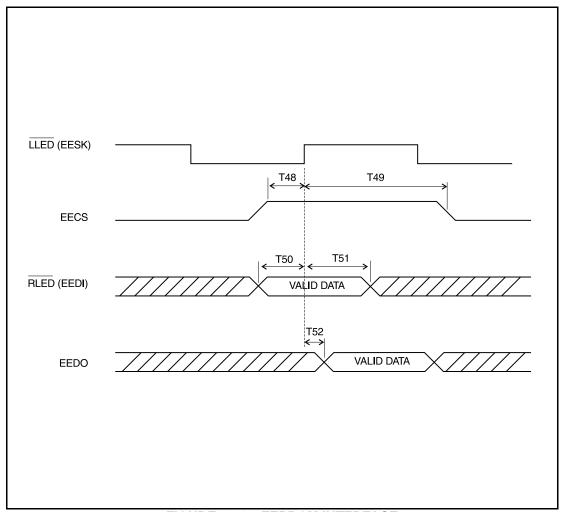

| FIGURE 10-12. EEPROM INTERFACE                        |     |

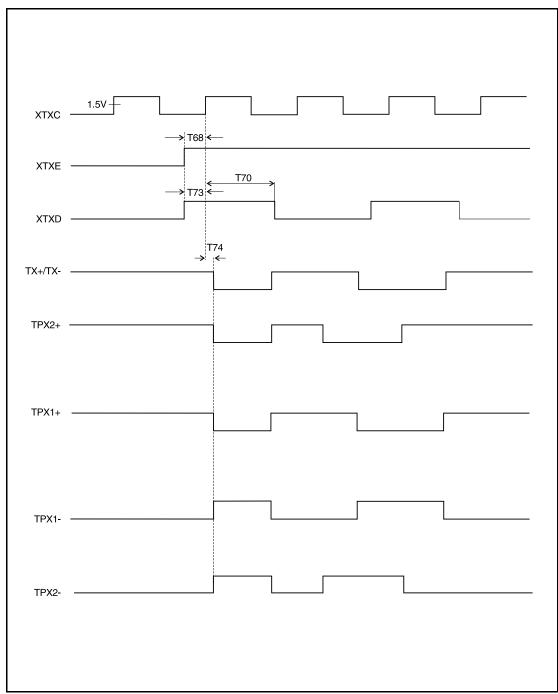

| FIGURE 10-13. TRANSMIT TIMING - START OF TRANSMISSION |     |

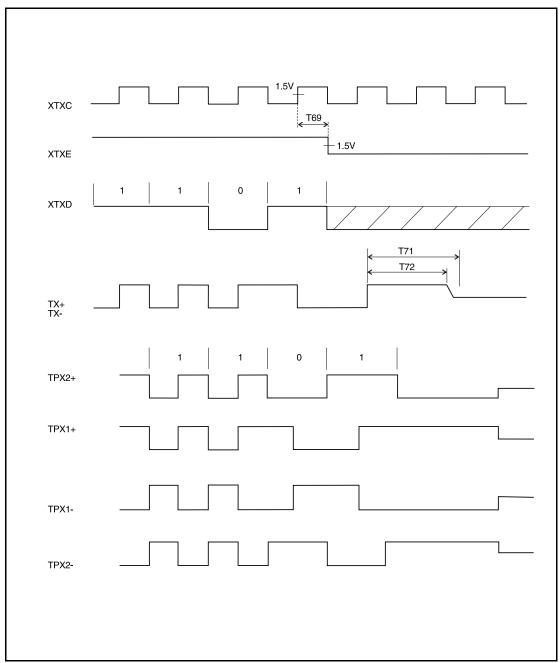

| FIGURE 10-14. TRANSMIT TIMING - END OF TRANSMISSION   |     |

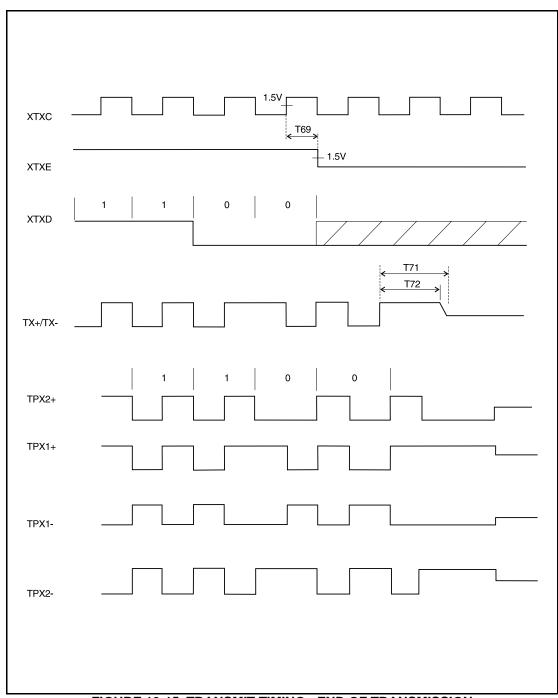

| FIGURE 10-15. TRANSMIT TIMING - END OF TRANSMISSION   |     |

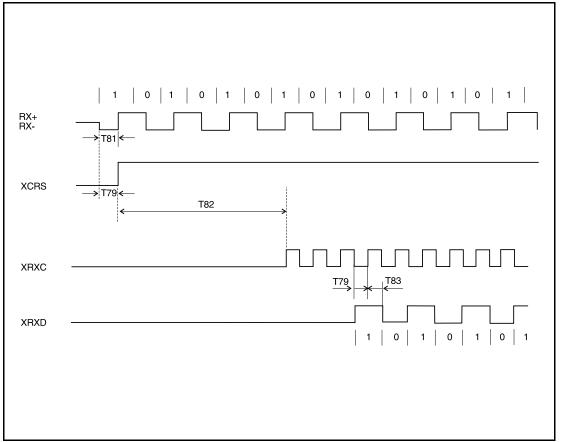

| FIGURE 10-16. RECEIVE TIMING - START OF PACKET        | 110 |

viii SMC

LIST OF FIGURES 83C795

| FIGURE 10-17. RECEIVE TIMING - END OF PACKET | 111 |

|----------------------------------------------|-----|

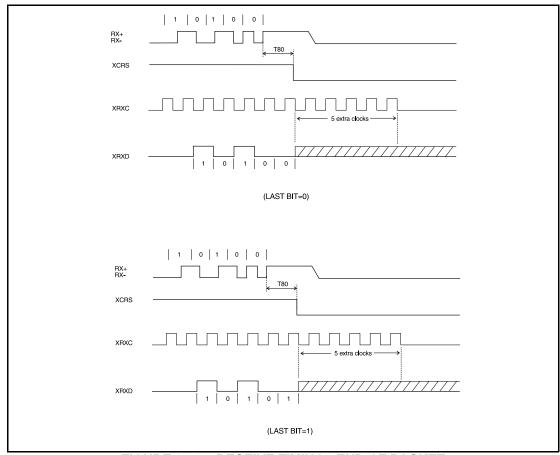

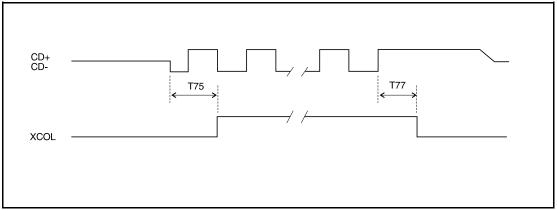

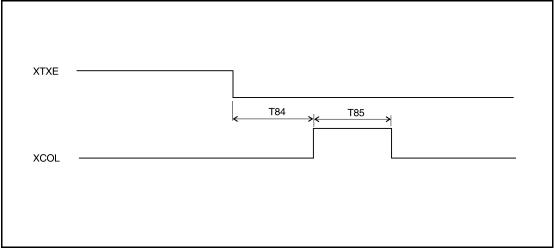

| FIGURE 10-18. COLLISION TIMING - TP          | 112 |

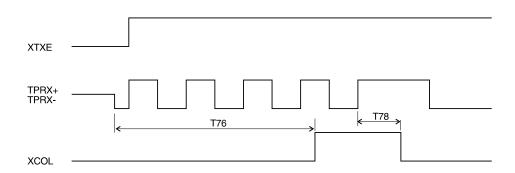

| FIGURE 10-19. COLLISION TIMING - AUI         | 112 |

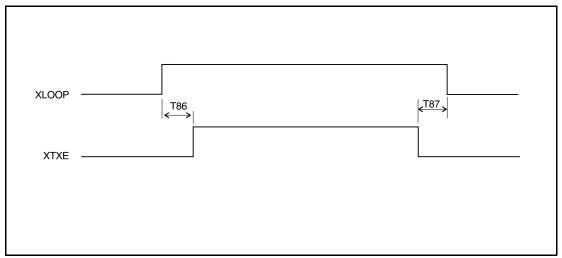

| FIGURE 10-20. LOOPBACK TIMING                | 113 |

| FIGURE 10-21. SQE TEST TIMING                | 113 |

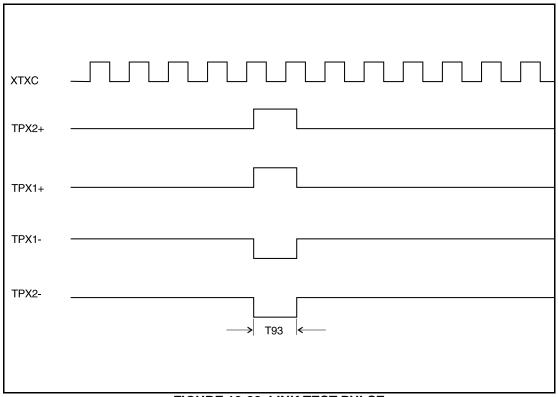

| FIGURE 10-22. LINK TEST PULSE                | 114 |

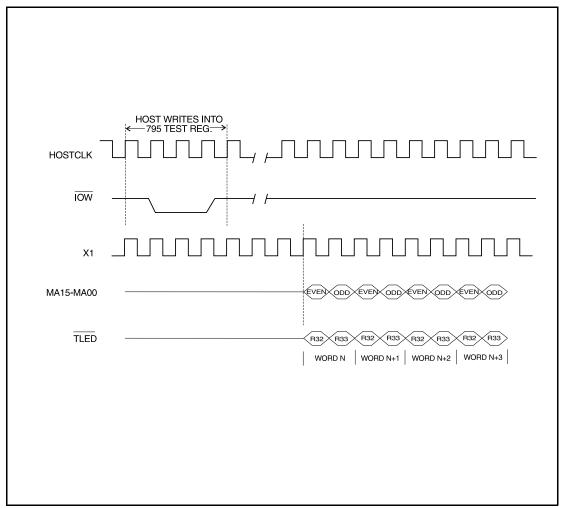

| FIGURE 10-23. ROM DUMP (TEST MODE)           | 115 |

| FIGURE 11-1 160-PIN POED PACKAGE             | 116 |

#### **LIST OF TABLES**

| TABLE 4-1. 83C795 PIN ASSIGNMENTS                      |

|--------------------------------------------------------|

| TABLE 4-2. I/O PIN MAPPING SCHEME                      |

| TABLE 4-3. I/O PIN OUTPUT VALUES                       |

| TABLE 5-1. HOST INTERFACE REGISTERS SUMMARY            |

| TABLE 5-2. LAN CONTROLLER REGISTERS - NORMAL MODE      |

| TABLE 5-3. LAN CONTROLLER REGISTERS - LINKED-LIST MODE |

| TABLE 5-4. REGISTER TERM DEFINITIONS                   |

| TABLE 5-5. BUFFER WINDOW SIZE FIELD                    |

| TABLE 5-6. ROM WINDOW SIZE FIELD                       |

| TABLE 5-7. INTERRUPT REQUEST FIELD                     |

| TABLE 5-8. PAGE SELECT FIELD                           |

| TABLE 5-9. SLOT TIME SELECTION FIELD                   |

| TABLE 5-10. GROUP REGISTER BITS                        |

| TABLE 5-11. STATION ADDRESS REGISTER BITS              |

| TABLE 5-12. LOOPBACK TEST SELECTION                    |

| TABLE 5-13. HOST INTERFACE REGISTER SUMMARY            |

| TABLE 5-14. LAN CONTROLLER REGISTER SUMMARY            |

| TABLE 6-1. HOST INTERFACE ADDRESS DECODERS             |

| TABLE 6-2. JUMPER EXAMPLE         53                   |

| TABLE 6-3. EEROM RECALL OPERATIONS                     |

| TABLE 6-4. CONFIG REGISTER/INIT PINS                   |

| TABLE 6-5. EEROM LOCATION ALLOCATION                   |

| TABLE 6-6. AUTO-CONFIGURATION PORTS                    |

| TABLE 6-7. PLUG AND PLAY BIT REMAPPING                 |

| TABLE 6-8. PLUG AND PLAY RESOURCE STRING STRUCTURE     |

| TABLE 7-1. DMA BURST LENGTH FIELD                      |

| TABLE 8-1. TSTAT FIELD VALUES                          |

| TABLE 8-2. FORMAT OF TRANSMIT DESCRIPTOR TABLE         |

| TABLE 8-3. MEANING OF DESCRIPTOR TABLE                 |

| TABLE 9-1. INPUT PIN VALUES                            |

| TABLE 9-2. OUTPUT PIN VALUES                           |

| TABLE 10-1. LIST OF TIMING DIAGRAMS                    |

| TABLE 10-2. TIMING PARAMETERS                          |

| TABLE 10-3. TEST PIN I/O MATCHING                      |

| TABLE 11-1 PACKAGE DIMENSIONS 117                      |

GENERAL DESCRIPTION 83C795

#### 1.0 GENERAL DESCRIPTION

The SMC 83C795 Ethernet System Controller implements the IEEE 802.3 protocol for networks such as Ethernet, Cheapernet, and 10BaseT. It is a highly integrated device that shrinks the essence of a LAN adapter card onto a single piece of silicon. It includes the 802.3 Media Access Control (MAC) functions, the Physical Layer Interface (PLI) for 10BASE-T media, and a host interface designed for simple connection to the Industry Standard Architecture (ISA) PC/AT bus.

To create a LAN adapter only the 83C795, a single buffer RAM, an EEROM chip, and an optional ROM for BIOS or IPL code storage are required. Transformers and supporting analog components complete an adapter design. All necessary control logic is provided by the 83C795.

The resulting LAN adapter appears to the host as a block of I/O registers with a block of shared memory, unless the I/O pipe is used. The base address for I/O registers is programmable as is the base address and size of the buffer memory.

This device is similar to the SMC 83C790 LAN controller with three major differences:

- A small memory cache has been added for host accesses to shared memory.

- An I/O pipe mode has been added to access the buffer memory.

- Auto-configurability logic has been added in order to comply with the new ISA Plug and Play specification.

As with the 83C790 chip, there are two basic modes of operation: normal and ALTEGO. In the normal mode, the LAN controller operates much like the 83C690 LAN Controller with received frames being buffered in a ring of contiguous, fixed-size buffers. When the ALTEGO feature is enabled, the device switches to a very different mode of operation. The differences are summarized here and explained in detail throughout the specification:

- Linked-list style of buffering instead of ring buffers.

- Different register map for LAN controller, exposing new registers for the linked-list buffering.

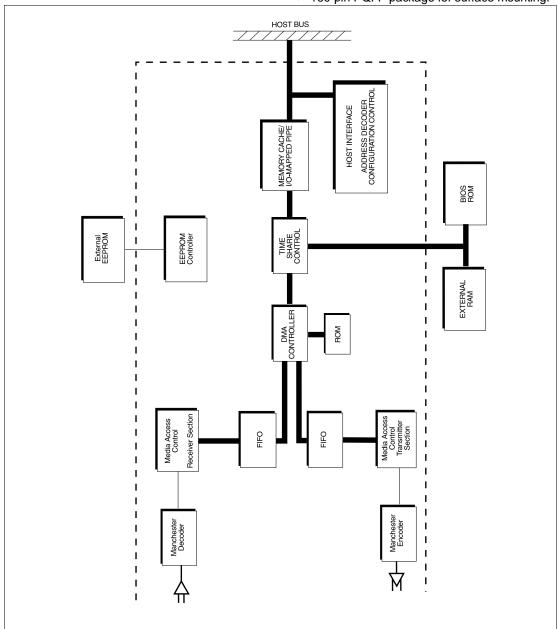

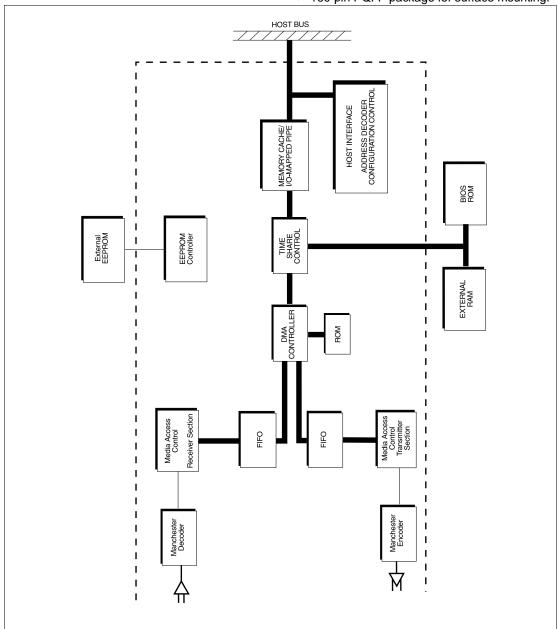

Figure 1-1 depicts the 83C795's functionality.

#### 2.0 FEATURES

The basic features of the 83C795 chip are summarized here:

- Memory caching with time-shared access to buffer RAM.

- Compliant with the ISA Plug And Play specification

- Software compatible with 83C790 drivers

- Direct interface with ISA bus without TTL buffers

- I/O-mapped pipe access to buffer RAM

- Extended length option for the twisted-pair port

- Underrun detection in early receive mode

- · Staggered address transfers supported

- · Ring-empty bit supplied to host

- Automatic ring-wrapping

- PC-98 bus support through addition of a jumper

- Buffered 20 MHz clock output available through addition of a jumper

- Support for diskless workstations via Initial Program Load ROM

- Programmable base address and window size for buffer memory and IPL ROM

- Support for paging of buffer memory and IPL ROM

- Programmable I/O base address

- Programmable bus width of either 8 or 16 bits

- Zero wait state operation

- Automatic loading of host interface configuration and LAN address from external serial EEPROM

- Separate address and data busses to memory with no external address latches

- 7 programmable interrupt levels

- Clock oscillator

- Full 802.3 MAC layer protocol implementation with extended features

- Support for transmission and reception of frames up to 32K bytes long

- Transmit frame start at any location no word alignment required

- Two modes of frame buffering: 83C690 mode and descriptor table mode

- Loopback modes internal and external

- Full-duplex DMA capability in loopback mode

- Built-in AUI serial interface including drivers and receivers

83C795 FEATURES

- Built-in 10BASE-T serial interface for Ethernet on Twisted-Pair including drivers and receivers

- Manchester Encoder/Decoder with clock recovery circuitry

- Multicast addressing using 64-bit hashing algorithm

- I/O pin mapping enables rapid board test development

- 160-pin PQFP package for surface mounting.

FIGURE 1-1. 83C795 BLOCK DIAGRAM

FUNCTIONAL DESCRIPTION 83C795

#### 3.0 FUNCTIONAL DESCRIPTION

The principle sections of the device are the:

- Host interface which mediates host access to internal registers and buffer memory.

- LAN Controller which performs 802.3 MAC layer protocol and does supporting DMA transfers to and from local buffer memory.

- Serial line interface which supplies drivers and receivers for AUI and TP interfaces and port control logic for the 10BASE-T interface. In addition, it provides Manchester encoding and decoding.

#### 3.1 DESCRIPTION OF DATA PATH

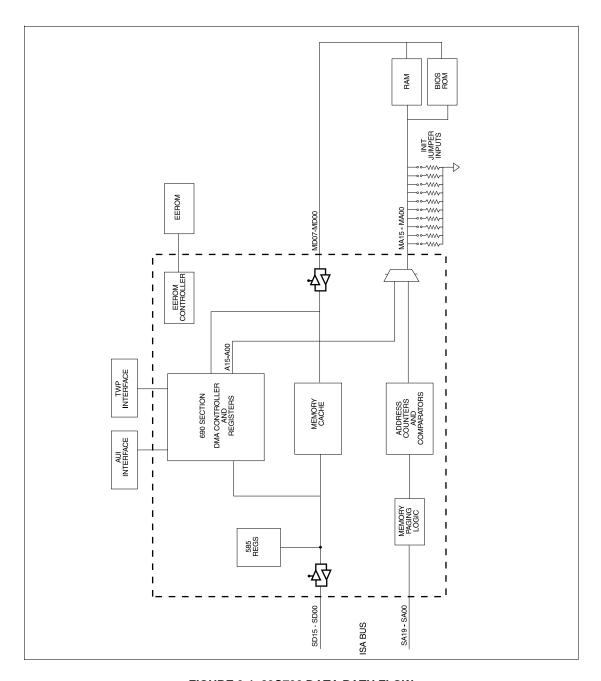

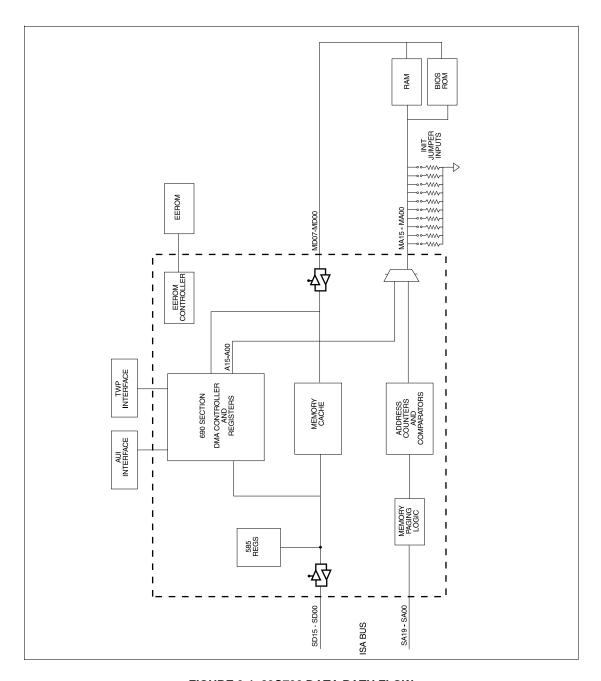

Figure 3-1 illustrates the data path for a 83C795-based board. All internal bytes wapping is handled by the memory cache. The data bus drivers are designed to drive the ISA bus directly.

#### 3.2 CONVENTIONS

A number of conventions are used in this databook.

- A bit may be described as "low" or "logical 0" when its value is set to 0. A bit is described as "high" or "logical 1" when its value is set to 1.

- The location of a bit is frequently described in this manner:

<register>.<bit>

For example, since the bit MENB is located in the CR Register, it might be described in this book as CR.MENB. Or, alternatively, since MENB is the sixth bit in the CR Register, it might also be described in this manner: CR.6

83C795

FIGURE 3-1. 83C790 DATA PATH FLOW

GENERAL DESCRIPTION 83C795

#### 1.0 GENERAL DESCRIPTION

The SMC 83C795 Ethernet System Controller implements the IEEE 802.3 protocol for networks such as Ethernet, Cheapernet, and 10BaseT. It is a highly integrated device that shrinks the essence of a LAN adapter card onto a single piece of silicon. It includes the 802.3 Media Access Control (MAC) functions, the Physical Layer Interface (PLI) for 10BASE-T media, and a host interface designed for simple connection to the Industry Standard Architecture (ISA) PC/AT bus.

To create a LAN adapter only the 83C795, a single buffer RAM, an EEROM chip, and an optional ROM for BIOS or IPL code storage are required. Transformers and supporting analog components complete an adapter design. All necessary control logic is provided by the 83C795.

The resulting LAN adapter appears to the host as a block of I/O registers with a block of shared memory, unless the I/O pipe is used. The base address for I/O registers is programmable as is the base address and size of the buffer memory.

This device is similar to the SMC 83C790 LAN controller with three major differences:

- A small memory cache has been added for host accesses to shared memory.

- An I/O pipe mode has been added to access the buffer memory.

- Auto-configurability logic has been added in order to comply with the new ISA Plug and Play specification.

As with the 83C790 chip, there are two basic modes of operation: normal and ALTEGO. In the normal mode, the LAN controller operates much like the 83C690 LAN Controller with received frames being buffered in a ring of contiguous, fixed-size buffers. When the ALTEGO feature is enabled, the device switches to a very different mode of operation. The differences are summarized here and explained in detail throughout the specification:

- Linked-list style of buffering instead of ring buffers.

- Different register map for LAN controller, exposing new registers for the linked-list buffering.

Figure 1-1 depicts the 83C795's functionality.

#### 2.0 FEATURES

The basic features of the 83C795 chip are summarized here:

- Memory caching with time-shared access to buffer RAM.

- Compliant with the ISA Plug And Play specification

- Software compatible with 83C790 drivers

- Direct interface with ISA bus without TTL buffers

- I/O-mapped pipe access to buffer RAM

- Extended length option for the twisted-pair port

- Underrun detection in early receive mode

- · Staggered address transfers supported

- · Ring-empty bit supplied to host

- Automatic ring-wrapping

- PC-98 bus support through addition of a jumper

- Buffered 20 MHz clock output available through addition of a jumper

- Support for diskless workstations via Initial Program Load ROM

- Programmable base address and window size for buffer memory and IPL ROM

- Support for paging of buffer memory and IPL ROM

- Programmable I/O base address

- Programmable bus width of either 8 or 16 bits

- Zero wait state operation

- Automatic loading of host interface configuration and LAN address from external serial EEPROM

- Separate address and data busses to memory with no external address latches

- 7 programmable interrupt levels

- Clock oscillator

- Full 802.3 MAC layer protocol implementation with extended features

- Support for transmission and reception of frames up to 32K bytes long

- Transmit frame start at any location no word alignment required

- Two modes of frame buffering: 83C690 mode and descriptor table mode

- Loopback modes internal and external

- Full-duplex DMA capability in loopback mode

- Built-in AUI serial interface including drivers and receivers

83C795 FEATURES

- Built-in 10BASE-T serial interface for Ethernet on Twisted-Pair including drivers and receivers

- Manchester Encoder/Decoder with clock recovery circuitry

- Multicast addressing using 64-bit hashing algorithm

- I/O pin mapping enables rapid board test development

- 160-pin PQFP package for surface mounting.

FIGURE 1-1. 83C795 BLOCK DIAGRAM

FUNCTIONAL DESCRIPTION 83C795

#### 3.0 FUNCTIONAL DESCRIPTION

The principle sections of the device are the:

- Host interface which mediates host access to internal registers and buffer memory.

- LAN Controller which performs 802.3 MAC layer protocol and does supporting DMA transfers to and from local buffer memory.

- Serial line interface which supplies drivers and receivers for AUI and TP interfaces and port control logic for the 10BASE-T interface. In addition, it provides Manchester encoding and decoding.

#### 3.1 DESCRIPTION OF DATA PATH

Figure 3-1 illustrates the data path for a 83C795-based board. All internal bytes wapping is handled by the memory cache. The data bus drivers are designed to drive the ISA bus directly.

#### 3.2 CONVENTIONS

A number of conventions are used in this databook.

- A bit may be described as "low" or "logical 0" when its value is set to 0. A bit is described as "high" or "logical 1" when its value is set to 1.

- The location of a bit is frequently described in this manner:

<register>.<bit>

For example, since the bit MENB is located in the CR Register, it might be described in this book as CR.MENB. Or, alternatively, since MENB is the sixth bit in the CR Register, it might also be described in this manner: CR.6

83C795

FIGURE 3-1. 83C790 DATA PATH FLOW

#### 4.0 PIN LIST

This section provides the pin list and pin/signal descriptions for the 83C795. Section 4.1 describes the input-to-output pin mapping feature.

FIGURE 4-1. 83C790 PIN OUT DIAGRAM (160 PINS)

| Mnemonic   | Pin Number | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AEN        | 93         | I   | PC ADDRESS ENABLE. Active low. When Addr <u>ess</u> E <u>nable is active the 83C795 responds</u> to any host strobe (IOR, IOW, MEMR, MEMW, SMEMR, SMEMW).                                                                                                                                                                                                                                         |

| BALE       | 29         | I   | PC ADDRESS LAT CH ENABLE. Used to latch valid addresses from the LA bus. Passes LA signals through internal latches while high and latches them on falling edge.                                                                                                                                                                                                                                  |

| BSR        | 115        | I   | BIAS RESISTOR. A resistor from BSR to VDD sets the internal bias levels. Nominal value is $10 \mathrm{K}\Omega$                                                                                                                                                                                                                                                                                   |

| CAP        | 113        | I   | PLL FILTER CAP. A capacitor (nominal value .01µF) from CAP to ground is used as part of the filter for the internal phase lock loop.                                                                                                                                                                                                                                                              |

| CD+<br>CD- | 126<br>125 | I   | AUT COLLISTON. CD+/CD- are used by the external transceiver to signal a collision by sending a 10MHz signal.                                                                                                                                                                                                                                                                                      |

| EECS       | 132        | 0   | EEROM Chip Select. An external 9356 serial EEROM is used to store up to 2048 bits of configuration data. These signals (along with LLED and RLED) interface with that chip.                                                                                                                                                                                                                       |

| EEDO       | 137        | I/O | EEROM DATA OUTPUT.                                                                                                                                                                                                                                                                                                                                                                                |

| GPOUT      | 110        | 0   | GENERAL PURPOSE OUTPUT. In some systems, this bit is wired to a shutdown control input of the DC/DC is olated power supply used in 10B as e2 applications. In other systems, this supplies a control signal for switching power supplies. (The DC signal's polarity on the 83C795 is the opposite of the 83C790.)                                                                                 |

| HOSTCLK    | 71         | I/O | Personal Computer BUS CLOCK.                                                                                                                                                                                                                                                                                                                                                                      |

| IO16CS     | 28         | 0   | 16 BIT I/O SELECTED. Active low. Indicates to the PC/AT bus that the I/O response will be 16 bits wide. Only used for the I/O pipe.                                                                                                                                                                                                                                                               |

| ĪOR        | 72         | I/O | PCI/OREAD. Active low. Reads an I/O register onto the PC data bus.                                                                                                                                                                                                                                                                                                                                |

| IORDY      | 90         | 0   | I/O IOR DY. Response to host access which can be used directly as 'I/O Channel Ready' when responding to a personal computer bus. It is pulled low (not ready) to lengthen I/O or memory cycles. When the 83C795 is ready to respond, the signal is driven high until the host access is completed, then becomes tristated. This signal is driven by a tri-state buffer capable of sinking 24 mA. |

| ĪOW        | 73         | I/O | PCI/OWRITE. Active low. Writes an I/O register from the PC data bus.                                                                                                                                                                                                                                                                                                                              |

| IRQ1       | 108        | I/O | PCINTERRUPT REQUEST LINES. Active high. Tristated when not active. IRQ2-9 on the PC/AT bus. IRQ1 is the same as the XTXD pin in some test modes.                                                                                                                                                                                                                                                  |

| IRO2       | 95         | I/O | IRQ3 on PC/AT bus. Same as XLOOP in some test modes.                                                                                                                                                                                                                                                                                                                                              |

| IRQ3       | 106        | I/O | IRQ5 on PC/AT bus. Same as XCRS in some test modes.                                                                                                                                                                                                                                                                                                                                               |

| IRQ4       | 107        | I/O | IRQ7 on PC/AT bus. Same as XRXC in some test modes.                                                                                                                                                                                                                                                                                                                                               |

| IRQ5       | 25         | I/O | IRQ10 on PC/AT bus. Same as XRXD in some test modes.                                                                                                                                                                                                                                                                                                                                              |

| IRQ6       | 24         | I/O | IRQ11 on PC/AT bus. Same as XCOL in some test modes.                                                                                                                                                                                                                                                                                                                                              |

| IRQ7       | 23         | I/O | IRQ15 on PC/AT bus. Same as XTXC in some test modes.                                                                                                                                                                                                                                                                                                                                              |

**TABLE 4-1. 83C795 PIN ASSIGNMENTS**

| Mnemonic                                                      | Pin Number                      | I/O | Description                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------------------------------------|---------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LA17-LA23                                                     | 13-19                           | I/O | PCLA ADDRESS BUS. Advanced timing version of system address lines A23-A17 from PC/AT bus. These are not assumed to be stable during the entire host cycle and are latched internally by the BALE signal (falling edge). These signals are active high.                                                                                                              |

| TLED                                                          | 131                             | I/O | TWPR LINK STATUS. If valid data or Link Test pulses are received on TPR+/TPR-, LLED is low (link status OK). When no data or Link Test pulses are received, LLED is high. The LLED pin can sink 4mA to drive an external LED. This pin also functions as the EEROM dock pin (formerly EESK) and functions as the shift control pin (formerly SHIFTIN) in scan mode. |

| M16CS                                                         | 26                              | 0   | MEMORY 16 SELECTED. Active low. Indicates to the PC/AT bus that RAM access response is 16 bits wide.                                                                                                                                                                                                                                                                |

| MA15-MA10                                                     | 139-144                         | 0   | MEMORY ADDRESS LINES. These pins bring out the DMA address to memory or feed-through the host address as modified for paging. When dumping ROM contents, these pins present ROM data bits:  MA15 ROM30 then ROM31 MA14 ROM28 then ROM29                                                                                                                             |

|                                                               |                                 |     | MA00 ROM00 then ROM01                                                                                                                                                                                                                                                                                                                                               |

| MA09/JMP9<br>MA08/JMP8<br>MA07/JMP7<br>MA06/JMP6<br>MA05/JMP5 | 145<br>146<br>148<br>149<br>150 | I/O | S ame as other MA lines except that during RESET, the drivers are disabled and the INIT jumpers are read through these pins and latched at the trailing edge of RESET. They are active high and are pulled up weakly by internal resistors $(35 \text{k}\Omega-150 \text{k}\Omega)$ .                                                                               |

| MAO4/JMP4<br>MAO3/JMP3<br>MAO2/JMP2<br>MAO1/JMP1<br>MAOO/JMP0 | 151<br>152<br>153<br>154<br>155 |     | To set a zero value on these pins, use an external pull-down resistor of 3.6K $\Omega$                                                                                                                                                                                                                                                                              |

| MD7<br>MD6-MD0                                                | 158<br>3-9                      | I/O | MEMORY DATA LINES. These pins connect to the data pins of the buffer RAM and the IPL or boot ROM.                                                                                                                                                                                                                                                                   |

| MEMR                                                          | 12                              | I/O | PCMEMORY READ for addresses exceeding 1 M. Active low.                                                                                                                                                                                                                                                                                                              |

| MEMW                                                          | 10                              | I/O | PCMEMORY WRITE for addresses exceeding 1 M. Active low.                                                                                                                                                                                                                                                                                                             |

| OS R                                                          | 112                             | I   | VCO BIAS RESISTOR. A resistor from OSR to VCC biases the internal VCO current. Nominal value is 24.9K $\Omega$ .                                                                                                                                                                                                                                                    |

| RAMOE                                                         | 156                             | 0   | RAMOUTPUT ENABLE. Active low.                                                                                                                                                                                                                                                                                                                                       |

| RAMWR                                                         | 157                             | 0   | RAM WRITE ENABLE. Active low.                                                                                                                                                                                                                                                                                                                                       |

| RESET                                                         | 95                              | I/O | SYSTEM RESET. Active high.                                                                                                                                                                                                                                                                                                                                          |

TABLE 4-1. 83C795 PIN ASSIGNMENTS (CONT.)

| Mnemonic                                                                                                | Pin Number                                                                      | I/O | Description                                                                                                                                                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RLED                                                                                                    | 130                                                                             | I/O | RECVLED DRIVER. When on, RLED drives low to turn on an external LED. If no data is received, RLED is off. If data is received, RLED goes active for approximately 50ms longer than the received packet length. This pin also serves as the EEROM data in pin (EEDI) and is used as the scan data input (formerly S CANIN) in scan mode. |

| ROMCS                                                                                                   | 138                                                                             | 0   | BIOS ROMOUTPUT ENABLE. Active low. Chip Select for ROM BIOS. Used for XTXE in some test modes.                                                                                                                                                                                                                                          |

| RX+<br>RX-                                                                                              | 124<br>123                                                                      | 1   | AUTRECETVE. The Manchester encoded data from the external transceiver is received on RX+/RX                                                                                                                                                                                                                                             |

| S A19 - 14<br>S A13 - 11<br>S A10 - 09<br>S A08 - 06<br>S A05 - 00                                      | 88 - 83<br>78 - 76<br>44 - 43<br>38 - 37<br>35 - 30                             | I/O | PC ADDRESS BUS. Normal timing version of system address lines. These signals are active high.                                                                                                                                                                                                                                           |

| SBHE                                                                                                    | 20                                                                              | 1   | PCBUSHIGHENABLE. Active low. Indicates a transfer of data on the upper byte of the data bus, SD8 through SD15.                                                                                                                                                                                                                          |

| S D15 - 14<br>S D13 - 12<br>S D11 - 10<br>S D09 - 08<br>S D07<br>S D06 - 04<br>S D03 - 02<br>S D01 - 00 | 45 - 46<br>48 - 49<br>51 - 52<br>54 - 55<br>69<br>65 - 63<br>61 - 60<br>58 - 57 | I/O | SYSTEM DATABUS. Data input and output to host and shared memory. These signals are active high.                                                                                                                                                                                                                                         |

| S ME MR                                                                                                 | 74                                                                              | I/O | LOW MEMORY READ STROBE. Reads buffer memory onto the PC data bus. It is active only when the memory address is within the first 1Mb of memory space. Active low.                                                                                                                                                                        |

| S ME MW                                                                                                 | 75                                                                              | I/O | LOW MEMORY WRITE STROBE. Writes buffer memory from the PC data bus. SMEMW is active only when the memory address is within the first 1Mb of memory space. Active low.                                                                                                                                                                   |

| TESTA<br>TESTB                                                                                          | 117<br>118                                                                      | I   | I/O-MAPPING CONTROL PINS. All signal pins on the 83C795 (except for the analog pins) have been divided into two groups, GROUPA and GROUPB. The functionality of these pins is controlled by the two test pins, as follows:                                                                                                              |

|                                                                                                         |                                                                                 |     | TESTA         TESTB         GROUPA         GROUPB           1         1         NORMAL         NORMAL           1         0         1         0           0         1         0         1           0         0         TRISTATE         TRISTATE                                                                                       |

TABLE 4-1. 83C795 PIN ASSIGNMENTS (CONT.)

| Mnemonic          | Pin Number                                                                                               | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------|----------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TLED              | 129                                                                                                      | 0   | TRANSMIT LED DRIVER. When on, TLED drives low to turn on an external LED. When there is no transmission (TXE inactive), TLED is off. When data is transmitted, TLED goes active for approximately 50ms longer than the transmitted packet length. TLED does not go active for Link Test pulses. This pin also serves as the scan data output (formerly SCANOUT) in scan mode, or as a 20 MHz buffered dock output if JUMPER8 is installed. |

| TPR+<br>TPR-      | 128<br>127                                                                                               | I   | TWPR RECEIVE. In 10BaseT operation, Manchester encoded-<br>data are received via TPR+/TPR They are connected to the<br>twisted pair medium through a transformer and filter.                                                                                                                                                                                                                                                               |

| TPX1+<br>TPX1-    | 103<br>102                                                                                               | 0   | TWPR TRANSMIT. TPX1+ and TPX1- are used for 10B as eT only. They are the high current positive and negative output pins.                                                                                                                                                                                                                                                                                                                   |

| TPX2+<br>TPX2-    | 104<br>101                                                                                               | 0   | TWPR TRANSMIT. TPX2+ and TPX2- are used for 10B as eT only.<br>They are the low current positive and negative output pins.                                                                                                                                                                                                                                                                                                                 |

| TX+<br>TX-        | 99<br>98                                                                                                 | 0   | AUTTRANS MIT. TX+ and TX- transmit differential, Manches ter encoded data to the trans ceiver. These are current-driving outputs that furnish ECL level signals when connected to required external pullup resistors of $150\Omega$                                                                                                                                                                                                        |

| VDD<br>(14 pins)  | 22, 41, 42,<br>47, 53, 59,<br>67, 68, 81,<br>82, 105,<br>111, 116,<br>119, 120,<br>134, 135,<br>159, 160 |     | +5 VOLT SOURCES. Some are for logic, some power the pin drivers, and others provide power to the analog portions of the drauit.                                                                                                                                                                                                                                                                                                            |

| VS S<br>(24 pins) | 1, 2, 11, 21, 27, 39, 40, 50, 56, 62, 66, 70, 79, 80, 89, 92, 94, 100, 114, 121, 122, 133, 136, 147      |     | GROUND. Some are for logic, some power the pin drivers, and others provide power to the analog portions of the drouit.                                                                                                                                                                                                                                                                                                                     |

| X1<br>X2          | 96<br>97                                                                                                 | 0   | CRYSTAL OS CILLATOR. The crystal is attached across these two pins. Must be 20.000 MHz $\pm50$ ppm. This clock operates the chip's logic and is divided by 2 internally to become the transmit clock.                                                                                                                                                                                                                                      |

| ZWS               | 91                                                                                                       | 0   | PCZERO WAIT STATE. Active low. Zero Wait State signal tells the microprocess or that it can complete the <u>present</u> bus cycle without inserting any additional wait cycles. ZWS is driven by a tri-state driver capable of sinking 24 mA.                                                                                                                                                                                              |

TABLE 4-1. 83C795 PIN ASSIGNMENTS (CONT.)

**83C795** PIN LIST

#### 4.1 SPECIAL INPUT-TO-OUTPUT PIN MAPPING

The 83C795 provides a special pin mapping feature which can be used for testing. The pins are divided into two groups, GROUPA and GROUPB, for the new I/O pin mapping scheme.

|     | GROUPA PINS |     | GROUPB PINS |

|-----|-------------|-----|-------------|

| PIN | NAME        | PIN | NAME        |

| 3   | MD06        | 4   | MD05        |

| 5   | MD04        | 6   | MD03        |

| 7   | MD02        | 8   | MD01        |

| 9   | MD00        | 10  | MEMW        |

| 12  | MEMR        | 13  | LA17        |

| 14  | LA18        | 15  | LA19        |

| 16  | LA20        | 17  | LA21        |

| 18  | LA22        | 19  | LA23        |

| 20  | SBHE        | 23  | IRQ7        |

| 24  | IRQ6        | 25  | IRQ15       |

| 26  | M16CS       | 28  | TO16CS      |

| 29  | BALE        | 30  | S A00       |

| 31  | S A01       | 32  | S A02       |

| 33  | S A03       | 34  | S A04       |

| 35  | S A05       | 36  | S A07       |

| 37  | S A06       | 38  | S A08       |

| 43  | S A09       | 44  | S A10       |

| 45  | S D15       | 46  | S D14       |

| 48  | S D13       | 49  | S D12       |

| 51  | S D11       | 52  | S D10       |

| 54  | S D09       | 55  | S D08       |

| 57  | S D00       | 58  | S D01       |

| 60  | S D02       | 61  | S D03       |

| 63  | S D04       | 64  | S D05       |

| 65  | S D06       | 69  | S D07       |

| 71  | BSCK        | 72  | IOR         |

| 73  | ĪOW         | 74  | S ME MR     |

| 75  | S ME MW     | 76  | S A11       |

| 77  | S A12       | 78  | S A13       |

| 83  | S A14       | 84  | S A15       |

| 85  | S A16       | 86  | S A17       |

| 87  | S A18       | 88  | S A19       |

TABLE 4-2. I/O PIN MAPPING SCHEME

|     | GROUPA PINS |     | GROUPB PINS |

|-----|-------------|-----|-------------|

| PIN | NAME        | PIN | NAM,E       |

|     | 100.01/     | 0.4 | 71110       |

| 90  | IOR DY      | 91  | ZWS         |

| 93  | AE N        | 95  | IRO2        |

| 106 | IRQ3        | 107 | IRQ4        |

| 108 | IRQ1        | 109 | RESET       |

| 110 | GPOUT       | 129 | RXM         |

| 130 | RLED        | 131 | LLED        |

| 132 | EECS        | 137 | EEDO        |

| 138 | ROMCS       | 139 | MA15        |

| 140 | MA14        | 141 | MA13        |

| 142 | MA12        | 143 | MA11        |

| 144 | MA10        | 145 | MA09        |

| 146 | MA08        | 148 | MA07        |

| 149 | MA06        | 150 | MA05        |

| 151 | MA04        | 152 | MA03        |

| 153 | MA02        | 154 | MA01        |

| 155 | MA00        | 156 | RAMOE       |

| 157 | RAMWR       | 158 | MD07        |

|     |             |     |             |

TABLE 4-2. I/O PIN MAPPING SCHEME (CONT.)

The I/O pin mapping test for this chip requires only two static vectors. The inputs you must set along with the desired output values are listed in Table 4-3.

| VECTOR | PIN DRIVEN HIGH          | PINS DRIVEN LOW          | PINS OUTPUTTING 1's | PINS OUTPUTTING 0's |

|--------|--------------------------|--------------------------|---------------------|---------------------|

| 1      | TESTA, RXP,<br>TPRP, CDP | TESTB, RXM,<br>TPRM, CDM | GROUPA pins         | GROUPB pins         |

| 2      | TESTB, RXM,<br>TPRM, CDM | TESTA, RXP,<br>TPRP, CDP | GROUPB pins         | GR OUPA pins        |

**TABLE 4-3. I/O PIN OUTPUT VALUES**

#### Note

This arrangement does not test the 83C795's analog outputs.

## 5.0 ETHERNET SYSTEM CONTROLLER REGISTERS

The register structure of the 83C795 is divided into two register groups: the Host Interface registers and the LAN Controller registers. The following sections describe the contents of each of these registers, detail the way they are accessed, and how they are used. Tables 5-1 through 5-3 provide a brief overview of these registers.

Refer to the Register Summary tables at the end of this section for a quick reference guide to all relevant register bit values.

| OFFSET | SWH = 0  | SWH = 1  |

|--------|----------|----------|

| 00     | CR       | CR       |

| 01     | EER      | EER      |

| 02     | IOPL     | IOPL     |

| 03     | IOPH     | IOPH     |

| 04     | HWR      | HWR      |

| 05     | BPR      | BPR      |

| 06     | ICR      | ICR      |

| 07     | REV/IOPA | REV/IOPA |

| 08     | LAN0     | GCR2     |

| 09     | LAN1     | _        |

| 0A     | LAN2     | IAR      |

| 0B     | LAN3     | RAR      |

| 0C     | LAN4     | BIO      |

| 0D     | LAN5     | GCR      |

| 0E     | BDID     | ERFAL    |

| 0F     | CKSM     | ERFAH    |

TABLE 5-1. HOST INTERFACE REGISTERS SUMMARY

| OFFSET | PAGE 0<br>READ | PAGE 0<br>WRITE | PAGE 1<br>READ | PAGE 1<br>WRITE | PAGE 2<br>READ | PAGE 2<br>WRITE | PAGE 3<br>READ | PAGE 3<br>WRITE |

|--------|----------------|-----------------|----------------|-----------------|----------------|-----------------|----------------|-----------------|

| 10     | CMD            | CMD             | CMD            | CMD             | CMD            | CMD             | CMD            | CMD             |

| 11     | INCRL          | RSTART          | STA0           | STA0            | RSTART         | INCRL           | TEST           | TEST            |

| 12     | INCRH          | RSTOP           | STA1           | STA1            | RSTOP          | INCRH           | RTEST          | RTEST           |

| 13     | BOUND          | BOUND           | STA2           | STA2            | TCNTL          | void            | TTEST          | TTEST           |

| 14     | TSTAT          | TSTARTH         | STA3           | STA3            | TSTARTH        | void            | TEST2          | TEST2           |

| 15     | COLCNT         | TCNTL           | STA4           | STA4            | NEXT           | NEXT            | TSTARTL        | TSTARTL         |

| 16     | {0}            | TCNTH           | STA5           | STA5            | TCNTH          | void            | {0}            | void            |

| 17     | INTSTAT        | INTSTAT         | CURR           | CURR            | ENH            | ENH             | _              | _               |

| 18     | ERWCNT         | ERWCNT          | GROUP0         | GROUP0          | RADDL          | RADDL           | _              | _               |

| 19     | RENH           | RENH            | GROUP1         | GROUP1          | RADDH          | RADDH           | _              | _               |

| 1A     | RCNTL          | void            | GROUP2         | GROUP2          | TADDL          | TADDL           | _              | _               |

| 1B     | RCNTH          | void            | GROUP3         | GROUP3          | TADDH          | TADDH           | _              | _               |

| 1C     | RSTAT          | RCON            | GROUP4         | GROUP4          | RCON           | void            | _              | _               |

| 1D     | ALICNT         | TCON            | GROUP5         | GROUP5          | TCON           | void            | _              | void            |

| 1E     | CRCCNT         | DCON            | GROUP6         | GROUP6          | DCON           | void            | _              | void            |

| 1F     | MPCNT          | INTMASK         | GROUP7         | GROUP7          | INTMASK        | void            | MANCH          | MANCH           |

TABLE 5-2. LAN CONTROLLER REGISTERS - NORMAL MODE

| OFFSET | PAGE 0<br>READ | PAGE 0<br>WRITE | PAGE 1<br>READ | PAGE 1<br>WRITE | PAGE 2<br>READ | PAGE 2<br>WRITE | PAGE 3<br>READ | PAGE 3<br>WRITE |

|--------|----------------|-----------------|----------------|-----------------|----------------|-----------------|----------------|-----------------|

| 10     | CMD            | CMD             | CMD            | CMD             | CMD            | CMD             | CMD            | CMD             |

| 11     | _              | RBEGIN          | STA0           | STA0            | RBEGIN         | _               | _              | _               |

| 12     | _              | REND            | STA1           | STA1            | REND           | _               | _              | _               |

| 13     | CURRL          | CURRL           | STA2           | STA2            | TBEGIN         | void            | _              | _               |

| 14     | TSTAT          | TEND            | STA3           | STA3            | TEND           | void            | _              | _               |

| 15     | COLCNT         | TBEGIN          | STA4           | STA4            | _              | void            | TSTARTL        | TSTARTL         |

| 16     | ERWCNT         | ERWCNT          | STA5           | STA5            | _              | void            | {0}            | void            |

| 17     | INTSTAT        | INTSTAT         | CURRH          | CURRH           | ENH            | ENH             | _              | _               |

| 18     | RTABL          | RTABL           | GROUP0         | GROUP0          | RDOWNL         | RDOWNL          | _              | _               |

| 19     | RTABH          | RTABH           | GROUP1         | GROUP1          | RDOWNH         | RDOWNH          | _              | _               |

| 1A     | TTABL          | TTABL           | GROUP2         | GROUP2          | TDOWNL         | TDOWNL          | _              | _               |

| 1B     | TTABH          | TTABH           | GROUP3         | GROUP3          | TDOWNH         | TDOWNH          | _              | _               |

| 1C     | RSTAT          | RCON            | GROUP4         | GROUP4          | RCON           | void            | _              | _               |

| 1D     | ALICNT         | TCON            | GROUP5         | GROUP5          | TCON           | void            | _              | void            |

| 1E     | CRCCNT         | _               | GROUP6         | GROUP6          | DCON           | void            | _              | void            |

| 1F     | MPCNT          | INTMASK         | GROUP7         | GROUP7          | INTMASK        | void            | MANCH          | MANCH           |

TABLE 5-3. LAN CONTROLLER REGISTERS - LINKED-LIST MODE

## 5.1 HOST INTERFACE INTERNAL REGISTERS

The following section describes the contents of the Host Interface Internal registers. This register set consists of 24 registers arranged in three groups of eight. These three groups are the LAN Address registers, the Hardware Configuration registers (which write to andread from the EEROM), and the Hardware Control registers. The Switch Register bit (HWR.SWH) determines whether the LAN Address Registers (SWH = 0) or the Hardware Configuration Registers (SWH = 1) are visible at any one time. (See HWR - Hardware Support Register on page 16 for more information on this bit.) The Hardware Control registers (including the CR, EER, HWR, BPR, ICR, and REV registers) are always visible.

Bits within registers may also have different functions depending on whether they are read from or written to.

Throughout this section, certain terms are used to describe each register and are defined below:

| Definition                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Delilillion                                                                                                                                                                                                                                                                                                              |

| Value During RESET Time                                                                                                                                                                                                                                                                                                  |

| If the INIT3, 2, 1, 0 jumpers = 1001, this value is loaded into the register immediately after RESET TIME. Some of these values are forced by hardware and others are recalled from EEROM. Recall time is on the order of 2 msec. While the initial recall is ongoing, register may have either the RESET or INIT values |

| This value is loaded when a recall is performed other than after a RESET.                                                                                                                                                                                                                                                |

| Possible register values are:                                                                                                                                                                                                                                                                                            |

| 1 = logical 1                                                                                                                                                                                                                                                                                                            |

| 0 = logical 0                                                                                                                                                                                                                                                                                                            |

| PIN = value unknown or                                                                                                                                                                                                                                                                                                   |

| wired to external pin.                                                                                                                                                                                                                                                                                                   |

| EE = value loaded from                                                                                                                                                                                                                                                                                                   |

| EEROM.                                                                                                                                                                                                                                                                                                                   |

| — = not used.                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                          |

**TABLE 5-4. REGISTER TERM DEFINITIONS**

#### 5.1.1 CR - Control Register

ReadWrite Port = 00

This register has control over buffer memory enabling and soft reset of the LAN controller.

| BIT | CR   | RESET |

|-----|------|-------|

| 7   | RNIC | 1     |

| 6   | MENB | 0     |

| 5   | _    | 0     |

| 4   | CR4  | 0     |

| 3   | CR3  | 0     |

| 2   | RP15 | 0     |

| 1   | RP14 | 0     |

| 0   | RP13 | 0     |

Bit 7: RNIC, Reset Network Interface Controller

Set RNIC to 1 then back to 0 to force a hardware reset to the LAN Controller.

Bit 6: MENB, Memory Enable

Set MENB to 1 to enable host access to shared memory.

Bit 4-3: CR4-CR3, Reserved For Increase In RP Field

#### Bit 2-0: RP15-RP13, RAM Offset

A buffer address is created by adding the contents of this field to the difference between the buffer base address and the address supplied by the SA19-SA00 lines. This sum is treated as a movable page offset which is then inserted into the buffer window. This offset values hould only be used when the memory provided is larger than the window selected.

#### 5.1.2 EER - EEROM Register

ReadWrite Port = 01