# **USB Host Charger Identification**

#### **General Description**

The SLG55570A is a USB host charger (dedicated charger) identification circuit. The device supports both the latest USB Battery Charging Specification Revision 1.2 including data contact detection and a set resistor bias for Apple\* compliant devices as well as legacy USB D+/D- short detection using data line pull-up.

#### **Features**

- · Low Supply Current

- · Automatic Current-Limit Switch Control

- · Automatic USB Charger Identification Circuit

- Apple iPad\* @ 2.4 A charging current support

- Chinese Telecom Standard YD/T 1591-2009 specification support

- Samsung Galaxy Tab\*\* charge scheme support

- · Pb-Free / RoHS Compliant / Halogen-Free

- TDFN-8 Package

#### **Target Applications**

- · Power bank

- · Car charger

- · USB universal wall charger

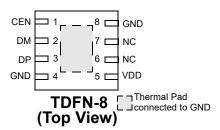

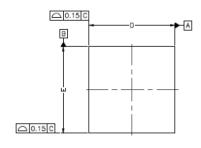

#### Pin Configuration - SLG55570A

- \* Apple iPhone, iPad and iPod are trademarks of Apple Inc., registered in the U.S. and other countries.

- \*\* Samsung Galaxy Tab are trademarks of Samsung Electronics, registered in Korea and other countries.

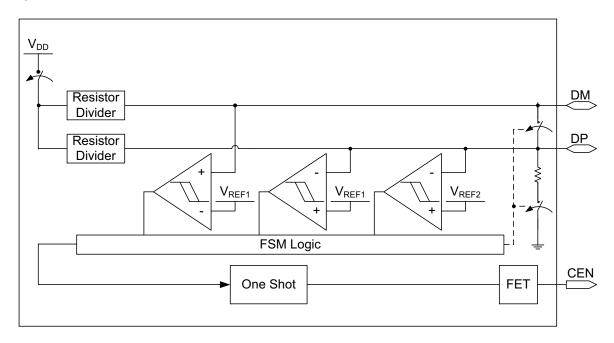

# **Block Diagram**

# Pin Description - SLG55570A

| Pin# | Pin Name    | Туре         | Pin Description                                                                                                                       |

|------|-------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 1    | CEN         | Output       | N-FET Open Drain Output. Current Limit Switch (CLS) Control Output. CEN will be low for 2 seconds (typ). Requires a pull up resistor. |

| 2    | DM          | Input/Output | USB Connector D-                                                                                                                      |

| 3    | DP          | Input/Output | USB Connector D+                                                                                                                      |

| 4    | GND         | GND          | Ground                                                                                                                                |

| 5    | VDD         | PWR          | Power Supply. Connect a $0.1\mu\text{F}$ capacitor between VDD and GND as close as possible to the device.                            |

| 6    | NC          | NC           | No Connect                                                                                                                            |

| 7    | NC          | NC           | No Connect                                                                                                                            |

| 8    | GND         | GND          | Ground                                                                                                                                |

| 9    | Thermal Pad | GND          | Ground (Must connect to Ground)                                                                                                       |

# **Ordering Information**

| Part Number  | Туре                   |

|--------------|------------------------|

| SLG55570AV   | TDFN-8                 |

| SLG55570AVTR | TDFN-8 - Tape and Reel |

000-0055570-101 Page 2 of 8

## **Absolute Maximum Ratings**

| Parameter                            | Min. | Max. | Unit |

|--------------------------------------|------|------|------|

| Supply Voltage                       | -0.3 | 6.0  | V    |

| Continuous Current into any terminal | -30  | +30  | mA   |

| Continuous Power Dissipation         | 954  |      | mW   |

| Operating Temperature Range          | -40  | 85   | °C   |

| Junction Temperature                 |      | 150  | °C   |

| Storage Temperature Range            | -65  | 150  | °C   |

| Lead Temperature (Soldering, 10s)    |      | 260  | °C   |

Note: Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **Electrical Characteristics - Power Supply**

$V_{DD}$  = 4.75 V to 5.25 V,  $T_A$  = 25°C (unless specified otherwise)

| Parameter       | Description                            | Condition/Note | Min. | Тур. | Max. | Unit |

|-----------------|----------------------------------------|----------------|------|------|------|------|

| $V_{DD}$        | Power Supply Range                     |                | 4.75 |      | 5.25 | V    |

| I <sub>DD</sub> | Supply Current<br>V <sub>DD</sub> = 5V |                |      | 140  | 160  | μΑ   |

## **Electrical Characteristics - Dynamic Performance**

$V_{DD}$  = 4.75 V to 5.25 V,  $T_A$  = 25°C (unless specified otherwise)

| Parameter       | Description          | Condition/Note |   |     |     | Unit |

|-----------------|----------------------|----------------|---|-----|-----|------|

| C <sub>ON</sub> | DP/DM On-Capacitance | f = 240MHz     | ' | 4.0 | 5.5 | pF   |

#### **Electrical Characteristics - Internal Resistors**

$V_{DD}$  = 4.75 V to 5.25 V,  $T_A$  = 25°C (unless specified otherwise)

| Parameter        | Description           | Condition/Note | Min.   | Тур.  | Max.   | Unit  |

|------------------|-----------------------|----------------|--------|-------|--------|-------|

| R <sub>PD</sub>  | DP/DM Short Pull-down |                | 350    | 500   | 700    | kΩ    |

| RT <sub>RP</sub> | RP1/RP2 Ratio         |                | 0.8544 | 0.863 | 0.872  | Ratio |

| R <sub>RP</sub>  | RP1 + RP2 Resistance  |                | 69.75  | 93.0  | 115.18 | kΩ    |

| RT <sub>RM</sub> | RM1/RM2 Ratio         |                | 0.8544 | 0.863 | 0.872  | Ratio |

| R <sub>RM</sub>  | RM1 + RM2 Resistance  |                | 69.75  | 93.0  | 115.18 | kΩ    |

000-0055570-101 Page 3 of 8

# **Electrical Characteristics - CEN Output**

$\rm V_{DD}$  = 4.75 V to 5.25 V,  $\rm T_A$  = 25°C (unless specified otherwise)

| Parameter            | Description Condition/Note   |                                                    | Min. | Тур. | Max. | Unit |

|----------------------|------------------------------|----------------------------------------------------|------|------|------|------|

| $T_{VBT}$            | V <sub>BUS</sub> Toggle Time |                                                    | 1.5  | 2.0  | 2.5  | s    |

| V <sub>OL_CEN</sub>  | CEN Output Logic Low Voltage |                                                    |      |      | 0.4  | V    |

| I <sub>OUT_CEN</sub> | CEN Output Leakage Current   | $V_{DD}$ = 5.5V $V_{CEN}$ = 5.5V or CEN deasserted |      |      | 1    | μΑ   |

#### **Electrical Characteristics - ESD Protection**

$V_{DD}$  = 4.75 V to 5.25 V,  $T_A$  = 25°C (unless specified otherwise)

| Parameter        | Description                           | Condition/Note   | Min. | Тур. | Max. | Unit |

|------------------|---------------------------------------|------------------|------|------|------|------|

| V <sub>ESD</sub> | ESD Protection Level (DP and DM Only) | Human Body Model |      | ±8   |      | kV   |

| V <sub>ESD</sub> | ESD Protection Level (All other pins) | Human Body Model |      | ±2   |      | kV   |

000-0055570-101 Page 4 of 8

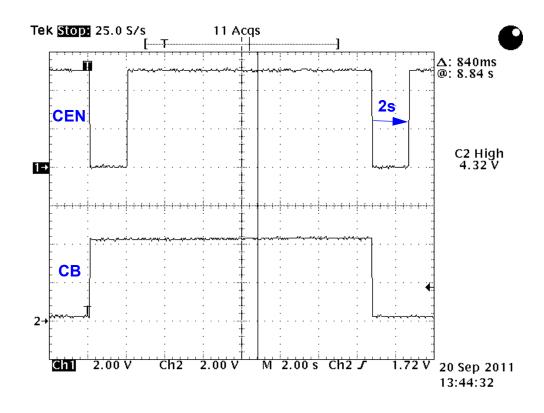

## **CEN Function Waveform**

000-0055570-101 Page 5 of 8

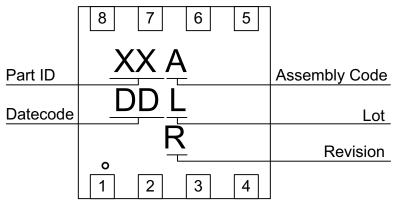

# **Package Top Marking System Definition**

XX - Part ID Field: identifies the specific device configuration A - Assembly Code Field: Assembly Location of the device.

DD - Date Code Field: Coded date of manufacture

L - Lot Code: Designates Lot #

R - Revision Code: Device Revision

000-0055570-101 Page 6 of 8

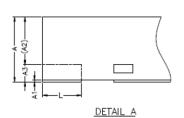

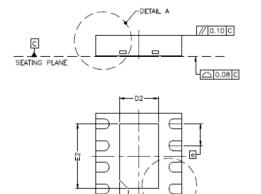

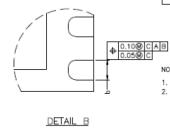

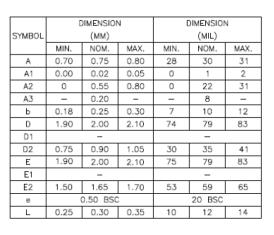

#### **Package Drawing and Dimensions**

#### 8 Lead TDFN Package JEDEC MO-229, Variation WCCD

- REFER TO JEDEC STD: MO-229.

DIMENSION "b" APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.15MM AND 0.30MM FROM THE TERMINAL TIP. IF THE TERMINAL HAS OPTIONAL RADIUS ON THE OTHER END OF THE TERMINAL, THE DIMENSION B SHOULD NOT BE MEASURED IN THAT RADIUS AREA.

000-0055570-101 Page 7 of 8

# **Tape and Reel Specifications**

| Package<br>Type  | # of         | Nominal<br>Package Size<br>[mm] | Max Units |         | Reel &           | Leader (min) |                | Trailer (min) |                | Таре          | Part          |

|------------------|--------------|---------------------------------|-----------|---------|------------------|--------------|----------------|---------------|----------------|---------------|---------------|

|                  | # of<br>Pins |                                 | per Reel  | per Box | Hub Size<br>[mm] | Pockets      | Length<br>[mm] | Pockets       | Length<br>[mm] | Width<br>[mm] | Pitch<br>[mm] |

| TDFN 8L<br>Green | 8            | 2 x 2 x 0.75                    | 3,000     | 3,000   | 178 / 60         | 100          | 400            | 100           | 400            | 8             | 4             |

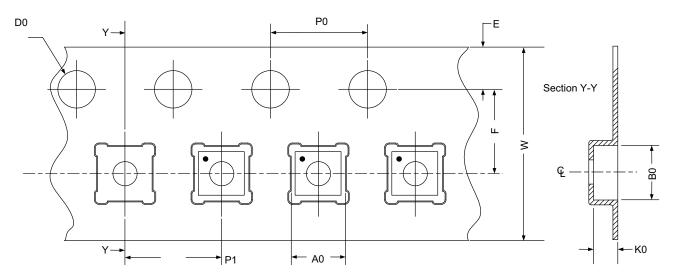

# **Carrier Tape Drawing and Dimensions**

| Package<br>Type  | PocketBTM<br>Length | PocketBTM<br>Width | Pocket<br>Depth | Index Hole<br>Pitch | Pocket<br>Pitch | Index Hole<br>Diameter | Index Hole<br>to Tape<br>Edge |     | Tape Width |

|------------------|---------------------|--------------------|-----------------|---------------------|-----------------|------------------------|-------------------------------|-----|------------|

|                  | A0                  | В0                 | K0              | P0                  | P1              | D0                     | E                             | F   | w          |

| TDFN 8L<br>Green | 2.3                 | 2.3                | 1.05            | 4                   | 4               | 1.55                   | 1.75                          | 3.5 | 8          |

Refer to EIA-481 specification

# **Recommended Reflow Soldering Profile**

Please see IPC/JEDEC J-STD-020: latest revision for reflow profile based on package volume of 3.00 mm<sup>3</sup> (nominal). More information can be found at www.jedec.org.

000-0055570-101 Page 8 of 8

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.