# SH79F1621

# Enhanced 8051 Microcontroller with 10bit ADC

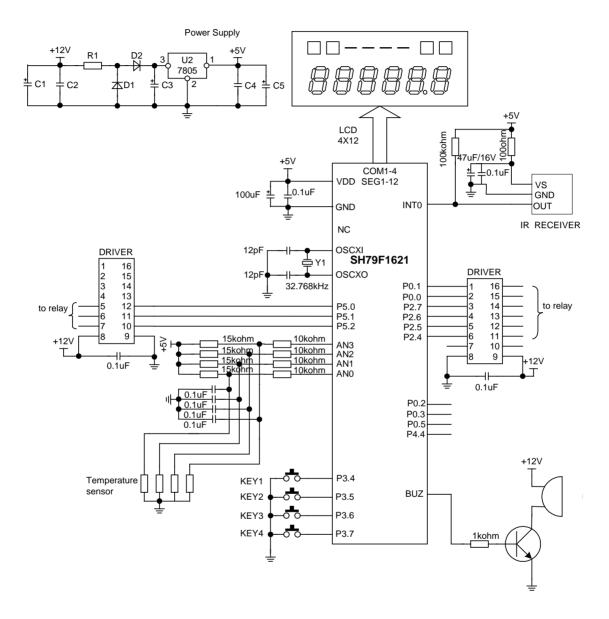

# 1. Features

- 8bits micro-controller with Pipe-line structured 8051 compatible instruction set

- Flash ROM: 16K Bytes

- RAM: internal 256 Bytes, external 256 Bytes, LCD RAM 19Bytes

- EEPROM-like: 1K Bytes

- Operation Voltage:

- $f_{OSC} = 32.768$ kHz 12MHz,  $V_{DD} = 2V 5.5V$

- Oscillator (code option)

- Crystal oscillator: 32.768kHz

- Crystal oscillator: 2MHz 12MHz

- Ceramic oscillator: 2MHz 12MHz

- Internal RC: 12MHz (±2%)/128K

- 41 CMOS bi-directional I/O pins

- Built-in pull-up resistor for input pin

- Four 16-bit timer/counters T2, T3, T4 and T5

SH79F1621 with standard 8051 at same clock speed.

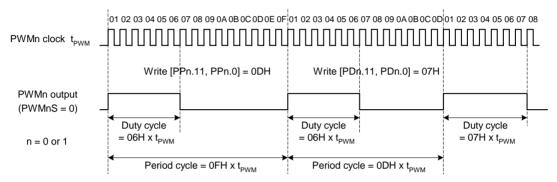

- One 12-bit PWM

- Powerful interrupt sources:

- Timer2, 3, 4, 5

- INT0, 1, 2, 3

- INT40, INT41, INT42, INT43

- ADC, EUART, SCM

- PWM

## 2. General Description

- EUART

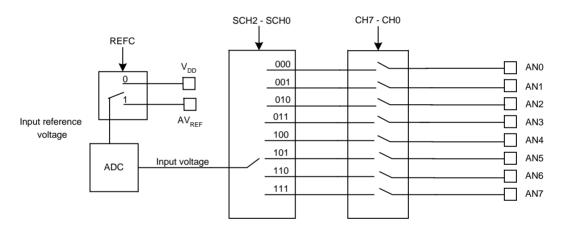

- 8channels 10-bits Analog Digital Converter (ADC), with comparator function built-in

- Buzzer

- LED driver:

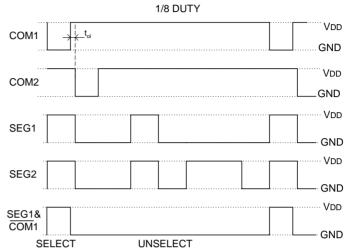

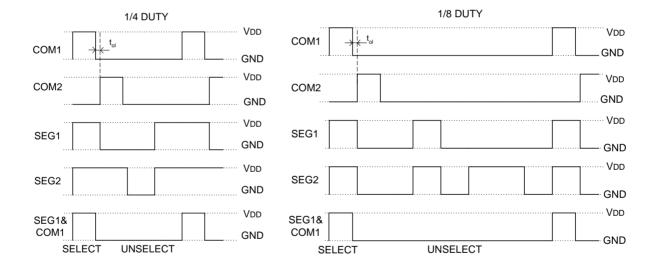

- 8 X 8 dots (1/8 duty)

- 4 X 8 dots (1/4 duty)

- LCD driver:

- 8 X 19 dots (1/8 duty 1/4 bias)

- 4 X 19 dots (1/4 duty 1/3 bias)

- Low Voltage Reset (LVR) function (enabled by code option)

- LVR voltage level 1: 4.3V

- LVR voltage level 2: 2.1V

- CPU Machine cycle: 1 oscillator clock

- Watch Dog Timer (WDT)

- Warm-up Timer

- Support Low power operation modes:

Idle Mode

- Power-Down Mode

- Flash Type

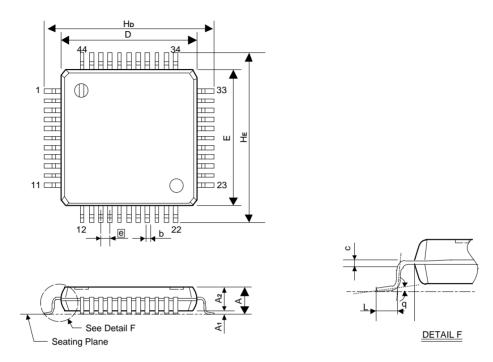

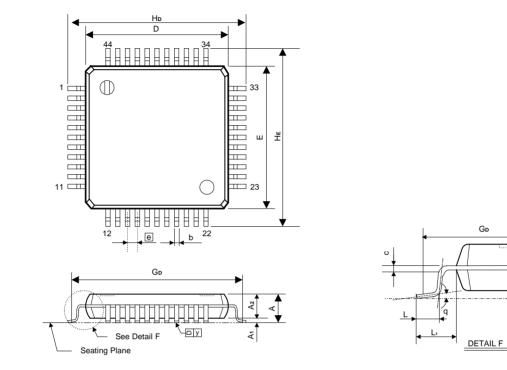

- Package: QFP44/LQFP44

V2.1

The SH79F1621 is a high performance 8051 compatible micro-controller, regard to its build-in Pipe-line instruction fetch structure, that helps the SH79F1621 can perform more fast operation speed and higher calculation performance, if compare

The SH79F1621 retains most features of the standard 8051. These features include internal 256 bytes RAM, UART and Int0-3.In addition, the SH79F1621 provides external 256 bytes RAM, It also contains 16K bytes Flash memory block both for

For high reliability and low cost issues, the SH79F1621 builds in Watchdog Timer, Low Voltage Reset function. And

program and data. Also the ADC and PWM timer functions are incorporated in SH79F1621.

SH79F1621 also supports two power saving modes to reduce power consumption.

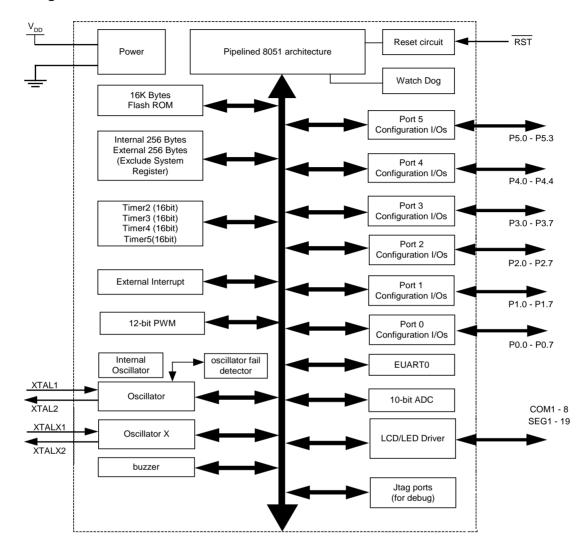

# 3. Block Diagram

# SH79F1621

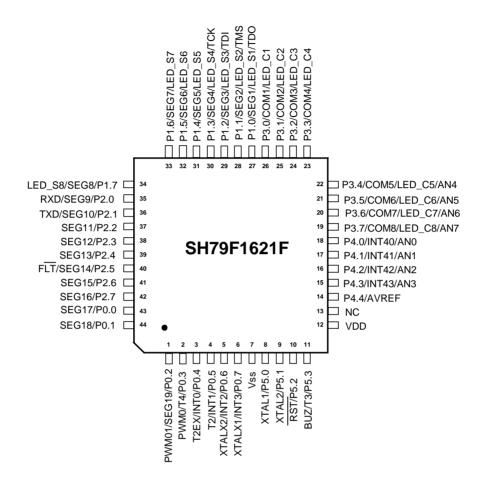

# 4. Pin Configuration

QFP44:

**Pin Configuration Diagram**

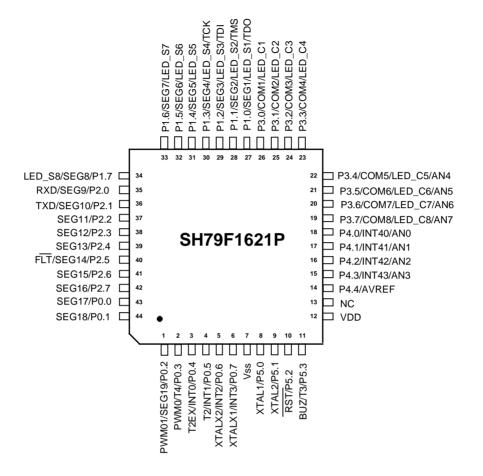

### LQFP 44:

#### **Pin Configuration Diagram**

#### Note:

The out most pin function has the highest priority, and the inner most pin function has the lowest priority (Refer to Pin Configuration Diagram. This means when one pin is occupied by a higher priority function (if enabled) cannot be used as the lower priority functional pin, even when the lower priority function is also enabled. Until the higher priority function is closed by software, can the corresponding pin be released for the lower priority function use.

## Table 4.1 Pin Function

| Pin No. | Pin Name             | Default function | Pin No. | Pin Name         | Default function |

|---------|----------------------|------------------|---------|------------------|------------------|

| 1       | PWM01/SEG19/P0.2     | P0.2             | 23      | LED_C4/COM4/P3.3 | P3.3             |

| 2       | PWM0/T4/P0.3         | P0.3             | 24      | LED_C3/COM3/P3.2 | P3.2             |

| *3      | T2EX/INT0/P0.4       | P0.4             | 25      | LED_C2/COM2/P3.1 | P3.1             |

| *4      | T2/INT1/P0.5         | P0.5             | 26      | LED_C1/COM1/P3.0 | P3.0             |

| 5       | XTALX2/INT2/P0.6     | P0.6             | 27      | LED_S1/SEG1/P1.0 | P1.0             |

| 6       | XTALX1/INT3/P0.7     | P0.7             | 28      | LED_S2/SEG2/P1.1 | P1.1             |

| 7       | V <sub>SS</sub>      |                  | 29      | LED_S3/SEG3/P1.2 | P1.2             |

| 8       | XTAL1/P5.0           |                  | 30      | LED_S4/SEG4/P1.3 | P1.3             |

| 9       | XTAL2/P5.1           |                  | 31      | LED_S5/SEG5/P1.4 | P1.4             |

| 10      | RST/P5.2             | RST              | 32      | LED_S6/SEG6/P1.5 | P1.5             |

| 11      | BUZ/T3/P5.3          | P5.3             | 33      | LED_S7/SEG7/P1.6 | P1.6             |

| 12      | V <sub>DD</sub>      |                  | 34      | LED_S8/SEG8/P1.7 | P1.7             |

| 13      | NC                   |                  | 35      | RXD/SEG9/P2.0    | P2.0             |

| 14      | AVREF/P4.4           | P4.4             | 36      | TXD/SEG10/P2.1   | P2.1             |

| 15      | AN3/INT43/P4.3       | P4.3             | 37      | SEG11/P2.2       | P2.2             |

| 16      | AN2/INT42/P4.2       | P4.2             | 38      | SEG12/P2.3       | P2.3             |

| 17      | AN1/INT41/P4.1       | P4.1             | 39      | SEG13/P2.4       | P2.4             |

| 18      | AN0/INT40/P4.0       | P4.0             | 40      | FLT/SEG14/P2.5   | P2.5             |

| 19      | AN7/LED_C8/COM8/P3.7 | P3.7             | 41      | SEG15/P2.6       | P2.6             |

| 20      | AN6/LED_C7/COM7/P3.6 | P3.6             | 42      | SEG16/P2.7       | P2.7             |

| 21      | AN5/LED_C6/COM6/P3.5 | P3.5             | 43      | SEG17/P0.0       | P0.0             |

| 22      | AN4/LED_C5/COM5/P3.4 | P3.4             | 44      | SEG18/P0.1       | P0.1             |

\* Note: P0.4, P0.5 are configured as N-channel open drain I/O

# 5. Pin Description

| Pin No.                 | Туре      | Description                                                                                                                                                                                                |

|-------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I/O PORT                | •         | ·                                                                                                                                                                                                          |

| P0.0 - P0.7             | I/O       | 8 bit General purpose CMOS I/O                                                                                                                                                                             |

| P1.0 - P1.7             | I/O       | 8 bit General purpose CMOS I/O                                                                                                                                                                             |

| P2.0 - P2.7             | I/O       | 8 bit General purpose CMOS I/O                                                                                                                                                                             |

| P3.0 - P3.7             | I/O       | 8 bit General purpose CMOS I/O                                                                                                                                                                             |

| P4.0 - P4.4             | I/O       | 5 bit General purpose CMOS I/O                                                                                                                                                                             |

| P5.0 - P5.3             | I/O       | 4 bit General purpose CMOS I/O                                                                                                                                                                             |

| Timer                   |           |                                                                                                                                                                                                            |

| T2                      | I/O       | Timer2 external input                                                                                                                                                                                      |

| Т3                      | I         | Timer3 external input                                                                                                                                                                                      |

| T4                      | I/O       | Timer4 external input/Comparator output                                                                                                                                                                    |

| T2EX                    | I         | Timer2 Reload/Capture/Direction Control                                                                                                                                                                    |

| PWM                     |           |                                                                                                                                                                                                            |

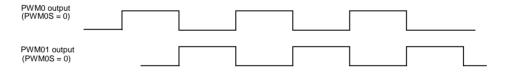

| PWM0                    | 0         | Output pin for 12-bit PWM timer                                                                                                                                                                            |

| PWM01                   | 0         | Output pin for 12-bit PWM timer with fixed phase relationship of PWM0                                                                                                                                      |

| FLT                     | I         | PWM Fault Detect input                                                                                                                                                                                     |

| EUART                   |           | ·                                                                                                                                                                                                          |

| RXD                     | I         | EUART data input                                                                                                                                                                                           |

| TXD                     | 0         | EUART data output                                                                                                                                                                                          |

| ADC                     | 1         |                                                                                                                                                                                                            |

| AN0 - AN7               | I         | ADC input channel                                                                                                                                                                                          |

| AVREF                   | I         | External ADC reference voltage input                                                                                                                                                                       |

| LCD                     |           |                                                                                                                                                                                                            |

| COM1 - COM8             | 0         | Common signal output for LCD display                                                                                                                                                                       |

| SEG1 - SEG19            | 0         | Segment signal output for LCD display                                                                                                                                                                      |

| LED                     | <u>.</u>  |                                                                                                                                                                                                            |

| LED_C1 - LED_C8         | 0         | Common signal output for LED display                                                                                                                                                                       |

| LED_S1 - LED_S8         | 0         | Segment signal output for LED display                                                                                                                                                                      |

| Interrupt & Reset & Clo | ock & Pow | /er                                                                                                                                                                                                        |

| INT0 - INT3             | I         | External interrupt 0-3 input source                                                                                                                                                                        |

| INT40 - INT43           | I         | External interrupt 40-43 input source                                                                                                                                                                      |

| RST                     | I         | The device will be reset by A low voltage on this pin longer than 10us, an internal resistor about $30k\Omega$ to V <sub>DD</sub> , So using only an external capacitor to GND can cause a power-on reset. |

| XTAL1                   | I         | Oscillator input                                                                                                                                                                                           |

| XTAL2                   | 0         | Oscillator output                                                                                                                                                                                          |

| XTALX1                  | I         | OscillatorX input                                                                                                                                                                                          |

| XTALX2                  | 0         | OscillatorX output                                                                                                                                                                                         |

| V <sub>SS</sub>         | Р         | Ground                                                                                                                                                                                                     |

| V <sub>DD</sub>         | Р         | Power supply (2.0 - 5.5V)                                                                                                                                                                                  |

(to be continued)

# (continue)

| Pin No.    | Туре | Description                       |  |  |  |  |  |  |  |

|------------|------|-----------------------------------|--|--|--|--|--|--|--|

| Buzzer     |      | ·                                 |  |  |  |  |  |  |  |

| BUZ        | 0    | Buzzer output pin                 |  |  |  |  |  |  |  |

| rogrammer  |      |                                   |  |  |  |  |  |  |  |

| TDO (P1.0) | 0    | Debug interface: Test data out    |  |  |  |  |  |  |  |

| TMS (P1.1) | I    | Debug interface: Test mode select |  |  |  |  |  |  |  |

| TDI (P1.2) | I    | Debug interface: Test data in     |  |  |  |  |  |  |  |

| TCK (P1.3) | I    | Debug interface: Test clock in    |  |  |  |  |  |  |  |

# 6. SFR Mapping

The SH79F1621 provides 256 bytes of internal RAM to contain general-purpose data memory and Special Function Register (SFR). The SFR of the SH79F1621 fall into the following categories:

| CPU Core Registers:                | ACC, B, PSW, SP, DPL, DPH                                                                                  |

|------------------------------------|------------------------------------------------------------------------------------------------------------|

| Enhanced CPU Core Registers:       | AUXC, DPL1, DPH1, INSCON, XPAGE                                                                            |

| Power and Clock Control Registers: | PCON, SUSLO                                                                                                |

| Flash Registers:                   | IB_OFFSET, IB_DATA, IB_CON1, IB_CON2, IB_CON3, IB_CON4, IB_CON5, FLASHCON                                  |

| Data Memory Register:              | XPAGE                                                                                                      |

| Hardware Watchdog Timer Registers: | RSTSTAT                                                                                                    |

| System Clock Control Register:     | CLKCON                                                                                                     |

| Interrupt System Registers:        | IEN0, IEN1, IENC, IPH0, IPL0, IPH1, IPL1, EXF0, EXF1                                                       |

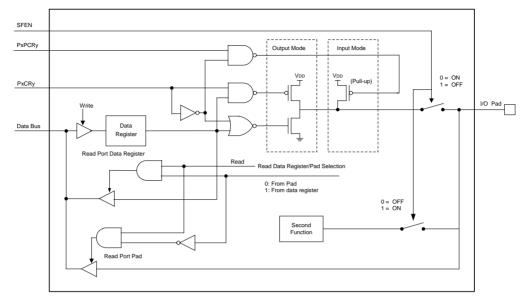

| I/O Port Registers:                | P0, P1, P2, P3, P4, P5, P0CR, P1CR, P2CR, P3CR, P4CR, P5CR, P0PCR, P1PCR, P2PCR, P3PCR, P4PCR, P5PCR, P0OS |

| Timer Registers:                   | TCON, T2CON, T2MOD, TH2, TL2, RCAP2L, RCAP2H, T3CON, TH3, TL3, T4CON, TH4, TL4, SWTHL, T5CON, TH5, TL5     |

| EUART Registers:                   | SCON, SBUF, SADEN, SADDR, PCON, RXCON                                                                      |

| ADC Registers:                     | ADCON, ADT, ADCH, ADDL, ADDH                                                                               |

| LCD Registers:                     | DISPCON, DISPCLK0, DISPCLK1, P0SS, P1SS, P2SS, P3SS                                                        |

| LED Registers:                     | DISPCON, DISPCLK0, DISPCLK1, P1SS, P3SS                                                                    |

| Buzzer Registers:                  | BUZCON                                                                                                     |

| PWM Registers:                     | PWMEN, PWMEN1, PWMLO, PWM0C, PWM0PL, PWM0PH, PWM0DL, PWM0DH                                                |

| LPD Registers:                     | LPDCON                                                                                                     |

SH79F1621

# Table 6.1 CPU Core SFRs

| Mnem   | Add | Name                     | POR/WDT/LVR<br>/PIN Reset Value | Bit7   | Bit6   | Bit5   | Bit4   | Bit3   | Bit2   | Bit1   | Bit0   |

|--------|-----|--------------------------|---------------------------------|--------|--------|--------|--------|--------|--------|--------|--------|

| ACC    | E0H | Accumulator              | 00000000                        | ACC.7  | ACC.6  | ACC.5  | ACC.4  | ACC.3  | ACC.2  | ACC.1  | ACC.0  |

| В      | F0H | B Register               | 00000000                        | B.7    | B.6    | B.5    | B.4    | B.3    | B.2    | B.1    | B.0    |

| AUXC   | F1H | C Register               | 00000000                        | C.7    | C.6    | C.5    | C.4    | C.3    | C.2    | C.1    | C.0    |

| PSW    | D0H | Program Status Word      | 0000000                         | CY     | AC     | F0     | RS1    | RS0    | OV     | F1     | Р      |

| SP     | 81H | Stack Pointer            | 00000111                        | SP.7   | SP.6   | SP.5   | SP.4   | SP.3   | SP.2   | SP.1   | SP.0   |

| DPL    | 82H | Data Pointer Low byte    | 0000000                         | DPL0.7 | DPL0.6 | DPL0.5 | DPL0.4 | DPL0.3 | DPL0.2 | DPL0.1 | DPL0.0 |

| DPH    | 83H | Data Pointer High byte   | 00000000                        | DPH0.7 | DPH0.6 | DPH0.5 | DPH0.4 | DPH0.3 | DPH0.2 | DPH0.1 | DPH0.0 |

| DPL1   | 84H | Data Pointer 1 Low byte  | 00000000                        | DPL1.7 | DPL1.6 | DPL1.5 | DPL1.4 | DPL1.3 | DPL1.2 | DPL1.1 | DPL1.0 |

| DPH1   | 85H | Data Pointer 1 High byte | 00000000                        | DPH1.7 | DPH1.6 | DPH1.5 | DPH1.4 | DPH1.3 | DPH1.2 | DPH1.1 | DPH1.0 |

| INSCON | 86H | Data pointer select      | -000-0                          | -      | BKS0   | -      | -      | DIV    | MUL    | -      | DPS    |

# Table 6.2 Power and Clock control SFRs

| Mnem  | Add | Name                 | POR/WDT/LVR<br>/PIN Reset Value | Bit7    | Bit6    | Bit5    | Bit4    | Bit3    | Bit2    | Bit1    | Bit0    |

|-------|-----|----------------------|---------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|

| PCON  | 87H | Power Control        | 000000                          | SMOD    | SSTAT   | -       | -       | GF1     | GF0     | PD      | IDL     |

| SUSLO | 8EH | Suspend Mode Control | 0000000                         | SUSLO.7 | SUSLO.6 | SUSLO.5 | SUSLO.4 | SUSLO.3 | SUSLO.2 | SUSLO.1 | SUSLO.0 |

SH79F1621

# Table 6.3 Flash control SFRs

| Mnem          | Add          | Name                                               | POR/WDT/LVR<br>/PIN Reset Value | Bit7            | Bit6            | Bit5            | Bit4            | Bit3            | Bit2            | Bit1            | Bit0            |

|---------------|--------------|----------------------------------------------------|---------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| IB_OFF<br>SET | FBH<br>Bank0 | Low byte offset of flash memory<br>for programming | 00000000                        | IB_OFF<br>SET.7 | IB_OFF<br>SET.6 | IB_OFF<br>SET.5 | IB_OFF<br>SET.4 | IB_OFF<br>SET.3 | IB_OFF<br>SET.2 | IB_OFF<br>SET.1 | IB_OFF<br>SET.0 |

| IB_DATA       | FCH<br>Bank0 | Data Register for programming<br>flash memory      | 00000000                        | IB_DATA.7       | IB_DATA.6       | IB_DATA.5       | IB_DATA.4       | IB_DATA.3       | IB_DATA.2       | IB_DATA.1       | IB_DATA.0       |

| IB_CON1       | F2H<br>Bank0 | Flash Memory Control Register 1                    | 00000000                        | IB_CON1.7       | IB_CON1.6       | IB_CON1.5       | IB_CON1.4       | IB_CON1.3       | IB_CON1.2       | IB_CON1.1       | IB_CON1.0       |

| IB_CON2       | F3H<br>Bank0 | Flash Memory Control Register 2                    | 0000                            | -               | -               | -               | -               | IB_CON2.3       | IB_CON2.2       | IB_CON2.1       | IB_CON2.0       |

| IB_CON3       | F4H<br>Bank0 | Flash Memory Control Register 3                    | 0000                            | -               | -               | -               | -               | IB_CON3.3       | IB_CON3.2       | IB_CON3.1       | IB_CON3.0       |

| IB_CON4       | F5H<br>Bank0 | Flash Memory Control Register 4                    | 0000                            | -               | -               | -               | -               | IB_CON4.3       | IB_CON4.2       | IB_CON4.1       | IB_CON4.0       |

| IB_CON5       | F6H<br>Bank0 | Flash Memory Control Register 5                    | 0000                            | -               | -               | -               | -               | IB_CON5.3       | IB_CON5.2       | IB_CON5.1       | IB_CON5.0       |

| XPAGE         | F7H<br>Bank0 | Memory Page                                        | 000000                          | -               | -               | XPAGE.5         | XPAGE.4         | XPAGE.3         | XPAGE.2         | XPAGE.1         | XPAGE.0         |

| FLASHCON      | A7H<br>Bank0 | Flash access control                               | 0                               | -               | -               | -               | -               | -               | -               | -               | FAC             |

# Table 6.4 WDT SFR

| Mnem    | Add          | Name                   | POR/WDT/LVR<br>/PIN Reset Value | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2  | Bit1  | Bit0  |

|---------|--------------|------------------------|---------------------------------|------|------|------|------|------|-------|-------|-------|

| RSTSTAT | B1H<br>Bank0 | Watchdog Timer Control | *-***000                        | WDOF | -    | PORF | LVRF | CLRF | WDT.2 | WDT.1 | WDT.0 |

\*Note: RSTSTAT initial value is determined by different RESET.

Table 6.5 CLKCON SFR

| Mnem   | Add          | Namo                          | POR/WDT/LVR<br>/PIN Reset Value | Bit/          | Bit6  | Bit5  | Bit4  | Bit3 | Bit2 | Bit1 | Bit0 |

|--------|--------------|-------------------------------|---------------------------------|---------------|-------|-------|-------|------|------|------|------|

| CLKCON | B2H<br>Bank0 | System Clock Control Register | 111000                          | 32k_<br>SPDUP | CLKS1 | CLKS0 | SCMIF | HFON | FS   | -    | -    |

SH79F1621

# Table 6.6 Interrupt SFRs

| Mnem  | Add          | Name                               | POR/WDT/LVR<br>/PIN Reset Value | BIT/      | Bit6  | Bit5  | Bit4  | Bit3  | Bit2  | Bit1  | Bit0  |

|-------|--------------|------------------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|-------|

| IEN0  | A8H<br>Bank0 | Interrupt Enable Control 0         | 0000-000                        | EA        | EADC  | ET2   | ES    | -     | EX1   | ET5   | EX0   |

| IEN1  | A9H<br>Bank0 | Interrupt Enable Control 1         | 000000-                         | ESCM/ELPD | ET4   | EPWM  | ET3   | EX4   | EX3   | EX2   | -     |

| IENC  | BAH<br>Bank0 | Interrupt 4channel enable control  | 0000                            | -         | -     | -     | -     | EXS43 | EXS42 | EXS41 | EXS40 |

| IENC1 | BBH<br>Bank0 | Interrupt channel enable control 1 | 00                              | -         | -     | -     | -     | -     | -     | ESCM1 | ELPD  |

| IPH0  | B4H<br>Bank0 | Interrupt Priority Control High 0  | -000-000                        | -         | PADCH | PT2H  | PSH   | -     | PX1H  | PT5H  | PX0H  |

| IPL0  | B8H<br>Bank0 | Interrupt Priority Control Low 0   | -000-000                        | -         | PADCL | PT2L  | PSL   | -     | PX1L  | PT5L  | PX0L  |

| IPH1  | B5H<br>Bank0 | Interrupt Priority Control High 1  | 000000-                         | PSCMH     | PT4H  | PPWMH | PT3H  | PX4H  | РХ3Н  | PX2H  | -     |

| IPL1  | B9H<br>Bank0 | Interrupt Priority Control Low 1   | 000000-                         | PSCML     | PT4L  | PPWML | PT3L  | PX4L  | PX3L  | PX2L  | -     |

| EXF0  | E8H<br>Bank0 | External interrupt Control 0       | 00000000                        | IT4.1     | IT4.0 | IT3.1 | IT3.0 | IT2.1 | IT2.0 | IE3   | IE2   |

| EXF1  | D8H<br>Bank0 | External interrupt Control 1       | 0000                            | -         | -     | -     | -     | IF43  | IF42  | IF41  | IF40  |

SH79F1621

# Table 6.7 Port SFRs

| Mnem  | Add          | Name                                 | POR/WDT/LVR<br>/PIN Reset Value | Bit7    | Bit6    | Bit5    | Bit4    | Bit3    | Bit2    | Bit1    | Bit0    |

|-------|--------------|--------------------------------------|---------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|

| P0    | 80H<br>Bank0 | 8-bit Port 0                         | 0000000                         | P0.7    | P0.6    | P0.5    | P0.4    | P0.3    | P0.2    | P0.1    | P0.0    |

| P1    | 90H<br>Bank0 | 8-bit Port 1                         | 00000000                        | P1.7    | P1.6    | P1.5    | P1.4    | P1.3    | P1.2    | P1.1    | P1.0    |

| P2    | A0H<br>Bank0 | 8-bit Port 2                         | 00000000                        | P2.7    | P2.6    | P2.5    | P2.4    | P2.3    | P2.2    | P2.1    | P2.0    |

| P3    | B0H<br>Bank0 | 8-bit Port 3                         | 00000000                        | P3.7    | P3.6    | P3.5    | P3.4    | P3.3    | P3.2    | P3.1    | P3.0    |

| P4    | C0H<br>Bank0 | 5-bit Port 4                         | 00000                           | -       | -       | -       | P4.4    | P4.3    | P4.2    | P4.1    | P4.0    |

| P5    | 80H<br>Bank1 | 4-bit Port 5                         | 0000                            | -       | -       | -       | -       | P5.3    | P5.2    | P5.1    | P5.0    |

| P0CR  | E1H<br>Bank0 | Port0 input/output direction control | 00000000                        | P0CR.7  | P0CR.6  | P0CR.5  | P0CR.4  | P0CR.3  | P0CR.2  | P0CR.1  | P0CR.0  |

| P1CR  | E2H<br>Bank0 | Port1 input/output direction control | 00000000                        | P1CR.7  | P1CR.6  | P1CR.5  | P1CR.4  | P1CR.3  | P1CR.2  | P1CR.1  | P1CR.0  |

| P2CR  | E3H<br>Bank0 | Port2 input/output direction control | 00000000                        | P2CR.7  | P2CR.6  | P2CR.5  | P2CR.4  | P2CR.3  | P2CR.2  | P2CR.1  | P2CR.0  |

| P3CR  | E4H<br>Bank0 | Port3 input/output direction control | 00000000                        | P3CR.7  | P3CR.6  | P3CR.5  | P3CR.4  | P3CR.3  | P3CR.2  | P3CR.1  | P3CR.0  |

| P4CR  | E5H<br>Bank0 | Port4 input/output direction control | 00000                           | -       | -       | -       | P4CR.4  | P4CR.3  | P4CR.2  | P4CR.1  | P4CR.0  |

| P5CR  | E1H<br>Bank1 | Port5 input/output direction control | 0000                            | -       | -       | -       | -       | P5CR.3  | P5CR.2  | P5CR.1  | P5CR.0  |

| P0PCR | E9H<br>Bank0 | Internal pull-high enable for Port0  | 00000000                        | P0PCR.7 | P0PCR.6 | P0PCR.5 | P0PCR.4 | P0PCR.3 | P0PCR.2 | P0PCR.1 | P0PCR.0 |

| P1PCR | EAH<br>Bank0 | Internal pull-high enable for Port1  | 00000000                        | P1PCR.7 | P1PCR.6 | P1PCR.5 | P1PCR.4 | P1PCR.3 | P1PCR.2 | P1PCR.1 | P1PCR.0 |

| P2PCR | EBH<br>Bank0 | Internal pull-high enable for Port2  | 00000000                        | P2PCR.7 | P2PCR.6 | P2PCR.5 | P2PCR.4 | P2PCR.3 | P2PCR.2 | P2PCR.1 | P2PCR.0 |

| P3PCR | ECH<br>Bank0 | Internal pull-high enable for Port3  | 00000000                        | P3PCR.7 | P3PCR.6 | P3PCR.5 | P3PCR.4 | P3PCR.3 | P3PCR.2 | P3PCR.1 | P3PCR.0 |

| P4PCR | EDH<br>Bank0 | Internal pull-high enable for Port4  | 00000                           | -       | -       | -       | P4PCR.4 | P4PCR.3 | P4PCR.2 | P4PCR.1 | P4PCR.0 |

| P5PCR | E9H<br>Bank1 | Internal pull-high enable for Port5  | 0000                            | -       | -       | -       | -       | P5PCR.3 | P5PCR.2 | P5PCR.1 | P5PCR.0 |

| P0OS  | EFH<br>Bank0 | Output mode control                  | 00                              | -       | -       | P0OS.5  | P0OS.4  | -       | -       | -       | -       |

SH79F1621

# Table 6.8 Timer SFRs

| Mnem   | Add          | Name                                         | POR/WDT/LVR<br>/PIN Reset Value | Bit7     | Bit6     | Bit5     | Bit4     | Bit3     | Bit2     | Bit1     | Bit0     |

|--------|--------------|----------------------------------------------|---------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|

| TCON   | 88H<br>Bank0 | Timer/Counter Control                        | 0000                            | -        | -        | -        | -        | IE1      | IT1      | IE0      | IT0      |

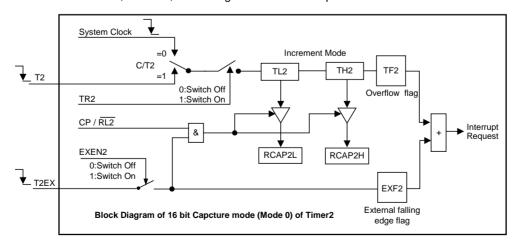

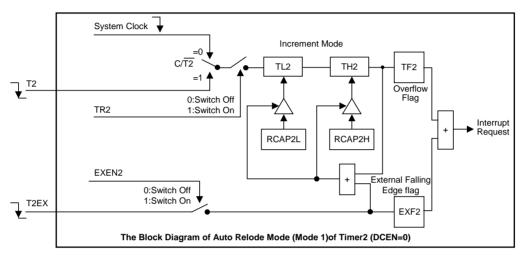

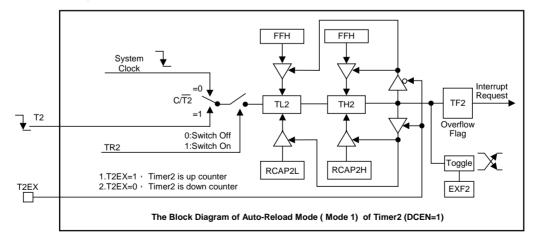

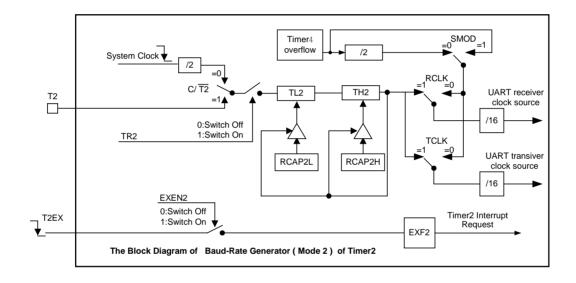

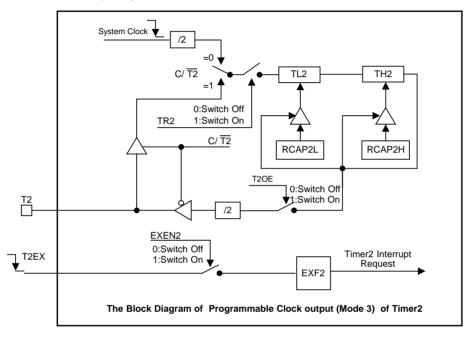

| T2CON  | C8H<br>Bank0 | Timer/Counter 2 Control                      | 00000000                        | TF2      | EXF2     | RCLK     | TCLK     | EXEN2    | TR2      | C/T 2    | CP/RL2   |

| T2MOD  | C9H<br>Bank0 | Timer/Counter 2 Mode                         | 00                              | -        | -        | -        | -        | -        | -        | T2OE     | DCEN     |

| RCAP2L | CAH<br>Bank0 | Timer/Counter 2 Reload<br>/Caprure Low Byte  | 00000000                        | RCAP2L.7 | RCAP2L.6 | RCAP2L.5 | RCAP2L.4 | RCAP2L.3 | RCAP2L.2 | RCAP2L.1 | RCAP2L.0 |

| RCAP2H | CBH<br>Bank0 | Timer/Counter 2 Reload<br>/Caprure High Byte | 00000000                        | RCAP2H.7 | RCAP2H.6 | RCAP2H.5 | RCAP2H.4 | RCAP2H.3 | RCAP2H.2 | RCAP2H.1 | RCAP2H.0 |

| TL2    | CCH<br>Bank0 | Timer/Counter 2 Low Byte                     | 00000000                        | TL2.7    | TL2.6    | TL2.5    | TL2.4    | TL2.3    | TL2.2    | TL2.1    | TL2.0    |

| TH2    | CDH<br>Bank0 | Timer/Counter 2 High Byte                    | 00000000                        | TH2.7    | TH2.6    | TH2.5    | TH2.4    | TH2.3    | TH2.2    | TH2.1    | TH2.0    |

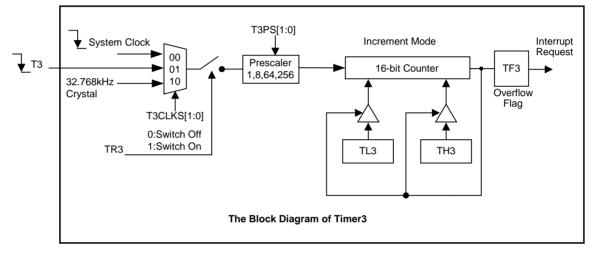

| T3CON  | 88H<br>Bank1 | Timer/Counter 3 Control                      | 0-00-000                        | TF3      | -        | T3PS.1   | T3PS.0   | -        | TR3      | T3CLKS.1 | T3CLKS.0 |

| SWTHL  | 89H<br>Bank1 | Timer/Counter data switch                    | 00                              | -        | -        | -        | -        | -        | -        | T5HLCON  | T3HLCON  |

| TL3    | 8CH<br>Bank1 | Timer/Counter 3 Low Byte                     | 00000000                        | TL3.7    | TL3.6    | TL3.5    | TL3.4    | TL3.3    | TL3.2    | TL3.1    | TL3.0    |

| TH3    | 8DH<br>Bank1 | Timer/Counter 3 High Byte                    | 00000000                        | TH3.7    | TH3.6    | TH3.5    | TH3.4    | TH3.3    | TH3.2    | TH3.1    | TH3.0    |

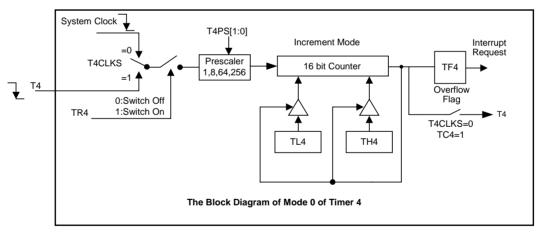

| T4CON  | C8H<br>Bank1 | Timer/Counter 4 Control                      | 00000000                        | TF4      | TC4      | T4PS1    | T4PS0    | T4M1     | T4M0     | TR4      | T4CLKS   |

| TL4    | CCH<br>Bank1 | Timer/Counter 4 Low Byte                     | 00000000                        | TL4.7    | TL4.6    | TL4.5    | TL4.4    | TL4.3    | TL4.2    | TL4.1    | TL4.0    |

| TH4    | CDH<br>Bank1 | Timer/Counter 4 High Byte                    | 00000000                        | TH4.7    | TH4.6    | TH4.5    | TH4.4    | TH4.3    | TH4.2    | TH4.1    | TH4.0    |

| T5CON  | C0H<br>Bank1 | Timer/Counter 5 Control                      | 0-000-0-                        | TF5      | -        | T5PS1    | T5PS0    | -        | -        | TR5      | -        |

| TL5    | CEH<br>Bank1 | Timer/Counter 5 Low Byte                     | 00000000                        | TL5.7    | TL5.6    | TL5.5    | TL5.4    | TL5.3    | TL5.2    | TL5.1    | TL5.0    |

| TH5    | CFH<br>Bank1 | Timer/Counter 5 High Byte                    | 00000000                        | TH5.7    | TH5.6    | TH5.5    | TH5.4    | TH5.3    | TH5.2    | TH5.1    | TH5.0    |

# Table 6.9 EUART SFRs

| Mnem  | Add          | Name                            | POR/WDT/LVR<br>/PIN Reset Value | Bit7    | Bit6     | Bit5      | Bit4    | Bit3    | Bit2    | Bit1    | Bit0    |

|-------|--------------|---------------------------------|---------------------------------|---------|----------|-----------|---------|---------|---------|---------|---------|

| SCON  | 98H<br>Bank0 | Serial Control                  | 00000000                        | SM0/FE  | SM1/RXOV | SM2/TXCOL | REN     | TB8     | RB8     | TI      | RI      |

| SBUF  | 99H<br>Bank0 | Serial Data Buffer              | 00000000                        | SBUF.7  | SBUF.6   | SBUF.5    | SBUF.4  | SBUF.3  | SBUF.2  | SBUF.1  | SBUF.0  |

| SADEN | 9BH<br>Bank0 | Slave Address Mask              | 00000000                        | SADEN.7 | SADEN.6  | SADEN.5   | SADEN.4 | SADEN.3 | SADEN.2 | SADEN.1 | SADEN.0 |

| SADDR | 9AH<br>Bank0 | Slave Address                   | 00000000                        | SADDR.7 | SADDR.6  | SADDR.5   | SADDR.4 | SADDR.3 | SADDR.2 | SADDR.1 | SADDR.0 |

| PCON  | 87H<br>Bank0 | Power & serial Control          | 000000                          | SMOD    | SSTAT    | -         | -       | GF1     | GF0     | PD      | IDL     |

| RxCON | 9FH<br>Bank0 | Rxd pin Schmidt voltage Control | 00                              | -       | -        | -         | -       | -       | -       | RxCON1  | RxCON0  |

## Table 6.10 ADC SFRs

| Mnem  | Add          | Name                      | POR/WDT/LVR<br>/PIN Reset Value | Bit7  | Bit6  | Bit5  | Bit4 | Bit3 | Bit2 | Bit1 | Bit0    |

|-------|--------------|---------------------------|---------------------------------|-------|-------|-------|------|------|------|------|---------|

| ADCON | 93H<br>Bank0 | ADC Control               | 00000000                        | ADON  | ADCIF | EC    | REFC | SCH2 | SCH1 | SCH0 | GO/DONE |

| ADT   | 94H<br>Bank0 | ADC Time Configuration    | 000-0000                        | TADC2 | TADC1 | TADC0 | -    | TS3  | TS2  | TS1  | TS0     |

| ADCH  | 95H<br>Bank0 | ADC Channel Configuration | 0000000                         | CH7   | CH6   | CH5   | CH4  | СНЗ  | CH2  | CH1  | CH0     |

| ADDL  | 96H<br>Bank0 | ADC Data Low Byte         | 00                              | -     | -     | -     | -    | -    | -    | A1   | A0      |

| ADDH  | 97H<br>Bank0 | ADC Data High Byte        | 0000000                         | A9    | A8    | A7    | A6   | A5   | A4   | A3   | A2      |

# Table 6.11 Buzzer SFR

| Mnem   | Add          |                       | POR/WDT/LVR<br>/PIN Reset Value |   | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|--------|--------------|-----------------------|---------------------------------|---|------|------|------|------|------|------|------|

| BUZCON | BDH<br>Bank0 | Buzzer output control | 0000                            | - | -    | -    | -    | BCA2 | BCA1 | BCA0 | BZEN |

# Table 6.12 LCD SFRs

| Mnem     | Add          | Name           | POR/WDT/LVR<br>/PIN Reset Value | Bit7    | Bit6   | Bit5   | Bit4   | Bit3   | Bit2   | Bit1   | Bit0   |

|----------|--------------|----------------|---------------------------------|---------|--------|--------|--------|--------|--------|--------|--------|

| DISPCON  | ABH<br>Bank0 | LCD Control    | 00000000                        | DISPSEL | LCDON  | ELCC   | DUTY   | VOL3   | VOL2   | VOL1   | VOL0   |

| DISPCON1 | ADH<br>Bank0 | LCD Control 1  | 00000                           | -       | -      | -      | RLCD   | FCCTL1 | FCCTL0 | MOD1   | MOD0   |

| DISPCLK0 | ACH<br>Bank0 | LCD clock 0    | 0000000                         | DCK0.7  | DCK0.6 | DCK0.5 | DCK0.4 | DCK0.3 | DCK0.2 | DCK0.1 | DCK0.0 |

| DISPCLK1 | AAH<br>Bank0 | LCD clock 1    | 0                               | -       | -      | -      | -      | -      | -      | -      | DCK1.0 |

| P0SS     | B6H<br>Bank0 | P0 mode Select | 000                             | -       | -      | -      | -      | -      | P0S2   | P0S1   | P0S0   |

| P1SS     | 9CH<br>Bank0 | P1 mode Select | 0000000                         | P1S7    | P1S6   | P1S5   | P1S4   | P1S3   | P1S2   | P1S1   | P1S0   |

| P2SS     | 9DH<br>Bank0 | P2 mode Select | 0000000                         | P2S7    | P2S6   | P2S5   | P2S4   | P2S3   | P2S2   | P2S1   | P2S0   |

| P3SS     | 9EH<br>Bank0 | P3 mode Select | 0000000                         | P3S7    | P3S6   | P3S5   | P3S4   | P3S3   | P3S2   | P3S1   | P3S0   |

# Table 6.13 LED SFRs

| Mnem     | Add          | Name           | POR/WDT/LVR<br>/PIN Reset Value | Bit7    | Bit6   | Bit5   | Bit4   | Bit3   | Bit2   | Bit1   | Bit0   |

|----------|--------------|----------------|---------------------------------|---------|--------|--------|--------|--------|--------|--------|--------|

| DISPCON  | ABH<br>Bank0 | LED Control    | 00-0                            | DISPSEL | LEDON  | -      | DUTY   | -      | -      | -      | -      |

| DISPCLK0 | ACH<br>Bank0 | LED clock 0    | 00000000                        | DCK0.7  | DCK0.6 | DCK0.5 | DCK0.4 | DCK0.3 | DCK0.2 | DCK0.1 | DCK0.0 |

| DISPCLK1 | AAH<br>Bank0 | LED clock 1    | 0                               | -       | -      | -      | -      | -      | -      | -      | DCK1.0 |

| P1SS     | 9CH<br>Bank0 | P1 mode Select | 00000000                        | P1S7    | P1S6   | P1S5   | P1S4   | P1S3   | P1S2   | P1S1   | P1S0   |

| P3SS     | 9EH<br>Bank0 | P3 mode Select | 00000000                        | P3S7    | P3S6   | P3S5   | P3S4   | P3S3   | P3S2   | P3S1   | P3S0   |

# Table 6.14 PWM SFRs

| Mnem   | Add          | Name                                | POR/WDT/LVR<br>/PIN Reset Value | Bit7    | Bit6    | Bit5    | Bit4    | Bit3    | Bit2    | Bit1    | Bit0    |

|--------|--------------|-------------------------------------|---------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|

| PWMEN  | CFH<br>Bank0 | PWM timer enable                    | -000                            | -       | EFLT    | -       | -       | EPWM01  | -       | -       | EPWM0   |

| PWMEN1 | B7H<br>Bank0 | PWM output enable                   | 0                               | -       | -       | -       | -       | -       | -       | -       | PWM0    |

| PWMLO  | E7H<br>Bank0 | PWM register Lock                   | 0000000                         | PWMLO.7 | PWMLO.6 | PWMLO.5 | PWMLO.4 | PWMLO.3 | PWMLO.2 | PWMLO.1 | PWMLO.0 |

| PWM0C  | D2H<br>Bank0 | 12-bit PWM Control                  | 00-0000                         | PWM0IE  | PWM0IF  | -       | FLTS    | FLTC    | PWM0S   | TnCK01  | TnCK00  |

| PWM0PL | D3H<br>Bank0 | 12-bit PWM Period Control low byte  | 00000000                        | PP0.7   | PP0.6   | PP0.5   | PP.4    | PP0.3   | PP0.2   | PP0.1   | PP0.0   |

| PWM0PH | D4H<br>Bank0 | 12-bit PWM Period Control high byte | 0000                            | -       | -       | -       | -       | PP0.11  | PP0.10  | PP0.9   | PP0.8   |

| PWM0DL | D5H<br>Bank0 | 12-bit PWM Duty Control low byte    | 0000000                         | PD0.7   | PD0.6   | PD0.5   | PD0.4   | PD0.3   | PD0.2   | PD0.1   | PD0.0   |

| PWM0DH | D6H<br>Bank0 | 12-bit PWM Duty Control high byte   | 0000                            | -       | -       | -       | -       | PD0.11  | PD0.10  | PD0.9   | PD0.8   |

| PWM0DT | D1H<br>Bank0 | PWM01 Dead time control             | 00000000                        | DT0.7   | DT0.6   | DT0.5   | DT0.4   | DT0.3   | DT0.2   | DT0.1   | DT0.0   |

# Table 6.15 LPD SFR

| Mnem   | Add          | Namo        | POR/WDT/LVR<br>/PIN Reset Value | Bit / | Bit6 | Bit5  | Bit4  | Bit3  | Bit2  | Bit1  | Bit0  |

|--------|--------------|-------------|---------------------------------|-------|------|-------|-------|-------|-------|-------|-------|

| LPDCON | B3H<br>Bank0 | LPD control | 00000000                        | LPDEN | LPDF | LPDMD | LPDIF | LPDS3 | LPDS2 | LPDS1 | LPDS0 |

Note: - : Unimplemented

## SFR Map Bank0

|     | Bit<br>addressable |         |          | Non       | Bit address | able     |         |          |     |

|-----|--------------------|---------|----------|-----------|-------------|----------|---------|----------|-----|

|     | 0/8                | 1/9     | 2/A      | 3/B       | 4/C         | 5/D      | 6/E     | 7/F      |     |

| F8H |                    |         |          | IB_OFFSET | IB_DATA     |          |         |          | FFH |

| F0H | В                  | AUXC    | IB_CON1  | IB_CON2   | IB_CON3     | IB_CON4  | IB_CON5 | XPAGE    | F7H |

| E8H | EXF0               | P0PCR   | P1PCR    | P2PCR     | P3PCR       | P4PCR    |         | P0OS     | EFH |

| E0H | ACC                | P0CR    | P1CR     | P2CR      | P3CR        | P4CR     |         | PWMLO    | E7H |

| D8H | EXF1               |         |          |           |             |          |         |          | DFH |

| D0H | PSW                | PWM0DT  | PWM0C    | PWM0PL    | PWM0PH      | PWM0DL   | PWM0DH  |          | D7H |

| C8H | T2CON              | T2MOD   | RCAP2L   | RCAP2H    | TL2         | TH2      |         | PWMEN    | CFH |

| C0H | P4                 |         |          |           |             |          |         |          | C7H |

| B8H | IPL0               | IPL1    | IENC     | IENC1     |             | BUZCON   |         |          | BFH |

| B0H | P3                 | RSTSTAT | CLKCON   | LPDCON    | IPH0        | IPH1     | P0SS    | PWMEN1   | B7H |

| A8H | IEN0               | IEN1    | DISPCLK1 | DISPCON   | DISPCLK0    | DISPCON1 |         |          | AFH |

| A0H | P2                 |         |          |           |             |          |         | FLASHCON | A7H |

| 98H | SCON               | SBUF    | SADDR    | SADEN     | P1SS        | P2SS     | P3SS    | RxCON    | 9FH |

| 90H | P1                 |         |          | ADCON     | ADT         | ADCH     | ADDL    | ADDH     | 97H |

| 88H | TCON               |         |          |           |             |          | SUSLO   |          | 8FH |

| 80H | P0                 | SP      | DPL      | DPH       | DPL1        | DPH1     | INSCON  | PCON     | 87H |

|     | 0/8                | 1/9     | 2/A      | 3/B       | 4/C         | 5/D      | 6/E     | 7/F      |     |

# Bank1

|     | Bit<br>addressable |       |     | Nor | Bit address | able |        |       |     |

|-----|--------------------|-------|-----|-----|-------------|------|--------|-------|-----|

|     | 0/8                | 1/9   | 2/A | 3/B | 4/C         | 5/D  | 6/E    | 7/F   |     |

| F8H |                    |       |     |     |             |      |        |       | FFH |

| F0H | В                  | AUXC  |     |     |             |      |        | XPAGE | F7H |

| E8H |                    | P5PCR |     |     |             |      |        |       | EFH |

| E0H | ACC                | P5CR  |     |     |             |      |        |       | E7H |

| D8H |                    |       |     |     |             |      |        |       | DFH |

| D0H | PSW                |       |     |     |             |      |        |       | D7H |

| C8H | T4CON              |       |     |     | TL4         | TH4  | TL5    | TH5   | CFH |

| COH | T5CON              |       |     |     |             |      |        |       | C7H |

| B8H | IPL0               | IPL1  |     |     |             |      |        |       | BFH |

| B0H |                    |       |     |     | IPH0        | IPH1 |        |       | B7H |

| A8H | IEN0               | IEN1  |     |     |             |      |        |       | AFH |

| A0H |                    |       |     |     |             |      |        |       | A7H |

| 98H |                    |       |     |     |             |      |        |       | 9FH |

| 90H |                    |       |     |     |             |      |        |       | 97H |

| 88H | T3CON              | SWTHL |     |     | TL3         | TH3  | SUSLO  |       | 8FH |

| 80H | P5                 | SP    | DPL | DPH | DPL1        | DPH1 | INSCON | PCON  | 87H |

|     | 0/8                | 1/9   | 2/A | 3/B | 4/C         | 5/D  | 6/E    | 7/F   |     |

Note: The unused addresses of SFR are not available.

# 7. Normal Function

## 7.1 CPU

# 7.1.1 CPU Core SFR

## Feature

CPU core registers: ACC, B, PSW, SP, DPL, DPH

### Accumulator

ACC is the Accumulator register. Instruction system adopts A as mnemonic symbol of accumulator.

### B Register

The B register is used during multiply and divide operations. For other instructions it can be treated as another scratch pad register.

## Stack Pointer (SP)

The Stack Pointer Register is 8 bits special register, It is incremented before data is stored during PUSH, CALL executions and it is decremented after data is out of stack during POP, RET, RETI executions. The stack may reside anywhere in on-chip internal RAM (00H-FFH). On reset, the Stack Pointer is initialized to 07H causing the stack to begin at location 08H.

#### Program Status Word Register (PSW)

The PSW register contains program status information.

#### Data Pointer Register (DPTR)

DPTR consists of a high byte (DPH) and a low byte (DPL). Its intended function is to hold a 16-bit address, but it may be manipulated as a 16-bit register or as two independent 8-bit registers.

Table 7.1 PSW Register

| D0H                              | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|----------------------------------|------|------|------|------|------|------|------|------|

| PSW                              | CY   | AC   | F0   | RS1  | RS0  | OV   | F1   | Р    |

| R/W                              | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R    |

| Reset Value<br>(POR/WDT/LVR/PIN) | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| Bit Number | Bit Mnemonic | Description                                                                                                                                                             |

|------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7          | CY           | Carry flag bit<br>0: no carry or borrow in an arithmetic or logic operation<br>1: a carry or borrow in an arithmetic or logic operation                                 |

| 6          | AC           | Auxiliary Carry flag bit<br>0: no auxiliary carry or borrow in an arithmetic or logic operation<br>1: an auxiliary carry or borrow in an arithmetic or logic operation  |

| 5          | FO           | F0 flag bit<br>Available to the user for general purposes                                                                                                               |

| 4-3        | RS[1:0]      | R0-R7 Register bank select bits<br>00: Bank0 (Address to 00H-07H)<br>01: Bank1 (Address to 08H-0FH)<br>10: Bank2 (Address to 10H-17H)<br>11: Bank3 (Address to 18H-1FH) |

| 2          | ov           | Overflow flag bit<br>0: no overflow happen<br>1: an overflow happen                                                                                                     |

| 1          | F1           | F1 flag bit<br>Available to the user for general purposes                                                                                                               |

| 0          | Р            | Parity flag bit<br>0: In the Accumulator,the bits whose value is 1 is even number<br>1: In the Accumulator,the bits whose value is 1 is odd number                      |

# 7.1.2 Enhanced CPU core SFRs

Extended 'MUL' and 'DIV' instructions: 16bit\*8bit, 16bit/8bit

- Dual Data Pointer

- Enhanced CPU core registers: AUXC, DPL1, DPH1, INSCON

The SH79F1621 has modified 'MUL' and 'DIV' instructions. These instructions support 16 bit operand. A new register - the register AUXC is applied to hold the upper part of the operand/result.

The AUXC register is used during 16 bit operand multiply and divide operations. For other instructions it can be treated as another scratch pad register.

After reset, the CPU is in standard mode, which means that the 'MUL' and 'DIV' instructions are operating like the standard 8051 instructions. To enable the 16 bit mode operation, the corresponding enable bit in the INSCON register must be set.

|     | Operation                 |              |                   | Result      |                    |

|-----|---------------------------|--------------|-------------------|-------------|--------------------|

|     | Operation                 |              | Α                 | В           | AUXC               |

| MUL | INSCON.2 = 0; 8 bit mode  | (A)*(B)      | Low Byte          | High Byte   |                    |

| MOL | INSCON.2 = 1; 16 bit mode | (AUXC A)*(B) | Low Byte          | Middle Byte | High Byte          |

| DIV | INSCON.3 = 0; 8 bit mode  | (A)/(B)      | Quotient Low Byte | Remainder   |                    |

| DIV | INSCON.3 = 1; 16 bit mode | (AUXC A)/(B) | Quotient Low Byte | Remainder   | Quotient High Byte |

#### **Dual Data Pointer**

Using two data pointers can accelerate data memory moves. The standard data pointer is called DPTR and the new data pointer is called DPTR1.

DPTR1 is similar to DPTR, which consists of a high byte (DPH1) and a low byte (DPL1). Its intended function is to hold a 16-bit address, but it may be manipulated as a 16-bit register or as two independent 8-bit registers.

The DPS bit in INSTCON register is used to choose the active pointer by setting 1 or 0. And all DPTR-related instructions will use the currently selected data pointer.

#### 7.1.3 Register

Table 7.2 Data Pointer Select Register

| 86H                              | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|----------------------------------|------|------|------|------|------|------|------|------|

| INSCON                           | -    | BKS0 | -    | -    | DIV  | MUL  | -    | DPS  |

| R/W                              | -    | R/W  | -    | -    | R/W  | R/W  | -    | R/W  |

| Reset Value<br>(POR/WDT/LVR/PIN) | -    | 0    | -    | -    | 0    | 0    | -    | 0    |

| Bit Number | Bit Mnemonic | Description                                                                           |

|------------|--------------|---------------------------------------------------------------------------------------|

| 6          | BKS0         | SFR Bank Selection Bit<br>0: SFR Bank0 selected<br>1: SFR Bank1 selected              |

| 3          | DIV          | <b>16 bit/8 bit Divide Selection Bit</b><br>0: 8 bit Divide<br>1: 16 bit Divide       |

| 2          | MUL          | <b>16 bit/8 bit Multiply Selection Bit</b><br>0: 8 bit Multiply<br>1: 16 bit Multiply |

| 0          | DPS          | Data Pointer Selection Bit<br>0: Data pointer<br>1: Data pointer1                     |

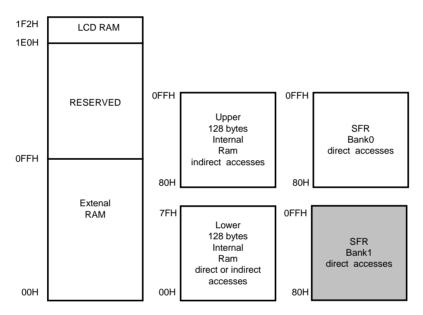

# 7.2 RAM

#### 7.2.1 Features

SH79F1621 provides both internal RAM and external RAM for random data storage. The internal data memory is mapped into four separated segments:

- The Lower 128 bytes of RAM (addresses 00H to 7FH) are directly and indirectly addressable.

- The Upper 128 bytes of RAM (addresses 80H to FFH) are indirectly addressable only.

- The Special Function Registers (SFR, addresses 80H to FFH) are directly addressable only.

- The 256 bytes of external RAM(addresses 00H to FFH) are indirectly accessed by MOVX instructions.

The Upper 128 bytes occupy the same address space as SFR, but they are physically separate from SFR space. When an instruction accesses an internal location above address 7FH, the CPU can distinguish whether to access the upper 128 bytes data RAM or to access SFR by different addressing mode of the instruction.

Note: the unused address is unavailable in SFR.

The Internal and External RAM Configuration

The SH79F1621 provides traditional method for accessing of external RAM. Use *MOVXA*, *@Ri* or *MOVX @Ri*, *A*; to access external low 256 bytes RAM; *MOVX A*, *@DPTR* or *MOVX @DPTR*, *A* also to access external 256 bytes RAM.

In SH79F1621 the user can also use XPAGE register to access external RAM only with *MOVX A*, *@Ri* or *MOVX @Ri*, *A* instructions. The user can use XPAGE to represent the high byte address of RAM above 256 Bytes.

But SH79F1621 only has 256 bytes external RAM, XPAGE must be set as 0.

In Flash SSP mode, the XPAGE can also be used as sector selector (Refer to SSP Function).

#### 7.2.2 Register

Table 7.3 Data Memory Page Register

| F7H                              | Bit7 | Bit6 | Bit5    | Bit4    | Bit3    | Bit2    | Bit1    | Bit0    |

|----------------------------------|------|------|---------|---------|---------|---------|---------|---------|

| XPAGE                            | -    | -    | XPAGE.5 | XPAGE.4 | XPAGE.3 | XPAGE.2 | XPAGE.1 | XPAGE.0 |

| R/W                              | -    | -    | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     |

| Reset Value<br>(POR/WDT/LVR/PIN) | -    | -    | 0       | 0       | 0       | 0       | 0       | 0       |

| Bit Number | Bit Mnemonic | Description       |

|------------|--------------|-------------------|

| 5-0        | XPAGE[5:0]   | RAM Page Selector |

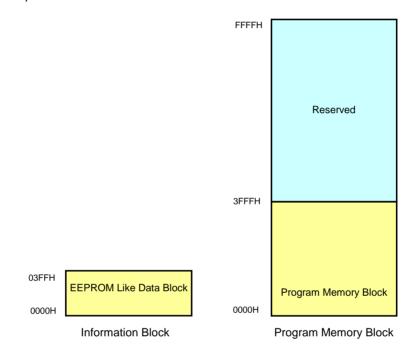

### 7.3 Flash Program Memory

#### 7.3.1 Features

- The program memory consists 16 X 1KB sectors, total 16KB

- Programming and erase can be done over the full operation voltage range

- Write, read and erase operation are all supported by In-Circuit Programming (ICP)

- Fast mass/sector erase and programming

- Minimum program/erase cycles: 100000

- Minimum years data retention: 10

- Low power consumption

The SH79F1621 embeds 16K flash program memory for program code. The flash program memory provides electrical erasure and programming and supports In-Circuit Programming (ICP) mode and Self-Sector Programming (SSP) mode.

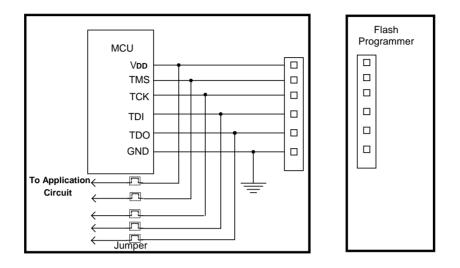

### 7.3.2 Flash Operation in ICP Mode

ICP mode is performed without removing the micro-controller from the system. In ICP mode, the user system must be power-off, and the programmer can refresh the program memory through ICP programming interface. The ICP programming interface consists of 6 wires (V<sub>DD</sub>, GND, TCK, TDI, TMS, TDO).

At first the four JTAG pins (TDO, TDI, TCK, TMS) are used to enter the programming mode. Only after the three pins are inputted the specified waveform, the CPU will enter the programming mode. For more detail description please refers to the FLASH Programmer's user guide.

#### The ICP mode supports the following operations:

#### (1) Code-Protect Control mode Programming

SH79F1621 implements code-protect function to offer high safeguard for customer code. Two modes are available for each sector.

Code-protect control mode 0: Used to enable/disable the write/read operation (except mass erase) from any programmer.

**Code-protect control mode 1:** Used to enable/disable the read operation through MOVC instruction from other sectors; or the sector erase/write operation through **SSP** Function.

To enable the wanted protect mode, the user must use the Flash Programmer to set the corresponding protect bit.

#### (2) Mass Erase

The mass erase operation will erase all the contents of program code, code option, code protect bit and customer code ID, regardless the status of code-protect control mode. (The Flash Programmer supplies customer code ID setting function for customer to distinguish their product.)

Mass erase is only available in Flash Programmer.

#### (3) Sector Erase

The sector erase operation will erase the contents of program code of selected sector . This operation can be done by Flash Programmer or the user's program.

If done by the Flash Programmer, the code-protect control mode 0 of the selected sector must be disabled.

#### (4) EEPROM-Like Erase

The EEPROM-Like erase operation will erase the contents of program code of EEPROM-Like. This operation can be done by Flash Programmer or the user's program.

#### (5) Write/Read Code

The Write/Read Code operation will write the customer code into the Flash Programming Memory or read the customer code from the Flash Programming Memory. This operation can be done by Flash Programmer or the user's program. If done by the user's program, the code-protect control mode 1 of the selected sector must be disabled. But the program can read/write its own sector regardless of its security bit.

If done by the Flash Programmer, the code-protect control mode 0 of the selected sector must be disabled.

#### (6) Write/Read EEPROM-Like

The Write/Read EEPROM-Like operation will write the customer data into the EEPROM-Like or read the customer data from the EEPROM-Like. This operation can be done by Flash Programmer or the user's program.

| Operation              | ICP                           | SSP                                             |

|------------------------|-------------------------------|-------------------------------------------------|

| Code Protection        | Yes                           | No                                              |

| Sector Erase           | Yes<br>(without security bit) | Yes<br>(without security bit)                   |

| Mass Erase             | Yes                           | No                                              |

| EEPROM-like Erase      | Yes                           | Yes                                             |

| Write/Read             | Yes<br>(without security bit) | Yes<br>(without security bit or its own sector) |

| EEPROM-like Write/Read | Yes                           | Yes                                             |

In ICP mode, all the flash operations are completed by the programmer through 6-wire interface. Since the program timing is very sensitive, five jumpers are needed ( $V_{DD}$ , TDO, TDI, TCK, TMS) to separate the program pins from the application circuit as the following diagram.

The recommended steps are as following:

- (1) The jumpers must be open to separate the programming pins from the application circuit before programming.

- (2) Connect the programming interface with programmer and begin programming.

- (3) Disconnect programmer and short these jumpers after programming is complete.

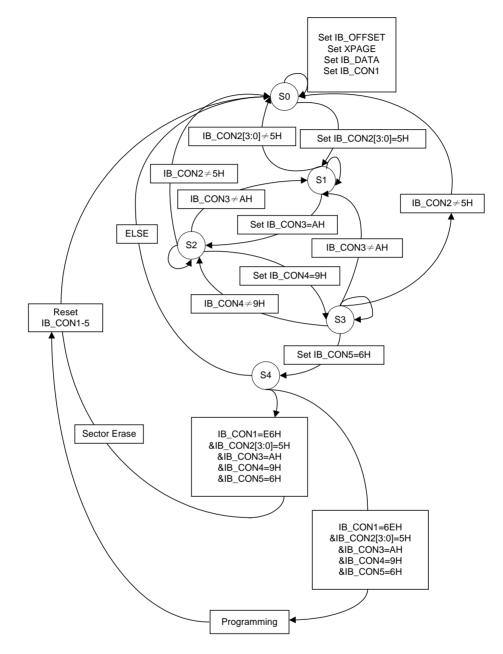

# 7.4 SSP Function

The SH79F1621 provides SSP (Self Sector Programming) function, each sector can be sector erased or programmed by the user's code if the selected sector is not be protected. But once sector has been programmed, it cannot be reprogrammed before sector erase.

The SH79F1621 builds in a complex control flow to prevent the code from carelessly modification. If the dedicated conditions are not met (IB\_CON2-5), the SSP will be terminated.

#### 7.4.1 SSP Register

Table 7.4 Offset Register for Programming

| F7H                              | Bit7 | Bit6 | Bit5    | Bit4    | Bit3    | Bit2    | Bit1    | Bit0    |

|----------------------------------|------|------|---------|---------|---------|---------|---------|---------|

| XPAGE                            | -    | -    | XPAGE.5 | XPAGE.4 | XPAGE.3 | XPAGE.2 | XPAGE.1 | XPAGE.0 |

| R/W                              | -    | -    | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     |

| Reset Value<br>(POR/WDT/LVR/PIN) | -    | -    | 0       | 0       | 0       | 0       | 0       | 0       |

### For Flash memory, one sector is 1024 bytes

| Bit Number | Bit Mnemonic | Description                                                                  |

|------------|--------------|------------------------------------------------------------------------------|

| 5-2        | XPAGE[5:2]   | Sector of the flash memory to be programmed, 000000means sector 0, and so on |

| 1-0        | XPAGE[1:0]   | High Address of Offset of the flash memory sector to be programmed           |

# For EEPROM-like memory, one sector is 256 bytes

| Bit Number | Bit Mnemonic | Description                                                              |

|------------|--------------|--------------------------------------------------------------------------|

| 5-2        | XPAGE[5:2]   | Reserved                                                                 |

| 1-0        | XPAGE[1:0]   | Sector of the flash memory to be programmed, 00means sector 0, and so on |

#### Table 7.5 Offset of Flash Memory for Programming

| FBH, Bank0                       | Bit7            | Bit6            | Bit5            | Bit4            | Bit3            | Bit2            | Bit1            | Bit0            |

|----------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| IB_OFFSET                        | IB_OFF<br>SET.7 | IB_OFF<br>SET.6 | IB_OFF<br>SET.5 | IB_OFF<br>SET.4 | IB_OFF<br>SET.3 | IB_OFF<br>SET.2 | IB_OFF<br>SET.1 | IB_OFF<br>SET.0 |

| R/W                              | R/W             | R/W             | R/W             | R/W             | R/W             | R/W             | R/W             | R/W             |

| Reset Value<br>(POR/WDT/LVR/PIN) | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0               |

| Bit Number | Bit Mnemonic   | Description                                                       |

|------------|----------------|-------------------------------------------------------------------|

| 7-0        | IB_OFFSET[7:0] | Low Address of Offset of the flash memory sector to be programmed |

#### Table 7.6 Data Register for Programming

| FCH, Bank0                       | Bit7      | Bit6      | Bit5      | Bit4      | Bit3      | Bit2      | Bit1      | Bit0      |

|----------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| IB_DATA                          | IB_DATA.7 | IB_DATA.6 | IB_DATA.5 | IB_DATA.4 | IB_DATA.3 | IB_DATA.2 | IB_DATA.1 | IB_DATA.0 |

| R/W                              | R/W       | R/W       | R/W       | R/W       | R/W       | R/W       | R/W       | R/W       |

| Reset Value<br>(POR/WDT/LVR/PIN) | 0         | 0         | 0         | 0         | 0         | 0         | 0         | 0         |

| Bit Number | Bit Mnemonic | Description           |

|------------|--------------|-----------------------|

| 7-0        | IB_DATA[7:0] | Data to be programmed |

# Table 7.7 SSP Type select Register

| F2H, Bank0                  | )     | Bit7      | Bit6                                                              | Bit5      | Bit4      | Bit3        | Bit2      | Bit1      | Bit0      |

|-----------------------------|-------|-----------|-------------------------------------------------------------------|-----------|-----------|-------------|-----------|-----------|-----------|

| IB_CON1                     |       | IB_CON1.7 | IB_CON1.6                                                         | IB_CON1.5 | IB_CON1.4 | IB_CON1.3   | IB_CON1.2 | IB_CON1.1 | IB_CON1.0 |

| R/W                         |       | R/W       | R/W                                                               | R/W       | R/W       | R/W         | R/W       | R/W       | R/W       |

| Reset Value<br>(POR/WDT/LVR |       | 0         | 0                                                                 | 0         | 0         | 0           | 0         | 0         | 0         |

| Bit Number                  | Bit N | Inemonic  |                                                                   |           | I         | Description |           |           |           |

| 7-0                         | IB_C  | ON1[7:0]  | SSP Type select<br>0xE6: Sector Erase<br>0x6E: Sector Programming |           |           |             |           |           |           |

# Table 7.8 SSP Flow Control Register1

| F3H, Bank0                  | )     | Bit7     | Bit6                                               | Bit5 | Bit4 | Bit3      | Bit2      | Bit1      | Bit0      |

|-----------------------------|-------|----------|----------------------------------------------------|------|------|-----------|-----------|-----------|-----------|

| IB_CON2                     |       | -        | -                                                  | -    | -    | IB_CON2.3 | IB_CON2.2 | IB_CON2.1 | IB_CON2.0 |

| R/W                         |       | -        | -                                                  | -    | -    | R/W       | R/W       | R/W       | R/W       |

| Reset Value<br>(POR/WDT/LVR | -     | -        | -                                                  | -    | -    | 0         | 0         | 0         | 0         |

| Bit Number                  | Bit N | Inemonic | Description                                        |      |      |           |           |           |           |

| 3-0                         | IB_C  | ON2[3:0] | Must be 05H, else Flash Programming will terminate |      |      |           |           |           |           |

# Table 7.9 SSP Flow Control Register2

| F4H, Bank0                  | )     | Bit7     | Bit6                                              | Bit5 | Bit4 | Bit3      | Bit2      | Bit1      | Bit0      |

|-----------------------------|-------|----------|---------------------------------------------------|------|------|-----------|-----------|-----------|-----------|

| IB_CON3                     |       | -        | -                                                 | -    | -    | IB_CON3.3 | IB_CON3.2 | IB_CON3.1 | IB_CON3.0 |

| R/W                         |       | -        | -                                                 | -    | -    | R/W       | R/W       | R/W       | R/W       |

| Reset Value<br>(POR/WDT/LVR | -     | -        | -                                                 | -    | -    | 0         | 0         | 0         | 0         |

| Bit Number                  | Bit N | Inemonic | Description                                       |      |      |           |           |           |           |

| 3-0                         | IB_C  | ON3[3:0] | Must be 0AH else Flash Programming will terminate |      |      |           |           |           |           |

# Table 7.10 SSP Flow Control Register3

| F5H, Bank0                    | Bit7         | Bit6 | Bit5 | Bit4 | Bit3        | Bit2      | Bit1      | Bit0      |

|-------------------------------|--------------|------|------|------|-------------|-----------|-----------|-----------|

| IB_CON4                       | -            | -    | -    | -    | IB_CON4.3   | IB_CON4.2 | IB_CON4.1 | IB_CON4.0 |

| R/W                           | -            | -    | -    | -    | R/W         | R/W       | R/W       | R/W       |

| Reset Value<br>(POR/WDT/LVR/F | PIN) -       | -    | -    | -    | 0           | 0         | 0         | 0         |

| Bit Number                    | Bit Mnemonic |      |      |      | Description |           |           |           |

| 3-0 | IB_CON4[3:0] | Must be 09H, else Flash Programming will terminate |

|-----|--------------|----------------------------------------------------|

|-----|--------------|----------------------------------------------------|

# Table 7.11 SSP Flow Control Register4

| F6H, Bank(                  | )     | Bit7     | Bit6        | Bit5                                               | Bit4 | Bit3      | Bit2      | Bit1      | Bit0      |

|-----------------------------|-------|----------|-------------|----------------------------------------------------|------|-----------|-----------|-----------|-----------|

| IB_CON5                     |       | -        | -           | -                                                  | -    | IB_CON5.3 | IB_CON5.2 | IB_CON5.1 | IB_CON5.0 |

| R/W                         |       | -        | -           | -                                                  | -    | R/W       | R/W       | R/W       | R/W       |

| Reset Value<br>(POR/WDT/LVR |       | -        | -           | -                                                  | -    | 0         | 0         | 0         | 0         |

| Bit Number                  | Bit N | Inemonic | Description |                                                    |      |           |           |           |           |

| 3-0                         | IB_C  | ON5[3:0] | Must be 06H | Must be 06H, else Flash Programming will terminate |      |           |           |           |           |

# 7.4.2 Flash Control Flow

# 7.4.3 SSP Programming Notice

To successfully complete SSP programming, the user's software must following the steps below:

#### (1) For Code/Data Programming:

- 1. Disable interrupt;

- 2. Fill in the XPAGE, IB\_OFFSET for the corresponding address;

- 3. Fill in IB\_DATA if programming is wanted;

- 4. Fill in IB\_CON1-5 sequentially;

- 5. Add 4 nops for more stable operation;

- 6. Code/Data programming, CPU will be in IDLE mode;

- 7. Go to Step 2 if more data are to be programmed;

- 8. Clear XPAGE; enable interrupt if necessary.

#### (2) For Sector Erase:

- 1. Disable interrupt;

- 2. Fill in the XPAGE for the corresponding sector;

- 3. Fill in IB\_CON1-5 sequentially;

- 4. Add 4 NOPs for more stable operation;

- 5. Sector Erase, CPU will be in IDLE mode;

- 6. Go to step 2 if more sectors are to be erased;

- 7. Clear XPAGE; enable interrupt if necessary.

#### (3) For Code Reading:

Just Use "MOVC A, @A+DPTR" or "MOVC A, @A+PC".

#### (4) For EEPROM-Like:

Steps is same as code programming, the diffenrences are:

1.Set FAC bit in FLASHCON register before programming or erase EEPROM-Like;

2.One sector of EEPROM-Like is 256 bytes.not 1024 bytes.

Table 7.12 Flash Access Control Register

| A7H, Bank0                       | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|----------------------------------|------|------|------|------|------|------|------|------|

| FLASHCON                         | -    | -    | -    | -    | -    | -    | -    | FAC  |

| R/W                              | -    | -    | -    | -    | -    | -    | -    | R/W  |

| Reset Value<br>(POR/WDT/LVR/PIN) | -    | -    | -    | -    | -    | -    | -    | 0    |

| Bit Number | Bit Mnemonic | Description                                                                                         |

|------------|--------------|-----------------------------------------------------------------------------------------------------|

| 0          | FAC          | FAC: Flash access control<br>0: MOVC or SSP access main memory<br>1: MOVC or SSP access EEPROM-like |

#### 7.5 System Clock and Oscillator

#### 7.5.1 Features

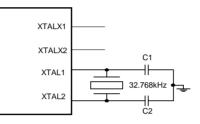

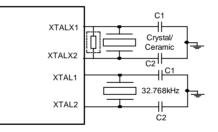

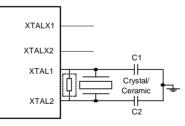

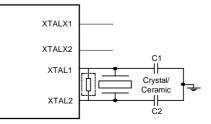

- Four oscillator types: 32.768kHz crystal, crystal oscillator, ceramic oscillator and 12MHz/128kHz internal RC

- 4 Oscillator pin (XTAL1, XTAL2, XTALX1, XTALX2)

- Built-in 12MHz Internal RC

- Built-in 32.768kHz speed up circuit

- Built-in system clock prescaler

#### 7.5.2 Clock Definition

The SH79F1621 have several internal clocks defined as below:

**OSCCLK:** the oscillator clock from one of the four oscillator types (32.768kHz crystal oscillator, crystal oscillator, ceramic oscillator and interal RC) fosc is defined as the OSCCLK frequency. tosc is defined as the OSCCLK period.

**OSCXCLK:** the oscillator clock from one of the three oscillator types (crystal oscillator, ceramic oscillator and interal RC) f<sub>OSCx</sub> is defined as the OSCXCLK frequency. t<sub>OSCX</sub> is defined as the OSCXCLK period.

**Note:** OSCXCLK does not exist when code option OP\_OSC is not 0011, 0110, 1010, 1101. (32.768kHz oscillator/128kHz internal RC is not selected, Refer to **code option** section for details)

WDTCLK: the internal WDT RC clock. f<sub>WDT</sub> is defined as the WDTCLK frequency. t<sub>WDT</sub> is defined as the WDTCLK period.

**OSCSCLK:** the input of system clock prescaler. It can be OSCCLK or OSCXCLK. f<sub>OSCS</sub> is defined as the OSCSCLK frequency. t<sub>OSCS</sub> is defined as the OSCSCLK period.

**SYSCLK:** system clock, the output of system clock prescaler. It is the CPU instruction clock.  $f_{SYS}$  is defined as the SYSCLK frequency.  $t_{SYS}$  is defined as the SYSCLK period.

#### 7.5.3 Description

SH79F1621 has four oscillator types: 32.768kHz crystal oscillator, crystal oscillator (2MHz-12MHz), ceramic Oscillator (2MHz-12MHz) and internal RC (12MHz,), which is selected by code option OP\_OSC (Refer to code option section for details). SH79F1621 have 4 Oscillator pin (XTAL1, XTAL2, XTALX1, XTALX2) and can generates one or two clock sources from four oscillator types. It is selected by code option OP\_OSC (Refer to **code option** section for details). The oscillator generates the basic clock pulse that provides the system clock to supply CPU and on-chip peripherals.

# 7.5.4 Register

Table 7.13 System Clock Control Register

| B2H, Bank0                       | Bit7      | Bit6  | Bit5  | Bit4  | Bit3 | Bit2 | Bit1 | Bit0 |

|----------------------------------|-----------|-------|-------|-------|------|------|------|------|

| CLKCON                           | 32k_SPDUP | CLKS1 | CLKS0 | SCMIF | HFON | FS   | -    | -    |

| R/W                              | R/W       | R/W   | R/W   | R     | R/W  | R/W  | -    | -    |

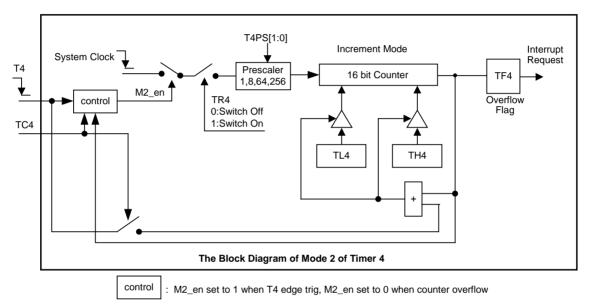

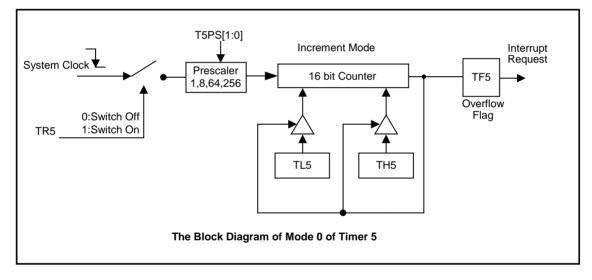

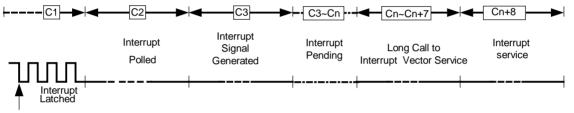

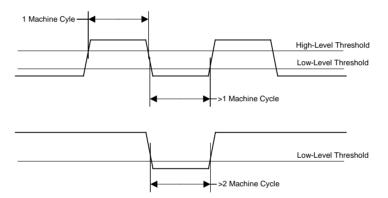

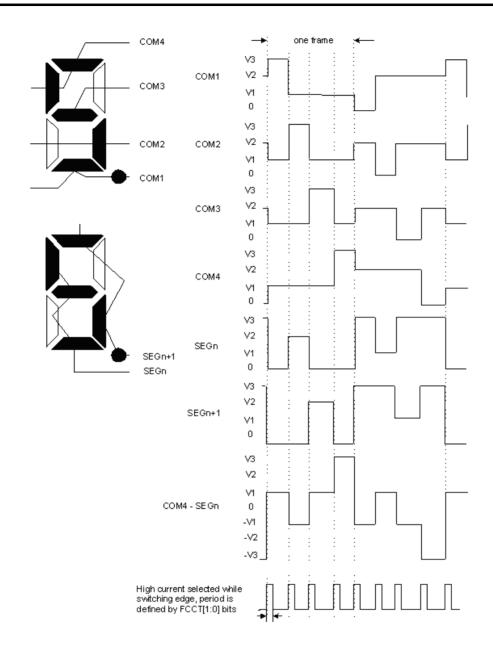

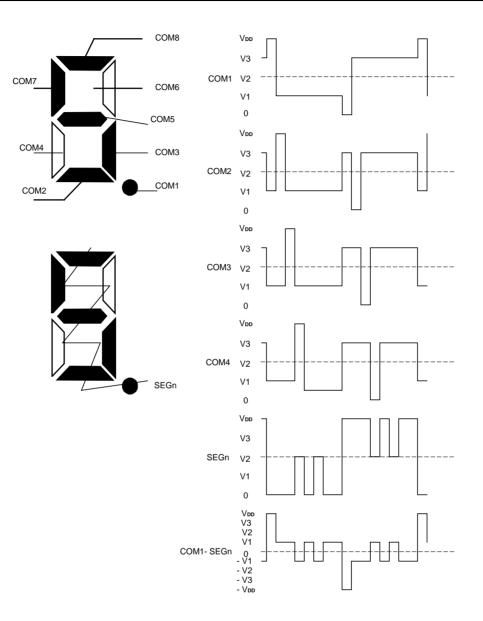

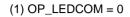

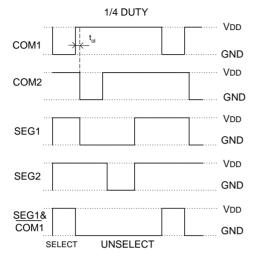

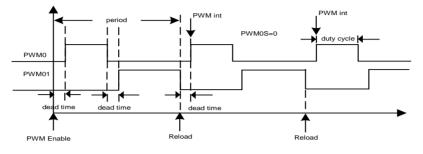

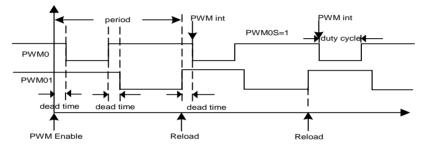

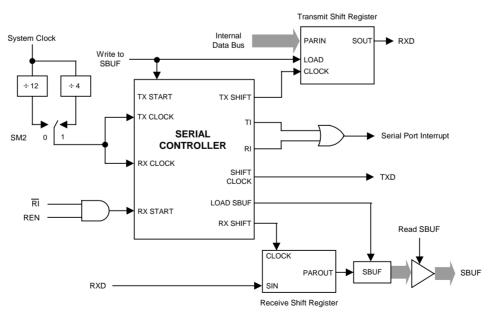

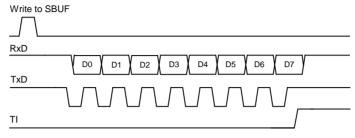

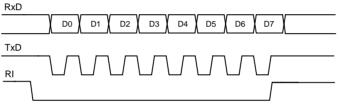

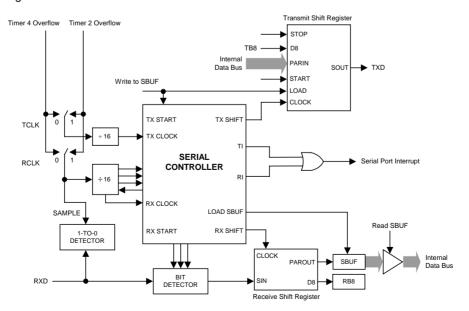

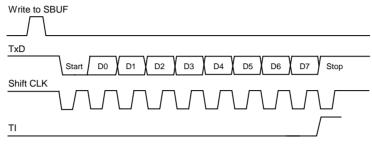

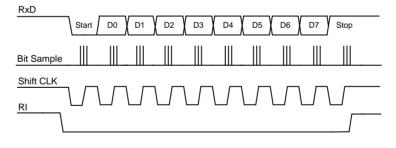

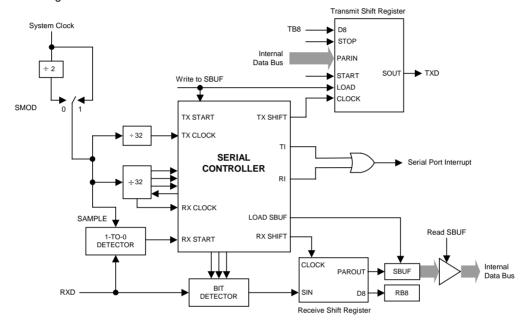

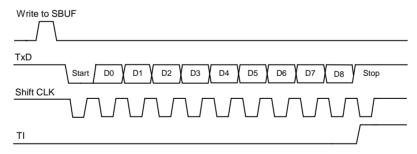

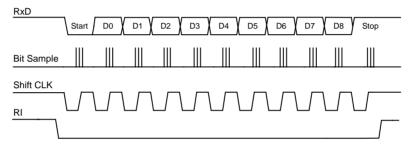

| Reset Value<br>(POR/WDT/LVR/PIN) | 1         | 1     | 1     | 0     | 0    | 0    | -    | -    |