# SH7722

Renesas 32-Bit RISC Microcomputer SH7780 Series R8A7722

-Preliminary -

#### Notes regarding these materials

- 1. This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

- 2. Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

- 3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

- 4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas products listed in this document, please confirm the latest product information with a Renesas sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas such as that disclosed through our website. (http://www.renesas.com)

- Renesas has used reasonable care in compiling the information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document.

- 6. When using or otherwise relying on the information in this document, you should evaluate the information in light of the total system before deciding about the applicability of such information to the intended application. Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products.

- 7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which require especially high quality and reliability such as safety systems, or equipment or systems for transportation and traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication transmission. If you are considering the use of our products for such purposes, please contact a Renesas sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

- 8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below:

(1) artificial life support devices or systems

- (2) aurainal implantations

- (2) surgical implantations

- (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life

- Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas Technology Corp., its affiliated companies and their officers, directors, and employees against any and all damages arising out of such applications.

- 9. You should use the products described herein within the range specified by Renesas, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or damages arising out of the use of Renesas products beyond such specified ranges.

- 10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 11. In case Renesas products listed in this document are detached from the products to which the Renesas products are attached or affixed, the risk of accident such as swallowing by infants and small children is very high. You should implement safety measures so that Renesas products may not be easily detached from your products. Renesas shall have no liability for damages arising out of such detachment.

- 12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from Renesas.

- 13. Please contact a Renesas sales office if you have any questions regarding the information contained in this document, Renesas semiconductor products, or if you have any other inquiries.

## **General Precautions on Handling of Product**

#### 1. Treatment of NC Pins

Note: Do not connect anything to the NC pins.

The NC (not connected) pins are either not connected to any of the internal circuitry or are used as test pins or to reduce noise. If something is connected to the NC pins, the operation of the LSI is not guaranteed.

#### 2. Treatment of Unused Input Pins

Note: Fix all unused input pins to high or low level.

Generally, the input pins of CMOS products are high-impedance input pins. If unused pins are in their open states, intermediate levels are induced by noise in the vicinity, a pass-through current flows internally, and a malfunction may occur.

#### 3. Processing before Initialization

Note: When power is first supplied, the product's state is undefined.

The states of internal circuits are undefined until full power is supplied throughout the chip and a low level is input on the reset pin. During the period where the states are undefined, the register settings and the output state of each pin are also undefined. Design your system so that it does not malfunction because of processing while it is in this undefined state. For those products which have a reset function, reset the LSI immediately after the power supply has been turned on.

#### 4. Prohibition of Access to Undefined or Reserved Addresses

Note: Access to undefined or reserved addresses is prohibited.

The undefined or reserved addresses may be used to expand functions, or test registers may have been be allocated to these addresses. Do not access these registers; the system's operation is not guaranteed if they are accessed.

#### 5. Reading from/Writing Reserved Bit of Each Register

Note: Treat the reserved bit of register used in each module as follows except in cases where the specifications for values which are read from or written to the bit are provided in the description.

The bit is always read as 0. The write value should be 0 or one, which has been read immediately before writing.

Writing the value, which has been read immediately before writing has the advantage of preventing the bit from being affected on its extended function when the function is assigned.

## **Preface**

This LSI is a RISC (Reduced Instruction Set Computer) microcomputer which includes a Renesas Technology-original RISC CPU as its core, and the peripheral functions required to configure a system. This LSI includes the SH4AL-DSP extended functions that have functional upward compatibility with the SH4AL-DSP.

Target Users: This manual was written for users who will be using this LSI in the design of

application systems. Users of this manual are expected to understand the fundamentals of electrical circuits, logical circuits, and microcomputers.

Objective: This manual was written to explain the hardware functions and electrical

characteristics of this LSI to the above users.

Note: This data sheet contains references to the SH7722 Hardware Manual. The contents of the

SH7722 Hardware Manual will be disclosed upon acceptance of a confidentiality agreement. For details, please contact a Renesas Technology sales representative.

#### Abbreviations

ALU Arithmetic Logic Unit

ASID Address Space Identifier

BSC Bus State Controller

CMT Compare Match Timer

CPG Clock Pulse Generator

CPU Central Processing Unit

DMA Direct Memory Access

DMAC Direct Memory Access Controller

DSP Digital Signal Processor

ETU Elementary Time Unit

FIFO First-In First-Out

FLCTL Flash Memory Controller

H-UDI User Debugging Interface

IIC Inter IC Bus

INTC Interrupt Controller

JTAG Joint Test Action Group

KEYSC Key Scan Interface

LCDC LCD Controller

LRU Least Recently Used

LSB Least Significant Bit

MMC Multi Media Card

MMU Memory Management Unit

MSB Most Significant Bit

PC Program Counter

PFC Pin Function Controller

RISC Reduced Instruction Set Computer

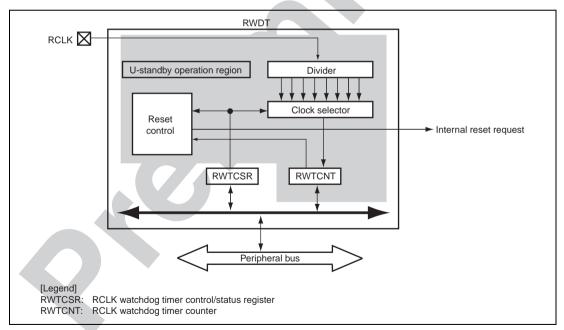

RWDT RCLK Watchdog Timer

SBSC SDRAM Bus State Controller

SCIF Serial Communication Interface with FIFO

SIO Serial Interface

SIOF Serial Interface with FIFO

SIU Sound Interface Unit

TAP Test Access Port

TLB Translation Lookaside Buffer

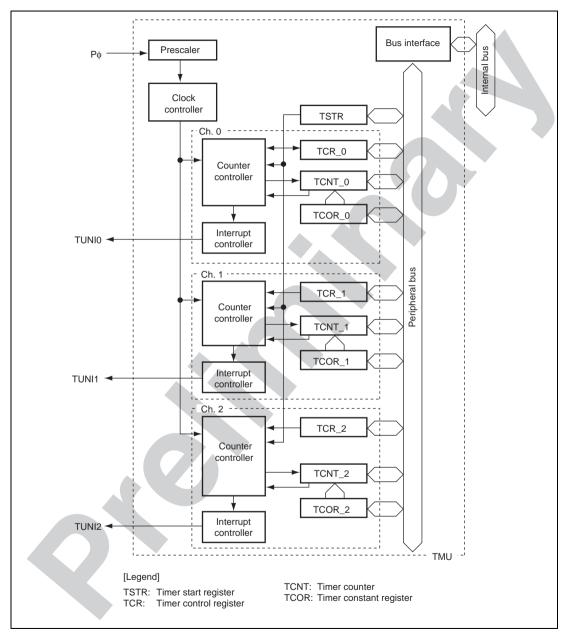

TMU Timer Unit

UART Universal Asynchronous Receiver/Transmitter

UBC User Break Controller

VIO Video I/O

VOU Video Output Unit

VPU Video Processing Unit

All trademarks and registered trademarks are the property of their respective owners.

## Content

| Sect | tion 1 O      | verview                                   | 1  |

|------|---------------|-------------------------------------------|----|

| 1.1  | Feature       | es                                        | 1  |

| 1.2  | Block Diagram |                                           |    |

| 1.3  | Pin Ass       | signments                                 |    |

|      | 1.3.1         | BGA-449 Pin Assignments                   | 15 |

|      | 1.3.2         | BGA-417 Pin Assignments                   | 33 |

| 1.4  | Pin Fu        | nctions                                   | 51 |

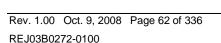

| Sect | tion 2 D      | SP Unit                                   | 63 |

| 2.1  | Overvi        | ew                                        | 63 |

| Sect | tion 3 M      | lemory Management Unit (MMU)              | 67 |

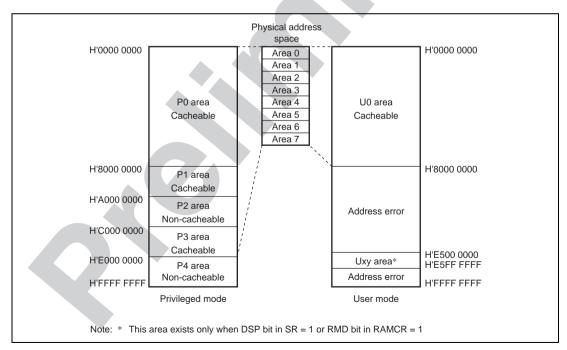

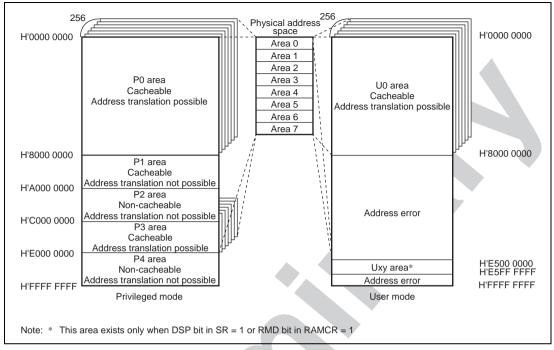

| 3.1  | Overvi        | ew of MMU                                 | 68 |

|      | 3.1.1         | Address Spaces                            | 70 |

| Sect | tion 4 Ca     | aches                                     | 77 |

| 4.1  | Feature       | es                                        | 77 |

| Sect | tion 5 O      | n-Chip Memory                             | 81 |

| 5.1  | Feature       | es                                        | 81 |

| Sect | tion 6 In     | terrupt Controller (INTC)                 | 85 |

| 6.1  | Feature       | es                                        | 85 |

| 6.2  | Input/C       | Output Pins                               | 87 |

| 6.3  | Interru       | pt Sources                                | 88 |

|      | 6.3.1         | NMI Interrupt                             | 88 |

|      | 6.3.2         | IRQ Interrupts                            | 88 |

|      | 6.3.3         | On-Chip Peripheral Module Interrupts      | 89 |

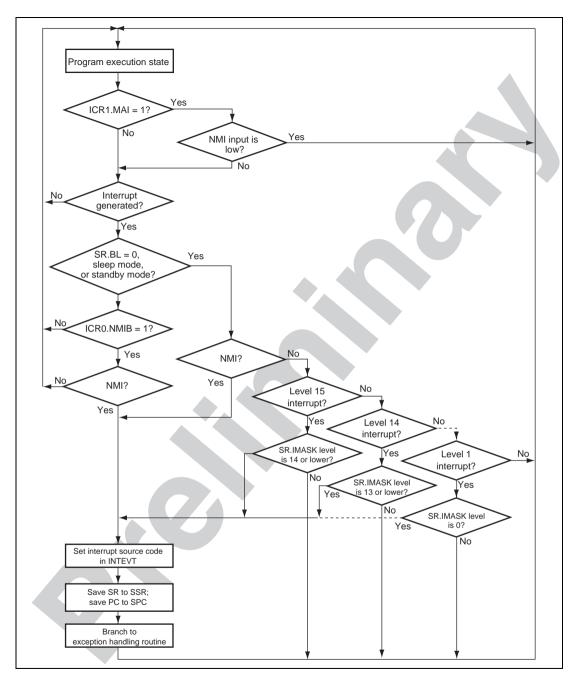

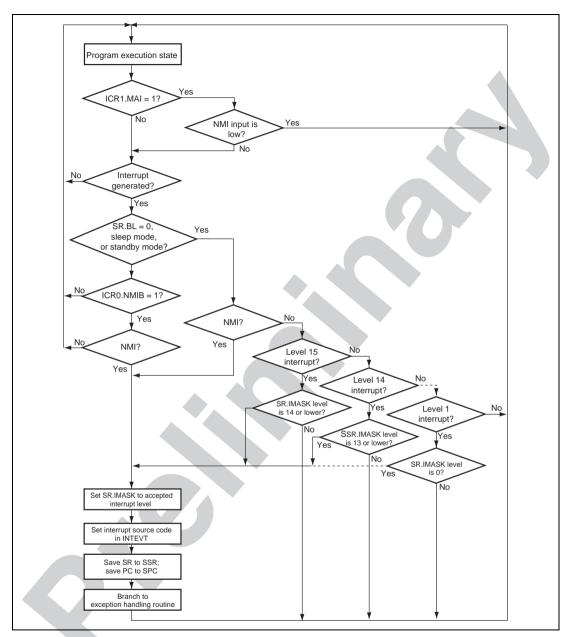

|      | 6.3.4         | Interrupt Exception Handling and Priority | 90 |

| 6.4  | Operation     |                                           | 93 |

|      | 6.4.1         | Interrupt Sequence                        | 93 |

|      | 6.4.2         | Multiple Interrupts                       | 96 |

|      | 6.4.3         | Interrupt Masking by MAI Bit              |    |

|      | 6.4.4         | Interrupt Disabling Function in User Mode | 97 |

| 6.5  | Interru       | pt Response Time                          | 98 |

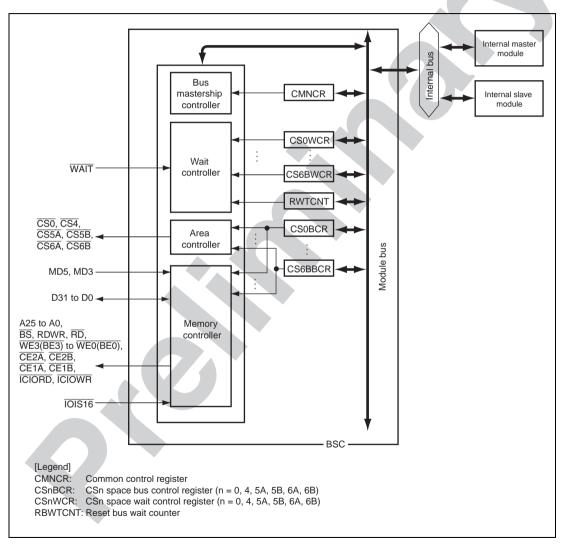

| Secti | ion 7 Bı | us State Controller (BSC)            | 99  |

|-------|----------|--------------------------------------|-----|

| 7.1   |          | S                                    |     |

| 7.2   | Input/C  | Output Pins                          | 101 |

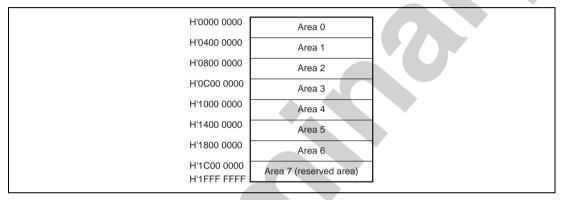

| 7.3   | Area O   | verview                              | 103 |

|       | 7.3.1    | Area Division                        | 103 |

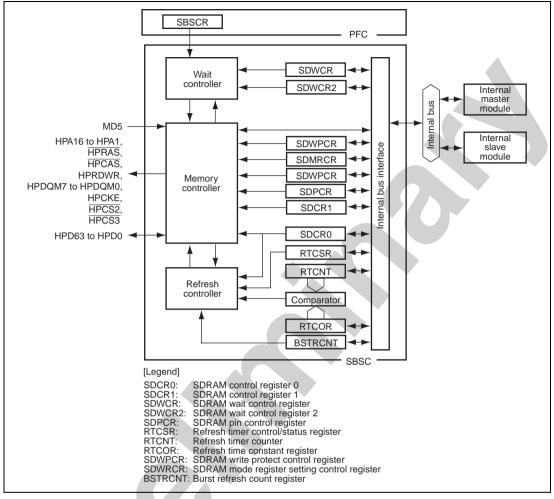

| Secti | ion 8 Bı | us State Controller for SDRAM (SBSC) | 105 |

| 8.1   | Feature  | S                                    | 105 |

| 8.2   | Input/C  | Output Pins                          | 107 |

| 8.3   | Area O   | verview                              | 108 |

|       | 8.3.1    | Address Map                          | 108 |

|       | 8.3.2    | Memory Bus Width                     | 109 |

|       | 8.3.3    | Data Alignment                       | 109 |

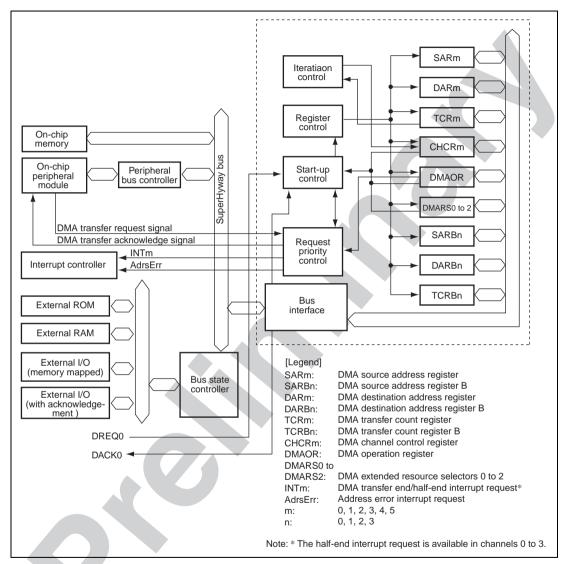

| Secti | ion 9 Di | rect Memory Access Controller (DMAC) | 111 |

| 9.1   |          | ·s                                   |     |

| 9.2   | Input/C  | Output Pins                          | 113 |

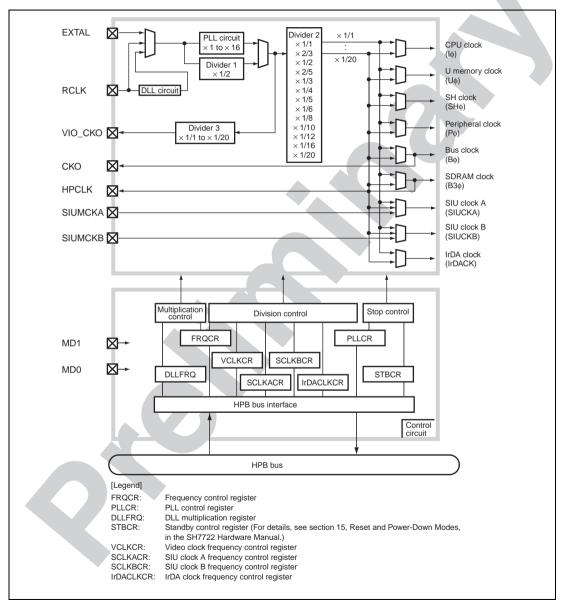

| Secti | ion 10 C | Clock Pulse Generator (CPG)          | 115 |

| 10.1  |          | es                                   |     |

| 10.2  |          | Diagram                              |     |

| 10.3  |          | Output Pins                          |     |

| Secti | ion 11 R | Reset and Power-Down Modes           | 119 |

| 11.1  |          | es                                   |     |

| 11.1  | 11.1.1   | Division of Power-Supply Areas       |     |

|       | 11.1.1   | Types of Resets and Power-Down Modes |     |

| 11.2  |          | Output Pins                          |     |

| 11.2  | Input/C  | 74tput 1 1115                        | 121 |

| Secti | ion 12 R | RCLK Watchdog Timer (RWDT)           | 123 |

| 12.1  | Feature  | S                                    | 123 |

| 12.2  | Input/C  | Output Pins for RWDT                 | 124 |

| Secti | ion 13 T | Cimer Unit (TMU)                     | 125 |

| 13.1  |          | ss                                   |     |

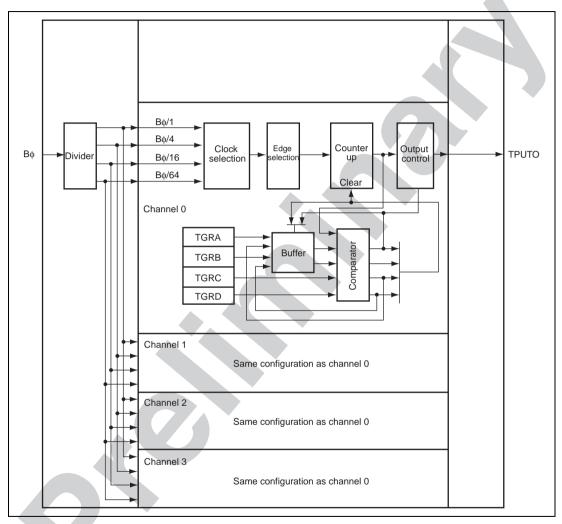

| Secti | ion 14 1 | 6-Bit Timer Pulse Unit (TPU)         | 127 |

| 14.1  |          | es                                   |     |

| 14.2  |          | Diagram                              |     |

| 14.3  |          | Output Pin                           |     |

|       | 1        | ±                                    |     |

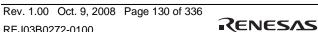

| Secti        | on 15 Compare Match Timer (CMT)                       | 131 |

|--------------|-------------------------------------------------------|-----|

| 15.1         | Features                                              | 131 |

| C4           | 16 9 - 16 9 - 1 1 10 (910)                            | 122 |

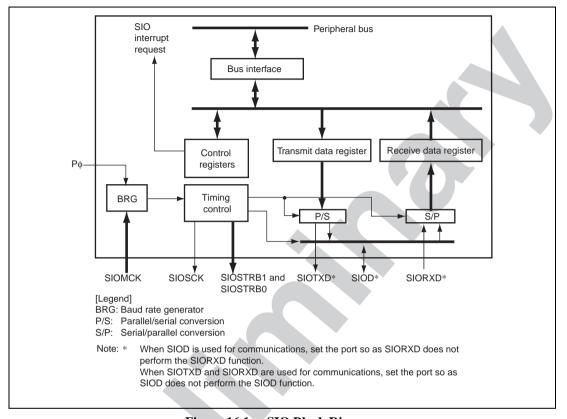

|              | on 16 Serial I/O (SIO)                                |     |

| 16.1         | Features                                              |     |

| 16.2         | Input/Output Pins                                     | 135 |

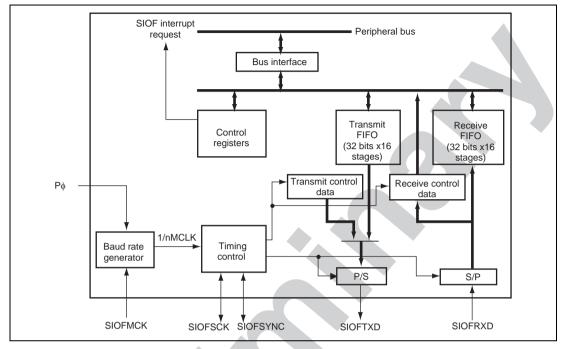

| Secti        | on 17 Serial I/O with FIFO (SIOF)                     | 137 |

| 17.1         | Features                                              |     |

| 17.2         | Input/Output Pins                                     | 139 |

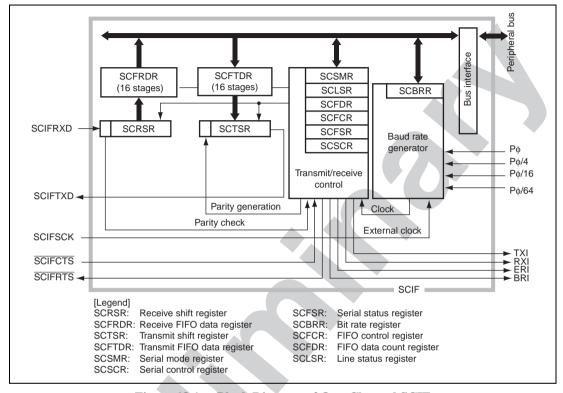

| Secti        | on 18 Serial Communication Interface with FIFO (SCIF) | 141 |

| 18.1         | Features                                              |     |

| 18.2         | Input/Output Pins                                     |     |

| 10.2         | input Output I ins                                    |     |

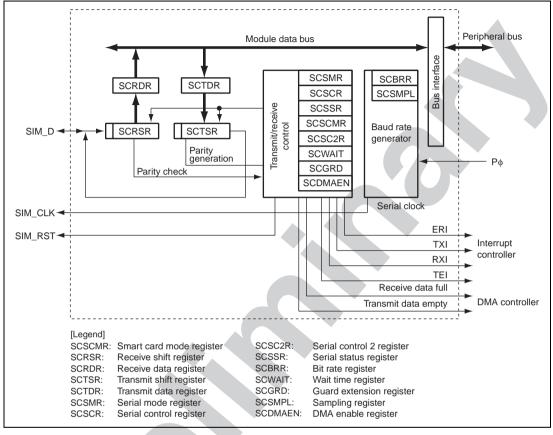

| Secti        | on 19 SIM Card Module (SIM)                           | 145 |

| 19.1         | Features                                              | 145 |

| 19.2         | Input/Output Pins                                     | 147 |

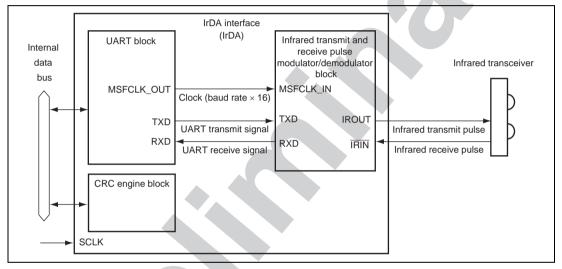

| Secti        | on 20 IrDA Interface (IrDA)                           | 149 |

| 20.1         | Features                                              |     |

| 20.2         | Input/Output Pins                                     |     |

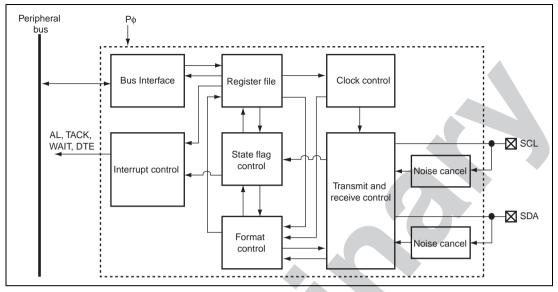

| Coot         | ion 21 I <sup>2</sup> C Bus Interface (IIC)           | 151 |

| 3ecu<br>21.1 | ` /                                                   |     |

|              | Features.                                             |     |

| 21.2         | Input/Output Pins                                     | 153 |

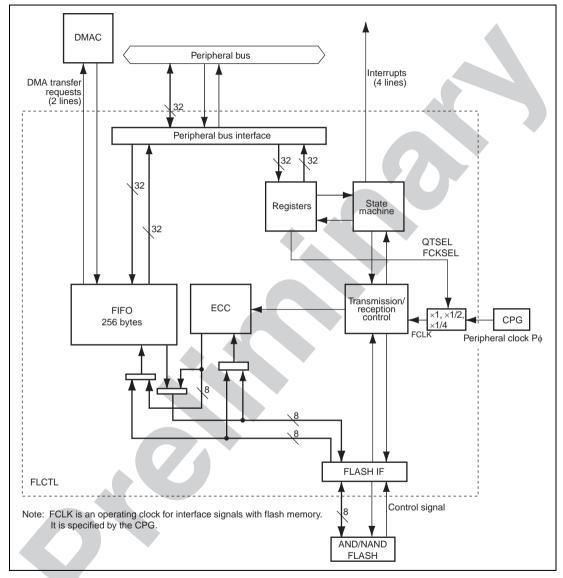

| Secti        | ion 22 AND/NAND Flash Memory Controller (FLCTL)       | 155 |

| 22.1         | Features                                              |     |

| 22.2         | Input/Output Pins                                     | 160 |

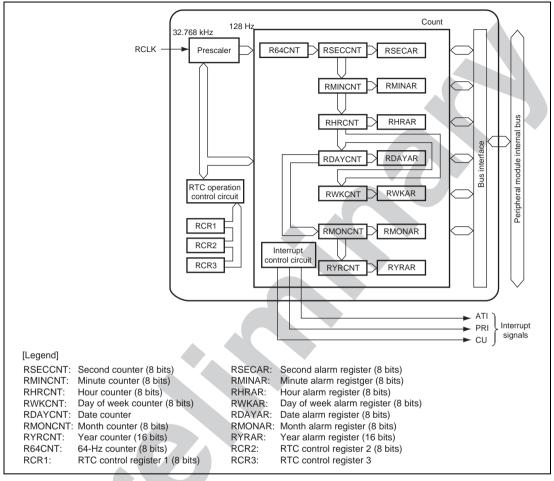

| Secti        | on 23 Realtime Clock (RTC)                            | 161 |

| 23.1         | Features                                              |     |

| 23.1         | Input/Output Pin                                      |     |

| 23.2         | Input/Output 1 in                                     | 103 |

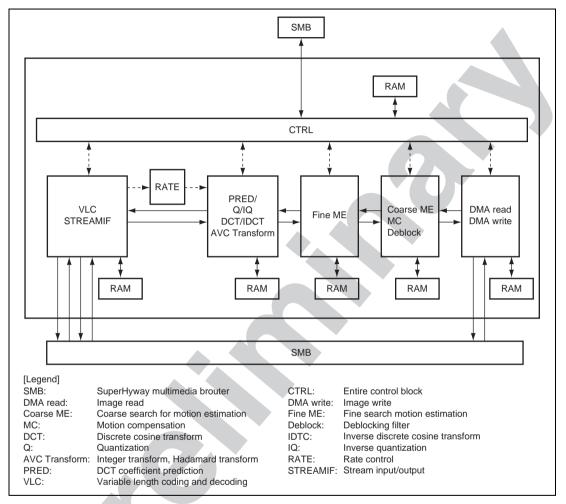

| Secti        | on 24 Video Processing Unit (VPU)                     | 165 |

| 24.1         | Features                                              |     |

| Secti        | on 25 Video I/O (VIO)                                 | 171 |

| 25.1         | Features                                              |     |

|              |                                                       |     |

| 25.2  | Functional Overview of CEU           | 174 |

|-------|--------------------------------------|-----|

| 25.3  | Pin Configuration of CEU             | 177 |

| Secti | ion 26 JPEG Processing Unit (JPU)    | 179 |

| 26.1  | Features                             |     |

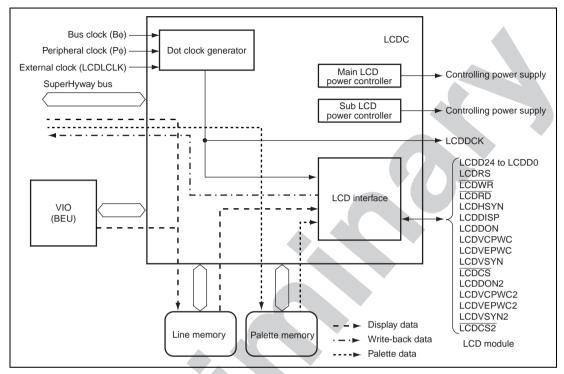

| Secti | ion 27 LCD Controller (LCDC)         | 181 |

| 27.1  | Features                             | 181 |

| 27.2  | Input/Output Pins                    |     |

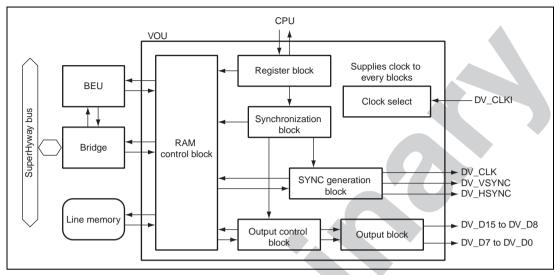

| Secti | ion 28 Video Output Unit (VOU)       | 187 |

| 28.1  | Features                             |     |

| 28.2  | Pin Configuration                    | 189 |

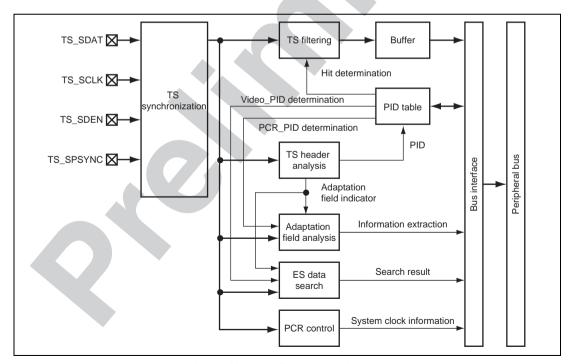

| Secti | ion 29 TS Interface (TSIF)           | 191 |

| 29.1  | Features                             | 191 |

| 29.2  | Input/Output Pins                    | 193 |

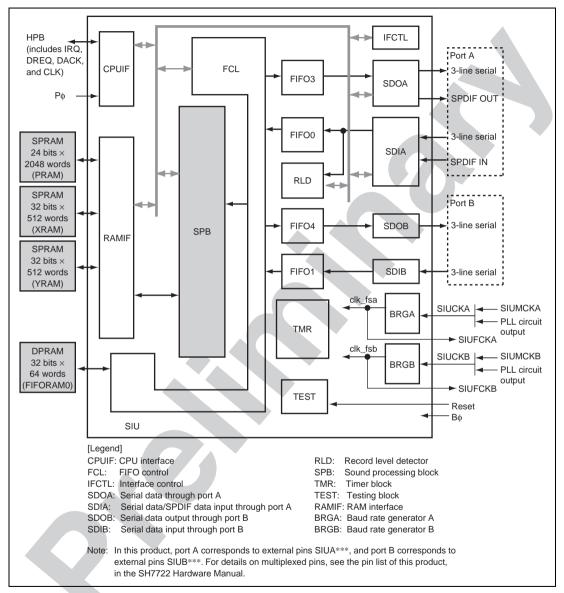

| Secti | ion 30 Sound Interface Unit (SIU)    | 195 |

| 30.1  | Features                             | 195 |

|       | 30.1.1 RAM Overview                  | 201 |

| 30.2  | Input/Output Pins                    | 202 |

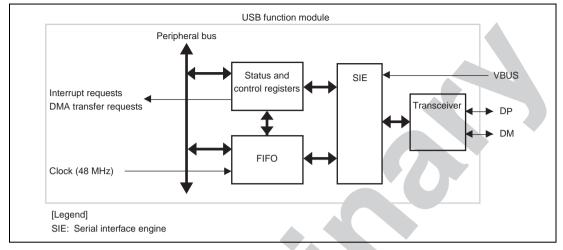

| Secti | ion 31 USB Function Module (USBF)    | 205 |

| 31.1  | Features                             |     |

| 31.2  | Input / Output Pins                  |     |

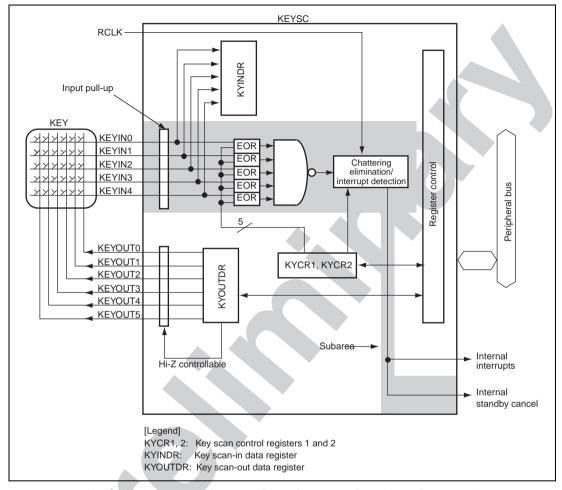

| Secti | ion 32 Key Scan Interface (KEYSC)    | 209 |

| 32.1  | Features                             |     |

| 32.2  | Input/Output Pins                    | 211 |

| Secti | ion 33 2D Graphics Accelerator (2DG) | 213 |

| 33.1  | Features                             |     |

| Secti | ion 34 Pin Function Controller (PFC) | 215 |

| 34.1  | Overview                             |     |

| Secti | ion 35 I/O Ports                     | 223 |

| 35.1  | Port A                               | 223 |

| 35.2  |                                      |     |

| 35.3    | Port C   |                                 | 224 |

|---------|----------|---------------------------------|-----|

| 35.4    | Port D   |                                 | 225 |

| 35.5    | Port E   |                                 | 225 |

| 35.6    | Port F   |                                 | 226 |

| 35.7    | Port G   |                                 | 227 |

| 35.8    | Port H   |                                 | 227 |

| 35.9    | Port J   |                                 | 228 |

| 35.10   | Port K   |                                 | 228 |

| 35.11   | Port L   |                                 | 229 |

| 35.12   | Port M   |                                 | 229 |

| 35.13   | Port N   |                                 | 230 |

| 35.14   | Port Q   |                                 | 230 |

| 35.15   | Port R   |                                 | 231 |

| 35.16   | Port S   |                                 | 231 |

| 35.17   | Port T   |                                 | 232 |

| 35.18   | Port U   |                                 | 232 |

| 35.19   | Port V   |                                 | 233 |

| 35.20   | Port W   |                                 | 233 |

| 35.21   | Port X   |                                 | 234 |

| 35.22   | Port Y   |                                 | 234 |

| 35.23   | Port Z   |                                 | 235 |

|         |          |                                 |     |

| Section |          | ser Break Controller (UBC)      |     |

| 36.1    | Features |                                 | 237 |

| a .     | 05.11    |                                 | 220 |

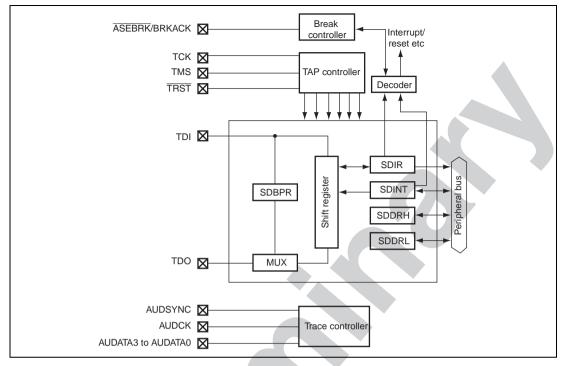

|         |          | ser Debugging Interface (H-UDI) |     |

| 37.1    |          |                                 |     |

| 37.2    | Input/Ou | tput Pins                       | 240 |

| C = =4: | on 20 El | a atui a al Chaus ataui ati a a | 242 |

|         |          | ectrical Characteristics        |     |

| 38.1    |          | Maximum Ratings                 |     |

| 38.2    |          | ended Operating Conditions      |     |

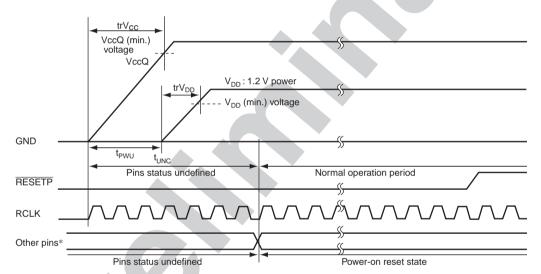

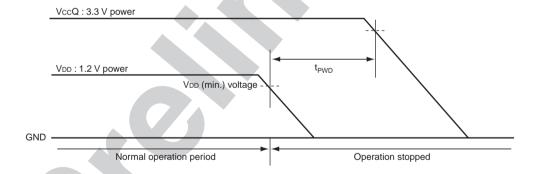

| 38.3    |          | on and Power-Off Order          |     |

| 38.4    |          | racteristics                    |     |

| 38.5    |          | racteristics                    |     |

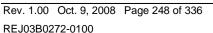

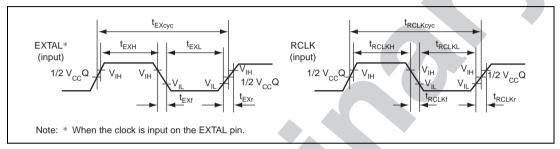

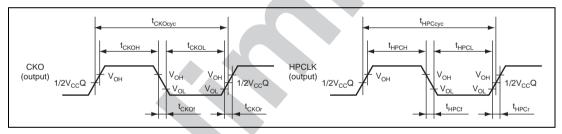

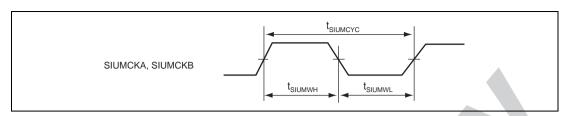

|         | 38.5.1   | Clock Timing                    |     |

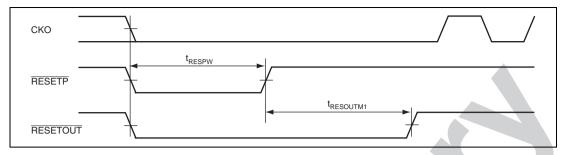

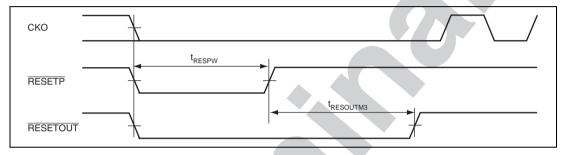

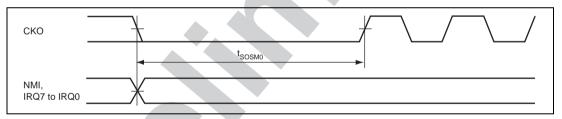

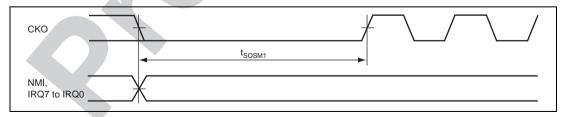

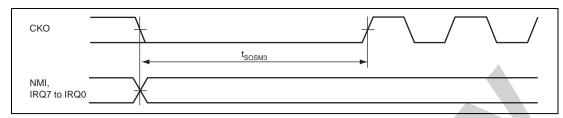

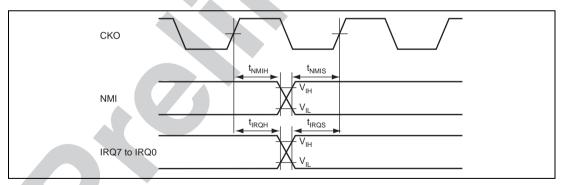

|         | 38.5.2   | Interrupt Signal Timing         |     |

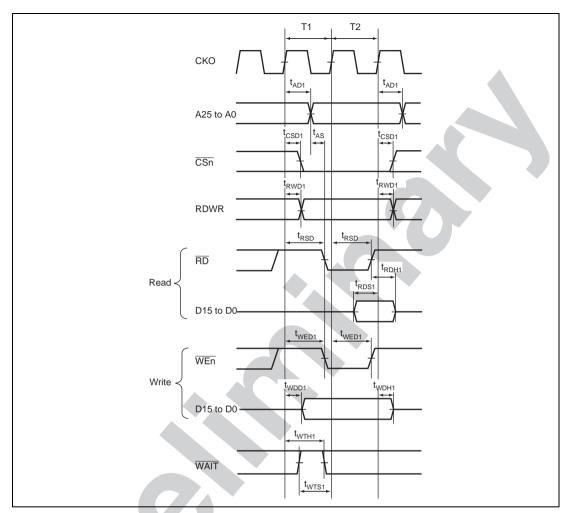

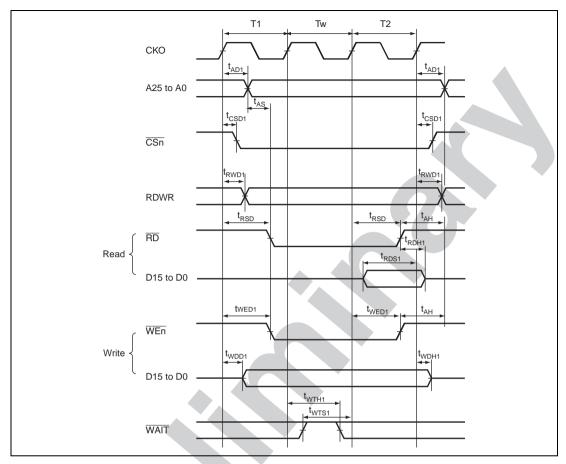

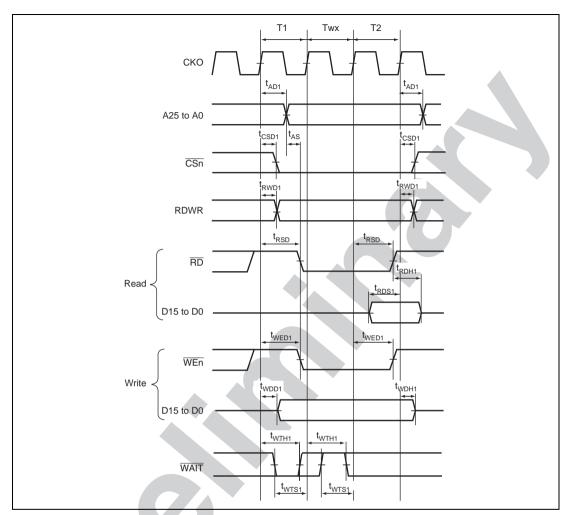

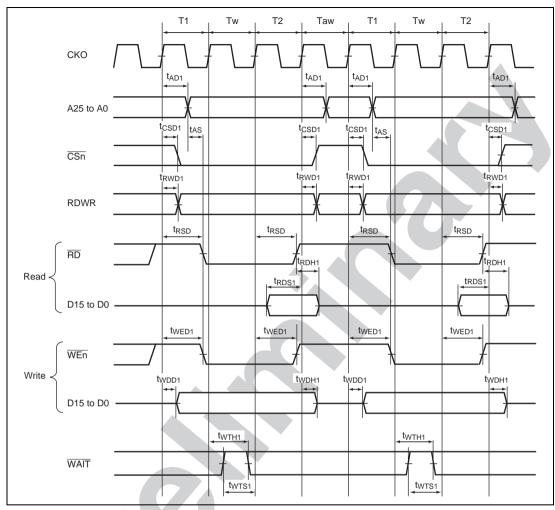

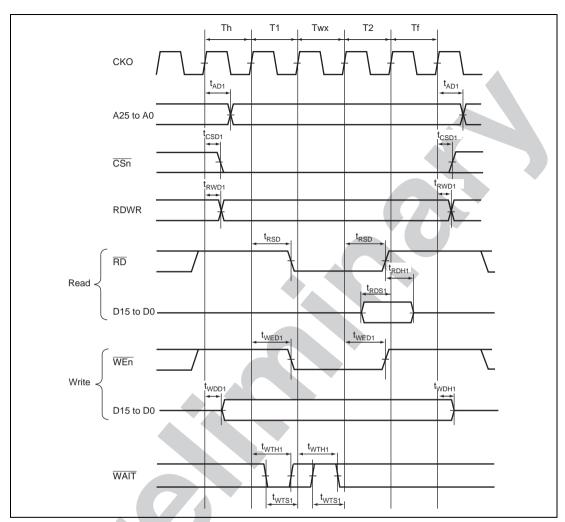

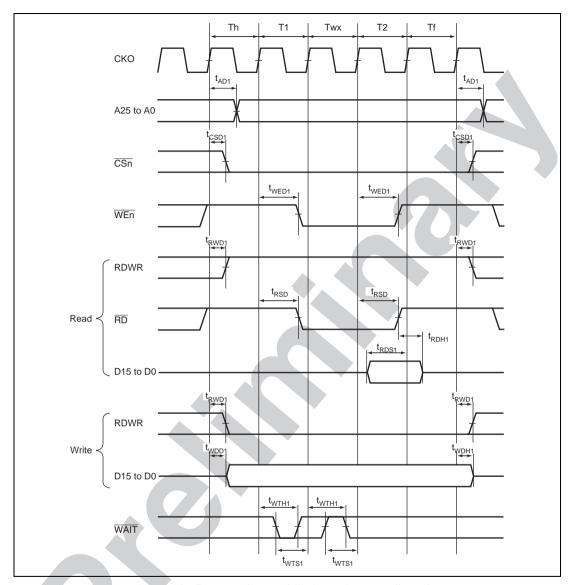

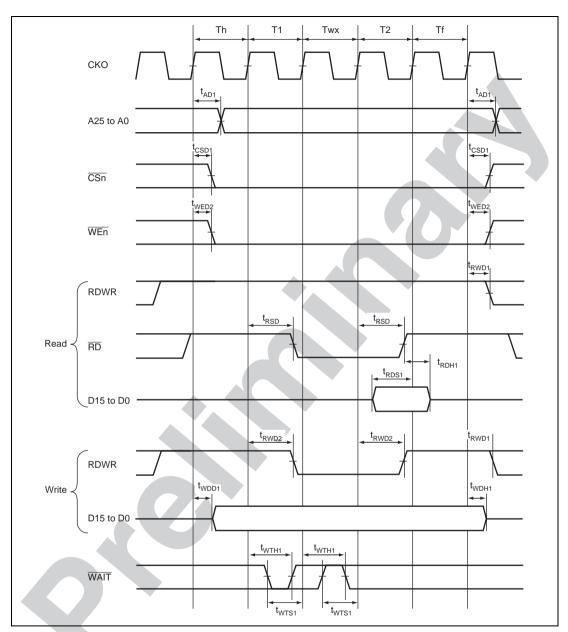

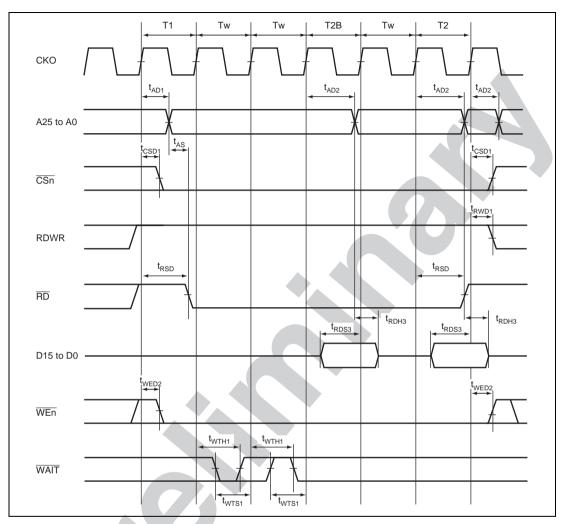

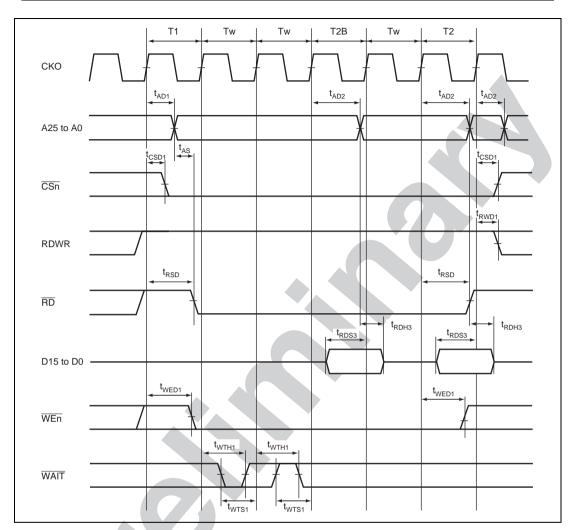

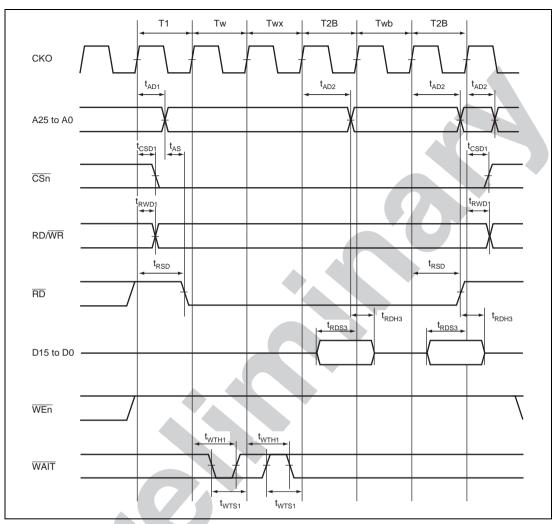

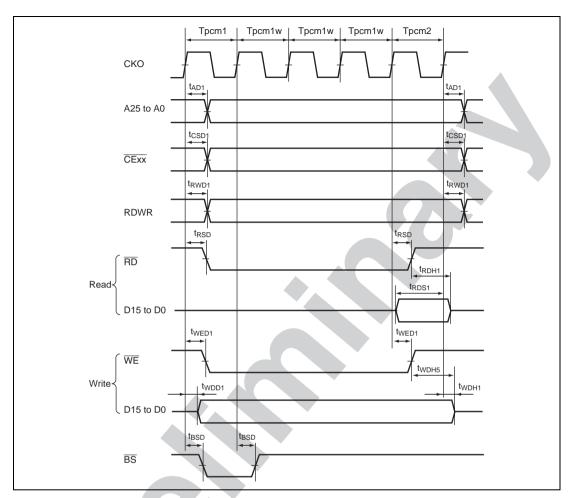

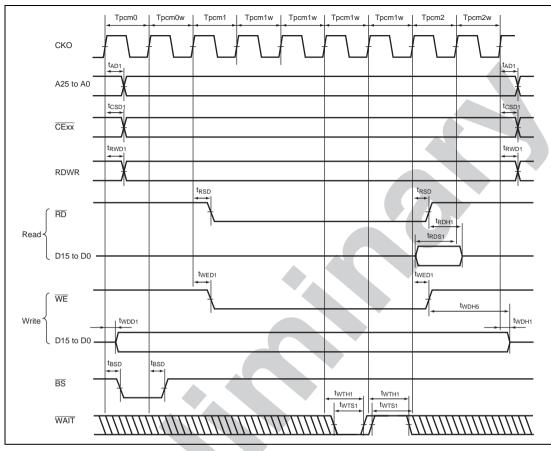

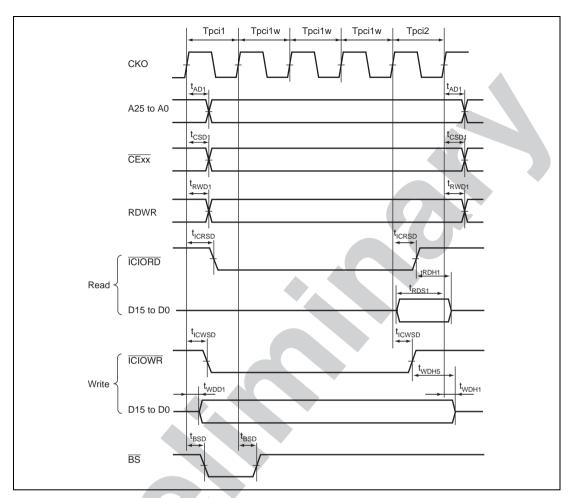

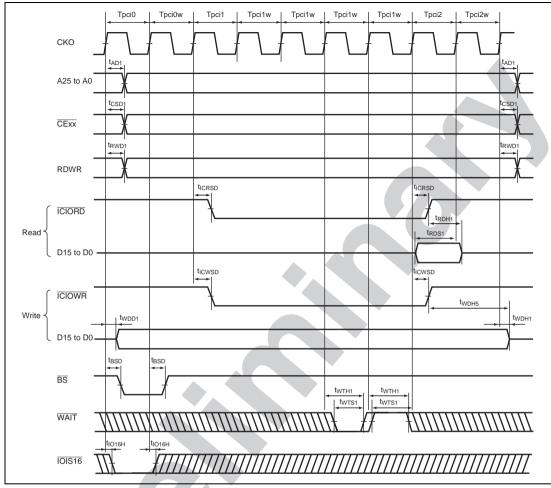

|         | 38.5.3   | BSC Bus Timing                  |     |

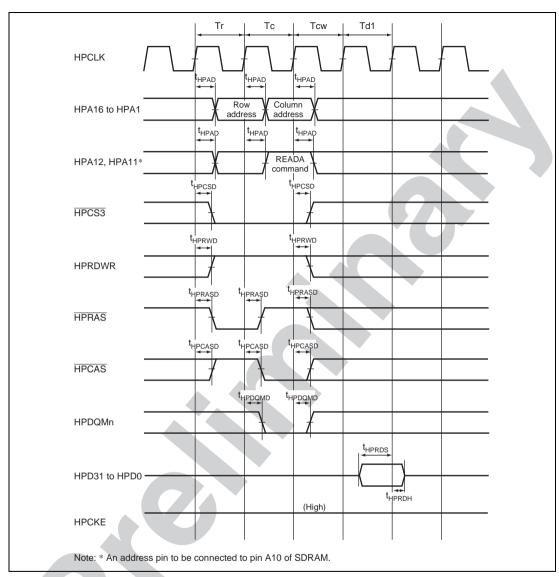

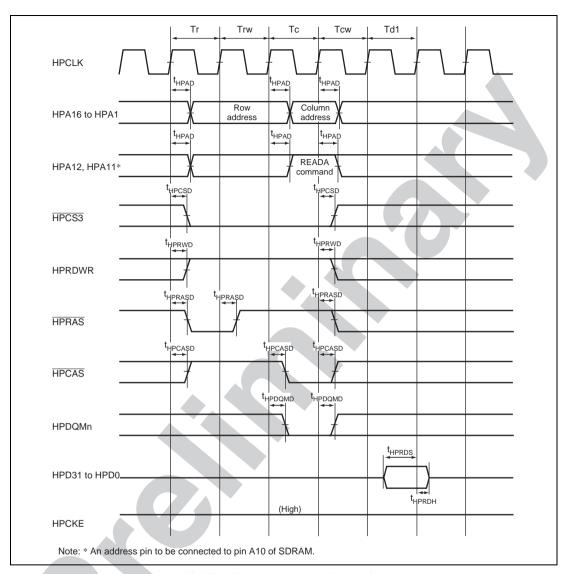

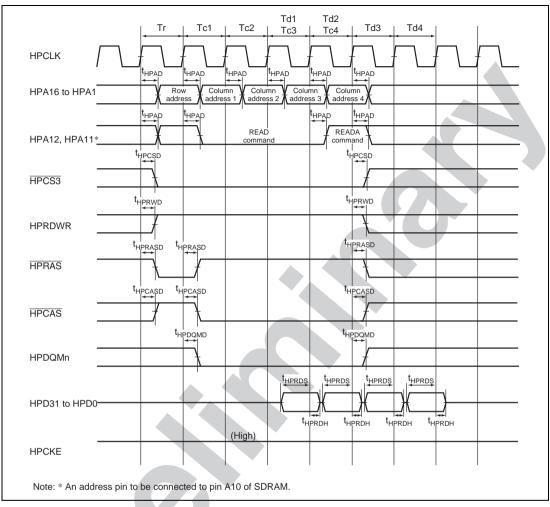

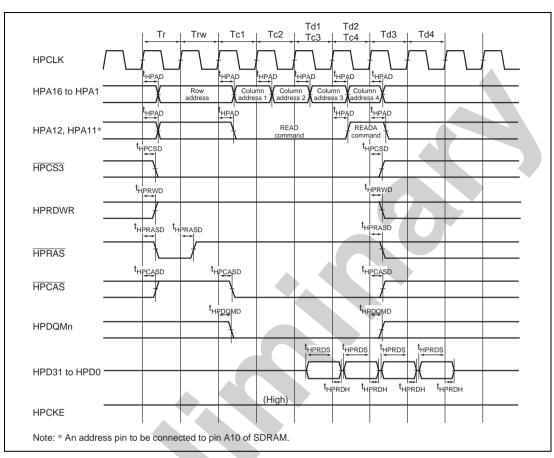

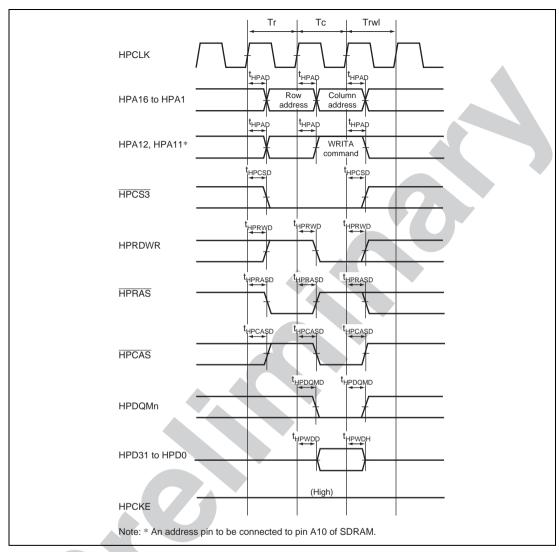

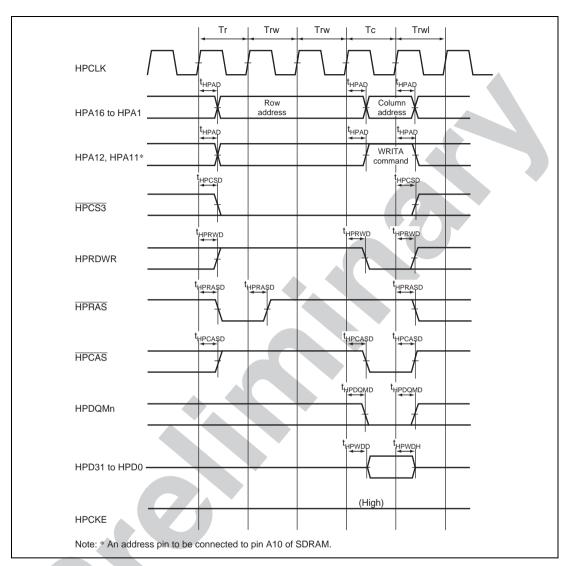

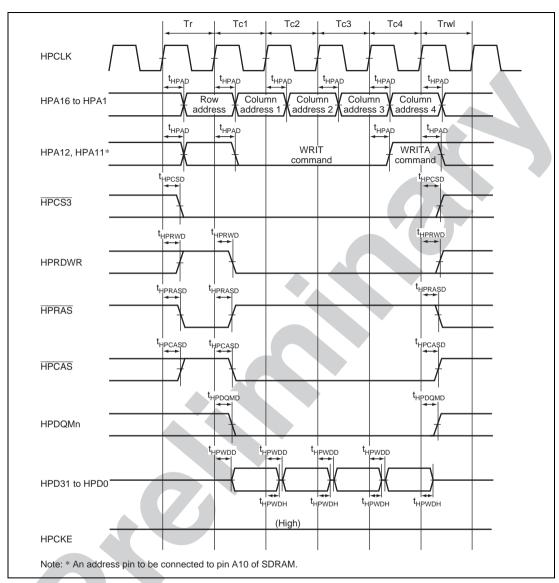

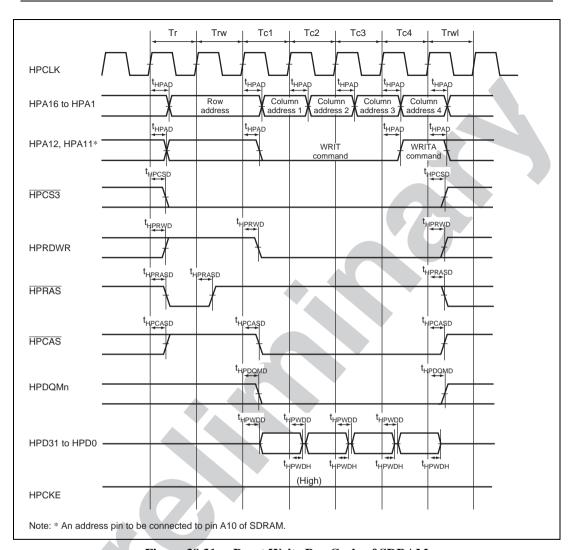

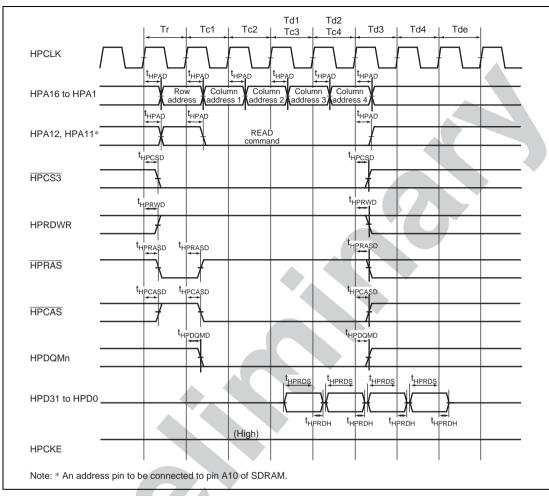

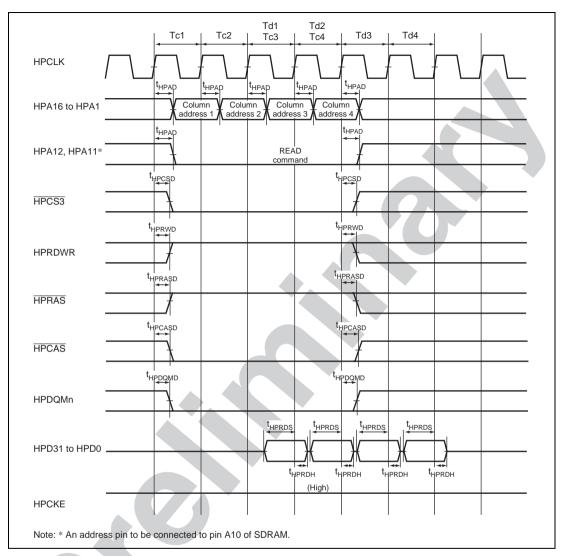

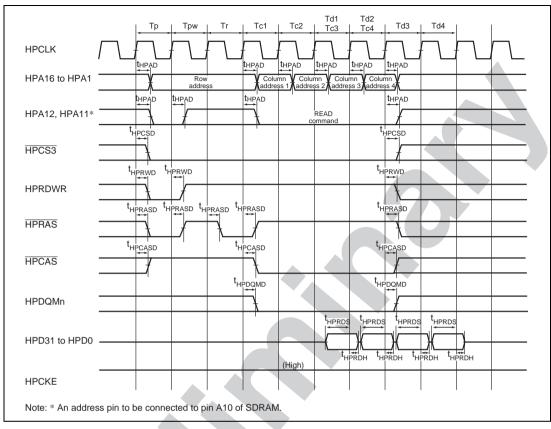

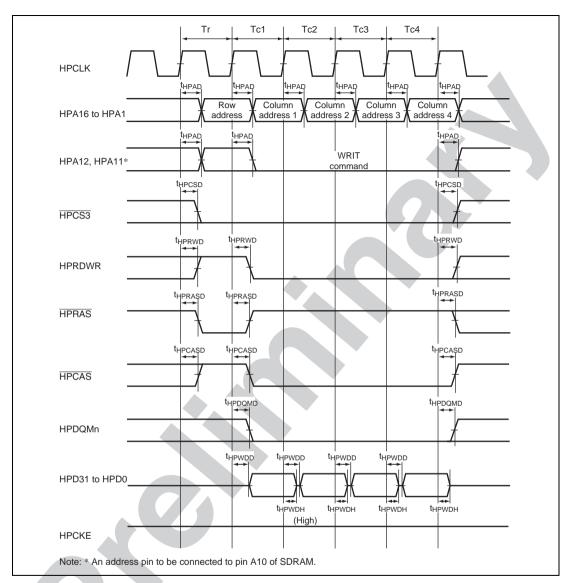

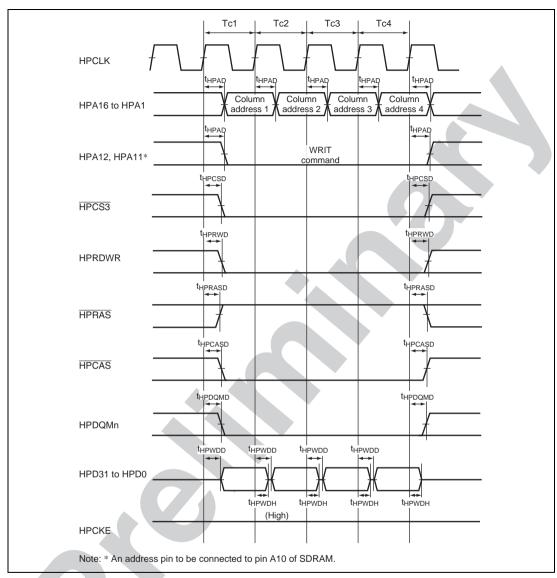

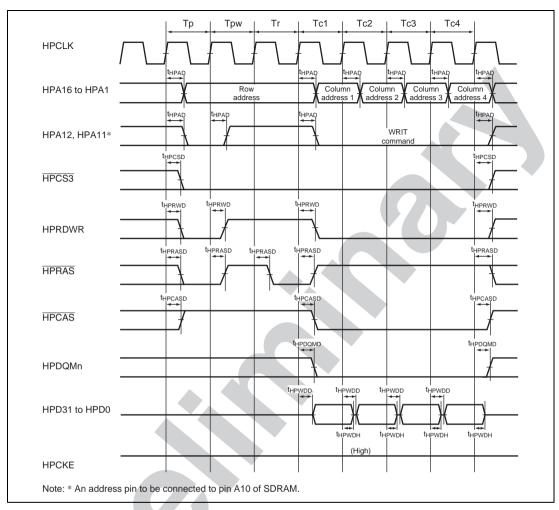

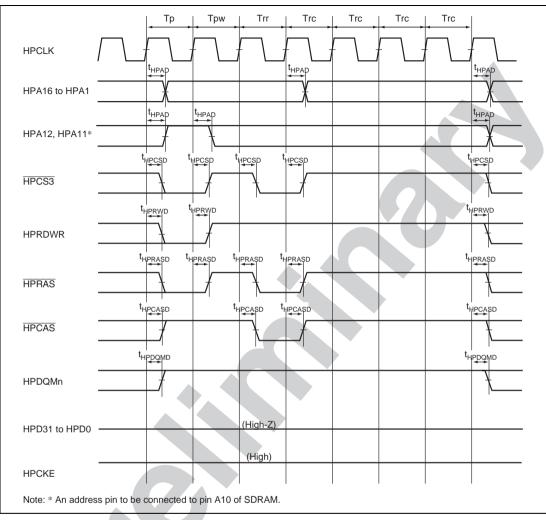

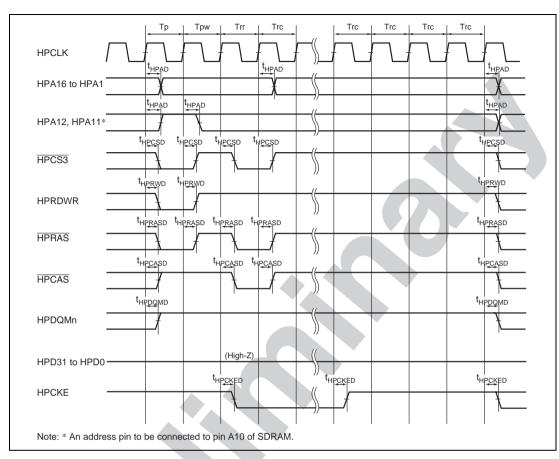

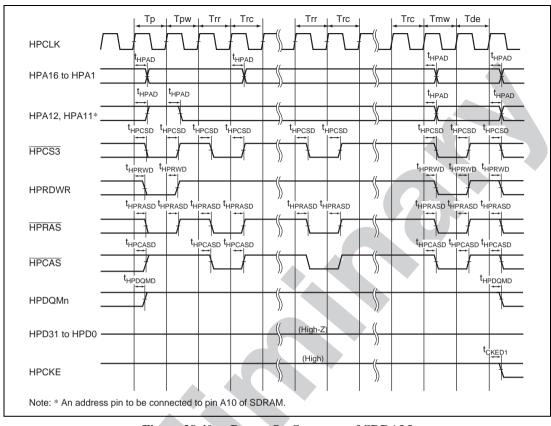

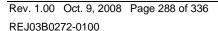

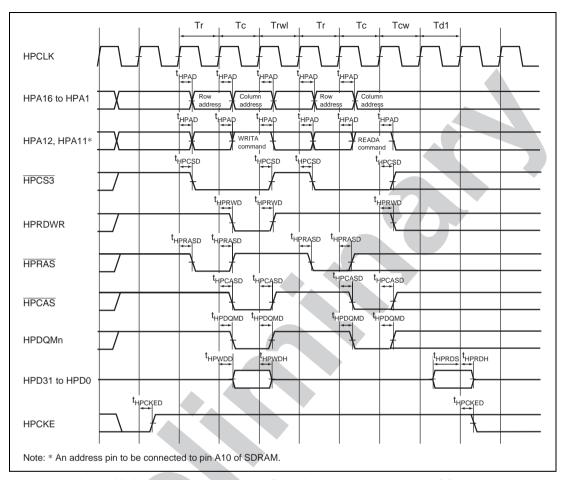

|         | 38.5.4   | SDRAM Timing (SDRAM Bus Timing) |     |

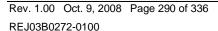

|         | 38.5.5   | I/O Port Signal Timing          | 291 |

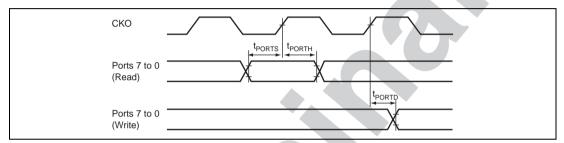

|     | 38.5.6  | DMAC Module Signal Timing             | 292 |

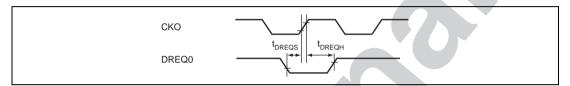

|-----|---------|---------------------------------------|-----|

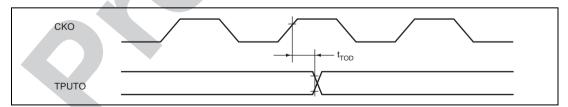

|     | 38.5.7  | SIM Module Signal Timing              | 293 |

|     | 38.5.8  | TPU Module Signal Timing              |     |

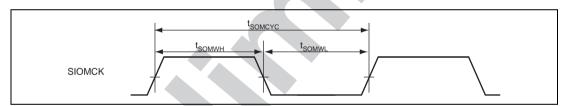

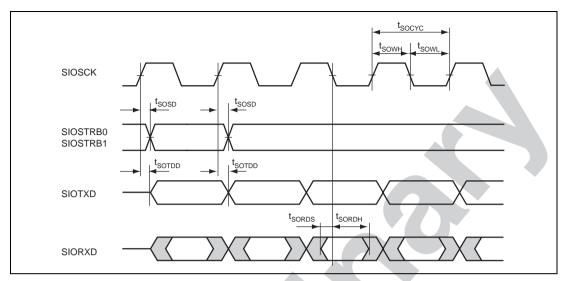

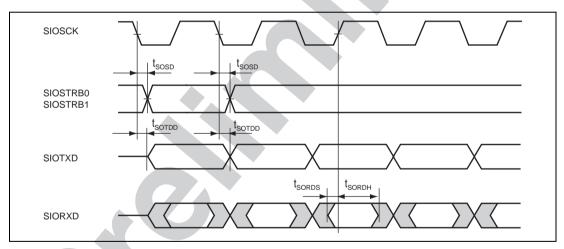

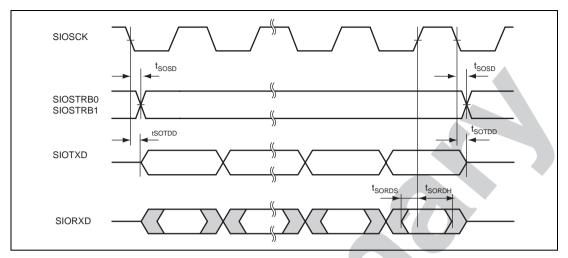

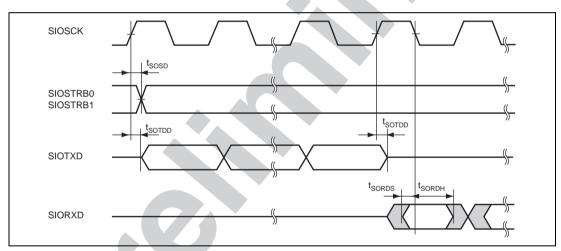

|     | 38.5.9  | SIO Module Signal Timing              | 294 |

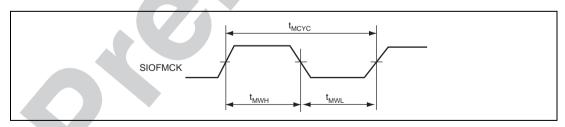

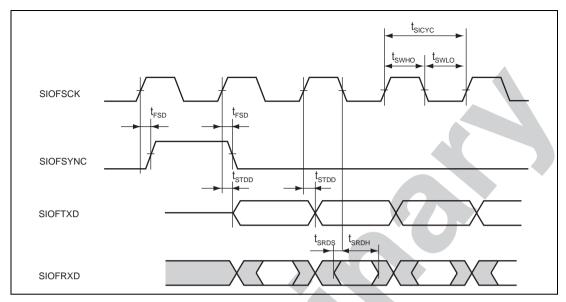

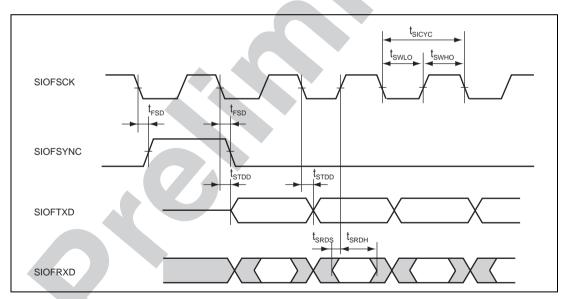

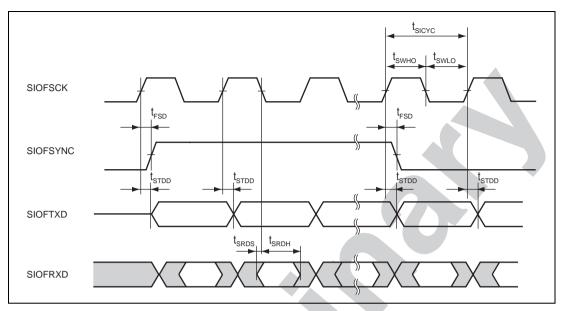

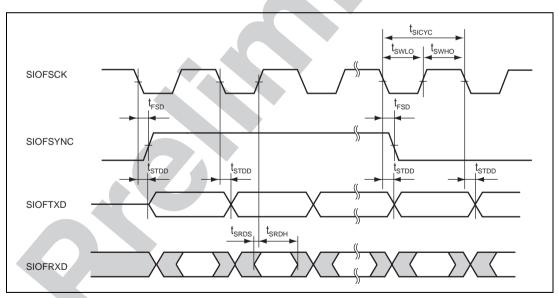

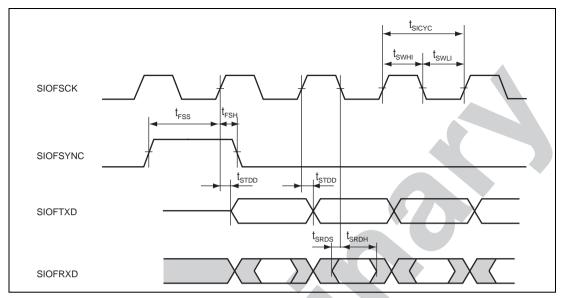

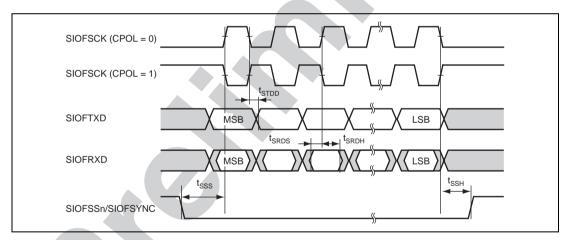

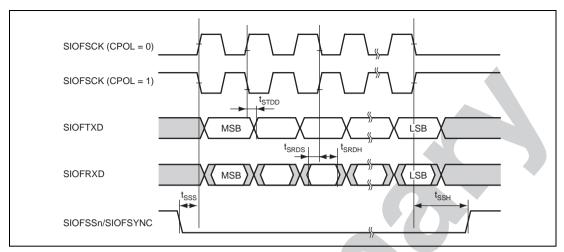

|     | 38.5.10 | SIOF Module Signal Timing             | 297 |

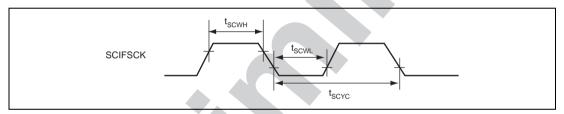

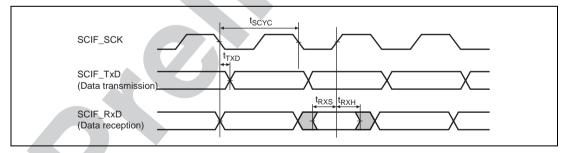

|     | 38.5.11 | SCIF Module Signal Timing             | 301 |

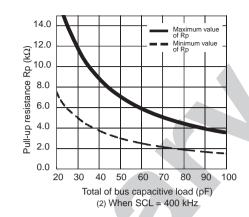

|     | 38.5.12 | I <sup>2</sup> C Module Signal Timing | 303 |

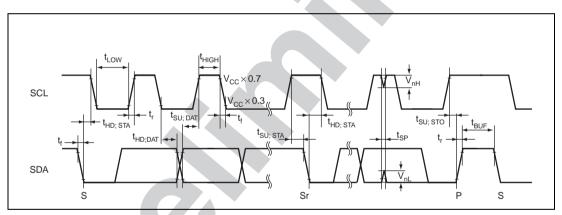

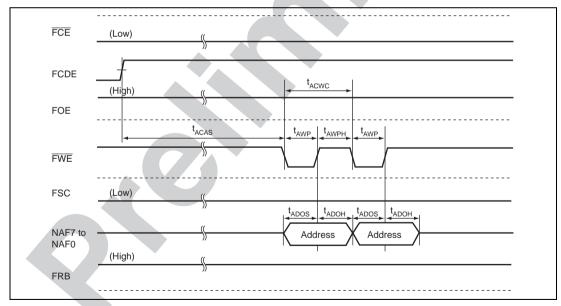

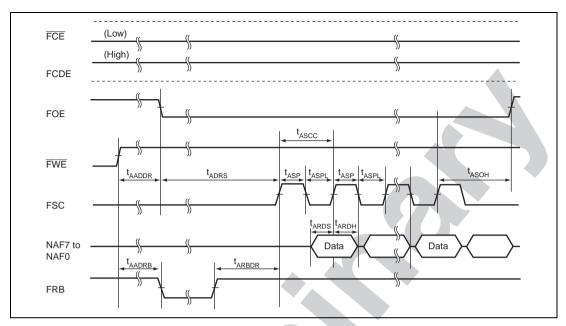

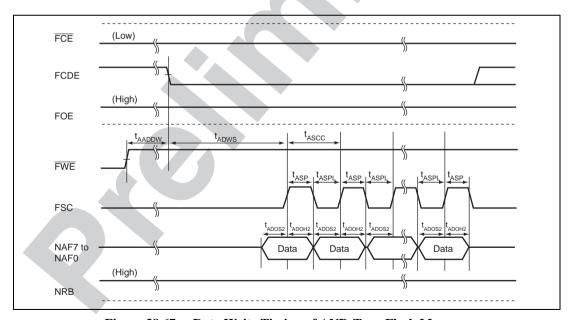

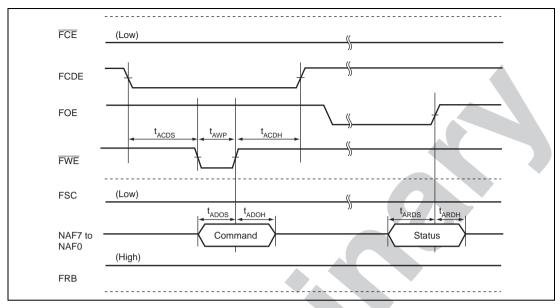

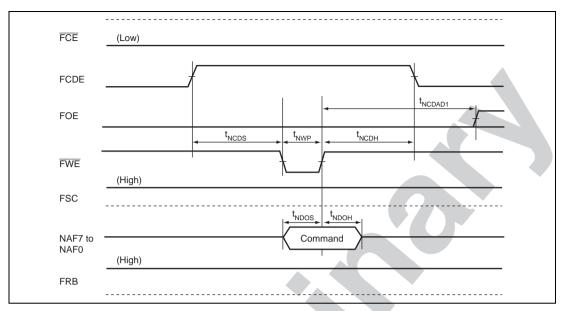

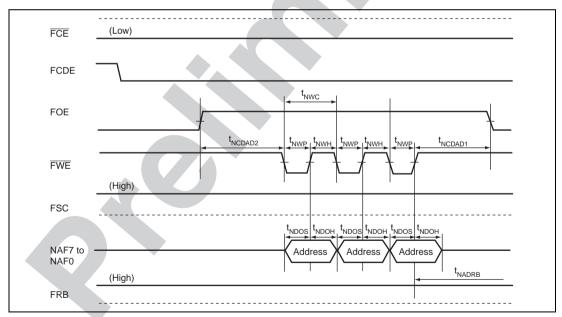

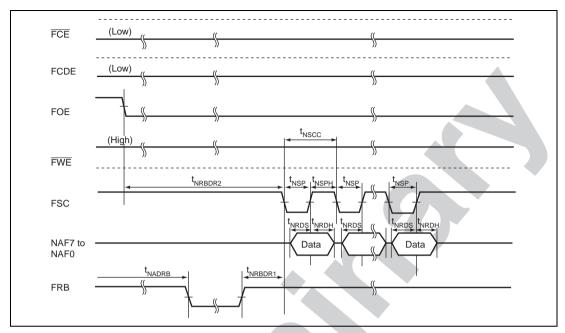

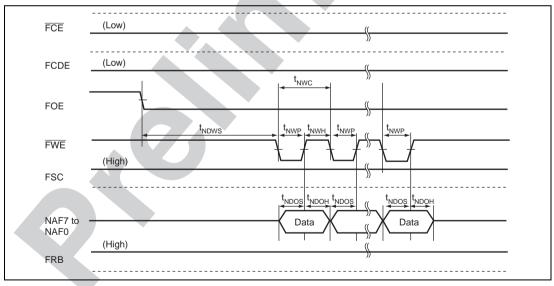

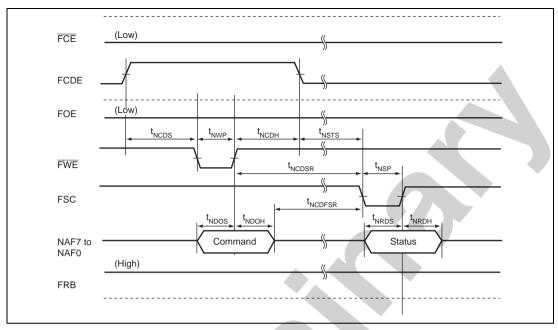

|     | 38.5.13 | FLCTL Module Signal Timing            | 305 |

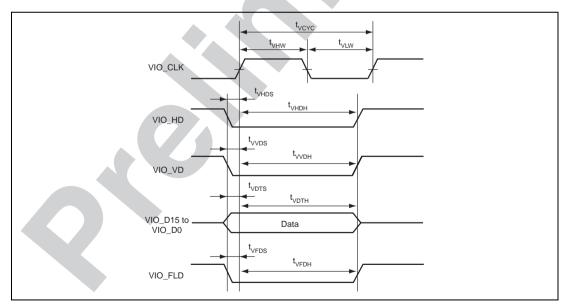

|     | 38.5.14 | VIO Module Signal Timing              | 313 |

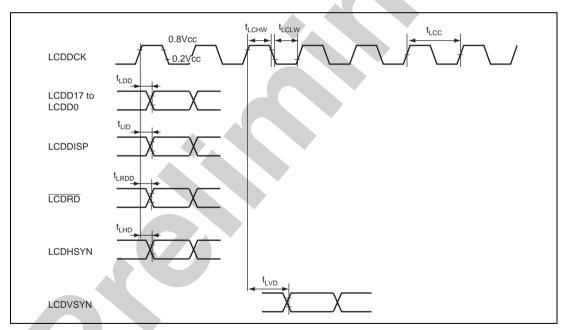

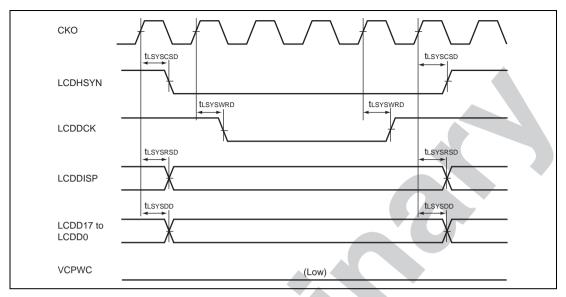

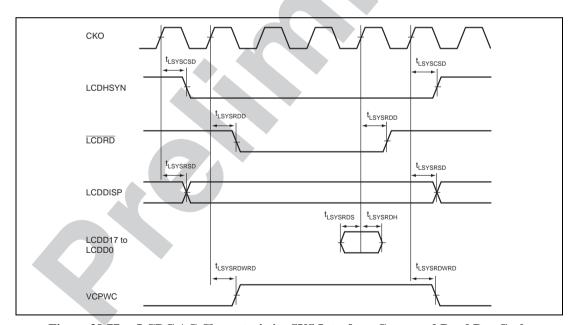

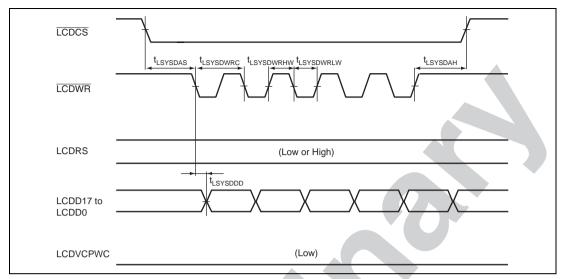

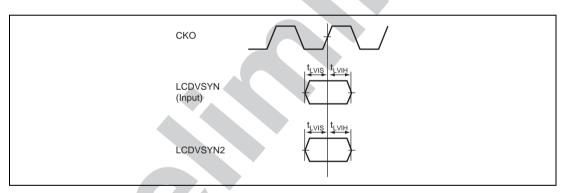

|     | 38.5.15 | LCDC Module Signal Timing             | 314 |

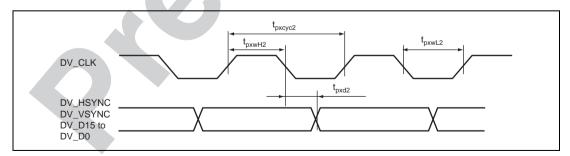

|     | 38.5.16 | VOU Module Signal Timing              | 318 |

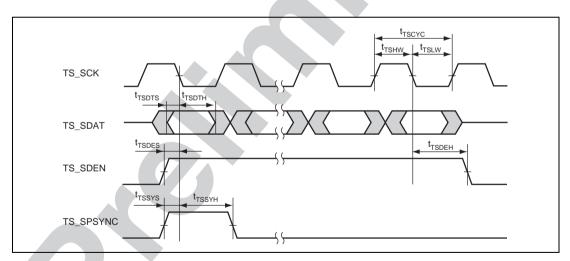

|     | 38.5.17 | TSIF Module Signal Timing             | 319 |

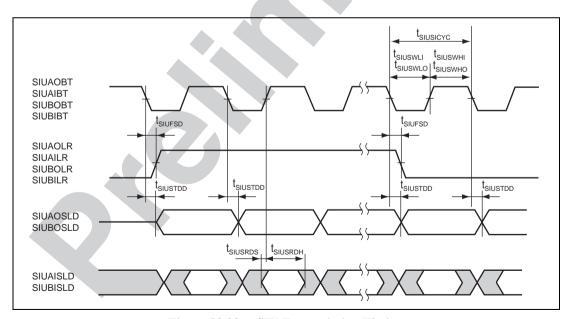

|     | 38.5.18 | SIU Module Signal Timing              | 320 |

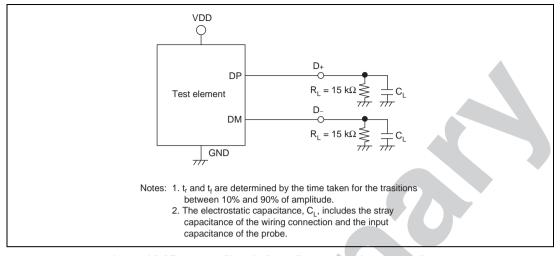

|     | 38.5.19 | USB Transceiver Timing (Full-Speed)   | 321 |

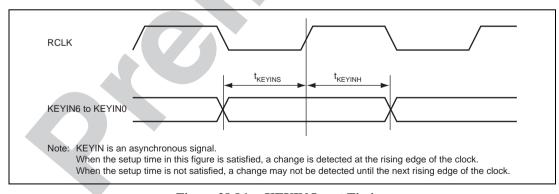

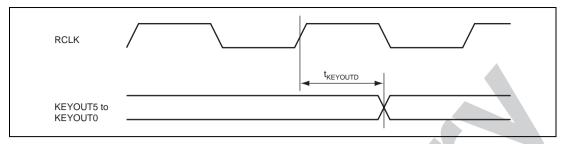

|     | 38.5.20 | KEYSC Module Signal Timing            | 322 |

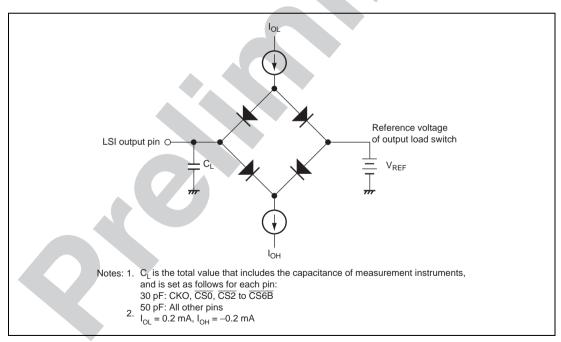

|     | 38.5.21 | AC Characteristic Test Conditions     | 323 |

| Apr | endix   |                                       | 325 |

| A.  |         | es in Reset and Power-Down States     |     |

| В.  |         | Dimensions                            |     |

|     | C       |                                       |     |

## Section 1 Overview

The SH7722 is a system LSI that incorporates an SH4AL-DSP microcontroller with a clock speed of up to 333 MHz as its core, together with a variety of functions required for multimedia applications. These include MPEG4 and H.264 accelerators, a 2D graphics accelerator, LCD controller, camera interface, and sound input/output module.

The SH4AL-DSP microcontroller is a 32-bit RISC-type SuperH architecture CPU with a DSP extension function, and is a new generation CPU core which is upward compatible with SH-1, SH2, and SH3-DSP at the instruction set level. Super scalar design in which two instructions are executed simultaneously allows high-speed processing. In addition, the strong power-management functions keep both operating current and standby current low.

This LSI is ideal for use in multimedia devices that require both high-performance operation and low power consumption.

#### 1.1 Features

The features of this LSI are listed in table 1.1.

#### Table 1.1 Features of This LSI

#### Item

#### **Features**

#### CPU

- · Renesas Technology original architecture

- Upward compatible with SH-1, SH-2, SH-3, and SH3-DSP at instruction set level

- 32-bit internal data bus

- General-register files

- Sixteen 32-bit general registers (eight 32-bit shadow registers)

- Seven 32-bit control registers

- Four 32-bit system registers

- RISC-type instruction set (upward compatible with SH-1, SH-2, SH-3, and SH3-DSP)

- Instruction length: 16-bit fixed length for improved code efficiency

- Load/store architecture

- Delayed branch instructions

- Instructions executed with conditions

- Instruction set based on the C language

- Super scalar design which executes two instructions simultaneously

- Instruction execution time: Two instructions per cycle (max.)

- Virtual address space: 4 Gbytes

- Space identifier ASID: 8 bits, 256 virtual address spaces

- On-chip multiplier

- Eight-stage pipeline

| Item            | Features                                                                                                                 |

|-----------------|--------------------------------------------------------------------------------------------------------------------------|

| DSP             | Mixture of 16-bit and 32-bit instructions                                                                                |

|                 | 32-/40-bit internal data bus                                                                                             |

|                 | Multiplier, ALU, and barrel shifter                                                                                      |

|                 | 32-bit multiplier for 16-bit x 16-bit operations                                                                         |

|                 | Large-capacity DSP data register files                                                                                   |

|                 | Six 32-bit data registers                                                                                                |

|                 | — Two 40-bit data registers                                                                                              |

|                 | Extended Harvard architecture for DSP data bus                                                                           |

|                 | — Two data buses                                                                                                         |

|                 | — One instruction bus                                                                                                    |

|                 | <ul> <li>Maximum of four parallel operations: ALU, multiplication, two load/store operations</li> </ul>                  |

|                 | <ul> <li>Two addressing units to generate addresses for two memory access</li> <li>DSP data addressing modes:</li> </ul> |

|                 |                                                                                                                          |

|                 | Increment and indexing (with or without modulo addressing)  Total purposed repost loop control.                          |

|                 | <ul><li>Zero-overhead repeat loop control</li><li>Conditional execution instructions</li></ul>                           |

|                 | User DSP mode and privileged DSP mode                                                                                    |

| Memory          | 4-Gbyte address space, 256 address spaces (8-bit ASID)                                                                   |

| management unit |                                                                                                                          |

| (MMU)           | Supports multiple page sizes: 1 Kbyte, 4 Kbytes, 64 Kbytes, or 1 Mbyte                                                   |

|                 | 4-entry full associative TLB for instructions                                                                            |

|                 | 64-entry full associative TLB for instructions and operands                                                              |

|                 | Specifies replacement way by software and supports random replacement                                                    |

|                 | algorithm                                                                                                                |

|                 | Address mapping allows direct access to TLB contents                                                                     |

|                 | Note: This LSI does not support the 32-bit address extended mode or the 32-bit boot function.                            |

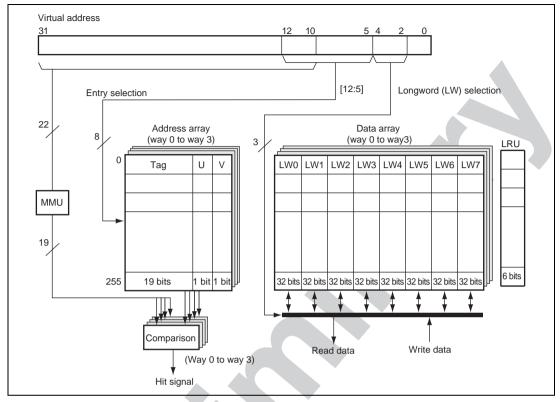

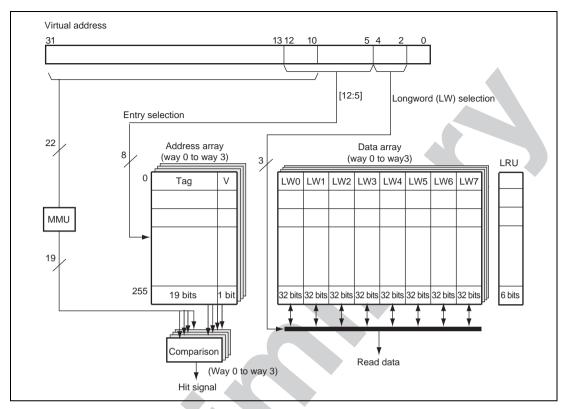

| Cache memory    | Instruction cache (IC)                                                                                                   |

|                 | — 32-kbyte, 4-way set associative                                                                                        |

|                 | — 32-byte block length                                                                                                   |

|                 | Operand cache (OC)                                                                                                       |

|                 | <ul> <li>32-kbyte, 4-way set associative</li> </ul>                                                                      |

|                 | — 32-byte block length                                                                                                   |

| •               | Selectable write mode (copy-back or write-through)                                                                       |

| Item              | Features                                                                                    |

|-------------------|---------------------------------------------------------------------------------------------|

| X/Y memory        | Three independent read/write ports                                                          |

|                   | — 8-/16-/32-bit access from CPU                                                             |

|                   | Maximum of two 16-bit accesses from DSP                                                     |

|                   | <ul> <li>8-/16-/32-/64-bit or 16-/32-byte access by SuperHyway bus master</li> </ul>        |

|                   | Total of 16 kbytes                                                                          |

|                   | Memory protective functions specialized for DSP access in addition to                       |

|                   | memory protective functions for CPU access                                                  |

| U memory          | Two independent read/write ports                                                            |

|                   | <ul><li>8-/16-/32-bit access from CPU</li></ul>                                             |

|                   | <ul> <li>8-/16-/32-/64-bit or 16-/32-byte access by SuperHyway bus master</li> </ul>        |

|                   | Large 128-kbyte memory                                                                      |

| IL memory         | Three independent read/write ports                                                          |

| (ILRAM)           | <ul> <li>Instruction fetch access from CPU using virtual address</li> </ul>                 |

|                   | <ul> <li>Instruction fetch access from CPU using physical address and 8-/16-/32-</li> </ul> |

|                   | bit operand access from CPU                                                                 |

|                   | <ul> <li>8-/16-/32-/64-bit or 16-/32-byte access by SuperHyway bus master</li> </ul>        |

|                   | Total of 4 kbytes                                                                           |

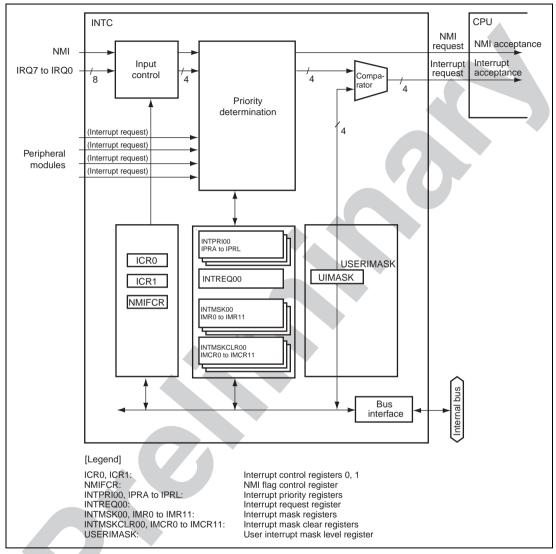

| Interrupt         | <ul> <li>Nine external interrupt pins (NMI, IRQ7 to IRQ0)</li> </ul>                        |

| controller (INTC) | NMI: Fall/rise selectable                                                                   |

|                   | <ul> <li>IRQ: Fall/rise/high level/low level selectable</li> </ul>                          |

|                   | On-chip peripheral interrupts: Priority can be specified for each module                    |

| Bus state         | Supports SRAM, burst ROM, and PCMCIA interfaces.                                            |

| controller (BSC)  | Physical address space is provided to support six areas in total: two areas                 |

|                   | (areas 0 and 4) of up to 64 Mbytes each and four areas (areas 5A, 5B, 6A,                   |

|                   | and 6B) of up to 32 Mbytes each.                                                            |

|                   | The following settings can be individually made for each area.                              |

|                   | Memory type: SRAM, NOR-Flash, burst ROM, PCMCIA                                             |

|                   | — Data bus width: Selectable from 16 bits and 32 bits (16 bits when the                     |

|                   | selected data bus width for the SBSC is 64 bits.)                                           |

|                   | Number of wait cycles                                                                       |

| Item                            | Features                                                                                                                                                                                     |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bus state                       | 3.3 V SDR-SDRAM can be directly connected                                                                                                                                                    |

| controller for<br>SDRAM (SBSC)  | <ul> <li>Physical address space is provided to support two areas (areas 2 and 3) of<br/>up to 64 Mbytes</li> </ul>                                                                           |

|                                 | Up to 128 Mbytes of SDRAM can be connected                                                                                                                                                   |

|                                 | <ul> <li>Data bus width: Selectable from 16 bits, 32 bits, and 64 bits (only 16 bits or<br/>32 bits can be selected when the selected data bus width for the BSC is 32<br/>bits.)</li> </ul> |

|                                 | Supports auto-refresh and self-refresh                                                                                                                                                       |

|                                 | Auto-precharge mode or bank active mode can be selected                                                                                                                                      |

| Direct memory access controller | Number of channels: Six channels. One of these channels (channel 0) can receive an external request                                                                                          |

| (DMAC)                          | Address space: 4 Gbytes on architecture                                                                                                                                                      |

|                                 | • Data transfer length: Bytes, words (2 bytes), longwords (4 bytes), 16 bytes, and 32 bytes                                                                                                  |

|                                 | Maximum transfer count: 16,777,216 transfers                                                                                                                                                 |

|                                 | Address mode: Dual address mode                                                                                                                                                              |

|                                 | <ul> <li>Transfer request: Selectable from three types of external request, on-chip<br/>peripheral module request, and auto request</li> </ul>                                               |

|                                 | Bus mode: Selectable from cycle steal mode (normal mode and intermittent mode) and burst mode                                                                                                |

|                                 | Priority: Selectable from fixed channel priority mode and round-robin mode                                                                                                                   |

|                                 | <ul> <li>Interrupt request: Supports interrupt request to CPU at the end of data transfer</li> </ul>                                                                                         |

|                                 | <ul> <li>Repeat function: Automatically resets the transfer source, destination, and<br/>count at the end of DMA transfer</li> </ul>                                                         |

|                                 | Reload function: Automatically resets the transfer source and destination at<br>the end of the specified number of DMA transfers                                                             |

| Item             | Features                                                                                                                 |

|------------------|--------------------------------------------------------------------------------------------------------------------------|

| Clock pulse      | Clock mode: Input clock selectable from external inputs (EXTAL and RCLK)                                                 |

| generator (CPG)  | Generates six types of system clocks                                                                                     |

|                  | — CPU clock (Iφ): Maximum 333.4 MHz (VDD = 1.25 to 1.35 V)                                                               |

|                  | — SH clock (SHφ): Maximum 133.4 MHz                                                                                      |

|                  | <ul> <li>U memory clock (Uφ): Maximum 133.4 MHz</li> </ul>                                                               |

|                  | — SDRAM clock (B3φ): Maximum 133.4 MHz                                                                                   |

|                  | — Bus clock (Bφ): Maximum 66.7 MHz                                                                                       |

|                  | <ul> <li>Peripheral clock (Pφ): Maximum 33.4 MHz</li> </ul>                                                              |

|                  | Supports power-down mode                                                                                                 |

|                  | <ul> <li>Module standby function (stops clocks for individual modules.)</li> </ul>                                       |

|                  | <ul> <li>Sleep mode (stops clocks for the CPU core.)</li> </ul>                                                          |

|                  | <ul> <li>Software standby mode (stops clocks in the LSI except the I/O area and<br/>the RCLK operation area.)</li> </ul> |

|                  | <ul> <li>U-standby mode (turns off the power in the LSI except the I/O area and</li> </ul>                               |

|                  | the RCLK operation area.)                                                                                                |

| Timer unit (TMU) | Internal three-channel 32-bit timer                                                                                      |

|                  | Auto-reload type 32-bit down counter                                                                                     |

|                  | <ul> <li>Internal prescaler for Pφ</li> </ul>                                                                            |

|                  | Interrupt request                                                                                                        |

| Compare match    | 32-bit timer of one channel (16 bits/32 bits can be selected)                                                            |

| timer (CMT)      | Source clock: RCLK                                                                                                       |

|                  | Compare match function provided                                                                                          |

|                  | Interrupt requests                                                                                                       |

| R watchdog timer | One-channel watchdog timer operating at RCLK                                                                             |

| (RWDT)           | Operational in power-down modes                                                                                          |

|                  | Generates a system reset when a counter overflow occurs                                                                  |

| Realtime clock   | Operates at RCLK and includes clock and calendar functions                                                               |

| (RTC)            | Generates alarm interrupt and periodic interrupt                                                                         |

| Timer pulse unit | Four pulse outputs possible                                                                                              |

| (TPU)            | Maximum of 4-phase PWM output possible                                                                                   |

| Item                         | Features                                                                                                                              |  |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|

| Serial I/O (SIO)             | One channel                                                                                                                           |  |

|                              | <ul> <li>Clocked synchronous mode (clock/data/strobe x 2)</li> </ul>                                                                  |  |

|                              | Data length programmable                                                                                                              |  |

|                              | <ul> <li>Programmable processing of clock polarity and data values in idle state<br/>(such as low level or high impedance)</li> </ul> |  |

|                              | Eight-bit fixed-length address, programmable data length                                                                              |  |

|                              | Strobe position programmable, level/edge-ready                                                                                        |  |

|                              | MSB/LSB changeable                                                                                                                    |  |

|                              | <ul> <li>Internal prescaler for Pφ</li> </ul>                                                                                         |  |

|                              | Interrupt request                                                                                                                     |  |

| Serial I/O with              | Two channels                                                                                                                          |  |

| FIFO (SIOF)                  | Internal 64-byte transmit/receive FIFOs                                                                                               |  |

|                              | Supports 8-/16-bit data and 16-bit stereo audio input/output                                                                          |  |

|                              | • Sampling rate clock input selectable from $P\phi$ and external pin                                                                  |  |

|                              | <ul> <li>Internal prescaler for Pφ</li> </ul>                                                                                         |  |

|                              | Interrupt request and DMAC request                                                                                                    |  |

|                              | SPI mode                                                                                                                              |  |

|                              | <ul> <li>Provides continuous full-duplex communication with SPI slave device in<br/>fixed master mode</li> </ul>                      |  |

|                              | <ul> <li>Serial clock (SCK) rise or fall edge selectable for data sampling timing</li> </ul>                                          |  |

|                              | <ul> <li>SCK clock phase selectable for transmit timing</li> </ul>                                                                    |  |

|                              | — Three slave devices selectable                                                                                                      |  |

|                              | <ul> <li>Transmit/receive data length fixed to 8 bits</li> </ul>                                                                      |  |

| Serial                       | Three channels                                                                                                                        |  |

| communication interface with | Internal 16-byte transmit/receive FIFOs                                                                                               |  |

| FIFO (SCIF)                  | High-speed UART for Bluetooth                                                                                                         |  |

|                              | <ul> <li>Internal prescaler for Pφ</li> </ul>                                                                                         |  |

|                              | <ul> <li>Interrupt request and DMAC request</li> </ul>                                                                                |  |

|                              | Both asynchronous and clock synchronous serial communications possible                                                                |  |

| Item                           | Features                                                                                                                                                  |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIM card                       | <ul> <li>One channel. Conforms to the ISO 7816-3 data protocol. (T = 0, T = 1)</li> </ul>                                                                 |

| interface (SIM)                | Asynchronous half-duplex character transmission protocol                                                                                                  |

|                                | Data length: 8 bits                                                                                                                                       |

|                                | Parity bit generation and check                                                                                                                           |

|                                | Selectable output clock cycles per etu (elementary time unit)                                                                                             |

|                                | Selectable direct convention/inverse convention                                                                                                           |

|                                | On-chip prescaler                                                                                                                                         |

|                                | Switchable clock polarity (high or low) in idle state                                                                                                     |

|                                | Interrupt request and DMAC request                                                                                                                        |

| IrDA interface                 | Conforms to version 1.2a                                                                                                                                  |

| (IrDA)                         | CRC calculation function                                                                                                                                  |

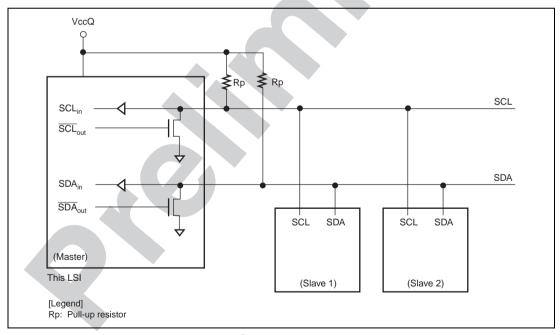

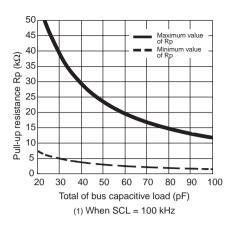

| I <sup>2</sup> C bus interface | Supports single master transmission/reception                                                                                                             |

| (IIC)                          | <ul> <li>Supports standard mode (100 kHz) and high-speed mode (400 kHz)</li> </ul>                                                                        |

| AND/NAND flash                 | Directly connected memory interface with AND-/NAND-type flash memory                                                                                      |

| memory<br>controller           | Read/write in sectors                                                                                                                                     |

| (FLCTL)                        | <ul> <li>Two types of transfer modes: Command access mode and sector access<br/>mode (512-byte data + 16-byte management code: with 4-bit ECC)</li> </ul> |

|                                | <ul> <li>Interrupt request and DMAC transfer request</li> </ul>                                                                                           |

|                                | Supports up to 4-Gbit of flash memory                                                                                                                     |

| Video processing               | MPEG-4 single video object plane (VOP) encoding and decoding                                                                                              |

| unit (VPU)                     | Applicable standard: MPEG-4 Simple Profile, MPEG-4 H.264 (Baseline)*                                                                                      |

|                                | Image size: Sub-QCIF to VGA                                                                                                                               |

|                                | Bit rate: Maximum 8 Mbps                                                                                                                                  |

|                                | Motion detection: Layer tracking (Renesas Technology original method)                                                                                     |

|                                | Rate control: Control with quantizing amount predicted (Renesas                                                                                           |

|                                | Technology original method), both VOP and MB supported                                                                                                    |

|                                | <ul> <li>Interrupt request and no DMAC request (bus master function supported)</li> </ul>                                                                 |

|                                | Note: Some of Baseline tools are not supported.                                                                                                           |

#### ltem

#### **Features**

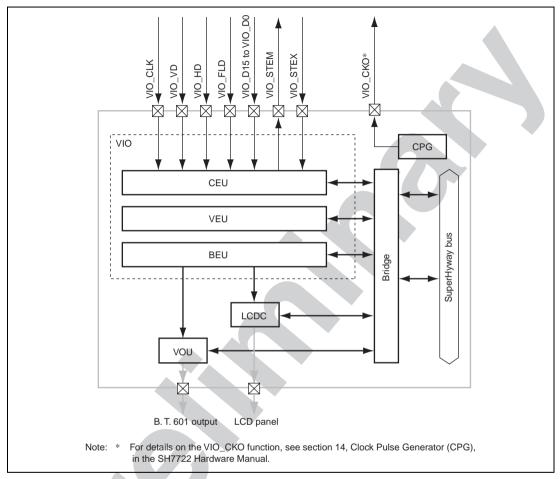

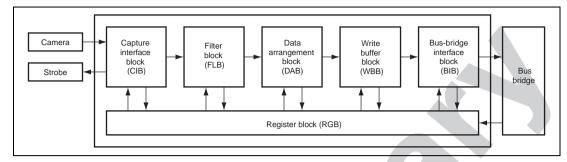

#### Video I/O (VIO)

A module that provides the interface with camera module and image processing

- CEU block (image capturing from camera module)

- Camera module interface:

Data (8 bits: YCbCr 4:2:2), horizontal sync signal (HD), vertical sync signal (VD)

- Size of captured image: 5M pixels, 3M pixels, 2M pixels, UXGA, SXGA, XGA, SVGA, VGA, CIF, QVGA, QCIF, QQVGA, Sub-QCIF, etc.

- Output image format: YCbCr (4:2:2/4:2:0)

- Image format conversion function:

Reduced image generating prefilter function

YCbCr 4:2:2 → YCbCr 4:2:2, YCbCr 4:2:0

YCbCr format (Y: 8 bits and CbCr: 16 bits)

- VEU block (image processing in memory)

- A. Video image processing function

Input image format: YCbCr image (Y/CbCr plane image), RGB image (RGB pack image)

Output image format: YCbCr image (Y/CbCr plane image), RGB image (RGB pack image)

Image processing function:

Scaling image generating filter function

YCbCr → RGB/RGB → YCbCr conversion function

Dithering function (in RGB color subtraction)

B. Filter processing function

Mirroring, vertical inversion, point symmetry,  $\pm 90$ -degree image conversion functions

Deblocking filter

Median filter

- C. Video image processing and filter processing combined operation

- BEU block (image blending)

- A. PinP function

Input image format: YCbCr image (Y/CbCr plane image), RGB image (RGB pack image)

Output image format: YCbCr image (Y/CbCr plane image), RGB image (RGB pack image)

B. Graphic processing function

Input graphic format: YCbCr/RGB image

Output graphic format: YCbCr/RGB image

C. PinP and graphic combined operation

Two PinP planes and one graphic plane can be blended simultaneously

- D. Results of processing are written back to memory

- Strobe control function (manual mode/auto mode)

- Frame drop function (1/2, 1/3, 1/4, 1/5, or 1/6 drop)

- Interrupt request is supported but DMAC request is not supported (with bus master function)

| Item              | Features                                                                                                                                                                                                                                                  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

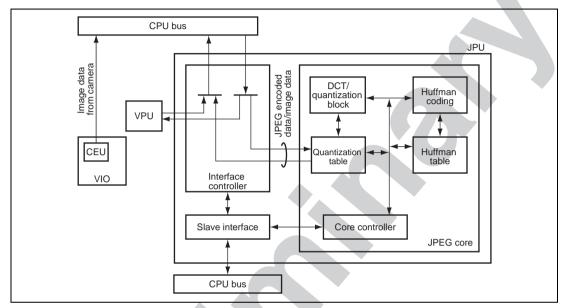

| JPEG processing   | Conforming specification: JPEG baseline                                                                                                                                                                                                                   |

| unit (JPU)        | Operating precision: Conforming to JPEG Part 2 and ISO-IEC10918-2                                                                                                                                                                                         |

|                   | Color format: YCbCr 4:2:2/YCbCr 4:2:0                                                                                                                                                                                                                     |

|                   | Quantization tables: Four tables                                                                                                                                                                                                                          |

|                   | Huffman tables: Four tables (two AC tables and two DC tables)                                                                                                                                                                                             |

|                   | <ul> <li>Target markers: Start of image (SOI), start of frame type 0 (SOF0), start of<br/>scan (SOS), define quantization tables (DQT), define Huffman tables (DHT),<br/>define restart interval (DRI), restart (RSTm), and end of image (EOI)</li> </ul> |

|                   | Interrupt request and no DMAC request (bus master function supported)                                                                                                                                                                                     |

| LCD controller    | Supported LCD panel: TFT color LCD                                                                                                                                                                                                                        |

| (LCDC)            | <ul> <li>Input data format: 8, 12, 16, 18, or 24 bpp</li> </ul>                                                                                                                                                                                           |

|                   | LCD driver interface                                                                                                                                                                                                                                      |

|                   | <ul> <li>Specialized LCD bus, independent of memory bus</li> </ul>                                                                                                                                                                                        |

|                   | <ul> <li>RGB interface or 80-series CPU bus interface selectable</li> </ul>                                                                                                                                                                               |

|                   | — Bus width: 8, 9, 12, 16, 18, or 24 bits                                                                                                                                                                                                                 |

|                   | <ul> <li>One-pixel one-time, two-time, or three-time transfer mode selectable</li> </ul>                                                                                                                                                                  |

|                   | <ul> <li>Signal polarity and SYNC output timing and width programmable in RGB interface</li> </ul>                                                                                                                                                        |

|                   | <ul> <li>Access cycle programmable in 80-series CPU bus interface</li> </ul>                                                                                                                                                                              |

|                   | <ul> <li>Dot clock: Bus clock, peripheral clock, or external clock selectable as the<br/>source clock</li> </ul>                                                                                                                                          |

|                   | <ul> <li>Display data fetch: Continuous mode (according to the refresh rate of the<br/>LCD panel) and one-shot mode (according to the frame rate of the movie)<br/>are supported. Image data can be fetched only for updated sections.</li> </ul>         |

|                   | Writing back the display data on the sub-LCD panel is supported.                                                                                                                                                                                          |

|                   | 256-entry, 24-bit-input/output built-in color palette                                                                                                                                                                                                     |

|                   | An interrupt can be generated at the frame and the user-specified line                                                                                                                                                                                    |

|                   | Interrupt request and no DMAC request (bus master function supported)                                                                                                                                                                                     |

| Video output unit | Output format: 16-bit interface with 8-bit Y and 8-bit C                                                                                                                                                                                                  |

| (VOU)             | Pixel frequency: 13.5 MHz, 27 MHz                                                                                                                                                                                                                         |

- Partial image display: Any background color (specified through the register)

+ display image

- Supported image size: Sub-QCIF, QVGA, VGA, etc.

- Interrupt request and no DMAC request (bus master function supported)

| Item                       | Features                                                                                                                                                                           |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TS interface               | Serial TS data input                                                                                                                                                               |

| (TSIF)                     | <ul> <li>Filters 38 kinds of PIDs in total (The PID values of PAT and CAT packets<br/>are fixed. For PCR, video, and audio packets, the PID values are<br/>predefined.)</li> </ul> |

|                            | Interrupt request and DMAC request                                                                                                                                                 |

| Sound interface            | Internal two channels                                                                                                                                                              |

| unit (SIUA/SIUB)           | 16-bit stereo                                                                                                                                                                      |

|                            | Supports PCM and I2S formats                                                                                                                                                       |

|                            | IEC60958 (SPDIF) supports stereo consumer mode                                                                                                                                     |

|                            | Two sound output systems and two sound input systems                                                                                                                               |

|                            | DSP functions (FIR filter, IIR filter, equalizer, etc.)                                                                                                                            |

|                            | Serial I/O can be directly connected to external A/D or D/A converter.                                                                                                             |

|                            | Internal prescaler                                                                                                                                                                 |

|                            | Supports slave mode                                                                                                                                                                |

|                            | Interrupt request and DMA transfer request                                                                                                                                         |

| USB function module (USBF) | Supports USB 2.0 high-speed mode (480 Mbps) and full-speed mode (12 Mbps)                                                                                                          |

|                            | Internal USB transceivers                                                                                                                                                          |

|                            | • Eight endpoints are supported in total. The endpoint number is switchable.                                                                                                       |

|                            | <ul> <li>Provides Control (endpoint 0), Bulk-transfer (five endpoints in total),</li> <li>Interrupt (two endpoints in total), and Isochronous (two endpoints in total)</li> </ul>  |

|                            | <ul> <li>Supports USB standard commands. The class/vendor commands are<br/>processed by firmware.</li> </ul>                                                                       |

|                            | FIFO buffers for endpoints (Bulk and Isochronous)                                                                                                                                  |

|                            | Module input clock: 48 MHz                                                                                                                                                         |

|                            | Interrupt request and DMAC request                                                                                                                                                 |

| Key scan                   | Key scan: Chattering elimination in key input interrupt detection is possible                                                                                                      |

| interface                  | Input or output bit numbers can be set to be programmable                                                                                                                          |

| (KEYSC)                    | (5 inputs/6 outputs, 6 inputs/5 outputs, 7 inputs/4 outputs.)                                                                                                                      |

|                            | Canceling software standby and U-standby modes by a key input                                                                                                                      |

| SD card host               | SD memory/SDIO interface supported                                                                                                                                                 |

| interface (SDHI)           | Maximum operating frequency: 25 MHz                                                                                                                                                |

|                            | Card detection function                                                                                                                                                            |

|                            | Interrupt request and DMA transfer request                                                                                                                                         |

#### **Features**

2D graphics accelerator (2DG)

- BitBLT function

- Supports the quadrangle drawing function and associated drawing modes

- Figure drawing functions

- Drawing rectangles and quadrangles

Filling with a single color or gradations between colors

Texture mapping

(Methods of mapping: Magnification, minification, and repetition)

(Filtering: Nearest neighbor interpolation, bilinear interpolation, and average pixel methods)

Coordinate transformation

Flipping graphics

Drawing horizontal straight lines

Drawing with a single color or gradations between colors

Texture mapping

(Methods of mapping: Magnification, minification, and repetition)

(Filtering: Nearest neighbor interpolation, bilinear interpolation, and average pixel methods)

- Pixel processing functions

- Scissor testing, alpha blending, shadowing, raster operation (ROP), and color conversion

- Color key and writing-mask control

- Interrupt request and no DMAC request (bus master function supported)

| Item              | Features                                                                                                      |

|-------------------|---------------------------------------------------------------------------------------------------------------|

| I/O port          | I/O port is switchable for each bit                                                                           |

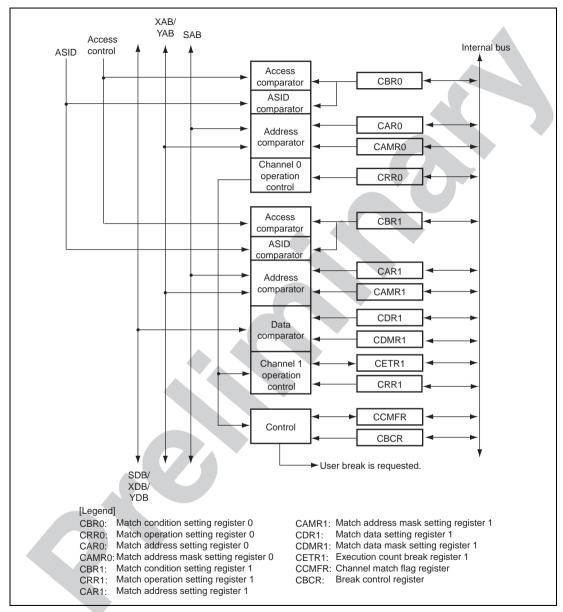

| User break        | Debugging with user break interrupts supported                                                                |

| controller (UBC)  | Two break channels                                                                                            |

|                   | <ul> <li>All of address, data value, access type, and data size can be set as break<br/>conditions</li> </ul> |

|                   | Supports sequential break function                                                                            |

| User debugging    | Supports E10A emulator                                                                                        |

| interface (H-UDI) | Realtime branch trace                                                                                         |

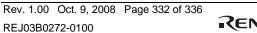

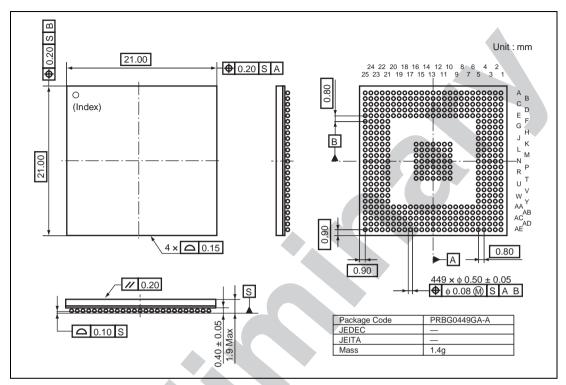

| Package           | PRBG0449GA-A, 449-pin BGA package: 21 mm × 21 mm, 0.8 mm-pitch                                                |

|                   | 417-pin LFBFA package: 13 mm × 13 mm, 0.5 mm-pitch                                                            |

| Power-supply      | • I/O: 3.0 to 3.6 V                                                                                           |

| voltage           | <ul> <li>Internal: 1.15 to 1.35 V</li> </ul>                                                                  |

| Process           | 90-nm CMOS, 7 metal layers                                                                                    |

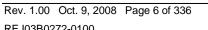

## 1.2 Block Diagram

Figure 1.1 shows a block diagram of this LSI.

Figure 1.1 Block Diagram

### 1.3 Pin Assignments

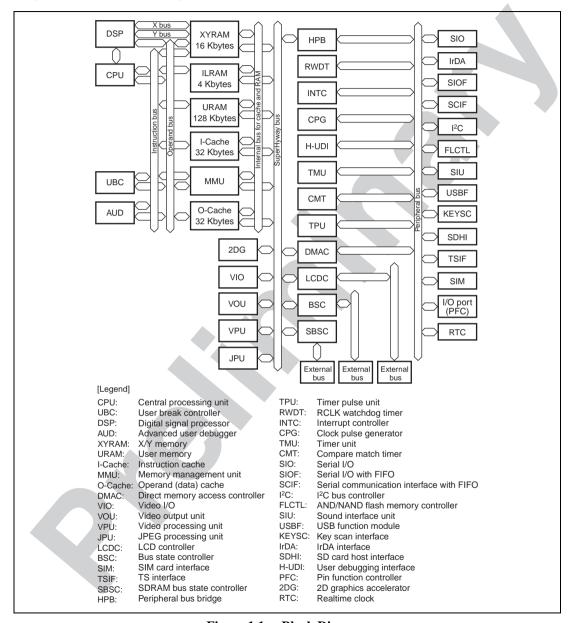

#### 1.3.1 BGA-449 Pin Assignments

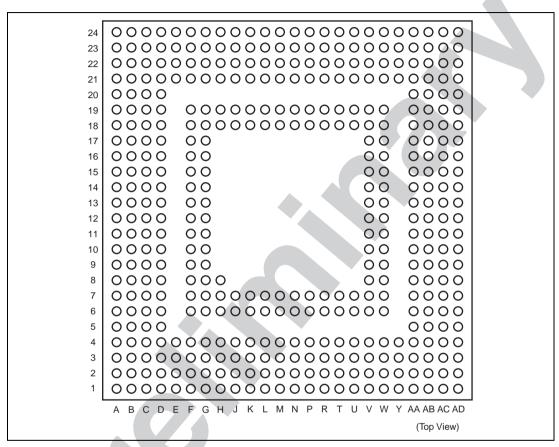

Figure 1.2 and table 1.2 show the pin assignments of BGA-449.

Figure 1.2 Pin Assignments (BGA-449)

**Table 1.2 Pin Assignments (BGA449)**

| Pin No. | Pin Name                           | Description                                                                                  | Treatment of<br>Unused Pin |

|---------|------------------------------------|----------------------------------------------------------------------------------------------|----------------------------|

| A1      | AV33                               | 3.3 V power supply for USB reference power supply circuit                                    | Always used                |

| A2      | V <sub>SS</sub>                    | Ground                                                                                       | Always used                |

| A3      | XTAL                               | Clock output                                                                                 | Open                       |

| A4      | EXTAL                              | External clock input                                                                         | Pulled down                |

| A5      | PTG3/AUDATA3                       | Port/AUD data output                                                                         | Open                       |

| A6      | AUDCK                              | AUD clock                                                                                    | Open                       |

| A7      | TCK                                | H-UDI test clock input                                                                       | Open                       |

| A8      | PTJ6                               | Port                                                                                         | Open                       |

| A9      | RCLK                               | 32.768 kHz clock input                                                                       | Always used                |

| A10     | TSTMD                              | Test mode setting                                                                            | Pulled up                  |

| A11     | MD0                                | Mode setting pin                                                                             | Always used                |

| A12     | PTS1/SCIF0_RXD                     | Port/SCIF receive data                                                                       | Open                       |

| A13     | PTK4/SIUAOLR/SIOF1_SYNC            | Port/SIU port A sound output L-R clock/SIOF1 frame signal                                    | Open                       |

| A14     | PTK1/SIUAOSLD/SIOF1_TXD            | Port/SIU port A sound output serial data/SIOF1 output data                                   | Open                       |

| A15     | PTK0/SIUMCKA/SIUFCKA/<br>SIOF1_MCK | Port/SIU port A master clock input/SIU port A sampling clock output/SIOF1 master clock input | Open                       |

| A16     | PTQ4/SIOF0_SYNC/<br>TS_SDEN        | Port/SIOF frame signal/<br>TS serial data enable                                             | Open                       |

| A17     | PTF6/SIUMCKB/SIUFCKB/<br>SIOMCK    | Port/SIU port B master clock input/SIU port B sampling clock output/SIO master clock         | Open                       |

| A18     | PTF2/SIUBILR/SIOD                  | Port/SIU port B sound input L-R clock/SIO Transmit/receive data                              | Open                       |

| A19     | PTD5/SDHID3                        | Port/SD data bus                                                                             | Pulled up                  |

| A20     | PTD1/SDHICMD                       | Port/SD command                                                                              | Open                       |