# SH68F093

8-Bit Microcontroller

## Features

- CMOS technology for low power consumption

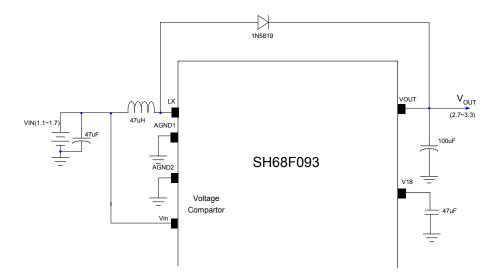

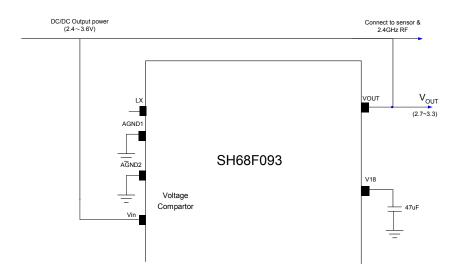

- Power Supply

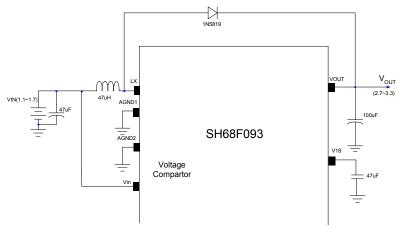

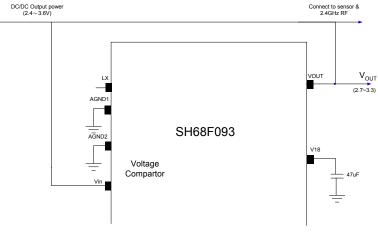

- DC-DC Input voltage ranges from 1.1V to 1.7V (static voltage without load)

- Fixed DC-DC output voltage: 2.7V or 3.3V

- Built-in 1.8V regulator for Micro-Processor (µP)

- 8-bit CMOS Micro-Processor (μP) core Instruction set is fully compatible with star

- Instruction set is fully compatible with standard 8051

Program Memory

- 16K Bytes Program Memory (flash ROM)

- Data Memory

- 512-byte DATA Memory: internal 256-byte RAM and external 256-byte RAM

- Interrupts

- 8 vector interrupt structure: two external interrupt, two base timer, resume Interrupt, wake-up Interrupt, OVL interrupt, and SPI interrupt

- Two programmable priority levels

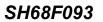

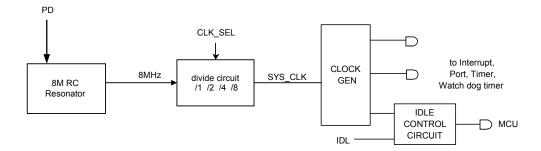

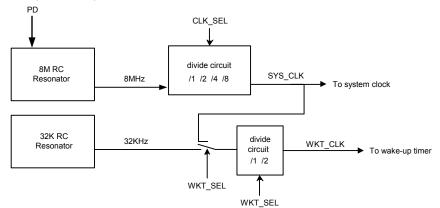

- On-Chip programmable RC Oscillator

- System Clock: 8MHz/4MHz/2MHz/1MHz

- Wake-up Timer: 8MHz/4MHz/2MHz/1MHz @IDLE mode

- Wake-up Timer: 32KHz/16KHz @Power down mode

- Operation frequency: Programmable

- Two 8-Bit auto-reloadable base timers

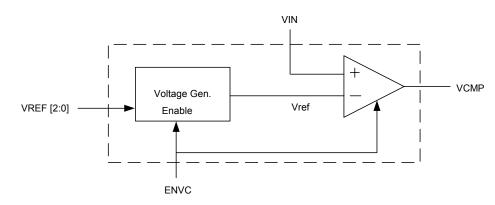

- One programmable voltage comparator

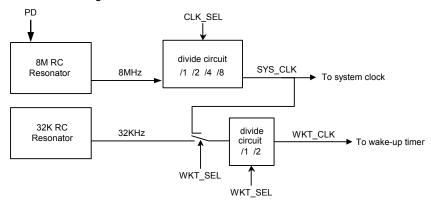

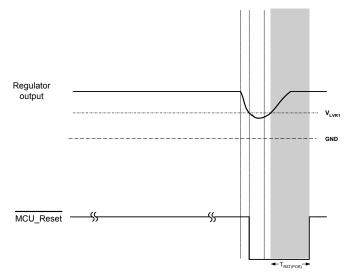

- Reset

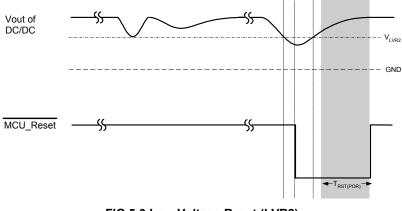

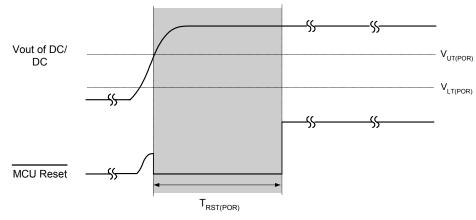

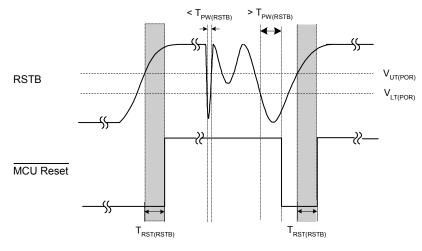

- Hardware reset: Low-Voltage Reset, Power-on reset, and External Reset

- Watch-dog Reset

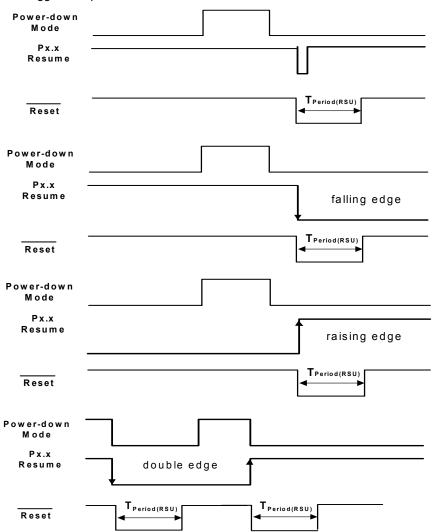

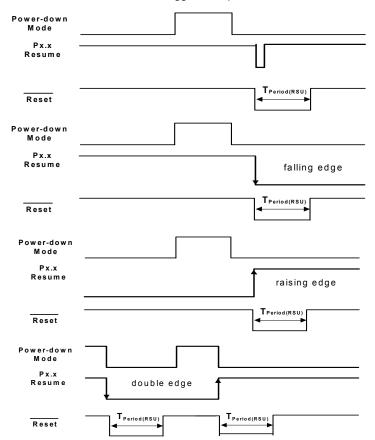

- Resume Reset

- General Purpose I/O

- Up to 20 Selectable GPIO on 28 pin SOP package

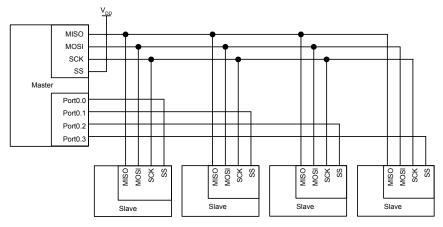

- Master/Slave SPI serial interface

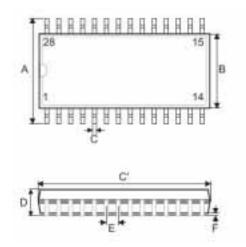

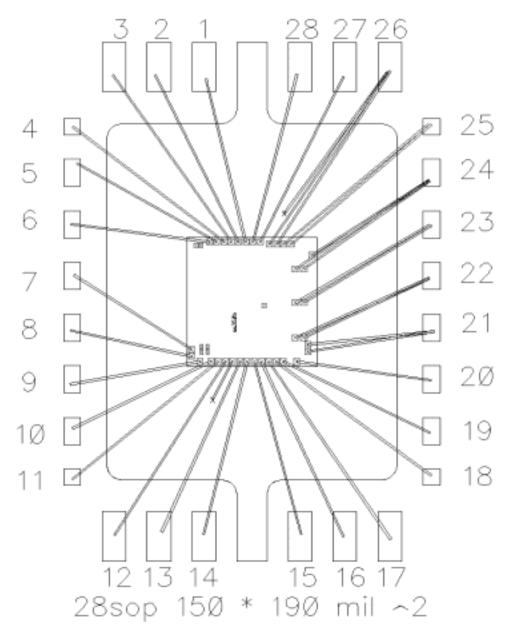

- Package

- 28 pin SOP, CHIPFORM

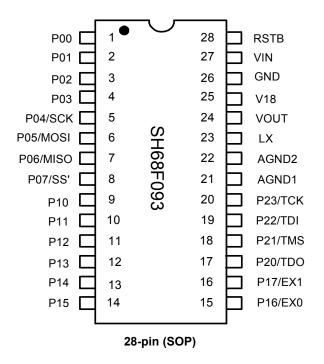

#### **General Description**

SH68F093, an 8-bit micro-controller, is designed for the high-performance and low-power RF mouse application. The microcontroller contains on-chip flash-type program 16K bytes ROM, internal 512 bytes RAM, two 8-bit base timers, a wake-up timer, a watch-dog timer, a DC-DC converter, a 1.8V regulator for µP core, built-in 8MHz RC resonator, POR/LVR reset, resume reset, programmable voltage comparator, and master/slave SPI interface.

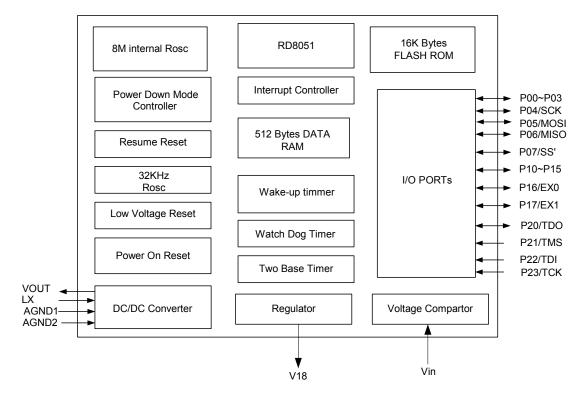

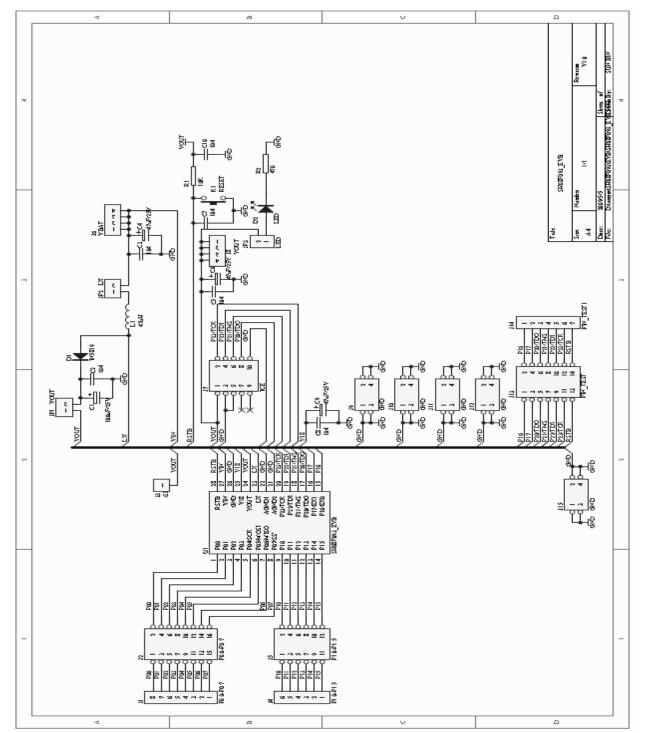

## **Pin Configurations**

#### **Block Diagram**

## Pin and Pad Descriptions

| Package Pin No.<br>28pin SOP | Pad No.  | Pad Name    | I/O        | Description                                             |

|------------------------------|----------|-------------|------------|---------------------------------------------------------|

| 1                            | 1        | P00         | I/O        | Bi-directional I/O pin                                  |

| 2                            | 2        | P01         | I/O        | Bi-directional I/O pin                                  |

| 3                            | 3        | P02         | I/O        | Bi-directional I/O pin                                  |

| 4                            | 4        | P03         | I/O        | Bi-directional I/O pin                                  |

| 5                            | 5        | P04<br>SCK  | I/O<br>I/O | Bi-directional I/O pin<br>SPI serial clock              |

| 6                            | 6        | P05<br>MOSI | I/O<br>I/O | Bi-directional I/O pin<br>SPI master output slave input |

| 7                            | 7        | P06<br>MISO | I/O<br>I/O | Bi-directional I/O pin<br>SPI master input slave output |

| 8                            | 8        | P07<br>/SS  | I/O<br>I   | Bi-directional I/O pin<br>SPI Slave Select              |

| 9                            | 9        | P10         | I/O        | Bi-directional I/O pin                                  |

| 10                           | 10       | P11         | I/O        | Bi-directional I/O pin                                  |

| 11                           | 11       | P12         | I/O        | Bi-directional I/O pin                                  |

| 12                           | 12       | P13         | I/O        | Bi-directional I/O pin                                  |

| 13                           | 14       | P14         | I/O        | Bi-directional I/O pin                                  |

| 14                           | 15       | P15         | I/O        | Bi-directional I/O pin                                  |

| 15                           | 16       | P16<br>EX0  | I/O<br>I   | Bi-directional I/O pin<br>External INT0                 |

| 16                           | 17       | P17<br>EX1  | I/O<br>I   | Bi-directional I/O pin<br>External INT1                 |

| 17                           | 18       | P20<br>TDO  | I/O<br>0   | Bi-directional I/O pin<br>JTAG DATA output pin          |

| 18                           | 19       | P21<br>TMS  | I<br>I     | Uni-directional input pin<br>JTAG MODE select pin       |

| 19                           | 20       | P22<br>TDI  | I<br>I     | Uni-directional input pin<br>JTAG DATA input pin        |

| 20                           | 21       | P23<br>TCK  |            | Uni-directional Input pin<br>JTAG clock input pin       |

| 21                           | 22/23    | AGND1       | I          | Analog Ground                                           |

| 22                           | 24/25    | AGND2       | I          | Analog Ground                                           |

| 23                           | 26/27    | LX          | Ι          | DC-DC Switching pin                                     |

| 24                           | 28/29/30 | VOUT/VDDIN  | I/O        | DC-DC Voltage output pin                                |

| 25                           | 31/32    | V18/VCC     | I/O        | Regulator pin                                           |

| 26                           | 33/34    | GND         | Ι          | Ground                                                  |

| 27                           | 35       | VIN         | Ι          | Voltage Comparator                                      |

| 28                           | 36       | RSTB        | Ι          | Reset pin                                               |

#### **Functional Description**

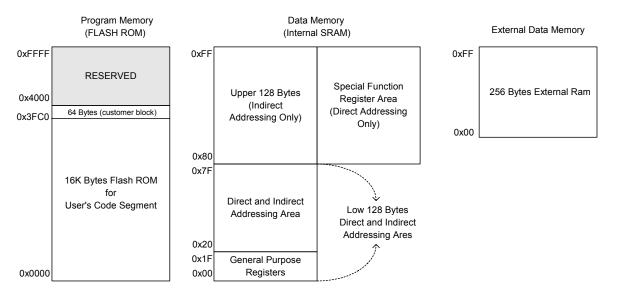

#### 1. Memory

#### 1.1. Memory Allocation

There are 16K bytes Program Memory and 512 bytes Data Memory.

#### 1.2. Program Memory

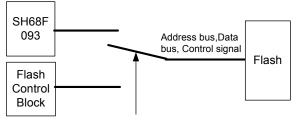

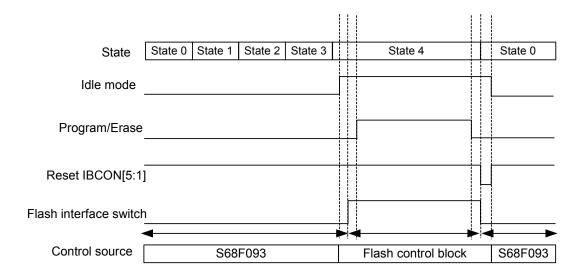

SH68F093 embeds 16K Bytes (0000H - 3FFFH) on-chip program memory for program code. The flash program memory provides electrical erasure and programming.

**Note:** The 0<sup>th</sup> sector (0000H - 03FFH) and the last 64 bytes for customer block (3FC0H - 3FFFH) are reserved and can't be used as program memory.

#### 1.3. Data Memory

SH68F093 provides internal 256-byte RAM and external 256-byte RAM.

Internal Special Function Registers (SFR): There are 128 bytes SFR, which is the internal reserved memory for system registers in the  $\mu$ P.

#### FIG. 1-1 SH68F093 Program/Data Memory Map

**Note:** SH68F093 provides traditional method for accessing of external RAM. Use MOVX A, @Ri or MOVX @Ri, A to access 256-byte external RAM.

## 1.4. Registers

|                                                                                                                             |                                                              |                                                                                                                                                                                                                                |                                                             |                                                                      | Syste                                                                                                        | m Registers                                                                                                    | ;                                                                                           |                                                                         |                                                                              |                                                                                                     |                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| Address                                                                                                                     | Name                                                         | Initial Value                                                                                                                                                                                                                  | R/W                                                         | Bit7                                                                 | Bit6                                                                                                         | Bit5                                                                                                           | Bit4                                                                                        | Bit3                                                                    | Bit2                                                                         | Bit1                                                                                                | Bit0                                                                         |

| 00E0H                                                                                                                       | ACC                                                          | 00H                                                                                                                                                                                                                            | R/W                                                         | ACC.7                                                                | ACC.6                                                                                                        | ACC.5                                                                                                          | ACC.4                                                                                       | ACC.3                                                                   | ACC.2                                                                        | ACC.1                                                                                               | ACC.0                                                                        |

| 00F0H                                                                                                                       | В                                                            | 00H                                                                                                                                                                                                                            | R/W                                                         | B.7                                                                  | B.6                                                                                                          | B.5                                                                                                            | B.4                                                                                         | B.3                                                                     | B.2                                                                          | B.1                                                                                                 | B.0                                                                          |

| 00D0H                                                                                                                       | PSW                                                          | 00H                                                                                                                                                                                                                            | R/W                                                         | CY                                                                   | AC                                                                                                           | F0                                                                                                             | RS1                                                                                         | RS0                                                                     | OV                                                                           | 0                                                                                                   | Р                                                                            |

| 0081H                                                                                                                       | SP                                                           | 07H                                                                                                                                                                                                                            | R/W                                                         | SP7                                                                  | SP6                                                                                                          | SP5                                                                                                            | SP4                                                                                         | SP3                                                                     | SP2                                                                          | SP1                                                                                                 | SP0                                                                          |

| 0082H                                                                                                                       | DPL                                                          | 00H                                                                                                                                                                                                                            | R/W                                                         | DPL7                                                                 | DPL6                                                                                                         | DPL5                                                                                                           | DPL4                                                                                        | DPL3                                                                    | DPL2                                                                         | DPL1                                                                                                | DPL0                                                                         |

| 0083H                                                                                                                       | DPH                                                          | 00H                                                                                                                                                                                                                            | R/W                                                         | DPH7                                                                 | DPH6                                                                                                         | DPH5                                                                                                           | DPH4                                                                                        | DPH3                                                                    | DPH2                                                                         | DPH1                                                                                                | DPH0                                                                         |

| 00F7h                                                                                                                       | XPAGE                                                        | 00H                                                                                                                                                                                                                            | R/W                                                         | XPAGE7                                                               | XPAGE6                                                                                                       | XPAGE5                                                                                                         | XPAGE4                                                                                      | XPAGE3                                                                  | XPAGE2                                                                       | XPAGE1                                                                                              | XPAGE0                                                                       |

|                                                                                                                             |                                                              |                                                                                                                                                                                                                                |                                                             | Idle a                                                               | and Power-d                                                                                                  | own Contro                                                                                                     | I Registers                                                                                 |                                                                         |                                                                              |                                                                                                     |                                                                              |

| Address                                                                                                                     | Name                                                         | Initial Value                                                                                                                                                                                                                  | R/W                                                         | Bit7                                                                 | Bit6                                                                                                         | Bit5                                                                                                           | Bit4                                                                                        | Bit3                                                                    | Bit2                                                                         | Bit1                                                                                                | Bit0                                                                         |

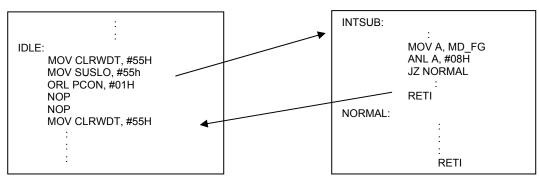

| 0087H                                                                                                                       | PCON                                                         | 0000000B                                                                                                                                                                                                                       | R/W                                                         | 0                                                                    | 0                                                                                                            | 0                                                                                                              | 0                                                                                           | 0                                                                       | 0                                                                            | PD                                                                                                  | IDL                                                                          |

| 008EH                                                                                                                       | SUSLO                                                        | 00H                                                                                                                                                                                                                            | R/W                                                         | SUSL7                                                                | SUSL6                                                                                                        | SUSL5                                                                                                          | SUSL4                                                                                       | SUSL3                                                                   | SUSL2                                                                        | SUSL1                                                                                               | SUSL0                                                                        |

| 00AFH                                                                                                                       | PRCON                                                        | 0000001B                                                                                                                                                                                                                       | R/W                                                         | 0                                                                    | 0                                                                                                            | 0                                                                                                              | 0                                                                                           | 0                                                                       | ENWDT                                                                        | 0                                                                                                   | ENLVR                                                                        |

|                                                                                                                             |                                                              |                                                                                                                                                                                                                                |                                                             |                                                                      |                                                                                                              | ) Ports Regi                                                                                                   |                                                                                             |                                                                         |                                                                              |                                                                                                     |                                                                              |

| Address                                                                                                                     | Name                                                         | Initial Value                                                                                                                                                                                                                  | R/W                                                         | Bit7                                                                 | Bit6                                                                                                         | Bit5                                                                                                           | Bit4                                                                                        | Bit3                                                                    | Bit2                                                                         | Bit1                                                                                                | Bit0                                                                         |

| 0080H                                                                                                                       | P0                                                           | 11111111B                                                                                                                                                                                                                      | R/W                                                         | P0.7                                                                 | P0.6                                                                                                         | P0.5                                                                                                           | P0.4                                                                                        | P0.3                                                                    | P0.2                                                                         | P0.1                                                                                                | P0.0                                                                         |

| 0090H                                                                                                                       | P1                                                           | 11111111B                                                                                                                                                                                                                      | R/W                                                         | P1.7                                                                 | P1.6                                                                                                         | P1.5                                                                                                           | P1.4                                                                                        | P1.3                                                                    | P1.2                                                                         | P1.1                                                                                                | P1.0                                                                         |

| 00A0H                                                                                                                       | P2                                                           | 00011111B                                                                                                                                                                                                                      | R/W                                                         | 0                                                                    | 0                                                                                                            | 0                                                                                                              | 0                                                                                           | P2.3                                                                    | P2.2                                                                         | P2.1                                                                                                | P2.0                                                                         |

| 00A2H                                                                                                                       | POWK                                                         | 0000000B                                                                                                                                                                                                                       | R/W                                                         | P0WK7                                                                | P0WK6                                                                                                        | P0WK5                                                                                                          | P0WK4                                                                                       | P0WK3                                                                   | P0WK2                                                                        | P0WK1                                                                                               | P0WK0                                                                        |

| 00A3H                                                                                                                       | P1WK                                                         | 00000000B                                                                                                                                                                                                                      | R/W                                                         | P1WK7                                                                | P1WK6                                                                                                        | P1WK5                                                                                                          | P1WK4                                                                                       | P1WK3                                                                   | P1WK2                                                                        | P1WK1                                                                                               | P1WK0                                                                        |

| 00A4H                                                                                                                       | P2WK                                                         | 00000000B                                                                                                                                                                                                                      | R/W                                                         | 0                                                                    | 0                                                                                                            | 0                                                                                                              | 0                                                                                           | P2WK3                                                                   | P2WK2                                                                        | P2WK1                                                                                               | P2WK0                                                                        |

| 009AH                                                                                                                       | P0CON                                                        | 0000000B                                                                                                                                                                                                                       | R/W                                                         | P0CON7                                                               | P0CON6                                                                                                       | P0CON5                                                                                                         | P0CON4                                                                                      | P0CON3                                                                  | P0CON2                                                                       | P0CON1                                                                                              | P0CON0                                                                       |

| 009BH                                                                                                                       | P1CON                                                        | 00000000B                                                                                                                                                                                                                      | R/W                                                         | P1CON7                                                               | P1CON6                                                                                                       | P1CON5                                                                                                         | P1CON4                                                                                      | P1CON3                                                                  | P1CON2                                                                       | P1CON1                                                                                              | P1CON0                                                                       |

| 009CH                                                                                                                       | P2CON                                                        | 0000000B                                                                                                                                                                                                                       | R/W                                                         | 0                                                                    | 0                                                                                                            | 0                                                                                                              | 0                                                                                           | P2CON3                                                                  | P2CON2                                                                       | P2CON1                                                                                              | P2CON0                                                                       |

| Addamaa                                                                                                                     | N                                                            | he total Malace                                                                                                                                                                                                                | DAM                                                         | D147                                                                 |                                                                                                              | Registers                                                                                                      | Dite                                                                                        | <b>D</b> 140                                                            | D:40                                                                         | Ditd                                                                                                | Dito                                                                         |

| Address                                                                                                                     | Name                                                         | Initial Value                                                                                                                                                                                                                  | R/W                                                         | Bit7                                                                 | Bit6                                                                                                         | Bit5                                                                                                           | Bit4                                                                                        | Bit3                                                                    | Bit2                                                                         | Bit1                                                                                                | Bit0                                                                         |

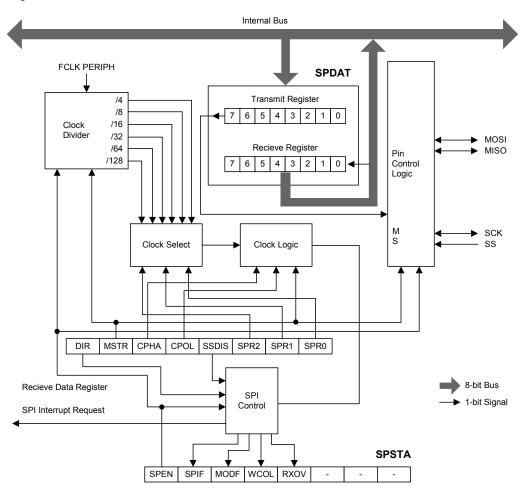

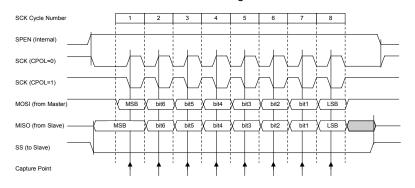

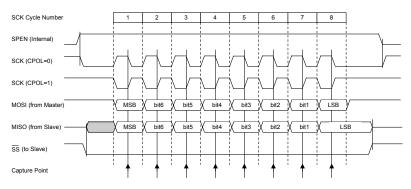

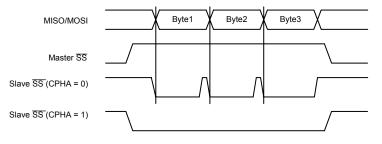

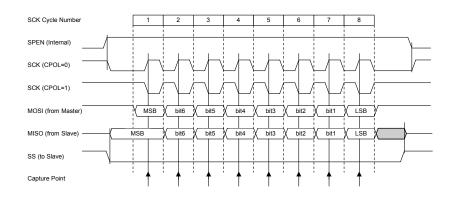

| 009DH                                                                                                                       | SPCON                                                        | 00H                                                                                                                                                                                                                            | R/W                                                         | DIR                                                                  | MSTR                                                                                                         | CPHA                                                                                                           | CPOL                                                                                        | SSDIS                                                                   | SPR2                                                                         | SPR1                                                                                                | SPR0                                                                         |

| 00F8H                                                                                                                       | SPSTA                                                        | 00H                                                                                                                                                                                                                            | R/W<br>R/W                                                  | SPEN                                                                 | SPIF                                                                                                         | MODF<br>SPD5                                                                                                   | WCOL                                                                                        | RXOV                                                                    | 0                                                                            | 0                                                                                                   | 0                                                                            |

| 009EH                                                                                                                       | SPDAT                                                        | 00H                                                                                                                                                                                                                            | R/W                                                         | SPD7                                                                 | SPD6                                                                                                         | se Timers                                                                                                      | SPD4                                                                                        | SPD3                                                                    | SPD2                                                                         | SPD1                                                                                                | SPD0                                                                         |

| Address                                                                                                                     | Name                                                         | Initial Value                                                                                                                                                                                                                  | R/W                                                         | Bit7                                                                 | Bit6                                                                                                         | Bit5                                                                                                           | Bit4                                                                                        | Bit3                                                                    | Bit2                                                                         | Bit1                                                                                                | Bit0                                                                         |

| 00D2H                                                                                                                       | BT0                                                          | 00H                                                                                                                                                                                                                            | R/W                                                         | BT07                                                                 | BT06                                                                                                         | BT05                                                                                                           | BT04                                                                                        | BT03                                                                    | BT02                                                                         | BT01                                                                                                | BT00                                                                         |

| 00D2H                                                                                                                       | BT0<br>BT1                                                   | 00H                                                                                                                                                                                                                            | R/W                                                         | BT07<br>BT17                                                         | BT00<br>BT16                                                                                                 | BT05<br>BT15                                                                                                   | BT04<br>BT14                                                                                | BT03<br>BT13                                                            | BT02<br>BT12                                                                 | BT01<br>BT11                                                                                        | BT00<br>BT10                                                                 |

| 00D4H                                                                                                                       | BTCON                                                        | 00H                                                                                                                                                                                                                            | R/W                                                         | ENBT1                                                                | BT1M2                                                                                                        | BT1M1                                                                                                          | BT1M0                                                                                       | ENBT0                                                                   | BT0M2                                                                        | BT0M1                                                                                               | BTOMO                                                                        |

| 00D4H<br>00D5H                                                                                                              | BTCLK                                                        | 00H                                                                                                                                                                                                                            | R/W                                                         | 0                                                                    | 0                                                                                                            | BT1CLK1                                                                                                        | BT1CLK0                                                                                     | 0                                                                       | 0                                                                            | BT0CLK1                                                                                             | BTOCLKO                                                                      |

| CODON                                                                                                                       | BIOLIC                                                       | 0011                                                                                                                                                                                                                           | 10.00                                                       | -                                                                    | -                                                                                                            |                                                                                                                | trol Register                                                                               |                                                                         |                                                                              | BIOOLICI                                                                                            | BIOOLIKU                                                                     |

| Address                                                                                                                     | Name                                                         | Initial Value                                                                                                                                                                                                                  | R/W                                                         | Bit7                                                                 | Bit6                                                                                                         | Bit5                                                                                                           | Bit4                                                                                        | Bit3                                                                    | Bit2                                                                         | Bit1                                                                                                | Bit0                                                                         |

|                                                                                                                             | WKT CON                                                      | F0H                                                                                                                                                                                                                            |                                                             | WKT_SEL1                                                             |                                                                                                              |                                                                                                                |                                                                                             |                                                                         | WKT2                                                                         | WKT1                                                                                                |                                                                              |

|                                                                                                                             |                                                              |                                                                                                                                                                                                                                |                                                             |                                                                      | WAL SELU                                                                                                     | ULK SELT                                                                                                       | ULK SELU                                                                                    | VVNIS                                                                   |                                                                              |                                                                                                     | VVNIU                                                                        |

|                                                                                                                             | RES CON                                                      | 00H                                                                                                                                                                                                                            |                                                             | 0                                                                    |                                                                                                              | OLK_SELT                                                                                                       | CLK_SEL0<br>0                                                                               | WKT3<br>0                                                               | 0                                                                            |                                                                                                     | WKT0<br>RES0                                                                 |

|                                                                                                                             | RES_CON                                                      | 00H                                                                                                                                                                                                                            | R/W                                                         |                                                                      | 0                                                                                                            | 0                                                                                                              | 0                                                                                           |                                                                         |                                                                              | RES1                                                                                                | RES0                                                                         |

|                                                                                                                             | -                                                            |                                                                                                                                                                                                                                | R/W                                                         | 0                                                                    | 0<br>Reset &                                                                                                 | 0<br>Resume Fla                                                                                                | 0<br>ag                                                                                     | 0                                                                       | 0                                                                            | RES1                                                                                                | RES0                                                                         |

| Address                                                                                                                     | -                                                            | Initial Value                                                                                                                                                                                                                  | R/W                                                         | 0                                                                    | 0                                                                                                            | 0<br>Resume Fla<br>Bit5                                                                                        | 0<br>ag<br>Bit4                                                                             |                                                                         | 0<br>Bit2                                                                    |                                                                                                     |                                                                              |

| Address                                                                                                                     | Name                                                         |                                                                                                                                                                                                                                | R/W<br><b>R/W</b>                                           | 0<br>Bit7<br>0                                                       | 0<br>Reset &<br>Bit6                                                                                         | 0<br>Resume Fla<br>Bit5<br>FLVR1                                                                               | 0<br>ag<br>Bit4<br>FLVR2                                                                    | 0<br>Bit3                                                               | 0<br>Bit2                                                                    | RES1<br>Bit1                                                                                        | RES0<br>Bit0                                                                 |

| Address                                                                                                                     | Name                                                         | Initial Value                                                                                                                                                                                                                  | R/W<br><b>R/W</b>                                           | 0<br>Bit7<br>0                                                       | 0<br>Reset &<br>Bit6<br>0                                                                                    | 0<br>Resume Fla<br>Bit5<br>FLVR1                                                                               | 0<br>ag<br>Bit4<br>FLVR2                                                                    | 0<br>Bit3                                                               | 0<br>Bit2                                                                    | RES1<br>Bit1                                                                                        | RES0<br>Bit0                                                                 |

| Address<br>0096H                                                                                                            | Name<br>MODE_FG                                              | Initial Value<br>00000001B                                                                                                                                                                                                     | R/W<br><b>R/W</b><br>R/W                                    | 0<br>Bit7<br>0<br>Wa                                                 | 0<br>Reset &<br>Bit6<br>0<br>tch-Dog Tin<br>Bit6                                                             | 0<br>Resume Fla<br>Bit5<br>FLVR1<br>ner Control                                                                | 0<br>Bit4<br>FLVR2<br>Registers<br>Bit4                                                     | 0<br>Bit3<br>PORT_RSU<br>Bit3                                           | 0<br>Bit2<br>WKUP_RS                                                         | RES1<br>Bit1<br>WDT<br>Bit1                                                                         | RES0<br>Bit0<br>POF<br>Bit0                                                  |

| Address<br>0096H<br>Address<br>0093H                                                                                        | Name<br>MODE_FG<br>Name                                      | Initial Value<br>00000001B<br>Initial Value                                                                                                                                                                                    | R/W<br>R/W<br>R/W                                           | 0<br>Bit7<br>0<br>Wa<br>Bit7                                         | 0<br>Reset &<br>Bit6<br>0<br>tch-Dog Tin<br>Bit6                                                             | 0<br>Resume Fla<br>Bit5<br>FLVR1<br>ner Control I<br>Bit5                                                      | 0<br>Bit4<br>FLVR2<br>Registers<br>Bit4                                                     | 0<br>Bit3<br>PORT_RSU<br>Bit3                                           | 0<br>Bit2<br>WKUP_RS<br>Bit2                                                 | RES1<br>Bit1<br>WDT<br>Bit1                                                                         | RES0<br>Bit0<br>POF<br>Bit0                                                  |

| Address<br>0096H<br>Address<br>0093H                                                                                        | Name<br>MODE_FG<br>Name<br>CLRWD                             | Initial Value<br>00000001B<br>Initial Value<br>55H                                                                                                                                                                             | R/W<br>R/W<br>R/W<br>W                                      | 0<br>Bit7<br>0<br>Wa<br>Bit7<br>CLRWDT7                              | 0<br>Reset &<br>Bit6<br>0<br>tch-Dog Tin<br>Bit6<br>CLRWDT6<br>0                                             | 0<br>Resume Fli<br>Bit5<br>FLVR1<br>ner Control I<br>Bit5<br>CLRWDT5                                           | 0<br>ag<br>FLVR2<br>Registers<br>Bit4<br>CLRWDT4<br>0                                       | 0<br>Bit3<br>PORT_RSU<br>Bit3<br>CLRWDT3                                | 0<br>Bit2<br>WKUP_RS<br>Bit2<br>CLRWDT2                                      | RES1<br>Bit1<br>WDT<br>Bit1<br>CLRWDT1                                                              | RES0<br>Bit0<br>POF<br>Bit0<br>CLRWDT0                                       |

| Address           0096H           Address           0093H           0094H           Address                                 | Name<br>MODE_FG<br>Name<br>CLRWD                             | Initial Value<br>00000001B<br>Initial Value<br>55H                                                                                                                                                                             | R/W<br>R/W<br>R/W<br>W                                      | 0<br>Bit7<br>0<br>Wa<br>Bit7<br>CLRWDT7                              | 0<br>Reset &<br>Bit6<br>0<br>tch-Dog Tin<br>Bit6<br>CLRWDT6<br>0                                             | 0<br>Resume Fli<br>FLVR1<br>ner Control I<br>Bit5<br>CLRWDT5<br>0                                              | 0<br>ag<br>FLVR2<br>Registers<br>Bit4<br>CLRWDT4<br>0                                       | 0<br>Bit3<br>PORT_RSU<br>Bit3<br>CLRWDT3                                | 0<br>Bit2<br>WKUP_RS<br>Bit2<br>CLRWDT2                                      | RES1<br>Bit1<br>WDT<br>Bit1<br>CLRWDT1                                                              | RES0<br>Bit0<br>POF<br>Bit0<br>CLRWDT0                                       |

| Address           0096H           Address           0093H           0094H                                                   | Name<br>MODE_FG<br>Name<br>CLRWD<br>PREWD                    | Initial Value<br>00000001B<br>Initial Value<br>55H<br>05H                                                                                                                                                                      | R/W<br>R/W<br>R/W<br>W<br>R/W                               | 0<br>Bit7<br>0<br>Wa<br>Bit7<br>CLRWDT7<br>0                         | 0<br>Reset &<br>Bit6<br>0<br>tch-Dog Tin<br>Bit6<br>CLRWDT6<br>0<br>Interrupt C                              | 0<br>Resume Fli<br>FLVR1<br>ner Control I<br>Bit5<br>CLRWDT5<br>0<br>control Regi                              | 0<br>ag<br>FLVR2<br>Registers<br>Bit4<br>CLRWDT4<br>0<br>sters                              | 0<br>Bit3<br>PORT_RSU<br>Bit3<br>CLRWDT3<br>0                           | 0<br>Bit2<br>WKUP_RS<br>Bit2<br>CLRWDT2<br>WDT2                              | RES1<br>Bit1<br>WDT<br>Bit1<br>CLRWDT1<br>WDT1                                                      | RES0<br>Bit0<br>POF<br>Bit0<br>CLRWDT0<br>WDT0                               |

| Address<br>0096H<br>Address<br>0093H<br>0094H<br>0094H<br>Address<br>00A8H<br>00A9                                          | Name<br>MODE_FG<br>CLRWD<br>PREWD<br>Name<br>IE<br>IE2       | Initial Value<br>00000001B<br>Initial Value<br>55H<br>05H<br>Initial Value                                                                                                                                                     | R/W<br>R/W<br>R/W<br>R/W<br>R/W                             | 0<br>Bit7<br>0<br>Wa<br>Bit7<br>CLRWDT7<br>0<br>Bit7                 | 0<br>Reset &<br>Bit6<br>0<br>tch-Dog Tin<br>Bit6<br>CLRWDT6<br>0<br>Interrupt C<br>Bit6<br>EOVL<br>0         | 0<br>Resume Fli<br>FLVR1<br>ner Control I<br>Bit5<br>CLRWDT5<br>0<br>control Regi<br>Bit5<br>EWKT<br>0         | 0<br>ag<br>FLVR2<br>Registers<br>Bit4<br>CLRWDT4<br>0<br>sters<br>Bit4<br>ERSU<br>0         | 0<br>Bit3<br>PORT_RSU<br>Bit3<br>0<br>Bit3<br>EBT1<br>0                 | 0<br>Bit2<br>WKUP_RS<br>Bit2<br>CLRWDT2<br>WDT2<br>Bit2                      | RES1<br>Bit1<br>WDT<br>Bit1<br>CLRWDT1<br>WDT1<br>Bit1                                              | RES0<br>Bit0<br>POF<br>Bit0<br>CLRWDT0<br>WDT0<br>Bit0                       |

| Address           0096H           Address           0093H           0094H           Address           0094H           0094H | Name<br>MODE_FG<br>CLRWD<br>PREWD<br>Name<br>IE              | Initial Value           0000001B           Initial Value           55H           05H           Initial Value           0000000B                                                                                                | R/W<br>R/W<br>R/W<br>W<br>R/W<br>R/W                        | 0<br>Bit7<br>0<br>Wa<br>Bit7<br>CLRWDT7<br>0<br>Bit7<br>EA           | 0<br>Reset &<br>Bit6<br>0<br>tch-Dog Tin<br>Bit6<br>CLRWDT6<br>0<br>Interrupt C<br>Bit6<br>EOVL              | 0<br>Resume Fli<br>Bit5<br>FLVR1<br>ner Control I<br>Bit5<br>CLRWDT5<br>0<br>control Regi<br>Bit5<br>EWKT      | 0<br>ag<br>FLVR2<br>Registers<br>Bit4<br>CLRWDT4<br>0<br>sters<br>Bit4<br>ERSU              | 0<br>Bit3<br>PORT_RSU<br>CLRWDT3<br>0<br>Bit3<br>EBT1                   | 0<br>Bit2<br>WKUP_RS<br>Bit2<br>CLRWDT2<br>WDT2<br>Bit2<br>EBT0              | RES1<br>Bit1<br>WDT<br>Bit1<br>CLRWDT1<br>WDT1<br>Bit1<br>EX1                                       | RES0<br>Bit0<br>POF<br>CLRWDT0<br>WDT0<br>Bit0<br>EX0                        |

| Address<br>0096H<br>Address<br>0093H<br>0094H<br>0094H<br>M<br>Address<br>00A8H<br>00A9<br>00B8H<br>00B9H                   | Name<br>MODE_FG<br>CLRWD<br>PREWD<br>Name<br>IE<br>IE2       | Initial Value           0000001B           Initial Value           55H           05H           Initial Value           0000000B           0000000B           0000000B           0000000B           0000000B           0000000B | R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W | 0<br>Bit7<br>0<br>Wa<br>Bit7<br>CLRWDT7<br>0<br>Bit7<br>EA<br>0      | 0<br>Reset &<br>Bit6<br>0<br>tch-Dog Tin<br>Bit6<br>CLRWDT6<br>0<br>Interrupt C<br>Bit6<br>EOVL<br>0         | 0<br>Resume Fli<br>FLVR1<br>ner Control I<br>Bit5<br>CLRWDT5<br>0<br>control Regi<br>Bit5<br>EWKT<br>0         | 0<br>ag<br>FLVR2<br>Registers<br>Bit4<br>CLRWDT4<br>0<br>sters<br>Bit4<br>ERSU<br>0         | 0<br>Bit3<br>PORT_RSU<br>CLRWDT3<br>0<br>Bit3<br>EBT1<br>0<br>PBT1<br>0 | 0<br>Bit2<br>WKUP_RS<br>Bit2<br>CLRWDT2<br>WDT2<br>Bit2<br>EBT0<br>0         | RES1<br><b>Bit1</b><br>WDT<br><b>Bit1</b><br>CLRWDT1<br>WDT1<br><b>Bit1</b><br>EX1<br>0<br>PX1<br>0 | RES0<br>Bit0<br>POF<br>CLRWDT0<br>WDT0<br>Bit0<br>EX0<br>ESPI                |

| Address<br>0096H<br>Address<br>0093H<br>0094H<br>0094H<br>Address<br>00A8H<br>00A9<br>00B8H                                 | Name<br>MODE_FG<br>CLRWD<br>PREWD<br>Name<br>IE<br>IE2<br>IP | Initial Value           0000001B           Initial Value           55H           05H           Initial Value           0000000B           0000000B           0000000B           0000000B                                       | R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W        | 0<br>Bit7<br>0<br>Wa<br>Bit7<br>CLRWDT7<br>0<br>Bit7<br>EA<br>0<br>0 | 0<br>Reset &<br>Bit6<br>0<br>tch-Dog Tin<br>Bit6<br>CLRWDT6<br>0<br>Interrupt C<br>Bit6<br>EOVL<br>0<br>POVL | 0<br>Resume Fla<br>FLVR1<br>ner Control I<br>Bit5<br>CLRWDT5<br>0<br>control Regi<br>Bit5<br>EWKT<br>0<br>PWKT | 0<br>ag<br>FLVR2<br>Registers<br>Bit4<br>CLRWDT4<br>0<br>sters<br>Bit4<br>ERSU<br>0<br>PRSU | 0<br>Bit3<br>PORT_RSU<br>CLRWDT3<br>0<br>Bit3<br>EBT1<br>0<br>PBT1      | 0<br>Bit2<br>WKUP_RS<br>Bit2<br>CLRWDT2<br>WDT2<br>Bit2<br>EBT0<br>0<br>PBT0 | RES1<br>Bit1<br>WDT<br>CLRWDT1<br>WDT1<br>Bit1<br>EX1<br>0<br>PX1                                   | RES0<br>Bit0<br>POF<br>Bit0<br>CLRWDT0<br>WDT0<br>Bit0<br>EX0<br>ESPI<br>PX0 |

#### Register (continued)

|         |          |               |     | Info      | prmation Blo | ock Control | Registers     |           |           |           |           |

|---------|----------|---------------|-----|-----------|--------------|-------------|---------------|-----------|-----------|-----------|-----------|

| Address | Name     | Initial Value | R/W | Bit7      | Bit6         | Bit5        | Bit4          | Bit3      | Bit2      | Bit1      | Bit0      |

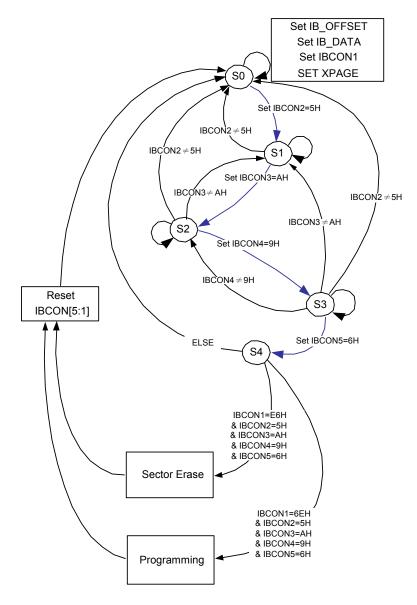

| 00F2H   | IBCON1   | 00H           | R/W | IBCON17   | IBCON16      | IBCON15     | IBCON14       | IBCON13   | IBCON12   | IBCON11   | IBCON10   |

| 00F3H   | IBCON2   | 00H           | R/W | 0         | 0            | 0           | 0             | IBCON23   | IBCON22   | IBCON21   | IBCON20   |

| 00F4H   | IBCON3   | 00H           | R/W | 0         | 0            | 0           | 0             | IBCON33   | IBCON32   | IBCON31   | IBCON30   |

| 00F5H   | IBCON4   | 00H           | R/W | 0         | 0            | 0           | 0             | IBCON43   | IBCON42   | IBCON41   | IBCON40   |

| 00F6H   | IBCON5   | 00H           | R/W | 0         | 0            | 0           | 0             | IBCON53   | IBCON52   | IBCON51   | IBCON50   |

| 00FBH   | IBOFFSET | 00H           | R/W | IBOFFSET7 | IBOFFSET6    | IBOFFSET5   | IBOFFSET4     | IBOFFSET3 | IBOFFSET2 | IBOFFSET1 | IBOFFSET0 |

| 00FCH   | IB_DAT   | 00H           | R/W | IBDATA7   | IBDATA6      | IBDATA5     | IBDATA4       | IBDATA3   | IBDATA2   | IBDATA1   | IBDATA0   |

|         |          |               |     | DC-DC &   | Voltage Co   | mparator Co | ontrol Regist | ters      |           |           |           |

| Address | Name     | Initial Value | R/W | Bit7      | Bit6         | Bit5        | Bit4          | Bit3      | Bit2      | Bit1      | Bit0      |

| 00C7H   | VSEL_D   | 0010000B      | R/W | 0         | 0            | DC_EN       | DCPD2         | DCPD1     | 0         | VSEL_DC   | VSEL_DC0  |

| 00C4H   | VC_CO    | 0100000B      | R/W | ENVC      | VREF2        | VREF1       | VREF0         | 0         | 0         | 0         | VCMP      |

Note1: Unlike the other resets (POR, LVR, and RST), resume reset will not reset some registers values

**Note2:** The read/write operations of reserved control registers may cause some unexpected events. Please remain aware during system software development.

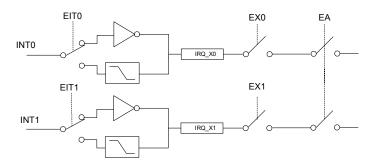

#### 2. Interrupt and Reset Vectors

- External Interrupt 0

- External Interrupt 1

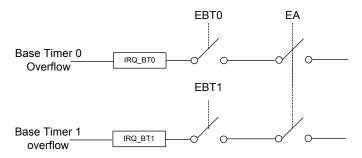

- Base Timer 0

- Base Timer 1

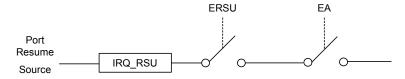

- Resume Interrupt

- Wake-up Interrupt

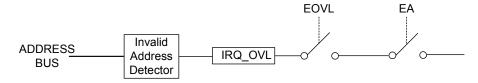

- OVL Interrupt

- SPI Interrupt

| Address | Interrupt Source     | Enable | IRQ Flag | Description                            |

|---------|----------------------|--------|----------|----------------------------------------|

| 0000H   | Reset                | -      | -        | System Reset                           |

| 0003H   | External Interrupt 0 | IE.0   | EX0      | P16 (falling edge/low level voltage)   |

| 000BH   | External Interrupt 1 | IE.1   | EX1      | P17 (falling edge/low level voltage)   |

| 0013H   | Base Timer 0         | IE.2   | EBT0     | Base Timer 0 Interrupt                 |

| 001BH   | Base Timer 1         | IE.3   | EBT1     | Base Timer 1 Interrupt                 |

| 0023H   | Resume Interrupt     | IE.4   | ERSU     | Port Resume Interrupt (IDLE mode)      |

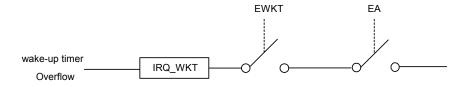

| 002BH   | Wake-up Interrupt    | IE.5   | EWKT     | Wake up timer Interrupt (IDLE mode)    |

| 0033H   | OVL Interrupt        | IE.6   | EOVL     | Invalid ROM address detector Interrupt |

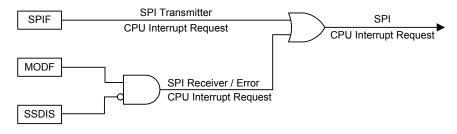

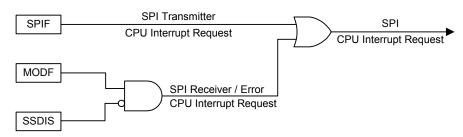

| 003BH   | SPI Interrupt        | IE2.0  | ESPI     | Serial peripheral interface Interrupt  |

#### 3. Micro-Processor

#### 3.1. General Description

SH68F093 is an 8-bit microprocessor optimized for control applications. Byte-processing and numerical operations on small data structures are facilitated by a variety of fast addressing modes for Internal RAM. The instruction set provides several byte instructions including multiply and divide instructions. In addition, several bit oriented instructions are also provided. This allows direct bit manipulation and testing in control and logic systems that require Boolean processing.

#### 3.2. Special Function Registers (SFRs)

SH68F093 has a total of 46 SFR's, as shown in the figure below --- SFR Map for SH68F093. Note that not all the addresses are occupied by SFR's. The unoccupied addresses are not implemented and should not be used by the customer. Read access from these unoccupied locations will return unpredictable data, while write accesses will have no effect on the chip.

|     |                     |     |        | SFR Map fo | r SH68F093 |         |         |         |     |

|-----|---------------------|-----|--------|------------|------------|---------|---------|---------|-----|

| F8H | SPSTA               | -   | -      | IB_OFFSET  | IB_DATA    | -       | -       | -       | FFH |

| F0H | В                   | -   | IBCON1 | IBCON2     | IBCON3     | IBCON4  | IBCON5  | XPAGE   | F7H |

| E8H | -                   | -   | -      | -          | -          | -       | -       | -       | EFH |

| E0H | ACC                 | -   | -      | -          | -          | -       | -       | -       | E7H |

| D8H | -                   | EIT | IF     |            | -          | -       | -       | -       | DFH |

| D0H | PSW                 | -   | BT0    | BT1        | BTCON      | BTCLK   | -       | -       | D7H |

| C8H | -                   | -   | -      | -          | -          | -       | -       | -       | CFH |

| C0H | -                   | -   | -      | -          | VC_CON     | -       | -       | VSEL_DC | C7H |

| B8H | IP                  | IP2 | -      | -          | -          | -       | -       | -       | BFH |

| B0H | -                   | -   | -      |            | -          | -       | -       | -       | B7H |

| A8H | IE                  | IE2 | -      | -          | -          | -       | -       | PRCON   | AFH |

| A0H | P2                  | -   | P0WK   | P1WK       | P2WK       | -       | -       | -       | A7H |

| 98H | -                   | -   | P0CON  | P1CON      | P2CON      | SPCON   | SPDAT   |         | 9FH |

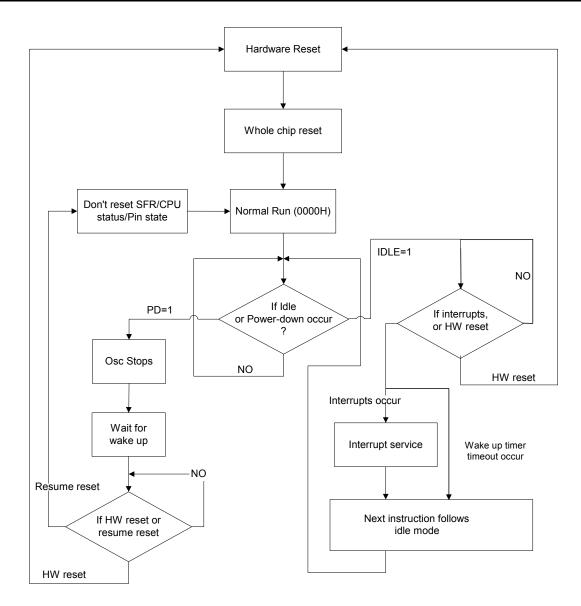

| 90H | P1                  | -   | -      | CLRWDT     | PREWDT     | WKT_CON | MODE_FG | RES_CON | 97H |