# Intel<sup>®</sup> Server Board SE7210TP1-E

# **Technical Product Specification**

Intel order number C49240-002

**Revision 2.0**

October 2004

**Enterprise Platforms and Services Marketing**

| Date          | Revision<br>Number | Modifications                                                       |

|---------------|--------------------|---------------------------------------------------------------------|

| February 2004 | 1.0                | Initial Release.                                                    |

| October 2004  | 2.0                | Updated BIOS information to be consistent with latest BIOS release. |

# **Revision History**

This product specification applies to the Intel® Server Board SE7210TP1-E with BIOS identifier SE7210TP P04.10.

Changes to this specification will be published in the Intel Server Board SE7210TP1-E Specification Update before being incorporated into a revision of this document.

# Disclaimers

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice.

The Intel<sup>®</sup> Server Board **Intel**® Server Board SE7210TP1-E may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel, Pentium, Itanium, and Xeon are trademarks or registered trademarks of Intel Corporation.

\*Other brands and names may be claimed as the property of others.

Copyright © Intel Corporation 2003 - 2004.

This page intentionally left blank

# **Table of Contents**

| 1. Introdu                      | ction                                                                         | 1  |

|---------------------------------|-------------------------------------------------------------------------------|----|

| 1.1                             | Chapter Outline                                                               | 1  |

| 1.2                             | Server Board Use Disclaimer                                                   | 2  |

| 2. Server                       | Board Overview                                                                | 3  |

| 2.1                             | SE7210TP1-E SKU Availability                                                  | 3  |

| 2.2                             | SE7210TP1-E Feature Set                                                       | 3  |

| 3. Functio                      | nal Architecture                                                              | 7  |

| 3.1                             | Processor Subsystem                                                           | 7  |

| 3.1.1                           | Reset Configuration Logic                                                     | 8  |

| 3.1.2                           | Processor Support                                                             | 8  |

| 3.1.3                           | Microcode                                                                     | 9  |

| 3.1.4                           | Processor Cache                                                               | 9  |

| 3.1.5                           | Hyper-Threading Technology                                                    | 9  |

| 3.2                             | Intel E7210 Chipset                                                           | 9  |

| 3.2.1                           | Intel 827210 Memory Controller Hub (MCH)                                      | 9  |

| 3.2.2                           | Intel 82802AC 8 Megabit Firmware Hub (FWH)                                    | 10 |

| 3.2.3                           | PCI-X                                                                         | 10 |

| 3.2.4                           | Low Profile Riser Slot                                                        | 10 |

| 3.2.5                           | SMBus Interface                                                               | 11 |

| 3.2.6                           | 6300ESB I/O Controller Hub                                                    | 11 |

| 3.2.7                           | PCI Interface                                                                 | 11 |

| 3.2.8                           | IDE Interface                                                                 | 12 |

| 3.2.9                           | Serial ATA (SATA) Controller                                                  | 12 |

| 3.2.10                          | Low Pin Count (LPC) Interface                                                 | 13 |

| 3.2.11                          | Compatibility Modules (DMA Controller, Timer/Counters, Interrupt Controller). | 13 |

| 3.2.12                          | Advanced Programmable Interrupt Controller (APIC)                             | 13 |

| 3.2.13                          | Universal Serial Bus (USB) Controller                                         | 13 |

| <b>3.2.14</b><br>ataSheet4U.com | Real Time Clock, CMOS SRAM, and Battery                                       | 14 |

| 3.2.15                          | GPIO                                                                          | 15 |

| 3.2.16                          | Enhanced Power Management                                                     | 15 |

| 3.2.17                          | System Management Bus (SMBus 2.0)                                             | 15 |

| 3.3                             | Memory Subsystem                                                              | 15 |

| 3.3.1                      | Memory Configurations                        | 17 |

|----------------------------|----------------------------------------------|----|

| 3.4                        | I/O Sub-System                               | 22 |

| 3.4.1                      | PCI Sub-System                               | 22 |

| 3.4.2                      | DMA Channels                                 | 24 |

| 3.4.3                      | Interrupts                                   | 24 |

| 3.4.4                      | PCI Interrupt Routing Map                    | 25 |

| 3.4.5                      | SCSI Support                                 | 26 |

| 3.4.6                      | IDE Support                                  | 30 |

| 3.4.7                      | SATA Support                                 | 30 |

| 3.4.8                      | Video Controller                             | 31 |

| 3.4.9                      | Network Interface Controller (NIC) Subsystem | 32 |

| 3.4.10                     | USB 2.0 Support                              | 35 |

| 3.4.11                     | I/O Controller                               | 35 |

| 3.5                        | Configuration and Initialization             | 36 |

| 3.5.1                      | Memory Space                                 | 36 |

| 3.5.2                      | I/O Мар                                      | 37 |

| 3.6                        | Clock Generation and Distribution            | 39 |

| 4. System                  | BIOS                                         | 40 |

| 4.1                        | BIOS Identification String                   | 43 |

| 4.2                        | Flash ROM                                    | 44 |

| 4.2.1                      | Removable Media Support                      | 44 |

| 4.2.2                      | Legacy USB                                   | 44 |

| 4.3                        | Resource Configuration                       | 45 |

| 4.3.1                      | PCI Autoconfiguration                        | 45 |

| 4.3.2                      | PCI IDE Support                              | 45 |

| 4.4                        | System Management BIOS (SMBIOS)              | 45 |

| 4.5                        | BIOS Updates                                 | 46 |

| 4.6                        | Recovering BIOS Data                         | 46 |

| 4.7                        | BIOS POST                                    | 47 |

| 4.7.1                      | User Interface                               | 47 |

| <b>4.8</b><br>aSheet4U.com | BIOS Setup Utility                           | 48 |

| 4.8.1                      | Localization                                 | 48 |

| 4.8.2                      | Keyboard Commands                            | 48 |

| 4.8.3                      | Entering BIOS Setup                          | 49 |

| 4.8.4                      | Menu Selection                               | 49 |

| 4.8.5                 | BOOT menu                                                                         | 60      |

|-----------------------|-----------------------------------------------------------------------------------|---------|

| 4.8.6                 | Security Menu                                                                     | 63      |

| 4.8.7                 | Server Menu                                                                       | 64      |

| 4.8.8                 | Exit Menu                                                                         | 68      |

| 4.9                   | Operating System Boot, Sleep and Wake                                             | 69      |

| 4.9.1                 | Microsoft* Windows* Compatibility                                                 | 69      |

| 4.9.2                 | Advanced Configuration and Power Interface (ACPI)                                 | 69      |

| 4.9.3                 | Sleep and Wake Functionality                                                      | 69      |

| 4.10                  | Security                                                                          | 72      |

| 4.10.1                | Administrator/User Passwords and F2 Setup Usage Model                             | 72      |

| 4.10.2                | Password Clear Jumper                                                             | 74      |

| 5. Platfor            | rm Management Architecture                                                        | 75      |

| 5.1                   | Essential Management Features and Functionality                                   | 75      |

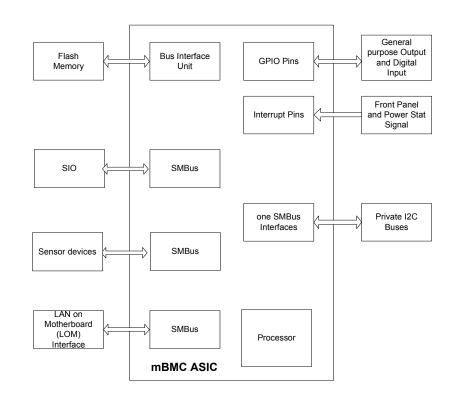

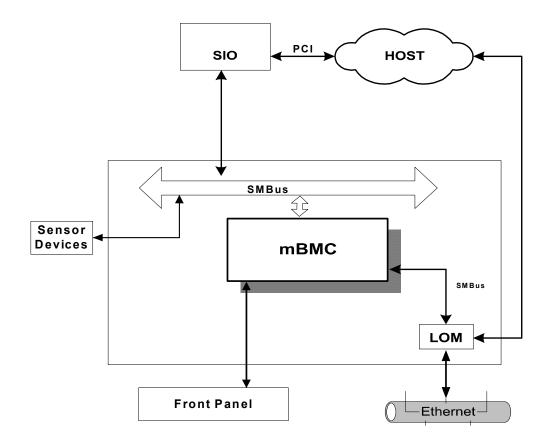

| 5.1.1                 | Overview of National* Semiconductor PC87431 Integrated Management Contr           | oller75 |

| 5.1.2                 | National Semiconductor PC87431 integrated management controller Self-test.        | 76      |

| 5.1.3                 | SMBus Interfaces                                                                  | 76      |

| 5.1.4<br>control      | External Interface to National Semiconductor PC87431 integrated managemer<br>ller |         |

| 5.1.5                 | Messaging Interfaces                                                              | 77      |

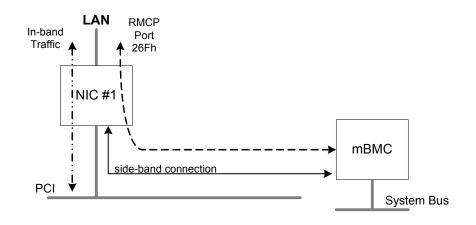

| 5.1.6                 | Direct Platform Control (IPMI over LAN)                                           | 80      |

| 5.1.7                 | Wake On LAN / Power On LAN and Magic Packet Support                               | 82      |

| 5.1.8                 | Watchdog Timer                                                                    | 83      |

| 5.1.9                 | System Event Log (SEL)                                                            | 83      |

| 5.1.10                | Sensor Data Record (SDR) Repository                                               | 84      |

| 5.1.11                | Event Message Reception                                                           | 84      |

| 5.1.12                | Event Filtering and Alerting                                                      | 84      |

| 5.1.13                | NMI Generation                                                                    | 88      |

| 5.1.14                | SMI Generation                                                                    | 89      |

| 5.2                   | Platform Management Interconnects                                                 | 89      |

| 5.2.1                 | Power Supply Interface Signals                                                    | 89      |

| 5.2.2                 | System Reset Control                                                              | 91      |

| aSheet4U.com<br>5.2.3 | Temperature-based Fan Speed Control                                               | 92      |

| 5.2.4                 | Front Panel Control                                                               | 93      |

| 5.2.5                 | Secure Mode Operation                                                             | 96      |

| 5.2.6                 | FRU Information                                                                   | 97      |

| 5.2.7      | LCD Support                                          | 97  |

|------------|------------------------------------------------------|-----|

| 5.3        | Sensors                                              |     |

| 5.3.1      | Sensor Type Codes                                    |     |

| 6. Error R | eporting and Handling                                |     |

| 6.1        | Error Sources and Types                              |     |

| 6.1.1      | PCI Bus Errors                                       |     |

| 6.1.2      | Processor Bus Errors                                 |     |

| 6.1.3      | Memory Bus Errors                                    |     |

| 6.2        | BIOS Error Messages, POST Codes, and BIOS Beep Codes |     |

| 6.2.1      | BIOS Error Messages                                  |     |

| 6.2.2      | Port 80h POST Codes                                  |     |

| 6.3        | Bus Initialization Checkpoints                       | 110 |

| 7. Connec  | ctor Pin-Outs and Jumper Blocks                      | 112 |

| 7.1        | Power Connectors                                     | 112 |

| 7.2        | PCI Bus Connectors                                   | 113 |

| 7.3        | Front Panel Connector                                | 114 |

| 7.4        | VGA Connector                                        | 115 |

| 7.5        | NIC /USB Connector                                   | 115 |

| 7.6        | SATA/SATA RAID Connectors                            | 116 |

| 7.7        | 6300ESB I/O IDE Connectors                           | 117 |

| 7.8        | Front Panel USB Header                               | 117 |

| 7.9        | Floppy Connector                                     | 118 |

| 7.10       | Serial Port Connector                                | 118 |

| 7.11       | Keyboard and Mouse Connector                         | 119 |

| 7.12       | Miscellaneous Headers                                |     |

| 7.12.1     | Fan Headers                                          |     |

| 7.13       | System Recovery and Update Jumper                    |     |

| 7.14       | Clear CMOS Jumper                                    |     |

| 7.15       | PASSWORD Jumper                                      |     |

| 7.16       | Write protected Jumper                               |     |

| 8. Enviror | nmental Specifications                               |     |

| 8.1        | Absolute Maximum Ratings                             |     |

| 8.2        | SE7210TP1-E Power Budget                             |     |

| 8.3        | Product Regulatory Compliance                        |     |

| 8.3.1      | Product Safety Compliance                            |     |

| 8.3.2      | Product EMC Compliance                       |     |

|------------|----------------------------------------------|-----|

| 8.3.3      | Product Regulatory Compliance Markings       | 125 |

| 8.4        | Electromagnetic Compatibility Notices        |     |

| 8.4.1      | FCC (USA)                                    | 125 |

| 8.4.2      | INDUSTRY CANADA (ICES-003)                   | 126 |

| 8.4.3      | Europe (CE Declaration of Conformity)        |     |

| 8.4.4      | Taiwan Declaration of Conformity             |     |

| 8.4.5      | Korean RRL Compliance                        | 127 |

| 8.4.6      | Australia / New Zealand                      |     |

| 8.5        | Replacing the Back-Up Battery                |     |

| 8.6        | Calculated Mean Time Between Failures (MTBF) |     |

| 8.7        | Mechanical Specifications                    |     |

| Appendix A | a: Glossary of Terms                         | 130 |

# **List of Figures**

| Figure 1. Intel Server Board SE7210TP1-E Diagram                                                            | 5   |

|-------------------------------------------------------------------------------------------------------------|-----|

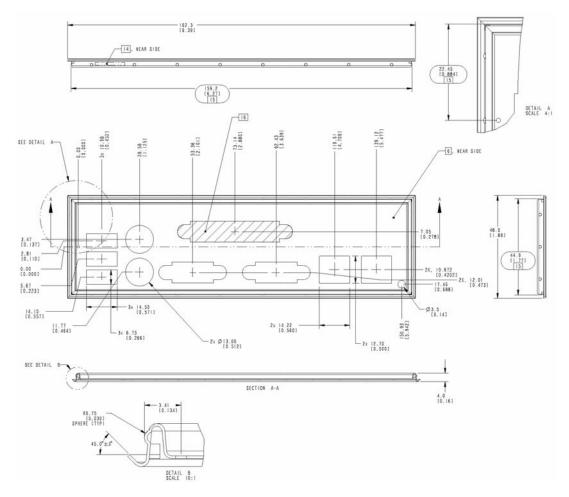

| Figure 2. Intel Server Board SE7210TP1-E Mechanical Drawing                                                 | 6   |

| Figure 3. Intel E7210 Chipset Block Diagram                                                                 | 10  |

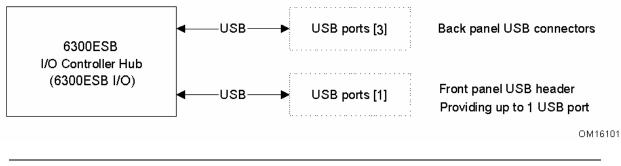

| Figure 4. USB Port Configuration                                                                            | 14  |

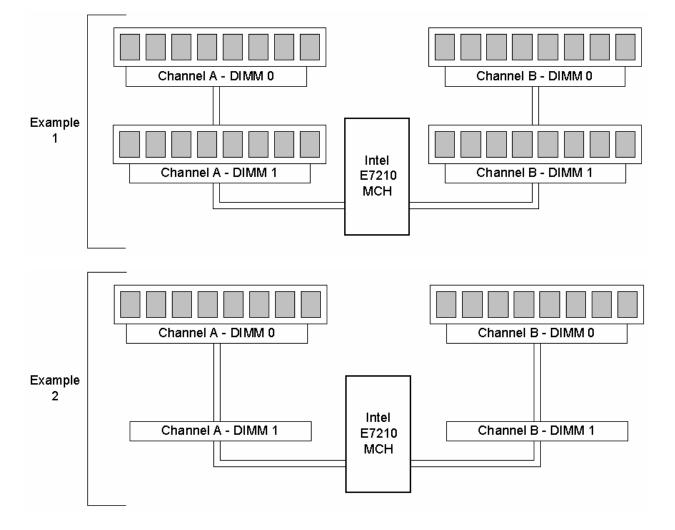

| Figure 5. Examples of Dual Channel Configuration with Dynamic Mode                                          | 18  |

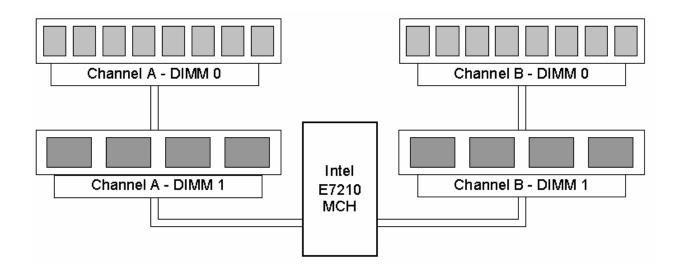

| Figure 6. Example of Dual Channel Configuration without Dynamic Mode                                        | 19  |

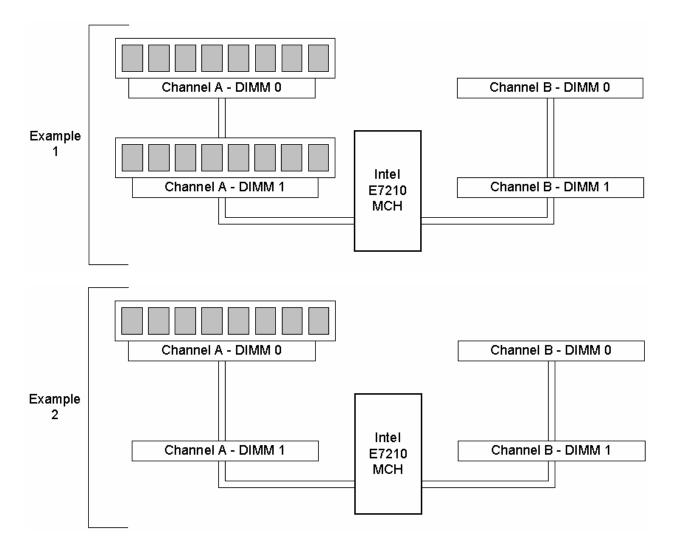

| Figure 7. Examples of Single Channel Configuration with Dynamic Mode                                        | 20  |

| Figure 8. Examples of Single Channel Configuration without Dynamic Mode                                     | 21  |

| Figure 9. LAN Connector LED Locations                                                                       | 34  |

| Figure 10: National Semiconductor PC87431 integrated management controller in a Server<br>Management System | 75  |

| Figure 11: External Interfaces to National Semiconductor PC87431 integrated management controller           | 77  |

| Figure 12 - IPMI-over-LAN                                                                                   | 81  |

| Figure 13: Power Supply Control Signals                                                                     | 89  |

| Figure 14. Intel Server Board SE7210TP1-E I/O Shield Drawing                                                | 129 |

# **List of Tables**

|   | Table 1. Processor Support Matrix                                                       | 8  |

|---|-----------------------------------------------------------------------------------------|----|

|   | Table 2. Supported Memory Configurations                                                | 16 |

|   | Table 3. Supported System Bus Frequency and Memory Speed Combinations                   | 16 |

|   | Table 4. Characteristics of Dual/Single Channel Configuration with/without Dynamic Mode | 17 |

|   | Table 5: PCI Bus Segment Characteristics                                                | 22 |

|   | Table 6. DMA Channels                                                                   | 24 |

|   | Table 7. Interrupts                                                                     | 24 |

|   | Table 8. PCI Interrupt Routing Map                                                      | 25 |

|   | Table 9: Video Modes                                                                    | 32 |

|   | Table 10. 10/100 Ethernet LAN Connector LEDs                                            | 34 |

|   | Table 11. 10/100/1000 LAN Connector LED States                                          | 34 |

|   | Table 12. System Memory Map                                                             | 36 |

|   | Table 13. PCI Configuration Space Map                                                   | 37 |

|   | Table 14. I/O Map                                                                       | 37 |

|   | Table 15. PCI Bus Configuration IDs                                                     | 39 |

|   | Table 16: Supported BIOS Features                                                       | 40 |

|   | Table 17: BIOS Setup Keyboard Command Bar Options                                       | 48 |

|   | Table 18: BIOS Setup Main Menu Options                                                  | 50 |

|   | Table 19. Advanced Menu                                                                 | 50 |

|   | Table 20. CPU Configuration Submenu                                                     | 51 |

|   | Table 21. IDE Configuration Submenu                                                     | 52 |

|   | Table 22. Primary/Secondary/Third/Fourth Master/Slave Submenu                           | 53 |

|   | Table 23. Primary/Secondary/Third/Fourth Master/Slave Submenu                           | 54 |

|   | Table 24. Primary/Secondary/Third/Fourth Master/Slave Submenu                           | 54 |

|   | Table 25. Primary/Secondary/Third/Fourth Master/Slave Submenu                           | 55 |

|   | Table 26. Primary/Secondary/Third/Fourth Master/Slave Submenu                           | 55 |

|   | Table 27. Floppy Configuration Submenu                                                  | 56 |

| + | Table 28. Super I/O Configuration Submenu                                               | 57 |

|   | Table 29. USB Configuration Submenu                                                     | 58 |

|   | Table 30. USB Mass Storage Device Configuration Sub-menu Selections                     | 58 |

|   | Table 31. PCI Configuration Submenu                                                     | 59 |

|   | Table 32. Boot Features                                                                 | 60 |

| Table 33. Boot Settings Configuration Submenu                                                        | 60               |

|------------------------------------------------------------------------------------------------------|------------------|

| Table 34. Boot Device Priority Submenu                                                               | 61               |

| Table 35. Boot Disk Drives Submenu                                                                   | 62               |

| Table 36. Removable Drives Submenu                                                                   | 62               |

| Table 37. CD/DVD Drives Submenu                                                                      | 63               |

| Table 38. Security Menu                                                                              | 63               |

| Table 39. Server Menu                                                                                | 64               |

| Table 40. System Managment Submenu                                                                   | 66               |

| Table 41. Serial Console Features Submenu                                                            | 67               |

| Table 42. Event Log Configuration Submenu                                                            | 68               |

| Table 43. Exit Menu                                                                                  | 68               |

| Table 44: Supported Wake Events                                                                      | 70               |

| Table 45. Effects of Pressing the Power Switch                                                       | 71               |

| Table 46. Power States and Targeted System Power                                                     | 71               |

| Table 47: Supported Channel Assigments                                                               | 78               |

| Table 48: LAN Channel Capacity                                                                       | 80               |

| Table 49: LAN Channel Specifications                                                                 | 81               |

| Table 50: PEF Action Priorities                                                                      |                  |

| Table 51. National Semiconductor PC87431 integrated management controller Fa           Event Filters | •                |

| Table 52: Power Control Initiators                                                                   | 91               |

| Table 53: System Reset Sources and Actions                                                           | 92               |

| Table 54: Chassis ID LEDs                                                                            | 94               |

| Table 55: Fault/Status LED                                                                           | 95               |

| Table 56: National Semiconductor PC87431 integrated management controller Bu                         | ilt-in Sensors99 |

| Table 57: SE7520JR2 Platform Sensors for Essentials Management                                       |                  |

| Table 58: POST Error Messages and Handling                                                           |                  |

| Table 59: POST Code Checkpoints                                                                      | 105              |

| Table60: Bootblock Initialization Code Checkpoints                                                   | 107              |

| Table61: Bootblock Recovery Code Checkpoints                                                         |                  |

| Table62 : POST Error Beep Codes                                                                      | 110              |

| Table63 BIOS Recovery Beep Codes                                                                     | 110              |

| Table 64. Bus Initialization Checkpoints                                                             | 110              |

| Table 65. Upper Nibble High Byte Functions                                                           | 110              |

| Table 66. Lower Nibble High Byte Functions                                                           | 111              |

| Table 67. Power Connector Pin-out (J4J1)                        | 112 |

|-----------------------------------------------------------------|-----|

| Table 68. 12V CPU Power Connector (J9B1)                        | 112 |

| Table 69. Auxiliary Signal Connector (J5G2)                     | 113 |

| Table 70. PCI Bus Connectors                                    | 113 |

| Table 71. High-Density Front Panel 34-Pin Header Pin Out (J3J4) | 114 |

| Table 72. VGA Connector Pin-out (J7A1)                          | 115 |

| Table 73. Magjack Connector (RJ45, 10/100/1000) Pin Out (J6A2)  | 115 |

| Table 74. Magjack Connector (RJ45, 10/100) Pin Out (J5A1)       | 116 |

| Table 75. Triple USB Pin Out (J9A2)                             | 116 |

| Table 76. SATA 7-pin Connectors Pin Out (J3G1, J3G2)            | 116 |

| Table 77. 6300ESB I/O IDE 40-pin Connector Pin Out (J4J2, J4J3) | 117 |

| Table 78. Front Panel USB Connector Pin-out (J5G1)              | 117 |

| Table 79. 34-pin Floppy Connector Pin Out (J3H1)                | 118 |

| Table 80. 9-pin Serial A Port Pin Out (J8A1)                    | 118 |

| Table 81. 10-pin Header Serial B Port Pin Out (J8A2)            | 119 |

| Table 82. Keyboard /Mouse PS/2 Connector Pin Out (J9A1)         | 119 |

| Table 83. Three-Pin Fan Headers Pin-Out                         | 120 |

| Table 84. BIOS Setup Configuration Jumper Settings (J1D1)       | 120 |

| Table 85. Clear CMOS Jumper Settings (J1D1)                     | 121 |

| Table 86. PASSWORD Jumper Settings (J1D1)                       | 121 |

| Table 87. BIOS WRITE PROTECTED Jumper Settings (J1D1)           | 122 |

| Table 88. Absolute Maximum Ratings                              | 123 |

| Table 89. SE7210TP1-E Power Budget                              | 123 |

This page left intentionally blank.

# 1. Introduction

This Technical Product Specification (TPS) provides detail to the architecture and feature set of the Intel® Server Board SE7210TP1-E.

The target audience for this document is anyone wishing to obtain more in depth detail of the server board than what is generally made available in the board's Users Guide. It is a technical document meant to assist people with understanding and learning more about the specific features of the board.

This is one of several technical documents available for this server board. All of the functional sub-systems that make up the board are described in this document. However, certain low level detail of specific sub-systems is not included. Design level information for specific sub-systems can be obtained by ordering the External Product Specification (EPS) for a given sub-system. The EPS documents available for this server board include the following:

- Intel® Server Board SE7210TP1-E BIOS External Product Specification

- Intel Server Management Essential Firmware EPS

These documents are not made publicly available and must be ordered by your local Intel representative.

## 1.1 Chapter Outline

This document is divided into the following chapters

- Chapter 1 Introduction

- Chapter 2 Product Overview

- Chapter 3 Board Architecture

- Chapter 4 System BIOS

- Chapter 5 Platform Management Architecture

- Chapter 6 Error Reporting and Handling

- Chapter 7 Connector Pin-out and Jumper Blocks

- Chapter 8 Environmental Specifications

- Chapter 9 Miscellaneous Board Information

- Appendix A Glossary of Terms

## 1.2 Server Board Use Disclaimer

Intel Corporation server boards contain a number of high-density VLSI and power delivery components which need adequate airflow to cool. Intel ensures through its own chassis development and testing that when Intel server building blocks are used together, the fully integrated system will meet the intended thermal requirements of these components. It is the responsibility of the system integrator who chooses not to use Intel developed server building blocks to consult vendor datasheets and operating parameters to determine the amount of air flow required for their specific application and environmental conditions. Intel Corporation can not be held responsible, if components fail or the server board does not operate correctly when used outside any of their published operating or non-operating limits.

# 2. Server Board Overview

The Intel® Server Board SE7210TP1-E is a monolithic printed circuit board with features that were designed to support the entry server markets.

## 2.1 SE7210TP1-E SKU Availability

In this document, "SE7210TP1-E" will be used to describe the family of boards that will be made available under a common marketing name. The core features for each board will be common; however each board will have the following distinctions:

| SE7210TP1:     | Onboard SATA (RAID)                                  |

|----------------|------------------------------------------------------|

| SE7210TP1SCSI: | Onboard SCSI + Onboard SATA (RAID)                   |

| SR1325TP1:     | Onboard SATA (RAID) + Low Profile PCI Slot and Riser |

Throughout this document, all references to SE7210TP1-E will refer to all three board SKUs unless specifically noted otherwise. The board you select to use may or may not have all the features described based on the listed board differences.

## 2.2 SE7210TP1-E Feature Set

The Intel Server Board SE7210TP1-E provides the following feature set:

- $\circ$  Support for an Intel<sup>®</sup> Celeron processor or an Intel<sup>®</sup> Pentium<sup>®</sup> 4 processor with hyperthreading technology in a  $\mu$ PGA478 socket.

- 400/533/800 MHz Front Side Bus (FSB)

- Intel<sup>®</sup> E7210 chipset

- Intel<sup>®</sup> 827210 Memory Controller Hub (MCH)

- Intel® 6300ESB I/O Controller Hub

- Intel<sup>®</sup> 82802AC 8 Megabit Firmware Hub (FWH)

- Support for single-sided or double-sided dual inline memory module (DIMM) double-data rate (DDR) memory providing up to 4 GB of system memory with four 184-pin DIMM sockets.

- PC3200 (400 MHz): to run 400 MHz memory at full speed requires an Intel Pentium 4 processor with 800 MHz system bus frequency.

- PC2700 (333 MHz): to run 333 MHz memory at full speed requires an Intel Pentium 4 processor with 533 MHz system bus frequency.

**Note:** PC2700 (333 MHZ) memory will run at 320 MHz frequency when using an Intel Pentium 4 processor with 800 MHz system bus frequency.

• PC2100 (266 MHZ): PC2100 (266 MHZ) memory may only be used with an Intel Pentium 4 processor with 400 MHz or 533 MHz system bus frequency only.

Intel 82547GI Platform LAN Connect (PLC) device for 10/100/1000 Mbits/sec Ethernet LAN www.DataSheet401,000 Mbits/sec Ethernet LAN connectivity

Intel 82551QM device for 10/100 Mbits/sec Ethernet LAN connectivity

- Two independent PCI buses (one 32-bit, 33 MHz, 5 V; one 64-bit, 66 MHz, 3.3V) with four PCI connectors and two embedded devices:

- Three PCI-X 64-bit PCI slots

- One 32-bit PCI slot

- Integrated 2D/3D graphics controller: ATI Rage\* XL Video Controller with 8 MB of SDRAM

- Optional single channel, Ultra 320 SCSI controller (on SE7210TP1SCSI): Adaptec\* 7901

- LPC (Low Pin Count) bus segment with one embedded device: Winbond\* W83627HF-AW LPC Bus I/O controller chip providing all PC-compatible I/O (floppy, serial, keyboard and mouse)

- Three external USB 2.0 ports on the back panel with an additional internal header, which provides support for one additional USB port for front panel support (four total possible USB 2.0 ports)

- One serial port and one serial port header

- Two Serial ATA (SATA) ports provide interface for SATA hard drives and ATAPI devices

- Two IDE interfaces with Ultra 33, 66 and 100 DMA mode

- Support for up to six system fans and one processor fan

- Server System Infrastructure (SSI)-compliant connectors for SSI interface support: front panel, power connector

- Intel Server Management 5.8 support via the National\* Semiconductor PC87431 integrated management controller

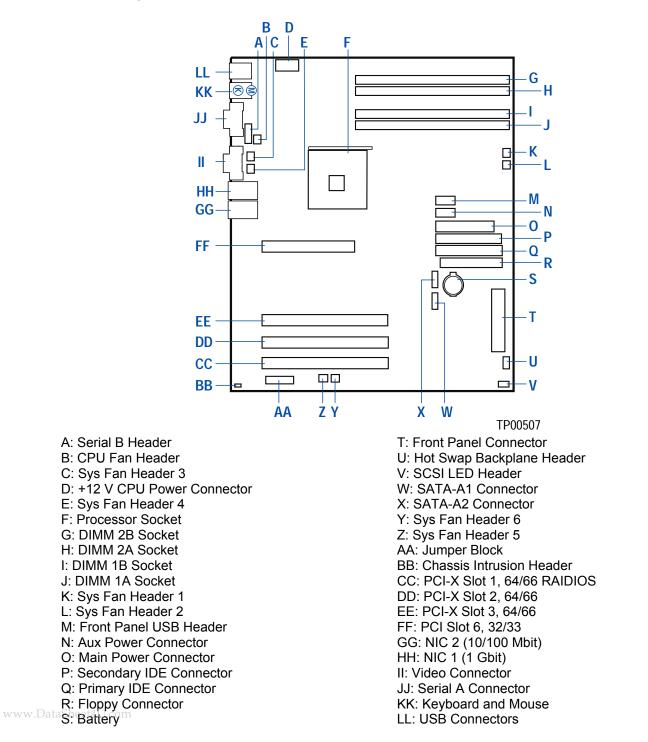

Figure 1. Intel Server Board SE7210TP1-E Diagram shows the board layout of the server board SE7210TP1-E. Each connector and major component is identified by number and identified below the figure.

#### Figure 1. Intel Server Board SE7210TP1-E Diagram

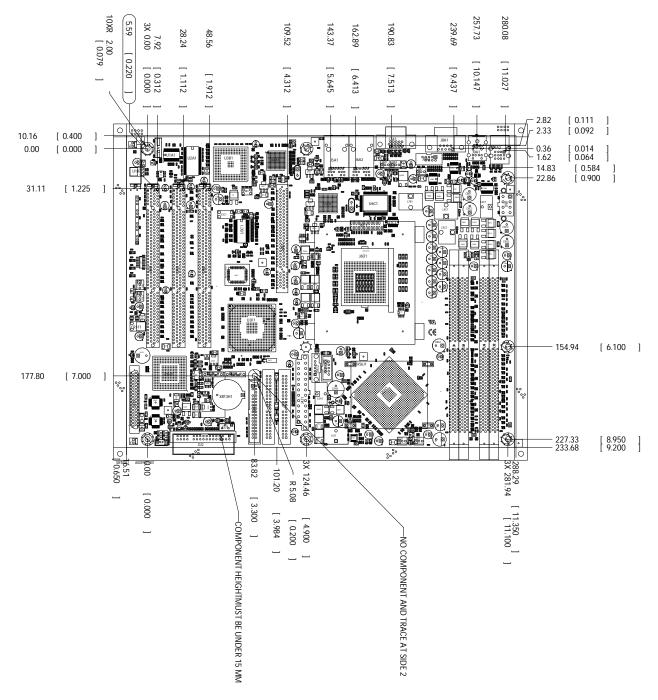

The following mechanical drawing shows the physical dimensions of the baseboard.

Figure 2. Intel Server Board SE7210TP1-E Mechanical Drawing

# 3. Functional Architecture

This chapter provides a high-level description of the functionality distributed between the architectural blocks of the Intel Server Board SE7210TP1-E.

# 3.1 Processor Subsystem

The support circuitry for the processor sub-system consists of the following:

```

Single µPGA478 processor socket

Processor host bus AGTL+ support circuitry.

www.DataSheefUser configuration logic.

```

#### 3.1.1 Reset Configuration Logic

The BIOS determines the processor stepping, cache size, and other processor information through the CPUID instruction. The requirement is for the processor to run at a fixed speed. The processor cannot be programmed to operate at a lower or higher speed.

On the SE7210TP1-E platform, the BIOS is responsible for configuring the processor speed. The BIOS uses CMOS settings to determine which speed to program into the speed setting device. The processor information is read at every system power-on.

#### 3.1.2 Processor Support

The Intel Server Board SE7210TP1-E supports a single Intel<sup>®</sup> Pentium<sup>®</sup> 4 processor, or a single Intel<sup>®</sup> Celeron<sup>®</sup> processor with a system bus of 400 /533 /800 MHz. The server board supports the processors listed in Table 1.

| Туре                                                          | Designation                                           | System Bus    | L2 Cache Size |

|---------------------------------------------------------------|-------------------------------------------------------|---------------|---------------|

| Pentium® 4 processor supporting Hyper-Threading<br>Technology | 3.4, 3.2 GHz                                          | 800 MHz       | 2 MB          |

| Pentium® 4 processor supporting Hyper-Threading Technology    | 3.4, 3.2, 3.0, 2.8<br>GHz                             | 800 MHz       | 1 MB          |

| Pentium® 4 processor supporting Hyper-Threading Technology    | 2.8 GHz                                               | 533 MHz       | 1 MB          |

| Pentium® 4 processor supporting Hyper-Threading Technology    | 3.2, 3.0, 2.80, 2.40,<br>2.60 GHz                     | 800 MHz       | 512 KB        |

| Pentium® 4 processor supporting Hyper-Threading Technology    | 3.06 GHz                                              | 533 MHz       | 512 KB        |

| Pentium® 4 processor                                          | 2.8, 2.66, 2.6, 2.53,<br>2.4, 2.26, 2.0 GHz           | 400 / 533 MHz | 512 KB        |

| Celeron® processor                                            | 2.8, 2.7, 2.6, 2.5,<br>2.4, 2.3, 2.2, 2.1,<br>2.0 GHz | 400 MHz       | 128 KB        |

#### Table 1. Processor Support Matrix

####

Use only the processors listed above. Use of unsupported processors can damage the board, the processor, and the power supply. See the Intel<sup>®</sup> Server Board SE7210TP1-E Specification Update or go to <u>http://support.intel.com/support/motherboards/server/SE7210TP1-E/</u> for the current list of supported processors for this board.

### ⇒ NOTE

Use only ATX12V or EPS12V compliant power supplies with the server board SE7210TP1-E. ATX12V and EPS12V power supplies have an additional power lead that provides required www.Datasupplemental power for the Intel Pentium 4 processor. The board will not boot if you do not connect the 20-pin (or 24-pin) and 4-pin (or 8-pin) leads of ATX12V or EPS12V power supplies to the corresponding connectors.

Do not use a standard ATX power supply. The board will not boot with a standard ATX power supply.

#### 3.1.3 Microcode

IA32 processors have the capability of correcting specific errata through the loading of an Intelsupplied data block (microcode update). The BIOS is responsible for storing the update in nonvolatile memory and loading it into each processor during POST. The BIOS performs all the recommended update signature verification prior to storing the update in the Flash.

#### 3.1.4 Processor Cache

The BIOS enables all levels of processor cache as early as possible during POST. There are no user options to modify the cache configuration, size or policies. All detected cache sizes are reported in the SMBIOS Type 7 structures. The largest and highest level cache detected is reported in BIOS Setup

#### 3.1.5 Hyper-Threading Technology

Intel<sup>®</sup> Pentium<sup>®</sup> 4 processors support Hyper-Threading Technology. The BIOS will detect processors that support this feature and will enable the feature during POST. BIOS Setup provides an option to selectively enable or disable this feature. The default behavior is enabled.

The BIOS will create additional entries in the ACPI MP tables to describe the virtual processors. The SMBIOS Type 4 structure will show only the physical processors installed.

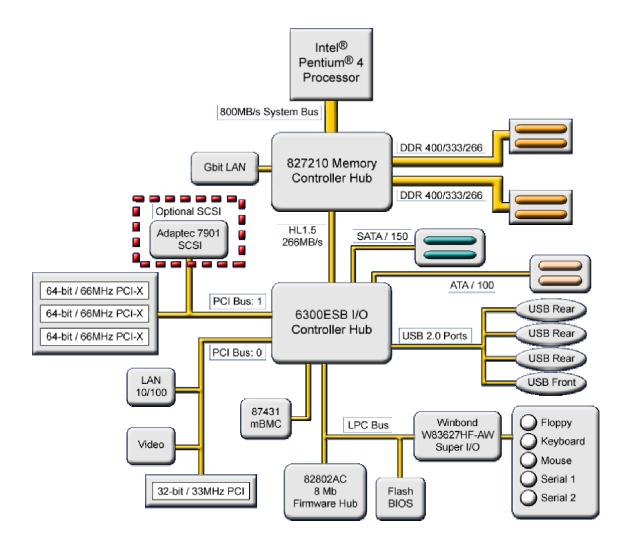

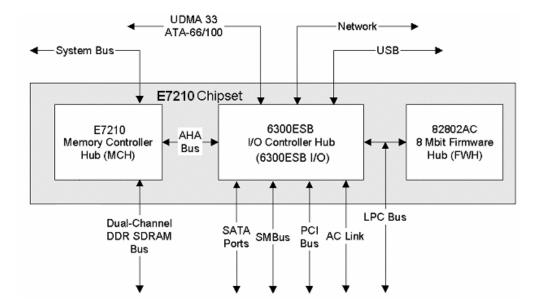

## 3.2 Intel E7210 Chipset

The Intel E7210 chipset consists of the following devices:

- Intel 827210 Memory Controller Hub (MCH) with Accelerated Hub Architecture (AHA) bus

- Intel 6300ESB I/O Controller Hub with AHA bus

- Intel 82802AC (8 Mbit) Firmware Hub (FWH)

#### 3.2.1 Intel 827210 Memory Controller Hub (MCH)

The MCH is a centralized controller for the system bus, the memory bus and the Accelerated Hub Architecture interface. The 6300ESB I/O is a centralized controller for the Server Board SE7210TP1-E's I/O paths. The FWH provides the nonvolatile storage of the BIOS. The component combination provides the chipset interfaces as shown in Figure 3.

Figure 3. Intel E7210 Chipset Block Diagram

### 3.2.2 Intel 82802AC 8 Megabit Firmware Hub (FWH)

The FWH provides the following:

- System BIOS program

- Logic that enables protection for storing and updating platform information

### 3.2.3 PCI-X

The PCI-X segment comes from 6300ESB I/O, and only runs at 66MHz maximum.

The PCI-X interfaces of the 6300ESB I/O are compliant with the PCI-X Addendum to the PCI Local Bus Specification Revision 1.0b as well as the Mode 1 and Mode 2 (266 MHz) sections of the PCI-X Electrical and Mechanical Addendum to the PCI Local Bus Specification Revision 2.0a and the PCI-X Protocol Addendum to the PCI Local Bus Specification Revision 2.0a. PCI-X Mode 2 provides enhancements over PCI that enable faster and more efficient data transfers. For conventional PCI Mode, the 6300ESB I/O supports PCI bus frequencies of 66 MHz, 100 MHz, and 133 MHz. For the PCI-X Mode 2, the 6300ESB I/O supports PCI bus frequencies of 66 MHz, 100 MHz, 133 MHz and 266 MHz.

On the SE7210TP1-E server board, the PCI-X interface (P64-A) is independently controlled to operate in either a conventional PCI or PCI-X mode. P64-A is routed to control I/O from the 82547GI Ethernet controller and is capable of supporting MCH CSA interfaces depending on the riser card used. P32-A is routed to control I/O from the 32-bit PCI slot and the Adaptec\* 7901Single Channel SCSI controller.

www.DataSheet4U.com

### 3.2.4 Low Profile Riser Slot

The Low Profile riser slot is a standard 202-pin slot supporting PCI-X signals. Its location on the board will allow only the use of low profile add-in cards.

#### 3.2.5 SMBus Interface

The SMBus interface can be used for system and power management related tasks. The interface is compliant with System Management Bus Specification Revision 2.0. The SMBus interface allows full read/write access to all configuration and memory spaces in the FWH.

#### 3.2.6 6300ESB I/O Controller Hub

The 6300ESB I/O is a multi-function device providing an upstream hub interface for access to several embedded I/O functions and features including:

- PCI Local Bus Specification, Revision 2.2 with support for 33 MHz PCI operations and 66 MHz PCI-X operations.

- ACPI power management logic support

- Enhanced DMA controller, interrupt controller, and timer functions

- Integrated IDE controller with support for Ultra ATA100/66/33

- Integrated SATA controller

- USB host interface with support for four USB ports; two UHCI host controllers; one EHCI high-speed USB 2.0 host controller

- System Management Bus (SMBus) Specification, Version 2.0 with additional support for I2C devices

- Low Pin Count (LPC) interface

- Firmware Hub (FWH) interface support

Each function within the 6300ESB has its own set of configuration registers. Once configured, each appears to the system as a distinct hardware controller sharing the same PCI bus interface.

**Performance Note:** The Hub Link 1.5 interface between the 6300ESB ICH and the 827210 MCH has a theoretical maximum throughput of 266MB/s. Each bus supported by the 6300ESB ICH will share the Hub Link 1.5 bandwidth, this includes the P64-A bus, the P32-A bus, the BMC interface, the LPC bus, the USB 2.0 interface, the Parallel ATA bus and the Serial ATA bus.

### 3.2.7 PCI Interface

The 6300ESB I/O PCI interface provides a 33 MHz, Revision 2.3 compliant implementation. All PCI signals are 5-V tolerant, except PME#. The 6300ESB I/O integrates a PCI arbiter that supports up to four external PCI bus masters in addition to the internal 6300ESB I/O requests. On the SE7210TP1-E server board this PCI interface is used to support on-board PCI devices including the ATI\* video controller.

### 3.2.8 IDE Interface

The 6300ESB I/O IDE controller has two independent bus-mastering IDE interfaces that can be independently enabled. The IDE interfaces support the following modes:

- Programmed I/O (PIO): processor controls data transfer.

- 8237-style DMA: DMA offloads the processor, supporting transfer rates of up to 16 MB/sec.

- Ultra DMA: DMA protocol on IDE bus supports Ultra 100 DMA Mode Transfers up to 100Mbytes/s for reads from disk;88.88 Mbytes/s for writes to disk. As well as Ultra66 and Ultra33 DMA mode..

- ATA-66: DMA protocol on IDE bus supporting host and target throttling and transfer rates of up to 66 MB/sec. The ATA-66 protocol is similar to Ultra DMA and is device driver compatible.

- ATA-100: DMA protocol on IDE bus allows host and target throttling. The 6300ESB I/O ATA-100 logic can achieve read transfer rates up to 100 MB/sec and write transfer rates up to 88 MB/sec.

#### ⇒ NOTE

ATA-66 and ATA-100 are faster timings and require a specialized 40-pin, 80-wire cable to reduce reflections, noise, and inductive coupling.

The IDE interfaces also support ATAPI devices (such as CD-ROM drives) and ATA devices using the transfer modes. The BIOS supports Logical Block Addressing (LBA) and Extended Cylinder Head Sector (ECHS) translation modes. The drive reports the transfer rate and translation mode to the BIOS.

The server board SE7210TP1-E supports Laser Servo (LS-120) diskette technology through the IDE interfaces. The BIOS supports booting from an LS-120 drive.

#### ⇒ NOTE

The BIOS will always recognize an LS-120 drive as an ATAPI floppy drive. To ensure correct operation, do not configure the drive as a hard disk drive.

### 3.2.9 Serial ATA (SATA) Controller

The SATA controller supports two SATA devices providing an interface for SATA hard disks and ATAPI devices. The SATA interface supports PIO IDE transfers up to 16 Mb/s and Serial ATA transfers up to 1.5 Gb/s (150 MB/s). The 6300ESB I/O's SATA system contains two independent SATA signal ports. They can be electrically isolated independently. Each SATA device can have independent timings. They can be configured to the standard primary and www.Datasecondary channels.

#### 3.2.10 Low Pin Count (LPC) Interface

The 6300ESB I/O implements an LPC Interface as described in the Low Pin Count Interface Specification, Revision 1.1. The Low Pin Count (LPC) Bridge function of the 6300ESB I/O resides in PCI Device 31: Function 0. In addition to the LPC bridge interface function, D31:F0 contains other functional units including DMA, interrupt controllers, timers, power management, system management, GPIO, and RTC.

# 3.2.11 Compatibility Modules (DMA Controller, Timer/Counters, Interrupt Controller)

The DMA controller incorporates the logic of two 82C37 DMA controllers, with seven independently programmable channels. Channels 0–3 are hardwired to 8-bit, count-by-byte transfers, and channels 5–7 are hardwired to 16-bit, count-by-word transfers. Any two of the seven DMA channels can be programmed to support fast Type-F transfers.

The 6300ESB I/O supports two types of DMA (LPC and PC/PCI). LPC DMA and PC/PCI DMA use the 6300ESB I/O's DMA controller. The PC/PCI protocol allows PCI-based peripherals to initiate DMA cycles by encoding requests and grants via two PC/PC REQ#/GNT# pairs. LPC DMA is handled through the use of the LDRQ# lines from peripherals and special encoding on LAD[3:0] from the host. Single, Demand, Verify, and Increment modes are supported on the LPC interface. Channels 0–3 are 8 bit channels. Channels 5–7 are 16 bit channels. Channel 4 is reserved as a generic bus master request.

The timer/counter block contains three counters that are equivalent in function to those found in one 82C54 programmable interval timer. These three counters are combined to provide the system timer function, and speaker tone. The 14.31818 MHz oscillator input provides the clock source for these three counters.

The 6300ESB I/O provides an ISA-compatible Programmable Interrupt Controller (PIC) that incorporates the functionality of two 82C59 interrupt controllers. The two interrupt controllers are cascaded so that 14 external and two internal interrupts are possible. In addition, the 6300ESB I/O supports a serial interrupt scheme. All of the registers in these modules can be read and restored. This is required to save and restore system state after power has been removed and restored to the platform.

### 3.2.12 Advanced Programmable Interrupt Controller (APIC)

In addition to the standard ISA-compatible PIC described in the previous section, the 6300ESB I/O incorporates the Advanced Programmable Interrupt Controller (APIC).

### 3.2.13 Universal Serial Bus (USB) Controller

The 6300ESB I/O contains an Enhanced Host Controller Interface Specification for Universal Serial Bus, Revision 1.0 -compliant host controller that supports USB high-speed signaling. www.DataHigh-speed USB 2.0 allows data transfers up to 480 Mb/s which is 40 times faster than full-speed USB. The 6300ESB I/O also contains four Universal Host Controller Interface (UHCI) controllers that support USB full-speed and low-speed signaling. The Intel Server Board SE7210TP1-E supports up to four USB 2.0 ports, supports Universal Host Controller Interface (UHCI) and Enhanced Host Controller Interface (EHCI), and uses UHCI- and EHCI-compatible drivers.

The 6300ESB I/O provides the USB controller for all ports, as shown in Figure 4. The port arrangement is as follows:

- · Three ports are implemented with stacked back panel connectors

- One port is routed to a USB header which can be connected with a USB cable to the front panel connector

Figure 4. USB Port Configuration

#### ⇒ NOTES

Server systems that have an unshielded cable attached to a USB port may not meet FCC Class B requirements, even if no device is attached to the cable. Use shielded cable that meets the requirements for full-speed devices.

#### 3.2.14 Real Time Clock, CMOS SRAM, and Battery

The real-time clock provides a time-of-day clock and a multi-century calendar with alarm features. The real-time clock supports 256 bytes of battery-backed CMOS SRAM in two banks that are reserved for BIOS use.

A coin-cell battery (CR2032) powers the real-time clock and CMOS memory. When the server is not plugged into a wall socket, the battery has an estimated life of three years. When the server is plugged in, the standby current from the power supply extends the life of the battery. The clock is accurate to  $\pm$  13 minutes/year at 25 °C with 3.3 VSB applied.

The time, date, and CMOS values can be specified in the BIOS Setup program. The CMOS values can be returned to their defaults by using the BIOS Setup program.

#### www.DataSheet4U.com

NOTE

If the battery and AC power fail, the custom defaults, if previously saved, will be loaded into CMOS RAM at power-on.

### 3.2.15 GPIO

Various general purpose inputs and outputs are provided for custom system design. The number of inputs and outputs varies depending on the 6300ESB I/O configuration. All unused GPI pins must be pulled high or low, so that they are at a predefined level and do not cause undue side effects.

#### 3.2.16 Enhanced Power Management

The 6300ESB I/O's power management functions include enhanced clock control, local and global monitoring support for 14 individual devices, and various low-power (suspend) states (e.g., Suspend-to-DRAM and Suspend-to-Disk). A hardware-based thermal management circuit permits software-independent entrance to low-power states. The 6300ESB I/O contains full support for the Advanced Configuration and Power Interface (ACPI) Specification, Revision 2.0b.

### 3.2.17 System Management Bus (SMBus 2.0)

The 6300ESB I/O contains an SMBus Host interface that allows the processor to communicate with SMBus slaves. This interface is compatible with most I2C devices. Special I2C commands are implemented. The 6300ESB I/O's SMBus host controller provides a mechanism for the processor to initiate communications with SMBus peripherals (slaves). Also, the 6300ESB I/O supports slave functionality, including the Host Notify protocol. Hence, the host controller supports eight command protocols of the SMBus interface (see System Management Bus (SMBus) Specification, Version 2.0): Quick Command, Send Byte, Receive Byte, Write Byte/Word, Read Byte/Word, Process Call, Block Read/Write, and Host Notify.

## 3.3 Memory Subsystem

The Intel 827210 Memory Controller Hub (MCH) is one component of the Intel E7210 chipset. The MCH is a centralized controller for the system bus, the memory bus and the accelerated hub architecture interface.

The server board SE7210TP1-E provides four DIMM slots and supports a maximum memory capacity of 4 GB. The DIMM organization is x72, which includes eight ECC check bits. ECC from the DIMMs are passed through to the processor's system bus. Memory scrubbing, single-bit error correction and multiple-bit error detection is supported. Memory can be implemented with either single-sided (one row) or double-sided (two row) DIMMs.

| DIMM Capacity | Configuration | DDR SDRAM DDR SDRAM Organization<br>Density Front-side/Back-side |                   | Number of DDR<br>SDRAM Devices |

|---------------|---------------|------------------------------------------------------------------|-------------------|--------------------------------|

| 128 MB        | DS            | 64 Mbit                                                          | 8 M x 8/8 M x 8   | 16                             |

| 128 MB        | SS            | 128 Mbit                                                         | 16 M x 8/empty    | 8                              |

| 128 MB        | SS            | 256 Mbit                                                         | 16 M x 16/empty   | 4                              |

| 256 MB        | DS            | 128 Mbit                                                         | 16 M x 8/16 M x 8 | 16                             |

| 256 MB        | SS            | 256 Mbit                                                         | 32 M x 8/empty    | 8                              |

| 256 MB        | SS            | 512 Mbit                                                         | 32 M x 16/empty   | 4                              |

| 512 MB        | DS            | 256 Mbit                                                         | 32 M x 8/32 M x 8 | 16                             |

| 512 MB        | SS            | 512 Mbit                                                         | 64 M x 8/empty    | 8                              |

| 1024 MB       | DS            | 512 Mbit                                                         | 64 M x 8/64 M x 8 | 16                             |

#### **Table 2. Supported Memory Configurations**

**Note:** In the second column, "DS" refers to double-sided memory modules (containing two rows of DDR SDRAM) and "SS" refers to single-sided memory modules (containing one row of DDR SDRAM).

DIMM and memory configurations must adhere to the following:

- 2.5 V (only) 184-pin DDR SDRAM DIMMs with gold-plated contacts

- Unbuffered, single-sided or double-sided DIMMs with the following restriction:

- Double-sided DIMMS with x16 organization are not supported.

- Maximum total system memory: 4 GB

- Minimum total system memory: 128 MB

- ECC and non-ECC DIMMs supported

- Serial Presence Detect

- PC3200 (400 MHZ), PC2700 (333 MHZ), and PC2100 (266 MHZ) SDRAM DIMMs

Table 3 lists the supported system bus frequency and memory speed combinations.

| Table 3. Supported System | n Bus Frequency and M | Memory Speed Combinations |

|---------------------------|-----------------------|---------------------------|

|---------------------------|-----------------------|---------------------------|

| To use this type of DIMM | The processor's system bus frequency must be |  |

|--------------------------|----------------------------------------------|--|

| PC3200 (400 MHZ)         | 800 MHz                                      |  |

| PC2700 (333 MHZ)         | 800 or 533 MHz (Note)                        |  |

| PC2100 (266 MHZ)         | 800, 533, or 400 MHz                         |  |

**Note:** When using PC2700 (333 MHZ) memory with an 800 MHz system bus frequency processor, the memory channel will be set to 320 MHz.

Only DIMMs tested and qualified by Intel or a designated memory test vendor will be supported on the Intel Server Board SE7210TP1-E. A list of qualified DIMMs will be made available through http://support.intel.com/support/motherboards/server/SE7210TP1-E/. Note that all DIMMs are supported by design, but only fully qualified DIMMs will be supported.

#### ⇒ NOTES

To be fully compliant with all applicable DDR SDRAM memory specifications, the board should be populated with DIMMs that support the Serial Presence Detect (SPD) data structure. This allows the BIOS to read the SPD data and program the chipset to accurately configure memory settings for optimum performance. If non-SPD memory is installed, the BIOS will attempt to correctly configure the memory settings, but performance and reliability may be impacted or the DIMMs may not function under the determined frequency.

For ECC functionality, all installed DIMMs must be ECC. If both ECC and non-ECC DIMMs are used, ECC will be disabled and will not function.

#### 3.3.1 Memory Configurations

The Intel 827210 MCH component provides two features for enhancing memory throughput:

- Dual Channel memory interface. The board has two memory channels, each with two DIMM sockets.

- Dynamic Addressing Mode. Dynamic mode minimizes overhead by reducing memory accesses.

Table 4 summarizes the characteristics of dual and single channel configurations with and without the use of Dynamic Mode.

| Throughput<br>Level                        | Configuration                    | Characteristics                                |  |  |

|--------------------------------------------|----------------------------------|------------------------------------------------|--|--|

| Highest                                    | Dual Channel with Dynamic Mode   | All DIMMs matched                              |  |  |

|                                            |                                  | (Example configurations are shown in Figure 5) |  |  |

| Dual Channel without Dynamic Mode          |                                  | DIMMs matched from Channel A to Channel B      |  |  |

|                                            |                                  | DIMMs not matched within channels              |  |  |

|                                            |                                  | (Example configuration is shown in Figure 6)   |  |  |

|                                            | Single Channel with Dynamic Mode | Single DIMM or DIMMs matched with a channel    |  |  |

|                                            |                                  | (Example configurations are shown in Figure 7) |  |  |

| Lowest Single Channel without Dynamic Mode |                                  | DIMMs not matched                              |  |  |

|                                            |                                  | (Example configurations are shown in Figure 8) |  |  |

#### Table 4. Characteristics of Dual/Single Channel Configuration with/without Dynamic Mode

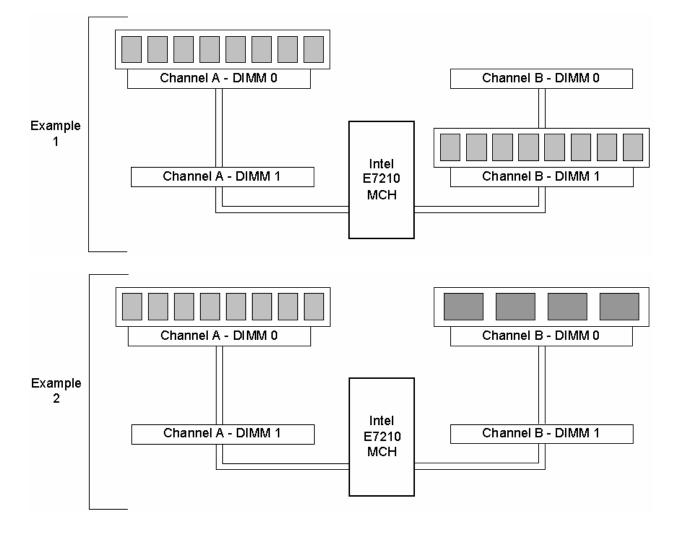

#### Dual Channel Configuration with Dynamic Mode (All DIMMs Matched)

Figure 5. Examples of Dual Channel Configuration with Dynamic Mode

Dual Channel Configuration without Dynamic Mode

- DIMMs not matched within channel

- DIMMs match Channel A to Channel B

Figure 6. Example of Dual Channel Configuration without Dynamic Mode

Single Channel Configuration with Dynamic Mode (Single DIMM or DIMMs matched within Channel)

Figure 7. Examples of Single Channel Configuration with Dynamic Mode

Single Channel Configuration without Dynamic Mode (DIMMs not matched)

Figure 8. Examples of Single Channel Configuration without Dynamic Mode

## 3.4 I/O Sub-System

The I/O sub-system is made up of several components: the 6300ESB I/O providing the PCI-X interfaces for the three PCI slots and riser slot on board 3, the on-board SCSI controller, the on-board Ethernet controllers, the onboard video controller, Super IO chip, and Management Sub-system. This section describes the function of each I/O interface and how they operate on the SE7210TP1-E server board.

#### 3.4.1 PCI Sub-System

The primary I/O bus for the Intel Server Board SE7210TP1-E is PCI, with two independent PCI buses. The PCI buses comply with the *PCI Local Bus Specification, Rev 2.2.* The PCI bus is directed through the Intel 6300ESB I/O Controller Hub. The table below lists the characteristics of the two PCI bus segments.

| PCI Bus Segment | Voltage | Width   | Speed  | Туре  | PCI I/O Card Slots                                                          |

|-----------------|---------|---------|--------|-------|-----------------------------------------------------------------------------|

| P32-A           | 5 V     | 32-bits | 33 MHz | PCI   | 1 - capable of supporting full-<br>length PCI add-in cards.                 |

|                 |         |         |        |       | Internal component use.                                                     |

| P64-A           | 3.3 V   | 64-bits | 66 MHz | PCI-X | 3 - capable of supporting full-<br>length PCI-X add-in cards                |

| P64-A           | 3.3 V   | 64-bits | 66 MHz | PCI-X | 1 - riser slot supporting low-<br>profile add-in cards (Only on<br>board 3) |

#### Table 5: PCI Bus Segment Characteristics

#### 3.4.1.1 P32-A: 32-bit, 33MHz PCI Sub-system

All 32-bit, 33-MHz PCI I/O for the SE7210TP1-E server board is directed through the 6300ESB I/O. The 32-bit, 33-MHz PCI segment created by the 6300ESB I/O is known as the P32-A segment. The P32-A segment supports the following devices:

- One 32-bit PCI slot

- 2D/3D Graphics Accelerator: ATI Rage XL Video Controller

- SIO Chip: Winbond\* W83627 HF-AW Super I/O

- Hardware monitoring sub-system: SMBUS.

#### 3.4.1.2 P64-A: 64-bit, 66MHz PCI Subsystem

There is one 64-bit PCI-X bus segment directed through the 6300ESB I/O. P64-A supports the interface for the on-board Adaptec\* 7901 Ultra 320 SCSI controller in addition to supporting up a maximum of three PCI slots.

#### 3.4.1.3 Scan Order

The BIOS assigns PCI bus numbers in a depth-first hierarchy, in accordance with the *PCI Local Bus Specification*. When a bridge device is located, the bus number is incremented in exception

of a bridge device in the chipsets. Scanning continues on the secondary side of the bridge until all subordinate buses are defined. PCI bus numbers may change when PCI-PCI bridges are added or removed. If a bridge is inserted in a PCI bus, all subsequent PCI bus numbers below the current bus will be increased by one.

### 3.4.1.4 Resource Assignment

The resource manager assigns the PIC-mode interrupt for the devices that will be accessed by the legacy code. The BIOS will ensure the PCI BAR registers and the command register for all devices are correctly set up to match the behavior of the legacy BIOS. Code cannot make assumptions about the scan order of devices or the order in which resources will be allocated to them. The BIOS will support the INT 1Ah PCI BIOS interface calls.

#### 3.4.1.5 Automatic IRQ Assignment

The BIOS automatically assigns IRQs to devices in the system for legacy compatibility. No method is provided to manually configure the IRQs for devices.

### 3.4.1.6 Option ROM Support

The option ROM support code in the BIOS will dispatch the option ROMs in available memory space in the address range 0C0000h-0DFFFFh and will follow all rules with respect to the option ROM space. The SE7210TP1-E BIOS will integrate option ROMs for the Intel 82547GI, Intel 82551QM, ATI Rage XL, SATA RAID and Adaptec 7901 SCSI controller.

### 3.4.1.7 Zero Channel RAID (ZCR) Capable Slot

The SCSI version of the Server Board SE7210TP1-E is capable of supporting the following zero channel RAID controllers, the Intel® RAID Controller SRCZCR and the Adaptec\* ASR-2010S RAID adapter. ZCR cards are only supported in slot one the P64-A PCI segment.

The ZCR add-in cards leverage the on-board SCSI controller along with their own built-in intelligence to provide a complete RAID controller subsystem on-board. The riser card and baseboard use an implementation commonly referred to as RAID I/O Steering (RAIDIOS) specification version 0.92 to support this feature. If either of these supported RAID cards are installed, then the SCSI interrupts are routed to the RAID adapter instead of to the PCI interrupt controller. Also the IDSEL of the SCSI controller is not driven to the controller and thus will not respond as an on-board device. The host-based I/O device is effectively hidden from the system.

### 3.4.2 DMA Channels

| Table 6. DMA Channels |  |              |                 |  |  |

|-----------------------|--|--------------|-----------------|--|--|

| DMA CI<br>Num         |  | Data Width   | System Resource |  |  |

| 0                     |  | 8 or 16 bits | Open            |  |  |

| 1                     |  | 8 or 16 bits |                 |  |  |

| 2                     |  | 8 or 16 bits | Diskette drive  |  |  |

| 3                     |  | 8 or 16 bits |                 |  |  |

| 4                     |  | 8 or 16 bits | DMA controller  |  |  |

| 5                     |  | 16 bits      | Open            |  |  |

| 6                     |  | 16 bits      | Open            |  |  |

| 7                     |  | 16 bits      | Open            |  |  |

### 3.4.3 Interrupts

The interrupts can be routed through the Advanced Programmable Interrupt Controller (APIC) portion of the 6300ESB I/O component. The APIC is supported in Windows\* 2000 Server and Windows XP and supports a total of 24 interrupts.

| IRQ | System Resource                                                    |

|-----|--------------------------------------------------------------------|

| NMI | I/O channel check                                                  |

| 0   | Reserved, interval timer                                           |

| 1   | Reserved, keyboard buffer full                                     |

| 2   | Reserved, cascade interrupt from slave PIC                         |

| 3   | COM2 (Note 1)                                                      |

| 4   | COM1 (Note 1)                                                      |

| 6   | Diskette drive                                                     |

| 8   | Real-time clock                                                    |

| 9   | Reserved for 6300ESB I/O system management bus                     |

| 10  | User available                                                     |

| 11  | User available                                                     |

| 12  | Onboard mouse port (if present, else user available)               |

| 13  | Reserved, math coprocessor                                         |

| 14  | Primary IDE (if present, else user available)                      |

| 15  | Secondary IDE (if present, else user available)                    |

| 16  | USB UHCI controller 1 (through PIRQA)                              |

| 17  | User available (through PIRQB)                                     |

| 18  | 6300ESB I/O USB controller 3 (through PIRQC)                       |

| 19  | 6300ESB I/O USB controller 2 (through PIRQD)                       |

| 20  | 6300ESB I/O LAN (through PIRQE)                                    |

| 21  | User available (through PIRQF)                                     |

| 22  | User available (through PIRQG)                                     |

| 23  | 6300ESB I/O USB 2.0 EHCI controller/User available (through PIRQH) |

Notes:

1. Default, but can be changed to another IRQ.

### 3.4.4 PCI Interrupt Routing Map

This section describes interrupt sharing and how the interrupt signals are connected between the PCI bus connectors and onboard PCI devices. The PCI specification specifies how interrupts can be shared between devices attached to the PCI bus. In most cases, the small amount of latency added by interrupt sharing does not affect the operation or throughput of the devices. In some special cases where maximum performance is needed from a device, a PCI device should not share an interrupt with other PCI devices. Use the following information to avoid sharing an interrupt with a PCI add-in card.

PCI devices are categorized as follows to specify their interrupt grouping:

- **INTA**: By default, all add-in cards that require only one interrupt are in this category. For almost all cards that require more than one interrupt, the first interrupt on the card is also classified as INTA.

- **INTB**: Generally, the second interrupt on add-in cards that require two or more interrupts is classified as INTB. (This is not an absolute requirement.)

- **INTC** and **INTD**: Generally, a third interrupt on add-in cards is classified as INTC and a fourth interrupt is classified as INTD.

The 6300ESB I/O has eight programmable interrupt request (PIRQ) input signals. All PCI interrupt sources either onboard or from a PCI add-in card connect to one of these PIRQ signals. Some PCI interrupt sources are electrically tied together on the Server Board SE7210TP1-E and therefore share the same interrupt. Table 8 shows an example of how the PIRQ signals are routed.

For example, using Table 8 as a reference, assume an add-in card using INTB is plugged into PCI bus connector 3. In PCI bus connector 3, INTB is connected to PIRQA, which is already connected to the Promise PDC20319 Controller. The add-in card in PCI bus connector 3 now shares an interrupt with the onboard interrupt source.

| IDSEL           | P_AD18              | PX_AD19             | PX_AD20             | PX_AD17 | P_AD16      | P_AD17        | P_AD18              |

|-----------------|---------------------|---------------------|---------------------|---------|-------------|---------------|---------------------|

| P_INTA*         |                     |                     |                     |         |             |               | INTA                |

| P_INTB*         |                     |                     |                     |         |             | INTB          | INTB                |

| P_INTC*         |                     |                     |                     |         |             |               | INTC                |

| P_INTD*         |                     |                     |                     |         |             |               | INTD                |

| P_INTE*         |                     |                     |                     |         |             |               | PIN B2, INTE        |

| P_INTF*         |                     |                     |                     |         | INTF        |               | PIN B4, INTE        |

| PX_INTA*        | INTA                | INTB                | INTC                |         |             |               |                     |

| PX_INTB*        | INTB                | INTC                | INTD                |         |             |               |                     |

| PX_INTC*        | INTC                | INTD                | INTA                |         |             |               |                     |

| PX_INTD*        | SCSI_A*             | INTA                | INTB                |         |             |               |                     |

| PX_IRQ*         |                     |                     |                     | IRQ3    |             |               |                     |

| REQ/GNT         | 1                   | 2                   | 3                   | 0       | 0           | 1             | 2                   |

| DataSheet4U.com | PCI 64 bit<br>SLOT1 | PCI 64 bit<br>SLOT2 | PCI 64 bit<br>SLOT3 | SCSI    | ATI<br>RAGE | LAN<br>10/100 | PCI 32 bit<br>SLOT6 |

| Table 8. | . PCI Interrupt | Routing Map |

|----------|-----------------|-------------|

|----------|-----------------|-------------|

### ⇒ NOTE

In PIC mode, the 6300ESB I/O can connect each PIRQ line internally to one of the IRQ signals (3, 4, 5, 6, 7, 9, 10, 11, 12, 14, and 15). Typically, a device that does not share a PIRQ line will have a unique interrupt. However, in certain interrupt-constrained situations, it is possible for two or more of the PIRQ lines to be connected to the same IRQ signal. See Table 7 for the allocation of PIRQ lines to IRQ signals in APIC mode.

### 3.4.5 SCSI Support

The SCSI sub-system consists of the Adaptec 7901 Single Channel, PC-2001-compliant PCI-X Ultra 320 SCSI controller which has one internal 80-pin connector (SCSI Channel A).

### 3.4.5.1 Adaptec 7901 Single Channel Ultra 320 SCSI Controller

The Adaptec 7901 is PCI bus master single-channel SCSI ASICs package. The Adaptec 7901 is an Ultra320 SCSI ASIC supporting a data transfer rate up to 320 MB/sec. The Adaptec 7901 complies with PCI Local Bus Specification, Revision 2.2 PCI-X Addendum, Rev. 1.0, and SCSI Parallel Interface-4 (SPI-4) for both Single-Ended (SE) and Low Voltage Differential (LVD) devices.

These ASICs comply with:

PCI Local Bus Specification, Revision 2.2 PCI-X Addendum, Revision. 1.0a SCSI Parallel Interface-4 (SPI-4), Revision 6

For both Single-Ended (SE) and LVD devices. In addition, they comply with the SCSI-3 standard and provide multimode SCSI support.

In PCI and PCI-X modes, these ASICs can operate as a multifunction 32-bit or 64-bit bus master capable of supporting zero-wait-state 32- or 64-bit memory transfers. They can also function as a PCI or PCI-X target.

The Adaptec 7901 supports up to 64-bit, 122 MHz PCI-X bus. The Ultra320 SCSI features for the Adaptec 7901 include:

- Double-transition (DT) clocking

- Paced transfers using packetized protocol

- Packetized protocol

- Dual data FIFO

- Quick arbitration and selection/reselection (QAS) protocol

- Manual PIO mode data transfer

- Automatic mode data transfer

- Normal (DMA) mode data transfer

www.DataSheet4U.ccCyclic redundancy check (CRC) codes

The single-channel Adaptec 7901 delivers Ultra320 SCSI data rates up to 320 MBytes/sec to address emerging bandwidth hungry applications, such as real-time video, data mining, Internet/Intranet, and scientific modeling and simulation. The chip features a 66 MHz, 64-bit PCI interface and a 133 MHz, 64-bit PCI-X interface.

Migration to new Ultra320 SCSI technology is easy with the Adaptec 7901. It is backward compatible with Ultra320, Ultra160, Ultra2, and earlier SCSI generations. The chip is available in a 356-pin Thermally Enhanced Ball Grid Array (TEBGA) package, which is signal compatible with the Ultra160 SCSI Adaptec 7892 for a smooth upgrade to Ultra320 SCSI.

Now offered with the Adaptec 7901 is HostRAID\*, an advanced RAID solution that includes hardware mirroring on the Adaptec 7901. HostRAID offers bootable RAID levels 0 and 1 with other advanced RAID features such as dedicated hot spares with automatic recovery, on-line capacity expansion, event scheduling, SAF-TE support, SNMP, DMI, and on-line RAID level migration.

The Adaptec 7901 uses Ultra320 technology to double Ultra160 data transfer rates up to 320 MBytes/sec. In addition, Adaptec Seamless Streaming\* technology allows the Adaptec 7901 to take full advantage of the SCSI packet protocol enhancements (transfers multiple commands, data contexts and statuses in single connection) that replaces the legacy SCSI protocol (transfers single commands, data contexts or statuses per connection).

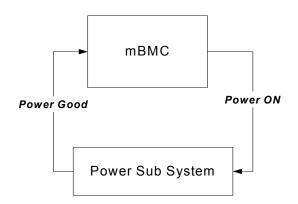

The Adaptec 7901 also supports Quick Arbitration and Selection (QAS) and SCSI arbitration fairness. QAS reduces the overhead of control release on the SCSI bus from one device to another. This improvement reduces command overhead and maximizes bus utilization. SCSI arbitration fairness prevents a device from dominating the bus by guaranteeing that all devices have an opportunity to arbitrate.