# datasheet

**PRODUCT SPECIFICATION**

CMOS analog NTSC/PAL image sensor with OmniPixel3-HS  $^{^{\mathsf{TM}}}$  technology for automotive applications

# applications

security and surveillance cameras

# ordering information

OV07959 (color, NTSC and PAL, Lead-free)

32-Pin PLCC

### features

- NTSC and PAL output (see sidebar note)

- high sensitivity

- automatic exposure/gain with 16-zone control

- horizontal and vertical windowing capability

- auto white balance control

- aperture/gamma correction

- slave compatible serial camera control bus (SCCB) control interface for register programming

- low power consumption

- low dark current

- overlay with single layer and color

- 32 bytes of one time programmable memory (OTP)

- SPI master for single static overlay and loading setting

- dynamic overlay controls

- defective pixel correction

#### note

Since it is impossible to check compatibility with all displays, check the interoperability before committing to mass production.

# key specifications (typical)

active array size:

NTSC: 648 x 488

power supply: core: 1.5V

analog: 3.3V

I/O: 1.8 ~ 3.3V

power requirements:

active: 220 mA standby: 28 µA

temperature range:

operating: -20°C to 70°C junction temperature

stable image: 0°C to 50°C junction temperature

optical size:

NTSC: 1/3.6" PAL: 1/3.6" chief ray angle: 0° (no microlens shift)

output formats: NTSC/PAL

maximum image transfer rate:

NTSC: 60 fields per second PAL: 50 fields per second

■ sensitivity: 12V/Lux-sec

■ shutter: rolling shutter (see sidebar note)

■ max S/N ratio: 46 dB

dynamic range: 72 dB @ 8x gain

scan mode: interlaced

pixel size: 6.0 µm x 6.0 µm

dark current: 15.6 mV/sec @ 50°C junction

temperature

image area: 4008 μm x 3024 μm

■ package dimensions: 10.0mm x 10.0 mm

#### note

Sensors with rolling shutter and high sensitivity can produce images with banding under certain fluorescent lighting conditions.

# table of contents

| 1 | sign | nal descriptions              | 01 |  |

|---|------|-------------------------------|----|--|

| 2 | syst | tem level description         | 03 |  |

|   | 2.1  | overview                      | 03 |  |

|   | 2.2  | architecture                  | 03 |  |

|   | 2.3  | PLL control                   | 05 |  |

|   | 2.4  | system control                | 05 |  |

|   |      | 2.4.1 external components     | 05 |  |

|   |      | 2.4.2 power management        | 05 |  |

|   |      | 2.4.3 system clock            | 05 |  |

|   | 2.5  | SCCB interface                | 06 |  |

|   | 2.6  | hardware and software standby | 06 |  |

|   |      | 2.6.1 hardware standby        | 06 |  |

|   |      | 2.6.2 software standby        | 06 |  |

|   | 2.7  | analog format                 | 06 |  |

| 3 | bloc | ck level description          | 07 |  |

|   | 3.1  | pixel array structure         | 07 |  |

| 4 | mec  | nechanical specifications     |    |  |

|   | 4.1  | physical specifications       | 08 |  |

|   | 4.2  | IR reflow specifications      | 09 |  |

# list of figures

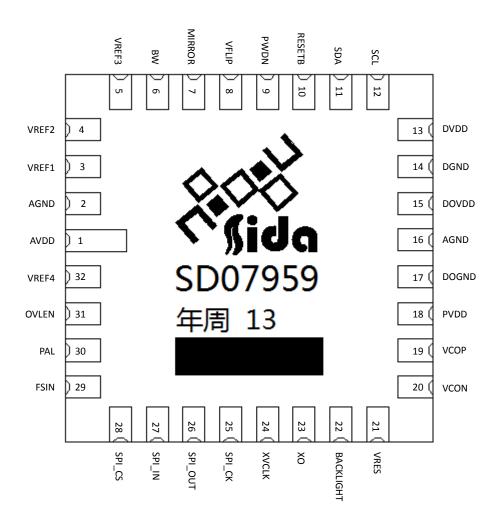

| figure 1-1 | pin diagram                       | 02 |

|------------|-----------------------------------|----|

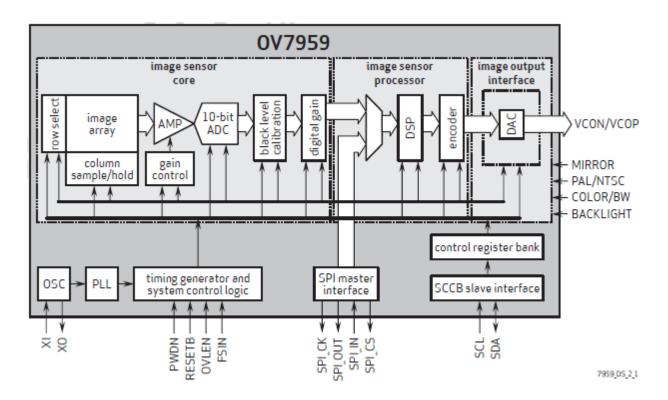

| figure 2-1 | OV7959 block diagram              | 03 |

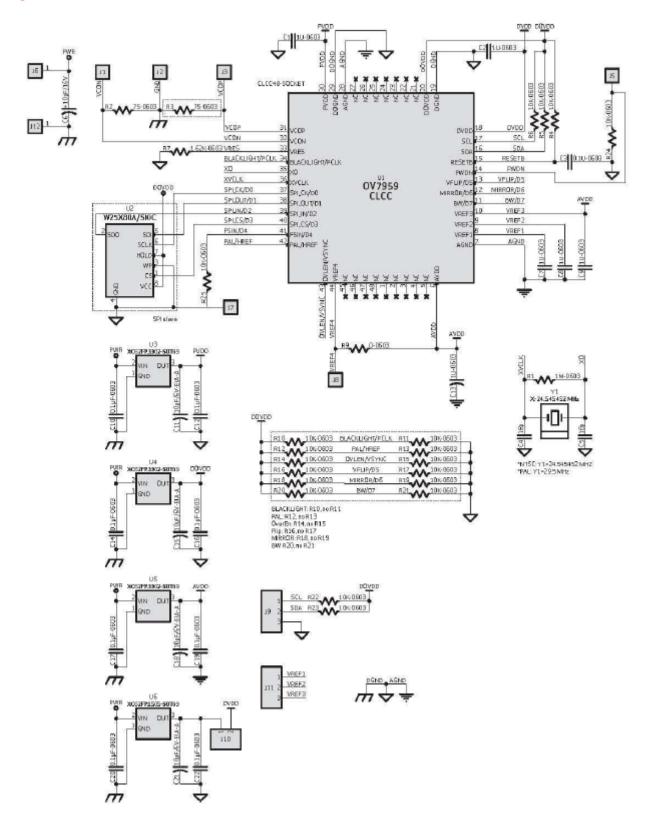

| figure 2-2 | OV7959 reference schematic        | 04 |

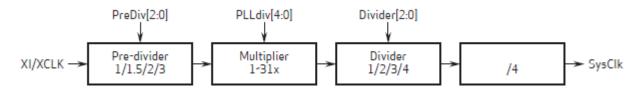

| figure 2-3 | PLL control diagram               | 05 |

| figure 3-1 | sensor array region filter layout | 07 |

| figure 4-1 | package specifications            | 30 |

| figure 4-2 | IR reflow ramp rate requirements  | 09 |

# list of tables

| table 1-1 | signal descriptions          | 01 |

|-----------|------------------------------|----|

| table 2-1 | analog format and frame rate | 06 |

| table 4-1 | package dimensions           | 30 |

| table 4-2 | reflow conditions            | 09 |

# 1 signal descriptions

**table 1-1** lists the signal descriptions and their corresponding pin numbers for the OV5653 image sensor. The package information is shown in **section 4**.

table 1-1 signal descriptions (sheet 1 of 2)

|               |             | •           |                                                                    |  |

|---------------|-------------|-------------|--------------------------------------------------------------------|--|

| Pad<br>number | signal name | pad<br>type | description                                                        |  |

| 01            | AVDD        | power       | 3.3V power                                                         |  |

| 02            | AGND        | ground      | analog ground                                                      |  |

| 03            | VREF1       | analog      | internal reference                                                 |  |

| 04            | VREF2       | analog      | internal reference                                                 |  |

| 05            | VREF3       | analog      | internal reference                                                 |  |

| 06            | BW          | input       | BW enable (active high) / DVP data bit 7                           |  |

| 07            | MIRROR      | input       | mirror enable (active high) / DVP data bit 6                       |  |

| 08            | VFLIP       | input       | vertical flip enable (active high) / DVP data bit 5                |  |

| 09            | PWDN        | input       | power down input (active high with pull down resistor)             |  |

| 10            | RESETB      | input       | reset input (active low with pull up resistor)                     |  |

| 11            | SDA         | I/O         | SCCB interface data pin                                            |  |

| 12            | SCL         | input       | SCCB interface input clock                                         |  |

| 13            | DVDD        | power       | 1.5V power reference                                               |  |

| 14            | DGND        | ground      | digital ground                                                     |  |

| 15            | DOVDD       | power       | 1.8~3.3V power                                                     |  |

| 16            | AGND        | ground      | analog ground                                                      |  |

| 17            | DOGND       | ground      | digital ground                                                     |  |

| 18            | PVDD        | power       | TV encoder power                                                   |  |

| 19            | VCOP        | output      | TV positive output                                                 |  |

| 20            | VCON        | output      | TV negative output                                                 |  |

| 21            | VRES        | analog      | internal reference (connected to AGND and 1.62K $\Omega$ resistor) |  |

| 22            | BACKLIGHT   | I/O         | backlight enable DVP PCLK output                                   |  |

| 23            | XO          | output      | clock output                                                       |  |

| 24            | XVCLK       | input       | system clock input                                                 |  |

| 25            | SPI_CK      | output      | SPI clock output / DVP data bit 0                                  |  |

|               |             |             |                                                                    |  |

table 1-1 signal descriptions (sheet 2 of 2)

| Pad<br>number | signal name | pad<br>type | description                             |

|---------------|-------------|-------------|-----------------------------------------|

| 26            | SPI_OUT     | output      | SPI data output / DVP data bit 1        |

| 27            | SPI_IN      | input       | SPI data input / DVP data bit 2         |

| 28            | SPI_CS      | output      | SPI chip select output / DVP data bit 3 |

| 29            | FSIN        | input       | frame sync signal / DVP data bit 4      |

| 30            | PAL         | input       | PAL switch / DVP HREF output            |

| 31            | OVLEN       | input       | overlay enable / DVP VSYNC output       |

| 32            | VREF4       | analog      | internal reference                      |

figure 1-1 pin diagram

# 2 system level description

#### 2.1 overview

The OV7959 color image sensor is low voltage, high performance CMOS image analog sensor that provides the full functionality of a single chip digital/analog NTSC/PAL image sensor using OmniPixel3-HS™ technology in a small footprint package. The image processing circuit also features black level calibration, lens correction, advanced auto white balance, auto exposure control, white/black pixel correction, color matrix and interpolation. It provides full-frame images via the control of the Serial Camera Control Bus (SCCB) interface. This product is ideal for applications requiring a small footprint, low voltage, low power and low cost color video camera.

#### 2.2 architecture

The OV7959 sensor core generates streaming pixel data at a constant frame rate with analog output.

The timing generator outputs clocks to access the rows of the imaging array, precharging and sampling the rows of array sequentially. In the time between precharging and sampling a row, the charge in the pixels decrease with exposure to incident light. This is the exposure time in rolling shutter architecture.

The exposure time is controlled by adjusting the time interval between precharging and sampling. After the data of the pixels in the row has been sampled, it is processed through analog circuitry to correct the offset and multiply the data with corresponding gain. Following analog processing is the ADC which outputs 10-bit data for each pixel in the array.

figure 2-1 OV7959 block diagram

figure 2-2 OV7959 reference schemetic

#### 2.3 PLL control

The OV7959 PLL allows input clock frequencies ranging from 6~27 MHz and has a maximum VCO frequency of 60 MHz. For NTSC output, the input clock frequency should be 24.545452 MHz. For PAL output, the input clock frequency should be 29.5 MHz.

PreDiv[2:0] (0x0305[2:0]) 1:1/1, 2:1/2, 3:1/3, others:1/1.5

PLLdiv[4:0] (0x0307[4:0]) is the multiplier parameter: multiplier 0:32x, 1:1x, 2:2x...31:31x

Divider[2:0] (0x0303[2:0]) is the system divider 1:/1, 2:/2, 3:/3, 4:/4

#### figure 2-3 OV7959 block diagra

### 2.4 system control

#### 2.4.1 external components

An external 3.14 ~ 3.47V power supply is used for array power. DOVDD, power for IO pad, can be from 1.7 to 3.47V. 1.5V core power is converted from DOVDD power by the internal regulator.

A resistor is required for TV out DAC power reference.

#### 2.4.2 power management

Suspend mode is controlled by the PWDN pin. In suspend mode, the internal clocks are stopped, sensor modules are powered off, and logic control blocks clock input from internal circuitry by logic control. Register values are saved while the sensor is in suspend mode.

Sleep mode can be controlled by register. During sleep mode, the SCCB clock keeps running. Register values can still be accessed while the sensor is in this mode.

In both suspend and standby modes, the TV output pin state is turned OFF and the 75 ohm termination is connected to GND.

#### 2.4.3 system clock

The on-chip PLL takes 24.545452 MHz (NTSC) or 29.5 MHz (PAL) clock signals from an external crystal. A clock divider is provided to generate different system frequencies.

#### 2.5 SCCB interface

The Serial Camera Control Bus (SCCB) interface controls the image sensor operation. Refer to the *OmniVision Technologies Serial Camera Control Bus (SCCB) Specification* for detailed usage of the serial control port.

## 2.6 hardware and software standby

Two suspend modes are available for the OV7959:

- · hardware standby

- · software standby

#### 2.6.1 hardware standby

To initiate hardware standby mode, the PWDN pin must be tied to high. When this occurs, the OV7959 internal device clock is halted and all internal counters are reset and registers are maintained.

#### 2.6.2 software standby

Executing a software standby through the SCCB interface suspends internal circuit activity but does not halt the device clock. All register content is maintained in standby mode.

### 2.7 analog format

#### table 2-1 analog format and frame rate

| function      | format | field rate    | input clock   |

|---------------|--------|---------------|---------------|

| analog autnut | NTSC   | 60 fields/sec | 24.545452 MHz |

| analog output | PAL    | 50 fields/sec | 29.5 MHz      |

# 3 block level description

### 3.1 pixel array structure

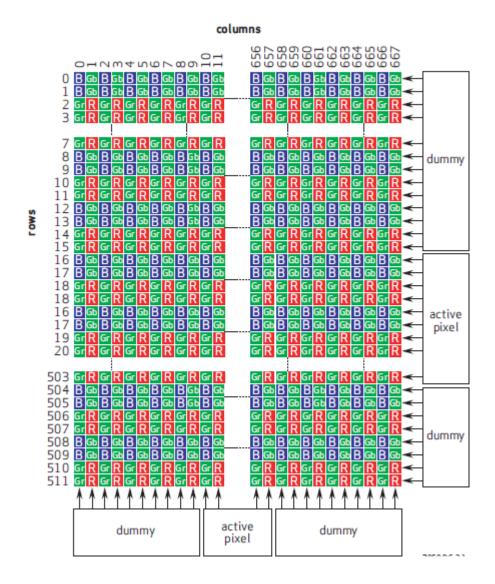

The OV7959 sensor has an image array of 668 columns by 512 rows (342,016 pixels).

Of the 342,016 pixels, 648 x 488 (316,224) are active pixels and can be output. The other pixels are used for black level calibration and interpolation

The sensor array design is based on a field integration read-out system with line-by-line transfer and an electronic shutter with a synchronous pixel read-out scheme.

figure 3-1 sensor array region color filter layout

# 4 mechanical specifications

### 4.1 physical specifications

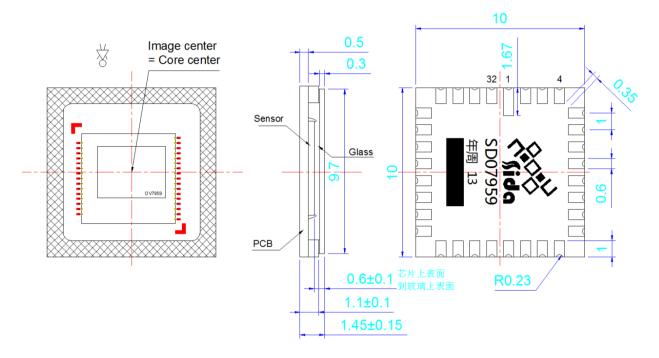

figure 4-1 package specifications

**Note1** all exposed metallized areas shall be gold-plate 0.05um min. thickness over nickel plate unless otherwise specified in purchase order

Note2 seal area and die attach area shall be without metallization

table 4-1 package dimensions (sheet 1 of 2)

| dimensions                        | millimeters  | inches                           |

|-----------------------------------|--------------|----------------------------------|

| Package size                      | 10.0±0.10 sq | $0.394 \!\pm\! 0.004\mathrm{sq}$ |

| Package height                    | 1.45±0.15    | 0.057±0.006                      |

| Substrate base height             | 0.5±0.05     | 0.0197±0.002                     |

| Cavity size                       | 8.10±0.20 sq | $0.319 \pm 0.008  \mathrm{sq}$   |

| Castellation height               | 0.52±0.05    | $0.021 \pm 0.002$                |

| Pin 1# pad size                   | 0.60 x 1.70  | 0.024 x 0.067                    |

| Pad size                          | 0.60 x 1.00  | 0.024 x 0.039                    |

| Pad pitch                         | 1.00±0.05    | 0.039±0.002                      |

| Package edge to first lead center | 0.85±0.10    | 0.034±0.004                      |

| End-to-end pad center-center      | 9.00±0.10    | $0.354 \pm 0.004$                |

table 4-1 package dimensions (sheet 2 of 2)

| dimensions                  | millimeters      | inches                         |

|-----------------------------|------------------|--------------------------------|

| Glass size                  | 9.70±0.10 sq     | $0.382\!\pm\!0.004\mathrm{sq}$ |

| Glass height                | $0.3 \pm 0.05$   | 0.012±0.002                    |

| Die thickness               | $0.30 \pm 0.015$ | 0.012±0.0006                   |

| Top of glass to image plane | 0.6±0.10         | 0.024±0.004                    |

| Substrate height            | 1.1±0.10         | 0.043±0.004                    |

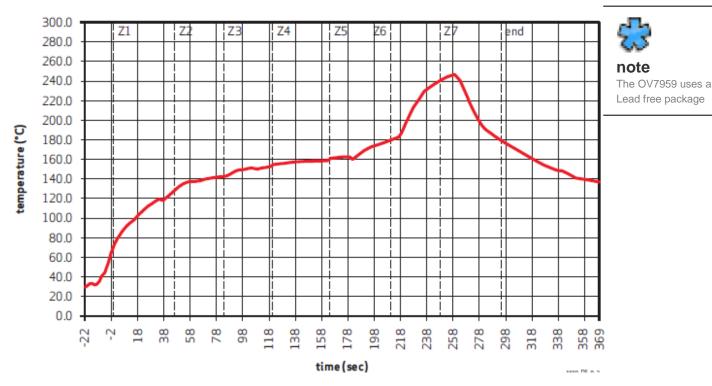

### 4.2 IR reflow specifications

figure 4-2 IR reflow ramp rate requirements

table 4-2 reflow conditions

| zone    | description                                                                                                             | exposure                          |

|---------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Ramp up | Heating from room temperature to 150 $^{\circ}\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ | Temperature slope ≤3°C per second |

| soaking | Heating from 150 $^{\circ}$ C to 200 $^{\circ}$ C                                                                       | 30 - 150 seconds                  |

| reflow  | Temperature higher than 217 $^{\circ}\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$          | 30 - 120 seconds                  |

| peak    | Maximum temperature in SMT                                                                                              | <b>245</b> ℃                      |

| cooling | Cooling from 217℃ to room temperature                                                                                   | Temperature slope ≤6°C per second |

- a. Maximum number of reflow cycles = 3

- b. N2 gas reflow or control O2 gas PPM < 500 as recommendation