# SCT3288 Advanced Baseband Processor

# DATASHEET

Advance Information

# Features

D3288/3

• Low power 4FSK modem

June 2023

- Digital PMR protocol engine

- Integrated vocoder

- Standards compliant AMBE+2<sup>™</sup>

- Other 2400bps options

- Integrated RF and audio interfaces

- 24-bit ADC/DACs

- Flexible receiver support

- I/Q or superhet

- Noise and anti-howl suppression

- Digital and analog PMR support

- With auto mode detection Single 3.3V supply

- On chip step down regulator for core supply

- 88QFN package

### **Applications**

- Dual mode PMR radios

- Dual mode PMR modules

- FSK data modems

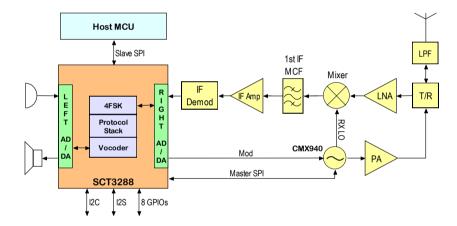

#### DMR/dPMR System with Conventional RF

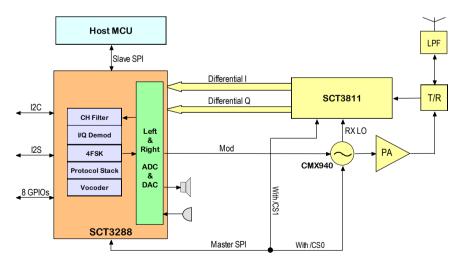

DMR/dPMR System with SCT3811

# **1** Brief Description

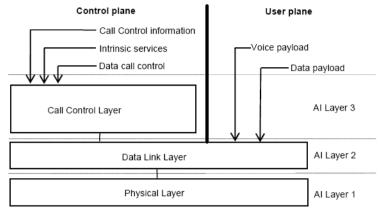

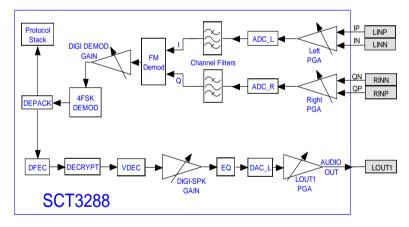

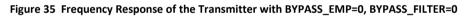

The SCT3288 is a low power high performance baseband processor supporting dPMR and DMR protocol. With an internal codec (audio band ADC and DAC), it completes the entire physical layer and data link layer, and most of the call control layer processing of dPMR and DMR protocols. In dPMR mode, SCT3288 complies with ETSI TS 102 490 and ETSI TS 102 658. In DMR mode, it complies with ETSI TS 102 361. The two front page diagrams show the SCT3288 used in a dPMR or DMR system with conventional RF circuits and used with the SCT3811 single conversion receiver. The SCT3288 is designed for easy migration from analog radios. The system designer can start with a typical analog radio, replacing the analog baseband processor with the SCT3288, to obtain the simplest form of a dPMR or DMR radio. To achieve the full potential of dPMR or DMR, application-level software programming is required on the host processor.

The SCT3288 contains an I2S interface, a slave SPI interface, a master SPI interface with two chip selectors, an I2C interface and 8 programmable I/O ports. The I2S is used for connection with an external codec or a receiver with digital I/Q interface. The master SPI can be used to control the RF PLL or a transceiver such as CMX940 and SCT3811.

The SCT3288 communicates with a host processor through the slave SPI interface. The firmware of the SCT3288 is stored on chip. The SCT3288 gives a response to the host processor to indicate that it has started up successfully and is ready to accept commands from the host processor. Following a correct command from the host the SCT3288 will then load and execute the entire firmware.

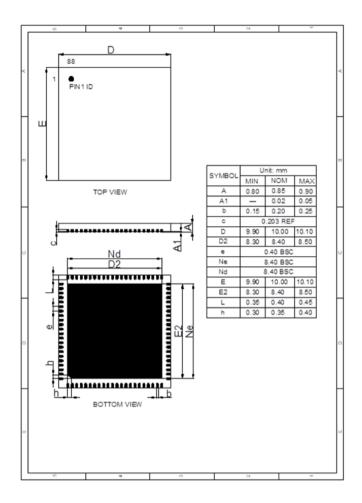

The SCT3288 core logic operates at 1.2 V, and the I/O operates at 1.8-3.6V. The SCT3288 is supplied in a QFN88 10x10mm<sup>2</sup> and 0.4mm pitch, ideal for small form factor designs.

The SCT3288 provides:

#### DMR

- Supports DMR Tier1 and Tier 2 (ETSI TS 102 361)

- Air interface physical layer (layer 1)

- Air interface data link layer (layer 2)

- Air interface call control layer (layer 3)

- Annex C (TS 102 361-2) support, with BCD addressing and automatic call match

- Transmit in slotted or continuous mode

- Receive in slotted or continuous mode

- Support TDMA direct mode

#### dPMR

- Supports dPMR Tier 1 (ETSI TS 102 490)

- Supports dPMR Tier 2 (ETSI TS 102 658) Mode 1 and Mode 2

- Air interface physical layer (layer 1)

- Air interface data link layer (layer 2)

- Air interface call control layer (layer 3)

- Full Annex A support, with BCD addressing and automatic call match

#### 4 FSK Modem

- 4800 bps data rate for dPMR and 9600 bps for DMR

- Automatic frame sync detection

- Programmable modulation index

- Support two-point modulation, and I/Q modulation

- BER Test Mode complied with ITU 0.153

#### Vocoder

- Built-in AMBE+2<sup>™</sup> vocoder from DVSI

- Supports 1031 Hz Tone and Silence Test Mode

#### Analog Mode Support

- Supports voice channel filters (LPF/HPF/Limiter), as well as pre-emphasis and de-emphasis filters

- Supports CTCSS/DCS generation and detection

- Supports arbitrary CTCSS/DCS code, and blind detection

- Supports the non-standard 55 Hz CTCSS tail tone

- Supports compander

• Automatic mode detection (analog and dPMR or analog & DMR) in receiver mode

### **Digital interfaces**

- 1 x I2S

- 1 x I2S\_Tx only

- 1 x I2S\_Rx only

- 1 x Slave SPI

- 1 x Master SPI with two chip selectors

- 1 x I2C

- 8 x programmable I/O

- 1 x UART

#### **Clock Generation Unit**

• The clock circuit can operate with either a crystal or external clock generator

#### **Power Supply**

- On-chip LDO generates 3.0V for internal analog circuits (except Codec) power supply.

- On-chip DC/DC generates 1.2V for core power supply.

- An external dedicated 3.3V analog power supply for the internal codec.

- A dedicated IO power supply, of 1.8V to 3.6V.

#### Codec

- Two channel 24-bit sigma-delta ADC and DAC.

- Audio PLL.

- Two differential inputs and 2 single-ended inputs.

- Two pairs of line outputs

- Programmable analog and digital gain

#### CONTENTS

| <u>Section</u> |                                               | Page |

|----------------|-----------------------------------------------|------|

| 0              | Introduction                                  | ii   |

| 1              | Brief Description                             | 2    |

| 2              | Block Diagram                                 | 8    |

| 3              | Performance Specification                     |      |

| 3.1            | Electrical Performance                        |      |

| 3.1.1          | Absolute Maximum Ratings – typical figures    |      |

| 3.1.2          | Operating Limits                              |      |

| 3.1.3          | Operating Characteristics                     |      |

| 3.2            | Slave SPI Timing                              | 12   |

| 3.3            | I2S Timing                                    |      |

| 3.3.1          | I2S Timing in Slave Mode                      |      |

| 3.3.2          | I2S Timing in Master Mode                     |      |

| 3.4            | Master SPI Timing                             |      |

| 3.5            | I2C Timing                                    |      |

| 3.6<br>3.7     | Reset and Power-on Timing<br>Interrupt Timing |      |

|                |                                               |      |

| 4              | Pin and Signal List                           |      |

| 5              | Component and PCB Recommendations             |      |

| 5.1            | Recommended External Components               |      |

| 5.1.1          | Xtal Interface                                |      |

| 5.1.2          | I2C Interface                                 |      |

| 5.1.3<br>5.1.4 | DC/DC Components                              |      |

| 5.1.5          | PLL and ROSC                                  |      |

| 5.1.6          | Digital Power and Decoupling                  |      |

| 5.1.7          | Codec                                         |      |

| 5.1.8          | GPIO Pins                                     |      |

| 6              | Hardware Description                          | . 23 |

| 6.1            | Clock Generation Unit                         |      |

| 6.1.1          | Xtal Frequency                                |      |

| 6.1.2          | PLL                                           | 23   |

| 6.1.3          | ROSC                                          | 23   |

| 6.2            | Power Supply                                  |      |

| 6.2.1          | DC/DC converter                               |      |

| 6.2.2          | LDO regulator                                 |      |

| 6.2.3          | IO Power Supply                               |      |

| 6.3            | Serial Interfaces                             |      |

| 6.3.1<br>6.3.2 | Slave SPI Master SPI                          |      |

| 6.3.2<br>6.3.3 | Master 591                                    |      |

| 6.3.4          | 12C                                           | -    |

| 6.3.5          | UART                                          | -    |

| 6.4            | System Interface                              |      |

| 6.5            | Programmable I/O                              | 28   |

| 6.6            | Codec                                         | 28   |

| 6.6.1          | Features                                      | 28   |

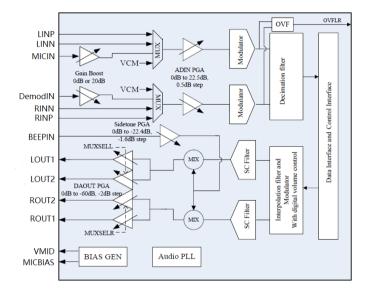

| 6.6.2          | Codec Block Diagram                           |      |

| 6.6.3          | Codec Description                             | 29   |

| 7              | Detailed Description                          | 31   |

| 7.1            | dPMR and DMR Implementation                   |      |

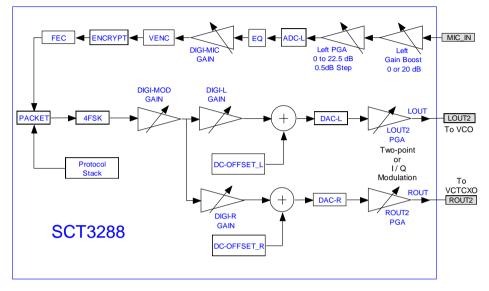

| 7.1.1          | Signal Flow for DMR/dPMR Transmitter          |      |

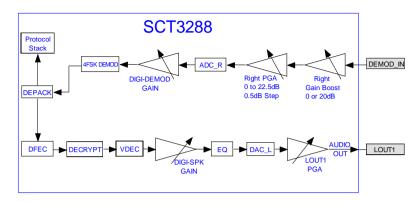

| 7.1.2          | Signal Flow for DMR/dPMR Receiver             |      |

| 7.1.3          | RF Timing Control for DMR                     |      |

| 7.1.4          | Vocoder Support<br>Analog Radio Support       |      |

| 7.2<br>7.2.1   | Signal Flow for Analog Transmitter            |      |

| 7.2.2          | Signal Flow for Analog Receiver               |      |

|                | - 0                                           |      |

<u>Page</u>

Page

| 7.3   | Premium Features (please refer to CML/Sicomm for further information on availability) |    |

|-------|---------------------------------------------------------------------------------------|----|

| 7.3.1 | Encryption                                                                            |    |

| 7.3.2 | Voice Recording and Play Back                                                         |    |

| 7.4   | Boot Loading                                                                          |    |

| 7.5   | Work Mode                                                                             |    |

| 7.5.1 | Normal Mode                                                                           | 40 |

| 7.5.2 | Sleep Mode                                                                            | 40 |

| 7.5.3 | Halt Mode                                                                             | 40 |

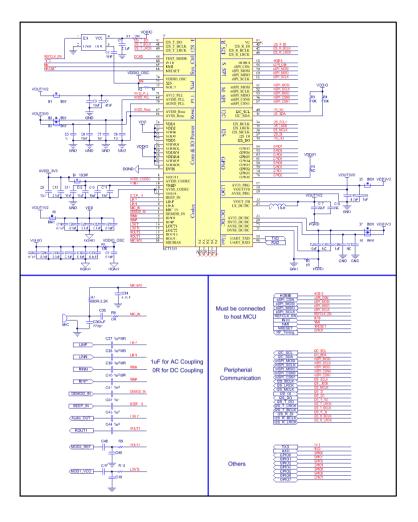

| 8     | Typical Application Circuit                                                           |    |

| 9     | Packet Interface                                                                      |    |

| 10    | Packaging                                                                             | 43 |

| 11    | Ordering Information                                                                  |    |

|       | -                                                                                     |    |

# <u>Table</u>

| Table 1 | Slave SPI Default Setting                    | .24 |

|---------|----------------------------------------------|-----|

|         | Master SPI Default Settings                  |     |

|         | I2C Default Setting                          |     |

|         | UART Default Setting                         |     |

|         | System Interface                             |     |

|         | Programmable I/O Signals                     |     |

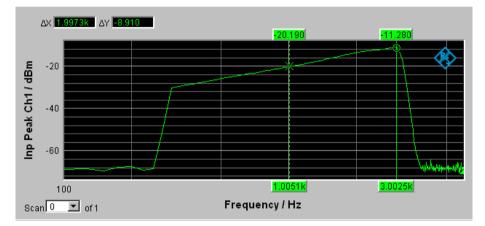

|         | Frequency Response of the Analog Transmitter |     |

|         | Frequency Response of the Analog Receiver    |     |

|         | ) SCT3288 Work Mode                          |     |

# **Figure**

| Figure 1 SCT3288 Block Diagram                                                                   |    |

|--------------------------------------------------------------------------------------------------|----|

| Figure 2 Slave SPI Timing                                                                        |    |

| Figure 3 I2S Timing in Slave Mode                                                                |    |

| Figure 4 I2S Timing in Master Mode                                                               |    |

| Figure 5 Master SPI Timing                                                                       |    |

| Figure 6 I2C Timing                                                                              |    |

| Figure 7 SCT3288 Reset and Power-on Timing                                                       |    |

| Figure 8 Interrupt Timing                                                                        |    |

| Figure 9 Xtal Interface                                                                          |    |

| Figure 10 I2C Interface                                                                          |    |

| Figure 11 DC/DC Components                                                                       | 19 |

| Figure 12 LDO Components                                                                         |    |

| Figure 13 PLL and ROSC Power Supply Decoupling                                                   | 20 |

| Figure 14 Digital Power and Decoupling                                                           | 20 |

| Figure 15 Codec Power and Reference                                                              | 21 |

| Figure 16 Microphone Input                                                                       | 21 |

| Figure 17 Demod and Beep Input                                                                   | 21 |

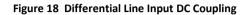

| Figure 18 Differential Line Input DC Coupling                                                    | 22 |

| Figure 19 Differential Line Input AC Coupling                                                    | 22 |

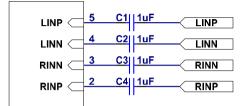

| Figure 20 Line Output                                                                            | 22 |

| Figure 21 Slave SPI Operation                                                                    | 24 |

| Figure 22 Data Transfer for I2C                                                                  | 25 |

| Figure 23 I2S Bus with delay mode, left alignment (N=16, 24, 32)                                 | 26 |

| Figure 24 I2S Bus without delay mode, left alignment (N=16, 24, 32)                              | 27 |

| Figure 25 I2S Bus with delay mode, right alignment (N=16, 24, 32)                                |    |

| Figure 26 I2S Bus without delay mode, right alignment (N=16, 24, 32)                             |    |

| Figure 27 Codec Block Diagram                                                                    |    |

| Figure 28 Signal Flow for DMR/dPMR Transmitter                                                   |    |

| Figure 30 Signal Flow for DMR/dPMR for FM Demodulated Signal Input                               |    |

| Figure 31 Signal Flow for DMR/dPMR Receiver for I/Q Signal Input                                 |    |

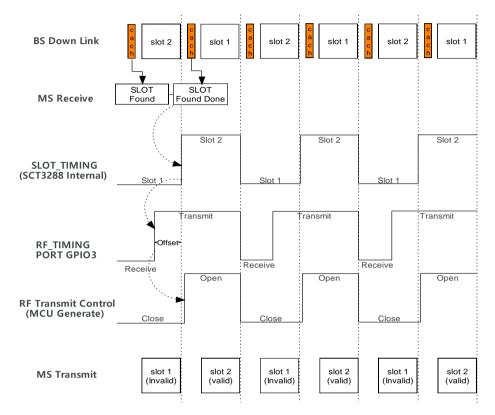

| Figure 32 TDMA Timing Control                                                                    |    |

| Figure 33 Signal Flow for Analog Transmitter                                                     |    |

| Figure 34 Frequency Response of the Transmitter with CH_SEL=0, BYPASS_EMP = 0, BYPASS_FILTER = 0 |    |

| Figure 35 Signal Flow for Analog Receiver with FM Demodulated Signal Input                       |    |

|                                                                                                  |    |

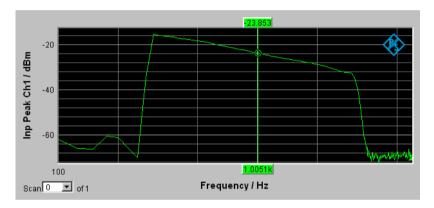

| Figure 36 Frequency Response of the Transmitter with BYPASS EMP=0, BYPASS FILTER=0 | 38 |

|------------------------------------------------------------------------------------|----|

| Figure 37 Signal Flow for Analog Receiver with I/Q Signal Input                    |    |

| Figure 38: SCT3288 Application Circuit                                             |    |

| Figure 39 Mechanical Outline of SCT3288 QFN88 Package                              | 43 |

# <u>History</u>

| Version | Changes                            | Date          |

|---------|------------------------------------|---------------|

| 3       | Limited Production release         | June 2023     |

| 2       | First public launch                | November 2021 |

| 1       | First release, Advance Information | June 2020     |

This is Advance Information; changes and additions may be made to this specification. Parameters marked TBD or left blank will be included in later issues. Items that are highlighted or greyed out should be ignored. These will be clarified in later issues of this document.

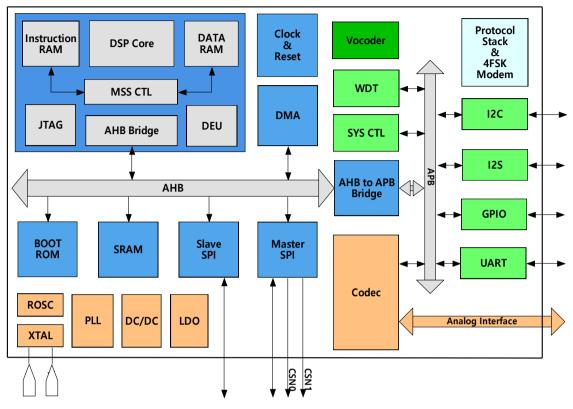

# 2 Block Diagram

Figure 1 SCT3288 Block Diagram

# **3** Performance Specification

# 3.1 Electrical Performance

# 3.1.1 Absolute Maximum Ratings – typical figures

Exceeding these maximum ratings can result in damage to the device.

| Parameter                              | Min. | Max.      | Unit  |

|----------------------------------------|------|-----------|-------|

| AV33 to AVSS                           | -0.3 | 3.9       | V     |

| DV33 to DVSS                           | -0.3 | 3.9       | V     |

| AVDD to AVSS                           | -0.3 | 3.9       | V     |

| VDD to VSSD                            | -0.3 | 1.5       | V     |

| AV12_PLL to AVSS                       | -0.3 | 1.5       | V     |

| VDDIO to VSSD                          | -0.3 | 3.9       | V     |

| Voltage on any pin to VSSD             | -0.3 | VDDIO+0.3 | V     |

| Voltage on any pin to AVSS             | -0.3 | AV33+0.3  | V     |

| Operating temperature range            | -40  | 85        | °C    |

| Storage Temperature                    | -55  | 125       | °C    |

| Total Power Dissipation at Tamb = 25°C | -    | 3500      | mW/°0 |

# 3.1.2 Operating Limits

Correct operation of the device outside these limits is not implied. The typical value is recommended.

| Parameter                   | Note | Min. | Тур            | Max. | Unit |

|-----------------------------|------|------|----------------|------|------|

| AV33_DC/DC to AVSS          |      | 1.7  | 3.3            | 3.6  | V    |

| DV33_DC/DC to DVSS          |      | 1.7  | 3.3            | 3.6  | V    |

| AV33_PRG to AVSS            |      | 3.0  | 3.3            | 3.6  | V    |

| AVDD_CODEC to AVSS          |      | 3.0  | 3.3            | 3.6  | V    |

| AVDD to AVSS                | 1    | 2.7  | 3.0            | 3.6  | V    |

| VDD to VSSD                 | 2    | 1.08 | 1.2            | 1.32 | V    |

| AV12 to AVSS                | 2    | 1.08 | 1.2            | 1.32 | V    |

| VDDIO to VSSD               |      | 1.8  | -              | 3.6  | V    |

| XTAL Frequency              |      | 12.8 | 19.2           | 26   | MHz  |

| External Clock Frequency    |      | 12.8 | 19.2 /<br>38.4 | 40   | MHz  |

| System Clock Frequency      |      |      | 153.6          | 200  | MHz  |

| Operating temperature range |      | -40  | 25             | 85   | С    |

Note:

1. AVDD comes from the on-chip LDO

2. The power supply comes from the on-chip DC/DC

### 3.1.3 Operating Characteristics

For the following conditions unless otherwise specified:

At 25 °C, AV33 = DV33 = VDDIO = 3.3V, AVDD = 3.0V (powered by on-chip LDO), VDD = 1.2V (powered by on-chip DC/DC). System clock is 153.6 MHz, and the codec sample rate is 24 kHz. Unused peripheral interface in typical application scenario (I2S\_R and I2S\_T) is disabled.

|                                  | Supply Current                              |      |           |      |          |

|----------------------------------|---------------------------------------------|------|-----------|------|----------|

| Parameter                        | Comment                                     | Min  | Тур       | Max  | Unit     |

| Normal mode                      |                                             |      |           |      |          |

| VDD                              | (Note 1)                                    |      | 24.1      |      | mA       |

| AV12_PLL                         |                                             |      | 0.52      |      | mA       |

| AVDD_ PLL                        |                                             |      | 0.5       |      | mA       |

| AVDD_ROSC                        |                                             |      | 13        |      | uA       |

| VDDIO                            |                                             |      | 0.88      |      | mA       |

| Sleep Mode                       |                                             |      |           |      |          |

| VDD                              | (Note 1)                                    |      | 0.57      |      | mA       |

| AV12_PLL                         | ( )                                         |      | 1.3       |      | uA       |

| AVDD_PLL                         |                                             |      | <1        |      | uA       |

| AVDD_ROSC                        |                                             |      | 13        |      | uA       |

| VDDIO                            |                                             |      | 0.8       |      | mA       |

| Halt Mode                        |                                             |      | 0.0       |      |          |

| VDD                              | (Note 1)                                    |      | 0.56      |      | mA       |

| AV12_PLL                         |                                             |      | 1.3       |      | uA       |

| _                                |                                             |      | <1        |      | uA       |

| AVDD_ PLL<br>AVDD_ROSC           |                                             |      | 13        |      | uA<br>uA |

| _                                |                                             |      |           |      |          |

| VDDIO                            |                                             |      | 0.8       |      | mA       |

|                                  | Digital Interface Logic                     |      |           |      |          |

| Logic Input                      |                                             | 2    |           |      |          |

| ViH                              | VDDIO = 3.3V                                | 2    |           |      | V        |

| V <sub>IL</sub>                  | VDDIO = 3.3V                                |      |           | 0.8  | V        |

| V <sub>IH</sub>                  | VDDIO = 2.5V                                | 1.7  |           |      | V        |

| VIL                              | VDDIO = 2.5V                                |      |           | 0.7  | V        |

| V <sub>IH</sub>                  | VDDIO = 1.8V                                | 1.05 |           |      | V        |

| V <sub>IL</sub>                  | VDDIO = 1.8V                                |      |           | 0.69 | V        |

| Logic Output                     |                                             |      |           |      |          |

| V <sub>он</sub>                  | VDDIO = 3.3V,                               | 2.4  |           |      | V        |

| V <sub>OL</sub>                  | $I_0 = 4 \text{ mA}$                        |      |           | 0.4  | V        |

| V <sub>OH</sub>                  | VDDIO = 2.5V,                               | 1.7  |           |      | V        |

| V <sub>OL</sub>                  | lo= 2mA                                     |      |           | 0.7  | V        |

| V <sub>OH</sub>                  | VDDIO = 1.8V,                               | 1.17 |           |      | V        |

| Vol                              | lo= 2mA                                     |      |           | 0.45 | V        |

|                                  | On-chip DC/DC                               |      |           |      |          |

| Input Voltage Range Vin          | • •                                         | 1.7  | 3.3       | 3.6  | V        |

| Output Voltage Vout              |                                             | 1.08 | 1.2       | 1.32 | V        |

| Efficiency η                     | SCT3288 Works in normal mode @ 3.3V input   |      | 76        |      | %        |

| Maximum Output Current           | mode @ 3.3v mput                            |      |           | 300  | m۸       |

| Maximum Output Current           | On shin LDO                                 |      |           | 500  | mA       |

| land Maltana Dan 14              | On-chip LDO                                 | 2.0  | 2.2       | 2.6  |          |

| Input Voltage Range Vin          |                                             | 3.0  | 3.3       | 3.6  | V        |

| Output Voltage Vout              | Vin >= 3V + Vdrop                           |      | 3.0       |      | V        |

|                                  | 3V <vin<3v+vdrop<sup>(2)</vin<3v+vdrop<sup> |      | Vin-Vdrop |      | V        |

| Dropout Voltage Vdrop            |                                             |      | 250       |      | m۷       |

| Output Accuracy                  | When Vout = 3V                              |      | +/-10     |      | %        |

| Output Current lout              |                                             |      |           | 200  | mA       |

|                                  | Codec                                       |      |           |      |          |

| Power Supply Range<br>AVDD_CODEC |                                             | 3.0  | 3.3       | 3.6  | V        |

| Supply current I <sub>AVDD</sub> | DAC&ADC, LOUT1, ROUT2                       |      |           |      |          |

| Normal mode                      | and DEMOD_IN active                         |      | 16.1      |      | mA       |

| Supply current I <sub>AVDD</sub>                    | All blocks powered down |       |            |     | _    |

|-----------------------------------------------------|-------------------------|-------|------------|-----|------|

| Sleep mode                                          | except Vref             |       | 0.3        |     | mA   |

| Supply current I <sub>AVDD</sub><br>Deep Sleep mode | All blocks powered down |       |            | <1  | μA   |

| VMID                                                |                         |       | 0.5*AVDD   |     | V    |

| Microphone Bias                                     |                         |       |            |     |      |

| Bias Voltage                                        |                         |       | 0.75*AVDD  |     | V    |

| Maximum Output Current                              |                         |       |            | 3   | mA   |

| Capacitive Load                                     |                         |       |            | 50  | pF   |

| Line Input                                          |                         |       |            |     |      |

| Resolution                                          |                         |       | 24         |     | bit  |

| THD (Total Harmonic Distortion)                     | (Note 3)                |       | -82        | -70 | dB   |

| Dynamic Range<br>(-60dB input, A-weighted)          | (Note 4)                |       | 96         |     | dB   |

| S/N (A-weighted)                                    | (Note 5)                | 80    | 96         |     | dB   |

| Channel Separation                                  | (Note 6)                |       | 100        |     | dB   |

| Channel Matching                                    |                         |       | 0.2        |     | dB   |

| Full Scale Input Voltage                            |                         |       |            |     |      |

| Single-ended V <sub>FS</sub>                        |                         |       | AVDD       |     | Vpp  |

| Differential V <sub>FS</sub>                        |                         |       | 2*AVDD     |     | Vpp  |

| Input Impedance                                     |                         |       | 10         |     | kohm |

| Input Capacitor                                     |                         |       | 50         |     | pF   |

| ADC Digital Filter                                  |                         |       |            |     |      |

| Passband                                            |                         |       | 0.4        |     | fs   |

| Passband Ripple                                     |                         |       | +/- 0.05   |     | dB   |

| Stopband                                            |                         | 0.6   |            |     | fs   |

| Stopband Attenuation                                | >0.583 fs               |       | -78        |     | dB   |

| Line output                                         |                         |       |            |     |      |

| THD (Total Harmonic Distortion)                     | (Note 3)                |       | -80        | -70 | dB   |

| Dynamic Range<br>(-60dB input, A-weighted)          | (Note 4)                |       | 98         |     | dB   |

| S/N (A-weighted)                                    | (Note 5)                | 85    | 98         |     | dB   |

| Channel Separation                                  | (Note 6)                |       | 100        |     | dB   |

| Channel Matching                                    |                         |       | 0.2        |     | dB   |

| Full Scale Output Voltage                           |                         |       | 0.875*AVDD |     | Vpp  |

| Load Resistance                                     |                         |       | 10         |     | kohm |

| Load Capacitor                                      |                         |       |            | 50  | pF   |

| DAC Digital Filter                                  |                         |       |            |     | •    |

| Passband                                            |                         |       | 0.444      |     | fs   |

| Passband Ripple                                     |                         |       | +/- 0.05   |     | dB   |

| Stopband                                            |                         | 0.556 |            |     | fs   |

| Stopband Attenuation                                | >0.583 fs               | -60   |            |     | dB   |

Note:

1. Does not include codec (AVDD\_CODEC), PLL analog and ROSC (ring oscillator) analog power

2. Not recommended.

3. THD is the Distortion/Signal ratio calculated with rms values.

4. Dynamic range is a measure of the difference between the highest and lowest portions of a signal. Normally a THD + N measurement at 60 dB is below full-scale. The measured signal is then corrected by adding 60dB (e.g. THD + N @ -60dB = -32 dB, DR = 92 dB).

- 5. SNR is a measure of the difference between the full-scale output and the output with no signal applied.

- 6. Channel Separation also is known as crosstalk, which measures how good one channel is isolated from another channel. Normally it is done by sending a full-scale signal to one channel and measuring the other.

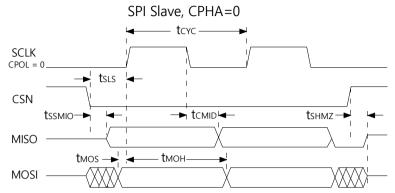

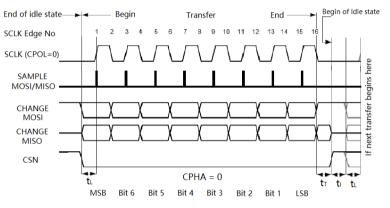

# 3.2 Slave SPI Timing

# Figure 2 Slave SPI Timing

| SPI Slave Timings  |                                | Notes | Min.                | Тур. | Max. | Units |

|--------------------|--------------------------------|-------|---------------------|------|------|-------|

| t <sub>CYC</sub>   | SCLK cycle time                |       | 500                 | -    | -    | ns    |

| t <sub>ssmio</sub> | CSN to MISO output             |       | 3.8                 | -    | 12   | ns    |

| t <sub>sls</sub>   | CSN to SCLK setup              |       | t <sub>cyc</sub> /2 | -    | -    | ns    |

| t <sub>CMID</sub>  | SCLK to MISO delay             |       | 3                   |      | 12   | ns    |

| t <sub>MOS</sub>   | MOSI to SCLK setup             |       | 4                   | -    | -    | ns    |

| t <sub>мон</sub>   | MOSI to SCLK hold              |       | 1.3                 | -    | -    | ns    |

| t <sub>shmz</sub>  | CSN to MOSI and MISO tri-state |       | 3.8                 | 10   | 12   | ns    |

# 3.3 I2S Timing

#### 3.3.1 I2S Timing in Slave Mode

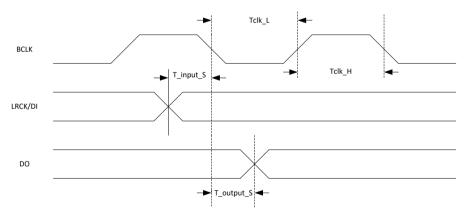

# Figure 3 I2S Timing in Slave Mode

| Parameter  | Description           | Min. | Тур. | Max. | Units |

|------------|-----------------------|------|------|------|-------|

| Tclk_L     | BLCK low level        | 68.5 | -    | -    | ns    |

| Tclk_H     | BLCK high level       | 68.5 | -    | -    | ns    |

| T_input_S  | LRCK/DI to BCLK setup | -    | -    | 26   | ns    |

| T_output_S | BCLK to DO setup      | -    | -    | 27   | ns    |

#### 3.3.2 I2S Timing in Master Mode

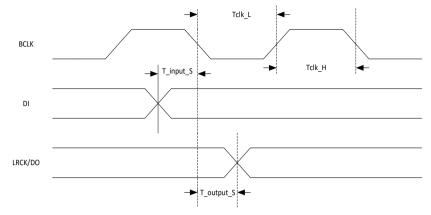

# Figure 4 I2S Timing in Master Mode

| Parameter  | Description           | Min. | Тур. | Max. | Units |

|------------|-----------------------|------|------|------|-------|

| Tclk_L     | BLCK low level        | 40   | -    | -    | ns    |

| Tclk_H     | BLCK high level       | 40   | -    | -    | ns    |

| T_input_S  | DI to BCLK setup      | -    | -    | 16   | ns    |

| T_output_S | BCLK to DO/LRCK setup | -    | -    | 10   | ns    |

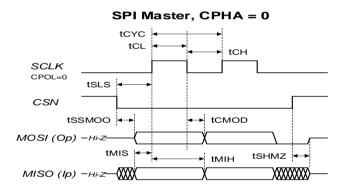

# 3.4 Master SPI Timing

= Level undefined or not important

# Figure 5 Master SPI Timing

| SPI Mas           | ter Timings                                  | Min.                | Тур. | Max. | Units |

|-------------------|----------------------------------------------|---------------------|------|------|-------|

| t <sub>CYC</sub>  | SCLK cycle time                              | 40                  | -    | -    | ns    |

| t <sub>CL</sub>   | SCLK low time                                | -                   | 20   | -    | ns    |

| t <sub>CH</sub>   | SSP CLK high time                            | -                   | 20   | -    | ns    |

| t <sub>sls</sub>  | CSN to SSP_CLK setup                         | t <sub>cyc</sub> /2 | -    | -    | ns    |

| t <sub>CMOD</sub> | SCLK to MOSI delay                           | -4                  | 0    | 11   | ns    |

| t <sub>MIS</sub>  | MISO to SCLK setup                           | -                   | -    | 7    | ns    |

| t <sub>MIH</sub>  | MISO to SCLK hold                            | 3                   | -    | -    | ns    |

| t <sub>shmz</sub> | CSN to MOSI and MISO tristate <sup>(2)</sup> | -                   | -    | 200  | ns    |

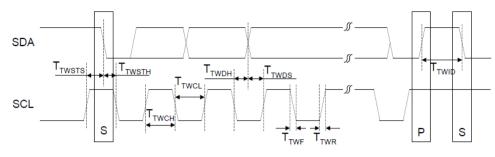

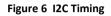

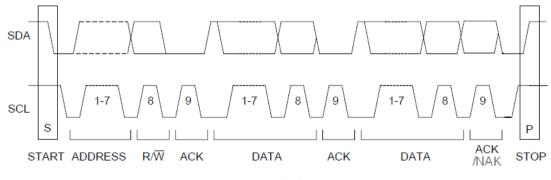

# 3.5 I2C Timing

| Parameter                               | Symbol | Min | Max | Unit |

|-----------------------------------------|--------|-----|-----|------|

| SCL Clock Frequency                     | Fscl   |     | 100 | kHz  |

| Bus Free Time Between Transmissions     | TTWID  | 4.7 |     | us   |

| Start Condition Hold Time               | TTWSTH | 4.0 |     | us   |

| Clock Low time                          | TTWCL  | 4.0 |     | us   |

| Clock High Time                         | TTWCH  | 4.0 |     | us   |

| Setup Time for Repeated Start Condition | TTWSTS | 4.7 |     | us   |

| SDA Hold Time from SCL Falling          | TTWDH  | 0.1 |     | us   |

| SDA Setup time to SCL Rising            | TTWDS  | 100 |     | ns   |

| Rise Time of SCL                        | TTWR   |     | 25  | us   |

| Fall Time SCL                           | TTWF   |     | 25  | ns   |

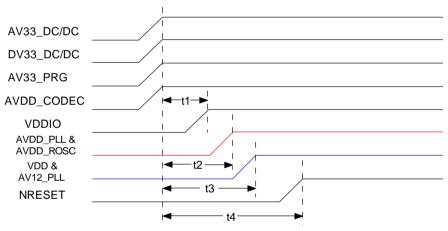

# 3.6 Reset and Power-on Timing

#### Note:

- 1. AVDD\_PLL and AVDD\_ROSC in red line derives from AV33\_PRG by on-chip LDO.

- 2. VDD and AV12\_PLL in blue line derives from AV33\_DC/DC and DV33\_DC/DC by on-chip DC/DC.

- 3. NRESET should be released after VDD and AV12\_PLL is powered up.

| Reference | Description                | Min | Max | Unit |

|-----------|----------------------------|-----|-----|------|

| t1        | Valid DSP to Valid I/O     | 0   |     | us   |

| t2        | On-chip LDO startup time   |     | 280 | us   |

| t3        | On-chip DC/DC startup time |     | 750 | us   |

| t4        | NRESET release time        | 1.5 |     | ms   |

# 3.7 Interrupt Timing

External interrupts INTO and NMI are edge-triggered and asynchronous. A sampled LOW-to-HIGH transition constitutes a valid interrupt. Figure 8 shows external interrupt timing relative to the processor clock. The table below describes the timing relationships in Figure 8.

#### Figure 8 Interrupt Timing

| Reference | Description                | Min | Max | Unit |

|-----------|----------------------------|-----|-----|------|

| t1        | Interrupt HIGH Pulse Width | 1   | —   | Т    |

| t2        | Interrupt LOW Pulse Width  | 1   | —   | Т    |

Note: T = processor clock period.

| Pin<br>No | Pin Name   | Pin<br>Type | Pin Description                           |

|-----------|------------|-------------|-------------------------------------------|

| 1         | DEMOD_IN   | AI          | Demod input                               |

| 2         | RINP       | AI          | Right ADC differential input positive     |

| 3         | RINN       | AI          | Right ADC differential input negative     |

| 4         | LINN       | AI          | Left ADC differential input negative      |

| 5         | LINP       | AI          | Left ADC differential input positive      |

| 6         | MIC IN     | AI          | Microphone input                          |

| 7         | BEEP_IN    | AI          | Beep tone input                           |

| 8         | VREFH      | Р           | Codec analog reference positive           |

| 9         | AVDD CODEC | Р           | Codec analog power supply                 |

| 10        | AVSS CODEC | Р           | Codec analog ground                       |

| 11        | VREFL      | P           | Codec analog reference negative           |

| 12        | ROUT1      | AO          | Right DAC line output 1                   |

| 13        | ROUT2      | AO          | Right DAC line output 2                   |

| 14        | VMID       | P           | Mid-rail reference decoupling point       |

| 15        | LOUT2      | AO          | Left DAC line output 2                    |

| 16        | LOUT1      | AO          | Left DAC line output 2                    |

| 17        | AV33 PRG   | P           | •                                         |

|           | _          |             | On chip LDO input, 3.3V typical           |

| 18        | VOUT_PRG   | P           | On chip LDO output, 3.0V typical          |

| 19        | AVSS_PRG   | P           | Analog ground of LDO                      |

| 20        | DV33_DC/DC | P           | On chip DC/DC analog power supply         |

| 21        | DVSS_DC/DC | P           | On chip DC/DC analog ground               |

| 22        | VOUT_FB    | Р           | On chip DC/DC Output Voltage Feedback Pin |

| 23        | AV33_DC/DC | Р           | On chip DC/DC power input                 |

| 24        | LX_DC/DC   | P           | On chip DC/DC Output Switch Node          |

| 25        | AVSS_DC/DC | P           | On chip DC/DC power ground                |

| 26        | VDD        | Р           | Core power supply                         |

| 27        | VDDIO      | Р           | IO power supply                           |

| 28        | NC         | -           | No connection                             |

| 29        | NC         | -           | No connection                             |

| 30        | NC         | -           | No connection                             |

| 31        | NC         | -           | No connection                             |

| 32        | NC         | -           | No connection                             |

| 33        | VDD        | Р           | Core power supply                         |

|           |            |             | I2S bit clock                             |

| 34        | I2S BCLK   | I/O         | Slave: input                              |

|           | _          |             | Master: output                            |

|           |            |             | I2S frame clock                           |

| 35        | I2S LRCK   | I/O         | Slave: input                              |

|           | _          |             | Master: output                            |

|           |            |             | I2S main clock                            |

| 36        | I2S MCLK   | 0           | Slave: No use                             |

|           | _          |             | Master: output                            |

| 37        | I2S_DI     |             | I2S serial data input                     |

| 38        | 12S_DO     | 0           | I2S serial data output                    |

| 39        | VDDIO      | P           | IO power supply                           |

| 40        | I2C_SCL    | 0           | I2C serial clock output                   |

| 41        | I2C SDA    | I/O         | I2C serial data output and input          |

| •-        | 0_00/      | 1/0         | I2S RX bit clock                          |

| 42        | I2S_R_BCLK | I/O         | Slave: input                              |

|           |            |             | Master: output                            |

| 43        | I2S_R_DI   | I           | I2S RX serial data input                  |

| 44        | TEST       | I           | Connect to ground                         |

| 45        | VDD        | Р           | Core power supply                         |

|           |            |             | I2S RX frame clock                        |

| 46        | I2S_R_LRCK | I/O         | Slave: input                              |

|           |            |             | Master: output                            |

| 47   | I2S T DO   | 0          | I2S TX serial data output                        |

|------|------------|------------|--------------------------------------------------|

|      |            |            | I2S TX bit clock                                 |

| 48   | I2S T BCLK | I/O        | Slave: input                                     |

| 40   |            | 1/0        | Master: output                                   |

|      |            |            | I2S TX frame clock                               |

| 49   | I2S T LRCK | 1/0        | Slave: input                                     |

| 75   |            | 1/0        | Master: output                                   |

| 50   | VDDIO      | Р          | IO power supply                                  |

| 51   | SPI MOSI   | Г<br>О     | SPI master MOSI                                  |

| 52   | SPI_WOSI   | 0          | SPI master serial clock output                   |

| 53   | -          | U          | SPI master MISO                                  |

|      | SPI_MISO   | P          |                                                  |

| 54   | VDDIO      | P<br>P     | IO power supply                                  |

| 55   | VDD        |            | Core power supply                                |

| 56   | SPI_CSN0   | 0          | SPI master chip select 0 output                  |

| 57   | SPI_CSN1   | 0          | SPI master chip select 1 output                  |

| 58   | SPI_S_CSN  |            | SPI slave chip select input from host processor  |

| 59   | SPI_S_MOSI |            | SPI slave MOSI                                   |

| 60   | SPI_S_MISO | 0          | SPI slave MISO                                   |

| 61   | SPI_S_SCLK |            | SPI slave clock input from host processor        |

| 62   | VDDIO      | Р          | IO power supply                                  |

| 63   | HOBIB      | 0          | SPI slave data output status                     |

| 64   | INTO       | I          | External Hardware Interrupt                      |

| 65   | NMI        | <u> </u>   | Non-maskable Interrupt                           |

| 66   | NRESET     |            | Chip hardware reset                              |

| 67   | AVDD_ROSC  | Р          | ROSC analog power supply                         |

| 68   | AVSS_ROSC  | P          | ROSC analog ground                               |

| 69   | AVDD_PLL   | P          | PLL analog power supply                          |

| 70   | AVSS_PLL   | Р          | PLL analog ground                                |

| 71   | AV12_PLL   | Р          | PLL 1.2V power supply                            |

| 72   | XIN        | AI         | XIN or external clock generator input            |

| 73   | XOUT       | AO         | XOUT                                             |

| 74   | VDDIO_OSC  | Р          | IO power supply for internal oscillator          |

| 75   | VDDIO      | Р          | IO power supply                                  |

| 76   | GPIO0      | I/O        | Programable IO0 (See note is section 5.1.1)      |

| 77   | VDD        | P          | Core power supply                                |

| 78   | GPIO1      | I/O        | Programable IO1                                  |

|      |            |            | Programable IO2, please see section 6.5 for more |

| 79   | GPIO2      | 1/0        | details                                          |

|      |            |            | Programable IO3, please see section 6.5 for more |

| 80   | GPIO3      | 1/0        | details                                          |

|      |            |            | Programable IO4, please see section 6.5 for more |

| 81   | GPIO4      | I/O        | details                                          |

|      |            |            | Programable IO5, please see section 6.5 for more |

| 82   | GPIO5      | I/O        | details                                          |

| 83   | GPIO6      | I/O        | Programable IO6 (See section 5.1.8)              |

| 84   | GPIO7      | I/O        | Programable IO7 (See section 5.1.8)              |

| 85   | UART_TXD   | 0          | UART transmit                                    |

| 86   | UART_RXD   | U          | UART receive                                     |

| 87   | NC         | -          | No connection                                    |

| 88   | MICBIAS    | AO         |                                                  |

|      |            | P          | Codec Microphone bias output                     |

| epad | VSSD       | ۲ <u>۲</u> | Digital ground                                   |

#### Note:

1. AO = analog output

2. Al = analog input

3. I/O = bidirectional

4. I = digital input

5. O = digital output

6. P = power or ground

# 5 Component and PCB Recommendations

# 5.1 Recommended External Components

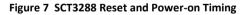

# 5.1.1 Xtal Interface

The clock circuit can operate with either a Xtal or external frequency oscillator. If using a Xtal, its frequency range should be 12.8 MHz to 26 MHz. If using an external frequency oscillator, its frequency range should be from 12.8 MHz to 40 MHz. Please refer to section 6.1.1 for more details about source clock. Figure 9 shows the different application for Xtal and external frequency oscillator.

Figure 9 Xtal Interface

Notes:

If the operating frequency is between 12.8 MHz to 25 MHz, the GPIO0 must be pulled high by an external 10k resistor or the host processor during reset or power up. For other operating frequencies, GPIO0 should be pulled low or left floating during reset or power up. After the reset or power up, GPIO0 can be used as a normal programmable I/O.

$C_{L1}$  and  $C_{L2}$  are the load capacitances. It is the effective load capacitance for which the crystal is tuned. In the above oscillator circuit, the load capacitance can be calculated by  $C_{L1}*C_{L2}$  /  $(C_{L1}+C_{L2})$ . This value can be found in the crystal manufacturer's user manual. The recommended value is 12 pF.

The tracks between the Xtal and the device pins should be as short as possible to achieve maximum stability and best start up performance. It is also important to achieve a low impedance connection between the Xtal capacitors and the ground plane.

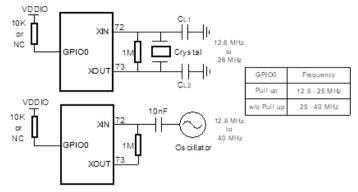

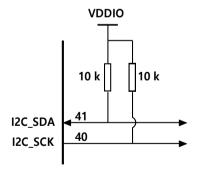

#### 5.1.2 I2C Interface

Figure 10 I2C Interface

Note:

10 k pull up resistors are necessary if the I2C is used.

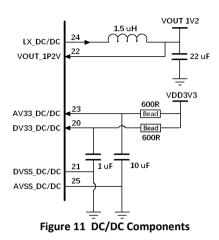

#### 5.1.3 DC/DC Components

#### Notes:

The inductor value affects its peak-to-peak ripple current, the output voltage ripple and the efficiency. For SCT3288 internal DC/DC, a  $1.5\mu$ H inductor with DCR smaller than  $30m\Omega$  and ISAT larger than 600mA is recommended.

The COUT will influence the output voltage ripple, load response, and the system stability. A  $22\mu$ F with low-ESR capacitor such as ceramic, it is recommended for COUT. The ESR of COUT shall NOT be larger than  $10m\Omega$ . The COUT should be connected to the inductor as close as possible. Connect the GND side of the capacitors directly to the ground plane of the board.

To prevent large voltage transients, a  $10\mu$ F low-ESR input capacitor CPIN is required to be placed between AV33\_DC/DC and AVSS\_DC/DC, and a 1.0uF low-ESR input capacitor CAIN is also required to be placed between DV33\_DC/DC and DVSS\_DC/DC. All the capacitors should be placed next to the corresponding pins as close as possible. Connect the GND side of all the capacitors directly to the ground plane of the board.

The input supply trace to its decoupling capacitors should be as short as possible. The decoupling capacitors provide the AC current to the internal power MOSFET and its driver. It is important to minimise the parasitic inductance from the capacitors to the chip pins. Minimise the switching power traces connecting LX\_DC/DC to the inductor to reduce radiated EMI and parasitic coupling. Keep sensitive nodes such as feedback pins away from or shielded from the large voltage swings on the switch node. Minimise the length of the connection between the step-down converter inductor and the output capacitor.

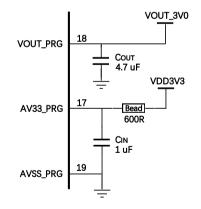

#### 5.1.4 LDO Components

Figure 12 LDO Components

Note:

A 4.7uF low-ESR capacitor, like ceramic capacitor, is recommended for COUT. It should be placed next to VOUT\_PRG pin as close as possible.

A 1uF low-ESR capacitor CIN is also recommended to place between AV33\_PRG and AVSS\_PRG. It also needs to be placed closely to the AV33\_PRG pin.

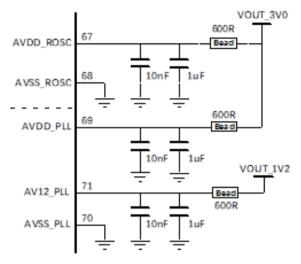

### 5.1.5 PLL and ROSC

Figure 13 PLL and ROSC Power Supply Decoupling

#### Note:

VOUT\_3V0 comes from the chip internal LDO output. VOUT\_1V2 comes from internal DC/DC output. Low-ESR ceramic capacitor 1uF and 10nF should be added between each power pin and ground. As a minimum the 10nF should be placed as close as possible to the power pin. Ferrite bead should be used to separate the analog power domain from digital power domain.

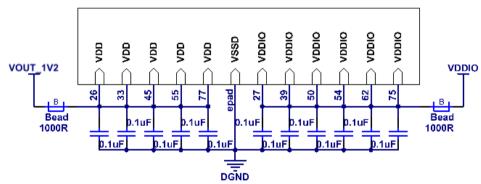

# 5.1.6 Digital Power and Decoupling

Figure 14 Digital Power and Decoupling

Note:

Core power VDD is supplied from the devices internal DC/DC converter, VDD digital supply pins should be connected to the DC/DC output through a ferrite bead. A decoupling capacitor should be placed for each VDD pin.

VDDIO supplies can be 1.8V to 3.6V and should keep same as the host processor I/O voltage. A decoupling capacitor should be placed for each VDD pin.

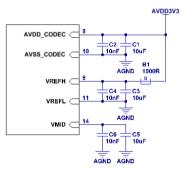

# 5.1.7 Codec

# 5.1.7.1 Power and Reference

Figure 15 Codec Power and Reference

Note:

Codec should be powered by a dedicated power source to achieve the best performance. The decoupling capacitors should be placed as close as possible to the pins. A ferrite bead is also required to separate analog power from the reference power.

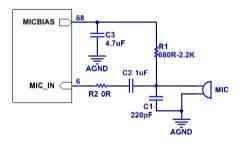

#### 5.1.7.2 Microphone Input

Figure 16 Microphone Input

Note:

The recommended component values are C1=220pF, C2=1uF, R1=680ohm~2.2kohm, R2=0ohm, also refer to the application circuit in the Microphone specification. MICBIAS decoupling capacitor is 4.7uF. The microphone also could be biased by an external power source.

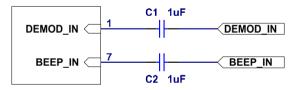

#### 5.1.7.3 Demod and Beep Input

Figure 17 Demod and Beep Input

Note:

The FM demodulated signal should be AC coupled to DEMOD\_IN. 1uF is recommended to achieve the good frequency response and the small transient variable DC.

Beep input also needs a 1uF coupling capacitor.

#### 5.1.7.4 Differential Line Input

Figure 19 Differential Line Input AC Coupling

Note:

The I/Q signal should be DC coupled to differential line inputs when SCT3288 is used with SCT3811 together. No extra components are required as shown in Figure 18.

It also supports AC coupling, the 1uF coupling capacitor is required as Figure 19.

#### 5.1.7.5 Line Output

Note:

The audio signal is output by LOUT1 and 1uF coupling capacitor is recommended.

The modulation signal is output by LOUT2 and ROUT2. Addition of the RC formed low-pass filter is recommended for both output paths. If two-point modulation is used, it is recommended that LOUT2 is AC coupled to VCO by C3 and ROUT2 should be DC coupled (C4 = 0R) to VCTCXO in order to control the carrier frequency error. ROUT2 could also be AC coupled to VCTCXO, and the carrier frequency error controlled directly by the user, for example use a DAC on the main MCU. The R, C, C3 and C4 value should be determined by design.

#### 5.1.8 GPIO Pins

All GPIO pins are configured as inputs with an internal pull-down circuit by default while the chip powering up. Please note that the GPIOO needs to be pulled up by 10k resistor if the input clock frequency is lower than 25MHz. Please refer to Figure 9 for more details. After a reset or power up, GPIOO can be used as a normal programmable I/O.

Please make sure that the GPIO6 has no pull-up resistor and is not pulled high by the host processor while the SCT3288 is resetting or powering up. After the reset or power up, GPIO6 can be used as normal programmable I/O.

# 6 Hardware Description

#### 6.1 Clock Generation Unit

# 6.1.1 Xtal Frequency

The SCT3288 is designed to work with a Xtal, or an external frequency oscillator within the ranges from 12.8 MHz to 40 MHz. If using a Xtal, its frequency range should be 12.8 MHz to 26 MHz. If using an external frequency oscillator, its frequency range can be 12.8 MHz to 40 MHz.

Please make sure the GPIO 0 is pulled up by a resistor when the chip is powering up or resetting if the frequency is between 12.8 MHz to 25 MHz. If the input frequency is between 26 MHz to 40MHz, this pull-up resistor is not needed. Please refer to Figure 9 for more details.

To comply with a DMR/dPMR requirement of 2 ppm on baseband timing, the clock input of SCT3288 should also be within 2 ppm. However, when communicating with another DMR/dPMR terminal also using SCT3288, a maximum tolerance of 20 ppm is acceptable. However, if DMR TDMA direct mode is to be supported, the clock input requirement is 0.5 ppm, per TS 102 361.

A 19.2 MHz or 38.4 MHz TCXO / VCTCXO is strongly recommended as the input clock to achieve the best performance.

# 6.1.2 PLL

SCT3288 integrates a built-in PLL to generate a high frequency processor clock from a slower off-chip clock source. It supports both integer mode and fraction mode. The highest output frequency can be 200 MHz. The PLL is supplied from an on-chip LDO and DC/DC converter. Please refer to Figure 13 for more details.

The PLL output frequency has been configured to 153.6 MHz (the reference clock can be 19.2 MHz or 38.4 MHz) by default when SCT3288 is booting up, and then SCT3288 will give a response to host MCU when PLL lock is achieved. The PLL will be powered down during the sleep mode and the system clock is switched to ROSC. All the control procedure is done by SCT3288 automatically according to the system work mode, so no manual intervention is required.

#### 6.1.3 ROSC

SCT3288 integrates a ring oscillator to generate a 1MHz clock as the default system clock when the chip starts up. It can also be used when the SCT3288 enters sleep mode to maintain some external hardware interrupts, which are used to wake the chip from sleep mode.

The ring oscillator's power supply comes from the on-chip LDO and consumes less than 20uA. Please refer to Figure 13 for more details about the ring oscillator's external components.

### 6.2 Power Supply

#### 6.2.1 DC/DC converter

To maximise power efficiency the SCT3288 has an on-chip low power synchronous step-down DC/DC converter, which converts 1.7 - 3.6V input power to a 1.2V output for the core power supply. Using the DC/DC converter allows the SCT3288 to be operated from a single supply voltage.

The DC/DC converter uses a current-mode, fixed frequency PWM control for optimal stability and transient response, also saving devices. To ensure the high efficiency at light load it will reduce the switching frequency and enter pulse-skip mode automatically. The DC/DC converter provides a maximum current of 300mA. For the DC/DC converter's external components please refer to **Figure 11**. Sharing the DC/DC converter output with other devices is not recommended.

### 6.2.2 LDO regulator

SCT3288 has an on-chip LDO regulator which provides a suitable power supply for all the analog parts of chip (except the codec which has independent positive and negative supply pins) such as PLL and ROSC from an external high voltage power supply. It is very convenient for a user to supply the chip with only one voltage although the whole chip needs two kinds of different voltages.

It generates 3V from 3.3V to 3.6V power supply. And it provides a maximum current of 200mA. For its external components please refer to Figure 12.

#### 6.2.3 IO Power Supply

SCT3288 has the dedicated IO power supply VDDIO which can operate from 1.8V to 3.6V. The VDDIO supply should be kept the same as users' host processor IO voltage. It also could be powered by on-chip LDO if 3.0V is chosen by user as IO voltage.

#### 6.3 Serial Interfaces

# 6.3.1 Slave SPI

A slave SPI is used for command, status and data transfers between the SCT3288 and the host processor. All the information has been packaged and defined in a separate document "SCT3288 Packet Interface". Pin 63 (HOBIB) will go high to notify the host processor when a change in status has occurred or something needs to be reported from the SCT3288 and the processor should read the SCT3288 through the slave SPI and respond accordingly.

MOSI is generated by the master on the falling edge of SCLK and is sampled by the slave (i.e. this SPI interface) on the rising edge of SCLK. MISO is generated by the slave on the falling edge of SCLK. The CSN line must be held low during a data transfer and kept high between transfers. MISO is high impedance when CSN is high. The number of data bytes is dependent on the length of command. The most significant bit is sent first. For detailed timings see section 3.2. This slave SPI operation is shown in Figure 21.

$t_L$  = Minimum leading time before the first SCLK edge

$t_T$  = Minimum trailing time after the last SCLK edge

t<sub>I</sub> = Minimum idle time between transfers (Minimum CSN high time)

Minimum 1/2 SCLK for trati and t

#### Figure 21 Slave SPI Operation

The master SPI has been configured as Table 2 when SCT3288 is booting up from boot ROM. The Data rate is limited to 2Mbps. Please note that this slave SPI works with HOBIB signal together. The HOBIB usually stays low, the host processor should immediately read SCT3288 when the HOBIB goes high, then keep reading until the HOBIB returns to low again.

#### Table 1 Slave SPI Default Setting

| Item              | Setting                                          |

|-------------------|--------------------------------------------------|

| Data Rate         | 2 Mbps Max                                       |

| Operation<br>mode | Mode 0, CPOL=0, CPHA=0                           |

| MSB or LSB        | MSB first                                        |

| SCLK state        | Sample at rising edge, in idle state SCLK is low |

| Width             | 16 bits                                          |

The default setting of slave SPI is shown as Table 1. This slave SPI interface is compatible with most common processor serial interfaces and may also be easily implemented with general purpose processor I/O pins controlled by a simple software routine.

#### 6.3.2 Master SPI

SCT3288 has a master SPI interface. This SPI interface is used for internal functionality while SCT3288 is being powered up or reset and is not available for use during power up and firmware loading.

After the firmware loading, the master SPI interface can be used to control external SPI device such as the SCT3811 and CMX940. The Master SPI interface has two independent chip selector signals for this control purpose. Its main features are as below:

- SPI master is configured with a 32byte FIFO

- Support DMA mode transaction

- Support four SPI operation modes

- Support full duplex operation

- Programmable MSB or LSB

The master SPI has been configured as Table 2 when SCT3288 is booting up from boot ROM. Its operation is the same as slave SPI Interface except it is the master side.

| Item              | Setting                                          |

|-------------------|--------------------------------------------------|

| Data Rate         | 4M bps                                           |

| Operation<br>mode | Mode 0, CPOL=0, CPHA=0                           |

| MSB or LSB        | MSB first                                        |

| SCLK state        | Sample at rising edge, in idle state SCLK is low |

| Width             | 8 bits                                           |

#### Table 2 Master SPI Default Settings

User can use this master SPI to control an external SPI device by the command of SPI\_OPERATION which is defined in a separate document "SCT3288 packet interface". For example: TBD

# 6.3.3 I2C

SCT3288 includes one standard I2C master interface to communicate with other external I2C peripherals. The I2C interface can support standard mode (100 kbps), fast mode (400 kbps), and high-speed mode (3.4 Mbps). It supports 7-bit or 10-bit addressing.

The SCT3288 preloaded firmware has configured the I2C as Table 3. Please note that the I2C is disabled by default to save the power consumption.

| Item         | Setting                               |

|--------------|---------------------------------------|

| Data rate    | Standard mode 100kbps                 |

| Address mode | 7-bit                                 |

| Address      | by command                            |

|              | · · · · · · · · · · · · · · · · · · · |

I2C interface is a bi-directional serial bus that uses a serial data line (SDA) and a serial clock line (SCL) for data transfer. The timing diagram for data transfer of this interface is given in Figure 22. Data are transmitted synchronously to SCL clock on the SDA line on a byte-by-byte basis. Each bit in a byte is sampled during SCL high with MSB bit being transmitted firstly. Each transferred byte is followed by an acknowledge bit from receiver to pull the SDA low. The transfer rate of this interface can be 100 kbps.

SCT3288 as the master initiates the transmission by sending a "start" signal, which is defined as a high-to-low transition at SDA while SCL is high. The first byte transferred is the slave address. It is a seven-bit chip address followed by a RW bit. The RW bit indicates the slave data transfer direction. Once an acknowledge bit is received, the data transfer starts to proceed on a byte-by-byte basis in the direction specified by the RW bit. The master can terminate the communication by generating a "stop" signal, which is defined as a low-to-high transition at SDA while SCL is high.

User can use this I2C to control other external I2C devices by the command of I2C\_OPERATION which is defined in a separate document "SCT3288 packet interface". For example: TBD

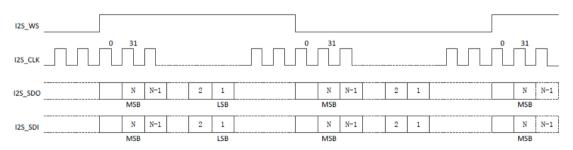

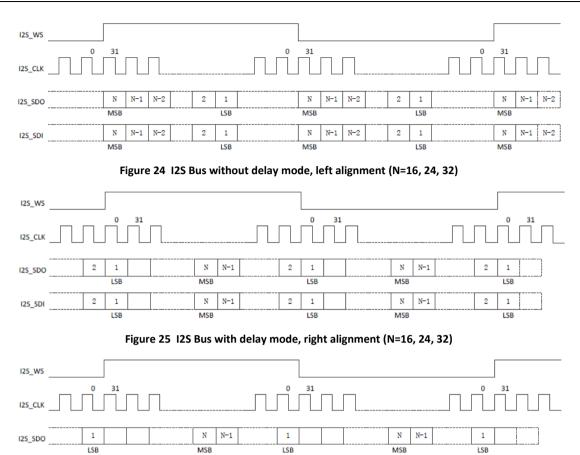

#### 6.3.4 I2S

SCT3288 has three I2S interfaces to transfer data with an external digital audio system or a transceiver with a digital I/Q interface: one operates in full duplex mode, one in Tx only mode and one in Rx only mode.

#### 6.3.4.1 Features

- Master or slave mode of operation

- The data width for each channel is 16 bits, 24 bits or 32 bits

- LRCK pulse width is always 32 times width of BCLK in master mode

- Master side LRCK pulse width should equal or bigger than slave side in slave mode

- Supports audio stereo data or audio mono data transmit and receive

- Supports consecutive or non-consecutive data transmit and receive

- Supports left or right alignment

- Only one channel is needed, and the selection of left or right channel can be configurable when transmit/receive audio mono data

- Serial data is transmitted in two's complement with the MSB first

- The latch for SD and LRCK can be defined at the rising or falling edge of BCLK

- The format can be switched between delayed (Philips) and non-delayed (non-Philips)

- Interrupt trigger or sentinel available when data in FIFO are empty or full

- The size of embedded FIFO is 32x16 bit, build with internal-register, including TX FIFO and RX FIFO

#### 6.3.4.2 I2S Operation

The I2S interface consists of a Left/Right clock called LRCK which has a frequency equal to the sample rate and is common to both input and output audio signal paths. The LRCK low and high levels indicate if the audio data reflects the left or right channel.

The I2S Interface may be configured to operate as either master or slave. If the SCT3288 I2S is the master, the LRCK, MCLK and BCLK pins are driven by the SCT3288 as outputs. MCLK output frequency must be 256xLRCK. If it is the slave, the LRCK and BCLK pins are configured as inputs and both pins should be driven by the external device. And the MCLK output will be disabled. The I2S Interface transmits serial audio data to the external device on the SDO output pin and receives serial audio data from the external device on the SDI input pin. I2S Interface may be configured to operate in several modes and supports both left and right alignment which are shown in Figure 23 to Figure 26. Please note that it only supports left alignment when it works in slave mode.

Figure 23 I2S Bus with delay mode, left alignment (N=16, 24, 32)

LSB Figure 26 I2S Bus without delay mode, right alignment (N=16, 24, 32)

1

#### 6.3.5 UART

I2S\_SDI

SCT3288 includes a programmable Universal Asynchronous Receiver/Transmitter (UART). The UART can be used to communicate with an external Host. Its main feature are as below:

N N-1

MSB

1

LSB

Transmit and receive FIFO depths is 16 •

N

MSB

N-1

1

LSB

- Programmable character properties, such as number of data bits per character (5-8), optional parity bit (odd or • even) and number of stop bits (1, 1.5 or 2)

- Programmable serial data baud rate

The SCT3288 preloaded firmware has configured the UART as Table 4. Please note that the UART is disabled by default.

| Item           | Setting |

|----------------|---------|

| Data<br>Length | 8bits   |

| Stop<br>bit    | 1 bit   |

| Parity         | None    |

| Baud<br>rate   | 38400   |

#### Table 4 UART Default Setting

#### 6.4 System Interface

This section describes the external system interface signals.

| Signal<br>Name | Input /<br>Output | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTO           | Input             | External Hardware Interrupts. The INTO signal provides an external hardware interrupt source to SCT3288. SCT3288 takes an interrupt when INTO is asserted. INTO is edge-triggered; a sampled LOW-to-HIGH transition defines one occurrence of the interrupt. INTO must be asserted for at least one processor clock period to guarantee the interrupt request is taken. INTO is always sampled on a rising edge of the processor clock, and transitions are ignored during reset. INTO is used to wake up SCT3288 when it is in SLEEP mode. If unused, INTO must be tied LOW. |

| NMI            | Input             | Non-maskable Interrupt. NMI is an external hardware interrupt that has the highest priority of all the SCT3288 interrupts. NMI is sampled on the rising edge of the processor clock, and must be asserted for a minimum of one processor clock period. A sampled LOW-to-HIGH transition asserts the NMI interrupt request. The processor branches to address 0. NMI has the same effect of a reset, without code downloading from the flash. If unused, this signal must be tied LOW.                                                                                         |

| NRESET         | Input             | Device Reset.<br>This signal starts SCT3288 reset process. After the initial power-up sequence,<br>NRESET must be asserted (LOW) for a minimum of five processor clock cycles to<br>guarantee proper reset of the device. The LOW-to-HIGH transition of this signal<br>causes the chip boot up from the internal boot ROM.                                                                                                                                                                                                                                                    |

# 6.5 Programmable I/O

The SCT3288 provides eight programmable I/O signals, GPIO[7:0], for general-purpose hardware interfacing. Each of these signals can be individually configured as input or output. The memory-mapped PIO register controls the behaviour of these signals.

The SCT3288 preloaded firmware has assigned the GPIO with the following functions:

| GPIO Number | Input /<br>Output | Descriptions                                                                                                                                                                                         |

|-------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO 0      |                   |                                                                                                                                                                                                      |

| GPIO 1      |                   |                                                                                                                                                                                                      |

| GPIO 2      | output            | Slave SPI handshake with host MCU<br>It uses a rising edge to inform the host MCU<br>that SCT3288 has data that needs to be<br>reported. Then HOBIB goes high to indicate<br>that the data is ready. |

| GPIO 3      | output            | DMR mode RF Timing port                                                                                                                                                                              |

| GPIO 4      | output            | SCT3811 High/Low injection indication<br>(available on SCT3288xxM only)<br>Low: Switch to Low injection<br>High: Switch to High injection                                                            |

| GPIO 5      | output            | SCT3288 work mode indication<br>Low: Normal Mode<br>High: Low Power Mode                                                                                                                             |

| GPIO 6      |                   |                                                                                                                                                                                                      |

| GPIO 7      |                   |                                                                                                                                                                                                      |

#### Table 6 Programmable I/O Signals

# 6.6 Codec

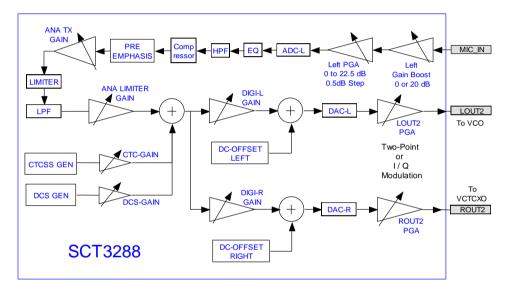

SCT3288 integrates a codec which has 2-channel 24bit sigma-delta ADC with two single-ended inputs and two differential input pairs and 2-channel 24bit sigma-delta DAC with two pairs line output. The codec also has an audio PLL to support a wide range of sample rates from 8 kHz to 96 kHz.

#### 6.6.1 Features

- ADC

- --THDN: -82dB

<sup>@</sup> 2023 Sicomm Technologies Ltd

- --Dynamic Range, SNR: 96dB

- DAC Line Output

- --THDN: -80dB

- --Dynamic Range, SNR: 98dB

- Stereo Line Input and Mono Microphone Input

- Internal 24-Bit Fractional PLL as the Audio CODEC Master Clock Generator

- Sampling Rates 8 kHz to 96 kHz

- Input overflow detection

- Stereo/Mono Mode

- Power Supply

- --Digital Core: 1.2V

- --Analog: 2.25V ~ 3.6V, 3.3V typical

#### 6.6.2 Codec Block Diagram

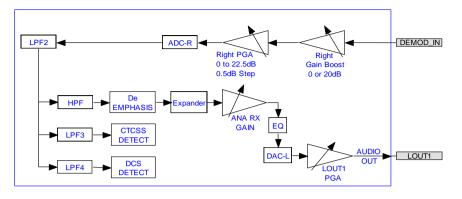

Figure 27 Codec Block Diagram

#### 6.6.3 Codec Description

#### 6.6.3.1 Sigma-Delta ADC/DAC

The codec integrates 2-channel 24-bit sigma-delta ADC and 2-channel 24-bit sigma-delta DAC. Such architecture allows for infinite adjustment of sample rate while maintaining linear phase response simply by changing the master clock frequency.

#### 6.6.3.2 Line Inputs

The codec includes six analog inputs pins 2 of which are fully-differential pairs and 1 pair of stereo single-ended inputs. The inputs are separated to left and right channel and connected to two multiplexers. Each multiplexer is followed by a PGA (programmable gain amplifier) which can provide 0 dB to 22.5 dB gain with 0.5 dB step.

The left and right channel differential line-in inputs are high impedance, low capacitance. There is no internal AC coupling capacitance inside the codec. Each channel includes independent PGA and mute function. Passive RF and active Anti-Alias filters which has a fc near 510KHz are also incorporated within the line inputs to prevent high frequencies aliasing into the audio band or otherwise degrading performance. The inputs PGA are biased internally through the operational amplifier to VMID. DC coupling for ADC analog signal is supported which is shown in Figure 18. It is recommended to maintain input signal common mode voltage near VMID for better performance. The recommended common mode voltage value will be AVDD/2, for better swing of internal circuit and preventing clipping at PGA output. The AC coupling is also supported, the external components required are shown in Figure 19. Please refer to Figure 30 and Figure 36 for the typical application about these analog signal path.

The Codec provides 2 single-ended inputs which are MIC\_IN and DEMOD\_IN. An extra gain boost is inserted for MIC\_IN and DEMOD\_IN path between the inputs and multiplexer. This gain boost provides 0 dB or 20 dB gain. Please refer to Figure 28 and Figure 29 for typical application about these analog signal path.

The codec also has a BEEP\_IN which is looped to line out directly through a PGA and a mixer. It is used to loop a user defined tone which is generated by host processor to audio signal output or modulation signal output.

The external components required are shown as Figure 16 and Figure 17.

#### 6.6.3.3 Line Outputs

The Codec provides four low impedance line outputs, suitable for driving typical line loads of impedance 10k and capacitance 50pF. Each output has an independent PGA and can be controlled independently. Please refer to Figure 28 and Figure 29 for typical application about these analog signal paths. The external components required are shown in Figure 20.

#### 6.6.3.4 PLL