# SCI7500F0A

# Contents

| OVERVIEW                                | 6-1  |

|-----------------------------------------|------|

| TERMINAL FUNCTIONS                      | 6-4  |

| EXPLANATIONS OF FUNCTIONS               | 6-8  |

| ELECTRICAL CHARACTERISTICS              | 6-15 |

| EXAMPLE OF CONNECTIONS (REFERENCE)      | 6-20 |

| EXTERNAL DIMENSIONS (REFERENCE)         | 6-22 |

| EXTERNAL SHAPE OF THE CHIP (SCI7500D0A) | 6-23 |

| COORDINATES OF RESPECTIVE PAD CENTERS   | 6-24 |

# **OVERVIEW**

# Description

The SCI7500F0A is a four-line simultaneous selection method MLS (Multi Line Selection) drive power supply IC for driving liquid crystal displays. Using its CMOS charge pump-type high-efficiency voltage converter circuit, the chip is able to generate all the bias voltages required for the four-line MLS drive based on a single 3.0 V power supply input.

When a system is structured from column (segment) drivers such as the SED1580, row (common) drivers such as the SED1751, and this IC, this structure is able to produce a module with extremely low power consumption when compared to a conventional drive method.

Moreover, even greater power conservation is possible when combined with an LCD controller that can pause data transmission (a controller such as the SED1360).

## **Features**

- Power Supply Voltage:

- 2.4 V to 3.6 V single-input power supply • Low Consumption Current: 340  $\mu$ A (in 6 × step-up mode, TYP)

- Standby Current:

- High Voltage Conversion Efficiency: 88% (6 × step-up mode, TYP)

- Generates all bias voltages required for 4-line MLS driving. An external contrast adjustment function can also be attached.

- Equipped with an internal charge pump-type DC/DC voltage converter circuit. Depending on the terminal settings, the chip can be switched between  $5 \times \text{step-up}$  (compatible with 1/200 duty) and  $6 \times$  step-up (compatible with 1/240 duty).

5 uA (MAX)

- Built-in electric charge discharging circuit for the liquid crystal drive current (VL).

- Internal "power off" function using an external signal (XSLP).

- Equipped internally with a liquid crystal drive polarity reverse signal generator circuit.

- The terminal settings can be used to set the range of time for the polarity reversal to 2H to 17H.

- Recommended panel size: VGA, 6.3" or less

- Product being shipped in QFP form ...... (QFP12-48 pin) SCI7500F0A

- Product being shipped in chip form ...... SCI7500D0A

- This product not designed for resistance to radiation.

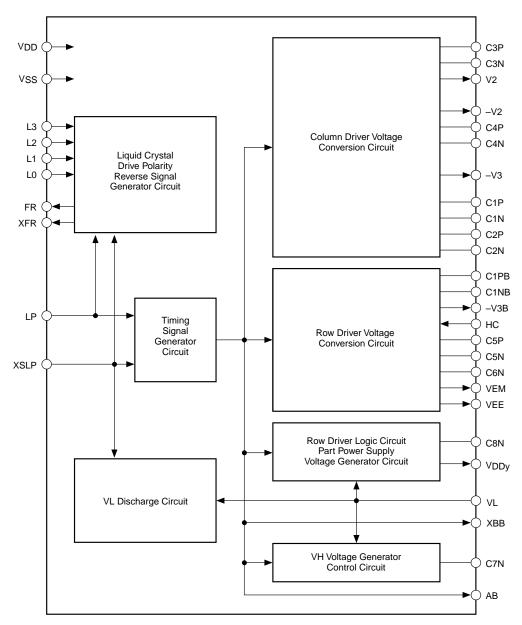

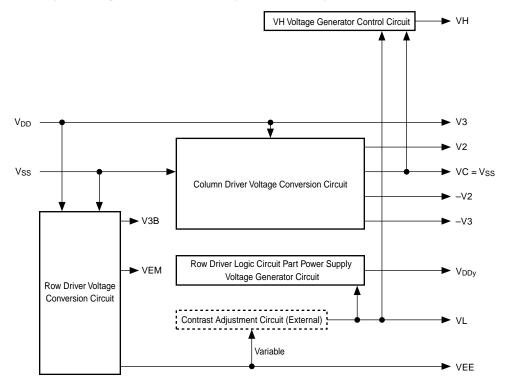

# **Block Diagram**

Figure 1: Block Diagram

# **Explanation of Block Diagram**

• Liquid Crystal Drive Polarity Reverse Signal Generator Circuit

This circuit generates the reverse polarity signal FR from the 1H period pulse signal LP. Pins L0 to L3 can be used to set the polarity reversal interval to 2H to 17H. Moreover, so that it will be possible to drive the top and bottom screens in a 2-screen drive panel in opposite phases, this IC outputs two signals with opposite polarities of each other (FR, XFR).

- Timing Signal Generator Circuit This circuit generates the clock for the charge pump from the 1H period pulse signal LP. When the display off control signal XSLP is set to the Vss level, the clock stops and the voltage converter operation stops.

- Column Driver Voltage Conversion Circuit

- This circuit generates the V2, -V2, and -V3 voltage levels required for column driving.

- Row Driver Voltage Conversion Circuit This generates the voltage (VEE) required for generating the power supply voltages (VH, VL) required for the row drivers. Using VDD as the reference, this generates either a 5 × or 6 × voltage level in the negative direction relative to the input power supply voltage. A terminal can be used to switch between the step-up modes. The contrast adjustment function is performed through the use of an external emitter follower circuit to adjust VEE to generate VL.

- Row Driver Logic Circuit Part Power Supply Voltage Generator Circuit This generates the power supply voltage (VDDy) required by the row driver logic circuit part. This generates a voltage that is higher than the voltage level VL by an amount equal to VDD–VSS.

- VH Voltage Generator Control Circuit This is a circuit for generating the power supply voltage (VH) required for the row driver. The VH voltage can be generated by an external MOS transistor and this circuit.

- VL Discharge Circuit At power off or display off, this circuit discharges the charge remaining on the row driver negative voltage level-side power supply voltage terminal (VL).

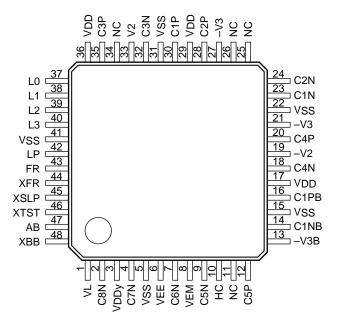

# TERMINAL FUNCTIONS

# **Terminal Layout Diagram**

| Terminal<br>No. | Terminal<br>Name | Terminal<br>No. | Terminal<br>Name | Terminal<br>No. | Terminal<br>Name | Terminal<br>No. | Terminal<br>Name |

|-----------------|------------------|-----------------|------------------|-----------------|------------------|-----------------|------------------|

| 1               | VL               | 13              | —Vзв             | 25              |                  | 37              | L0               |

| 2               | C8N              | 14              | C1NB             | 26              | _                | 38              | L1               |

| 3               | Vddy             | 15              | Vss              | 27              | -V3              | 39              | L2               |

| 4               | C7N              | 16              | C1PB             | 28              | C2P              | 40              | L3               |

| 5               | Vss              | 17              | Vdd              | 29              | Vdd              | 41              | Vss              |

| 6               | Vee              | 18              | C4N              | 30              | C1P              | 42              | LP               |

| 7               | C6N              | 19              | -V2              | 31              | Vss              | 43              | FR               |

| 8               | VEM              | 20              | C4P              | 32              | C3N              | 44              | XFR              |

| 9               | C5N              | 21              | -V3              | 33              | V2               | 45              | XSLP             |

| 10              | HC               | 22              | Vss              | 34              |                  | 46              | XTST             |

| 11              |                  | 23              | C1N              | 35              | C3P              | 47              | AB               |

| 12              | C5P              | 24              | C2N              | 36              | Vdd              | 48              | XBB              |

# Explanation of Terminals Liquid Crystal Drive Polarity Reverse Signal Generator Circuit

| Terminal<br>Name | I/O | SCI7500FoA<br>Terminal Number | SCI7500D <sub>0A</sub><br>PAD Number | Function                                                                                                                                                            |

|------------------|-----|-------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L0 to L3         | I   | 37 to 40                      | 1 to 4                               | Polarity reverse time setting terminals.<br>These are the input terminals for setting the polarity reverse time.<br>The time can be set in the range of 2H to 17H.  |

| FR               | 0   | 43                            | 7                                    | Polarity reverse forward phase signal terminal. This terminal outputs the signal that is generated by the polarity reverse signal generating circuit.               |

| XFR              | 0   | 44                            | 8                                    | Polarity reverse signal reverse phase terminal.<br>This outputs the signal that is in the reverse phase from the<br>polarity reverse forward phase signal terminal. |

# **Timing Signal Generator Circuit**

| Terminal<br>Name | I/O | SCI7500F <sub>0A</sub><br>Terminal Number | SCI7500D <sub>0A</sub><br>PAD Number | Function                                                                                                                                                                                                                           |

|------------------|-----|-------------------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LP               | I   | 42                                        | 6                                    | Display data latch pulse input terminal.<br>This is the input terminal for generating the charge pump clock<br>and the polarity reverse signal. It is necessary to input into this<br>terminal a pulse signal with a period of 1H. |

| XSLP             | I   | 45                                        | 9                                    | The display off control signal terminal.<br>Setting this terminal to the VSS level stops the clock and stops<br>the operations of the voltage converter.                                                                           |

# Column Driver Voltage Conversion Circuit

| Terminal<br>Name | I/O | SCI7500F <sub>0A</sub><br>Terminal Number | SCI7500D <sub>0A</sub><br>PAD Number | Function                                                                                                             |

|------------------|-----|-------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| C3P              | (O) | 35                                        | 43                                   | The positive-side connection terminal for the flying capacitor CP3 for generating the V <sub>2</sub> output voltage. |

| C3N              | (O) | 32                                        | 41                                   | The negative-side connection terminal for the flying capacitor CP3 for generating the V2 output voltage.             |

| V2               | 0   | 33                                        | 42                                   | V2 output voltage terminal.                                                                                          |

| C4P              | (O) | 20                                        | 31                                   | The positive-side connection terminal for the flying capacitor CP4 for generating the $-V_2$ output voltage.         |

| C4N              | (O) | 18                                        | 29                                   | The negative-side connection terminal for the flying capacitor CP4 for generating the $-V_2$ output voltage.         |

| -V2              | 0   | 19                                        | 30                                   | -V2 output voltage terminal.                                                                                         |

| C1P              | (O) | 30                                        | 39                                   | The positive-side connection terminal for the flying capacitor CP1 for generating the $-V_3$ output voltage.         |

| C1N              | (O) | 23                                        | 34                                   | The negative-side connection terminal for the flying capacitor CP1 for generating the $-V_3$ output voltage.         |

| C2P              | (O) | 28                                        | 37                                   | The positive-side connection terminal for the flying capacitor CP2 for generating the $-V_3$ output voltage.         |

| C2N              | (O) | 24                                        | 35                                   | The negative-side connection terminal for the flying capacitor CP2 for generating the $-V_3$ output voltage.         |

| -V3              | 0   | 21, 27                                    | 32, 36                               | -V <sub>3</sub> output voltage terminal.                                                                             |

| Terminal<br>Name | I/O | SCI7500F <sub>0A</sub><br>Terminal Number | SCI7500D <sub>0A</sub><br>PAD Number | Function                                                                                                                                                                                    |

|------------------|-----|-------------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C1PB             | (O) | 16                                        | 27                                   | The positive-side connection terminal for the flying capacitor CP1B and CP8 for generating the $-V_{3B}$ output voltage.                                                                    |

| C1NB             | (O) | 14                                        | 25                                   | The negative-side connection terminal for the flying capacitor CP1B for generating the $-V_{3B}$ output voltage.                                                                            |

| —Vзв             | 0   | 13                                        | 24                                   | The negative V <sub>3B</sub> output voltage terminal. This is an output terminal equipped as the middle voltage level for generating the VEE output voltage.                                |

| нс               | I   | 10                                        | 22                                   | The step-up mode select terminal. When this terminal is tied Vss, then the chip is put into 5 X step-up mode. However, when it is connected to $-3B$ , the chip is set to 6 X step-up mode. |

| C5P              | (O) | 12                                        | 23                                   | The positive-side connection terminal for the flying capacitor CP5 and CP6 for generating the VEM output voltage.                                                                           |

| C5N              | (O) | 9                                         | 21                                   | The negative-side connection terminal for the flying capacitor CP5 for generating the VEM output voltage.                                                                                   |

| VEM              | 0   | 8                                         | 20                                   | The VEM output voltage terminal.<br>This is an output terminal equipped as the middle voltage level for<br>generating the VEE output voltage.                                               |

| C6N              | (O) | 7                                         | 19                                   | The negative-side connection terminal for the flying capacitor CP6 for generating the VEE output voltage. (The positive-side of CP6 is C5P.)                                                |

| Vee              | 0   | 6                                         | 18                                   | The VEE output voltage terminal.<br>By changing the HC terminal interconnection method, it is<br>possible to switch between the 5-level step-up mode and the<br>6-level step-up mode.       |

# Row Driver Voltage Conversion Circuit

# Common Driver Logic Circuit Part Power Supply Voltage Generator Circuit

| Terminal<br>Name | I/O | SCI7500F <sub>0A</sub><br>Terminal Number | SCI7500D <sub>0A</sub><br>PAD Number | Function                                                                                                                                                                                                                                                                                       |

|------------------|-----|-------------------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C8N              | (O) | 2                                         | 14                                   | The negative-side connection terminal for the flying capacitor CP8 for generating the VDDy output voltage. The positive connection terminal for CP8 is the same as C1PB.                                                                                                                       |

| Vddy             | 0   | 3                                         | 15                                   | The row driver logic circuit part power supply output terminal.<br>This generates the power supply voltage required for the row<br>driver logic circuit part. The output is higher than the VL level in<br>the positive direction by an amount equal to the difference<br>between VDD and Vss. |

# VH Voltage Generator Control Circuit

| Terminal<br>Name | I/O | SCI7500F <sub>0A</sub><br>Terminal Number | SCI7500D <sub>0A</sub><br>PAD Number | Function                                                                                                                                                                                     |

|------------------|-----|-------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AB               | 0   | 47                                        | 11                                   | The V <sub>H</sub> output voltage generator clock terminal A.<br>This is the clock output terminal for the external N-channel MOS<br>transistor control.                                     |

| ХВВ              | 0   | 48                                        | 12                                   | The V <sub>H</sub> output voltage generator clock terminal B.<br>This is the clock output terminal for the external P-channel MOS<br>transistor control.                                     |

| C7N              | (O) | 4                                         | 16                                   | The negative-side connection terminal for the flying capacitor<br>CP7 for generating the VH output voltage. The positive-side<br>connection terminal corresponds to the external transistor. |

# VL Discharge Circuit

| Terminal<br>Name | I/O | SCI7500FoA<br>Terminal Number | SCI7500D <sub>0A</sub><br>PAD Number | Function                                                                                                                                                                                                                                                                                            |

|------------------|-----|-------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VL               | I   | 1                             | 13                                   | This is the row driver negative voltage level power supply voltage terminal.<br>The VL signal that is used to adjust the contrast is input to this terminal. This serves as the power supply for the VH voltage generator control circuit.<br>XSLP operates the discharge circuit at the VSS level. |

## **The Test Circuit**

| Terminal<br>Name | I/O | SCI7500F <sub>0A</sub><br>Terminal Number | SCI7500D <sub>0A</sub><br>PAD Number | Function                                                                               |

|------------------|-----|-------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------|

| XTST             | I   | 46                                        | 10                                   | This is a test terminal.<br>Insure that this terminal is always tied to the Vod level. |

#### Power Supply Terminals <Note 1>

| Terminal<br>Name | I/O | SCI7500FoA<br>Terminal Number | SCI7500D <sub>0A</sub><br>PAD Number | Function                                 |

|------------------|-----|-------------------------------|--------------------------------------|------------------------------------------|

| Vdd              | I   | 17, 29,<br>36 *1              | 28, 38<br>44 *1                      | Input power supply terminals (positive). |

| Vss              | I   | 5, 15, 22,<br>31, 41 *1       | 5, 17, 26<br>33, 40 *1               | Input power supply terminals (negative). |

Note: \*1 Please connect these power supply terminals externally.

# **EXPLANATIONS OF FUNCTIONS**

## **Overview of Operation**

The SCI7500F0A is a power supply IC for operating the 4-line simultaneous selection method MLS (Multi Line Selection) driver LCDs. Using its CMOS charge pump-type high-efficiency voltage converter circuit, this chip can produce all of the bias voltages necessary for a 4-line MLS driving based on a single 3.0 V power supply.

The voltage levels produced are as follows:

- The liquid crystal drive power supply voltages required for the column drivers (V3 = VDD, V2, VC = VSS, -V2, -V3).

- The liquid crystal drive power supply voltages required for the row drivers (VH, VC = VSS, VL).

- The power supply voltages for the logic circuits of the row driver (VDDy).

However, the row driver low voltage-side power supply voltage (VL) requires an external bipolar transistor for adjusting the contrast. Moreover, external MOS transistors (2SK\*\*\*, 2SJ\*\*\*) are required for generating the row driver high-level power supply voltage (VH).

Depending on a terminal setting, the chip can switch between 6 X step-up mode and 5 X step-up mode, with 1/240 duty and 1/200 duty, respectively. Consequently, it is possible to obtain the required voltages with maximum efficiency.

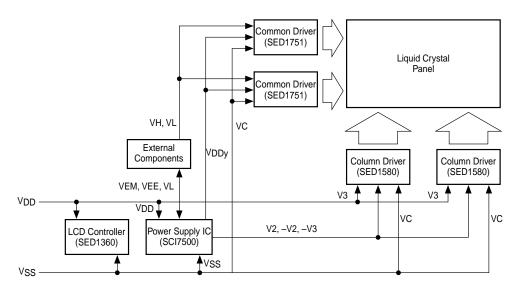

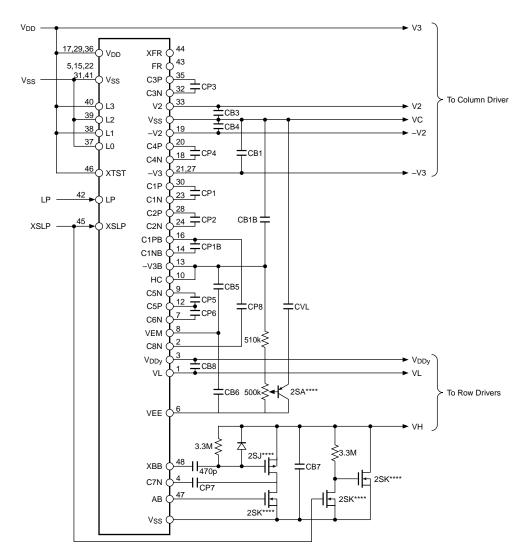

An example of a system structure diagram for the power supply interconnections is given below:

Figure 2: The System Configuration

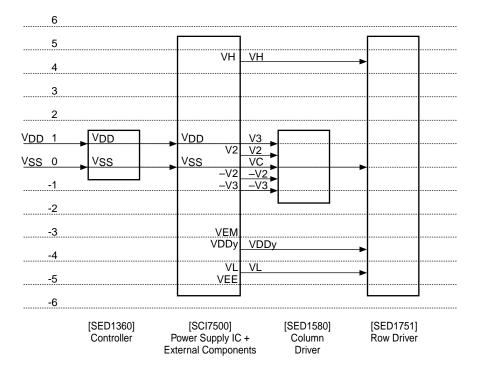

The relationships between voltage levels in the system shown in Figure 2 are given in the table below.

Figure 3: The Relationships Between Voltages Within the System (in 6 × step-up mode)

The logical formulas for each of the voltage levels is as given below:

| When in 6 × s<br>(when HC is con      |                                                  | When in $5 \times$ step-up mode (when HC is connected to Vss). |                                                  |  |

|---------------------------------------|--------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------|--|

| Logical Formula                       | Voltage level when<br>VDD = 3.0V<br>and Vss = 0V | Logical Formula                                                | Voltage level when<br>VDD = 3.0V<br>and Vss = 0V |  |

| $VH = -VL = 5 (VDD - VSS) - \alpha$   | 15.0–α                                           | $V_{H} = -V_{L} = 4 (V_{DD} - V_{SS}) - \alpha$                | 12.0–α                                           |  |

| V3 = VDD-VSS                          | 3.0                                              | V3 = VDD-VSS                                                   | 3.0                                              |  |

| V <sub>2</sub> = 1/2 (VDD-VSS)        | 1.5                                              | V2 = 1/2 (VDD-VSS)                                             | 1.5                                              |  |

| Vc = Vss                              | 0                                                | Vc = Vss                                                       | 0                                                |  |

| $-V_2 = -1/2$ (VDD-VSS)               | -1.5                                             | $-V_2 = -1/2$ (VDD-VSS)                                        | -1.5                                             |  |

| $-V_3 = -V_{3B} = -(V_{DD} - V_{SS})$ | -3.0                                             | $-V_3 = -V_{3B} = -(V_{DD} - V_{SS})$                          | -3.0                                             |  |

| Vem = -3 (Vdd-Vss)                    | -9.0                                             | $V_{EM} = -2 (V_{DD} - V_{SS})$                                | -6.0                                             |  |

| $VDDy = -4 (VDD-VSS) + \alpha$        | -12.0 + α                                        | $V_{DDy} = -3 (V_{DD} - V_{SS}) + \alpha$                      | -9.0 + α                                         |  |

| $V_L = -5 (V_{DD} - V_{SS}) + \alpha$ | -15.0 + α                                        | $VL = -4 (VDD - VSS) + \alpha$                                 | -12.0 + α                                        |  |

| Vee = -5 (Vdd-Vss)                    | -15.0                                            | VEE = -4 (VDD-VSS)                                             | -12.0                                            |  |

Where  $\alpha = \text{variable} \ge 0$  (contrast adjustment)

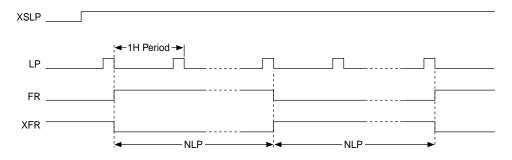

# The Liquid Crystal Drive Polarity Reverse Signal Generator Circuit

This circuit produces the polarity reverse signal from the 1H period pulse signal LP. Terminals L0 to L3 can be used to set the polarity reversed period in the range of 2H to 17H. So that the upper and lower screens can be driven in mutually opposite phases when a 2-screen drive panel is used, this IC outputs two signals with mutually opposing polarities (i.e. with opposite phases) from the FR and the XFR terminals. The timing of the output transitions is synchronized with the falling edge of the LP signal.

Figure 4: LP and FR Signal Timing Diagram

The relationship between the NLP during the polarity reversed interval and the settings of terminals L0 to L3 is as shown below:

| Terminal | Terminal Settings While Polarity is Reversed |    |    |      |           | Function   |           |  |

|----------|----------------------------------------------|----|----|------|-----------|------------|-----------|--|

| L3       | L2                                           | L1 | L0 | Time | NLP       |            |           |  |

|          |                                              | 0  | 0  | 17H  | LP Signal | 17th pulse |           |  |

|          | 0                                            | 0  | 1  | 2H   | LP Signal | 2nd pulse  |           |  |

|          | 0                                            | 1  | 0  | 3H   | LP Signal | 3rd pulse  |           |  |

|          |                                              | I  | 1  | 4H   | LP Signal | 4th pulse  |           |  |

| 0        |                                              | 0  | 0  | 5H   | LP Signal | 5th pulse  |           |  |

|          |                                              | 0  | 1  | 6H   | LP Signal | 6th pulse  |           |  |

|          | 1                                            | 4  | 0  | 7H   | LP Signal | 7th pulse  |           |  |

|          |                                              | 1  |    | 1    | 8H        | LP Signal  | 8th pulse |  |

|          |                                              | 0  | 0  | 9H   | LP Signal | 9th pulse  |           |  |

|          | 0                                            | 0  | 1  | 10H  | LP Signal | 10th pulse |           |  |

|          | 0                                            | 1  | 0  | 11H  | LP Signal | 11th pulse |           |  |

| 1        |                                              |    | 1  | 12H  | LP Signal | 12th pulse |           |  |

| 1        |                                              | 0  | 0  | 13H  | LP Signal | 13th pulse |           |  |

|          | 1                                            | 0  | 1  | 14H  | LP Signal | 14th pulse |           |  |

|          |                                              | 1  | 0  | 15H  | LP Signal | 15th pulse |           |  |

|          |                                              |    | 1  | 16H  | LP Signal | 16th pulse |           |  |

# The Timing Signal Generator Circuit

This generates the clock for the charge pump from the 1H period pulse signal LP. When the display off control signal XSLP is set to Vss, this clock stops and the IC voltage converter operation halts. The VH output voltage generator clocks AB and XBB are also produced by this circuit.

| Input Signal XSLP |  |

|-------------------|--|

| Input Signal LP   |  |

| Output Signal AB  |  |

| Output Signal XBB |  |

Figure 5: The AB and XBB Signal Output Timing

# The Voltage Converter Circuit

The voltage converter circuit comprises a CMOS charge pump-type DC/DC converter. The relational diagram of the voltage converter circuits within this IC is as shown below. The numbers within parentheses in the diagram correspond to the number in "Figure 1: Block Diagram."

Figure 6: A Relational Diagram of the Voltage Converter Circuits

| When in 6 × st<br>(when HC is conn                         |                                                  | When in 5 $\times$ step-up mode (when HC is connected to VSS). |                                                  |  |

|------------------------------------------------------------|--------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------|--|

| Logical Formula                                            | Voltage level<br>when VDD = 3.0V<br>and VSS = 0V | Logical Formula                                                | Voltage level<br>when VDD = 3.0V<br>and VSS = 0V |  |

| VH = -VL = 5 (VDD-VSS)-a                                   | 15.0–α                                           | $V_{H} = -V_{L} = 4 (V_{DD} - V_{SS}) - \alpha$                | 12.0–α                                           |  |

| V3 = VDD-VSS                                               | 3.0                                              | V3 = VDD-VSS                                                   | 3.0                                              |  |

| V2 = 1/2 (VDD-VSS)                                         | 1.5                                              | V2 = 1/2 (VDD-VSS)                                             | 1.5                                              |  |

| Vc = Vss                                                   | 0                                                | Vc = Vss                                                       | 0                                                |  |

| -V <sub>2</sub> = -1/2 (V <sub>DD</sub> -V <sub>SS</sub> ) | -1.5                                             | $-V_2 = -1/2$ (VDD-VSS)                                        | -1.5                                             |  |

| $-V_3 = -V_{3B} = -(V_{DD} - V_{SS})$                      | -3.0                                             | $-V_3 = -V_{3B} = -(V_{DD} - V_{SS})$                          | -3.0                                             |  |

| Vem = -3 (Vdd-Vss)                                         | -9.0                                             | $V_{EM} = -2 (V_{DD} - V_{SS})$                                | -6.0                                             |  |

| $VDDy = -4 (VDD - VSS) + \alpha$                           | -12.0+ α                                         | $V_{DDy} = -3 (V_{DD} - V_{SS}) + \alpha$                      | -9.0 + α                                         |  |

| $V_L = -5 (V_{DD} - V_{SS}) + \alpha$                      | -15.0+ α                                         | $VL = -4 (VDD - VSS) + \alpha$                                 | -12.0 + α                                        |  |

| VEE = -5 (VDD-VSS)                                         | -15.0                                            | VEE = -4 (VDD-VSS)                                             | -12.0                                            |  |

Logical Formulas for the Various Voltage Levels

Where  $\alpha = variable \ge 0$  (contrast adjustment)

The capacitors for the charge pump can be of two different types: the flying capacitors which transition between a charged state and a discharged state, and the storage capacitor that stores charge. The clock that controls the state changes in the flying capacitors is generated by the timing signal generator circuit from the display data latch pulse input terminal LP. The operating frequency f sw of the flying capacitor is calculated as follows:

$fsw = 1/(2 \times t_{CLP})$ Where t CLP is the LP frequency.

The voltage logic that is biased by both ends of the flying capacitors and storage capacitors is as shown below: (Reference "10. Example of Connections (Reference)" regarding recommended capacitance values and connection methods for the capacitors.)

#### Flying Capacitors and Storage Capacitors

| Capacitor<br>Name |                  | Voltage logic fo<br>both ends of | Column side/                   |             |

|-------------------|------------------|----------------------------------|--------------------------------|-------------|

| INAI              | 6 × step-up mode |                                  | $5 \times \text{step-up mode}$ | Row side    |

|                   | CP1              | VDD-VSS                          | VDD-VSS                        |             |

|                   | CP2              | VDD-VSS                          | VDD-VSS                        | Column Cide |

|                   | CP3              | 1/2 (VDD-VSS)                    | 1/2 (VDD-VSS)                  | Column Side |

| Eb dia a          | CP4              | 1/2 (VDD-VSS)                    | 1/2 (VDD-VSS)                  |             |

| Flying            | CP1B             | Vdd-Vss                          | VDD-VSS                        |             |

| Capacitor         | CP5              | 2 (VDD-Vss)                      | VDD-VSS                        |             |

|                   | CP6              | 2 (VDD-VSS)                      | 2 (VDD-VSS)                    | Row side    |

|                   | CP7              | 5 (Vdd-Vss) -α                   | 4 (VDD-VSS) -α                 |             |

|                   | CP8              | 5 (Vdd-Vss) -α                   | 4 (VDD-VSS) -α                 |             |

|                   | CB1              | Vdd-Vss                          | VDD-VSS                        |             |

|                   | CB3              | 1/2 (VDD-VSS)                    | 1/2 (VDD-VSS)                  | Column side |

|                   | CB4              | 1/2 (VDD-VSS)                    | 1/2 (VDD-VSS)                  |             |

| Charasta          | CB1B             | VDD-VSS                          | VDD-VSS                        |             |

| Storage           | CB5              | 2 (VDD-VSS)                      | VDD-VSS                        |             |

| Capacitor         | CB6              | 2 (VDD-VSS)                      | 2 (VDD-VSS)                    | Devusida    |

|                   | CB7              | 5 (VDD–VSS) – $\alpha$           | 4 (VDD-VSS) -α                 | Row side    |

|                   | CB8              | Vdd-Vss                          | VDD-VSS                        |             |

|                   | CVL              | 5 (Vdd-Vss) -α                   | 4 (VDD-VSS) -α                 |             |

Where  $\alpha$  = variable  $\geq$  0 (contrast adjustment)

In the column driver voltage converter circuit either flying capacitor CP1 or CP2 can be omitted. When the panel is smaller than a 6.3 inch VGA panel, or if one wishes to sacrifice image quality to save cost, one may consider this omission; however, the output impedance will increase and will be outside of what is indicated in "Electrical Characteristics," and thus we recommend that you experimentally confirm the structure for each application.

Switching between the step-up modes in the row driver voltage converter circuits can be done by setting the HC terminal. When the HC terminal is connected to -V3B, then the system will be in  $6 \times$  step-up mode, but when the HC terminal is connected to the Vss terminal, then the system will be in  $5 \times$  step-up mode. Furthermore, by connecting the -V3 terminal to the -V3B terminal, it is possible to omit the flying capacitor CP1B and storage capacitor CP1B. However, when these capacitors are omitted, the output impedance will increase and will be outside of what is indicated in "Electrical Characteristics," and thus we recommend that you experimentally confirm the structure for each application.

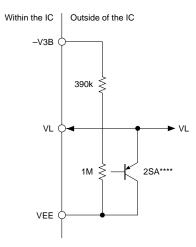

# The Contrast Adjustment Circuit

The row driver negative voltage-side power supply voltage VL can be adjusted and generated by an external emitter follower circuit using VEE. The contrast adjustment function is shown in the circuit connection example below:

Figure 7: Contrast Adjustment Circuit

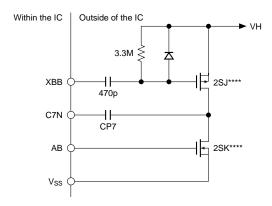

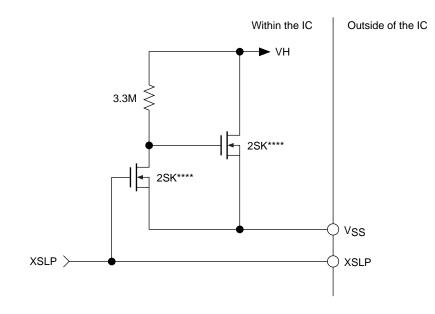

### The VH Voltage Generator Control Circuit

The row driver positive voltage-side power supply voltage VH can be generated from this circuit and the VH output voltage generator clocks AB, XBB, and external components. This is shown in the circuit connection example below.

Figure 8: Example of Circuit Connections for Generating the VH Voltage

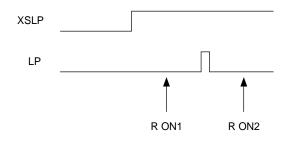

# The VL Discharge Circuit

When XSLP is put to the Vss level, the VL discharge circuit within the IC is triggered, and residual charge at the row driver negative voltage-side power supply voltage terminal VL is discharged to the Vss level. The VL voltage adjusted for the contrast must be input to the VL terminal. (See "The Contrast Adjustment Circuit.")

# The VH Discharge Circuit

When XSLP is put to the Vss level, the residual charge at the row driver positive voltage-side power supply terminal VH can be discharged to the Vss level through an external MOS transistor. An example circuit connection is shown below.

Figure 9: The VH Discharge Circuit

• •

~ . .

# ELECTRICAL CHARACTERISTICS

# The Absolute Maximum Ratings

|                                |        |         |              |                      | Vss = 0V                                         |

|--------------------------------|--------|---------|--------------|----------------------|--------------------------------------------------|

| ltem                           | Signal | Rated   | Value        | Units                | Notes                                            |

| item                           | Signal | Minimum | Maximum      | Units                | Notes                                            |

| Input power supply voltage 1   | Vdd    |         | 3.7          | V                    | VDD terminal                                     |

| Input power supply voltage 2   | VL     | VEE-0.3 | 0.3          | V                    | VL terminal                                      |

| Input terminal voltage         | VI     | -0.3    | Vdd + 3.0    | V                    | The L3 to L0, LP,<br>XSLP, and XTST<br>terminals |

| Input current                  | IDD    | —       | 10           | mA                   | Vdd, Vl                                          |

| Output current 1               | IV2    | —       | 6            | mA                   | V2 terminal                                      |

| Output current 2               | I-V2   | —       | 6            | mA                   | -V2 terminal                                     |

| Output current 3               | I-V3   | _       | 5            | mA                   | -V3 terminal                                     |

| Output current 4               | I VEE  |         | 1            | mA                   | VEE terminal                                     |

| Output current 5               | I VDDy |         | 0.1          | mA                   | VDDy terminal                                    |

| Allowable loss                 | Pd     |         | 100          | mW                   | Ta ≤ 55 °C                                       |

| Operating temperature          | Topr   | -30     | 85           | °C                   | —                                                |

| Storage temperature            | Tstg   | -55     | 150          | °C                   | _                                                |

| Soldering temperature and time | Tsol   | —       | 260 	imes 10 | $^{\circ}C \times S$ | At the lead                                      |

Notes: \*1 Do not apply a voltage from the outside to the output terminals nor to the capacitor connection terminals.

Notes: \*2 Operating failures and/or permanent damage may occur if this chip is used under conditions exceeding the absolute maximum ratings listed above. Moreover, the reliability of this chip may be dramatically compromised even if the chip continues to function normally for a time.

# **DC Characteristics**

|                                          |        | Standard                                                                                                                                                                               | connections <n< th=""><th>ote 1&gt;, Ll</th><th>P period</th><th><math>= 69 \mu s, 1</math></th><th>LP widt</th><th><math>h = 1 \mu s.</math></th></n<> | ote 1>, Ll | P period  | $= 69 \mu s, 1$ | LP widt | $h = 1 \mu s.$ |

|------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------|-----------------|---------|----------------|

| ltom                                     | Cumhal | Derem                                                                                                                                                                                  | Parameters                                                                                                                                              |            | Standards |                 | Units   | Notes          |

| Item                                     | Symbol | Param                                                                                                                                                                                  | elers                                                                                                                                                   | Min        | Тур       | Max             | Units   | Notes          |

| Input power<br>supply voltage            | Vdd    | _                                                                                                                                                                                      |                                                                                                                                                         | 2.4        | 3.0       | 3.6             | V       | —              |

| Input power<br>supply voltage            | VL     | _                                                                                                                                                                                      |                                                                                                                                                         | VEE+0.6    | _         | -V3             | V       | —              |

| High level<br>input voltage              | Vін    | Applicable terminals<br>XSLP, L0 to L3, XT                                                                                                                                             |                                                                                                                                                         | 0.8Vdd     | —         | Vdd             | V       | —              |

| Low level<br>input voltage               | VIL    | $V_{DD} = 2.4 \text{ to } 3.6 \text{V}$                                                                                                                                                | 51                                                                                                                                                      | 0          | —         | 0.2Vdd          | V       | —              |

| Input leakage<br>current                 | Ilin   | $\label{eq:VSS} \begin{array}{l} Vss \leq VI \leq Vdd, \\ Vdd = 2.4 \text{ to } 3.6 V \end{array}$                                                                                     |                                                                                                                                                         | -0.5       | —         | 0.5             | μΑ      | —              |

| V2 output                                | V2     | lo = 2mA                                                                                                                                                                               | VDD = 2.4V                                                                                                                                              | 1.148      | _         | 1.2             | V       | —              |

| voltage                                  | V2     | (to Vss)                                                                                                                                                                               | VDD = 2.7V                                                                                                                                              | 1.298      | —         | 1.35            |         |                |

| -V2 output                               | -V2    | lo = 2mA                                                                                                                                                                               | VDD = 2.4V                                                                                                                                              | -1.2       | —         | -1.120          | V       | 2              |

| voltage                                  | -V2    | (from Vss)                                                                                                                                                                             | VDD = 2.7V                                                                                                                                              | -1.35      | —         | -1.272          |         |                |

| –V3 output                               | -V3    | lo = 1mA                                                                                                                                                                               | VDD = 2.4V                                                                                                                                              | -2.4       | _         | -2.340          | V       | 2              |

| voltage                                  | -V3    | (from Vss)                                                                                                                                                                             | VDD = 2.7V                                                                                                                                              | -2.7       | _         | -2.644          |         |                |

| VEE output                               | VEE    | lo = 0.4mA                                                                                                                                                                             | VDD = 2.4V                                                                                                                                              | -12.0      | _         | -11.2           | V       | —              |

| voltage                                  | VEE    | (from Vss)                                                                                                                                                                             | VDD = 2.7V                                                                                                                                              | -13.5      | —         | -12.7           |         |                |

| VDDy output                              | Vddy   | lo = 0.02mA                                                                                                                                                                            | VDD = 2.4V                                                                                                                                              | VL + 2.33  | _         | VL + 2.40       | V       | —              |

| voltage                                  | VDDy   | (to VL)                                                                                                                                                                                | VDD = 2.7V                                                                                                                                              | VL + 2.63  | —         | VL + 2.70       |         |                |

| Output<br>resistor 1                     | Ron1   | Applicable<br>terminal: C7N                                                                                                                                                            | VDD = 2.4V                                                                                                                                              | —          | _         | 16              | Ω       | 3              |

| resistor i                               |        | Iон = -0.2mA                                                                                                                                                                           | VDD = 2.7V                                                                                                                                              | —          | —         | 15              |         |                |

| Output                                   | Ron2   | Applicable<br>terminal: C7N                                                                                                                                                            | VDD = 2.4V                                                                                                                                              | _          | _         | 21              | Ω       | 3              |

| resistor 1                               |        | lон = 0.2mA                                                                                                                                                                            | VDD = 2.7V                                                                                                                                              | —          | —         | 20              |         |                |

| High level<br>output voltage             | Vон    | Applicable<br>terminals:                                                                                                                                                               | Іон = −20μА                                                                                                                                             | Vdd-0.1    | _         | Vdd             | V       | _              |

| Low level<br>output voltage              | Vol    | XBB, AB, FR, XFR<br>VDD = 2.4 to 3.6V                                                                                                                                                  | Ιοι = 20μΑ                                                                                                                                              | 0          | —         | 0.1             | V       | —              |

| Consumption                              | IOPR5  | $5 \times \text{step-up}$ , no load VDD = $3.0$ V                                                                                                                                      |                                                                                                                                                         | —          | 250       | 330             | μA      | —              |

| Current                                  | IOPR6  | $6 \times step-up$ , no load                                                                                                                                                           | 6 × step-up, no load VDD = 3.0V                                                                                                                         |            | 340       | 470             | μA      | —              |

| Static current                           | la     | VDD = 2.4 to 3.6V, X                                                                                                                                                                   | VDD = 2.4 to 3.6V, XSLP = 0V                                                                                                                            |            | _         | 5               | μA      | —              |

| Step-up power<br>converter<br>efficiency | Peff   | $6 \times \text{step-up}, V_{DD} = 3.0V$<br>The load conditions were as follows:<br>$V_2: Io = 2mA$<br>$-V_2: Io = 2mA$<br>$-V_3: Io = 1mA$<br>$V_4: Io = 0.4mA$<br>$V_5: Io = 0.02mA$ |                                                                                                                                                         | _          | 88        | _               | %       | _              |

When not otherwise specified:  $Ta = -30^{\circ}C$  to  $+85^{\circ}C$ , Vss = 0V,  $6 \times$  step-up, VL = VEE + 0.6V, Standard connections <Note 1>, LP period = 69µs, LP width = 1µs.

Notes 1. For standard connections, see "Example of Connections (Reference)."

2. Measured in a state where negative charges were not applied to -V2 and -V3 simultaneously.

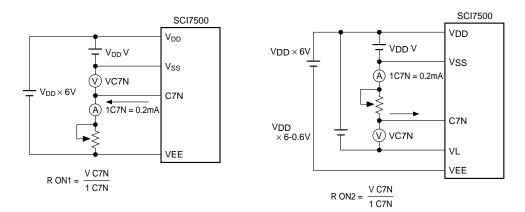

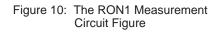

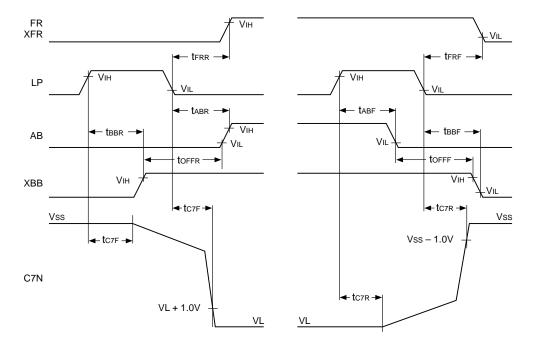

3. The measurement circuits and timing of the output resistance 1 RON1, and output resistance 2 RON2 are as shown below.

Figure 11: The RON2 Measurement Circuit

# **AC Characteristics**

The AC test parameters:

- Input voltage level: VIH = 0.8 VDD V

- VIL = 0.2 VDD V

- Input signal rise time: Tr = max 10 ns

Input signal fall time: Tf = max 10 ns

- $V_{DD} = 2.4 \text{ to } 3.6 \text{ V}$   $V_{SS} = 0 \text{ V}$  $T_a = -30 \text{ to } 85 \text{ °C}$

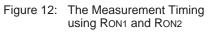

## **Input Timing Characteristics**

| ltarra            | Currents of  |     | Ratings  |      | Linite | Nataa |

|-------------------|--------------|-----|----------|------|--------|-------|

| Item              | Symbol       | Min | Тур      | Max  | Units  | Notes |

| LP Period         | <b>t</b> CLP | 50  | 65 to 90 | 125  | μs     |       |

| LP Pulse<br>Width | twlp         | 70  |          | 2000 | ns     | *1    |

Note \*1 While the chip continues to function with LP pulse widths in excess of 2000 ns, the wider the LP pulse width, the higher the output impedance of the various output voltages. For this IC, although we are recommending inputting of LP signals through the LP pin as the basic clock, inputting of other signals through the LP pin will also provide the same characteristics as far as the signals being input can satisfy the above specifications.

#### (Reference) LP Period

| Frame Frequency | Duty  | LP Period |

|-----------------|-------|-----------|

| 40              | 1/200 | 125 μs    |

| 60              | 1/200 | 83 µs     |

| 60              | 1/240 | 69 µs     |

| 80              | 1/240 | 52 μs     |

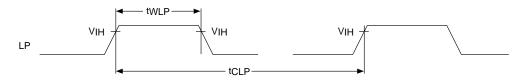

# **Output Timing Characteristics**

| LP pulse width = $1\mu$ s, 6 X | step-up voltag | ge, VL = VE | E + 0.6V, S | tandard Conn | ections |

|--------------------------------|----------------|-------------|-------------|--------------|---------|

|                                |                |             |             |              |         |

| ltem                                        | Signal       | Applicable | Load       | Rated Values |      | Units |

|---------------------------------------------|--------------|------------|------------|--------------|------|-------|

| Item                                        | Signal       | Terminals  | Conditions | Min          | Max  | Units |

| FR signal rise delay time                   | <b>t</b> FRR | FR, XFR    |            | 330          | 3300 | ns    |

| FR signal fall delay time                   | <b>t</b> FRF | FR, XFR    | C∟ = 50pF  | 330          | 3300 | ns    |

| AB signal rise delay time                   | <b>t</b> abr | AB         |            | 230          | 2000 | ns    |

| AB signal fall delay time                   | <b>t</b> ABF | AB         |            | 180          | 1900 | ns    |

| XBB signal rise delay time                  | <b>t</b> BBR | XBB        |            | 130          | 1100 | ns    |

| XBB signal fall delay time                  | <b>t</b> BBF | XBB        | *2         | 280          | 3200 | ns    |

| Rising edge output phase differential time  | toffr        | AB, XBB    |            | 1000         | 2400 | ns    |

| Falling edge output phase differential time | tofff        | AB, XBB    |            | 1000         | 2200 | ns    |

| C7N signal falling edge delay time          | tc7F         | C7N        | *3         | 270          | 2400 | ns    |

| C7N signal rising edge delay time           | tc7R         | C7N        | 3          | 490          | 3800 | ns    |

\*2 When 2SJ185, 2SK1399 (manufactured by NEC) are used.\*3 With a load with standard connections. Note

Note

# EXAMPLE OF CONNECTIONS (REFERENCE)

Standard Connections for the  $6 \times$  step-up mode.

| Capacitor Name | Capacitance Value (µF) | Capacitor Name | Capacitance Value (µF) |

|----------------|------------------------|----------------|------------------------|

| CP1            | 4.7                    | CB1            | 4.7                    |

| CP2            | 4.7                    | CB3            | 4.7                    |

| CP3            | 4.7                    | CB4            | 4.7                    |

| CP4            | 4.7                    | CB5            | 1.0                    |

| CP5            | 1.0                    | CB6            | 1.0                    |

| CP6            | 1.0                    | CB7            | 1.0                    |

| CP7            | 1.0                    | CB8            | 0.1                    |

| CP8            | 0.1                    | CB1B           | 4.7                    |

| CP1B           | 4.7                    | CVL            | 1.0                    |

The capacitance values for the capacitors are the recommended value for a 6.3 inch VGA liquid crystal panel. The characteristics shown in "Electrical Characteristics" are the characteristics obtained when capacitors with the values shown above are used. Consequently, while one may consider reducing the capacitance values of these capacitors when a liquid crystal panel smaller than a 6.3-inch VGA screen is used, in such a case the output impedance would increase, and thus we recommend experimental verification for each product type, and that the capacitance values be set such that the liquid crystal drive voltages are stable.

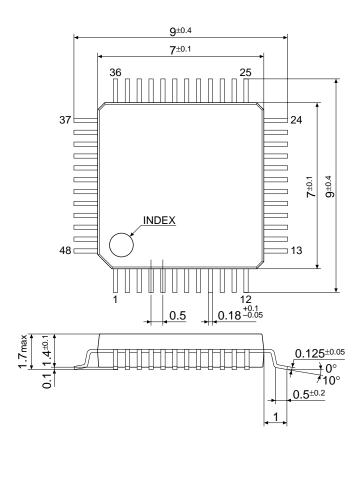

# **EXTERNAL DIMENSIONS (REFERENCE)**

Note: These dimensions are subject to change without notice.

Plastic QFP12-48 pin

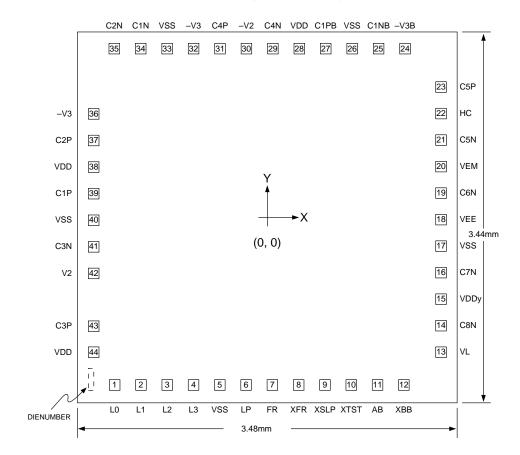

# EXTERNAL SHAPE OF THE CHIP (SCI7500D0A)

## PAD layout

| Chip size:           | $3.48 mm \times 3.44 mm$     |

|----------------------|------------------------------|

| Chip thickness:      | $400 \mu m \pm 30 \mu m$     |

| PAD hole size:       | $100 \mu m \times 100 \mu m$ |

| Substrate potential: | VDD                          |

| DIE number:          | F7500D0A                     |

# COORDINATES OF RESPECTIVE PAD CENTERS

Unit: µm

| PAD No. | PAD name | Х       | Y       |

|---------|----------|---------|---------|

| 1       | LO       | -1431.2 | -1554.4 |

| 2       | L1       | -1191.2 |         |

| 3       | L2       | -951.2  |         |

| 4       | L3       | -711.2  |         |

| 5       | Vss      | -471.2  |         |

| 6       | LP       | -280.8  |         |

| 7       | FR       | -40.8   |         |

| 8       | XFR      | 199.2   |         |

| 9       | XSLP     | 439.2   |         |

| 10      | XTST     | 679.2   |         |

| 11      | AB       | 919.2   |         |

| 12      | XBB      | 1159.2  | V       |

| 13      | VL       | 1574.4  | -1264.8 |

| 14      | C8N      |         | -1024.8 |

| 15      | VDDy     |         | -784.8  |

| 16      | C7N      |         | -544.8  |

| 17      | Vss      |         | -304.8  |

| 18      | VEE      |         | -64.8   |

| 19      | C6N      |         | 175.2   |

| 20      | VEM      |         | 415.2   |

| 21      | C5N      |         | 655.2   |

| 22      | HC       | •       | 895.2   |

|         |          |         | e inter pun |

|---------|----------|---------|-------------|

| PAD No. | PAD name | Х       | Y           |

| 23      | C5P      | 1574.4  | 1135.2      |

| 24      | -V3B     | 1235.2  | 1554.4      |

| 25      | C1NB     | 995.2   |             |

| 26      | Vss      | 755.2   |             |

| 27      | C1PB     | 475.2   |             |

| 28      | Vdd      | 235.2   |             |

| 29      | C4N      | -4.8    |             |

| 30      | -V2      | -244.8  |             |

| 31      | C4P      | -484.8  |             |

| 32      | -V3      | -724.8  |             |

| 33      | Vss      | -964.8  |             |

| 34      | C1N      | -1204.8 |             |

| 35      | C2N      | -1444.8 | V           |

| 36      | -V3      | -1574.4 | 935.2       |

| 37      | C2P      |         | 655.2       |

| 38      | VDD      |         | 415.2       |

| 39      | C1P      |         | 175.2       |

| 40      | Vss      |         | -64.8       |

| 41      | C3N      |         | -304.8      |

| 42      | V2       |         | -544.8      |

| 43      | C3P      |         | -1024.8     |

| 44      | VDD      | V       | -1264.8     |

# **EPSON** International Sales Operations

#### AMERICA

# EPSON ELECTRONICS AMERICA, INC. HEADQUARTERS

1960 E. Grand Ave El Segundo, CA 90245, U.S.A. Phone : +1-310-955-5300 Fax : +1-310-955-5400

#### SALES OFFICES West

150 River Oaks Parkway San Jose, CA 95134, U.S.A. Phone : +1-408-922-0200 Fax : +1-408-922-0238

#### Central

1450 East American Lane Suite 1550 Schaumburg, IL 60173, U.S.A. Phone : +1-847-517-7667 Fax : +1-847-517-7601

101 Virginia Street, Suite 290 Crystal Lake, IL 60014, U.S.A. Phone : +1-815-455-7630 Fax : +1-815-455-7633

#### Northeast

301 Edgewater Place, Suite 120 Wakefield, MA 01880, U.S.A. Phone : +1-781-246-3600 Fax : +1-781-246-5443

#### Southeast

4300 Six Forks Road, Suite 430 Raleigh, NC 27609, U.S.A. Phone : +1-919-781-7667 Fax : +1-919-781-6778

1700 Spinnaker Drive Alptaretta, GA 30005, U.S.A. Phone : +1-770-754-4872 Fax : +1-770-753-0601

# EUROPE

#### EPSON EUROPE ELECTRONICS GmbH HEADQUARTERS

Riesstrasse 15 80992 Muenchen, GERMANY Phone : +49- (0) 89-14005-0 Fax : +49- (0) 89-14005-110

#### - GERMANY -SALES OFFICE

Breidenbachstrasse 46 D-51373 Leverkusen, GERMANY Phone : +49- (0) 214-83070-0 Fax : +49- (0) 214-83070-10

#### - UNITED KINGDOM -

UK BRANCH OFFICE G6 Doncastle House, Doncastle Road Bracknell, Berkshire RG12 8PE, ENGLAND Phone : +44- (0) 1344-381700 Fax : +44- (0) 1344-381701

#### - FRANCE -FRENCH BRANCH OFFICE

1 Avenue de l' Atlantique, LP 915 Les Conquerants Z.A. de Courtaboeuf 2, F-91976 Les Ulis Cedex, FRANCE Phone : +33- (0) 1-64862350 Fax : +33- (0) 1-64862355

## ASIA

- HONG KONG, CHINA -EPSON HONG KONG LTD. 20/F., Harbour Centre, 25 Harbour Road Wanchai, HONG KONG Phone : +852-2585-4600 Fax : +852-2827-4346 Telex : 65542 EPSCO HX

#### - CHINA -

SHANGHAI EPSON ELECTRONICS CO., LTD. 4F, Bldg., 27, No. 69, Gui Jing Road Caohejing, Shanghai, CHINA Phone : 21-6485-5552 Fax : 21-6485-0775

- TAIWAN, R.O.C. - **EPSON TAIWAN TECHNOLOGY & TRADING LTD.** 10F, No. 287,Nanking East Road, Sec. 3 Taipei, TAIWAN, R.O.C. Phone : 02-2717-7360 Fax : 02-2712-9164 Telex : 24444 EPSONTB

#### HSINCHU OFFICE

13F-3, No.295, Kuang-Fu Road, Sec. 2 HsinChu 300, TAIWAN, R.O.C. Phone : 03-573-9900 Fax : 03-573-9169

#### - SINGAPORE -

EPSON SINGAPORE PTE., LTD.

No. 1 Temasek Avenue, #36-00

Millenia Tower, SINGAPORE 039192

Phone : +65-337-7911

Fax : +65-334-2716

#### - KOREA -

## SEIKO EPSON CORPORATION KOREA OFFICE

10F, KLI 63 Bldg., 60 Yoido-Dong Youngdeungpo-Ku, Seoul, 150-010, KOREA Phone : 02-784-6027 Fax : 02-767-3677

- JAPAN -SEIKO EPSON CORPORATION ELECTRONIC DEVICES MARKETING DIVISION

Electronic Device Marketing Department IC Marketing & Engineering Group 421-8, Hino, Hino-shi, Tokyo 191-8501, JAPAN Phone: +81-(0)42-587-5816 Fax: +81-(0)42-587-5624

# ED International Marketing Department I

(Europe & U.S.A.) 421-8, Hino, Hino-shi, Tokyo 191-8501, JAPAN Phone: +81-(0)42-587-5812 Fax: +81-(0)42-587-5564

**ED International Marketing Department II (Asia)** 421-8, Hino, Hino-shi, Tokyo 191-8501, JAPAN Phone: +81-(0)42-587-5814 Fax: +81-(0)42-587-5110

In pursuit of **"Saving" Technology**, Epson electronic devices. Our lineup of semiconductors, liquid crystal displays and quartz devices assists in creating the products of our customers' dreams. **Epson IS energy savings**. **MLS Driver Chip Set**

# SEIKO EPSON CORPORATION

# ELECTRONIC DEVICES MARKETING DIVISION

Electronic Devices Information on Epson WWW Server

http://www.epson.co.jp

First issue Nov., 1997 Printed Oct., 1998 in Japan  $\bigoplus$  A