### **SCAN921821**

# Dual 18-Bit Serializer with Pre-emphasis, IEEE 1149.1 (JTAG), and At-Speed BIST

### **General Description**

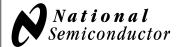

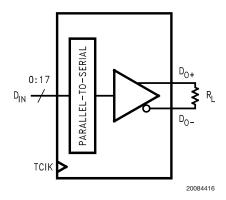

The SCAN921821 is a dual channel 18-bit serializer featuring signal conditioning, boundary SCAN, and at-speed BIST. Each serializer block transforms an 18-bit parallel LVCMOS/LVTTL data bus into a single Bus LVDS data stream with embedded clock. This single serial data stream with embedded clock simplifies PCB design and reduces PCB cost by narrowing data paths that in turn reduce PCB size and layers. The single serial data stream also reduces cable size, the number of connectors, and eliminates clock-to-data and data-to-data skew.

Each channel also has an 8-level selectable pre-emphasis feature that significantly extends performance over lossy interconnect. Each channel also has its own powerdown pin that saves power by reducing supply current when the channel is not being used.

The SCAN921821 also incorporates advanced testability features including IEEE 1149.1 and at-speed BIST PRBS pattern generation to facilitate verification of board and link integrity

#### **Features**

- 15-66 MHz Dual 18:1 Serializer with 2.376 Gbps total throughput

- 8-level selectable pre-emphasis on each channel drives lossy cables and backplanes

- >15kV HBM ESD protection on Bus LVDS I/O pins

- Robust BLVDS serial data transmission with embedded clock for exceptional noise immunity and low EMI

- Power saving control pin for each channel

- IEEE 1149.1 "JTAG" Compliant

- At-Speed BIST PRBS generation

- No external coding required

- Internal PLL, no external PLL components required

- Single +3.3V power supply

- Low power: 260 mW (typ) per channel at 66 MHz with PRBS-15 pattern

- Single 3.3 V supply

- Fabricated with advanced CMOS process technology

- Industrial -40 to +85°C temperature range

- Compact 100-ball FBGA package

### **Block Diagram**

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage  $(V_{DD})$  = -0.3V to +4V

Supply Voltage (V<sub>DD</sub>)

Ramp Rate < 30 V/ms

LVCMOS/LVTTL Input

Voltage -0.3V to  $(V_{DD} + 0.3V)$

LVCMOS/LVTTL Output

Voltage -0.3V to  $(V_{DD} + 0.3V)$

Bus LVDS Driver Output

Voltage -0.3V to +3.9V

Bus LVDS Output Short

Circuit Duration 10ms

Junction Temperature +150°C

Storage Temperature -65°C to +150°C

Lead Temperature

(Soldering, 4 seconds) +220°C

Maximum Package Power Dissipation at 25°C FBGA-100 3.57 W

Derating Above 25°C

Thermal resistance  $\theta_{JA}$   $\theta_{JC}$

ESD Rating

HBM, 1.5 K $\Omega$ , 100 pF

All pins 28.57 mW/°C

www.DataSheat  $\Omega$   $35^{\circ}\text{C/W}$   $11.1^{\circ}\text{C/W}$  28.57 mW/°C

www.DataSheat  $\Omega$   $35^{\circ}\text{C/W}$   $35^{\circ}\text{C/W}$

>15 kV

>1200 V

>2 kV

## Recommended Operating Conditions

Bus LVDS pins

CDM

MM, 0Ω, 200 pF

|                                                     | Min  | Nom | Max  | Units  |

|-----------------------------------------------------|------|-----|------|--------|

| Supply Voltage $(V_{DD})$                           | 3.15 | 3.3 | 3.45 | V      |

| Operating Free Air<br>Temperature (T <sub>A</sub> ) | -40  | +25 | +85  | °C     |

| Clock Rate                                          | 15   |     | 66   | MHz    |

| Supply Noise                                        |      |     | 100  | mV p-p |

#### **DC Electrical Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol           | Parameter                    | Conditions                                                            | Min  | Тур  | Max             | Units |

|------------------|------------------------------|-----------------------------------------------------------------------|------|------|-----------------|-------|

| LVCMOS/I         | VTTL Input DC Specifi        | ications                                                              | •    | •    | •               |       |

| V <sub>IH</sub>  | High Level Input<br>Voltage  |                                                                       | 2.0  |      | V <sub>DD</sub> | V     |

| V <sub>IL</sub>  | Low Level Input<br>Voltage   |                                                                       | GND  |      | 0.8             | V     |

| V <sub>CL</sub>  | Input Clamp Voltage          | I <sub>CL</sub> = -18 mA                                              | -1.5 | -0.7 |                 | V     |

| I <sub>INH</sub> | High Level Input<br>Current  | $V_{IN} = V_{DD} = V_{DDMAX}$                                         | -20  | ±2   | +20             | μΑ    |

| I <sub>INL</sub> | Low Level Output<br>Current  | $V_{IN} = V_{SS}, V_{DD} = V_{DDMAX}$                                 | -10  | ±2   | +10             | μА    |

| 1149.1 (JT       | AG) DC Specifications        |                                                                       |      |      |                 |       |

| V <sub>IH</sub>  | High Level Input<br>Voltage  |                                                                       | 2.0  |      | V <sub>DD</sub> | V     |

| V <sub>IL</sub>  | Low Level Input<br>Voltage   |                                                                       | GND  |      | 0.8             | V     |

| V <sub>CL</sub>  | Input Clamp Voltage          | I <sub>CL</sub> = -18 mA                                              | -1.5 | -0.7 |                 | V     |

| I <sub>INH</sub> | High Level Input<br>Current  | $V_{IN} = V_{DD} = V_{DDMAX}$                                         | -20  |      | +20             | μΑ    |

| I <sub>INL</sub> | Low Level Output<br>Current  | $V_{IN} = V_{SS}, V_{DD} = V_{DDMAX}$                                 | -200 |      | +200            | μΑ    |

| V <sub>OH</sub>  | High Level Output<br>Voltage | I <sub>OH</sub> = -9 mA                                               | 2.3  |      | V <sub>DD</sub> | mV    |

| $V_{OL}$         | Low Level Output<br>Voltage  | I <sub>OL</sub> = 9 mA                                                | GND  |      | 0.5             | mV    |

| I <sub>os</sub>  | Output Short Circuit Current | V <sub>OUT</sub> = 0 V                                                | -100 | -80  | -50             | mA    |

|                  | Output Tri-state             | $\overline{\text{PWDN}}$ or EN = 0.8V, $V_{\text{OUT}} = 0 \text{ V}$ | -10  |      | +10             | μΑ    |

| $I_{OZ}$         | Current                      | PWDN or EN = 0.8V, V <sub>OUT</sub> = VDD                             | -30  |      | +30             | μA    |

## DC Electrical Characteristics (Continued)

Over recommended operating supply and temperature ranges unless otherwise specified.

www.DataSheet4U.

| Symbol                                        | Parameter                                       | Conditions                                                                         |                                                          | Min  | Тур  | Max  | Units |

|-----------------------------------------------|-------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------|------|------|------|-------|

|                                               | 0.0.1.1.00.0                                    |                                                                                    |                                                          |      |      |      |       |

| sus LVD                                       | S Output DC Specificati                         | ons                                                                                | 1                                                        |      | 1    | 1    |       |

| $V_{OD}$                                      | Output Differential Voltage (DO+) - (DO-)       | Figure 10, $R_L = 100\Omega$                                                       |                                                          | 450  | 500  | 550  | mV    |

| $\Delta V_{OD}$                               | Output Differential Voltage Unbalance           |                                                                                    |                                                          |      | 2    | 15   | mV    |

| Vos                                           | Offset Voltage                                  |                                                                                    |                                                          | 1.05 | 1.2  | 1.25 | ٧     |

| $\Delta V_{OS}$                               | Offset Voltage<br>Unbalance                     |                                                                                    |                                                          |      | 2.7  | 15   | mV    |

|                                               |                                                 | Pre-Emph                                                                           | nasis Level = 1                                          | 1.10 | 1.24 | 1.35 |       |

|                                               |                                                 | Pre-Emph                                                                           | nasis Level = 2                                          | 1.35 | 1.47 | 1.55 |       |

|                                               | Pre-Emphasis Output                             | Pre-Emphasis Level = 3                                                             |                                                          | 1.55 | 1.70 | 1.80 |       |

| $Q_{POV}$                                     | Voltage Ratio                                   | Pre-Emphasis Level = 4                                                             |                                                          | 1.80 | 1.91 | 1.95 |       |

|                                               | V <sub>ODPRE</sub> / V <sub>OD</sub> I          | Pre-Emphasis Level = 5                                                             |                                                          | 1.95 | 2.08 | 2.20 |       |

|                                               |                                                 | Pre-Emphasis Level = 6                                                             |                                                          | 2.10 | 2.21 | 2.35 |       |

|                                               |                                                 | Pre-Emphasis Level = 7                                                             |                                                          | 2.15 | 2.30 | 2.50 |       |

| los                                           | Output Short Circuit Current                    | DO = 0V, Din = H, PWDN and EN = 2.4V                                               |                                                          | -10  | -25  | -75  | mA    |

|                                               | TRI-STATE Output                                | PWDN or EN = 0.8V, DO = 0V (Note 4)           PWDN or EN = 0.8V, DO = VDD (Note 4) |                                                          | -10  | ± 1  | +10  | μΑ    |

| $I_{OZ}$                                      | Current                                         |                                                                                    |                                                          | -55  | ± 6  | +55  | μΑ    |

| ower Su                                       | pply Current (DVDD, PV                          | /DD and AVDD Pins)                                                                 |                                                          |      | •    | •    |       |

|                                               | Total Cumply Current                            |                                                                                    | f = 66 MHz, PRBS-15<br>Pattern                           |      | 160  | 225  | mA    |

| Total Supply Current  (includes load current) | $C_L = 15pF,$ $R_L = 100 \Omega$                | f = 66 MHz, Worst  Case Pattern (Checker-Board  Pattern)                           |                                                          | 180  |      | mA   |       |

|                                               | Total Supply Current                            |                                                                                    | f = 66 MHz, PRBS-15<br>Pattern                           |      | 240  |      | mA    |

| I <sub>DDP</sub>                              | with Pre-Emphasis<br>(includes load<br>current) | $C_L = 15pF,$<br>$R_L = 100 \Omega$                                                | f = 66 MHz, Worst  Case Pattern (Checker-Board  Pattern) |      | 280  | 325  | mA    |

| I <sub>DDX</sub>                              | Supply Current<br>Powerdown                     | PWDN = 0.8V, EN = 0.8V                                                             |                                                          |      | 1.0  | 3.0  | mA    |

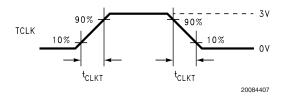

## **Timing Requirements for TCLK**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol            | Parameter           | Conditions | Min  | Тур  | Max  | Units    |

|-------------------|---------------------|------------|------|------|------|----------|

| +                 | Transmit Clock      |            | 15.2 | Т    | 66.7 | ns       |

| t <sub>TCP</sub>  | Period              |            | 13.2 | 1    | 00.7 | 115      |

| +                 | Transmit Clock High |            | 0.4T | 0.5T | 0.6T | ns       |

| t <sub>TCIH</sub> | Time                |            | 0.41 | 0.51 | 0.01 | 115      |

| Trar              | Transmit Clock Low  |            | 0.4T | 0.5T | 0.6T | ns       |

| t <sub>TCIL</sub> | Time                |            | 0.41 | 0.51 | 0.01 | 113      |

| +                 | TCLK Input          |            |      | 3    | 6    | ns       |

| t <sub>CLKT</sub> | Transition Time     |            |      | 3    | 0    | 115      |

| t <sub>JIT</sub>  | TCLK Input Jitter   | (Note 5)   |      |      | 80   | ps (RMS) |

|                   | •                   |            |      |      | •    | •        |

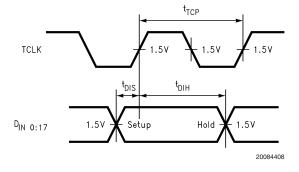

#### **AC Electrical Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.

www.DataSheet4U.com

| Symbol            | Parameter                                         | Conditions                                | Min                  | Тур                    | Max                   | Units    |

|-------------------|---------------------------------------------------|-------------------------------------------|----------------------|------------------------|-----------------------|----------|

|                   | AC Specifications                                 |                                           |                      | - 71                   | 1110111               |          |

|                   | Bus LVDS                                          |                                           |                      |                        |                       |          |

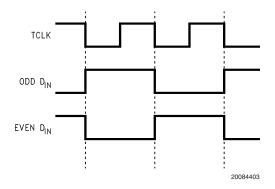

| t <sub>LLHT</sub> | Low-to-High                                       |                                           | 0.3                  | 0.4                    | ns                    |          |

|                   | Transition Time                                   | Figure 2, (Note 5)                        |                      |                        |                       |          |

|                   | Bus LVDS                                          | $R_L = 100\Omega$ ,                       |                      |                        |                       |          |

| t <sub>LHLT</sub> | High-to-Low                                       | C <sub>L</sub> =10pF to GND               |                      | 0.3                    | 0.4                   | ns       |

|                   | Transition Time                                   |                                           |                      |                        |                       |          |

| +                 | DIN (0-17) Setup to                               | Figure 4 (Note F)                         | 1.9                  |                        |                       | ne       |

| t <sub>DIS</sub>  | TCLK                                              | Figure 4, (Note 5) $R_{L} = 100\Omega,$   | 1.9                  |                        |                       | ns       |

| t <sub>DIH</sub>  | DIN (0-17) Hold from                              | $C_L = 10032$ ,<br>$C_L = 10$ F to GND    | 0.6                  |                        |                       | ns       |

| — ЧОН             | TCLK                                              | CL=TOPT to GITE                           | 0.0                  |                        |                       |          |

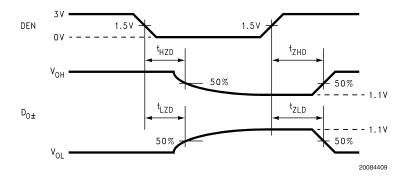

| t <sub>HZD</sub>  | DO ± HIGH to                                      |                                           |                      | 3.9                    | 10                    | ns       |

|                   | TRI-STATE Delay                                   |                                           |                      |                        |                       |          |

| t <sub>LZD</sub>  | DO ± LOW to                                       | Figure 5                                  |                      | 3.5                    | 10                    | ns       |

|                   | TRI-STATE Delay                                   | $R_1 = 100\Omega$ ,                       |                      |                        |                       |          |

| t <sub>zhD</sub>  | DO ± TRI-STATE to                                 | C <sub>L</sub> =10pF to GND               |                      | 3.2                    | 10                    | ns       |

|                   | DO ± TRI-STATE to                                 |                                           |                      |                        |                       |          |

| t <sub>ZLD</sub>  |                                                   |                                           | 2.4                  | 10                     | ns                    |          |

|                   | LOW Delay                                         |                                           |                      |                        |                       |          |

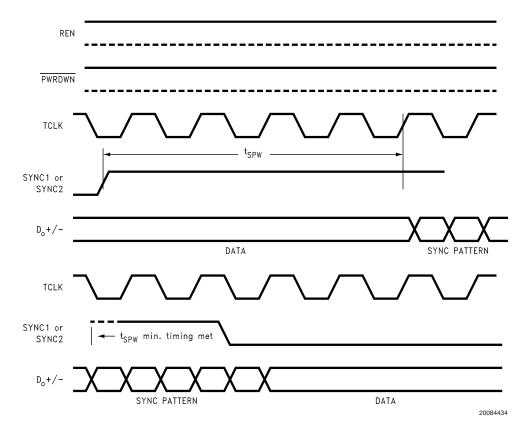

| t <sub>SPW</sub>  | SYNC Pulse Width                                  | Figure 7,                                 | 5*t <sub>TCP</sub>   |                        | 6*t <sub>TCP</sub>    | ns       |

|                   | $R_{L} = 100\Omega$ Serializer PLL Lock Figure 6, |                                           |                      |                        |                       |          |

| t <sub>PLD</sub>  | Time                                              | Figure 6, $R_L = 100\Omega$               | 510*t <sub>TCP</sub> |                        | 1024*t <sub>TCP</sub> | ns       |

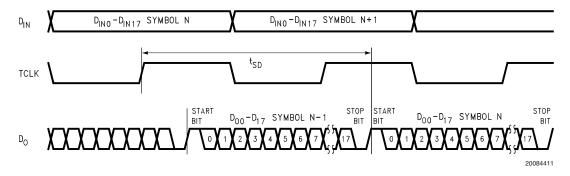

|                   | Serializer Delay                                  | Figure 8, $R_L = 100\Omega$               | t + 2.5              | t <sub>TCP</sub> + 4.5 | t + 6.5               | ns       |

| t <sub>SD</sub>   | Channel to Channel                                | 1 igaic 0 , 11 = 100s2                    | TCP + 2.5            | TCP + 4.0              | TCP + 0.0             | 110      |

| t <sub>skcc</sub> | Skew                                              |                                           |                      | 70                     |                       | ps       |

|                   |                                                   | Room Temperature, V <sub>DD</sub> = 3.3V, |                      |                        |                       | ps       |

| t <sub>RJIT</sub> | Random Jitter                                     | 66 MHz                                    |                      | 6.1                    |                       | (RMS)    |

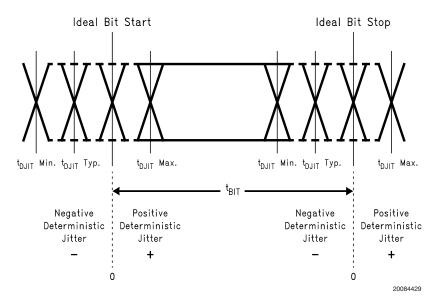

|                   | Deterministic Jitter                              | 15 MHz                                    | -390                 |                        | 320                   | ps       |

| t <sub>DJIT</sub> | Figure 9, (Note 5)                                | 66 MHz                                    | -60                  |                        | 30                    | ps       |

| 1149.1 (JT        | AG) AC Specification                              |                                           |                      |                        |                       | <u> </u> |

|                   | Maximum TCK Clock                                 |                                           |                      |                        |                       |          |

| f <sub>MAX</sub>  | Frequency                                         |                                           | 25                   |                        |                       | MHz      |

|                   | TDI or TMS Setup to                               |                                           | 0.4                  |                        |                       |          |

| t <sub>S</sub>    | TCK, H or L                                       |                                           | 2.4                  |                        |                       | ns       |

|                   | TDI or TMS Hold                                   | C <sub>L</sub> = 15pF,                    | 0.0                  |                        |                       |          |

| t <sub>H</sub>    | from TCK, H or L                                  |                                           | 2.8                  |                        |                       | ns       |

| _                 | TCK Pulse Width, H                                | $R_L = 500 \Omega$                        | 10                   |                        |                       | ne       |

| t <sub>W1</sub>   | or L                                              |                                           | 10                   |                        |                       | ns       |

| t <sub>W2</sub>   | TRST Pulse Width, L                               |                                           | 10                   |                        |                       | ns       |

| tees              | Recovery Time,                                    |                                           | 2                    |                        |                       | ns       |

| t <sub>REC</sub>  | TRST to TCK                                       |                                           | _                    |                        |                       | 110      |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" specifies conditions of device operation.

**Note 2:** Typical values are given for  $V_{CC} = 3.3V$  and  $T_A = +25^{\circ}C$ .

Note 3: Current into device pins is defined as positive. Current out of device pins is defined as negative. Voltages are referenced to ground except VOD,  $\Delta$ VOD, VTH and VTL which are differential voltages.

$<sup>\</sup>textbf{Note 4:} \quad I_{OZ} \text{ is measured at each pin. The DOUT pin not under test is floated to isolate the TRI-STATE current flow.}$

Note 5: Guaranteed by Design (GBD) using statistical analysis.

## **AC Timing Diagrams and Test Circuits**

www.DataSheet4U.

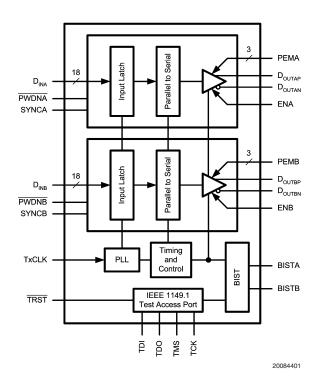

FIGURE 1. "Worst Case" Serializer IDD Test Pattern

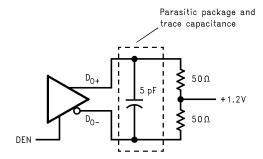

FIGURE 2. Serializer Bus LVDS Distributed Output Load and Transition Times

FIGURE 3. Serializer Input Clock Transition Time

FIGURE 4. Serializer Setup/Hold Times

## AC Timing Diagrams and Test Circuits (Continued)

www.DataSheet4U.com

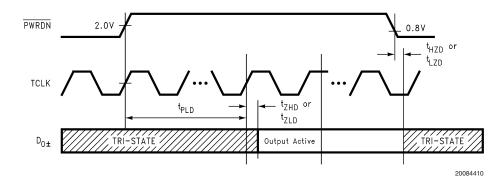

FIGURE 5. Serializer TRI-STATE Test Circuit and Timing

FIGURE 6. Serializer PLL Lock Time, and PWRDN TRI-STATE Delays

## AC Timing Diagrams and Test Circuits (Continued)

www.DataSheet4U

FIGURE 7. SYNC Timing Delay

FIGURE 8. Serializer Delay

## AC Timing Diagrams and Test Circuits (Continued)

www.DataSheet4U.com

FIGURE 9. Deterministic Jitter and Ideal Bit Position

$\mathsf{V}_\mathsf{OD} = (\mathsf{DO}^+) - (\mathsf{DO}^-).$

Differential output signal is shown as (DO+)-(DO-), device in Data Transfer mode.

FIGURE 10.  $V_{\rm OD}$  Diagram

## **Pre-emphasis Truth Table**

| PEM LEVEL | PEM2 | PEM1 | PEM0 |

|-----------|------|------|------|

| 0         | L    | L    | L    |

| 1         | L    | L    | Н    |

| 2         | L    | Н    | L    |

| 3         | L    | Н    | Н    |

| 4         | Н    | L    | L    |

| 5         | Н    | L    | Н    |

| 6         | Н    | Н    | L    |

| 7         | Н    | Н    | Н    |

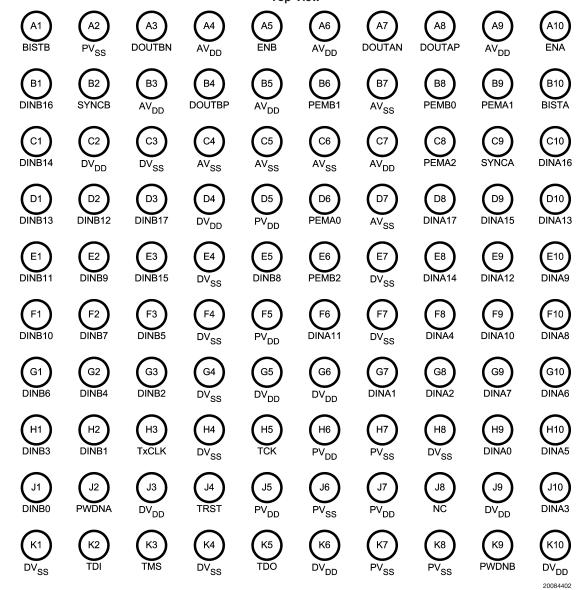

## Pin Diagram

www.DataSheet4U.

#### SCAN921821TVV Top View

#### **Pin Descriptions** www.DataSheet4U.com Pin Name Pin Count I/O, Type Description **DATA PINS** DINA0-17 18 Transmitter inputs. There is a pull-down circuitry on each of these pins which are I, LVCMOS active if respective PWDNA or PWDNB pin is pulled high. **DINB0-17** 18 **DOUTAP** 1 **DOUTAN** 1 O,BLVDS Inverting and non-inverting differential transmitter outputs. **DOUTBP** 1 **DOUTAN** 1 **TIMING AND CONTROL PINS** Transmitter reference clock. Used to strobe data at the inputs and to drive the **TxCLK** 1 I. LVCMOS transmitter PLL. There is a pull-up circuitry on this pin which is always active. Transmitter outputs enable pins. There is a pull-down circuitry on each of these **ENA** 1 pins that are active if corresponding PWDNA or PWDNB pin is pulled high. I, LVCMOS When these pins are set to LOW, the transmitter outputs will be disabled. The **ENB** 1 PLL will remain locked. Stand-by mode pins. There is a pull-down circuitry on each of these pins that are **PWDNA** 1 I, LVCMOS always active. When these pins are set to LOW, the transmitter will be put in low **PWDNB** 1 power mode and the PLL will lose lock. Transmitter synchronization pins. There is a pull-down circuitry on each of these **SYNCA** 1 pins that are active if corresponding PWDNA or PWDNB pin is pulled high. I, LVCMOS When these pins are set to HIGH, the transmitter will ignore incoming data and **SYNCB** 1 send SYNC patterns to provide a locking reference to receiver(s). **PRE-EMPHASIS PINS** PEMA0-2 8-level pre-emphasis selection pins. There is a pull-down circuitry on each of these pins which are active if corresponding $\overline{\text{PWDNA}}$ or $\overline{\text{PWDNB}}$ pin is pulled I, LVCMOS PEMB0-2 3 **JTAG PINS** TDI 1 I, LVCMOS Test Data Input to support IEEE 1149.1. There is a pull-up circuitry on this pin which is always active. TDO Test Data Output to support IEEE 1149.1. 1 O, LVCMOS TMS 1 I, LVCMOS Test Mode Select Input to support IEEE 1149.1. There is a pull-up circuitry on this pin which is always active. TCK 1 I, LVCMOS Test Clock Input to support IEEE 1149.1. There is no failsafe circuitry on this pin. **TRST** 1 I. LVCMOS Test Reset Input to support IEEE 1149.1. There is a pull-up circuitry on this pin which is always active. **BIST PINS BISTA** 1 I, LVCMOS BIST selection pins. These pins select which transmitter will generate a PRBS like data. There is a pull-down circuitry on these pins which are active if **BISTB** 1 corresponding PWDNA or PWDNB pin is pulled high. **POWER PINS** AVDD 6 I, POWER Power Supply for the LVDS circuitry. DVDD 8 I, POWER Power Supply for the digital circuitry. **PVDD** 5 Power Supply for the PLL and BG circuitry. I, POWER I, POWER **AVSS** 5 Ground reference for the LVDS circuitry. DVSS 10 I, POWER Ground reference for the digital circuitry. **PVSS** 5 I, POWER Ground reference for the PLL and BG circuitry. **OTHER PINS** NC 1 N/A Not connected.

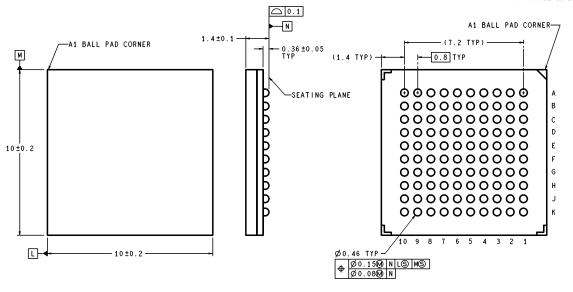

DIMENSIONS ARE IN MILLIMETERS

SLC100A (Rev B)

Dimensions shown in millimeters only Order Number SCAN921821TSM **NS Package Number SLC100A**

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### BANNED SUBSTANCE COMPLIANCE

National Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

National Semiconductor **Americas Customer** Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

**National Semiconductor Europe Customer Support Center** Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +44 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790

**National Semiconductor** Asia Pacific Customer Support Center Email: ap.support@nsc.com **National Semiconductor** Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560

IEEE 1149.1 (JTAG), and At-Speed BIST