# SC6820 Device Specification

Version 1.0 HW-SC6820--DS-0001 Dec 12, 2011 D1

Spreadtrum Communications, Inc., Confidential and Proprietary

# **IMPORTANT NOTICE**

#### **COPYRIGHT NOTICE**

Copyright © 2010, Spreadtrum Communications, Inc. All rights reserved.

#### **TRADEMARKS**

Spreadtrum Communications, Inc. and Spreadtrum Communications, Inc.'s products are exclusively owned by Spreadtrum Communications, Inc. References to other companies and their products use trademarks owned by the respective companies and are for reference purpose only.

#### WARRANTY DISCLAIMER

Spreadtrum Communications, Inc. makes no representations or warranties, either express or implied, by or with respect to anything in this document, and shall not be liable for any implied warranties of merchantability or fitness for a particular purpose or for any indirect, special or consequential damages.

#### **CONFIDENTIALITY**

The information contained herein (including any attachments) is confidential. The recipient hereby acknowledges the confidentiality of this document, and except for the specific purpose, this document shall not be disclosed to any third party.

# **Revision History**

| Version | Data       | Owner      | Note                    |

|---------|------------|------------|-------------------------|

| 0.8     | 10/26/2011 | Joey Jiang | First draft;            |

| 1.0     | 12/12/2011 | Joey Jiang | Update chapter 3,4,9,10 |

|         |            |            |                         |

|         |            |            |                         |

|         |            |            |                         |

|         |            |            |                         |

|         |            |            |                         |

|         |            |            |                         |

|         |            |            |                         |

|         |            |            |                         |

|         |            |            |                         |

|         |            |            |                         |

|         |            |            |                         |

|         |            |            |                         |

| REV | ISION | HISTORY.             |                                             | 3  |

|-----|-------|----------------------|---------------------------------------------|----|

| 1   | SYS   | TEM OVER             | RVIEW                                       | 11 |

|     | 1.1   | General              | Description                                 | 11 |

|     | 1.2   | SC6820               | Features                                    | 12 |

|     |       | 1.2.1                | General Features                            | 12 |

|     |       | 1.2.2                | Platform Features                           | 13 |

|     |       | 1.2.3                | Modem Features                              | 14 |

|     |       | 1.2.4                | Power Management Features                   | 15 |

|     |       | 1.2.5                | Multi-media Features                        | 15 |

|     | 1.3   | Application          | ons                                         | 16 |

|     | 1.4   | Chip Arc             | hitecture                                   | 18 |

| 2   | PAC   | KAGE INF             | FORMATION                                   | 19 |

|     | 2.1   | Top Mark             | king Definition                             | 19 |

|     | 2.2   | LFBGA F              | Pinout                                      | 20 |

|     | 2.3   | Package              | e Outline                                   | 21 |

|     | 2.4   | Reflow P             | Profile                                     | 23 |

| 3   | PIN   | INFORMA <sup>-</sup> | TION                                        | 24 |

|     |       | 3.1.1                | Pin symbol descriptions                     | 24 |

|     |       | 3.1.2                | Pin List                                    |    |

|     |       | 3.1.3                | Pin Multiplexed Function List               | 42 |

|     |       | 3.1.4                | Control Registers                           | 51 |

| 4   | ELE   | CTRICAL S            | SPECIFICATIONS                              | 62 |

|     | 4.1   |                      | cifications                                 |    |

|     |       | 4.1.1                | Absolute Maximum Ratings                    |    |

|     |       | 4.1.2                | Recommended Operating Conditions            |    |

|     |       | 4.1.3                | Thermal Characteristics                     |    |

|     |       | 4.1.4                | ESD Characteristics                         | 63 |

|     |       | 4.1.5                | DC Characteristics                          | 63 |

|     | 4.2   | AC Char              | acteristics                                 | 65 |

|     | 4.3   | Performa             | ance Specifications                         | 66 |

|     |       | 4.3.1                | GSM Baseband                                | 67 |

|     |       | 4.3.2                | Voice Band                                  | 68 |

|     |       | 4.3.3                | Phase-Locked Loop (PLL)                     | 75 |

|     |       | 4.3.4                | RTC Oscillator                              | 76 |

|     |       | 4.3.5                | USB 2.0 PHY                                 | 77 |

|     |       | 4.3.6                | GSM APC DAC                                 |    |

|     |       | 4.3.7                | Auxiliary Analog-to-Digital Converter (ADC) |    |

|     |       | 4.3.8                | Low Dropout Regulators                      | 78 |

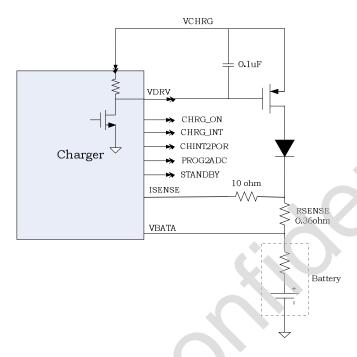

|     |       | 4.3.9                | Charger                                     |    |

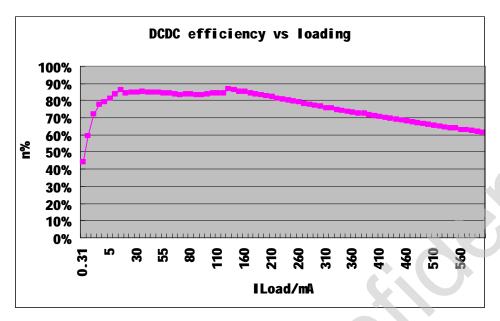

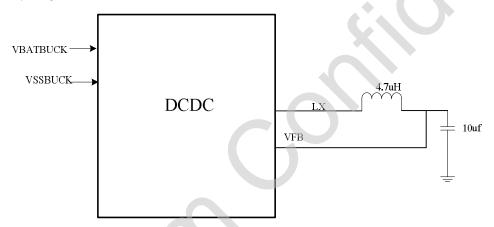

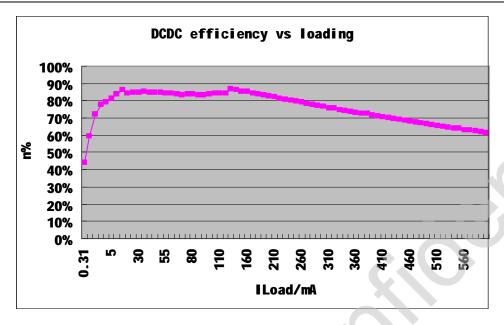

|     |       | 4.3.10               | DC-DC                                       | 92 |

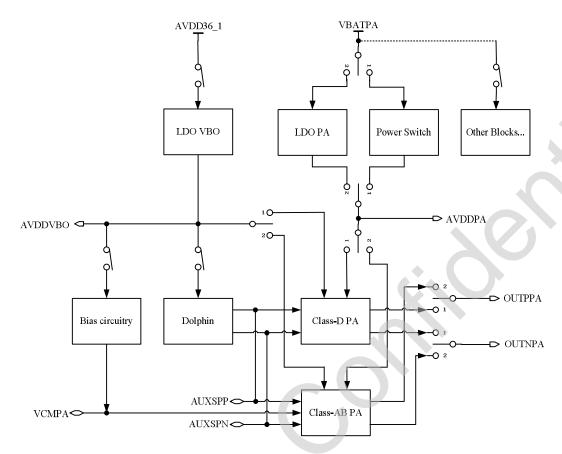

|     |       | 4.3.11               | Audio PA                                    |    |

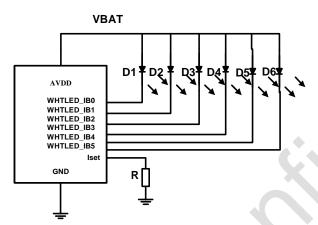

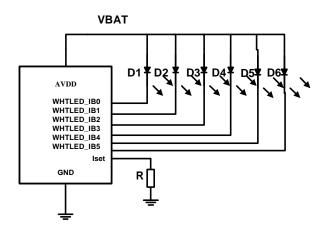

|     |       | 4.3.12               | LCD Backlight LED Driver                    |    |

|     |       | 4.3.13               | Keypad Backlight LED Driver                 |    |

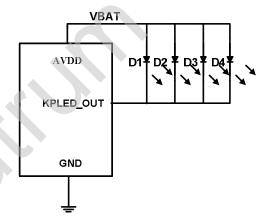

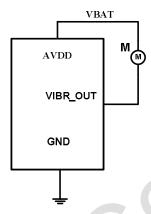

|     |       | 4.3.14               | Vibarator                                   | 99 |

| 5 | MICF | RO-CONTROI      | LLER UNIT SUBSYSTEM          | . 100                                                                                                                                                                                                                                                                                                                            |  |  |

|---|------|-----------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|   | 5.1  | Processor       |                              | . 100                                                                                                                                                                                                                                                                                                                            |  |  |

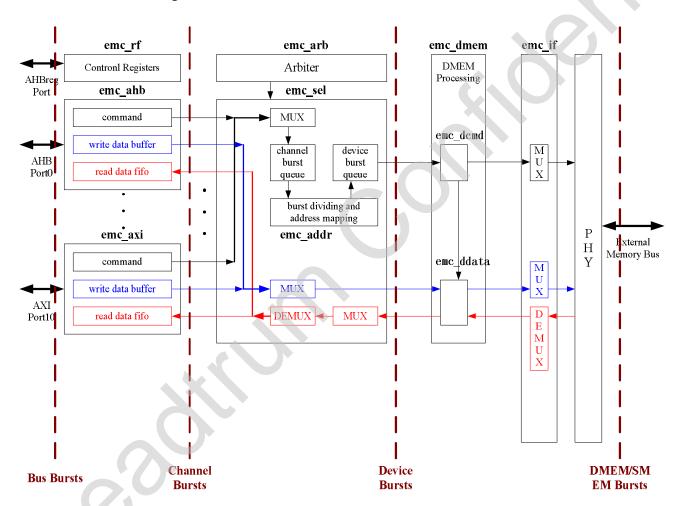

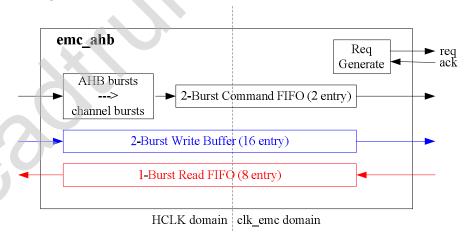

|   | 5.2  | External Me     | emory Controller             | . 105                                                                                                                                                                                                                                                                                                                            |  |  |

|   |      | 5.2.1           | Overview                     | . 105                                                                                                                                                                                                                                                                                                                            |  |  |

|   |      | 5.2.2           | Features                     | . 105                                                                                                                                                                                                                                                                                                                            |  |  |

|   |      | 5.2.3           | Signal Description           | . 107                                                                                                                                                                                                                                                                                                                            |  |  |

|   |      | 5.2.4           | Function Description         | . 109                                                                                                                                                                                                                                                                                                                            |  |  |

|   |      | 5.2.5           | Control Registers            | . 159                                                                                                                                                                                                                                                                                                                            |  |  |

|   |      | 5.2.6           | Application Notes            | . 190                                                                                                                                                                                                                                                                                                                            |  |  |

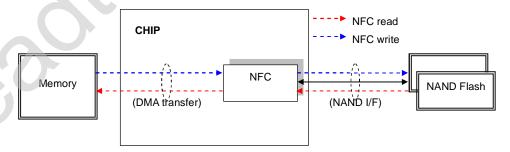

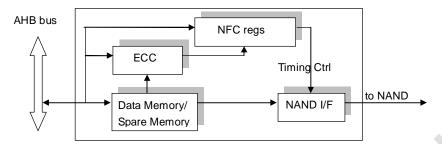

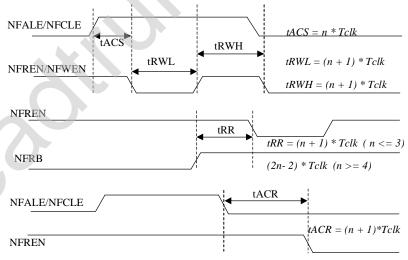

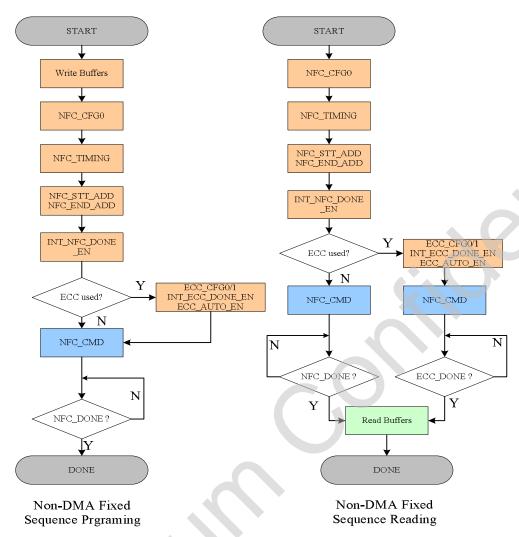

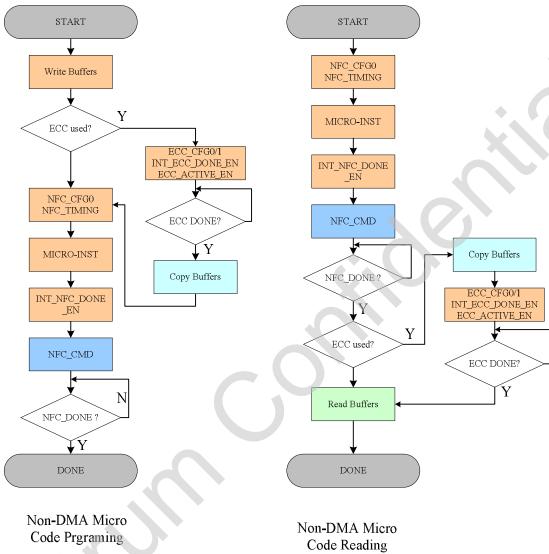

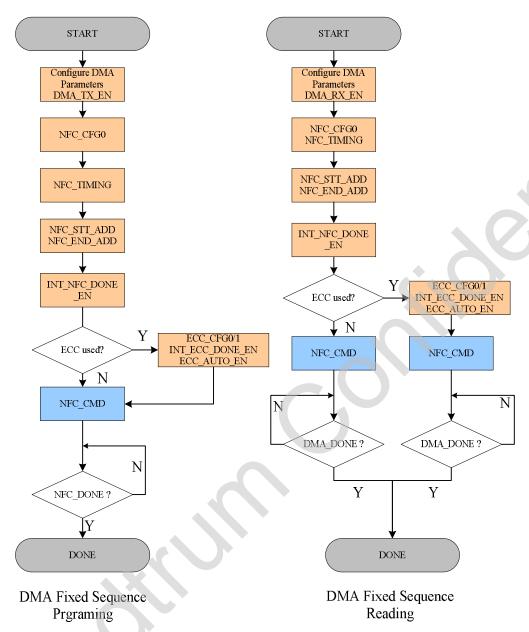

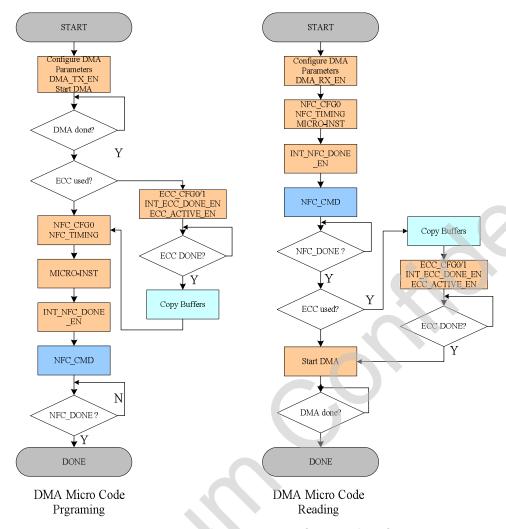

|   | 5.3  | NFC             |                              | . 211                                                                                                                                                                                                                                                                                                                            |  |  |

|   |      | 5.3.1           | Overview                     | . 211                                                                                                                                                                                                                                                                                                                            |  |  |

|   |      | 5.3.2           | Features                     | ~                                                                                                                                                                                                                                                                                                                                |  |  |

|   |      | 5.3.3           | Signal Description           |                                                                                                                                                                                                                                                                                                                                  |  |  |

|   |      | 5.3.4           | Function Description         |                                                                                                                                                                                                                                                                                                                                  |  |  |

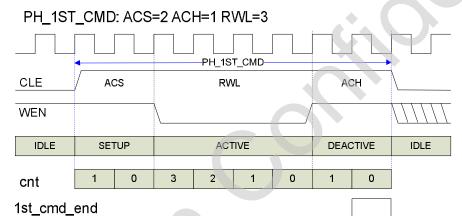

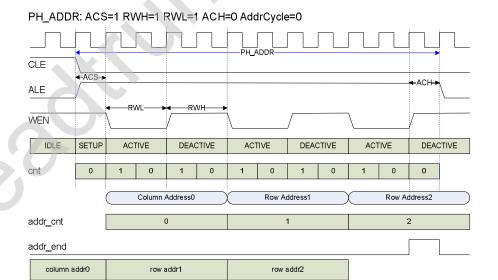

|   |      | 5.3.5           | Micro-Instruction            | . 217                                                                                                                                                                                                                                                                                                                            |  |  |

|   |      | 5.3.6           | Control Registers            | . 221                                                                                                                                                                                                                                                                                                                            |  |  |

|   |      | 5.3.7           | ECC                          |                                                                                                                                                                                                                                                                                                                                  |  |  |

|   |      | 5.3.8           | Application Notes            | . 241                                                                                                                                                                                                                                                                                                                            |  |  |

|   | 5.4  | DMA Contro      | oller                        | . 249                                                                                                                                                                                                                                                                                                                            |  |  |

|   |      | 5.4.1           | Overview                     | . 249                                                                                                                                                                                                                                                                                                                            |  |  |

|   |      | 5.4.2           | Features                     | . 249                                                                                                                                                                                                                                                                                                                            |  |  |

|   |      | 5.4.3           | Function Description         | . 250                                                                                                                                                                                                                                                                                                                            |  |  |

|   |      | 5.4.4           | DMA Logic Request Channels   | . 251                                                                                                                                                                                                                                                                                                                            |  |  |

|   |      | 5.4.5           | Control Registers            | . 252                                                                                                                                                                                                                                                                                                                            |  |  |

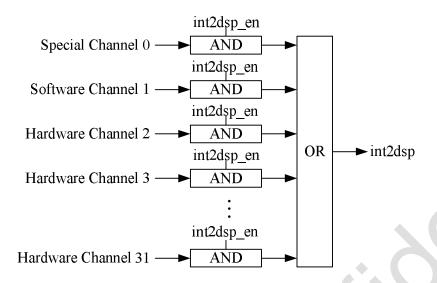

|   |      | 5.4.6           | Application Notes            | . 285                                                                                                                                                                                                                                                                                                                            |  |  |

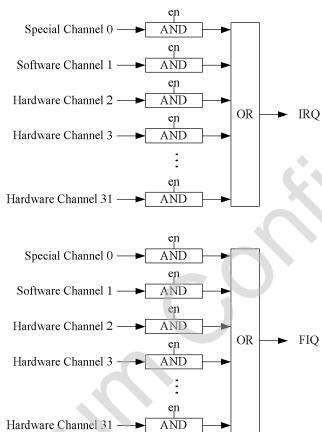

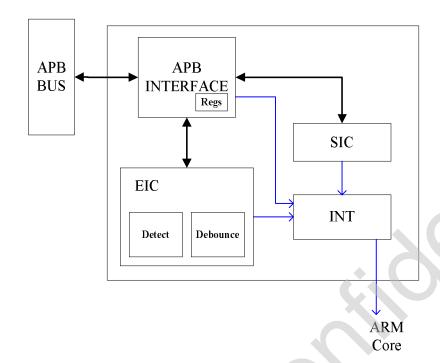

|   | 5.5  | MCU Interru     | upt Controller               | . 285                                                                                                                                                                                                                                                                                                                            |  |  |

|   |      | 5.5.1           | Overview                     | . 285                                                                                                                                                                                                                                                                                                                            |  |  |

|   |      | 5.5.2           | Features                     | . 285                                                                                                                                                                                                                                                                                                                            |  |  |

|   |      | 5.5.3           | Function Description         | . 285                                                                                                                                                                                                                                                                                                                            |  |  |

|   |      | 5.5.4           | Interrupt Channel Assignment | . 287                                                                                                                                                                                                                                                                                                                            |  |  |

|   |      | 5.5.5           | Control Registers            | . 105<br>. 105<br>. 107<br>. 109<br>. 159<br>. 190<br>. 211<br>. 211<br>. 212<br>. 217<br>. 221<br>. 240<br>. 241<br>. 249<br>. 249<br>. 250<br>. 251<br>. 285<br>. 285<br>. 285<br>. 285<br>. 285<br>. 285<br>. 287<br>. 297<br>. 297<br>. 297<br>. 298<br>. 298<br>. 306<br>. 306<br>. 306<br>. 307<br>. 313<br>. 313<br>. 313 |  |  |

|   |      | 5.5.6           | Application Notes            | . 297                                                                                                                                                                                                                                                                                                                            |  |  |

|   | 5.6  | AXI Bus Mo      | nitor                        | . 297                                                                                                                                                                                                                                                                                                                            |  |  |

|   |      | 5.6.1           | Overview                     | . 297                                                                                                                                                                                                                                                                                                                            |  |  |

|   |      | 5.6.2           | Features                     | . 297                                                                                                                                                                                                                                                                                                                            |  |  |

|   |      | 5.6.3           | Signal Description           | . 298                                                                                                                                                                                                                                                                                                                            |  |  |

|   |      | 5.6.4           | Function Description         | . 298                                                                                                                                                                                                                                                                                                                            |  |  |

|   |      | 5.6.5           | Control Registers            | . 298                                                                                                                                                                                                                                                                                                                            |  |  |

|   |      | 5.6.6           | Application Note             | . 306                                                                                                                                                                                                                                                                                                                            |  |  |

|   | 5.7  | AHB Bus Monitor |                              |                                                                                                                                                                                                                                                                                                                                  |  |  |

|   |      | 5.7.1           | Overview                     | . 306                                                                                                                                                                                                                                                                                                                            |  |  |

|   |      | 5.7.2           | Features                     | . 306                                                                                                                                                                                                                                                                                                                            |  |  |

|   |      | 5.7.3           | Bus Monitor Assignment       | . 307                                                                                                                                                                                                                                                                                                                            |  |  |

|   |      | 5.7.4           | Control Registers            |                                                                                                                                                                                                                                                                                                                                  |  |  |

| 5 | 5.8  | RTC Timer.      |                              |                                                                                                                                                                                                                                                                                                                                  |  |  |

|   |      | 5.8.1           | Overview                     |                                                                                                                                                                                                                                                                                                                                  |  |  |

|   |      | 5.8.2           | Features                     | . 313                                                                                                                                                                                                                                                                                                                            |  |  |

|   |      | 5.8.3           | Signal Description           |                                                                                                                                                                                                                                                                                                                                  |  |  |

|   |      |                 |                              |                                                                                                                                                                                                                                                                                                                                  |  |  |

|   |      | 5.8.4       | Function Description | . 314 |

|---|------|-------------|----------------------|-------|

|   |      | 5.8.5       | Control Registers    | . 314 |

|   |      | 5.8.6       | Application Notes    | . 329 |

|   | 5.9  | General Pur | pose Timer           | . 330 |

|   |      | 5.9.1       | Overview             | . 330 |

|   |      | 5.9.2       | Features             | . 330 |

|   |      | 5.9.3       | Signal Description   | . 330 |

|   |      | 5.9.4       | Function Description | .330  |

|   |      | 5.9.5       | Control Registers    | . 331 |

|   |      | 5.9.6       | Application Notes    | . 340 |

|   | 5.10 | Watch       | hdog Timer           | . 341 |

|   |      | 5.10.1      | Overview             | .341  |

|   |      | 5.10.2      | Features             | . 342 |

|   |      | 5.10.3      | Signal Description   |       |

|   |      | 5.10.4      | Function Description | . 342 |

|   |      | 5.10.5      | Control Registers    | . 342 |

|   |      | 5.10.6      | Application Notes    | . 349 |

|   | 5.11 | Syste       | m Timer              | . 350 |

|   |      | 5.11.1      | Overview             | . 350 |

|   |      | 5.11.2      | Features             | . 350 |

|   |      | 5.11.3      | Signal Description   | . 350 |

|   |      | 5.11.4      | Function Description | . 350 |

|   |      | 5.11.5      | Control Registers    | . 351 |

|   |      | 5.11.6      | Application Notes    | . 353 |

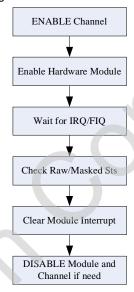

|   | 5.12 | MCU         | JTAG Interface       | . 353 |

|   |      | 5.12.1      | JTAG Timing          | . 354 |

| 6 | MICR | O-CONTROL   | LER UNIT PERIPHERALS | . 355 |

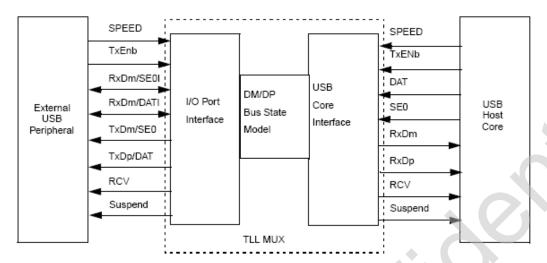

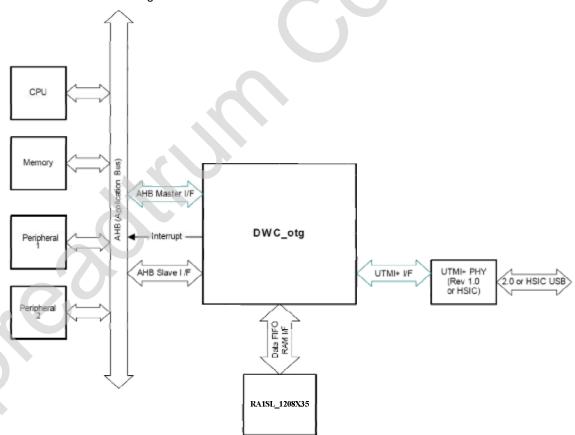

|   | 6.1  | USB Device  | Interface            | . 355 |

|   |      | 6.1.1       | Overview             | . 355 |

|   |      | 6.1.2       | Features             | . 355 |

|   |      | 6.1.3       | Signal Description   | . 356 |

|   |      | 6.1.4       | Function Description |       |

|   |      | 6.1.5       | Control Registers    | . 358 |

|   |      | 6.1.6       | Application Notes    | . 411 |

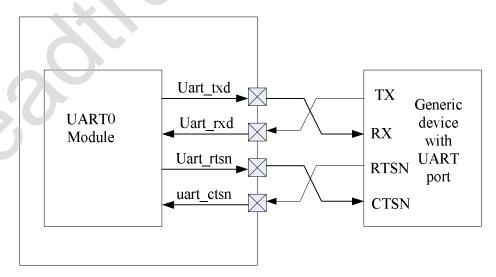

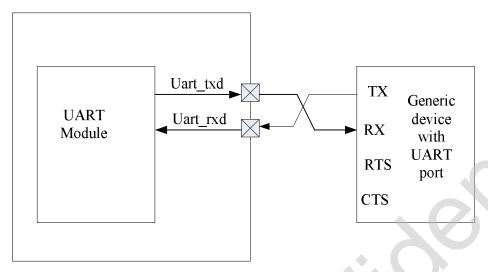

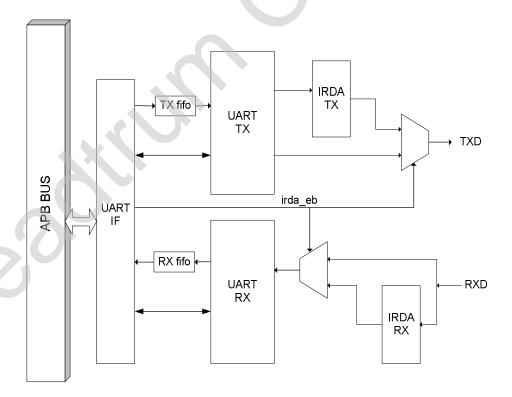

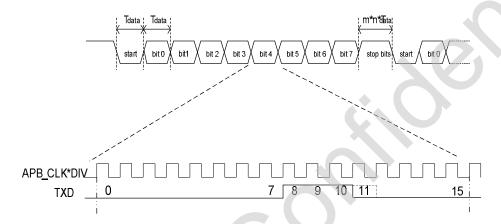

|   | 6.2  | UART and I  | rDA interface        | . 413 |

|   |      | 6.2.1       | Overview             | . 413 |

|   |      | 6.2.2       | Features             | . 413 |

|   |      | 6.2.3       | Signal Description   | .414  |

|   |      | 6.2.4       | Function Description |       |

|   |      | 6.2.5       | Control Registers    |       |

|   |      | 6.2.6       | Application Notes    |       |

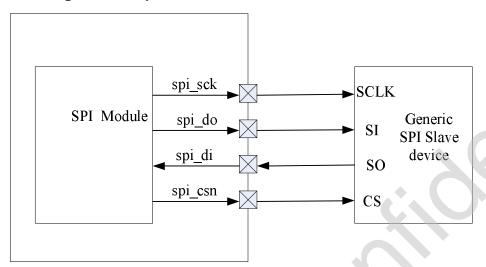

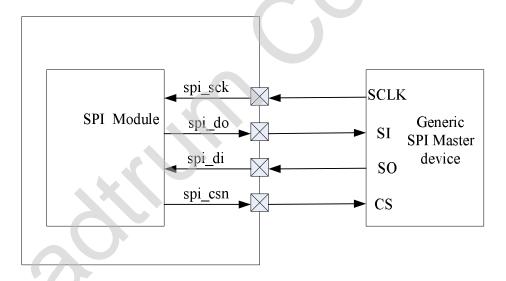

|   | 6.3  |             | e                    |       |

|   |      | 6.3.1       | Overview             |       |

|   |      | 6.3.2       | Features             |       |

|   |      | 6.3.3       | Signal Description   |       |

|   |      | 6.3.4       | Function Description |       |

|   |      | 6.3.5       | Control Registers    |       |

|   |      | 6.3.6       | Application Notes    |       |

|   |      |             | • •                  |       |

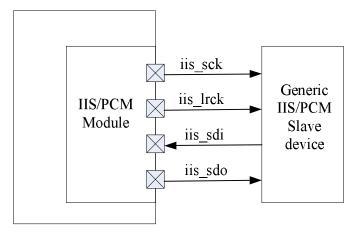

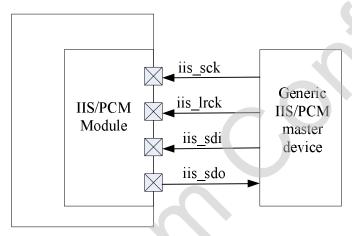

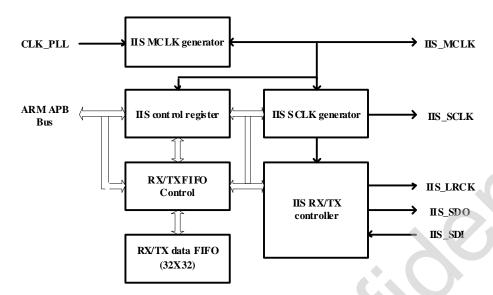

| 6.4  | IIS and PCM   | 1 Interface          | 452   |

|------|---------------|----------------------|-------|

|      | 6.4.1         | Overview             | 452   |

|      | 6.4.2         | Features             | 452   |

|      | 6.4.3         | Signal Description   | 452   |

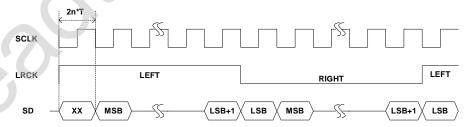

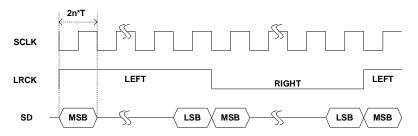

|      | 6.4.4         | Function Description | 453   |

|      | 6.4.5         | Control Registers    | 458   |

|      | 6.4.6         | Application Notes    | 471   |

| 6.5  | I2C Interface | 9                    | 472   |

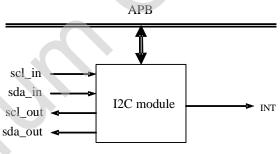

|      | 6.5.1         | Overview             | 472   |

|      | 6.5.2         | Features             | 472   |

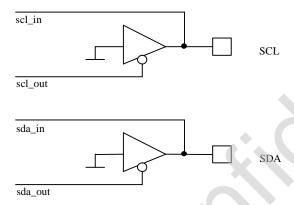

|      | 6.5.3         | Signal Description   | . 473 |

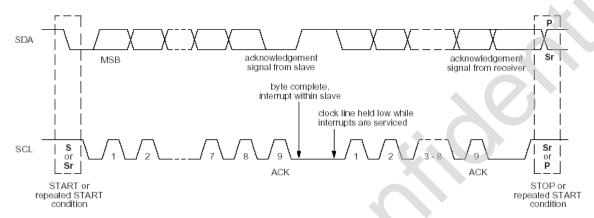

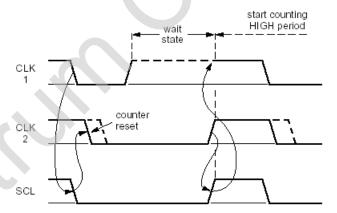

|      | 6.5.4         | Function Description | 473   |

|      | 6.5.5         | Control Registers    | 475   |

|      | 6.5.6         | Application Notes    |       |

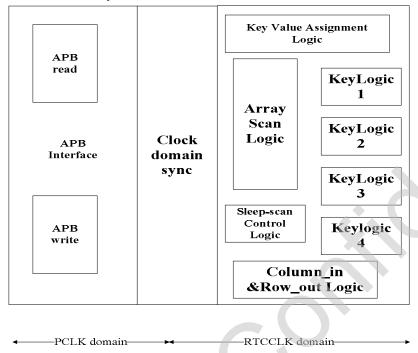

| 6.6  | Keypad Inter  | rface                | 480   |

|      | 6.6.1         | Overview             | 480   |

|      | 6.6.2         | Features             | 481   |

|      | 6.6.3         | Signal Description   | 481   |

|      | 6.6.4         | Function Description |       |

|      | 6.6.5         | Control Registers    | 483   |

|      | 6.6.6         | Application Notes    | 498   |

|      | 6.6.7         | Clock enable         | 498   |

|      | 6.6.8         | KPD configuration    | 498   |

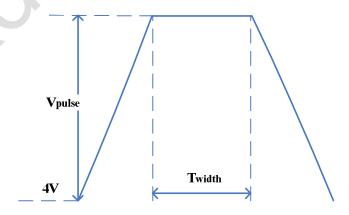

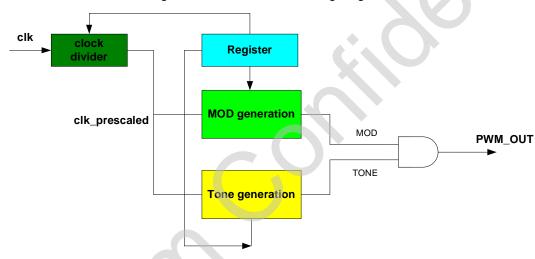

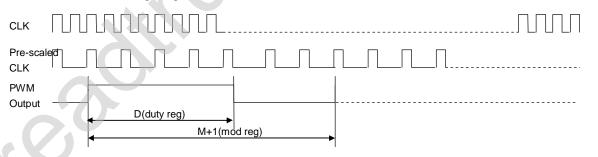

| 6.7  | Pulse Width   | Modulation(PWM)      |       |

|      | 6.7.1         | Overview             | 498   |

|      | 6.7.2         | Features             | 498   |

|      | 6.7.3         | Signal Description   | 498   |

|      | 6.7.4         | Function Description |       |

|      | 6.7.5         | Control Registers    | 500   |

|      | 6.7.6         | Application Notes    | 503   |

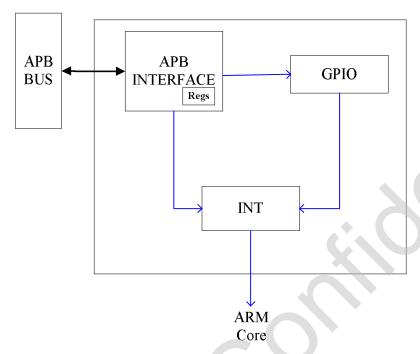

| 6.8  | GPIO          |                      | 504   |

|      | 6.8.1         | Overview             | 504   |

|      | 6.8.2         | Features             | 504   |

|      | 6.8.3         | Function Description | 505   |

|      | 6.8.4         | Control Registers    | 505   |

|      | 6.8.5         | Application Notes    | 512   |

| 6.9  | EIC           |                      |       |

|      | 6.9.1         | Overview             | 512   |

|      | 6.9.2         | Features             | 513   |

|      | 6.9.3         | Function Description | 513   |

|      | 6.9.4         | Control Registers    |       |

|      | 6.9.5         | Application Notes    | 532   |

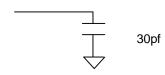

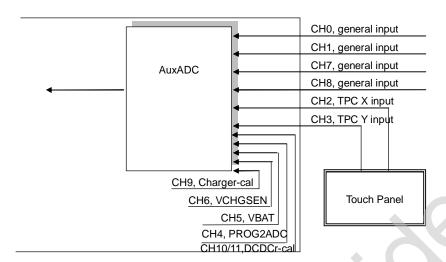

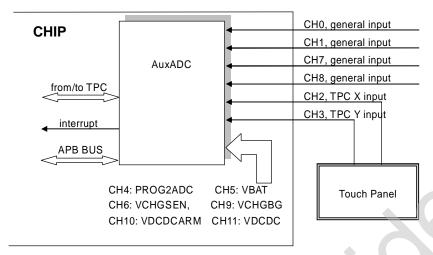

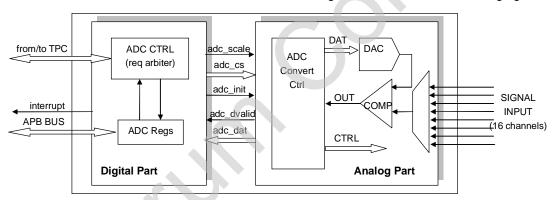

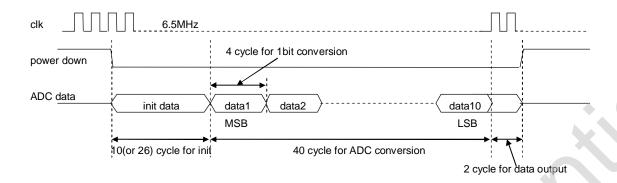

| 6.10 | Auxilia       | ary ADC              | 532   |

|      | 6.10.1        | Overview             |       |

|      | 6.10.2        | Features             | 533   |

|      | 6.10.3        | Signal Description   | 533   |

|      | 6.10.4        | Function Description |       |

|      | 6.10.5        | Control Registers    |       |

|      |               |                      |       |

|       | 6.10.6      | Application Notes         | . 540 |

|-------|-------------|---------------------------|-------|

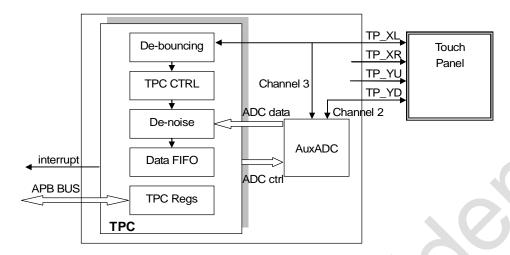

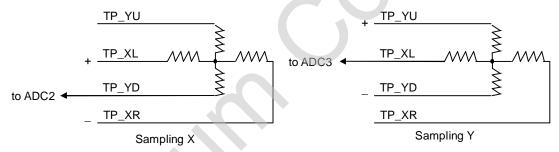

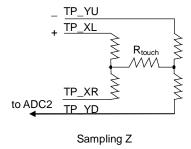

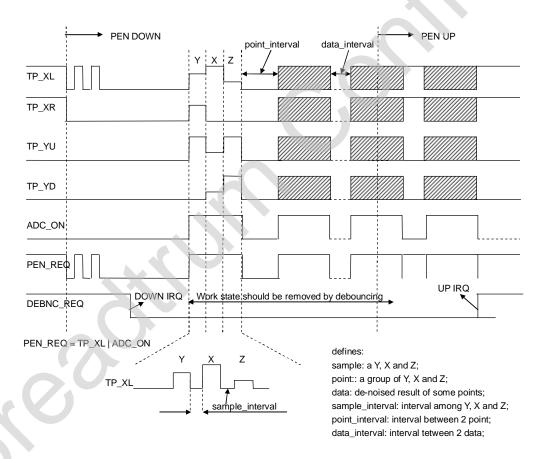

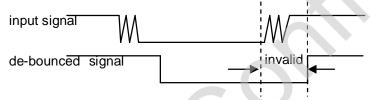

| 6.11  | Touch       | n Pannel Controller (TPC) | . 541 |

|       | 6.11.1      | Overview                  | . 541 |

|       | 6.11.2      | Features                  | . 541 |

|       | 6.11.3      | Signal Description        | . 542 |

|       | 6.11.4      | Function Description      | . 542 |

|       | 6.11.5      | Control Registers         | . 545 |

|       | 6.11.6      | Application Notes         | . 555 |

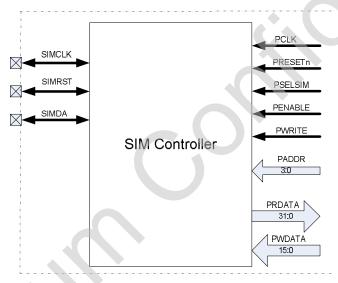

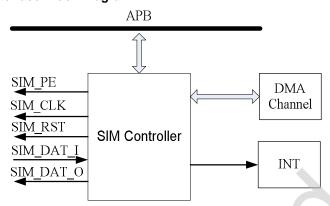

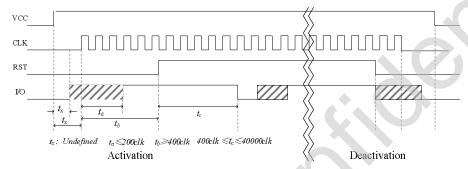

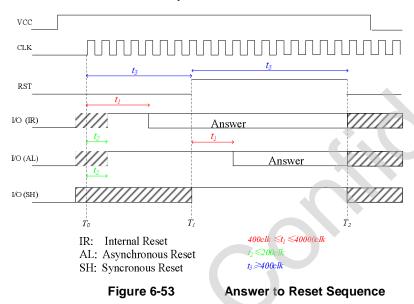

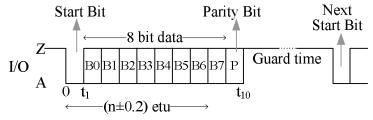

| 6.12  | SIM (       | Card Interface            | 556   |

|       | 6.12.1      | Overview                  | . 556 |

|       | 6.12.2      | Features                  | 556   |

|       | 6.12.3      | Signal Description        | .557  |

|       | 6.12.4      | Function Description      | . 558 |

|       | 6.12.5      | Control Registers         |       |

|       | 6.12.6      | Application Notes         | . 575 |

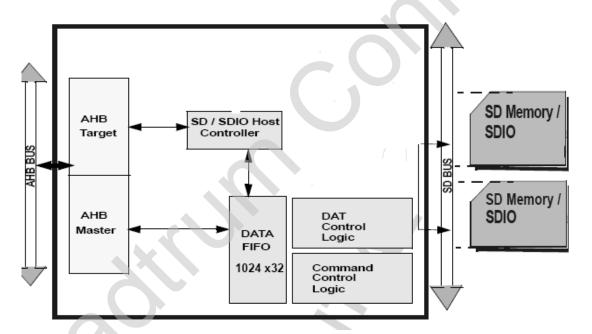

| 6.13  | SDIO        | Host Controller           | . 576 |

|       | 6.13.1      | Overview                  |       |

|       | 6.13.2      | Features                  | . 576 |

|       | 6.13.3      | Signal Description        | . 576 |

|       | 6.13.4      | Function Description      |       |

|       | 6.13.5      | Control Registers         | . 578 |

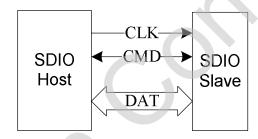

| 6.14  | SDIO        | slave Controller          | 606   |

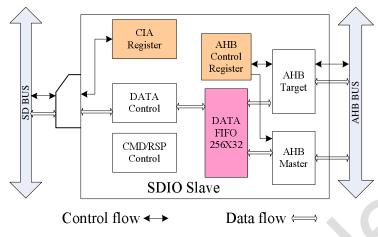

|       | 6.14.1      | Overview                  | 606   |

|       | 6.14.2      | Features                  | 606   |

|       | 6.14.3      | Signal Description        | . 607 |

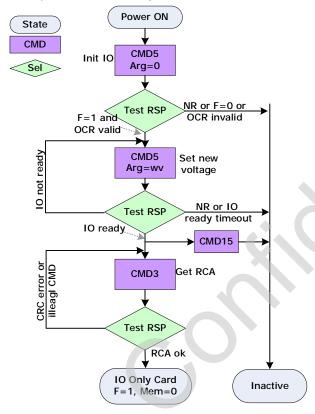

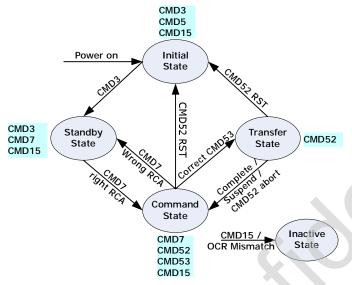

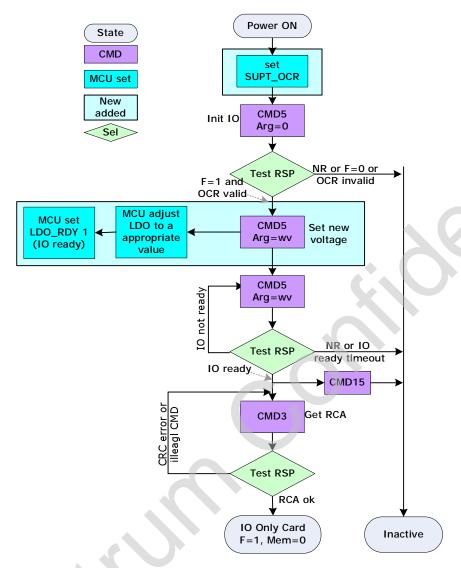

|       | 6.14.4      | Function Description      | . 607 |

|       | 6.14.5      | Control Registers         | 614   |

|       | 6.14.6      | Application Notes         | 642   |

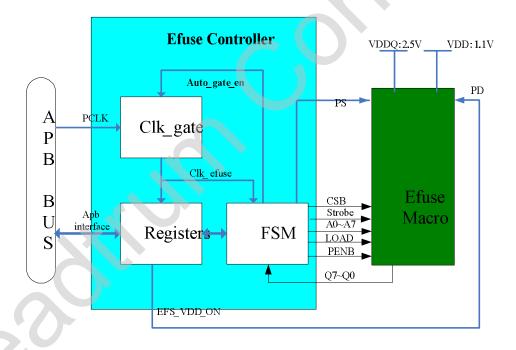

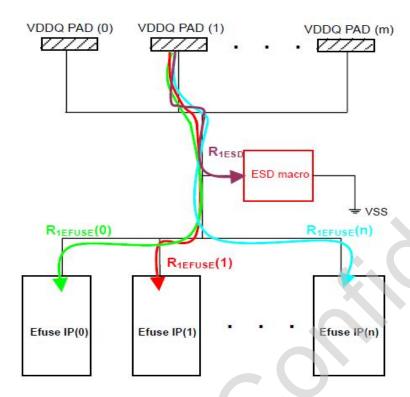

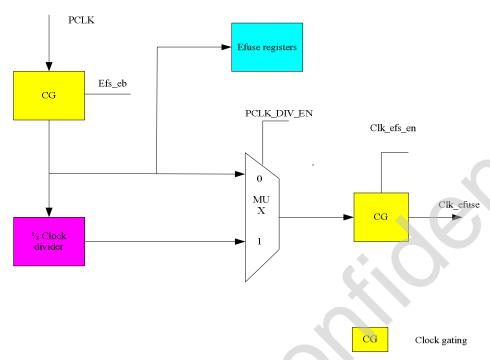

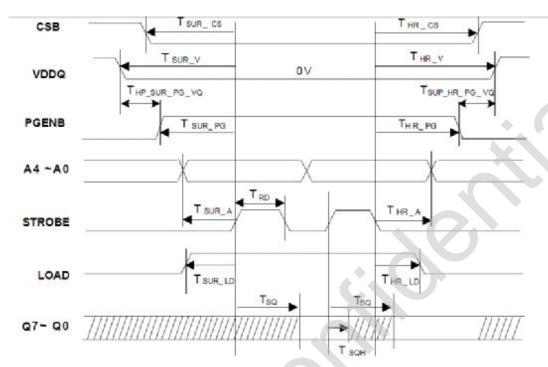

| 6.15  | Efuse       |                           | 644   |

|       | 6.15.1      | Overview                  | . 644 |

|       | 6.15.2      | Features                  |       |

|       | 6.15.3      | Signal Description        | . 645 |

|       | 6.15.4      | Function Description      | 645   |

|       | 6.15.5      | Control Registers         | 646   |

|       | 6.15.6      | Application Notes         | 657   |

| MUL,1 | ΓΙ-MEDIA SU | BSYSTEM                   | . 663 |

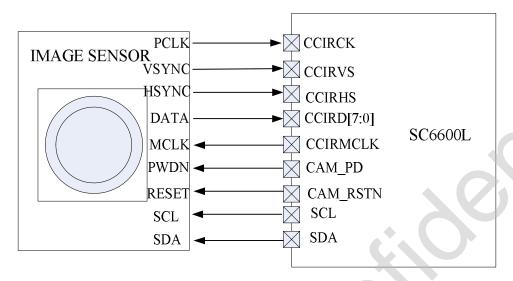

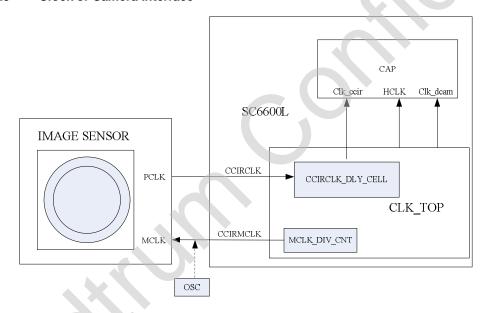

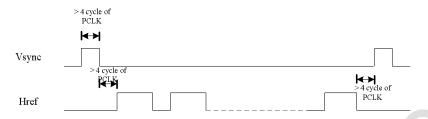

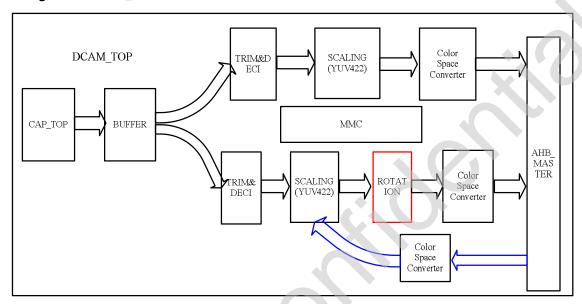

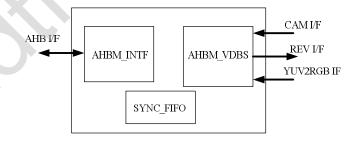

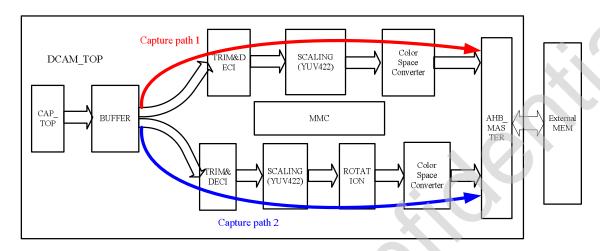

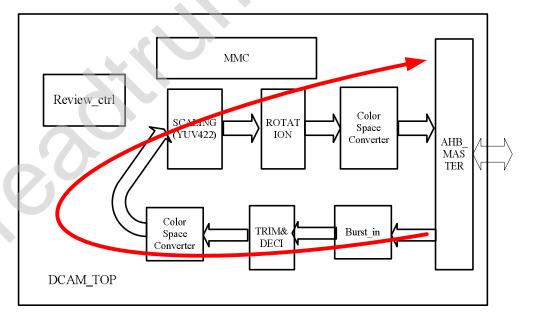

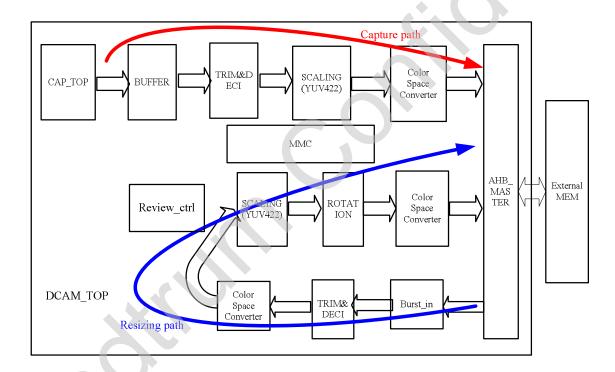

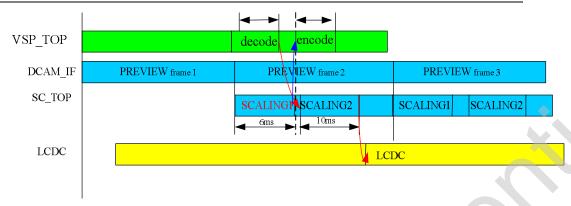

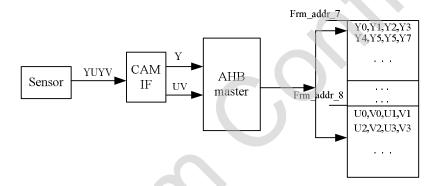

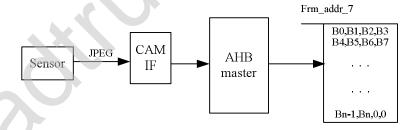

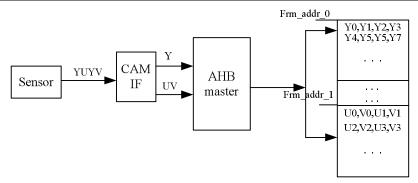

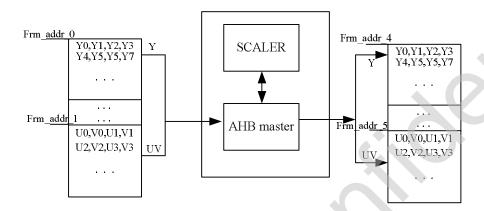

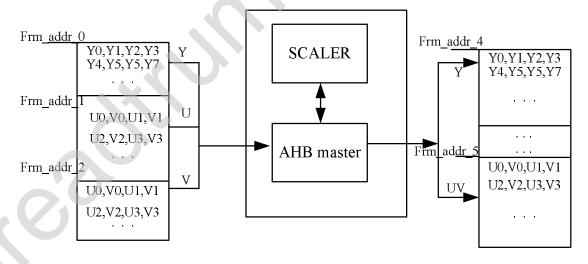

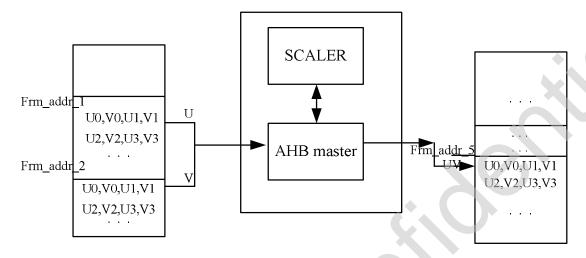

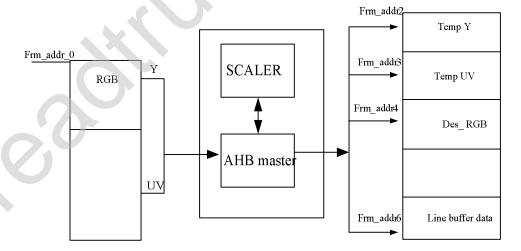

| 7.1   | Dcam        |                           | 663   |

|       | 7.1.1       | Overview                  | 663   |

|       | 7.1.2       | Features                  | 663   |

|       | 7.1.3       | Signal Description        | . 664 |

|       | 7.1.4       | Function Description      | 669   |

|       | 7.1.5       | Control Registers         | 674   |

|       | 7.1.6       | Application Notes         | .719  |

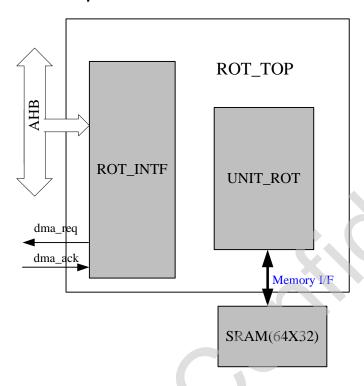

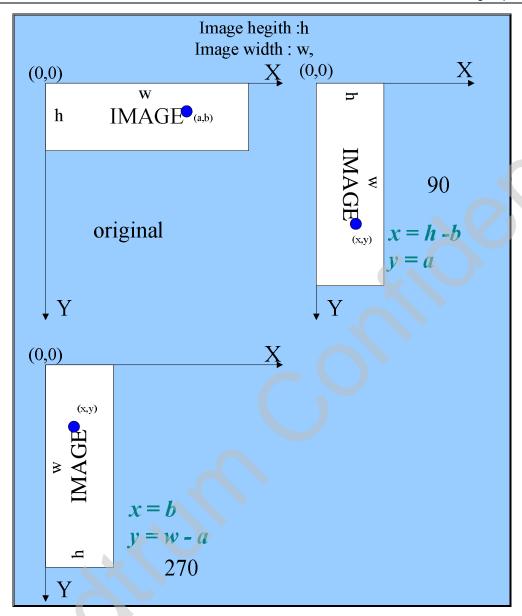

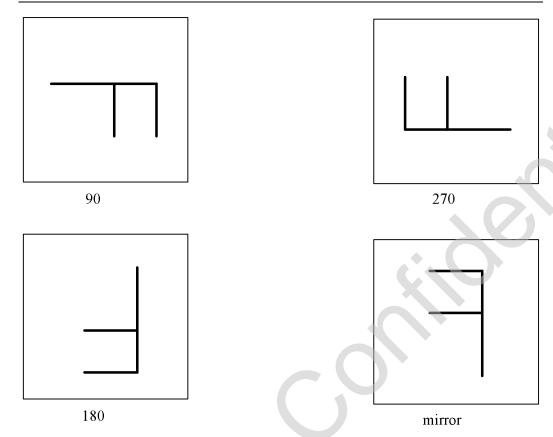

| 7.2   | Rotation    |                           | . 726 |

|       | 7.2.1       | Overview                  | .726  |

|       | 7.2.2       | Features                  | . 726 |

|       | 7.2.3       | Signal Description        | . 726 |

|       | 7.2.4       | Function Description      | . 727 |

|   |       | 7.2.5    | Control Registers                 | 730 |

|---|-------|----------|-----------------------------------|-----|

|   |       | 7.2.6    | Application Notes                 | 743 |

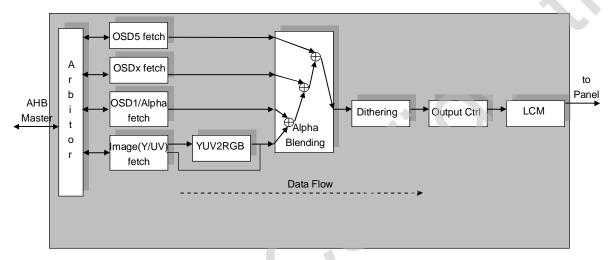

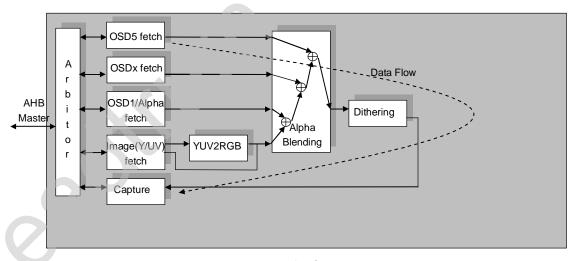

|   | 7.3   | LCDC     |                                   | 743 |

|   |       | 7.3.1    | Overview                          | 743 |

|   |       | 7.3.2    | Features                          | 743 |

|   |       | 7.3.3    | Signal Description                | 746 |

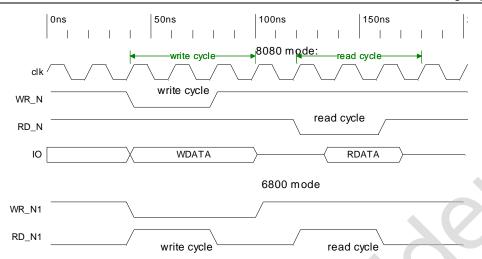

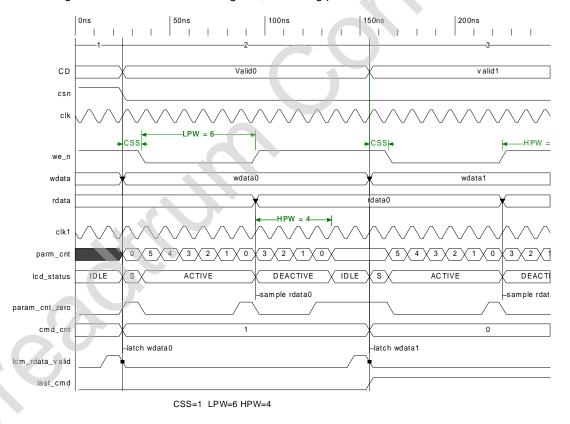

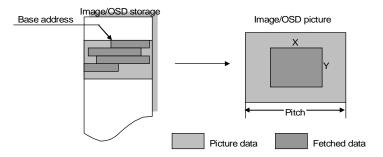

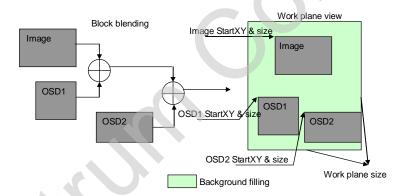

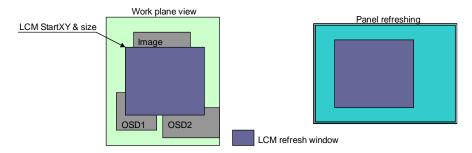

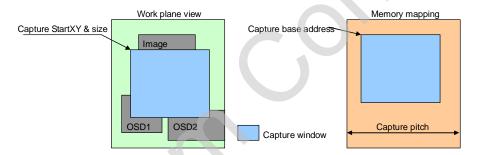

|   |       | 7.3.4    | Function Description              |     |

|   |       | 7.3.5    | Control Registers                 | 756 |

|   |       | 7.3.6    | Application Notes                 |     |

|   | 7.4   | Graphics |                                   |     |

|   |       | 7.4.1    | Overview                          |     |

|   |       | 7.4.2    | Pixel processor features          | 801 |

|   |       | 7.4.3    | Geometry processor features       |     |

|   |       | 7.4.4    | Level 2 cache controller features |     |

|   |       | 7.4.5    | MMU                               |     |

|   |       | 7.4.6    | PMU                               |     |

|   | ALIDI |          | EM                                |     |

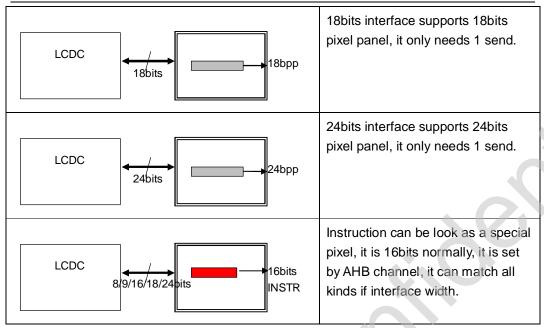

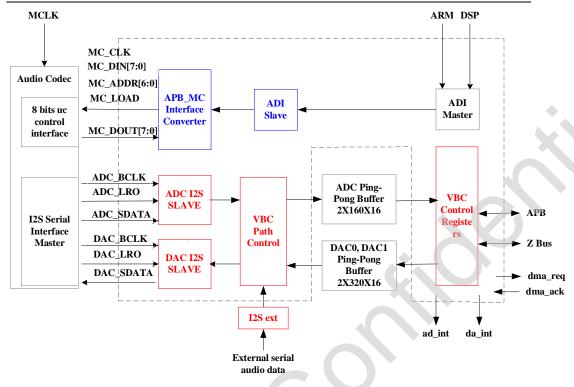

| 8 | 8.1   |          | EW                                |     |

|   | 8.2   |          |                                   |     |

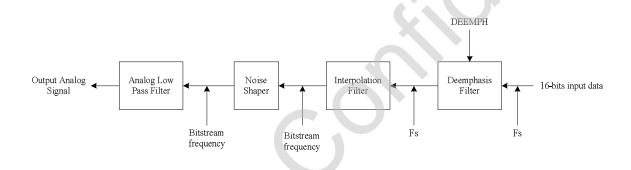

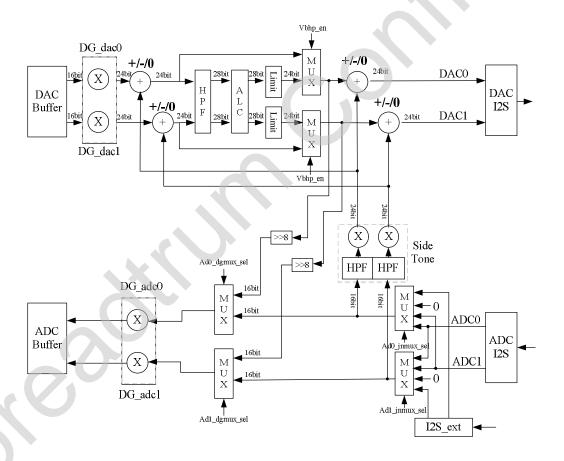

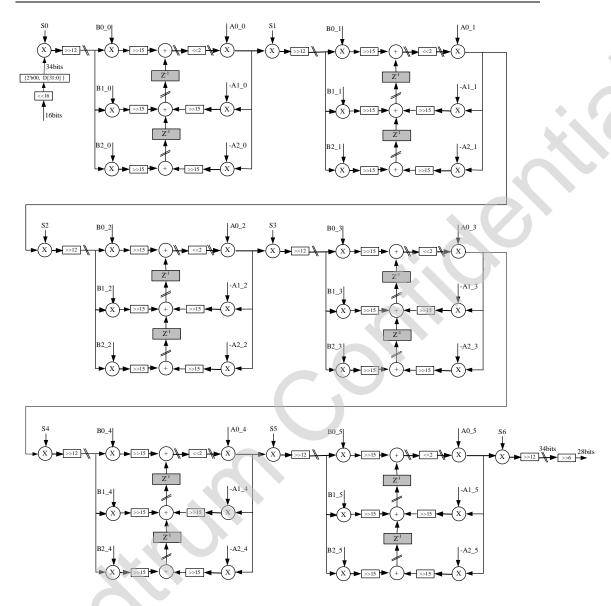

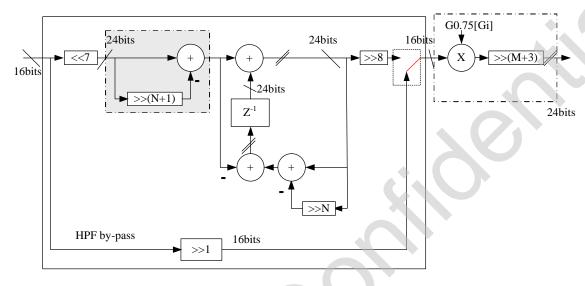

|   | _     |          | c Path Details                    |     |

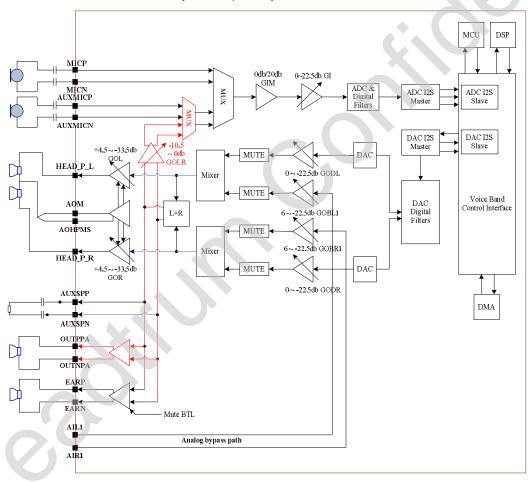

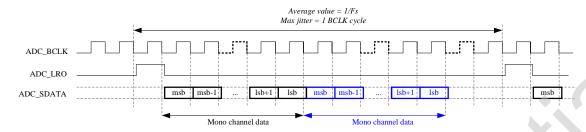

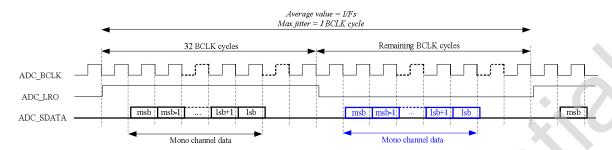

|   | 8.3   | 8.3.1    | ADC Path                          |     |

|   |       |          |                                   |     |

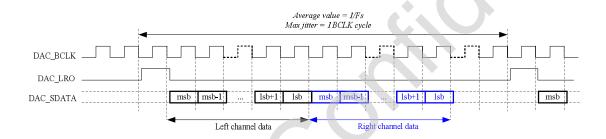

|   |       | 8.3.2    | DAC Path                          |     |

|   |       | 8.3.3    | Analog Line-in Path               |     |

|   |       | 8.3.4    | Mixer Path                        |     |

|   | 0.4   | 8.3.5    | Output Branch Description         |     |

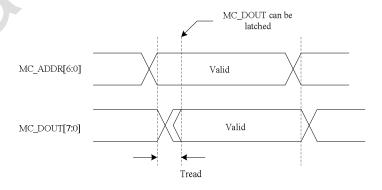

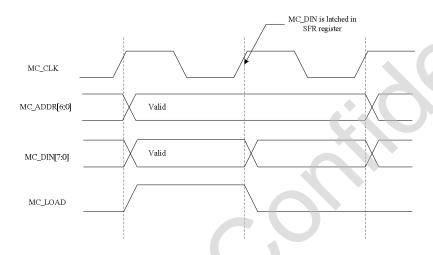

|   | 8.4   |          | nterface                          |     |

|   |       | 8.4.1    | General Features                  |     |

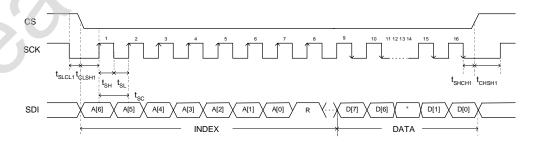

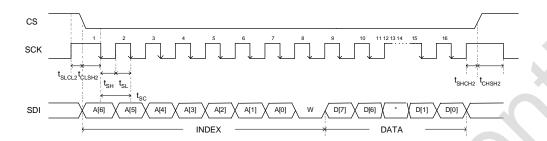

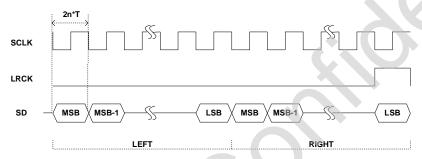

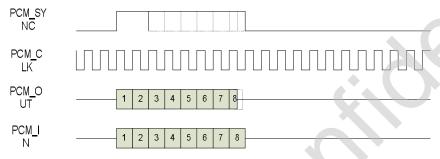

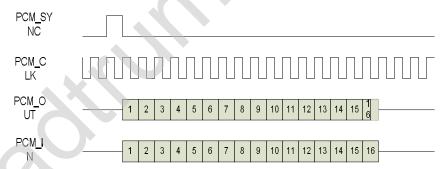

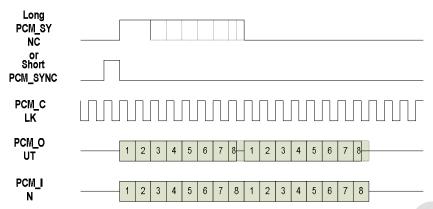

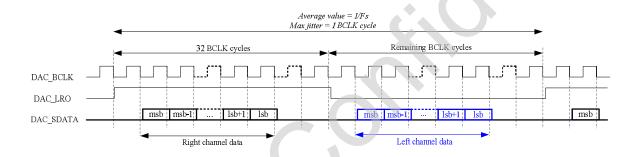

|   |       | 8.4.2    | DSP Mode Timing                   |     |

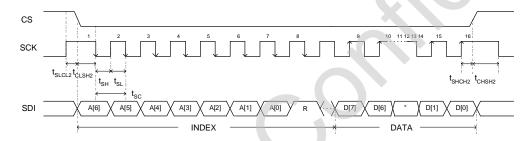

|   | 0.5   | 8.4.3    | I2S Mode Timing                   |     |

|   | 8.5   |          | ce                                |     |

|   |       | 8.5.1    | Overview                          |     |

|   |       | 8.5.2    | Features                          |     |

|   |       | 8.5.3    | Signal Description                |     |

|   |       | 8.5.4    | Function Description              |     |

|   |       | 8.5.5    | Control Registers                 |     |

|   | 8.6   |          | c Control Registers               |     |

|   |       | 8.6.1    | VB_AICR                           |     |

|   |       | 8.6.2    | VB_CR1                            |     |

|   |       | 8.6.3    | VB_CR2                            |     |

|   |       | 8.6.4    | VB_CCR1                           |     |

|   |       | 8.6.5    | VB_CCR2                           |     |

|   |       | 8.6.6    | VB_PMR1                           |     |

|   |       | 8.6.7    | VB_PMR2                           |     |

| • |       | 8.6.8    | VB_CRR                            |     |

|   |       | 8.6.9    | VB_ICR                            |     |

|   |       | 8.6.10   | VB_IFR                            |     |

|   |       | 8.6.11   | VB_CGR1                           |     |

|   |       | 8.6.12   | VB_CGR2                           | 904 |

|     |       | 8.6.13       | VB_CGR3                          | 905  |

|-----|-------|--------------|----------------------------------|------|

|     |       | 8.6.14       | VB_CGR8                          | 906  |

|     |       | 8.6.15       | VB_CGR9                          | 907  |

|     |       | 8.6.16       | VB_CGR10                         | 908  |

|     |       | 8.6.17       | VB_TR1                           | 909  |

|     |       | 8.6.18       | VB_TR2                           | 911  |

|     | 8.7   | Application  | Note                             | 912  |

|     |       | 8.7.1        | ARM Control Mode                 | 912  |

|     |       | 8.7.2        | DSP Control Mode                 | 913  |

|     |       | 8.7.3        | DMA Controlling Mode             | 914  |

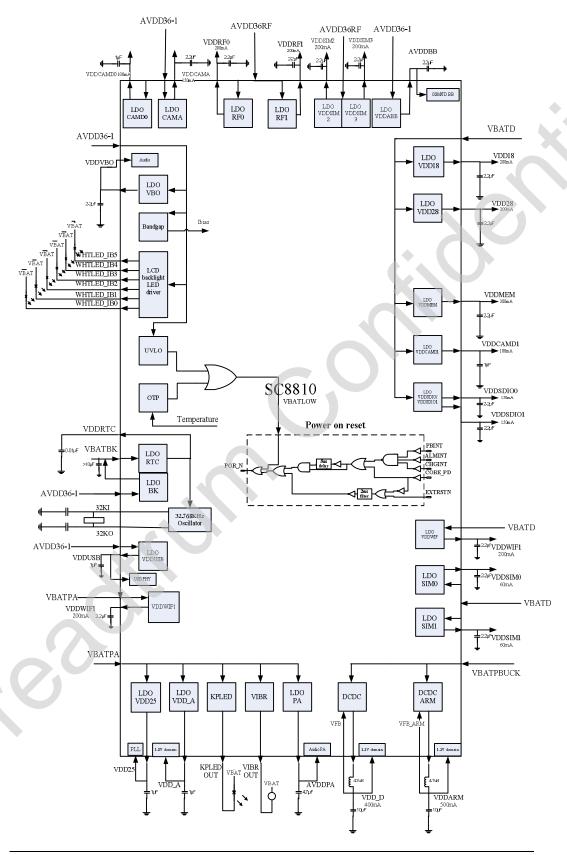

| 9   | POW   | ER MANAGI    | EMENT                            | 917  |

|     | 9.1   | Overview     |                                  | 917  |

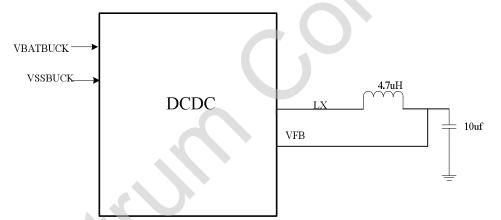

|     | 9.2   | LDO and D    | C-DC                             | 919  |

|     | 9.3   | Charger      |                                  | 938  |

|     |       | 9.3.1        | Charging Process                 | 939  |

|     |       | 9.3.2        | Programming Charge Current       | 940  |

|     |       | 9.3.3        | Charge Standby                   |      |

|     |       | 9.3.4        | Recharge Control                 | 940  |

|     |       | 9.3.5        | Software Over Current Protection | 940  |

|     | 9.4   | LCD Backli   | ght LED Driver                   | 940  |

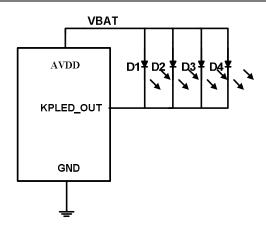

|     | 9.5   | Keypad Bad   | cklight LED Driver               | 942  |

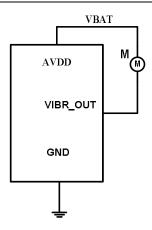

|     | 9.6   | Vibrator Dri | ver                              | 943  |

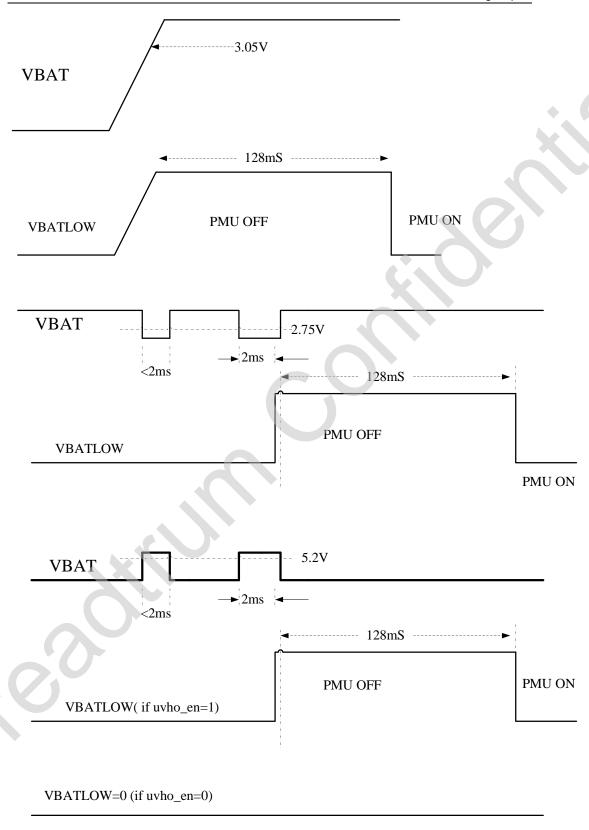

|     | 9.7   | UVLO         |                                  | 945  |

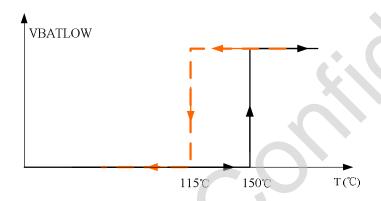

|     | 9.8   | OTP          |                                  | 947  |

|     | 9.9   | Band-Gap     |                                  | 947  |

|     | 9.10  | Powe         | er Control                       | 947  |

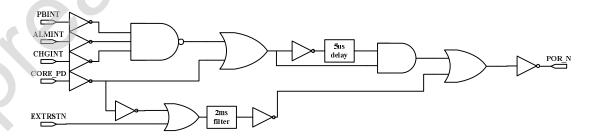

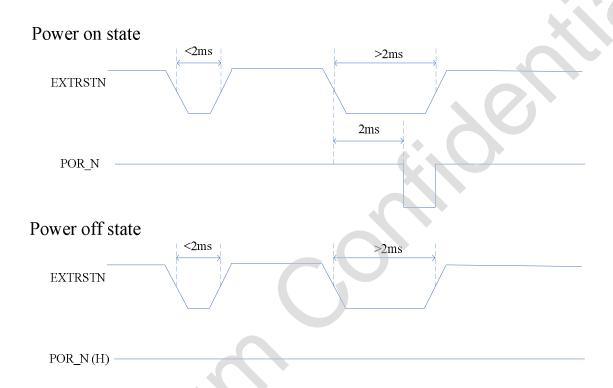

|     |       | 9.10.1       | Power on Procedure               | 947  |

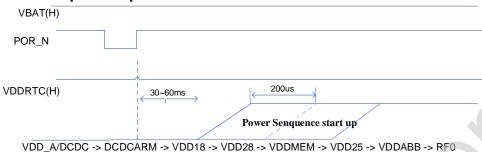

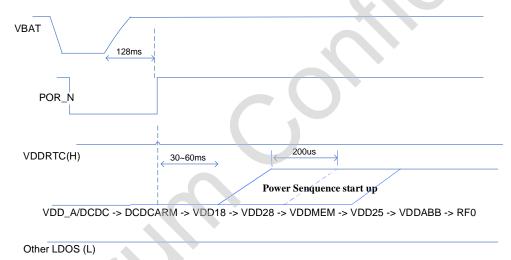

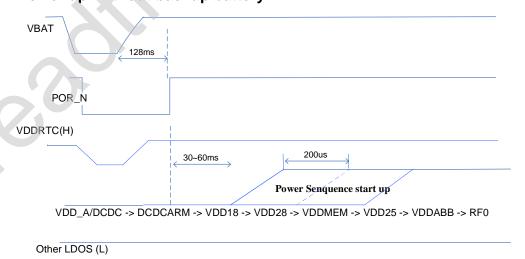

|     |       | 9.10.2       | Power on Sequence                | 950  |

|     |       | 9.10.3       | Reset sequence                   | 951  |

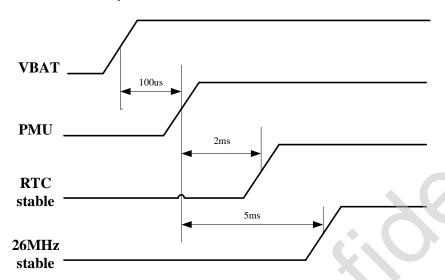

|     |       | 9.10.4       | Clock stable sequence            | 952  |

| 10  | ANAL  | OG CONTR     | OL REGISTERS                     | 953  |

|     | 10.1  | Globa        | al Register                      | 953  |

|     |       | 10.1.1 ARM   | l Side                           | 953  |

| APP | ENDIX |              |                                  | 1007 |

|     |       |              | breviations                      |      |

|     |       |              |                                  |      |

# 1 System Overview

SC6820 is a GSM/GPRS/EDGE baseband (BB) chip for mobile devices, and it also integrated a lot of multimedia accelerators and 3D graphic engine to develop rich multimedia applications. This document specifies the functions and features of SC6820.

# 1.1 General Description

SC6820 is a highly integrated mixed signal baseband processor for GSM/GPRS/EDGE applications. It consists with support of specially optimized architecture and many dedicate accelerators. SC6820 can achieve high performance and low power for a lot of applications. Proprietary architectures and algorithms were developed for low power ASIC design and power management. Unique techniques are used for noise/offset calibration and cancellation. Overall, SC6820 presents a revolutionary platform for mobile devices.

#### **Platform**

SC6820 is capable of running the ARM<sup>®</sup> Cortex A5<sup>TM</sup> 32-bit RISC processor at up to 1GHz, thus providing fast data processing capabilities. The high clock frequency, separate code and data caches are included to improve the overall system efficiency.

For large amount of data transfer, high performance DMA (Direct Memory Access) with hardware flow control is implemented, which greatly enhance the data movement efficiency with reducing MCU and DSP processing load.

Targeted as a high performance platform for mobile applications, Unique ID (UID) and secure boot are also provided to prevent unauthorized porting of the software load and fulfill other applications.

#### **External Memory**

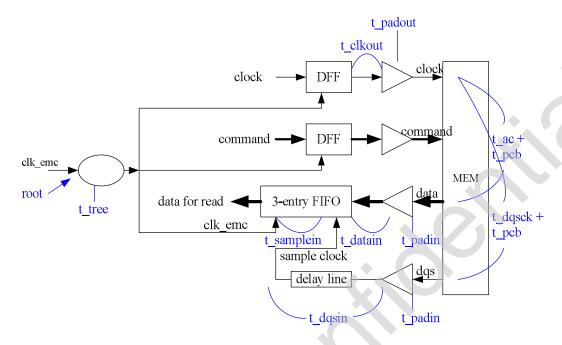

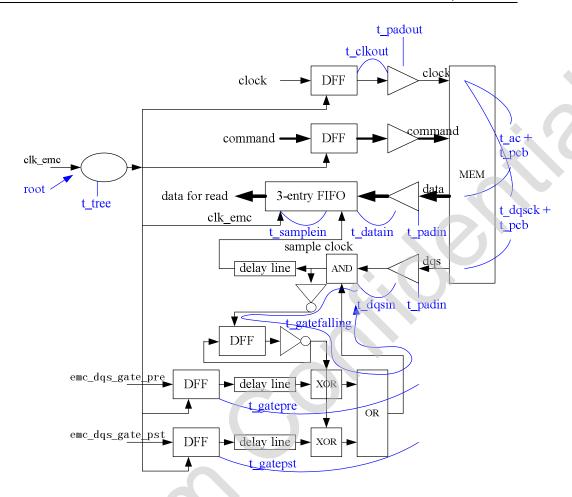

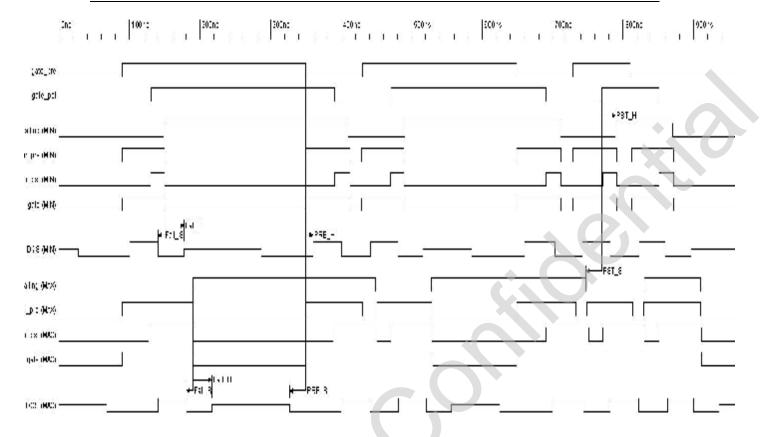

SC6820 supports mobile DDR/SDR-SDRAM, Nand flash. The external memory interface is designed for 1.8V I/O voltage. The driving strength is configurable for signal integrity adjustment.

#### Multi-media

SC6820 integrated digital still camera processor, H.264 decoder and MPEG4/H.263/JPEG codec engines. The multi-media subsystem provides a connection to up to 2 CMOS image sensors. With its high performance application platform.

SC6820 utilizes high resolution DAC, digital audio, and audio synthesis technology to provide superior audio features for all future multi-media needs.

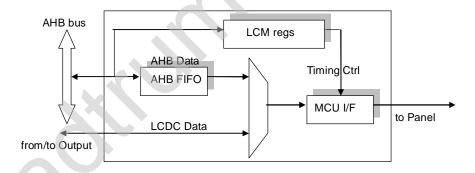

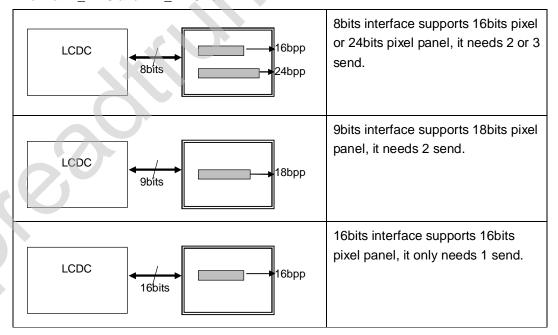

Furthermore, a dedicated LCDC controller enables MCU interface to 8/9/16/18/24 bit LCM panels, which provides much better configurability for multi-media products.

#### Peripherals and connectivity interface

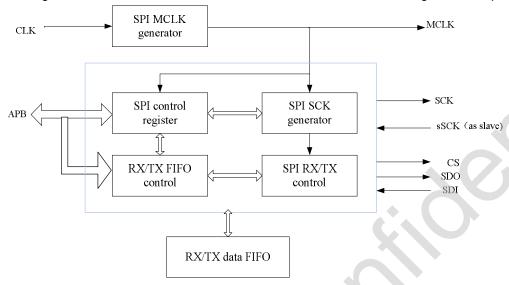

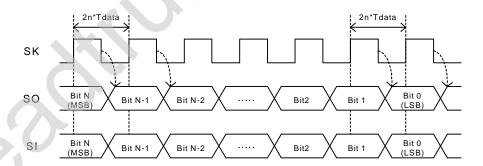

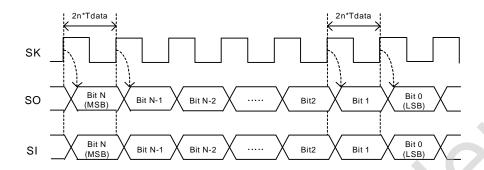

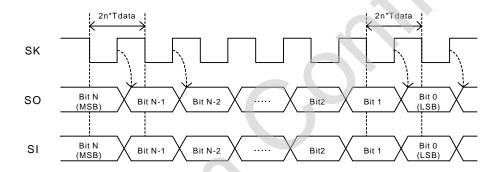

SC6820 incorporates myriads of advanced peripherals for different applications. It supports 3 UART, 2 IIS/PCM, 2 SPI, Keypad controller, 2 SIM controller, 4 PWM, 4 I<sup>2</sup>C, USB2.0, 2 SDIO, Touch Panel controller, and General Purpose Programmable I/Os(GPIO). These interfaces provide SC6820 users with the highest degree of flexibility in implementing solutions suitable for the targeted application.

#### **Radio**

SC6820 integrates a mixed-signal baseband front-end in order to provide a well-organized radio interface with flexibility for efficient customization. The front-end contains gain and offset calibration mechanisms, and filters with programmable coefficients for comprehensive compatibility control on RF modules.

The RF interface also consists of the following parts:

- An RF power amplifier control, which controls the timing of an RF power amplifier ON/OFF as well as its output power.

- An RF serial port, which is used to program control registers inside the RF module.

- RF parallel controls, which form a group of control signals to control the ON/OFF of the RF active components and passive couplers/switches.

#### <u>Audio</u>

SC6820 audio interface integrates D/A and A/D converters for Voice band, it also provides stereo input and analog MUX.

#### **Power Management**

With 2 DCDC and 22 LDO on chip ,SC6820 offers various low-power features to help reduce system power consumption. These features include deep sleep(standby mode), ARM system sleep, DSP system sleep, ARM processor sleep mode, DSP processor sleep mode, power down mode for individual peripheral etc. The advanced low leakage CMOS process which SC6820 adopted provide and overall low leakage solution.

#### **Package**

SC6820 is offered in a 13 mm x 13 mm x 1.4 mm 454 ball, 0.5 mm ball pitch LFBGA package

#### 1.2 SC6820 Features

SC6820 is Spreadtrum's 3rd-generation GSM/GPRS/EDGE ASIC solution chip. It inherits most of the features from SC6820 series with performance improvement and feature enhancement.

## 1.2.1 General Features

- With ARM® Cortex<sup>™</sup> A5 @ 1GHz, 32 bits DDR @ 400MHz, embedded Graphics and multimedia accelerators. The overall system performance of processor, graphics engine, DDR interface have been well organized, so SC6820 completes the AP requirements of prevalent Android phone

- mixed signal baseband processor for GSM/GPRS/EDGE applications

- Low power and high-performance device of mixed signal CMOS technology

- External supply voltages: battery 3.6V(typical),optional backup battery 3.0V(typical)

- Internal supply voltages: analog 3.0V or 3.3V, digital I/O 2.85V or 1.8V(typical), digital core 1.1V(typical) and RTC power supply 1.8V(typical)

- Integrated power management, voice band, audio band, and base band analog front ends

#### 1.2.2 Platform Features

#### **MCU** subsystem

- ARM® Cortex<sup>TM</sup> A5 32-bit RISC processor, up to 1G Hz

- 32 KB L1 I-cache and 32 KB L1 D-cache

- 256KB L2 Cache

- 32 KB dedicate on-chip SRAM

- 10 KB on-chip SRAM shared with DCAM (Digital Camera module)

- High performance multi-layer AHB-Lite bus system and low power APB system

- 24KB on-chip ROM for laboratory or factory programming and system boot

- Support boot from NAND, USB or UART

- Support memory re-mapping mechanism

- Dedicate DMA with 32 logical request channels

- Two general purpose RTC timers for task schedule and system timing recording

- One system timer with 1 ms counting scale

- Watchdog timer for system crash recovery

- 4 bus monitors for MCU system debug or performance analysis

- JTAG port for in-circuit emulation

- Support UID and secure boot

#### Note:

ARM® Cortex<sup>™</sup> A5is a registered trademark of Advanced RISC Machines Limited.

#### **Graphics subsystem**

Integrate Mali-300 GPU, a hardware accelerator for 2D and 3D graphics systems, consisits of

- A Pixel Processor (PP)

- a Geometry Processor(GP)

- a Level 2 Cache Controller(L2)

- a Memory Management Unit (MMU) for each GP and PP included in the GPU

#### **External memory interface**

- Support NAND flash, mobile DDR/SDR-SDRAM

- Two external memory controllers: NAND controller and External Memory Controller (EMC), supporting the following memory combinations:

- ; NAND + DDR/SDR-SDRAM

- NAND flash is supported by NAND controller, with the following features:

- ; Support 8 bit and 16 bit devices

- ; Support 1.8 V and 3.0 V devices

- ; Support hardware ECC generation up to 24 bits

- i Support small page (512 bytes) and large page (up to 8K bytes)

- For small page device, support 4 consecutive memory read/write, and for large page, only support single page operation

- SDR/DDR SDRAM are supported by External Memory Controller, with the features list below:

- Support only 1.8 V devices

- ; Support up to 2G bits with single CS

- ; SDRAM support 16 bit and 32 bit devices

- Support up to 2 chip select channels (2 CS)

- Support up to 512M byte devices

- Memory clock is optional to clk\_emc/2 or clk\_emc/4 (clk\_emc is the EMC controller clock, up to 400 MHz)

#### Peripheral and connectivity interfaces

- Support 4 SIM cards and both 1.8 V or 3.0 V devices

- Support SDIO 2.0

- Support USB 2.0 High speed

- Three UARTs

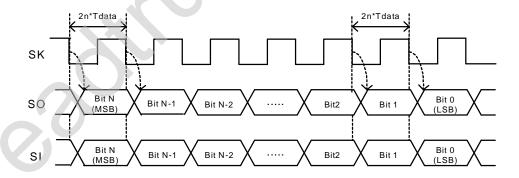

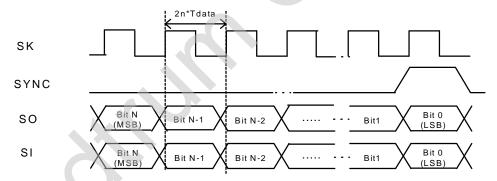

- Two SPI, support both master and slave, support 3-wire SPI, 4-wire SPI and synchronous SPI

- Two IIS and PCM, for audio codec connection

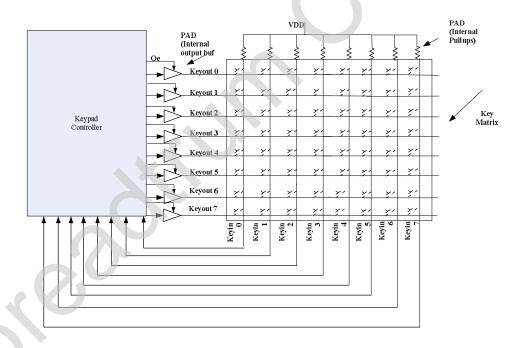

- Support 8-column x 8-row keypad with internal pull-up resistors

- Four I2C interface

- More than 100 GPIO pins

- Four PWM outputs

- Four 10-bit ADC input

- ETM port

#### 1.2.3 Modem Features

#### Implementation

- Signal processing for modem functions is mainly implemented in CEVA DSP sub-system

- System timing

- For GSM/GPRS/EDGE, recommend use a low swing 26 MHz master clock input.

- Time tracking in power saving mode

- 16 general RFCTL wires for RF chip or antenna control

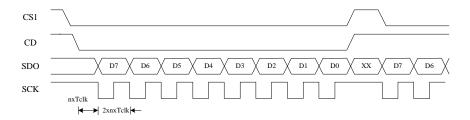

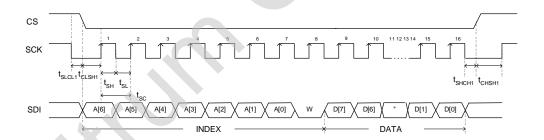

- 1 dedicate SPI ports for BB-RF chip communication

- 10-bit D/A converter with programmable gain

#### Note:

• CEVAX® is a registered trademark of CEVA, Inc.

#### **GSM/GPRS/EDGE** baseband

- Compatible with GSM/GPRS/EDGE Release 1999, GSM850,GSM900, DCS1800, and PCS1900 recommendations

- Complete in-phase and quadrature (I/Q) component interface between the Digital Signal Processor (DSP) and RF module

- EGPRS class12, typeB (MCS1-9 in downlink and MCS1-9 in uplink)

Cryptographic Algorithms: (A5/1, A5/2 and A5/3, GEA 1, GEA 2 and GEA3 algorithms)

#### Voice and modem codec

- Audio signal conversion between microphone/earphone and DSP

- · Second set converters for auxiliary microphone/speaker

- Stereo audio output

- Integrated microphone bias

- Integrated Class A/B or Class D

- Quad vocoders for adaptive multi-rate (AMR), enhanced full rate (EFR), half rate(HR), and full rate (FR)

- Dial tone generation

- Voice memo

- Noise reduction

- Echo suppression/echo cancellation

- Digital sidetone generator with programmable gain

- Voice power amplifier with programmable gain

## 1.2.4 Power Management Features

- Integrated two DC-DC and 25 low dropout regulators (LDOs), supplying power for internal chip or external devices. All such DC-DC and LDOs can be powered down and up with software management.

- Support standby mode with small deep-sleep current

- Integrated Li-ion battery charger, support charging from USB or external adaptor. The charger voltage can be measured with auxiliary ADC.

## 1.2.5 Multi-media Features

#### **LCD** display

- Integrated LCD controller (LCDC), support 2 chip select: LCD\_CS0 and LCD\_CS1

- Support MCU interface

- Support dual display panels: use LCD\_CS1 to connect sub-panel, and LCD\_CS0 to connect main display panel

- Support 8/9/16/18/24 bit LCM interfaces

- Support LCM format RGB565 and RGB666 and RGB888

- Typical image sizes: QCIF, QVGA,WQVGA, CIF, VGA,WVGA, FWVGA

- Support hardware display rotation

#### Image signal processor

- Support image sensor sizes up to 5M pixels

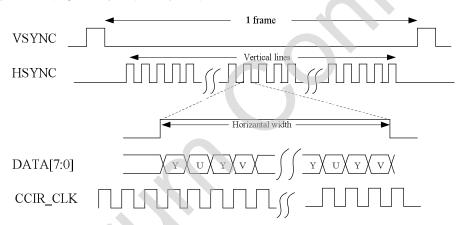

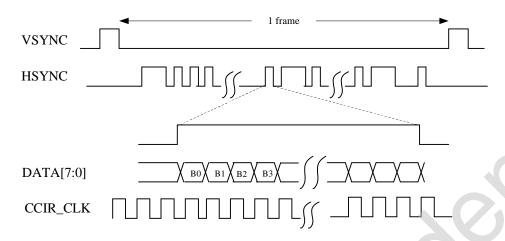

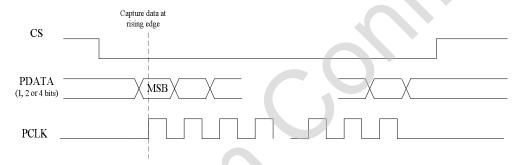

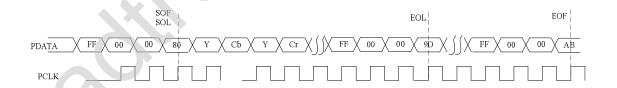

- Support image sensor data YUV422 format and JPEG format

- Support scaling down/up function, scaling factor from 1/4 to 2

- Support hardware rotation

- Support JPEG decoder baseline profile, as defined in ISO/IEC 10918-1, with sizes up to 8M pixels, and color format YUV444, YUV422/YUV422R, YUV420, YUV411 /YUV411R or gray scale.

- Support JPEG encoder baseline profile, as defined in ISO/IEC 10918-1, with sizes up to 8M pixels, and color format YUV422 or YUV420

- Support PNG,GIF decoder

#### Video codec

- Support H264 decoder compliant with ITU-T H.264 baseline profile, D1 30 fps

- Support H263 decoder, compliant with ITU H.263 profile 0. D1 30fps.

- Support H263 encoder compliant with ITU H.263 baseline profile CIF 30fps

- Support MPEG4 decoder compliant with ISO/IEC 14496-2 (MPEG4 Part 2 2001) @ simple profile, D1 30 fps

- Support MPEG4 encoder compliant with ISO/IEC 14496-2 (MPEG4 Part 2 2001) @ simple profile, D1 15fps

#### **Audio codec**

- Wavetable synthesis up to 64 tones

- Support AAC/AAC+ decoding,

- PCM record and playback

- Digital audio playback

- MPEG1 audio layer3, MPEG2 low sampling rate extension layer3, MPEG 2.5 layer3

- MIDI

- AMR-NB

- DRA

- WMA

# 1.3 Applications

SC6820 provides a single-chip baseband solution for GSM/GPRS/EDGE dual-mode wireless telephone handsets and data modems conforming to the GSM/GPRS (Release 1999, GSM850, GSM900, DCS1800 and PCS1900, quad-band).

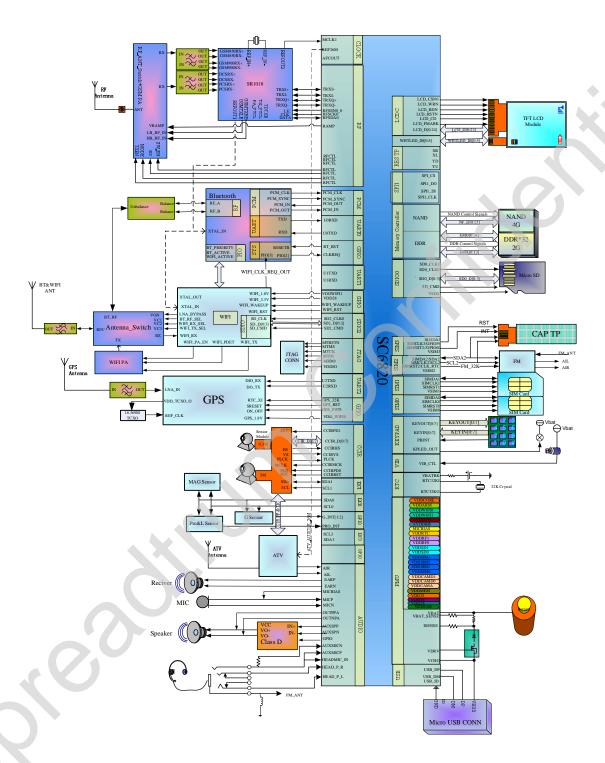

Figure 1-1 A typical application diagram of SC6820

# 1.4 Chip Architecture

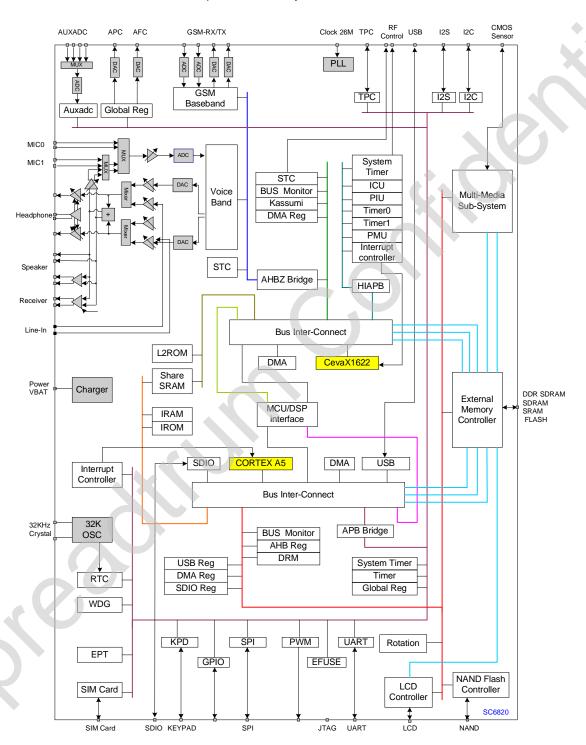

Figure 1-2 shows the chip-level functional block diagram of SC6820. This chip architecture is based on two processor subsystems, an MCU and a DSP, and other functional blocks are connected to one or both of the buses and provide various hardware accelerations and interfaces to other components in the system.

Figure 1-2 SC6820 chip-level functional block diagram

# 2 Package Information

Plastic-encapsulated surface mount packages are sensitive to damage induced by absorbed moisture and temperature. ALL the SC6820 chips are MSL 3, which had been marked on the label for every package.

# 2.1 Top Marking Definition

Figure 2-1 Top marking definition

## 2.2 LFBGA Pinout

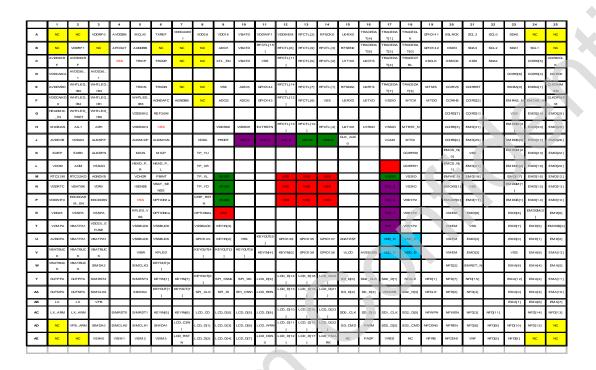

Figure 2-2 454-ball LFBGA pinout

# 2.3 Package Outline

Figure 2-3 Package outline

|                             | SYMBOL | COMN | MON DIMENS | SIONS |

|-----------------------------|--------|------|------------|-------|

|                             |        | MIN. | NOR.       | MAX.  |

| TOTAL THICKNESS             | Α      |      |            | 1.3   |

| STAND OFF                   | A1     | 0.16 |            | 0.26  |

| SUBSTRATE THICKNESS         | A2     |      | 0.26       | REF   |

| MOLD THICKNESS              | А3     |      | 0.7        | REF   |

| BODY SIZE                   | D      |      | 13         | BSC   |

| BODT SIZE                   | E      |      | 13         | BSC   |

| BALL DIAMETER               |        |      | 0.3        |       |

| BALL OPENING                |        |      | 0.275      |       |

| BALL WIDTH                  | Ь      | 0.27 |            | 0.37  |

| BALL PITCH                  | е      |      | 0.5        | BSC   |

| BALL COUNT                  | n      |      | 454        |       |

| EDGE BALL CENTER TO CENTER  | D1     |      | 12         | BSC   |

| EDGE BALL CENTER TO CENTER  | E1     |      | 12         | BSC   |

| BODY CENTER TO CONTACT BALL | SD     |      |            | BSC   |

| BODT CENTER TO CONTACT BALL | SE     |      |            | BSC   |

| PACKAGE EDGE TOLERANCE      | aaa    |      | 0.1        |       |

| MOLD FLATNESS               | bbb    |      | 0.2        |       |

| COPLANARITY                 | ddd    |      | 0.08       |       |

| BALL OFFSET (PACKAGE)       | eee    |      | 0.15       |       |

| BALL OFFSET (BALL)          | fff    |      | 0.08       |       |

|                             |        |      |            |       |

| <b>^</b>                    |        |      |            |       |

|                             |        |      |            |       |

|                             |        |      |            |       |

|                             |        |      |            |       |

|                             |        |      |            |       |

Figure 2-4 Package parameters

## 2.4 Reflow Profile

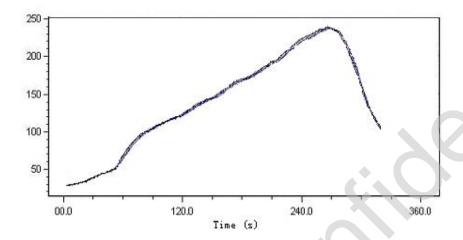

Figure 2-5 Reflow profile

#### Note:

- 1. Recommended reflow profile for lead-free solder paste

- ; Ramp at 1-2°C per second to 245+/-5°C

- ; Dwell at 235°C for 10 seconds

- ; Dwell at 217°C for 30~60s

- : Total reflow time is about 220~270 s

- : Cold down ramp < 4°C/s

- 2. Recommended solder paste type

- ; SnAgCu solder paste

- Metal contents should be about 88.5%

- 3. Recommended parameter for stencil making

- Metal mask thickness: 5 mils

- Opening area ratio: 100%

# **3 Pin Information**

# 3.1.1 Pin symbol descriptions

The following table explains the symbols used in the pin lists.

Table 3-1 Definition of pin symbols

| Field        | Symbol                    | Type Description                                                                                         |  |  |  |  |

|--------------|---------------------------|----------------------------------------------------------------------------------------------------------|--|--|--|--|

|              | I                         | Digital input                                                                                            |  |  |  |  |

|              | 0                         | Digital output                                                                                           |  |  |  |  |

|              | O/T                       | Digital output with tri-state option                                                                     |  |  |  |  |

|              | I/O                       | Digital bi-directional pin                                                                               |  |  |  |  |

|              | I/O/T                     | Digital bi-directional pin with tri-state option                                                         |  |  |  |  |

| Pin          | PI                        | Power pin, input from external power supply                                                              |  |  |  |  |

| Туре         | PIO                       | Power pin, input from external or floating to use internal LDO power supply                              |  |  |  |  |

|              | PO                        | Power pin, output for external devices                                                                   |  |  |  |  |

|              | G                         | Ground pin                                                                                               |  |  |  |  |

|              | Al                        | Analog input pin                                                                                         |  |  |  |  |

|              | AO                        | Analog output pin                                                                                        |  |  |  |  |

|              | AIO                       | Analog bi-directional pin                                                                                |  |  |  |  |

|              | IPU                       | Input with pull-up                                                                                       |  |  |  |  |

|              | IPD                       | Input with pull-down                                                                                     |  |  |  |  |

| Pin<br>Value | ОН                        | Output "1"                                                                                               |  |  |  |  |

|              | OL                        | Output "O"                                                                                               |  |  |  |  |

|              | Z                         | Tri-state                                                                                                |  |  |  |  |

|              | VBAT                      | Battery power supply input                                                                               |  |  |  |  |

|              | VDD_D<br>/VDD1P2          | Power supply for core and ARM, the internal power source are DCDC for CORE and DCDC for ARM              |  |  |  |  |

|              | VIO<br>/VIO_1<br>/VIO_2   | Power supply for I/O, the internal power source is VDD18 or VDD28                                        |  |  |  |  |

| Power        | VMEM                      | Power supply for SRAM/SDRAM memories, the internal power source is VDDMEM                                |  |  |  |  |

|              | VCAM                      | Power supply for Digital Camera, the internal power source is VDDCARM0 or VDDCARM1 or VDDCARMA           |  |  |  |  |

|              | VNF                       | Power supply for NAND flash and LCM, the internal power source is VDD28 or VDD18                         |  |  |  |  |

|              | VSIM0<br>/VSIM1<br>/VSIM2 | Power supply for SIM card 0 1 2 3, the internal power source are LDO_SIM0 LDO_SIM1 LDO_SIM2 and LDO_SIM3 |  |  |  |  |

| Field | Symbol              | Type Description                                                         |

|-------|---------------------|--------------------------------------------------------------------------|

|       | /VSIM3              |                                                                          |

|       | VDDRF0<br>/VDDRF1   | Power supply for RF , the internal power source are VDDRF0/VDDRF1        |

|       | VDDRTC              | Power supply for RTC                                                     |

|       | VDDUSB              | Power supply for USB                                                     |

|       | VDD25               | Power supply for PLL and Efuse                                           |

|       | VSD                 | Power supply for SD card , the internal power source is VDDSD0 or VDDSD1 |

|       | AVDDBB              | Analog base-band RX/TX power supply, the internal power source is AVDDBB |

|       | AVDDVB              | Analog voice-band power supply , the internal power source is AVDDVB     |

|       | VDDWIF0<br>/VDDWIF1 | Power supply for external Wif or other application                       |

|       | VDD_A               | Supply for 26MHz buffer and pLL                                          |

## **3.1.2 Pin List**

## Table 3-2 Pin List

| Ball   | Pin Type                         | Pin Name  | Default<br>Direction | Power | At Reset         | After Reset   | Descrption                    |  |  |

|--------|----------------------------------|-----------|----------------------|-------|------------------|---------------|-------------------------------|--|--|

| Clock  | Clock & Reset Interface (3 Pins) |           |                      |       |                  |               |                               |  |  |

| C9     | SPBC2_24X                        | XTL_EN    | 0                    | VIO_2 | le=0,<br>oe=1, 1 | ie=0, oe=1, 1 | External<br>Crystal<br>Enable |  |  |

| P8     | SPBC2_24X_S                      | CHIP_RSTN | I                    | VIO   | le=1,<br>oe=0    | le=1, oe=0    |                               |  |  |

| M6     | SPSOS2_24X_H                     | PBINT     | I                    | VIO   | le=1,<br>oe=0    | le=1, oe=0    |                               |  |  |

| Produ  | ction Test Interface (1 I        | Pins)     |                      |       |                  |               |                               |  |  |

| J9     | SPPAD3_S                         | PRODT     |                      | VIO   |                  |               |                               |  |  |

| GPIO I | Interface (10 Pins)              |           | <u>'</u>             |       | <u>'</u>         |               |                               |  |  |

| U13    | SPBC2_24X                        | GPIO135   | I/O                  | VIO_1 | le=0,<br>oe=1, 0 | ie=1, oe=0    |                               |  |  |

| V14    | SPBC2_24X                        | GPIO136   | I/O                  | VIO_1 | ie=0,<br>oe=1, 0 | ie=1, oe=0    |                               |  |  |

| U14    | SPBC2_24X                        | GPIO137   | I/O                  | VIO_1 | ie=0,<br>oe=1, 0 | ie=1, oe=0    |                               |  |  |

| U12    | SPBC2_24X                        | GPIO138   | I/O                  | VIO_1 | ie=0,<br>oe=1, 0 | ie=1, oe=0    |                               |  |  |

| V13    | SPBC2_24X                        | GPIO139   | I/O                  | VIO_1 | ie=0,<br>oe=1, 0 | ie=1, oe=0    |                               |  |  |

| U8     | SPBC2_24X                        | GPIO140   | I/O                  | VIO_1 | ie=0,            | ie=1, oe=0    |                               |  |  |

| Ball | Pin Type           | Pin Name | Default<br>Direction | Power | At Reset              | After Reset     | Descrption |

|------|--------------------|----------|----------------------|-------|-----------------------|-----------------|------------|

|      |                    |          |                      |       | oe=1, 0               |                 |            |

| A19  | SPBC2_24X          | GPIO141  | I/O                  | VIO_2 | ie=0,<br>oe=1, 0      | ie=1, oe=0      |            |

| B19  | SPBC2_24X          | GPIO142  | I/O                  | VIO_2 | ie=0,<br>oe=1, 0      | ie=1, oe=0      | • (        |

| F11  | SPBC2_24X          | GPIO143  | I/O                  | VIO_2 | ie=0,<br>oe=1, 0      | ie=1, oe=0      | X          |

| E11  | SPBC2_24X          | GPIO144  | I/O                  | VIO_2 | ie=0,<br>oe=1, 0      | ie=1, oe=0      |            |

| SIM0 | Interface (3 Pins) |          |                      | •     |                       |                 |            |

| AD4  | SPCBC2_24X         | SIMCLK0  | 0                    | VSIM0 | ie=0,<br>oe=1, 0      | ie=0, oe=1, 0   |            |

| AD3  | SPSBC2_24X         | SIMDA0   | I/O/T                | VSIM0 | ie=1,<br>oe=0,<br>wpu | ie=1, oe=0, wpu |            |

| AC4  | SPCBC2_24X         | SIMRST0  | 0                    | VSIM0 | ie=0,<br>oe=1, 0      | ie=0, oe=1, 0   |            |

| SIM1 | Interface (3 Pins) |          |                      |       |                       |                 |            |

| AD5  | SPCBC2_24X         | SIMCLK1  | 0                    | VSIM1 | ie=0,<br>oe=1, 0      | ie=0, oe=1, 0   |            |

| AD6  | SPSBC2_24X         | SIMDA1   | I/O/T                | VSIM1 | ie=1,<br>oe=0,<br>wpu | ie=1, oe=0, wpu |            |

| AC5  | SPCBC2_24X         | SIMRST1  | 0                    | VSIM1 | ie=0,<br>oe=1, 0      | ie=0, oe=1, 0   |            |

| SIM2 | Interface (3 Pins) |          |                      |       |                       |                 |            |

| AA3  | SPCBC2_24X         | SIMCLK2  | 0                    | VSIM2 | ie=0,<br>oe=1, 0      | ie=0, oe=1, 0   |            |

| W3   | SPSBC2_24X         | SIMDA2   | I/O/T                | VSIM2 | ie=1,<br>oe=0,<br>wpu | ie=1, oe=0, wpu |            |

| Y3   | SPCBC2_24X         | SIMRST2  | 0                    | VSIM2 | ie=0,<br>oe=1, 0      | ie=0, oe=1, 0   |            |

| SIM3 | Interface (3 Pins) |          |                      |       |                       |                 |            |

| W5   | SPCBC2_24X         | SIMCLK3  | 0                    | VSIM3 | ie=0,<br>oe=1, 0      | ie=0, oe=1, 0   |            |

| AA5  | SPSBC2_24X         | SIMDA3   | I/O/T                | VSIM3 | ie=1,<br>oe=0,        | ie=1, oe=0, wpu |            |

| Y5   | SPCBC2_24X         | SIMRST3  | 0                    | VSIM3 | ie=0,<br>oe=1, 0      | ie=0, oe=1, 0   |            |

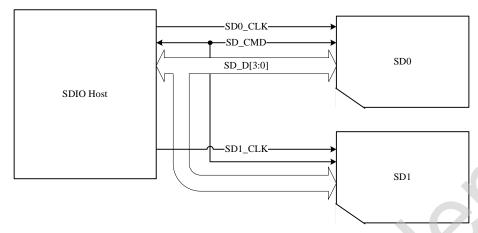

| SDIO | Interface (7 Pins) |          |                      |       | 1 3321, 0             |                 |            |

| AC15 | SPCBC2_24X         | SD0_CLK  | I/O/T                | VSD   | ie=0,<br>oe=1, 0      | ie=0, oe=1, 0   |            |

| AD15 | SPCBC2_24X         | SD_CMD   | I/O/T                | VSD   | ie=1,<br>oe=0,wpu     | ie=1, oe=0,wpu  |            |

| Y15  | SPCBC2_24X         | SD_D[0]  | I/O/T                | VSD   | ie=1,<br>oe=0,wpu     | ie=1, oe=0,wpu  |            |

|      |                    | l        | L                    | l     |                       | <u> </u>        | 1          |

| Ball  | Pin Type              | Pin Name  | Default<br>Direction | Power | At Reset              | After Reset     | Descrption |

|-------|-----------------------|-----------|----------------------|-------|-----------------------|-----------------|------------|

| AC16  | SPCBC2_24X            | SD_D[1]   | I/O/T                | VSD   | ie=1,<br>oe=0,wpu     | ie=1, oe=0,wpu  |            |

| AA15  | SPCBC2_24X            | SD_D[2]   | I/O/T                | VSD   | ie=1,<br>oe=0,wpu     | ie=1, oe=0,wpu  |            |

| AA16  | SPCBC2_24X            | SD_D[3]   | I/O/T                | VSD   | ie=1,<br>oe=0,wpu     | ie=1, oe=0,wpu  |            |

| AC17  | SPCBC2_24X            | SD1_CLK   | I/O/T                | VSD   | ie=0,<br>oe=1, 0      | ie=0, oe=1, 0   |            |

| SDIO2 | Interface (6 Pins)    |           |                      |       |                       |                 |            |

| Y16   | SPCBC2_24X            | SD2_CLK   | I/O/T                | VSD2  | ie=0,<br>oe=1, 0      | ie=0, oe=1, 0   |            |

| AD18  | SPCBC2_24X            | SD2_CMD   | I/O/T                | VSD2  | ie=1,<br>oe=0,wpu     | ie=1, oe=0,wpu  |            |

| AC18  | SPCBC2_24X            | SD2_D[0]  | I/O/T                | VSD2  | ie=1,<br>oe=0,wpu     | ie=1, oe=0,wpu  |            |

| Y17   | SPCBC2_24X            | SD2_D[1]  | I/O/T                | VSD2  | ie=1,<br>oe=0,wpu     | ie=1, oe=0,wpu  |            |

| AD17  | SPCBC2_24X            | SD2_D[2]  | I/O/T                | VSD2  | ie=1,<br>oe=0,wpu     | ie=1, oe=0,wpu  |            |

| AA18  | SPCBC2_24X            | SD2_D[3]  | I/O/T                | VSD2  | ie=1,<br>oe=0,wpu     | ie=1, oe=0,wpu  |            |

| Keypa | d Interface (16 Pins) |           |                      |       |                       |                 |            |

| Y8    | SPCBC2_24X            | KEYOUT[0] | O/T                  | VIO_1 | ie= oe=0              | ie= oe=0        |            |

| AA6   | SPCBC2_24X            | KEYOUT[1] | O/T                  | VIO_1 | ie= oe=0              | ie= oe=0        |            |

| W6    | SPCBC2_24X            | KEYOUT[2] | O/T                  | VIO_1 | ie= oe=0              | ie= oe=0        |            |

| V9    | SPCBC2_24X            | KEYOUT[3] | O/T                  | VIO_1 | ie= oe=0              | ie= oe=0        |            |

| V8    | SPCBC2_24X            | KEYOUT[4] | O/T                  | VIO_1 | ie= oe=0              | ie= oe=0        |            |

| U11   | SPCBC2_24X            | KEYOUT[5] | O/T                  | VIO_1 | ie= oe=0              | ie= oe=0        |            |

| V10   | SPCBC2_24X            | KEYOUT[6] | O/T                  | VIO_1 | ie= oe=0              | ie= oe=0        |            |

| AA7   | SPCBC2_24X            | KEYOUT[7] | O/T                  | VIO_1 | ie= oe=0              | ie= oe=0        |            |

| V12   | SPCBC2_24X            | KEYIN[0]  | I                    | VIO_1 | ie= oe=0              | ie=1, oe=0, wpu |            |

| Y6    | SPCBC2_24X            | KEYIN[1]  | I                    | VIO_1 | ie=1,<br>oe=0,<br>wpd | ie=1, oe=0, wpu |            |

| U9    | SPCBC2_24X            | KEYIN[2]  | I                    | VIO_1 | ie= oe=0              | ie=1, oe=0, wpu |            |

| T9    | SPCBC2_24X            | KEYIN[3]  | I                    | VIO_1 | ie= oe=0              | ie=1, oe=0, wpu |            |

| V11   | SPCBC2_24X            | KEYIN[4]  | I                    | VIO_1 | ie= oe=0              | ie=1, oe=0, wpu |            |

| AC6   | SPCBC2_24X            | KEYIN[5]  | I                    | VIO_1 | ie= oe=0              | ie=1, oe=0, wpu |            |

| AC7   | SPCBC2_24X            | KEYIN[6]  | I                    | VIO_1 | ie= oe=0              | ie=1, oe=0, wpu |            |

| Y7    | SPCBC2_24X            | KEYIN[7]  | I                    | VIO_1 | ie= oe=0              | ie=1, oe=0, wpu |            |

|       | erface (5 Pins)       |           |                      |       |                       |                 |            |

| AA9   | SPBC2_24X             | SPI_DI    | I                    | VIO_1 | ie=1,<br>oe=0,wpu     | ie=1, oe=0,wpu  |            |

| AA8   | SPBC2_24X             | SPI_CLK   | I/O                  | VIO_1 | ie=0,                 | ie=0, oe=1, 0   |            |

| Ball  | Pin Type             | Pin Name | Default<br>Direction | Power    | At Reset              | After Reset     | Descrption |

|-------|----------------------|----------|----------------------|----------|-----------------------|-----------------|------------|

|       |                      |          |                      |          | oe=1, 0               |                 |            |

| Y10   | SPBC2_24X            | SPI_DO   | I/O                  | VIO_1    | ie=0,<br>oe=1, 0      | ie=0, oe=1, 0   |            |

| Y9    | SPBC2_24X            | SPI_CSN0 | О/Т                  | VIO_1    | ie=0,<br>oe=1, 1      | ie=0, oe=1, 1   | <b>*</b>   |

| AA10  | SPBC2_24X            | SPI_CSN1 | O/T                  | VIO_1    | ie=0,<br>oe=1, 1      | ie=0, oe=1, 1   | X          |

| JTAG  | Interface (5 Pins)   |          |                      |          |                       |                 |            |

| F19   | SPCBC2_24X           | MTDO     | О/Т                  | VIO_2    | ie=0,<br>oe=1, 0      | ie=0, oe=1, 0   |            |

| J18   | SPCBC2_24X           | MTDI     | I                    | VIO_2    | ie=1,<br>oe=0,<br>wpu | ie=1, oe=0, wpu |            |

| F18   | SPCBC2_24X           | MTCK     | I                    | VIO_2    | ie=1,<br>oe=0,<br>wpu | ie=1, oe=0, wpu |            |

| E19   | SPCBC2_24X           | MTMS     | I                    | VIO_2    | ie=1,<br>oe=0,<br>wpu | ie=1, oe=0, wpu |            |

| H18   | SPCBC2_24X           | MTRST_N  |                      | VIO_2    | ie=1,<br>oe=0,<br>wpd | ie=1, oe=0, wpd |            |

| UART  | 0 Interface (4 Pins) |          |                      |          |                       |                 |            |

| F16   | SPCBC2_24X           | U0TXD    | 0                    | VIO_2    | ie=0,<br>oe=1, 1      | ie=0, oe=1, 1   |            |

| A15   | SPCBC2_24X           | U0RXD    |                      | VIO_2    | ie=1,<br>oe=0,<br>wpu | ie=1, oe=0, wpu |            |

| C16   | SPCBC2_24X           | U0CTS    | I                    | VIO_2    | ie=1,<br>oe=0,<br>wpu | ie=1, oe=0, wpu |            |

| E16   | SPCBC2_24X           | UORTS    | 0                    | VIO_2    | ie=0,<br>oe=1, 1      | ie=0, oe=1, 1   |            |

| UART  | 1 Interface (2 Pins) |          |                      |          |                       |                 |            |

| C15   | SPCBC2_24X           | U1TXD    | 0                    | VIO_2    | ie=1,<br>oe=0,<br>wpu | ie=0, oe=1, 1   |            |

| H16   | SPCBC2_24X           | U1RXD    | I                    | VIO_2    | ie=1,<br>oe=0,<br>wpu | ie=1, oe=0, wpu |            |

| UART  | 2 Interface (2 Pins) |          |                      | l        |                       |                 |            |

| H15   | SPCBC2_24X           | U2TXD    | 0                    | VIO_2    | ie=1,<br>oe=0,<br>wpu | ie=0, oe=1, 1   |            |

| F15   | SPCBC2_24X           | U2RXD    | I                    | VIO_2    | ie=1,<br>oe=0,<br>wpu | ie=1, oe=0, wpu |            |

| LCD I | nterface (31 Pins)   |          |                      | <u> </u> | '                     |                 |            |

| AD7   | SPCBC2_24X           | LCD_CSN1 | 0                    | VLCD     | ie=0,                 | ie=0, oe=1, 1   |            |

|       |                      |          | ĺ                    | l        | 10-0,                 | 0, 00 1, 1      |            |

| Ball | Pin Type    | Pin Name  | Default<br>Direction | Power | At Reset         | After Reset   | Descrption |

|------|-------------|-----------|----------------------|-------|------------------|---------------|------------|

|      |             |           |                      |       | oe=1, 1          |               |            |

| AE7  | SPCBC2_24X  | LCD_RSTN  | 0                    | VLCD  | ie=0,<br>oe=1, 0 | ie=0, oe=1, 1 |            |

| AC8  | SPCBC2_24X  | LCD_CD    | 0                    | VLCD  | ie=0,<br>oe=1, 0 | ie=0, oe=1, 0 | <b>*</b> ( |

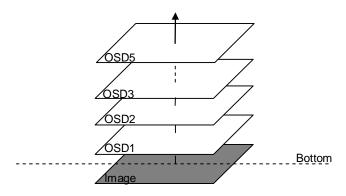

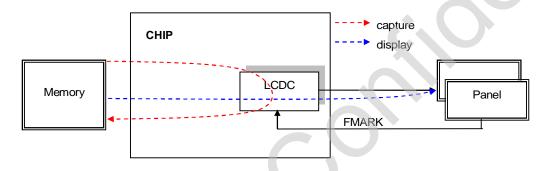

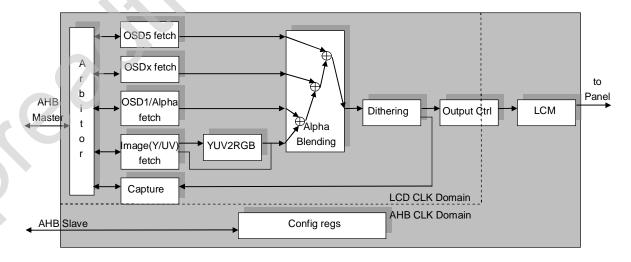

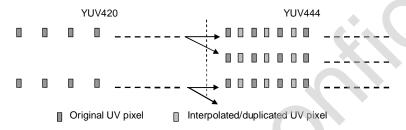

| AC9  | SPCBC2_24 X | LCD_D[0]  | I/O                  | VLCD  | ie=1,<br>oe=0    | ie=1, oe=0    | X          |