# **SIMATIC S5**

# S5-100U Programmable Controller

System Manual CPU 100/102/103

EWA 4NEB 812 6120-02b

**Edition 04**

www.DataSheet4U.com

STEP ® SINEC ® and SIMATIC ® are registered trademarks of Siemens AG. LINESTRA® is a registered trademark of the OSRAM Company. Subject to change without prior notice.

The reproduction, transmission or use of this document or its contents is not permitted without express written authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved.

Copyright© Siemens AG 1992

# Introduction

| The SIMATIC S5 System Family                         | 1              |

|------------------------------------------------------|----------------|

| Technical Description                                | 2              |

| Installation Guidelines                              | 3              |

| Start-Up and Program Tests                           | 4              |

| Diagnostics and Troubleshooting                      | 5              |

| Addressing                                           | 6              |

| Introduction to STEP 5                               | 7              |

| STEP 5 Operations                                    | 8              |

| Integrated Blocks and Their Functions                | 9              |

| Interrupt Processing                                 | 10             |

| Analog Value Processing                              | 11             |

| The Integral Real-Time Clock, for CPU 103 and Higher | 12             |

| Connecting the S5-100U to SINEC L1                   | 13             |

| Module Spectrum                                      | 14             |

| Function Modules                                     | 15             |

| Appendices                                           | A/B/C<br>D/E/F |

| Index                                                |                |

www.DataSheet4II.com

# Contents

|       |                                                  |                                                                                                                                                                                                                                                                | Page                                                     |

|-------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| How t | o Use T                                          | his Manual                                                                                                                                                                                                                                                     | xv                                                       |

| 1     | The S                                            | IMATIC S5 System Family                                                                                                                                                                                                                                        | 1 - 1                                                    |

| 2     | Techn                                            | iical Description                                                                                                                                                                                                                                              | 2 - 1                                                    |

|       | 2.1                                              | Programmable Controller Design                                                                                                                                                                                                                                 | 2 - 1                                                    |

|       | 2.2<br>2.2.1<br>2.2.2                            | Principle of Operation for the Programmable Controller  Functional Units                                                                                                                                                                                       | 2 - 3<br>2 - 3<br>2 - 6                                  |

| 3     | Install                                          | ation Guidelines                                                                                                                                                                                                                                               | 3 - 1                                                    |

|       | 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4          | Installing S5-100U Components Assembling a Tier Multi-Tier Expansion Cabinet Mounting Vertical Mounting                                                                                                                                                        | 3 - 1<br>3 - 1<br>3 - 5<br>3 - 7<br>3 - 8                |

|       | 3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4          | Wiring Connection Methods: Screw-Type Terminals and Crimp Snap-in Connecting the Power Supply to the S5-100U Connecting Digital Modules Connecting the Digital Input/Output Module                                                                             | 3 - 9<br>3 - 9<br>3 - 12<br>3 - 13<br>3 - 18             |

|       | 3.3<br>3.3.1<br>3.3.2<br>3.3.3                   | Electrical Configuration  Electrical Configuration for the S5-100U  Electrical Configuration with External I/Os  Non-Floating and Floating Configurations                                                                                                      | 3 - 20<br>3 - 20<br>3 - 21<br>3 - 25                     |

|       | 3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5 | Wiring Arrangement, Shielding, and Measures to Guard against Electromagnetic Interference Running Cables Inside and Outside a Cabinet Running Cables Outside Buildings Equipotential Bonding Shielding Cables Special Measures for Interference-Free Operation | 3 - 29<br>3 - 29<br>3 - 30<br>3 - 31<br>3 - 32<br>3 - 33 |

|                 |                                         |                                                                                                                                             | Page                                      |

|-----------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| ₩₩.<br><b>4</b> | DataSheet<br>Start-                     | 4U.com<br>Up and Program Tests                                                                                                              | 4 - 1                                     |

|                 | 4.1<br>4.1.1<br>4.1.2<br>4.1.3          | Operating Instructions CPU Operator Panel Operating Modes Performing an Overall Reset on the Programmable Controller                        | 4 - 1<br>4 - 1<br>4 - 1<br>4 - 2          |

|                 | 4.2<br>4.2.1<br>4.2.2                   | Starting Up a System Suggestions for Configuring and Installing the Product Procedures for Starting Up the Programmable Controller          | 4 - 3<br>4 - 3<br>4 - 4                   |

|                 | 4.3                                     | Loading the Program into the Programmable Controller                                                                                        | 4 - 5                                     |

|                 | 4.4<br>4.4.1<br>4.4.2                   | Backing Up the Program                                                                                                                      | 4 - 7<br>4 - 7<br>4 - 8                   |

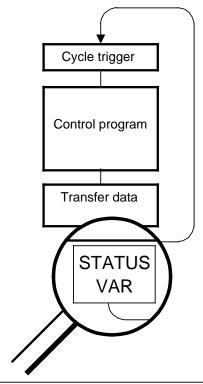

|                 | 4.5                                     | Program-Dependent Signal Status Display "STATUS"                                                                                            | 4 - 8                                     |

|                 | 4.6                                     | Direct Signal Status Display "STATUS VAR"                                                                                                   | 4 - 9                                     |

|                 | 4.7                                     | Forcing Outputs, "FORCE", for CPU 103 and Higher                                                                                            | 4 - 10                                    |

|                 | 4.8                                     | Forcing Variables, "FORCE VAR"                                                                                                              | 4 - 10                                    |

|                 | 4.9                                     | Search Function                                                                                                                             | 4 - 11                                    |

|                 | 4.10                                    | Program Check, for CPU 103 and Higher                                                                                                       | 4 - 11                                    |

| 5               | Diagn                                   | ostics and Troubleshooting                                                                                                                  | 5 - 1                                     |

|                 | 5.1                                     | Indication of Errors by LEDs                                                                                                                | 5 - 1                                     |

|                 | 5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4 | CPU Malfunctions  "ISTACK" Analysis Function Interrupt Analysis Errors during Program Copying Explanation of the Mnemonics Used in "ISTACK" | 5 - 1<br>5 - 1<br>5 - 4<br>5 - 5<br>5 - 6 |

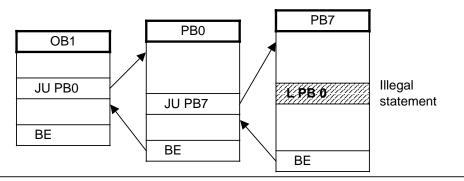

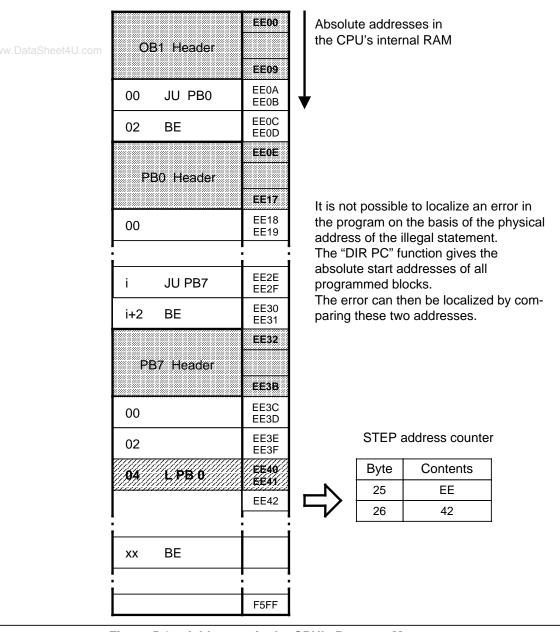

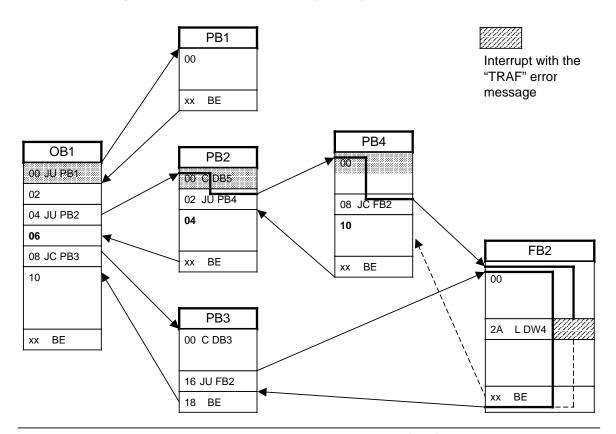

|                 | 5.3<br>5.3.1<br>5.3.2                   | Program Errors                                                                                                                              | 5 - 8<br>5 - 8<br>5 - 11                  |

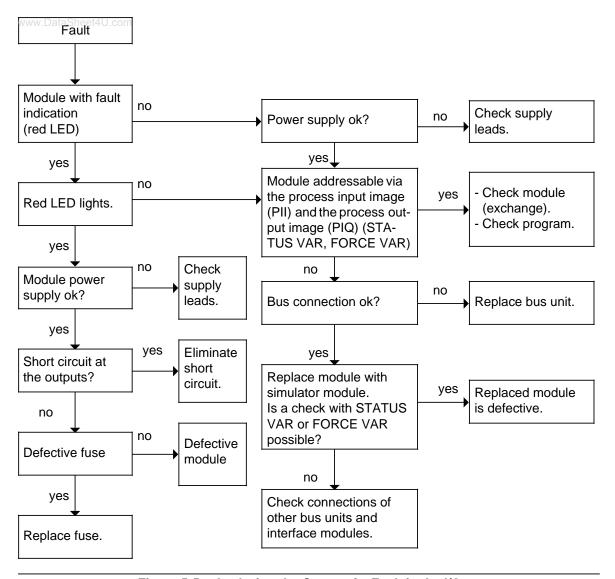

|                 | 5.4                                     | I/O Faults                                                                                                                                  | 5 - 12                                    |

|                 | 5.5                                     | System Parameters                                                                                                                           | 5 - 12                                    |

|                 | 5.6                                     | The Last Resort                                                                                                                             | 5 - 13                                    |

|   |                                                  |                                                                                                                                                                                       | Page                                         |

|---|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 6 | DataSheet4<br>Addre                              | lU.com<br>essing                                                                                                                                                                      | 6 - 1                                        |

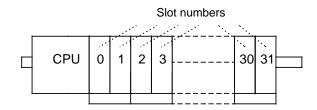

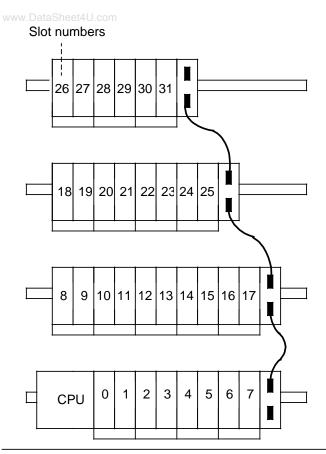

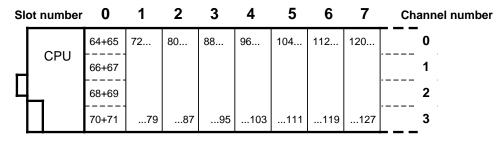

|   | 6.1                                              | Slot Numbering                                                                                                                                                                        | 6 - 1                                        |

|   | 6.2                                              | Digital Modules                                                                                                                                                                       | 6 - 4                                        |

|   | 6.3                                              | Analog Modules                                                                                                                                                                        | 6 - 5                                        |

|   | 6.4<br>6.4.1<br>6.4.2                            | Combined Input Modules and Output Modules Output Modules with Error Diagnostics Digital Input/Output Module, 16 Inputs, 16 Outputs, 24 V DC for All CPUs Version 8MA02 and Higher and | 6 - 6<br>6 - 6                               |

|   | 6.4.3                                            | for CPU 102, Version 8MA01, Revision 5 and Higher                                                                                                                                     | 6 - 7<br>6 - 7                               |

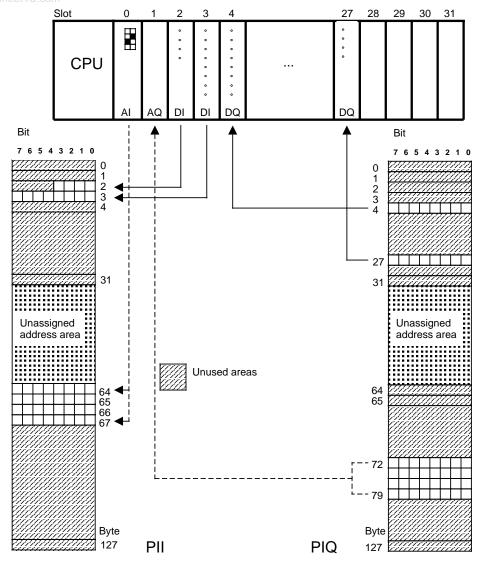

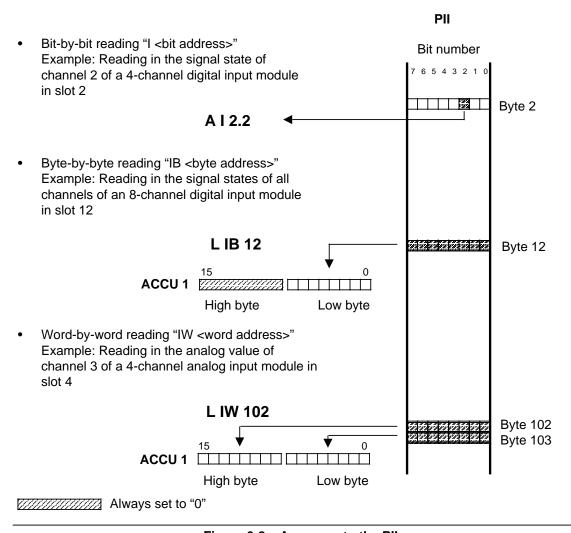

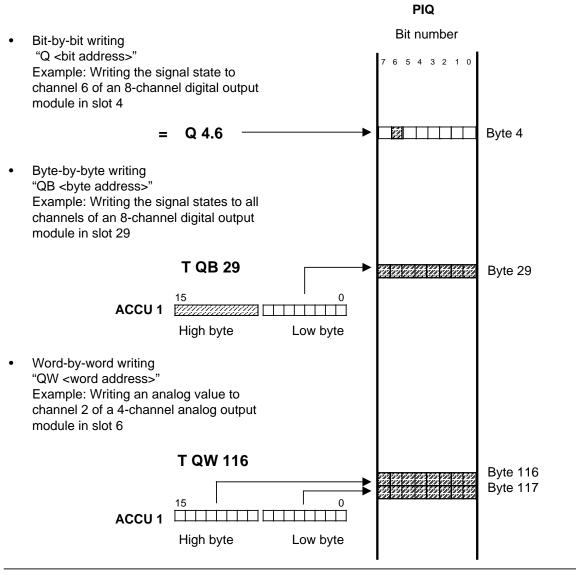

|   | 6.5<br>6.5.1<br>6.5.2                            | The Structure of Process Image Input and Output Tables                                                                                                                                | 6 - 8<br>6 - 10<br>6 - 11                    |

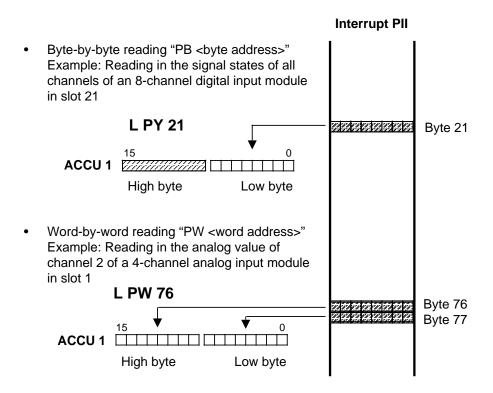

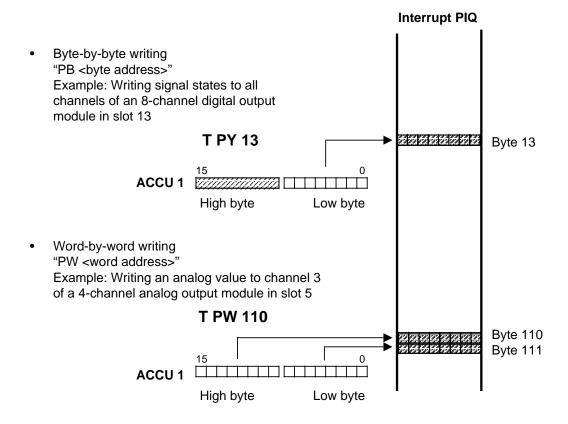

|   | 6.6<br>6.6.1<br>6.6.2                            | Interrupt Process Images Tables and Time-Controlled Program Processing in OB13 for CPU 103, Version 8MA02 and Higher Accessing the Interrupt PII Accessing the Interrupt PIQ          | 6 - 12<br>6 - 12<br>6 - 14                   |

|   | 6.7                                              | RAM Address Assignments                                                                                                                                                               | 6 - 15                                       |

| 7 | Introd                                           | uction to STEP 5                                                                                                                                                                      | 7 - 1                                        |

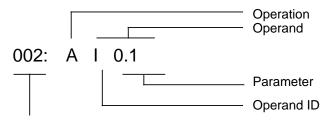

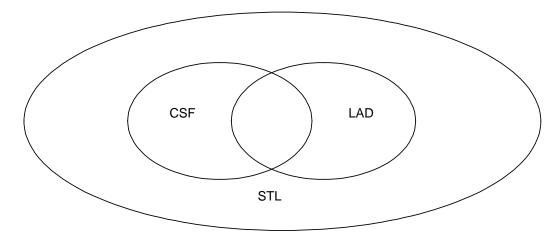

|   | 7.1<br>7.1.1<br>7.1.2<br>7.1.3                   | Writing a Program  Methods of Representation Operand Areas Circuit Diagram Conversion                                                                                                 | 7 - 1<br>7 - 1<br>7 - 3<br>7 - 3             |

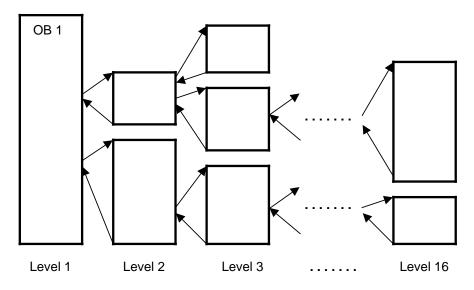

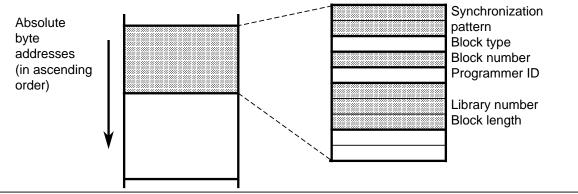

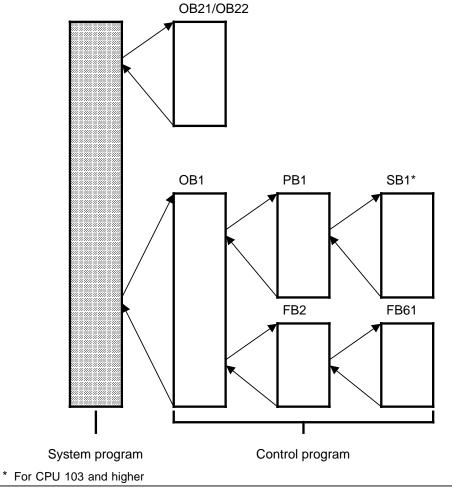

|   | 7.2<br>7.2.1<br>7.2.2                            | Program Structure                                                                                                                                                                     | 7 - 4<br>7 - 4<br>7 - 5                      |

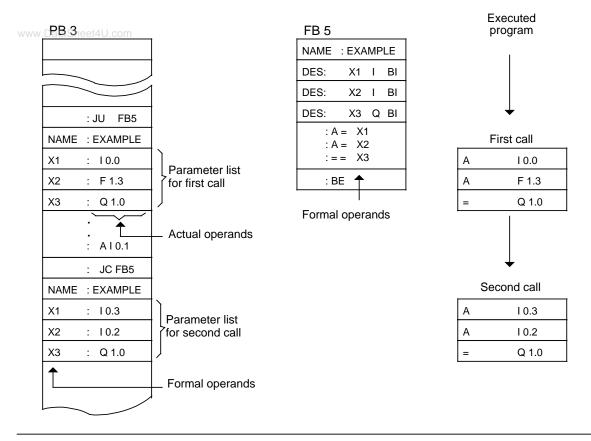

|   | 7.3<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>7.3.5 | Block Types Organization Blocks Program Blocks Sequence Blocks, for CPU 103 and Higher Function Blocks Data Blocks                                                                    | 7 - 7<br>7 - 9<br>7 - 11<br>7 - 11<br>7 - 16 |

|   | 7.4<br>7.4.1<br>7.4.2<br>7.4.3                   | Program Processing Program Processing with CPU 102 START-UP Program Processing Cyclic Program Processing Time Controlled Program Processing for CPU 102                               | 7 - 18<br>7 - 19<br>7 - 24<br>7 - 26         |

|   | 7.4.4                                            | Time-Controlled Program Processing, for CPU 103  Version 8MA02 and Higher                                                                                                             | 7 - 28                                       |

|   |                     |                                                                | Page   |

|---|---------------------|----------------------------------------------------------------|--------|

|   | DataSheet4<br>7.4.5 | U.com Interrupt-Driven Program Processing, for CPU 103         |        |

|   |                     | Version 8MA02 and Higher                                       | 7 - 29 |

|   | 7.5                 | Processing Blocks                                              | 7 - 30 |

|   | 7.5.1               | Changing Programs                                              | 7 - 30 |

|   | 7.5.2               | Changing Blocks                                                | 7 - 30 |

|   | 7.5.3               | Compressing the Program Memory                                 | 7 - 30 |

|   | 7.6                 | Number Representation                                          | 7 - 31 |

| 8 | STEP                | 5 Operations                                                   | 8 - 1  |

|   | 8.1                 | Basic Operations                                               | 8 - 1  |

|   | 8.1.1               | Boolean Logic Operations                                       | 8 - 2  |

|   | 8.1.2               | Set/Reset Operations                                           | 8 - 7  |

|   | 8.1.3               | Load and Transfer Operations                                   | 8 - 10 |

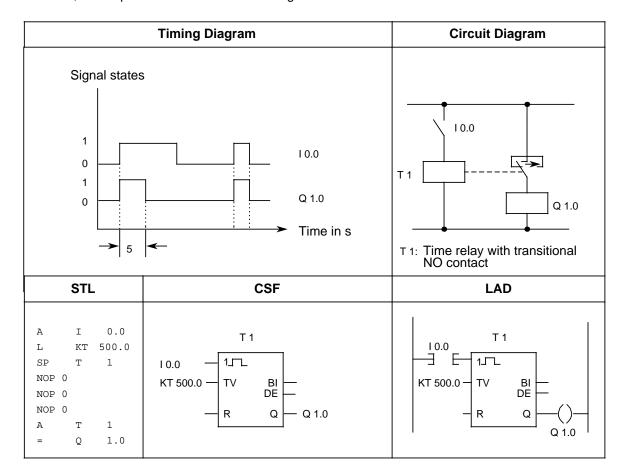

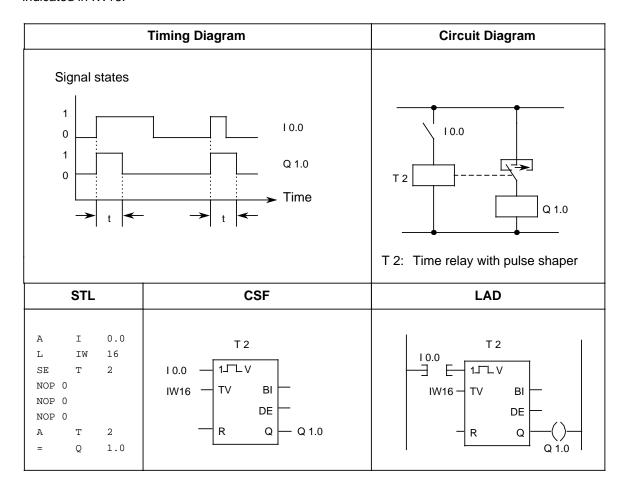

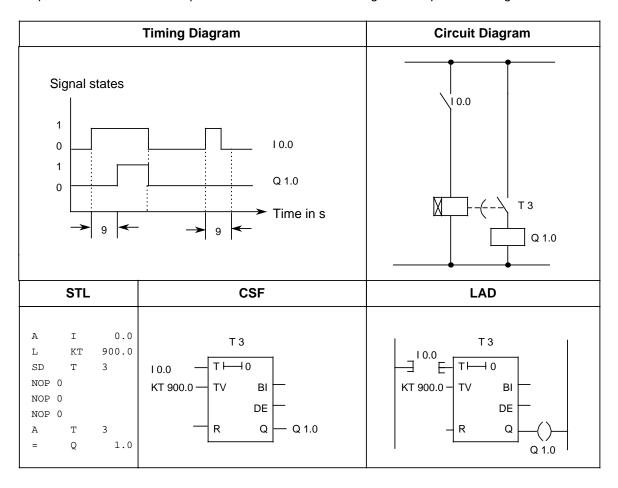

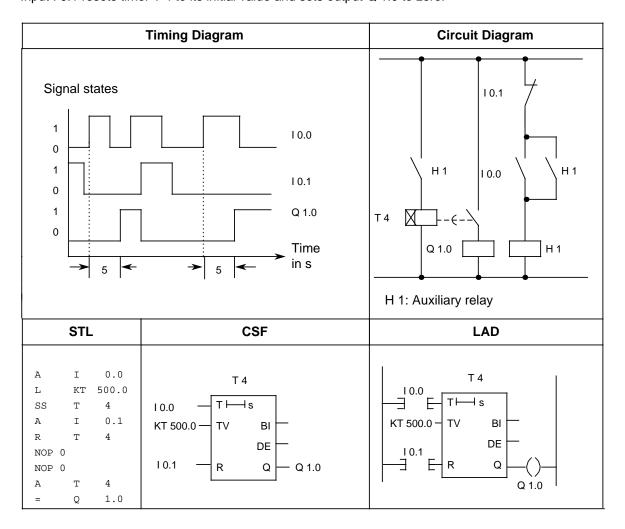

|   | 8.1.4               | Timer Operations                                               | 8 - 15 |

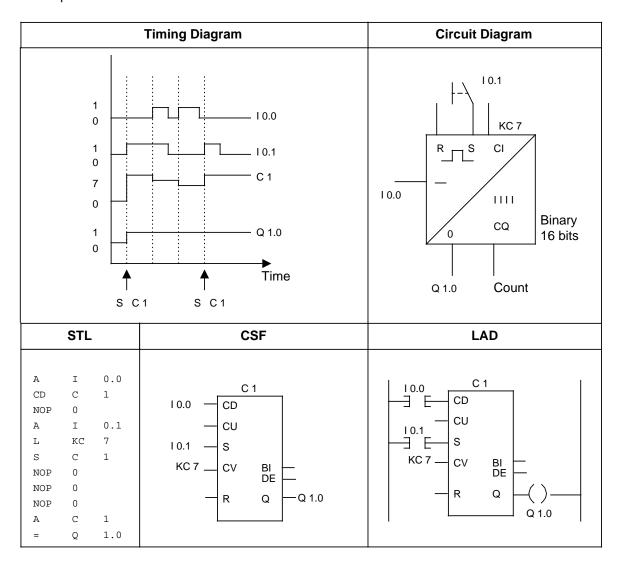

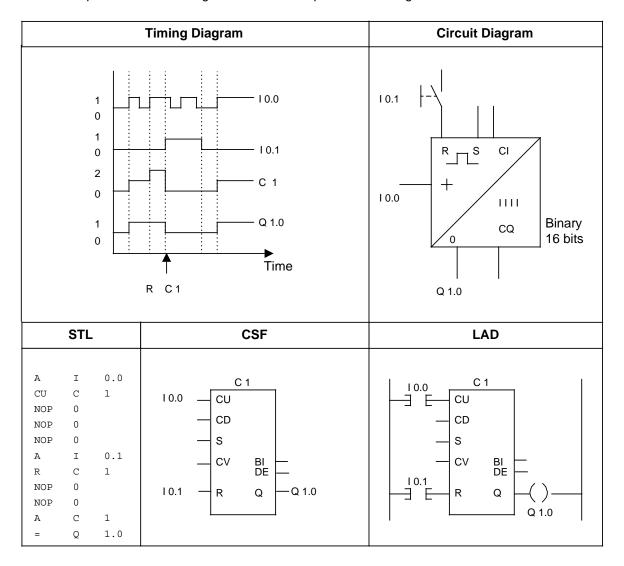

|   | 8.1.5               | Counter Operations                                             | 8 - 25 |

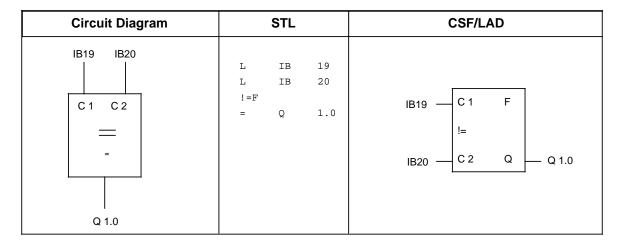

|   | 8.1.6               | Comparison Operations                                          | 8 - 30 |

|   | 8.1.7               | Arithmetic Operations                                          | 8 - 31 |

|   | 8.1.8               | Block Call Operations                                          | 8 - 33 |

|   | 8.1.9               | Other Operations                                               | 8 - 38 |

|   | 8.2                 | Supplementary Operations                                       | 8 - 39 |

|   | 8.2.1               | Load Operation, for CPU 103 and Higher                         | 8 - 40 |

|   | 8.2.2               | Enable Operation, for CPU 103 and Higher                       | 8 - 41 |

|   | 8.2.3               | Bit Test Operations, for CPU 103 and Higher                    | 8 - 42 |

|   | 8.2.4               | Digital Logic Operations                                       | 8 - 44 |

|   | 8.2.5               | Shift Operations                                               | 8 - 48 |

|   | 8.2.6               | Conversion Operations                                          | 8 - 50 |

|   | 8.2.7               | Decrement/Increment, for CPU 103 and Higher                    | 8 - 52 |

|   | 8.2.8               | Disable/Enable Interrupt, for CPU 103 Version 8MA02 and Higher | 8 - 53 |

|   | 8.2.9               | "DO" Operation, for CPU 103 and Higher                         | 8 - 54 |

|   | 8.2.10              | Jump Operations                                                | 8 - 56 |

|   | 8.2.11              | Substitution Operations, for CPU 103 and Higher                | 8 - 58 |

|   | 8.3                 | System Operations, for CPU 103 and Higher                      | 8 - 64 |

|   | 8.3.1               | Set Operations                                                 | 8 - 64 |

|   | 8.3.2               | Load and Transfer Operations                                   | 8 - 64 |

|   | 8.3.3               | Arithmetic Operations                                          | 8 - 67 |

|   | 8.3.4               | Other Operations                                               | 8 - 68 |

|   | 8.4                 | Condition Code Generation                                      | 8 - 69 |

|   | 8.5                 | Sample Programs                                                | 8 - 71 |

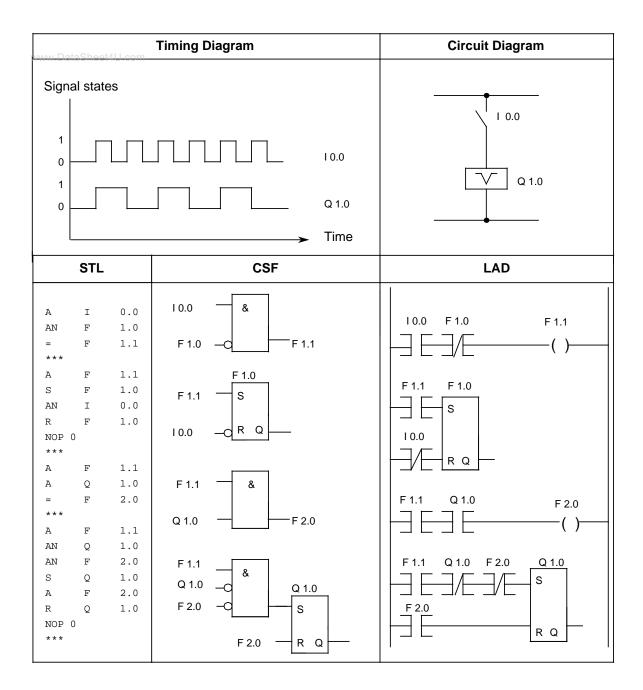

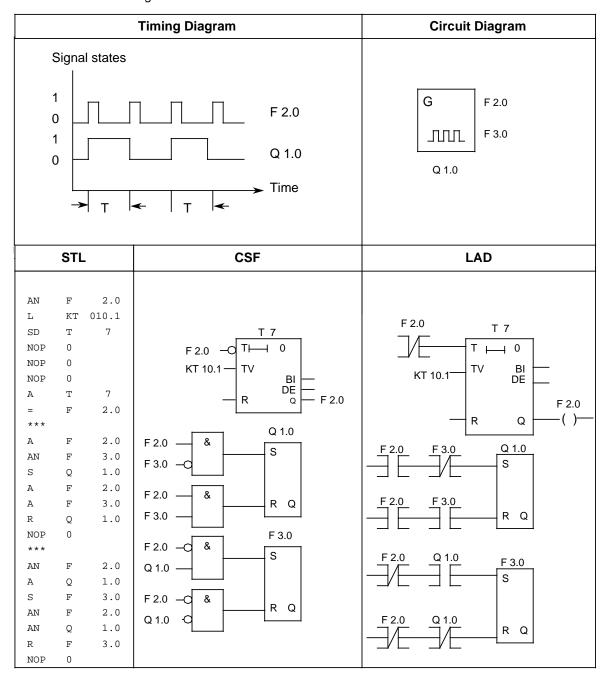

|   | 8.5.1               | Momentary-Contact Relay/Edge Evaluation                        | 8 - 71 |

|   | 8.5.2               | Binary Scaler/Binary Divider                                   | 8 - 71 |

|   | 853                 | Clock/Clock-Pulse Generator                                    | 8 - 73 |

|    |                       |                                                                           | Page    |

|----|-----------------------|---------------------------------------------------------------------------|---------|

| 9  | DataSheet4<br>Integra | ted Blocks and Their Functions                                            | 9 - 1   |

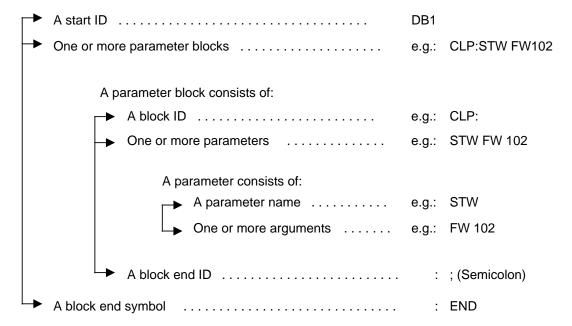

|    | 9.1                   | Assigning Internal Functions to DB1, for CPU 103 Version 8MA03 and Higher | 9 - 1   |

|    | 9.1.1                 | Configuration and Default Settings for DB1                                | 9 - 1   |

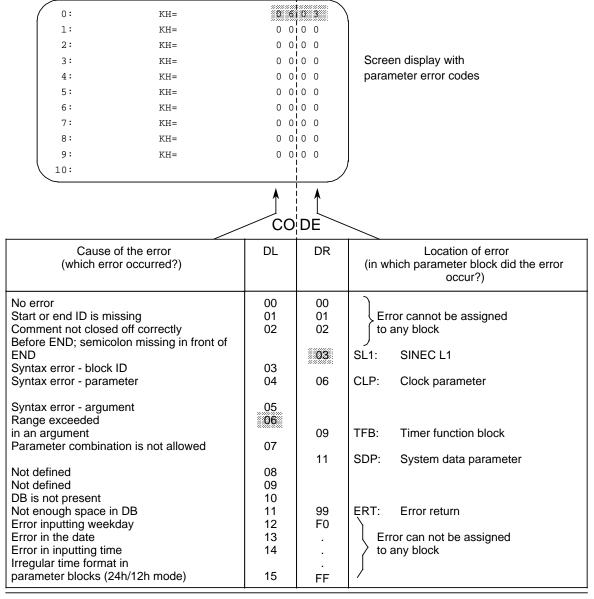

|    | 9.1.1                 | Setting the Address for the Parameter Error Code in DB1                   | 9 - 2   |

|    | 9.1.2                 | Assigning Parameters in DB1                                               | 9 - 4   |

|    | 9.1.4                 | Rules for Setting Parameters in DB1                                       | 9 - 4   |

|    | 9.1.4                 |                                                                           | 9 - 4   |

|    | 9.1.5                 | How to Recognize and Correct Parameter Errors                             | 9 - 0   |

|    | 9.1.6                 | Transferring DB1 Parameters to the Programmable Controller                | 9 - 9   |

|    | 9.1.7                 | Defining System Characteristics in DB1                                    | 9 - 10  |

|    | 9.2                   | Integrated Function Blocks,                                               |         |

|    |                       | for CPU 102 Version 8MA02 and Higher                                      | 9 - 11  |

|    | 9.2.1                 | Code Converter : B4 - FB240                                               | 9 - 12  |

|    | 9.2.2                 | Code Converter : 16 - FB241                                               | 9 - 12  |

|    | 9.2.3                 | Multiplier: 16 - FB242                                                    | 9 - 13  |

|    | 9.2.4                 | Divider: 16 - FB243                                                       | 9 - 13  |

|    | 9.2.5                 | Analog Value Conditioning Modules FB250 and FB251                         | 9 - 14  |

|    | 9.3                   | Integrated Organization Blocks                                            | 9 - 14  |

|    | 9.3.1                 | Scan Time Triggering OB31, for CPU 103 and Higher                         | 9 - 14  |

|    | 9.3.2                 | Battery Failure OB34                                                      | 9 - 14  |

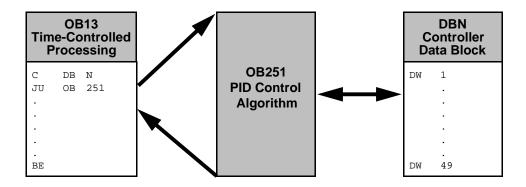

|    | 9.3.3                 | OB251 PID Algorithm,                                                      |         |

|    |                       | for CPU 103 Version 8MA02 and Higher                                      | 9 - 15  |

| 10 | Interru               | pt Processing                                                             | 10 - 1  |

|    | 10.1                  | Interrupt Processing with OB2, for CPU 103                                |         |

|    |                       | Version 8MA02 and Higher                                                  | 10 - 1  |

|    | 10.2                  | Calculating Interrupt Reaction Times                                      | 10 - 5  |

| 11 | Analog                | g Value Processing                                                        | 11 - 1  |

| •  | 7111010               | , value i recoccing                                                       |         |

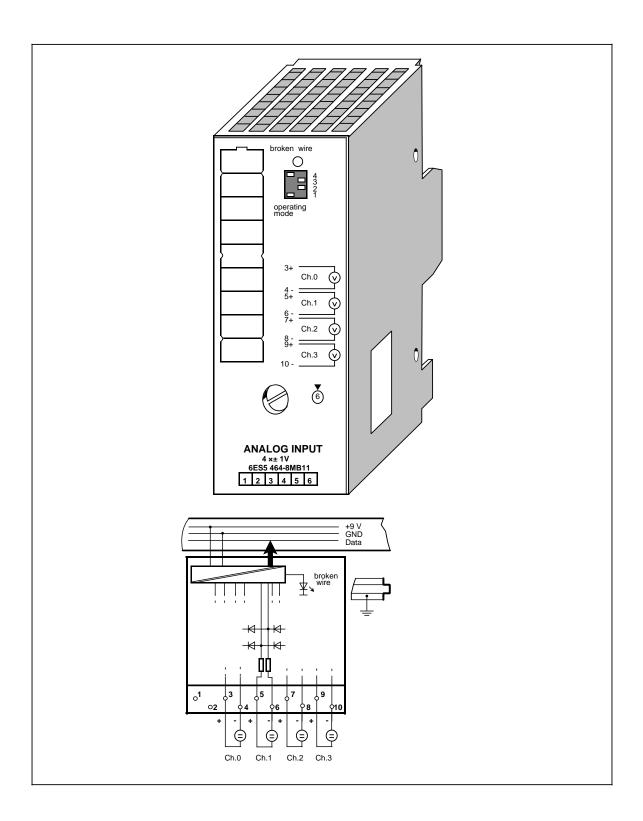

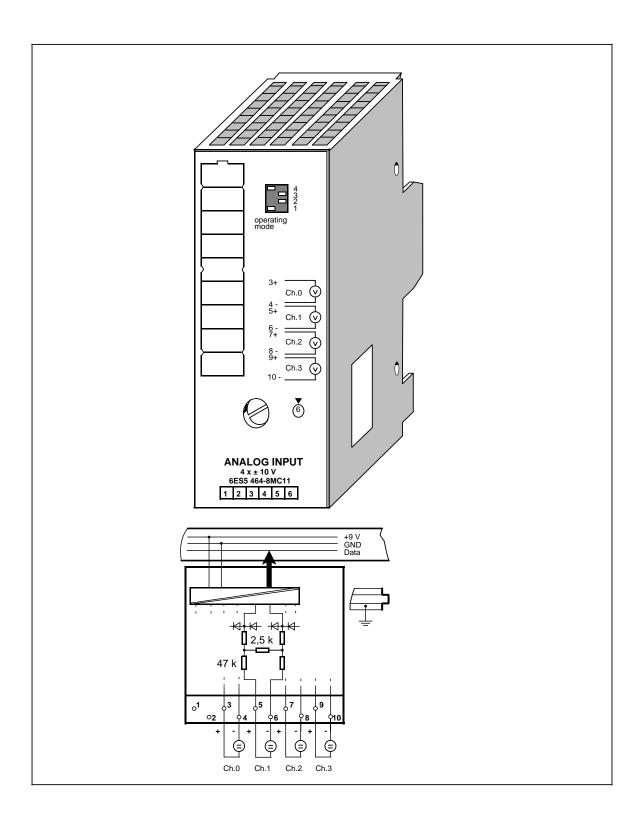

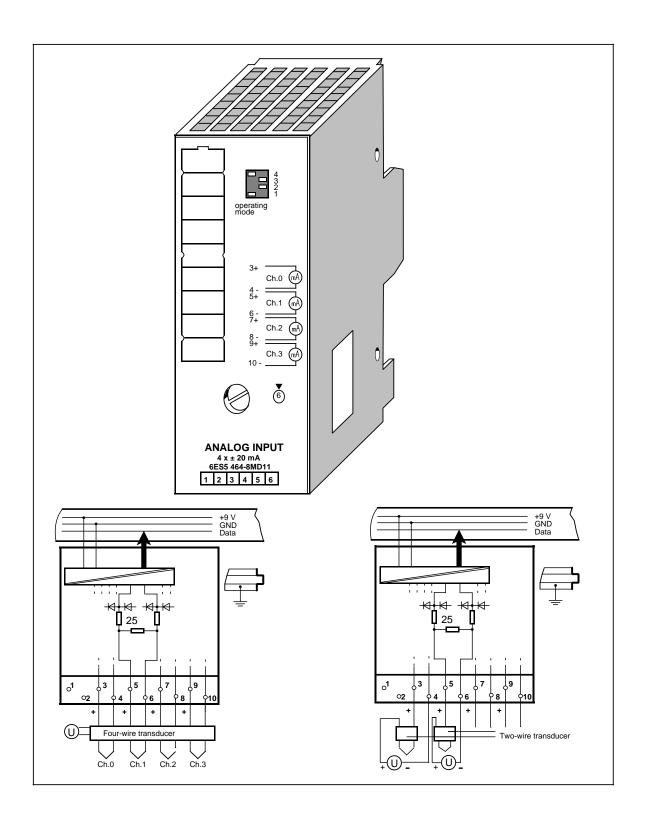

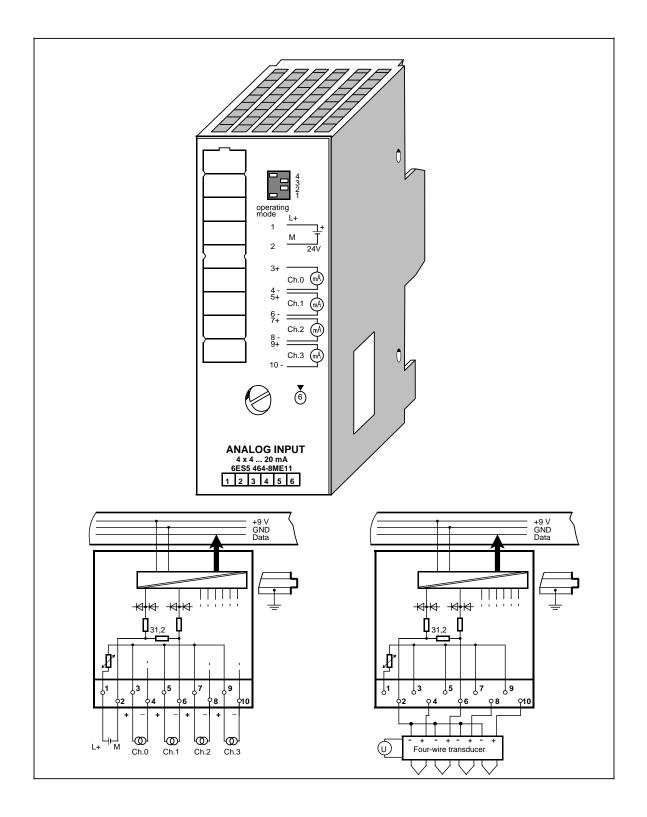

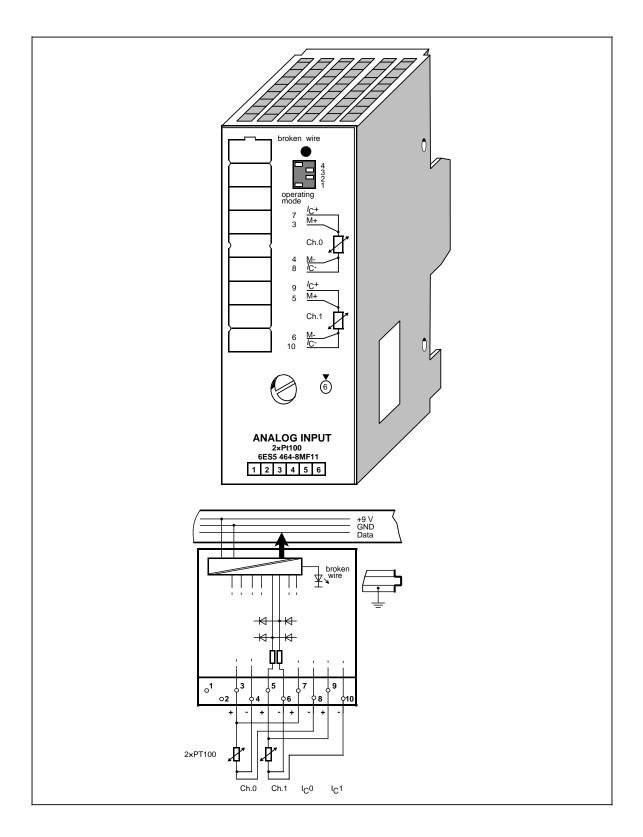

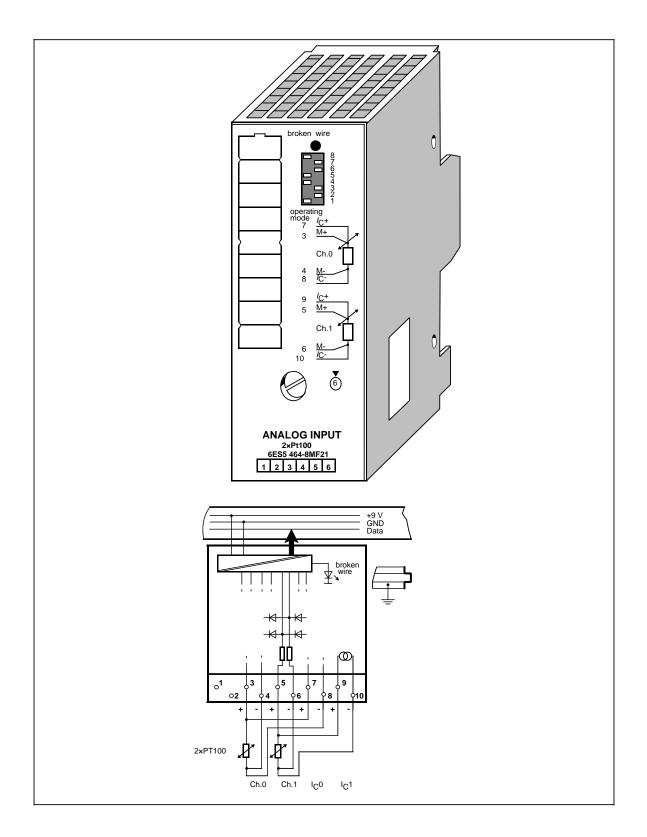

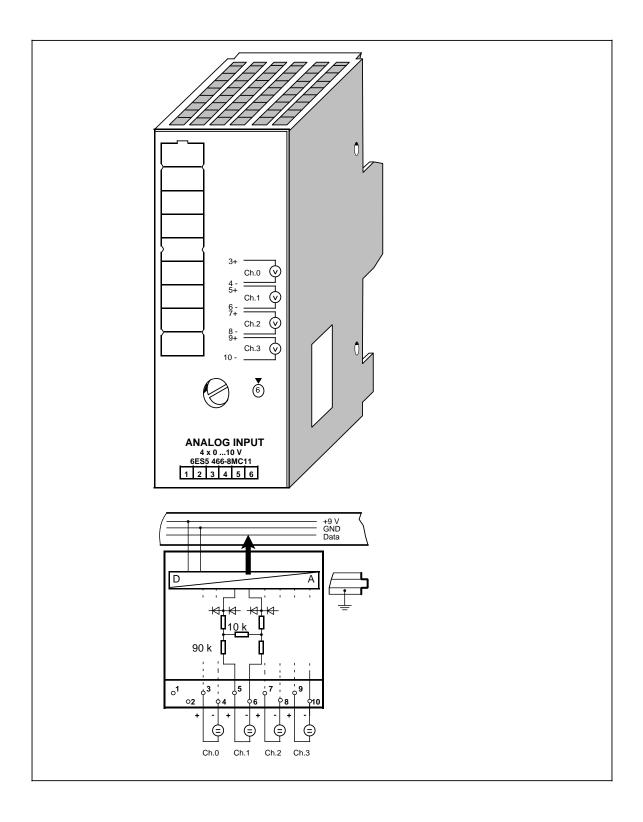

|    | 11.1                  | Analog Input Modules                                                      | 11 - 1  |

|    | 11.2                  | Connecting Current and Voltage Sensors to Analog                          |         |

|    | 11.2.1                | <b>9</b>                                                                  | 11 - 1  |

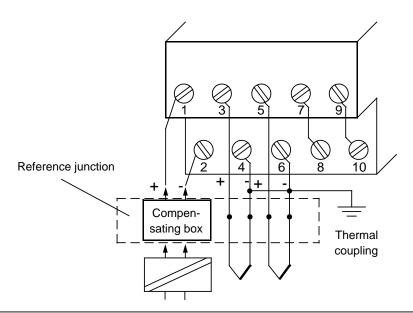

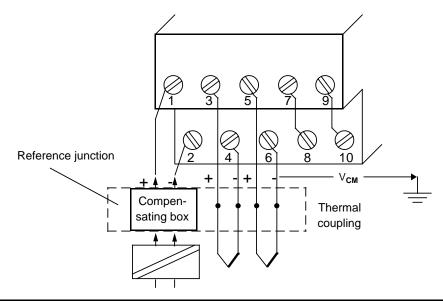

|    |                       | Non-Isolated Thermocouples                                                | 11 - 2  |

|    |                       | Two-Wire Connection of Voltage Sensors                                    | 11 - 3  |

|    |                       | Two-Wire Connection of Current Sensors                                    | 11 - 4  |

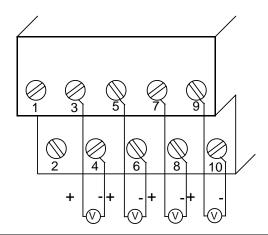

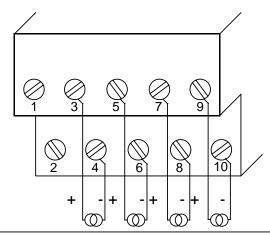

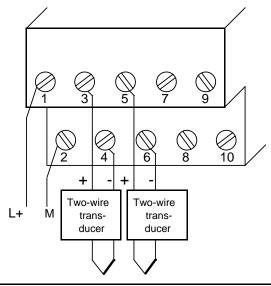

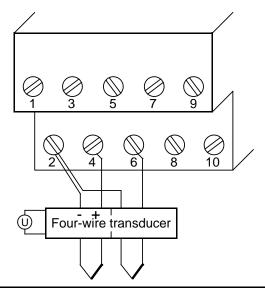

|    |                       | Connection of Two-Wire and Four-Wire Transducers                          | 11 - 4  |

|    | 11.2.5                | Connection of Resistance Thermometers                                     | 11 - 6  |

|    | 11.3                  | Start-Up of Analog Input Modules                                          | 11 - 7  |

|    | 11.4                  | Analog Value Representation of Analog Input Modules                       | 11 - 11 |

EWA 4NEB 812 6120-02b İΧ

|    |                                      |                                                                                                                                                                                                                                           | Page                                                |

|----|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

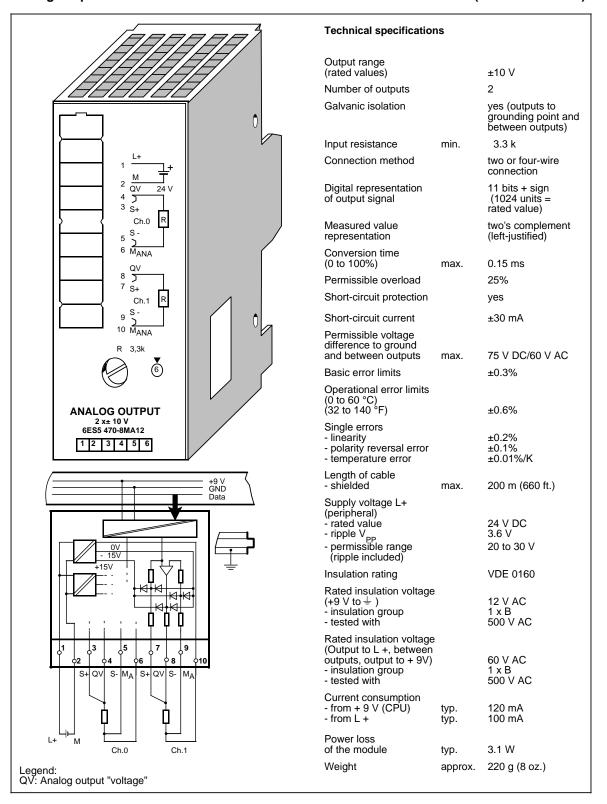

|    |                                      | Analog Output Modules                                                                                                                                                                                                                     | 11 - 19<br>11 - 19<br>11 - 20                       |

|    | 11.6<br>11.6.1<br>11.6.2             | Analog Value Conversion: Function Blocks FB250 and FB251                                                                                                                                                                                  | 11 - 22<br>11 - 22<br>11 - 25                       |

| 12 | The Int                              | tegral Real-Time Clock, for CPU 103 Version 8MA02 and Higher                                                                                                                                                                              | 12 - 1                                              |

|    | 12.1                                 | Function                                                                                                                                                                                                                                  | 12 - 1                                              |

|    | 12.2<br>12.2.1<br>12.2.2<br>12.2.3   | Setting Parameters in DB1, for CPU 103 Version 8MA03 and Higher                                                                                                                                                                           | 12 - 2<br>12 - 2<br>12 - 3<br>12 - 4                |

|    |                                      | Programming the Integral Real-Time Clock in DB1, for CPU 103 Version 8MA03 and Higher Setting the Clock in DB1 Setting the Prompt Time in DB1 Setting the Operating Hours Counter in DB1 Entering the Clock Time Correction Factor in DB1 | 12 - 5<br>12 - 5<br>12 - 6<br>12 - 7<br>12 - 7      |

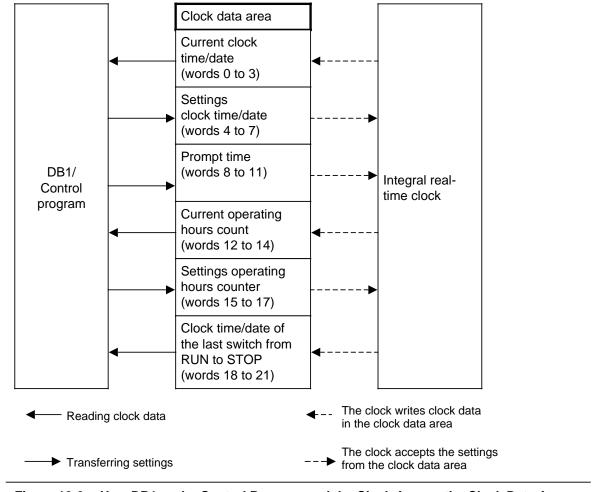

|    | 12.4                                 | Structure of the Clock Data Area                                                                                                                                                                                                          | 12 - 8                                              |

|    | 12.5                                 | Structure of the Status Word and How to Scan It                                                                                                                                                                                           | 12 - 12                                             |

|    | 12.6                                 | Setting Parameters for the Clock Data Area and the Status Word in the System Data Area                                                                                                                                                    | 12 - 15                                             |

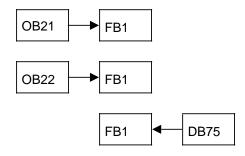

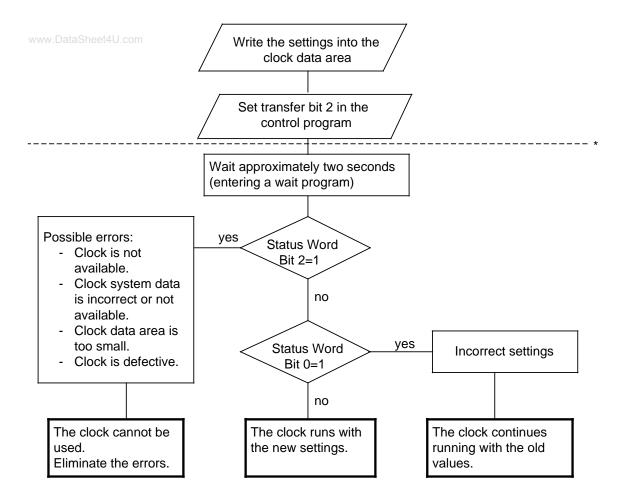

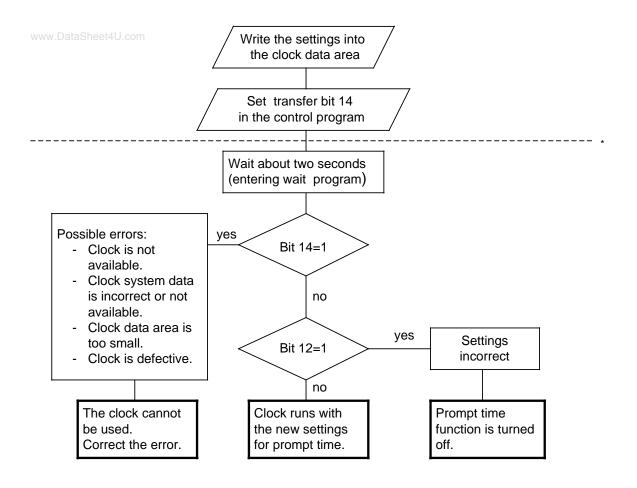

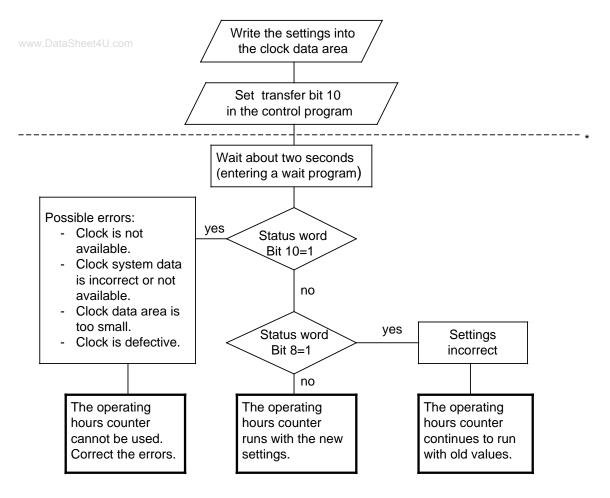

|    | 12.7.1<br>12.7.2<br>12.7.3<br>12.7.4 | Programming the Integral Real-Time Clock in the User Program Reading and Setting the Clock Programming the Prompt Function Programming the Operating Hours Counter Entering the Clock Time Correction Factor                              | 12 - 21<br>12 - 21<br>12 - 25<br>12 - 30<br>12 - 35 |

|        |                                    |                                                                                                                                                                                      | Page                                     |

|--------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| www.Da | Conne                              | cting the S5-100U to SINEC L1, for CPU 102 and Higher                                                                                                                                | 13 - 1                                   |

|        | 13.1                               | Connecting the Programmable Controllers to the L1 Bus Cable                                                                                                                          | 13 - 1                                   |

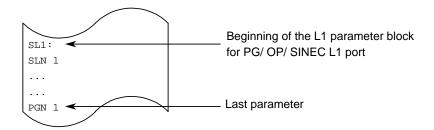

|        | 13.2<br>13.2.1<br>13.2.2           | Setting Parameters in the Programmable Controller for Exchanging Data  How to Program in a Function Block, for CPU 102 and Higher  Setting Parameters in DB1, for CPU 103 and Higher | 13 - 1<br>13 - 2<br>13 - 5               |

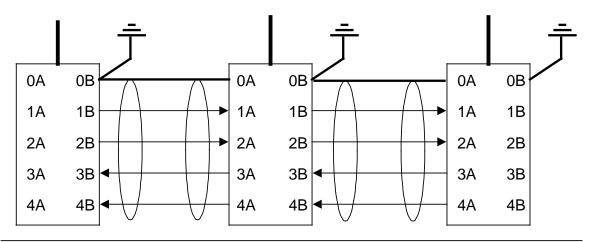

|        |                                    | Coordinating Data Exchange in the Control Program                                                                                                                                    | 13 - 7<br>13 - 8<br>13 - 9<br>13 - 11    |

| 14     | Module                             | e Spectrum                                                                                                                                                                           | 14 - 1                                   |

|        | 14.1                               | General Technical Specifications                                                                                                                                                     | 14 - 3                                   |

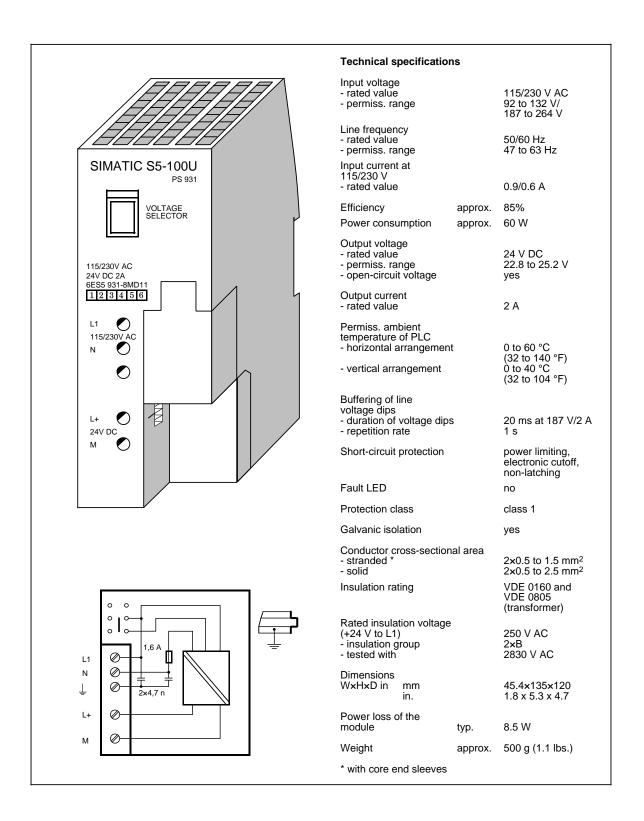

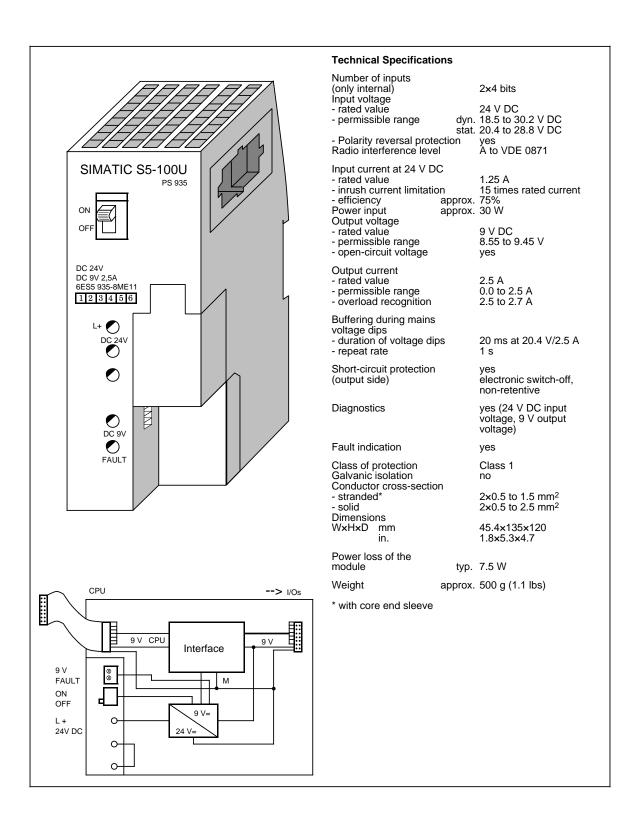

|        | 14.2                               | Power Supply Modules                                                                                                                                                                 | 14 - 4                                   |

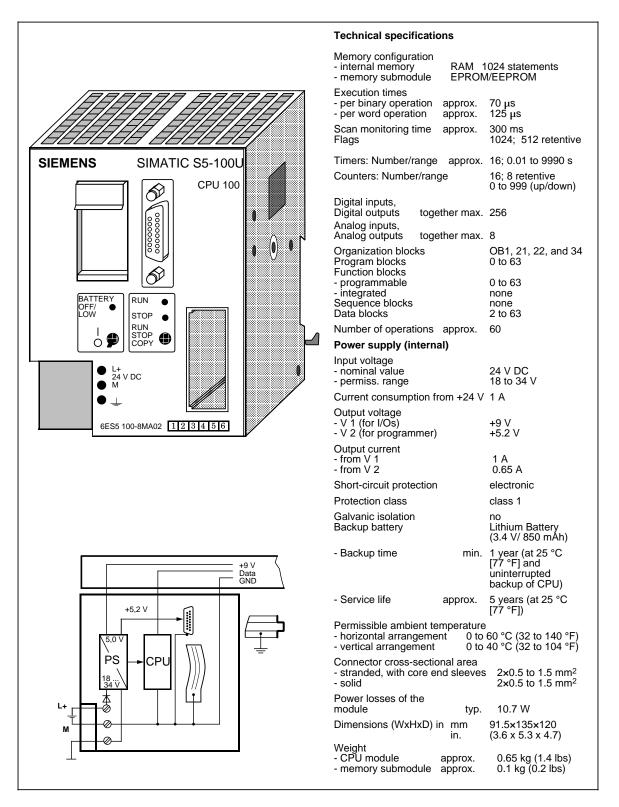

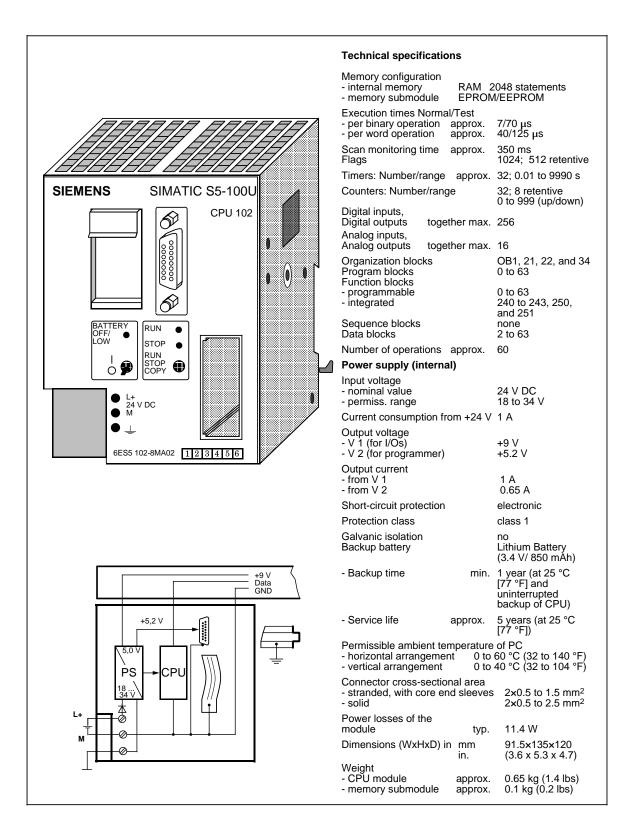

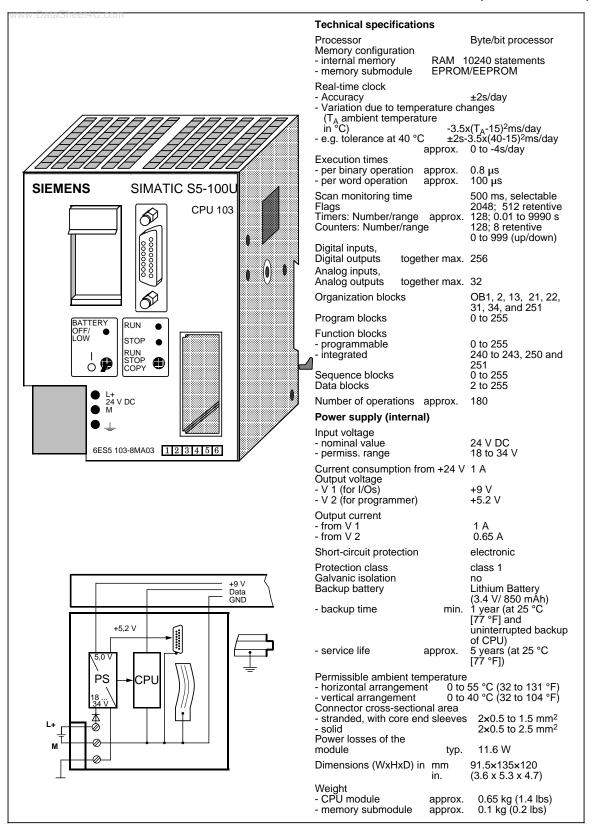

|        | 14.3                               | Central Processing Units                                                                                                                                                             | 14 - 7                                   |

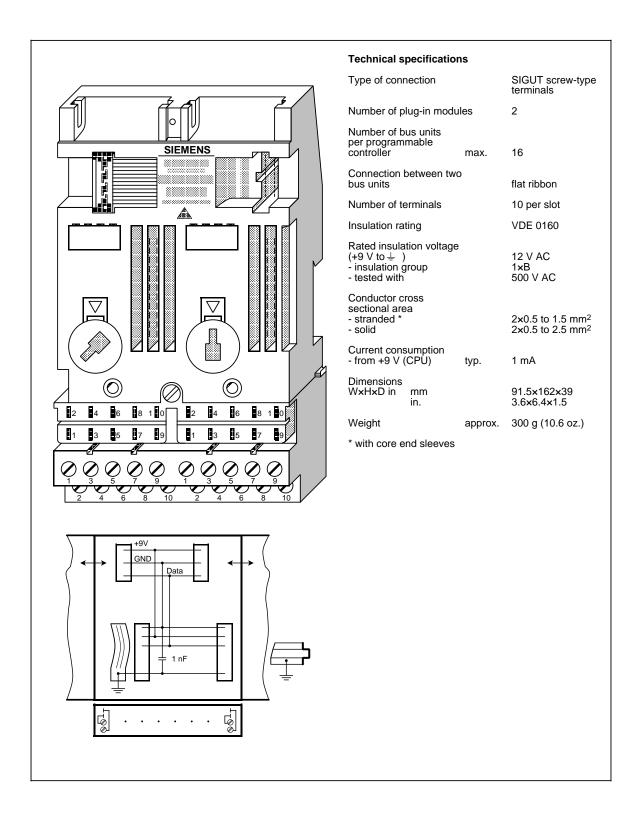

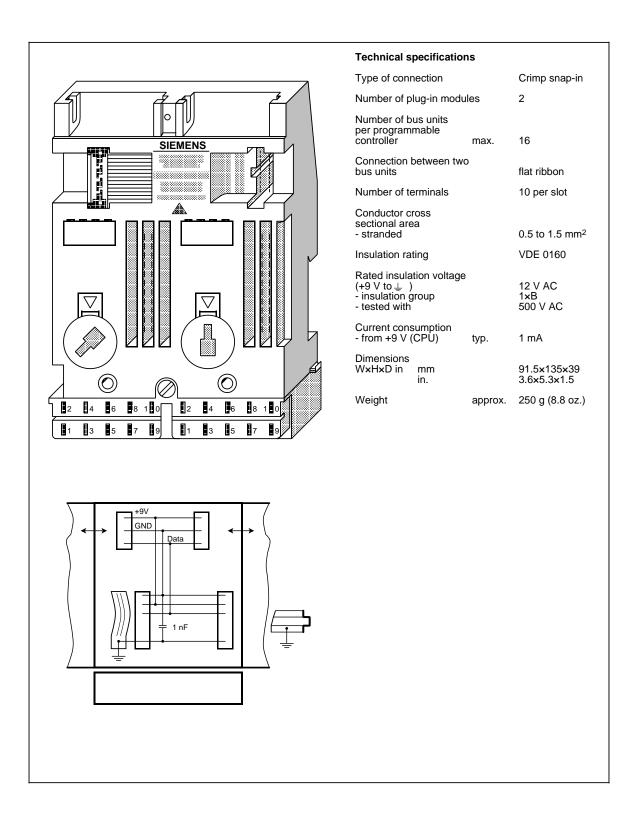

|        | 14.4                               | Bus Units                                                                                                                                                                            | 14 - 10                                  |

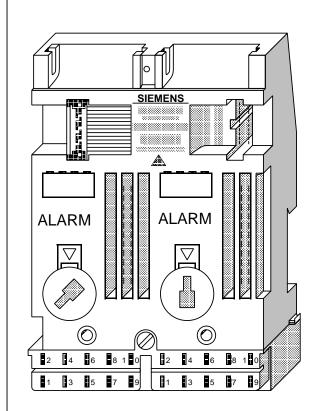

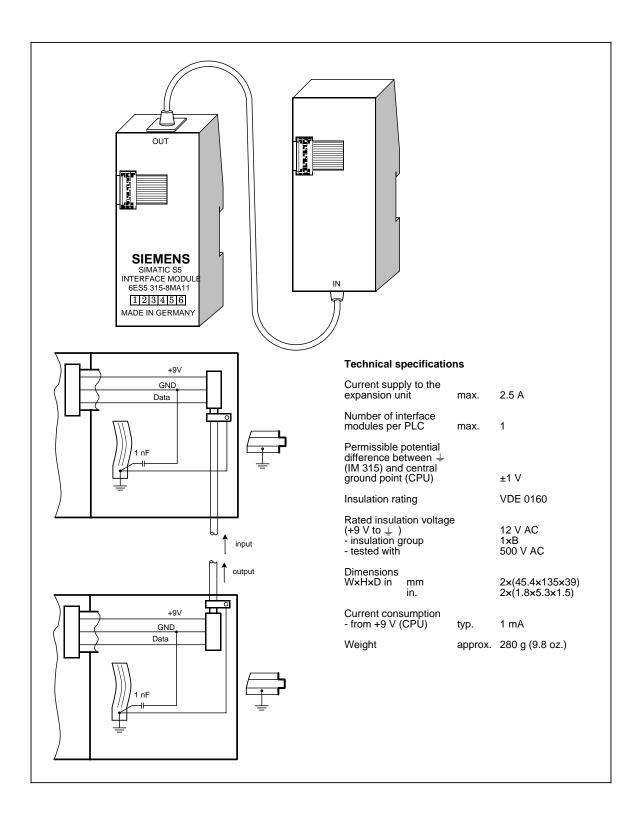

|        | 14.5                               | Interface Modules                                                                                                                                                                    | 14 - 14                                  |

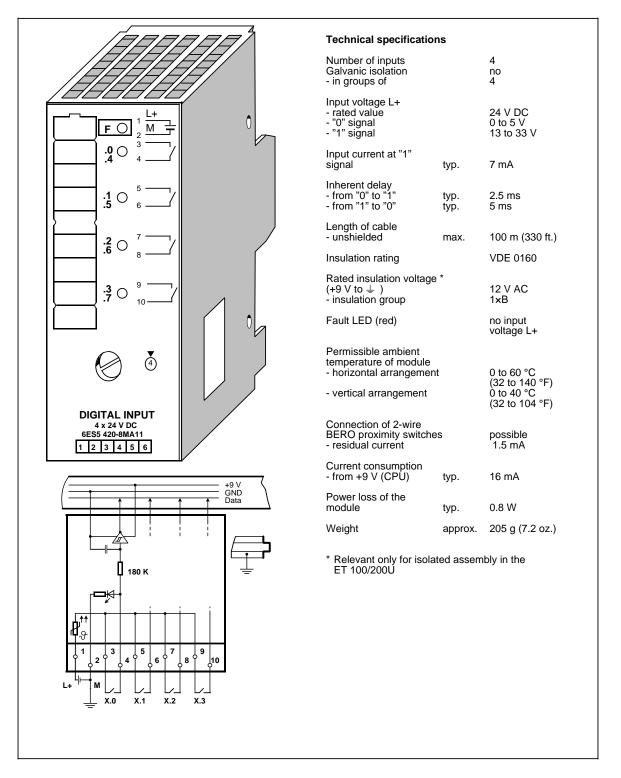

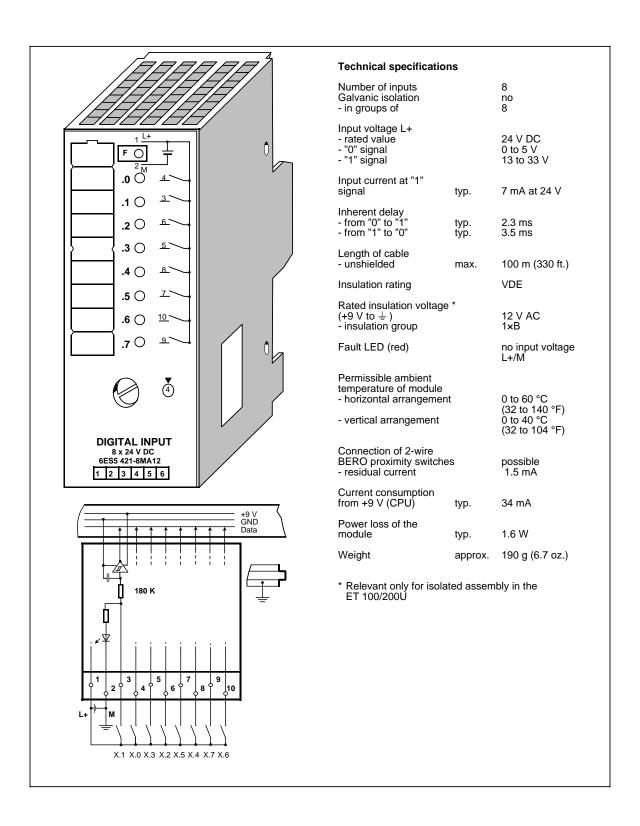

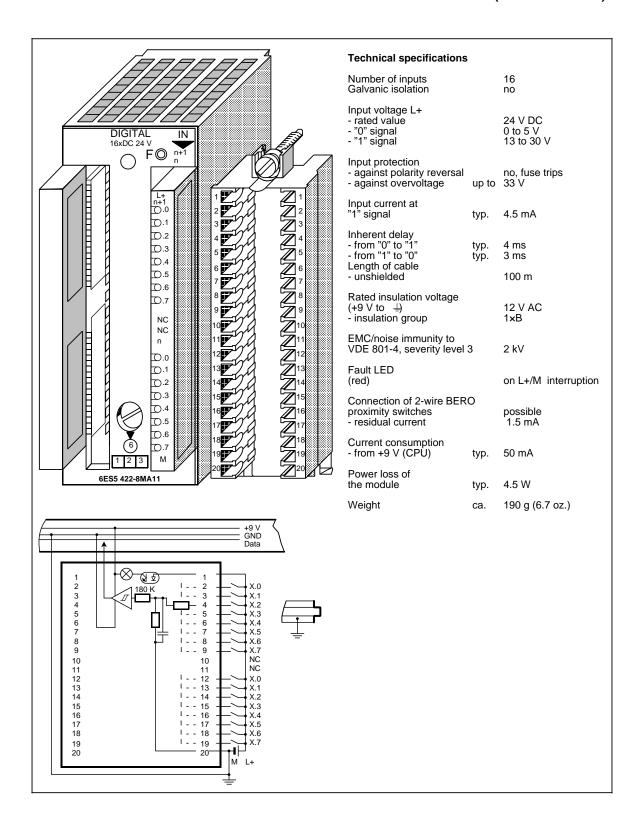

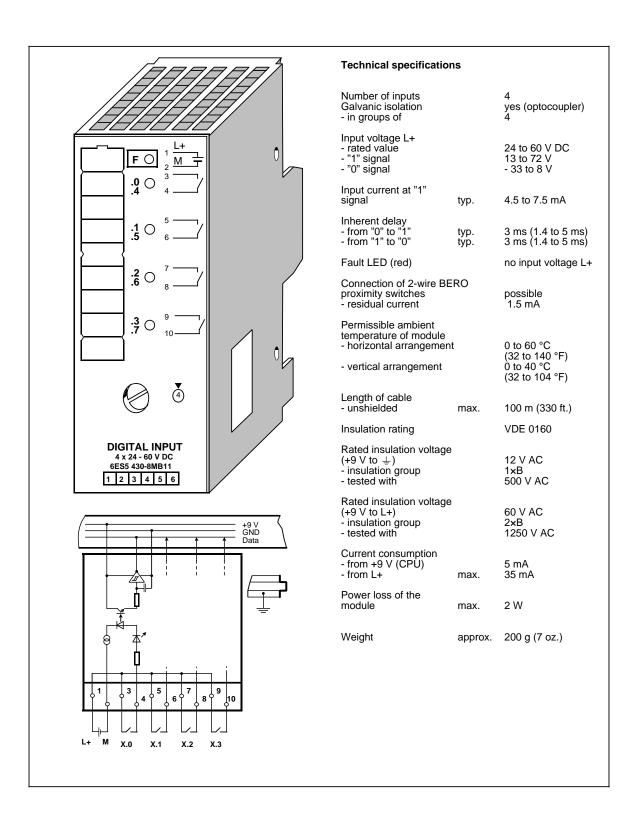

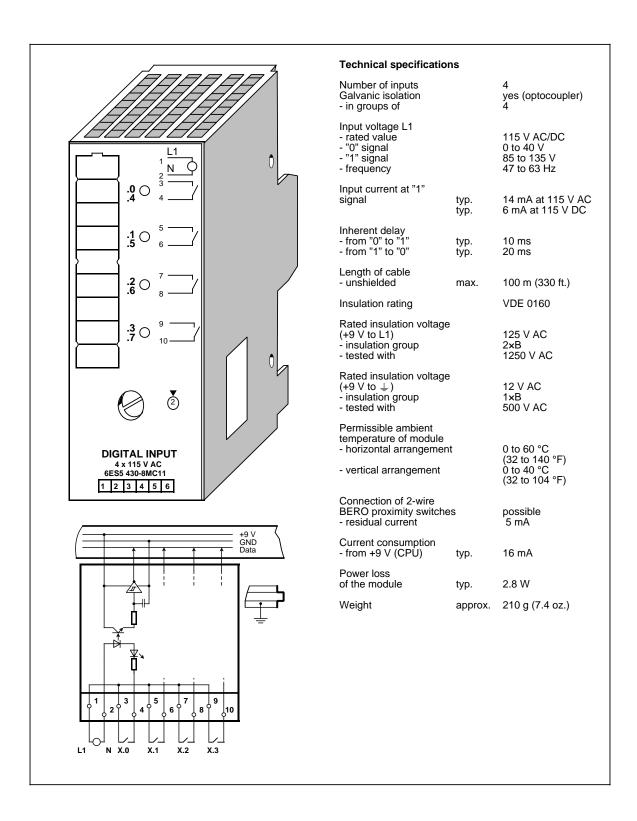

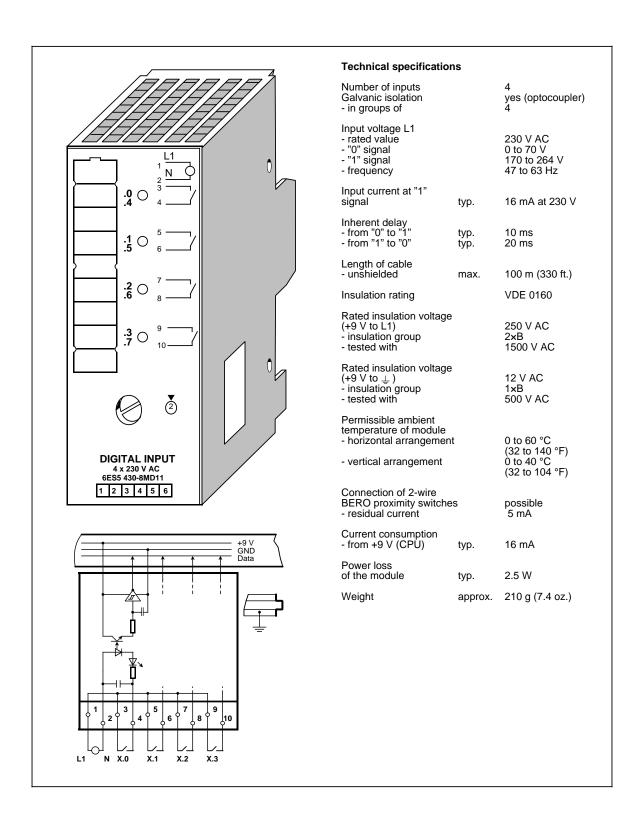

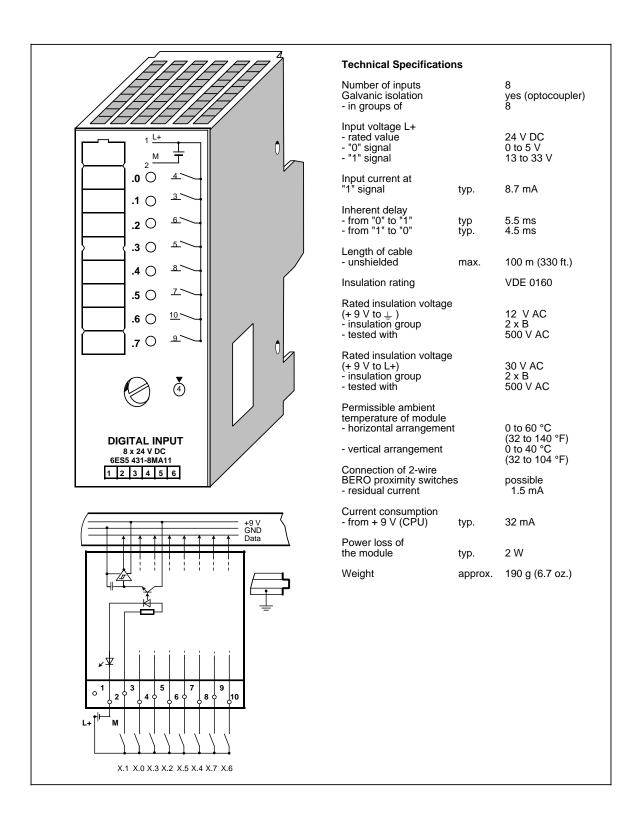

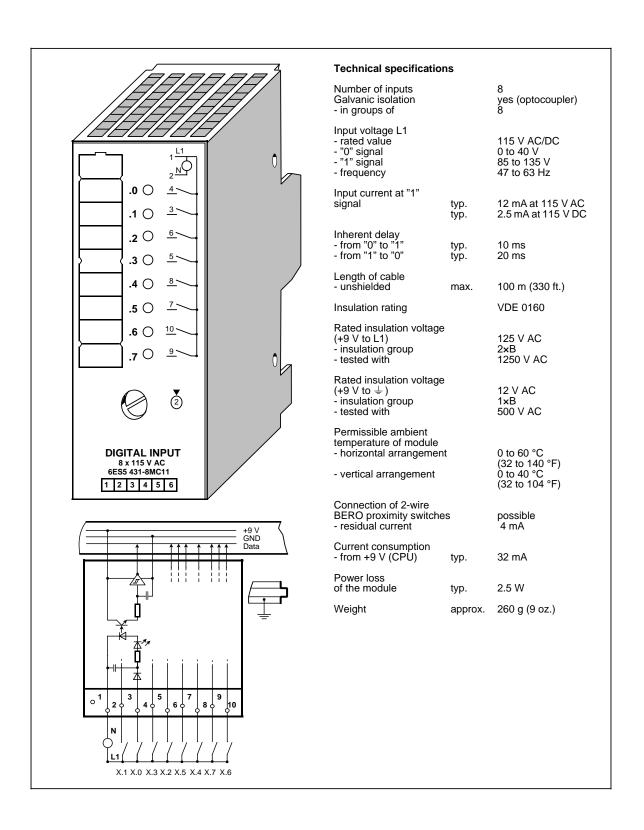

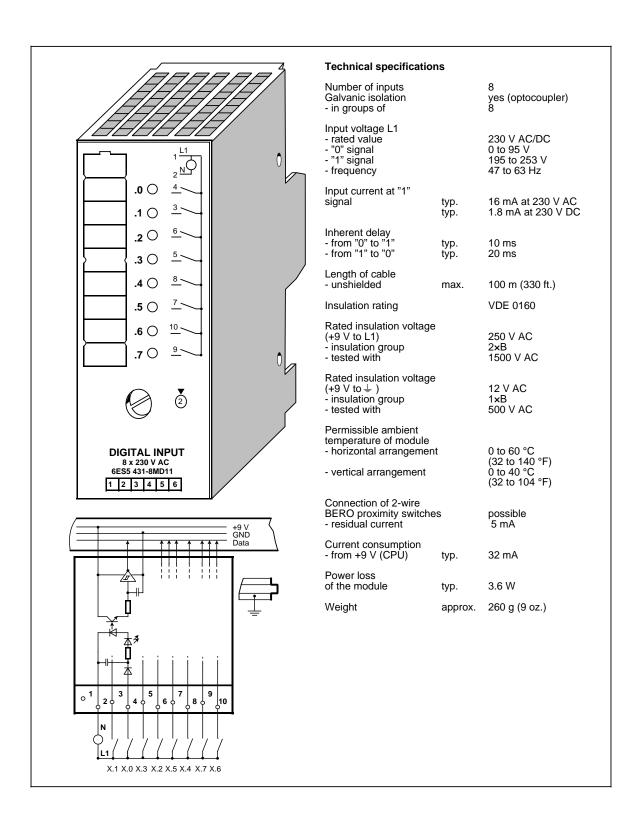

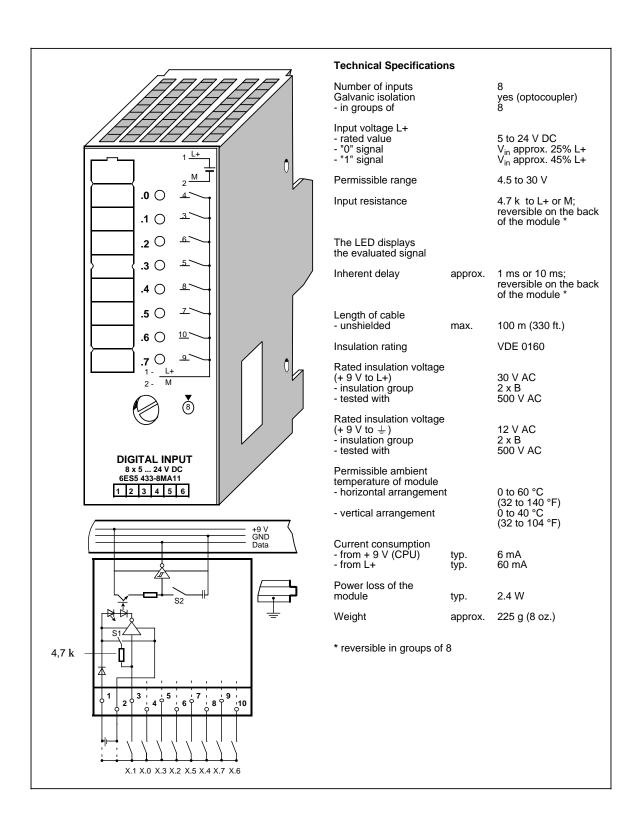

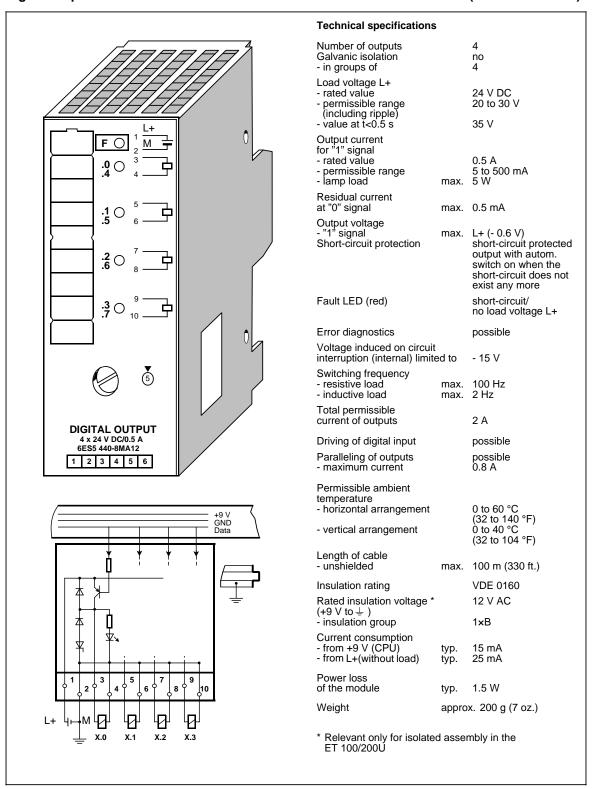

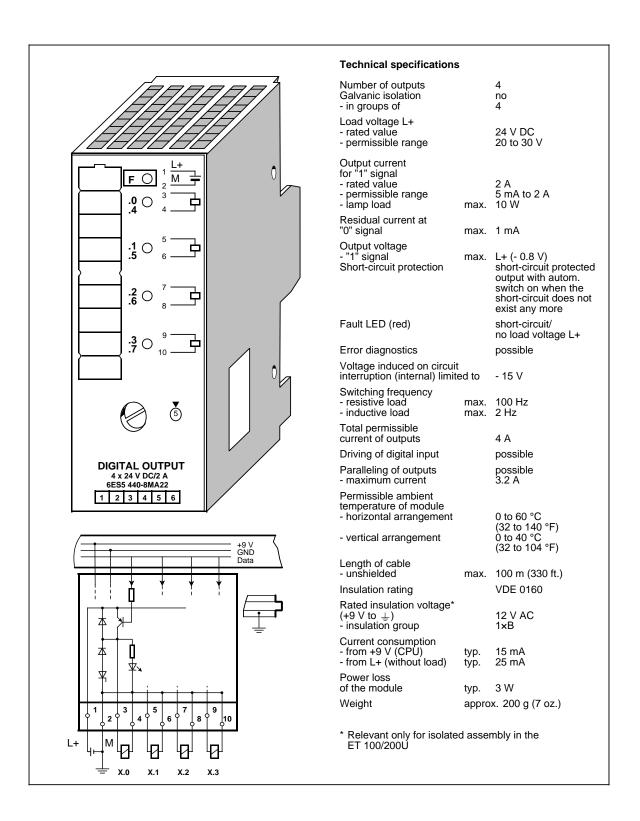

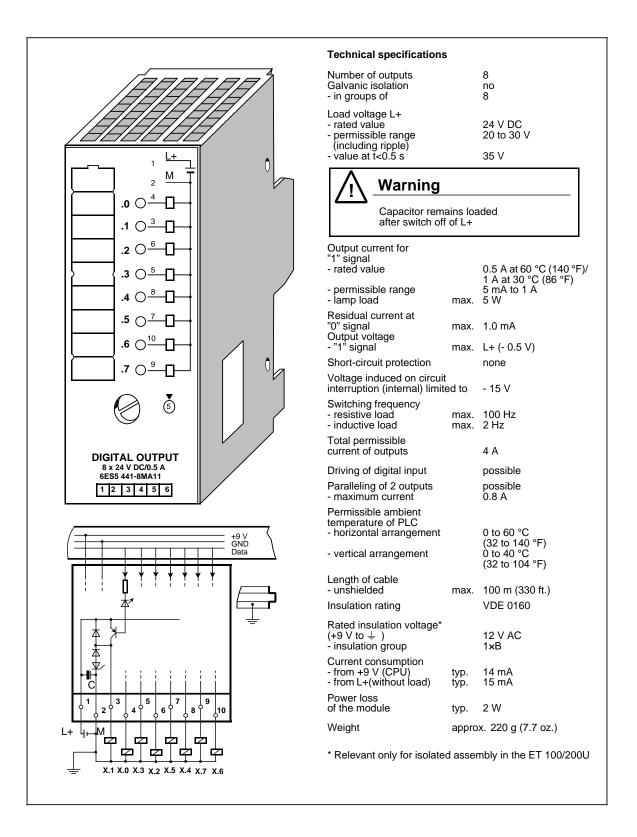

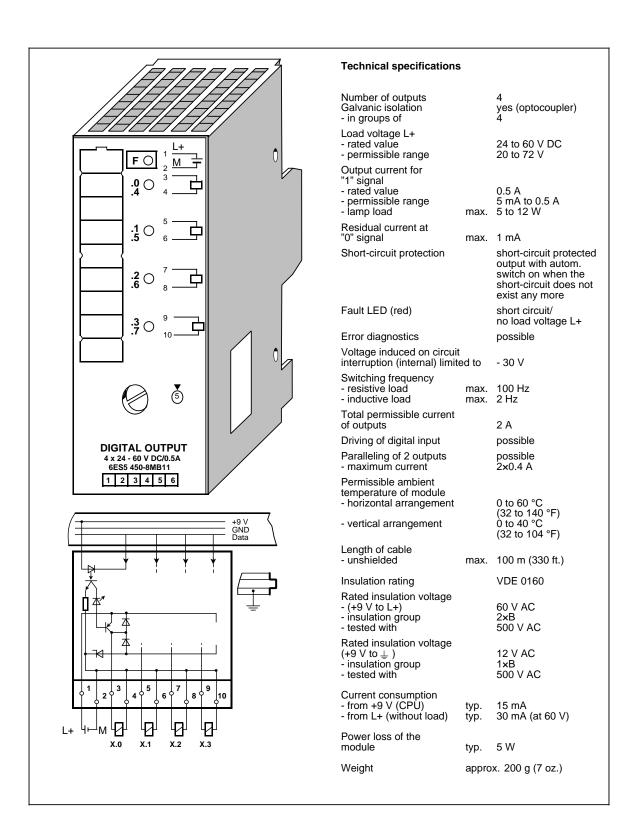

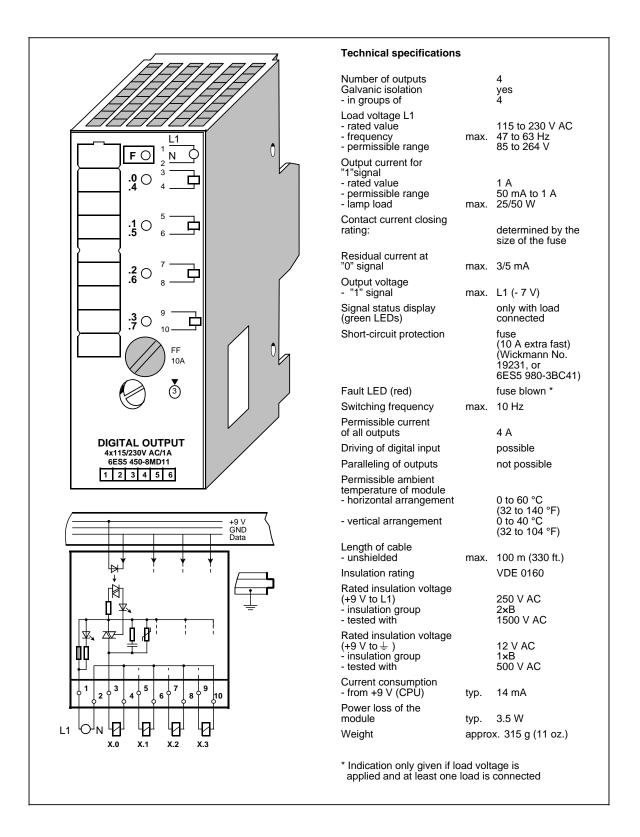

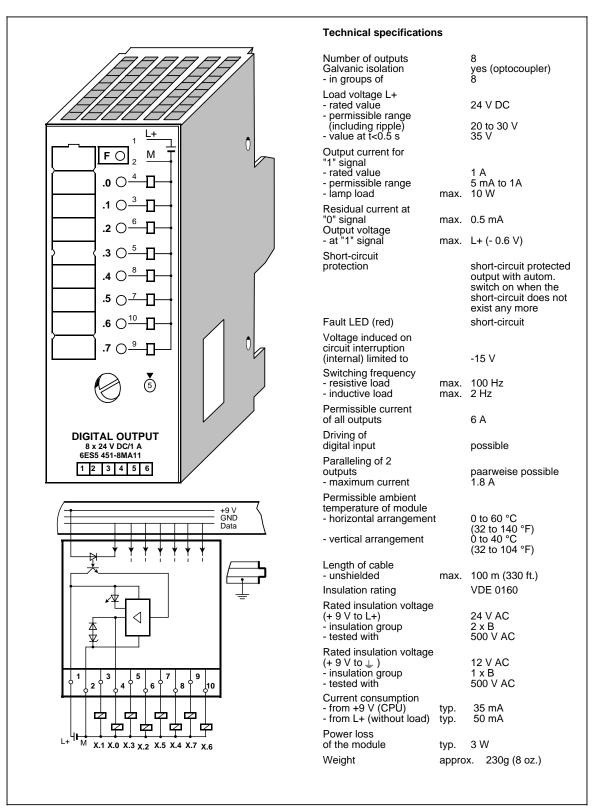

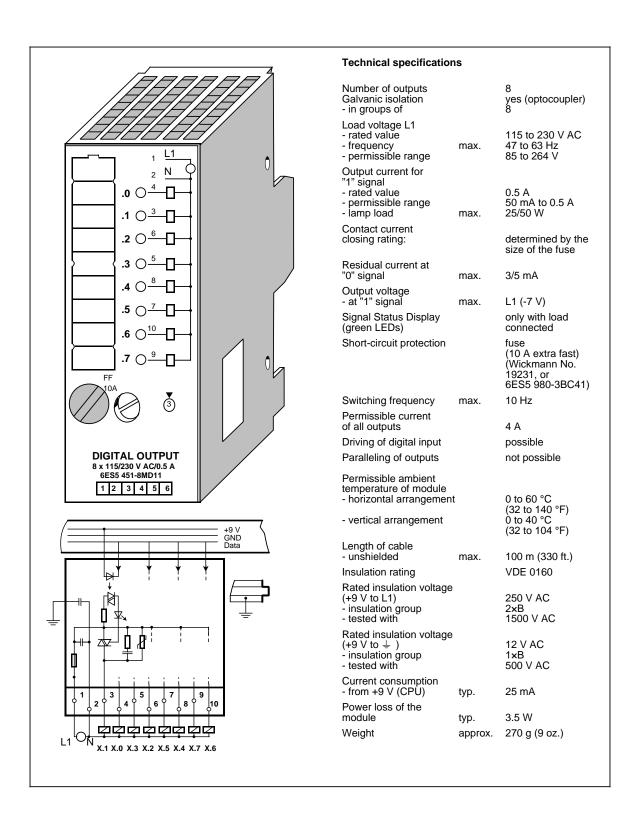

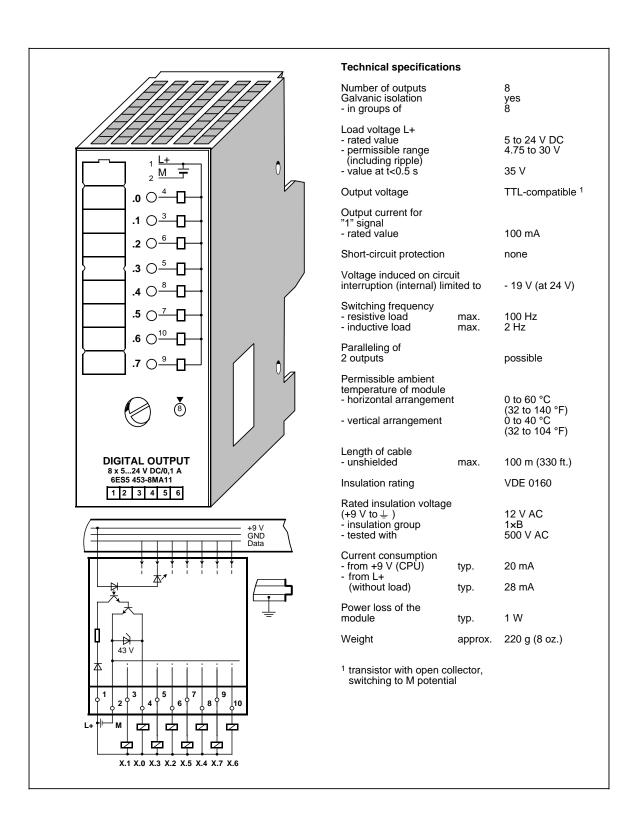

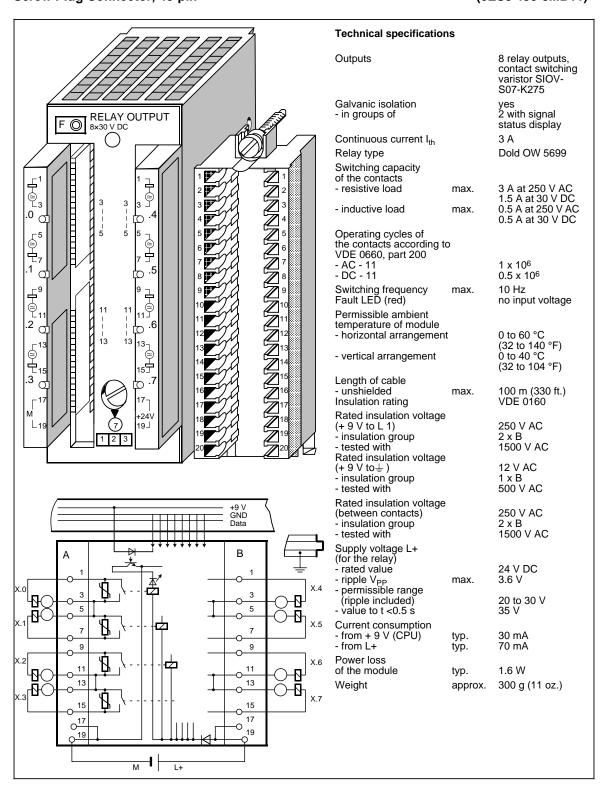

|        | 14.6<br>14.6.1<br>14.6.2<br>14.6.3 | Digital Modules Digital Input Modules Digital Output Modules Digital Input/Output Modules                                                                                            | 14 - 16<br>14 - 16<br>14 - 26<br>14 - 36 |

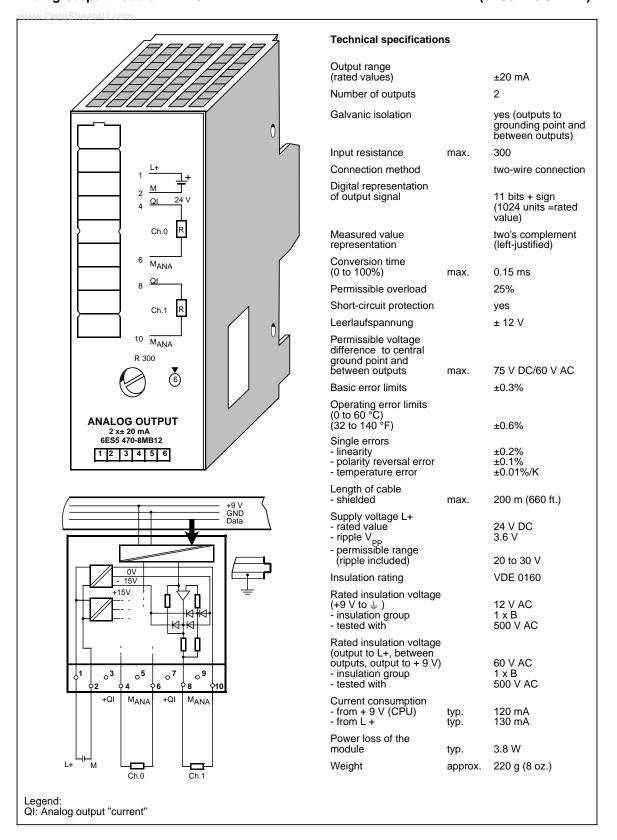

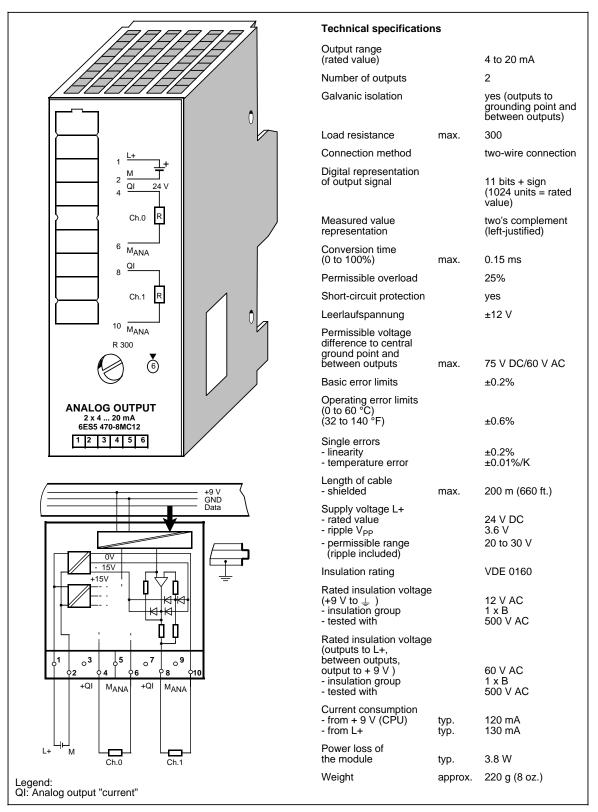

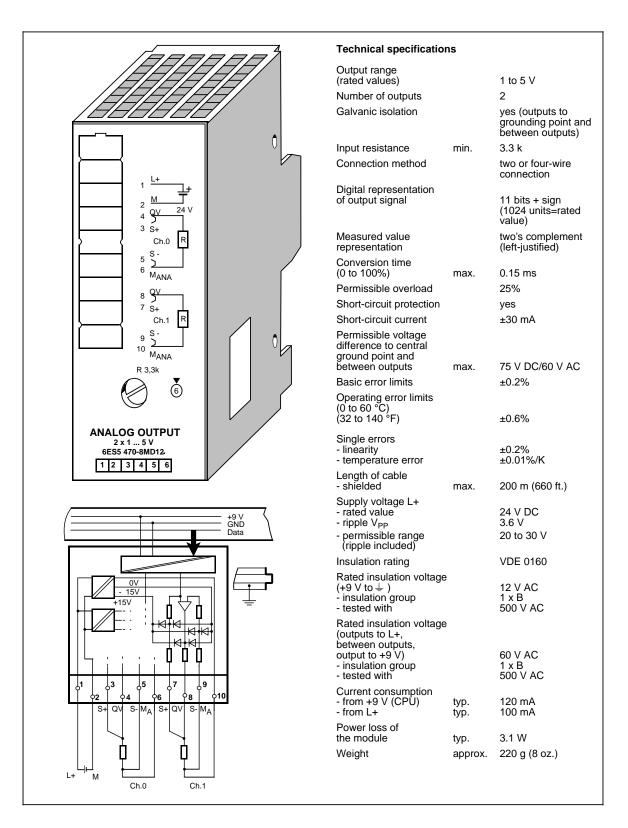

|        | 14.7<br>14.7.1<br>14.7.2           | Analog Modules Analog Input Modules Analog Output Modules                                                                                                                            | 14 - 38<br>14 - 38<br>14 - 56            |

| 15     | Functi                             | on Modules                                                                                                                                                                           | 15 - 1                                   |

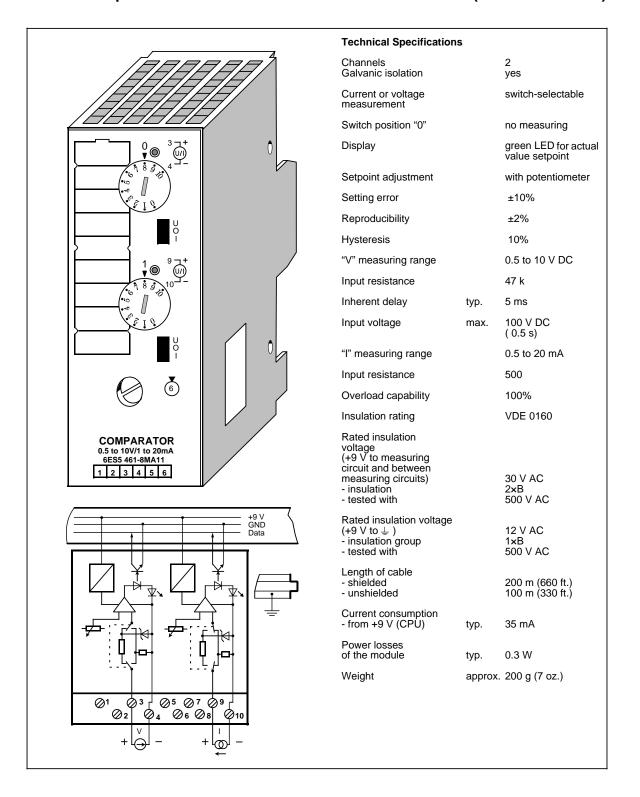

|        | 15.1                               | Comparator Module 2×1 to 20 mA/0.5 to 10 V                                                                                                                                           | 15 - 1                                   |

|        | 15.2                               | Timer Module 2×0.3 to 300 s                                                                                                                                                          | 15 - 4                                   |

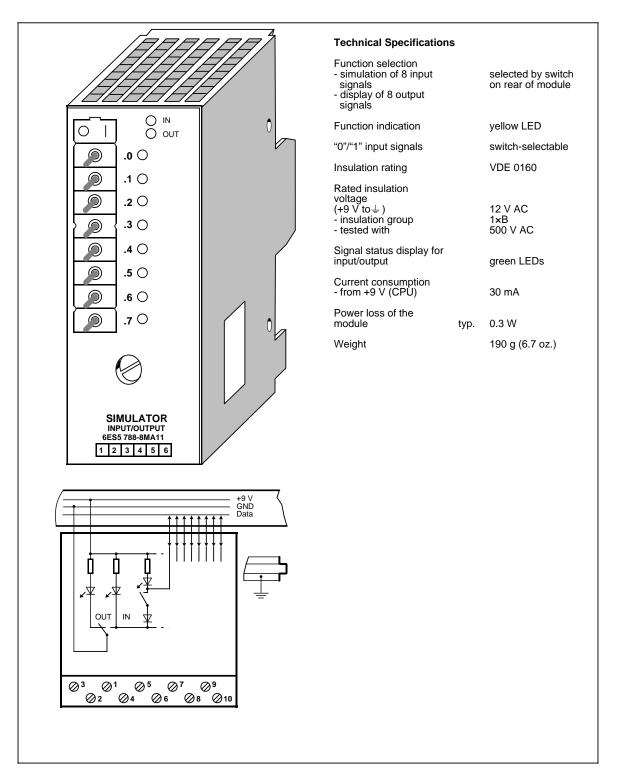

|        | 15.3                               | Simulator Module                                                                                                                                                                     | 15 - 7                                   |

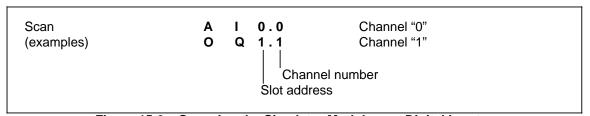

|        | 15.4                               | Diagnostic Module                                                                                                                                                                    | 15 - 9                                   |

χi EWA 4NEB 812 6120-02b

|                |                                            | Page               |

|----------------|--------------------------------------------|--------------------|

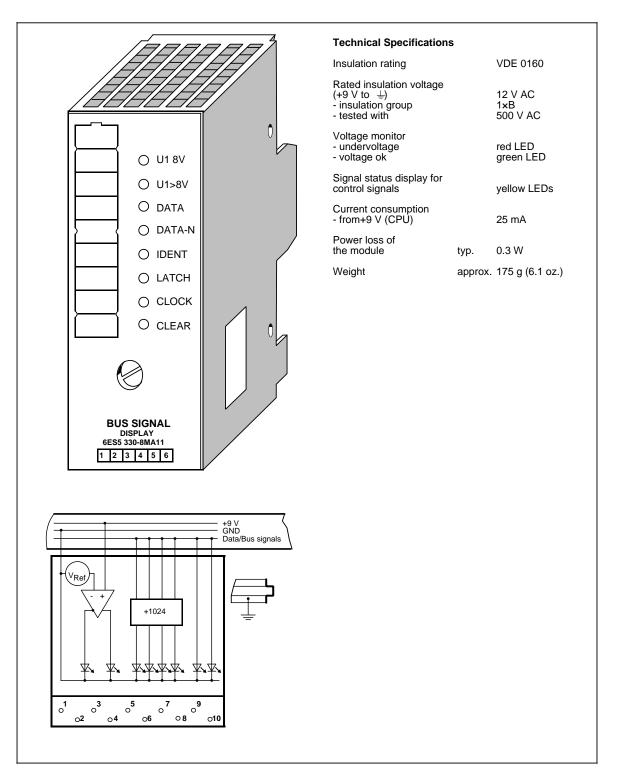

| 15.5           | Counter Module 2x0 to 500 Hz               | 15 - 12            |

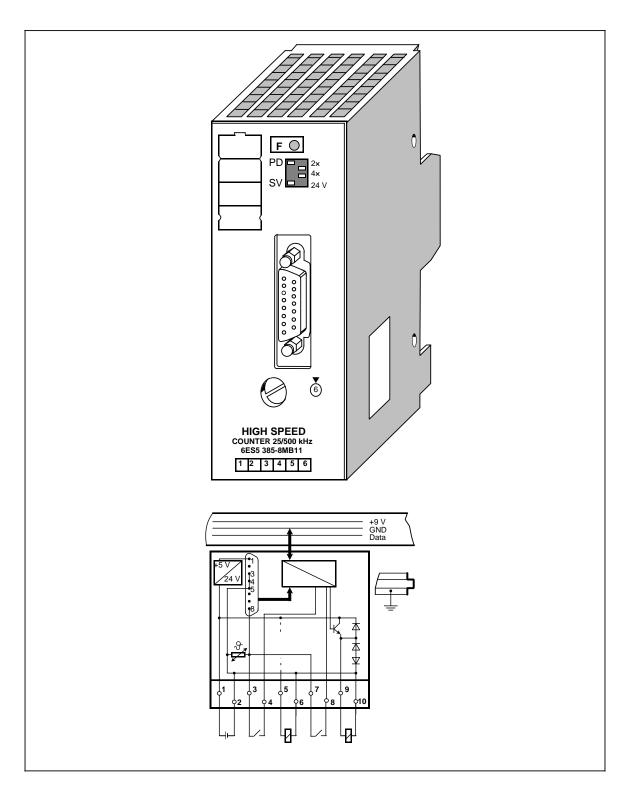

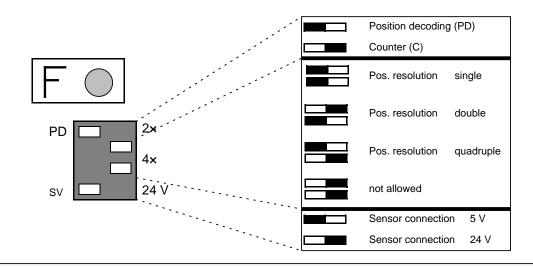

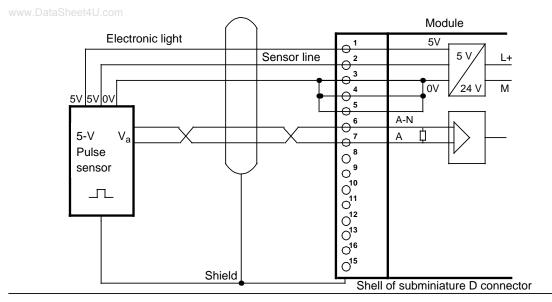

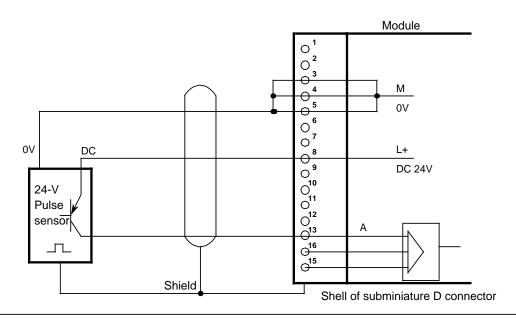

| 15.6<br>15.6.1 | Counter Module 25/500 kHz                  | 15 - 17<br>15 - 20 |

| 15.6.1         |                                            | 15 - 20            |

|                | Functional Description of the Counter Mode | 15 - 27            |

| 15.6.4         |                                            | 15 - 29            |

| 15.6.5         | Entering New Setpoints for the Counter and |                    |

|                | Position Decoder                           | 15 - 38            |

| 15.6.6         | Addressing                                 | 15 - 39            |

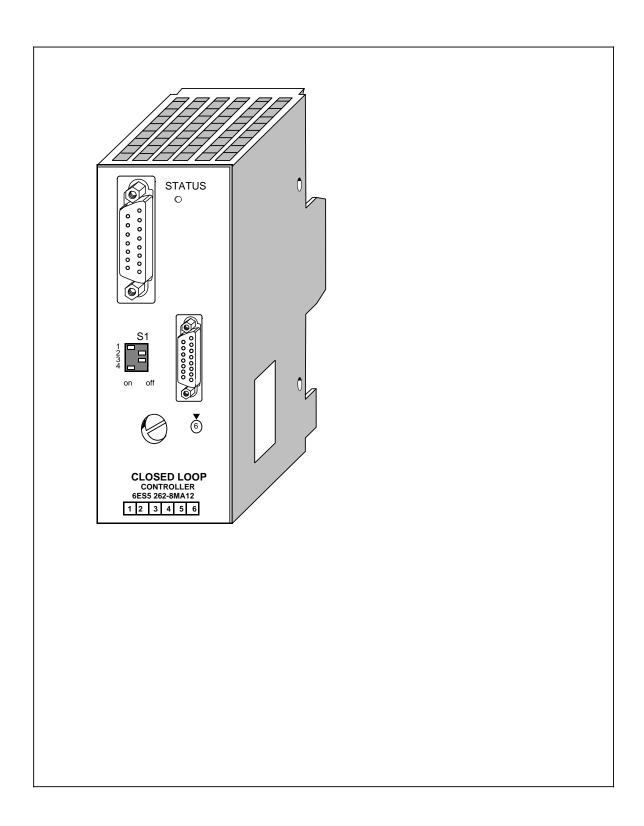

| 15.7           | Closed-Loop Control Module IP 262          | 15 - 41            |

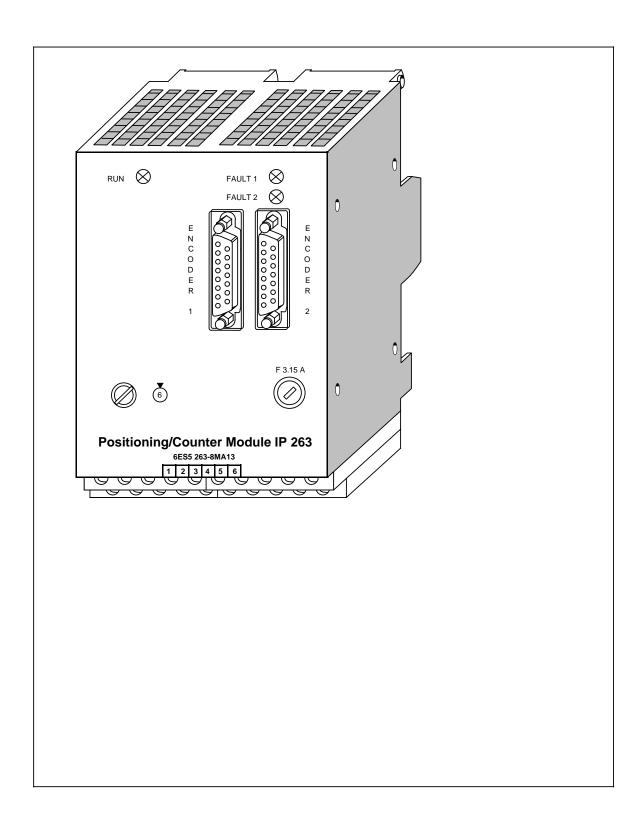

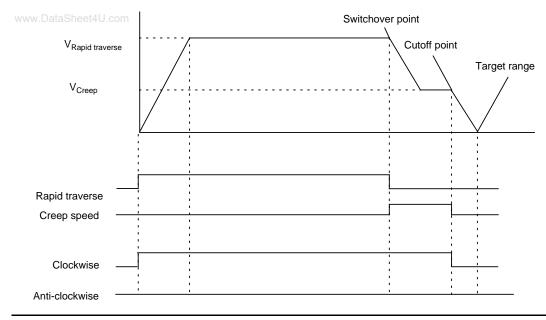

| 15.8           | IP 263 Positioning Module                  | 15 - 45            |

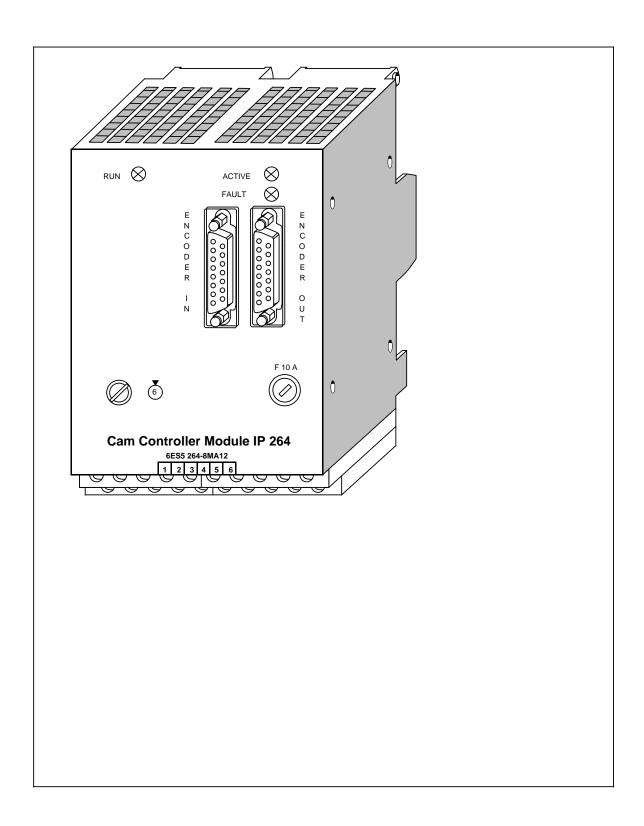

| 15.9           | IP 264 Electronic Cam Controller Module    | 15 - 49            |

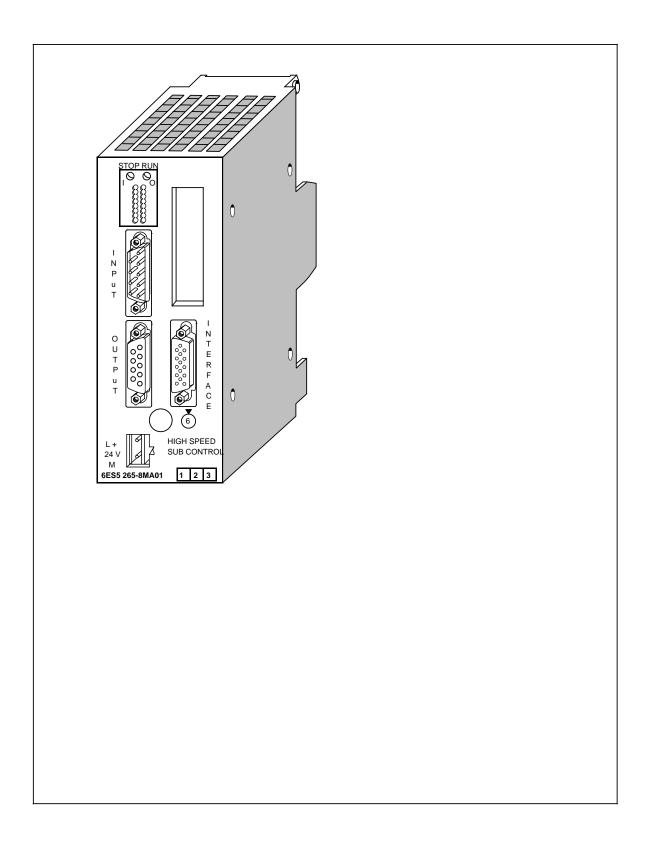

| 15.10          | IP 265 High Speed Sub Control              | 15 - 52            |

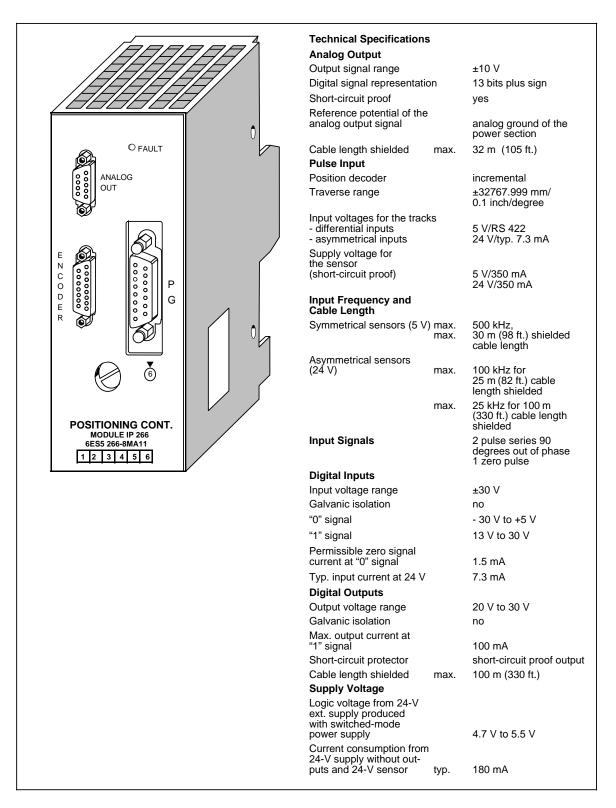

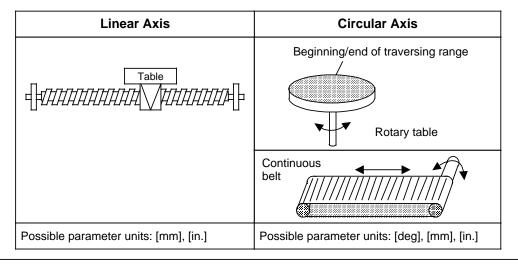

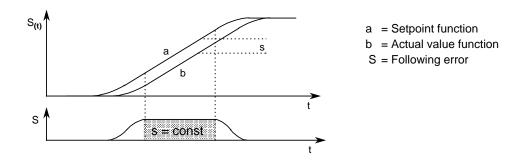

| 15.11          | Positioning Module IP 266                  | 15 - 55            |

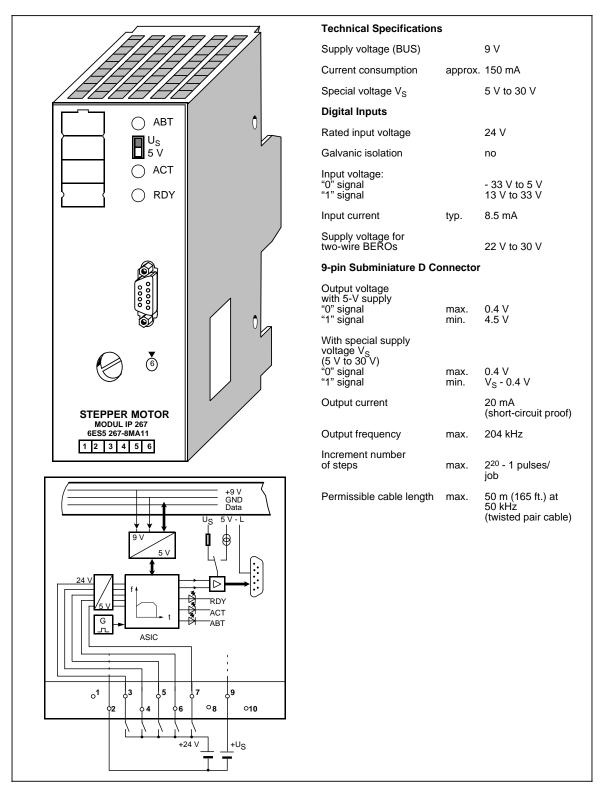

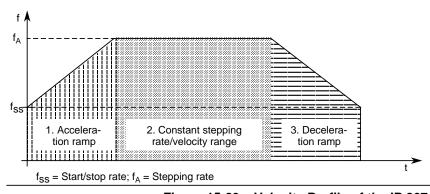

| 15.12          | Stepper Motor Control Module IP 267        | 15 - 59            |

| 15.13          | Communications Modules                     | 15 - 62            |

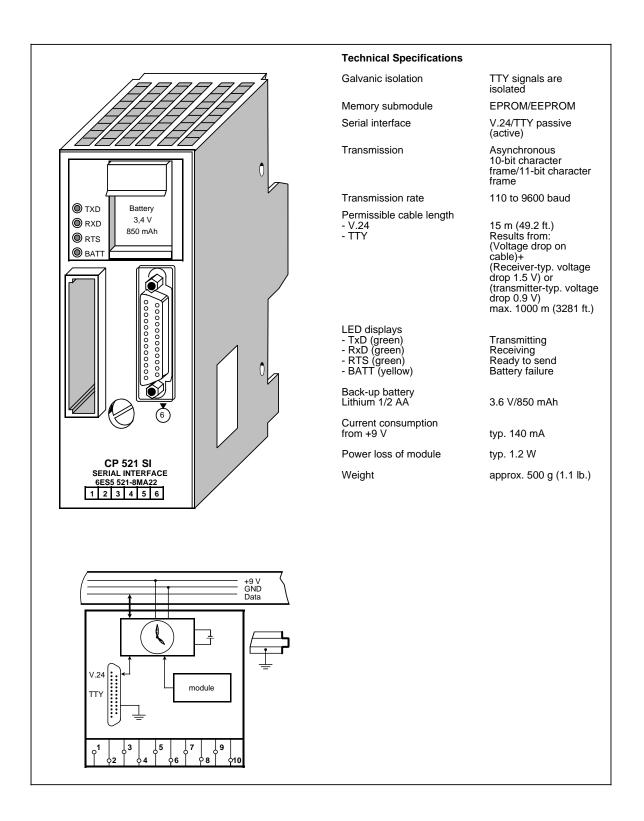

| 15.13.         | 1 Printer Communications Module CP 521     | 15 - 62            |

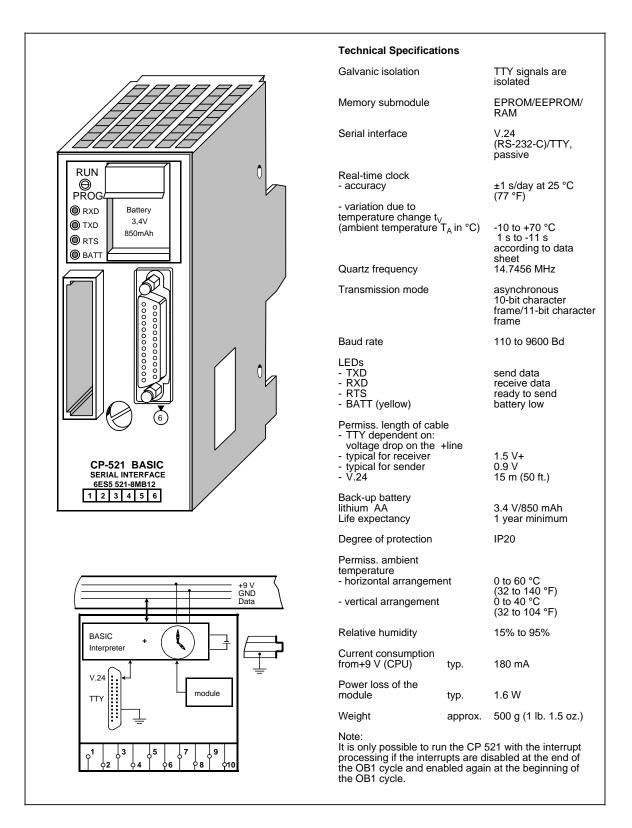

| 15.13.2        | 2 Communications Module CP 521 BASIC       | 15 - 65            |

# **Appendices**

| A | Opera                                   | tions List, Machine Code and List of Abbreviations                                                                              | A - 1                                       |

|---|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

|   | A.1<br>A.1.1<br>A.1.2<br>A.1.3<br>A.1.4 | Operations List Basic Operations Supplementary Operations System Operations, for CPU 102 and Higher Evaluation of CC 1 and CC 0 | A - 1<br>A - 1<br>A - 8<br>A - 13<br>A - 14 |

|   | A.2                                     | Machine Code Listing                                                                                                            | A - 15                                      |

|   | A.3                                     | List of Abbreviations                                                                                                           | A - 18                                      |

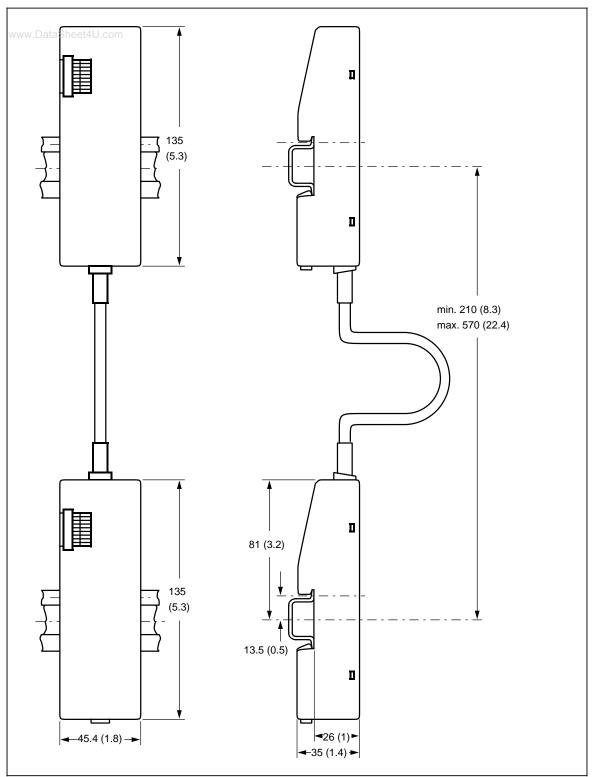

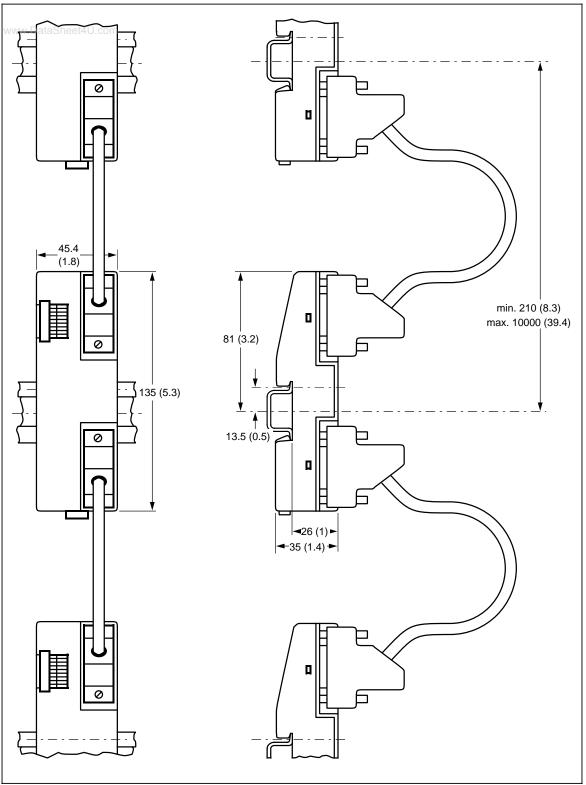

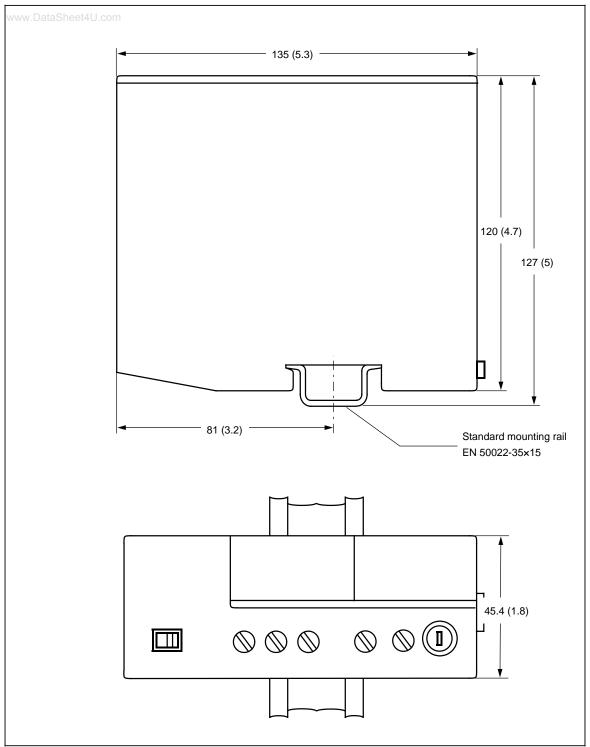

| В | Dimer                                   | nsion Drawings                                                                                                                  | B - 1                                       |

| С | Active                                  | and Passive Faults in Automation Equipment                                                                                      | C - 1                                       |

| D | Inform                                  | nation for Ordering Accessories                                                                                                 | D - 1                                       |

| E | Refere                                  | ence Materials                                                                                                                  | E - 1                                       |

| F | Sieme                                   | ns Addresses Worldwide                                                                                                          | F - 1                                       |

Index

xiii EWA 4NEB 812 6120-02b

www.DataSheet4II.com

# **How to Use This System Manual**

www.DataSheet4U.com

The S5-100U is a programmable controller for lower and intermediate performance ranges. It meets all the requirements for a modern programmable controller. To use this controller optimally, you need detailed information.

In this system manual we have attempted to present this information as completely and as well organized as possible. Certain information is repeated in various chapters so that you do not have to leaf through the manual to find what you need.

This How to Use This System Manual section gives you information that will make it easier for you to find what you need. This section explains how the manual is organized.

# **Contents of This System Manual**

- Hardware Description (Chapters 1, 2, and 3)

These chapters describe the controllers: how they fit into the SIMATIC® S5 family of programmable controllers, how they function, and how you install them.

- Start-Up Information (Chapters 4, 5, and 6)

These chapters summarize the information you need to start up your programmable controller.

These chapters describe how the hardware and software influence each other.

- The Programming Language of the Programmable Controllers (Chapters 7, 8, and 9)

These chapters describe the structure, operations, and structuring aids of the STEP® 5 programming language.

- Functions of the Programmable Controllers (Chapters 10, 11, 12, 13)

Each of these chapters contains a complete description of a particular function, from wiring to programming. Subjects include analog value processing, counter and interrupt inputs, integral clock, and the programmable controller as a SINEC® L1 slave.

- Module Spectrum (Chapters 14 and 15)

These chapters contain information about all the currently available S5-100U modules that you can use to expand your controller. Chapter 15, Function Modules, includes the modules that require an extensive description (i. e., more than just technical specifications).

- Overviews (Appendices)

In these chapters you will find not only a complete list of operations but also dimension drawings, a description of errors that may occur during operation of the programmable controller, maintenance and repair procedures, a list of accessories, and reference literature about programmable controllers.

You will find correction pages at the end of the system manual. Use them to indicate any corrections, additions, or suggestions for improvement you might have. Send these suggestions to us. They will help us to improve the next edition of this system manual.

EWA 4NEB 812 6120-02b XV

### Conventions

www.DataSheet4U.com

This system manual is organized in menu form to make it easier for you to find information. This means the following:

- Each chapter is marked with printed tabs.

- At the front of the system manual is an overview page that lists the title of each chapter. Following this page, you will find a table of contents.

- At the beginning of each chapter is a table of contents for that chapter. Each chapter has three

level headings that are numbered. The fourth level heading is not numbered but appears in

boldface type.

- Pages, figures, and tables are numbered separately for each chapter. On the back of the table

of contents for each chapter you will find a list of the figures and tables that appear in that

chapter.

This system manual employs the following specific structuring devices:

- Specific terms have characteristic abbreviations (e. g., programmer is PG).

Appendix A contains a list of abbreviations.

- Footnotes are marked with a raised number (e. g., "1") or a raised asterisk (" \* "). You will find the corresponding explanations in the lower margin of the page or under a figure or table if the footnote appears in one of these.

- Lists are designated with bullets (• as in this particular listing) or with hyphens (-).

- Cross references are indicated as follows: (see section 7.3.2). There are no references to specific page numbers.

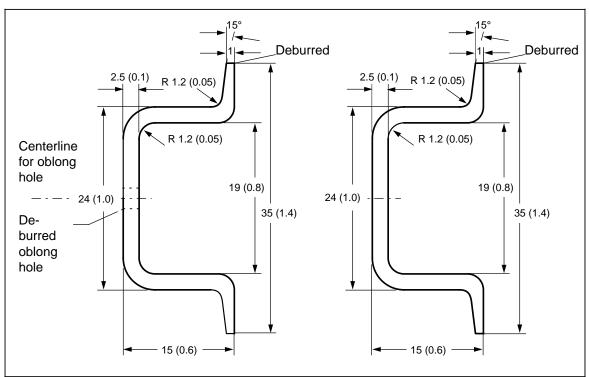

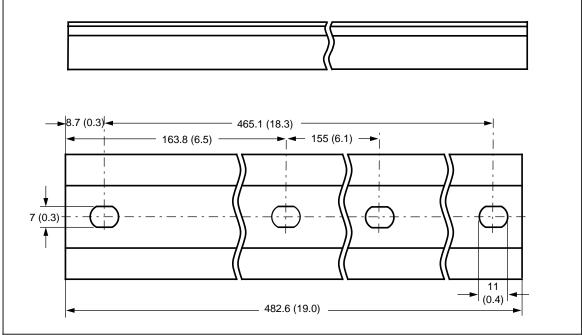

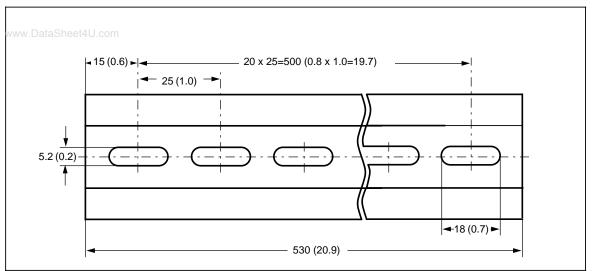

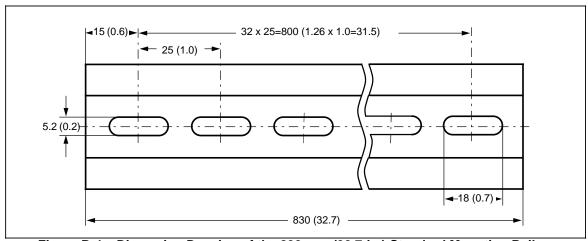

- Dimensions in drawings are indicated in millimeters and inches.

- Value ranges are indicated as follows: 17 to 21 or 17-21.

- Especially important information appears in framed boxes such as the following:

# Warning

You will find definitions for the terms "Warning," "Danger," "Caution," and "Note" in the Safety-Related Guidelines for the User at the end of the introduction.

xvi EWA 4NEB 812 6120-02b

# Changes Made to the Second Edition of the S5-100U System Manual (Order Number: 6ES5 998-0UB22)

### S5-100U System Manual (Order Number 6ES5 998-0UB23) has been completely revised:

- The format was adapted to the other system manuals in the SIMATIC S5 family.

- The contents were updated and reorganized.

### Some of the functions of CPU 103 have been expanded:

- The default settings (default parameters) for DB1 have been integrated into CPU 103

version 8MA03. This feature makes it easier for you to use the internal CPU functions.

The following chapters were included or completely revised in the system manual:

- Chapter 9 "Integrated Blocks and Their Functions"

- Chapter 12 "Integral Real-Time Clock, for CPU 103 Version 8MA02 and Higher"

- Chapter 13 "Connecting the S5-100U to SINEC L1, for CPU 102 and Higher"

- The execution times of some operations have been reduced considerably, compared to the "old" CPU 103. For the new execution times refer to the list of operations in Appendix A.

### The S5-100U system has been expanded to include an additional module:

The "Communications Module CP 521 BASIC" is described in section 15.10.2.

# Changes Made to the Third Edition of the S5-100U System Manual (Order Number: 6ES5 998-0UB23)

The contents were updated.

# **Training**

Siemens offers a wide range of training courses for SIMATIC S5 users. Contact your Siemens representative for more information.

EWA 4NEB 812 6120-02b XVII

#### www.DataSheet4LLcom

# Safety-Related Guidelines for the User

This document provides the information required for the intended use of the particular product. The documentation is written for technically qualified personnel.

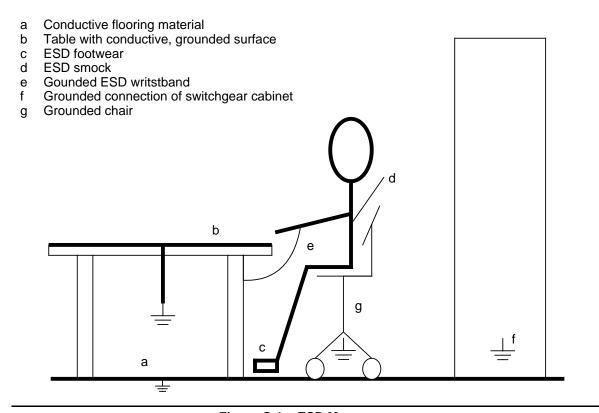

Qualified personnel as referred to in the safety guidelines in this document as well as on the product itself are defined as follows.

- System planning and design engineers who are familiar with the safety concepts of automation equipment.

- Operating personnel who have been trained to work with automation equipment and are conversant with the contents of the document in as far as it is connected with the actual operation of the plant.

- Commissioning and service personnel who are trained to repair such automation equipment and who are authorized to energize, de-energize, clear, ground, and tag circuits, equipment, and systems in accordance with established safety practice.

### **Danger Notices**

The notices and guidelines that follow are intended to ensure personal safety, as well as protect the products and connected equipment against damage.

The safety notices and warnings for protection against loss of life (the users or service personnel) or for protection against damage to property are highlighted in this document by the terms and pictograms defined here. The terms used in this document and marked on the equipment itself have the following significance.

# Danger

indicates that death, severe personal injury or substantial property damage <u>will</u> result if proper precautions are not taken.

#### Caution

indicates that minor personal injury or property damage can result if proper precautions are not taken.

# Warning

indicates that death, severe personal injury or substantial property damage <u>can</u> result if proper precautions are not taken.

#### Note

contains important information about the product, its operation or a part of the document to which special attention is drawn.

### **Proper Usage**

# Warning

- The equipment/system or the system components may only be used for the applications described in the catalog or the technical description, and only in combination with the equipment, components, and devices of other manufacturers as far as this is recommended or permitted by Siemens.

- The product will function correctly and safely only if it is transported, stored, set up, and installed as intended, and operated and maintained with care.

XVIII EWA 4NEB 812 6120-02b

1 The SIMATIC S5 System Family

| Figures |                                         |       |  |  |

|---------|-----------------------------------------|-------|--|--|

| 1-1     | Members of the SIMATIC S5 System Family | 1 - 1 |  |  |

# AUT 91 FE 1016

# 1 The SIMATIC S5 System Family

www.DataSheet4U.com

The programmable controllers (PLCs) in the SIMATIC S5 family offer economical solutions to simple control tasks and to complex computer functions.

Figure 1-1. Members of the SIMATIC S5 System Family

The S5-100U programmable controller is one of the smallest and most economical of the programmable controllers in the SIMATIC S5 family. The S5-100U is especially suited for small automation tasks. It is economical to use these programmable controllers if you want to replace more than five control relays.

### The S5-100U has the following features:

### Modular Design

Depending on the CPU you use, the S5-100U allows you to have a maximum of 448 digital inputs and outputs. It is suitable for machine control and for process automation and monitoring on a medium scale. The S5-100U allows a broad expansion capability with various types of modules to adapt optimally to a control task.

### Rugged, Lightweight Design

All of the modules you can use with the S5-100U are block-type modules that are small, rugged, and easy to use. The modules operate without fans. None of these modules has electromagnetically sensitive electronics. The modules are plugged into bus units and screwed tightly so that they are vibration-proof.

The bus units snap onto a standard mounting rail. You can configure the S5-100U in one or more tiers and configure it vertically or horizontally. The S5-100U offers such a wide range of configuration possibilities that you can use it in rough and difficult operating conditions.

### Simple Programming

The programming language is STEP 5 and its comprehensive operations set. It provides three different methods of representation, - four, if you have a CPU 103 or higher.

You can use any of the U series programmers to program your S5-100U, or you can load programs from memory submodules.

1-2 EWA 4NEB 812 6120-02b

| <b>2</b><br>www.Dat | Techn<br>taSheet4L    | ical Description                                                                                                    |       |  |

|---------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------|-------|--|

|                     | 2.1                   | Programmable Controller Design                                                                                      | 2 - 1 |  |

|                     | 2.2<br>2.2.1<br>2.2.2 | Principle of Operation for the Programmable Controller Functional Units  Mode of Operation for the External I/O Bus | 2 - 3 |  |

| Figures                                |                                                                                                                                                                     |                                                    |  |  |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6 | The S5-100U Functional Units of the S5-100U Example of an Arithmetic Logic Unit's Mode of Operation Accumulator Design Structure of the External I/O Bus Data Cycle | 2 - 1<br>2 - 3<br>2 - 5<br>2 - 5<br>2 - 6<br>2 - 7 |  |  |

| Table                                  | Tables                                                                                                                                                              |                                                    |  |  |

| 2-1<br>2-2                             | Retentive and Non-Retentive Operands                                                                                                                                | 2 - 5<br>2 - 8                                     |  |  |

# 2 Technical Description

This chapter describes the design and principle of operation for the S5-100U programmable controller and its accessories.

# 2.1 Programmable Controller Design

The S5-100U belongs to the SIMATIC S5 range of programmable controllers. The S5-100U consists of various functional units (modules) that you can combine according to the task you want to perform.

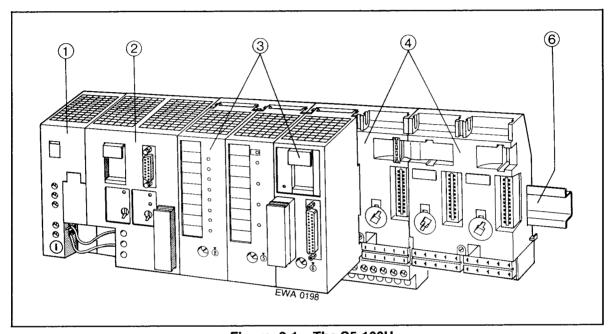

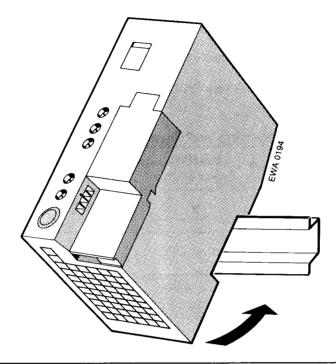

Figure 2-1. The S5-100U

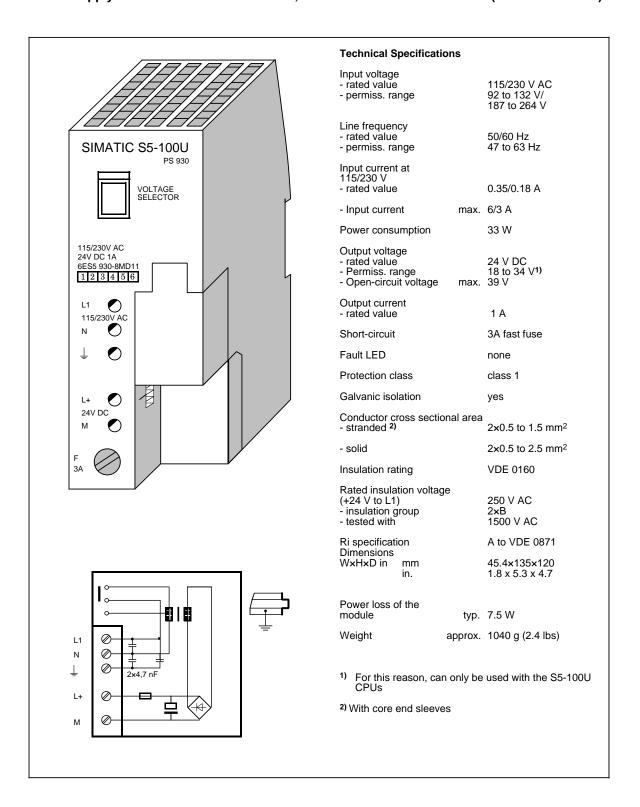

# ① Power supply module (PS 930)

This module is required if 24 V DC is not available for the CPU.

# ② Central processing unit (CPU)

The CPU scans the control program. In the event of a power failure, a backup battery located in the battery compartment saves the memory contents (9).

The control program can be stored in a memory submodule.

The CPU has a serial port, and you can connect a programmer, an operator panel, or a SINEC L1 bus to it.

2-1

### Input/output modules

Input/output modules transfer information between the CPU and such process peripherals as sensors, actuators, and transducers. You can use the following types of input/output modules with your S5-100U:

- Digital input modules and digital output modules (4, 8, and 16/16 channel)

- Use these modules for simple control tasks involving signal states "0" and "1" only.

- Analog input modules and analog output modules

- Use these modules to record and generate such variable quantities as currents and voltages.

- Timer module

- Use this module to set various times without having to change the program.

- Counter module

- Use this module to count pulses up to 500 Hz. You can input comparison values without having to change the program.

- High-speed counter/position detection module

- Use the high-speed counter to record high-speed counter pulses of 25/500 kHz. You can use this module for position detection in a positioning task.

- Comparator module

- This module makes it possible for you to monitor preset comparison values, such as for current and voltage.

- Simulator module

- Use this module to generate digital input signals or to display digital output signals.

- Diagnostic module

- Use this module to check the function of the I/O bus.

- Communications module (CP)

- Use this module to output message texts with the date and clock time to a connected printer. You can also use this module to connect to external systems.

- Intelligent I/O module (IP)

- Use these intelligent input/output modules for such special tasks as temperature control and positioning tasks.

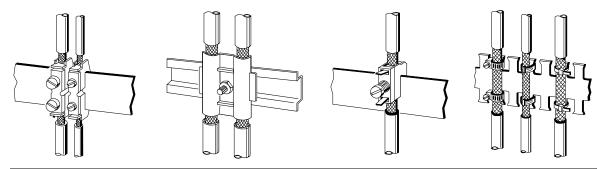

### Bus units with terminal blocks (Crimp-snap-in or SIGUT, screw type)

Use bus units to connect the CPU to input/output modules. You can plug two input/output modules into a single bus unit.

#### Interface modules (IM)

Use these modules to assemble your S5-100U in a multi-tier configuration.

### Standard mounting rail

Mount your programmable controller on the standard mounting rail.

2-2 EWA 4NEB 812 6120-02b

# 2.2 Principle of Operation for the Programmable Controller

The remainder of this chapter explains how your S5-100U processes your program.

# 2.2.1 Functional Units

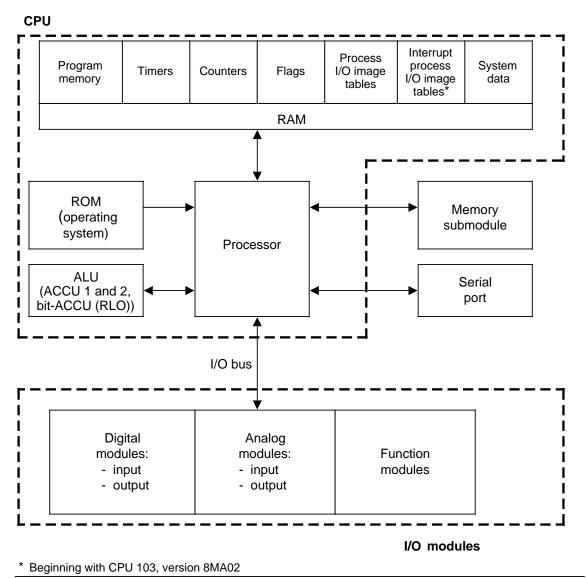

Figure 2-2. Functional Units of the S5-100U

EWA 4NEB 812 6120-02b 2-3

| Technical Description | S5-100L |

|-----------------------|---------|

| 1 Commodi Description | 00 1000 |

### Program Memory (EPROM/EEPROM)

In order to safely store the control program outside of your S5-100U, you must store it on an EPROM or EEPROM memory submodule (see section 4.4).

Programs that are available on a memory submodule (EPROM or EEPROM) can be copied to the internal program memory (see section 4.3). This internal program memory is a reserved area of the CPU's internal RAM memory.

The internal RAM memory has the following characteristics:

- The memory contents can be changed quickly.

- Memory contents are lost when there is a supply voltage failure and there is no battery backup.

# **Operating System (ROM)**

The operating system contains system programs that determine how the user program is executed, how inputs and outputs are managed, how the memory is divided, and how data is managed. The operating system is fixed and cannot be changed.

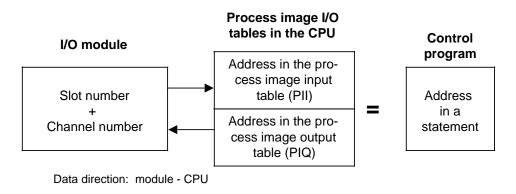

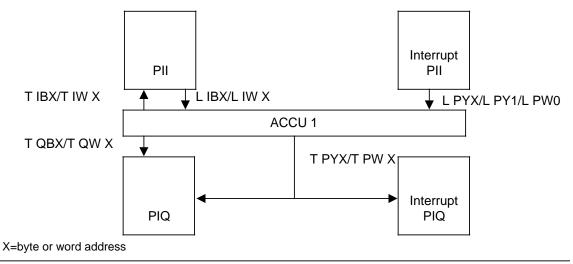

### **Process Image Tables (PII, PIQ)**

Signal states of input and output modules are stored in the CPU in "process image tables". Process image tables are reserved areas in the RAM of the CPU.

Input and output modules have the following separate image tables:

- Process image input table (PII)

- · Process image output table (PIQ)

# **Serial Interface**

You can connect programmers, operator panels, and monitors to the serial port (cable connector). You can use the serial port to connect your S5-100U as a slave to the SINEC L1 local area network.

### Timers, Counters, Flags

The CPU has timers, counters, and flags available internally that the control program can use. The program can set, delete, start, and stop the timers and counters. The time and count values are stored in reserved areas of the RAM memory.

There is another area in the RAM memory where information such as intermediate results can be stored as flags. You can address the flags by bits, bytes, or words.

If battery backup is available, then some of the flags and counters remain in the internal RAM memory even if the supply voltage fails or your S5-100U is switched off. These flags and counters are retentive.

2-4 EWA 4NEB 812 6120-02b

Table 2-1 gives information about the number and retentive characteristics (the internal memory contents are retained/are not retained) of these timers, counters, and flags.

| Operand  | Retentive      | Non-Retentive |               |               |  |

|----------|----------------|---------------|---------------|---------------|--|

| Operand  | CPU 100 to 103 | CPU 100       | CPU 102       | CPU 103       |  |

| Flags    | 0.0 to 63.7    | 64.0 to 127.7 | 64.0 to 127.7 | 64.0 to 255.7 |  |

| Counters | 0 to 7         | 8 to 15       | 8 to 31       | 8 to 127      |  |

| Timers   |                | 0 to 15       | 0 to 31       | 0 to 127      |  |

Table 2-1. Retentive and Non-Retentive Operands

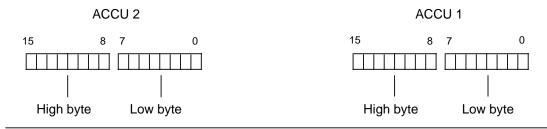

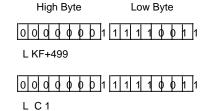

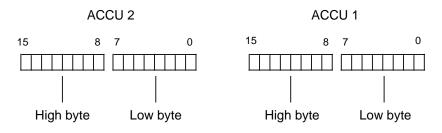

### **Arithmetic Unit**

The arithmetic unit (ALU) consists of two accumulators, ACCU 1 and 2. The accumulators can process byte and word operations.

Figure 2-3. Example of an Arithmetic Logic Unit's Mode of Operation

### Accumulator Design

Figure 2-4. Accumulator Design

### **Processor**

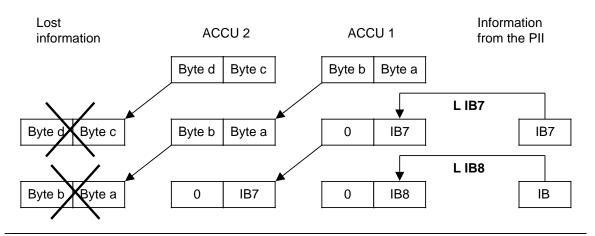

According to the control program, the processor calls statements in the program memory in sequence and executes them. It processes the information from the PII and takes into consideration the values of internal timers and counters as well as the signal states of internal flags.

#### External I/O Bus

The I/O bus is the electrical connection for all signals that are exchanged between the CPU and the S5-100U modules in a programmable controller.

EWA 4NEB 812 6120-02b 2-5

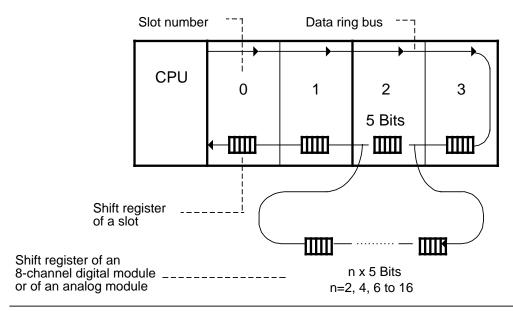

# 2.2.2 Mode of Operation for the External I/O Bus

The S5-100U has a serial bus for the transfer of data between the CPU and the I/O modules. This serial bus has the following characteristics:

- The modular design permits optimal adaptation to the particular control task.

- No addresses have to be set on the I/O modules.

- · A terminating resistor connector is not required.

- Direct access to individual modules is not possible.

A number of shift registers moves the data (Figure 2-5).

Four data bits and one check bit for bus monitoring are assigned to each slot in the bus unit. All modules requiring more than four data bits have their own shift register and therefore do not have to use the shift register of the particular slot.

Figure 2-5. Structure of the External I/O Bus

2-6 EWA 4NEB 812 6120-02b

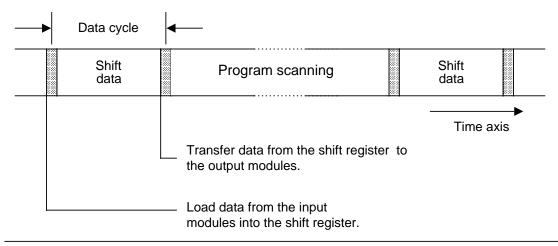

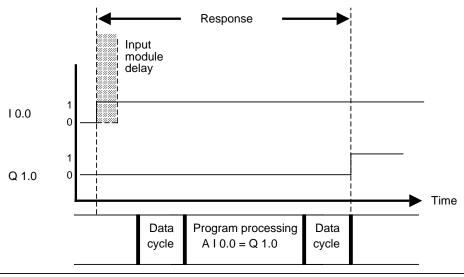

### **Data Cycle**

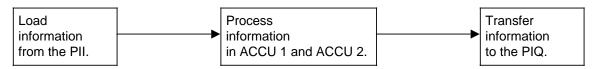

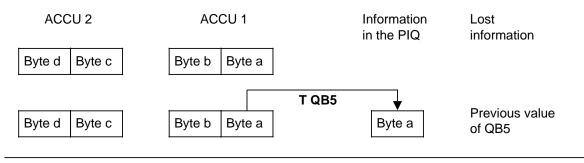

Prior to a program scan, the external I/O bus transfers current information from the input modules to the process image input table (PII). At the same time, information contained in the process image output table (PIQ) is transferred to the output modules.

Figure 2-6. Data Cycle

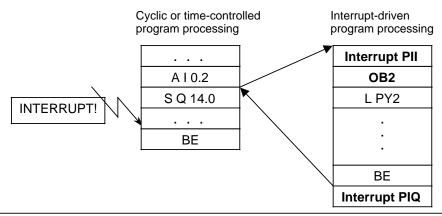

### Interrupt Data Cycle, for CPU 103 version 8MA02 and higher

There is an interrupt input data cycle prior to each time-controlled or interrupt-driven program scan.

Before a time-controlled program scan, current information about the input modules is read into the interrupt PII. Before an interrupt-driven program scan, interrupt inputs on slots 0 and 1 only are read into the interrupt PII.

Following a time-controlled program scan, there is not an interrupt output data cycle until data has been moved into the interrupt PIQ via a transfer operation (see section 6.6.2). Information is output from the interrupt PIQ to the output modules during an interrupt output data cycle. The PIQ is updated.

EWA 4NEB 812 6120-02b 2-7

### Length of the Shift Register

The total length of the shift register is obtained from the sum of the data bits of all plugged-in modules and of the empty slots. The check bit is not counted.

You must know the length of the shift register to be able to determine the data cycle time. Data cycle time is 25  $\mu$ s x number of data bits.

Table 2-2. Number of Bits per Module in the Shift Register

| Plugged-in Module                                                    | Number of Data Bits |

|----------------------------------------------------------------------|---------------------|

| Diagnostic module or vacant slot                                     | 4                   |

| 4-channel digital input and output modules                           | 4                   |

| 500 Hz comparator module, 500 Hz timer module, 500 Hz counter module | 4                   |

| 25 KHz counter module                                                | 32                  |

| 8-channel digital input and output modules                           | 8                   |

| Digital input and output module, 16 inputs/16 outputs                | 16                  |

| Simulator module                                                     | 8                   |

| Analog modules for each activated channel                            | 16*                 |

| CP 521, IP 262, IP 266, IP 267                                       | 64                  |

| Refer to the individual manuals for information on other modules.    |                     |

This does not apply to the 466-8MC11 analog input module (8 data bits).

The CPU specifies the maximum length of the shift register in a particular configuration.

• CPU 100: 256 data bits, 128 (max.) of these from analog modules

• CPU 102: 480 data bits, 256 (max.) of these from analog modules

CPU 103: 704 data bits, 512 (max.) of these from analog modules

### Note

If the maximum expansion allowed is exceeded, the S5-100U goes into the STOP mode. The "PEU" bit (I/O not ready) is set in the ISTACK.

2-8 EWA 4NEB 812 6120-02b

# **Examples:**

a) CPU 100: This CPU lets you operate six digital modules (8-channel) and two analog modules (4-channel):

b) CPU 100: This CPU **does not** let you use three digital modules (8-channel) with three analog modules (4-channel) because the maximum permissible number of analog data bits would be exceeded:

c) CPU 102: This CPU lets you operate seven digital modules (8-channel) and four analog modules (4-channel):

d) CPU 102: This CPU **does not** let you use 20 digital modules (8-channel) with 5 analog modules (4-channel) because the maximum permissible number of analog data bits would be exceeded:

e) CPU 103: This CPU lets you operate 24 digital modules (8-channel) and eight analog modules (4-channel):

f) CPU 103: This CPU **does not** let you use 31 digital modules (8-channel) with four analog modules (2-channel) because the maximum permissible number of slots would be exceeded:

EWA 4NEB 812 6120-02b 2-9

www.DataSheet4II.com

| 3 Instal | lation Guidelines                                          |        |

|----------|------------------------------------------------------------|--------|

| 3.1      | Installing S5-100U Components                              | 3 - 1  |

| 3.1.1    | Assembling a Tier                                          | 3 - 1  |

| 3.1.2    | Multi-Tier Expansion                                       | 3 - 5  |

| 3.1.3    | Cabinet Mounting                                           | 3 - 7  |

| 3.1.4    | Vertical Mounting                                          | 3 - 8  |

| 3.2      | Wiring                                                     | 3 - 9  |

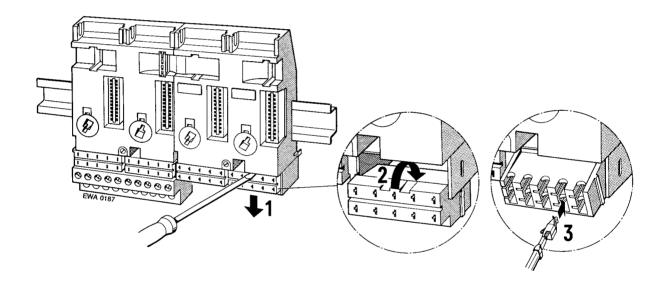

| 3.2.1    | Connection Methods: Screw-Type Terminals and Crimp Snap-in | 3 - 9  |

| 3.2.2    | Connecting the Power Supply to the S5-100U                 | 3 - 12 |

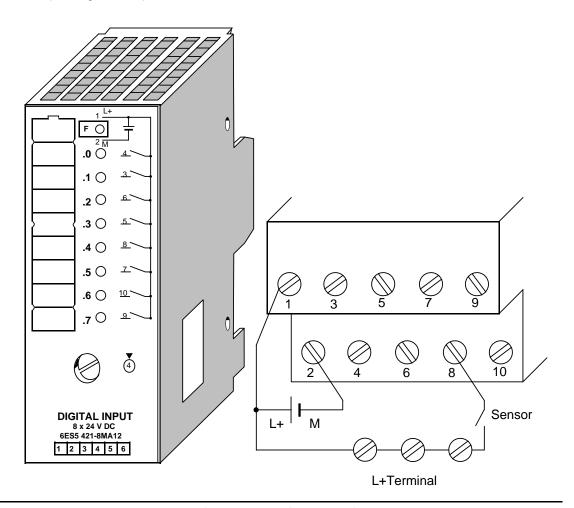

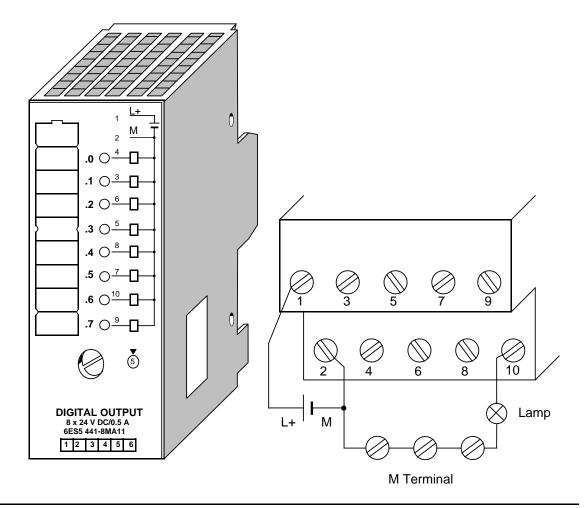

| 3.2.3    | Connecting Digital Modules                                 | 3 - 13 |

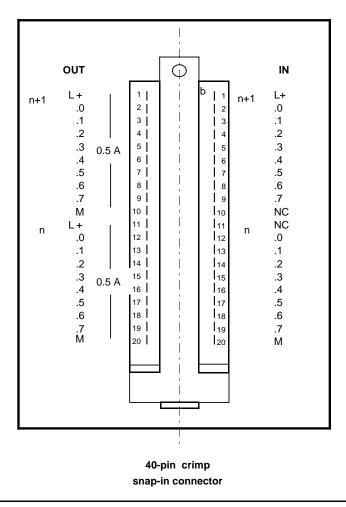

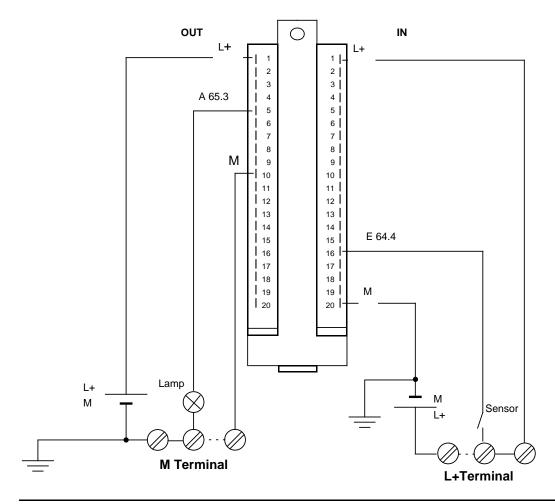

| 3.2.4    | Connecting the Digital Input/Output Module                 | 3 - 18 |

| 3.3      | Electrical Configuration                                   | 3 - 20 |

| 3.3.1    | Electrical Configuration for the S5-100U                   | 3 - 20 |

| 3.3.2    | Electrical Configuration with External I/Os                | 3 - 21 |

| 3.3.3    | Non-Floating and Floating Configurations                   | 3 - 25 |

| 3.4      | Wiring Arrangement, Shielding, and Measures to             | 3 - 29 |

| 3.4.1    | Running Cables Inside and Outside a Cabinet                | 3 - 29 |

| 3.4.2    | Running Cables Outside Buildings                           | 3 - 30 |

| 3.4.3    | Equipotential Bonding                                      | 3 - 31 |

| 3.4.4    | Shielding Cables                                           | 3 - 32 |

| 3.4.5    | Special Measures for Interference-Free Operation           | 3 - 33 |

| Figures |                                                                         |        |

|---------|-------------------------------------------------------------------------|--------|

| 3-1     | Mounting the PS 930 Power Supply Module                                 | 3 - 2  |

| 3-2     | Removing Bus Units                                                      | 3 - 3  |

| 3-3     | Coding System to Prevent an Inadvertent Interchange of Modules          | 3 - 4  |

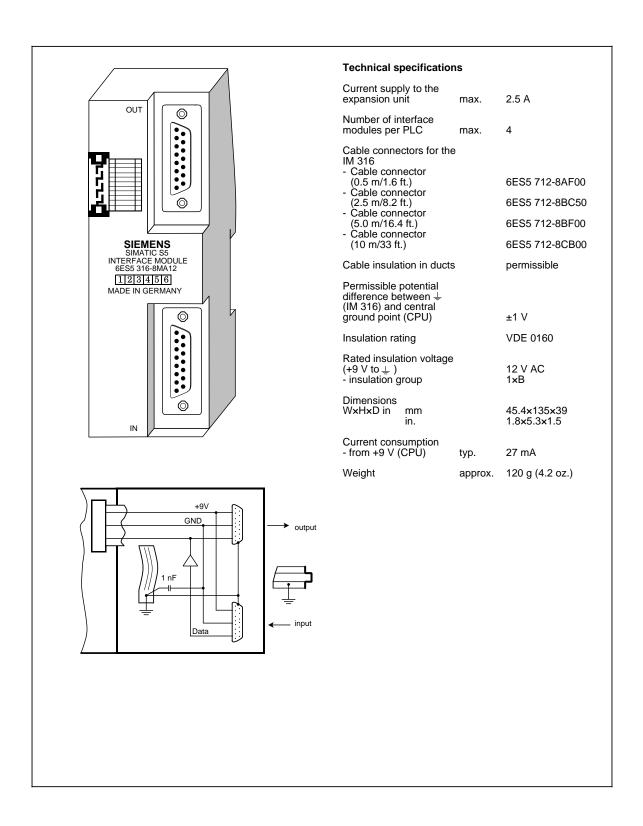

| 3-4     | Interconnecting Tiers with Interface Modules (6ES5 316-8MA12)           | 3 - 5  |

| 3-5     | Multi-Tier Configuration in a Cabinet with the                          |        |

|         | IM 316 Interface Module (6ES5 316-8MA12)                                | 3 - 7  |

| 3-6     | Cabinet Mounting with a Series of Devices                               | 3 - 8  |

| 3-7     | Vertically Mounting a Programmable Controller                           | 3 - 8  |

| 3-8     | SIGUT/Screw-Type Connection Method                                      | 3 - 9  |

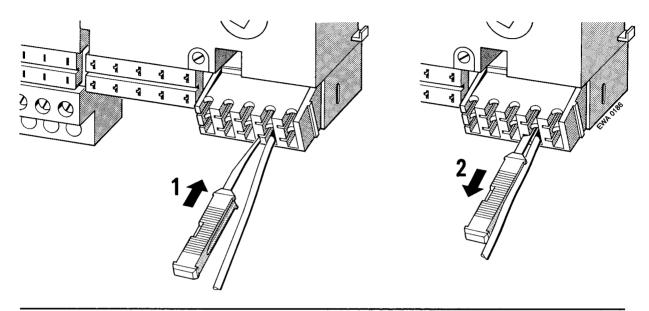

| 3-9     | Mounting the Crimp Snap-in Terminal                                     | 3 - 10 |

| 3-10    | Disconnecting a Terminal                                                | 3 - 11 |

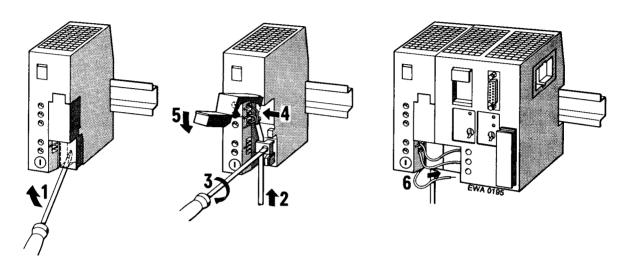

| 3-11    | Connecting a Power Supply Module and a CPU                              | 3 - 12 |

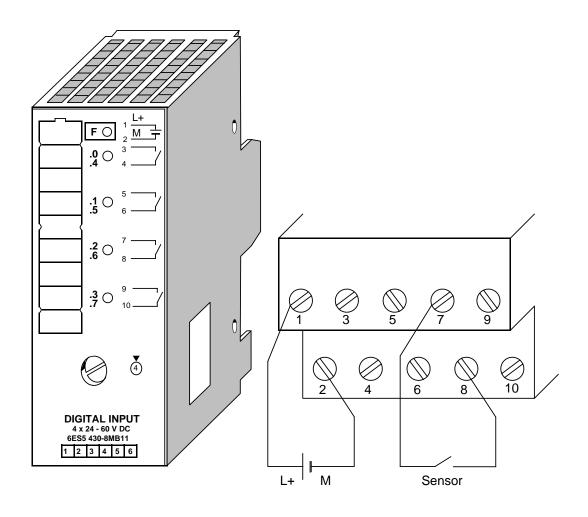

| 3-12    | Two-Wire Connection of a Sensor to Channel 2                            | 3 - 14 |

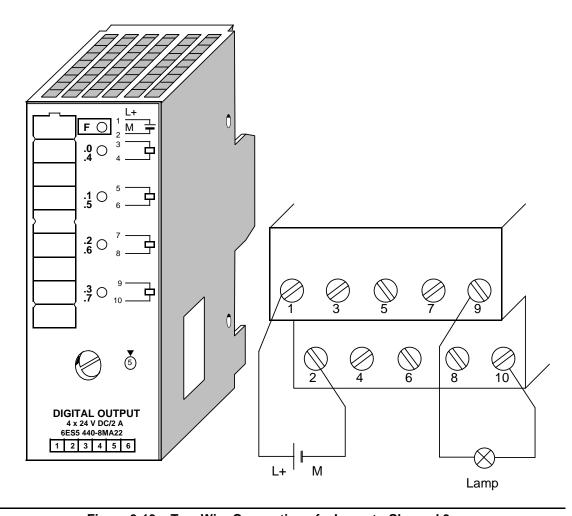

| 3-13    | Two-Wire Connection of a Lamp to Channel 3                              | 3 - 15 |

| 3-14    | Connecting a Sensor to Channel 4                                        | 3 - 16 |

| 3-15    | Connecting a Lamp to Channel 6                                          | 3 - 17 |

| 3-16    | Front View of the Digital I/O Module with a Crimp Snap-In Connector     |        |

|         | (simplified view and not true to scale)                                 | 3 - 18 |

| 3-17    | Connecting a Sensor and a Load to Digital Input/Output Module 482       | 3 - 19 |

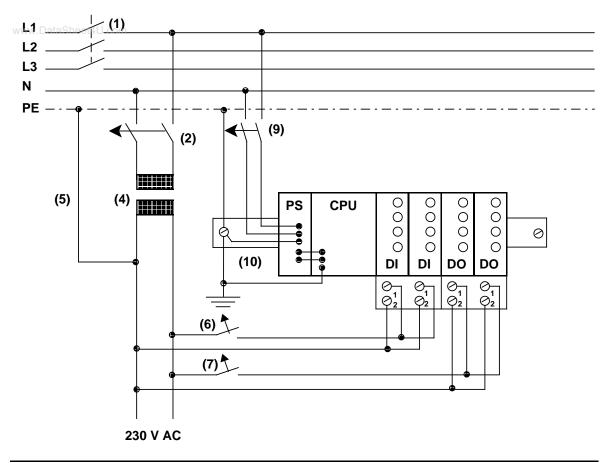

| 3-18    | Configuration Possibility: S5-100U with 115/230 V AC Power Supply       |        |

|         | for Programmable Controller, Sensors, and Actuators                     | 3 - 22 |

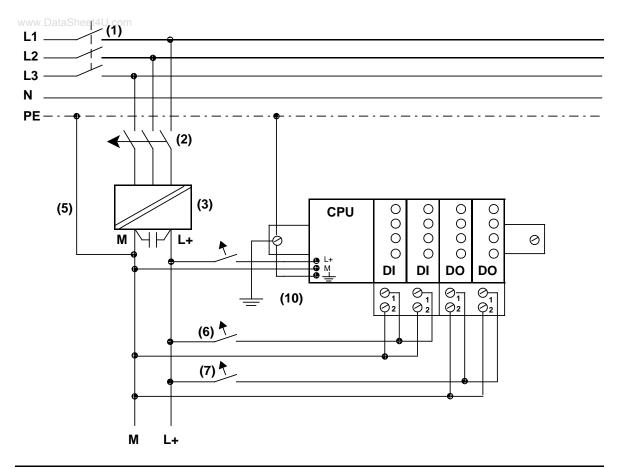

| 3-19    | Configuration Possibility: S5-100U with 24 V DC Power Supply (with Safe |        |

|         | Electrical Isolation According to DIN VDE 0160) for Programmable        |        |

|         | Controller, Sensors, and Actuators                                      | 3 - 23 |

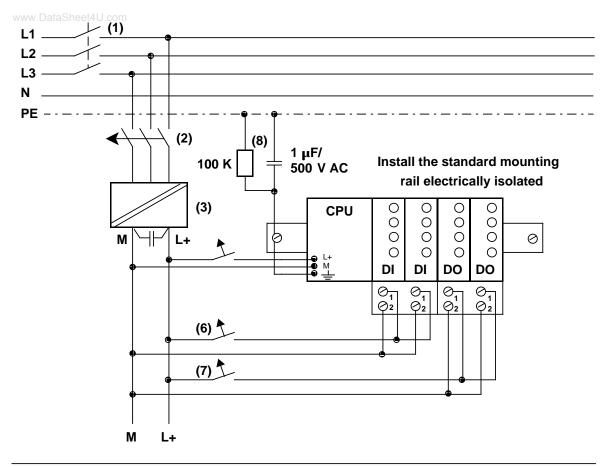

| 3-20    | Non-Grounded Operation; 24 V DC Power Supply (with Safe Electrical Iso- |        |

|         | lation According to DIN VDE 0160) for Programmable Controller and I/Os  | 3 - 24 |

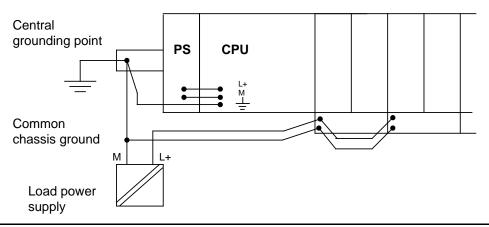

| 3-21    | Example: Non-Floating Connection of I/Os to the S5-100U                 | 3 - 25 |

| 3-22    | Simplified Representation of a Non-Floating I/O Connection              | 3 - 26 |

| 3-23    | Simplified Representation of a Galvanically Isolated Connection         |        |

|         | of the I/Os to the S5-100U                                              | 3 - 27 |

| 3-24    | A Simplified Representation of a Floating I/O Connection                |        |

| 3-25    | Laying Equipotential Bonding Conductor and Signal Label                 | 3 - 31 |

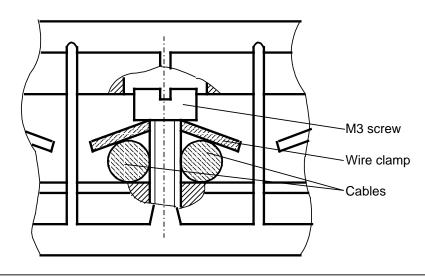

| 3-26    | Fixing Shielded Cables with Various Types of Cable Clamps               | 3 - 33 |

| 3-27    | Wiring Coils                                                            | 3 - 33 |

| 3-28    | Measures for Suppressing Interference from                              | 0 01   |

|         | Fluorescent Lamps in the Cabinet                                        | 3 - 34 |

| Table   | es                                                                      |        |

| 3-1     | Installing, Removing, and Changing S5-100U Components                   | 3 - 1  |

| 3-2     | Connecting the Load Voltage                                             | 3 - 13 |

| 3-3     | Rules for Common Running of Lines                                       | 3 - 29 |

# 3 Installation Guidelines

www.DataSheet4U.com

## 3.1 Installing S5-100U Components

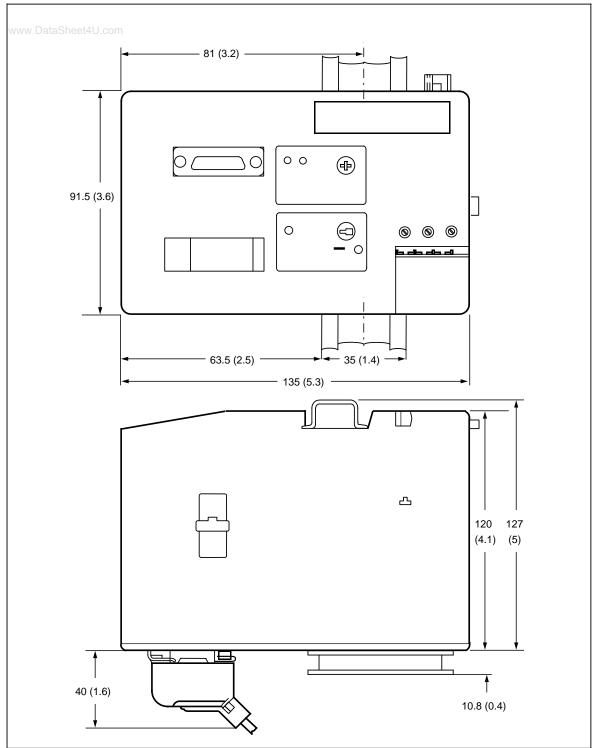

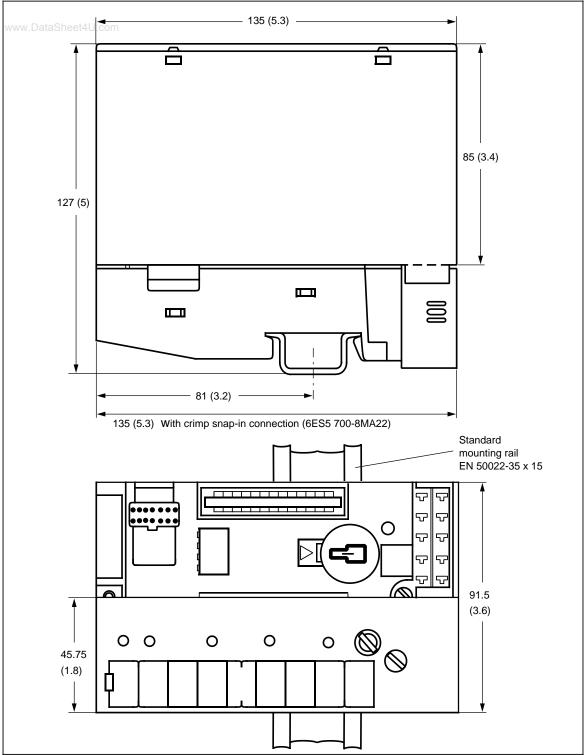

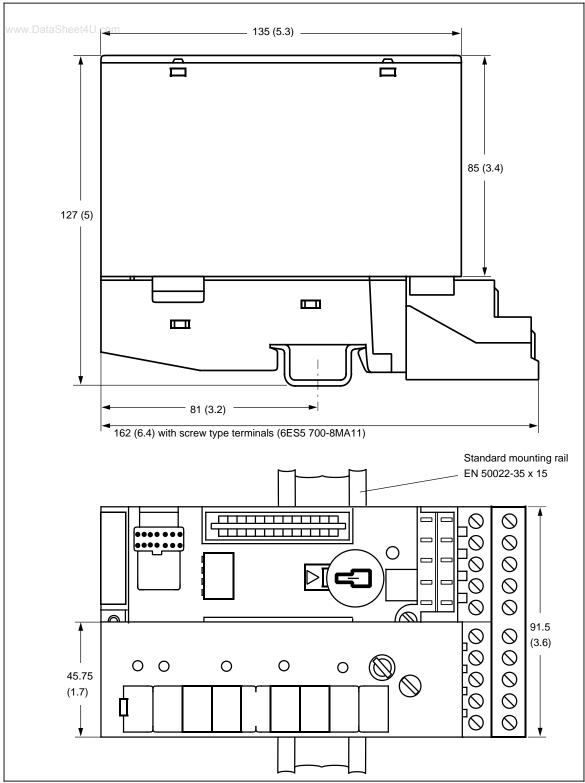

Except for the I/O module, all of the S5-100U components are mounted on standard mounting rails in accordance with DIN EN 50022-35x15. Mount the rails on a metal plate to obtain the same reference potential.

Bus units with a SIGUT/screw-type, or crimp snap-in connection method have different heights.

If you install, remove, or change any parts of your S5-100U system, your system must be in the state indicated in Table 3-1.

Table 3-1. Installing, Removing, and Changing S5-100U Components

| Installing, Removing, and Changing: | S5-100U<br>Power Status  | S5-100U<br>Operating Mode | Load<br>Voltage |

|-------------------------------------|--------------------------|---------------------------|-----------------|

| I/O modules                         | Х                        | STOP                      | OFF             |

| Bus units<br>Interface modules      | Power OFF                | Х                         | Х               |

| CPU power supply                    | Power supply voltage OFF | Х                         | Х               |

X=not relevant

# 3.1.1 Assembling a Tier

You need the following components to configure the S5-100U:

- Power supply module

- Central processing unit

- Bus units

- I/O modules

If you do not have a 24 V DC power supply, you must have a power supply module.

Mount the first module on the extreme left end of the standard mounting rail. Add other modules to the right of the first module.

#### Mounting the PS 930 Power Supply Module

The backplane design makes it easy to attach this module to the standard mounting rail.

- 1. Hook the module onto the standard mounting rail.

- 2. Swing the module back until the slide snaps into place (see Figure 3-1).

Figure 3-1. Mounting the PS 930 Power Supply Module

### Removing the PS 930 Power Supply Module

- 1. Turn off the 115 V/230 V AC power supply.

- 2. Remove the connections between the CPU and the power supply module.

- 3. Use a screwdriver to press down on the slide on the bottom of the module.

- 4. Swing the module up and out of the standard mounting rail.

#### **Mounting the Central Processing Unit**

Follow the same procedure you used to mount the PS 930 power supply module (see Figure 3-1).

- 1. Hook the CPU onto the rail and to the right of the power supply module.

- 2. Swing the CPU back until the slide snaps into place.

### **Removing the CPU**

- 1. Remove the I/O module located at slot "0".

- 2. Pull the connection (ribbon cable) between the CPU and the first bus unit.

- 3. Pull the connections between the CPU and the power supply module.

- 4. Use a screwdriver to press down on the slide on the bottom of the module.

- 5. Swing the module up and out of the standard mounting rail.

#### **Mounting Bus Units**

Use the same procedures to mount the bus unit that you used to mount both the power supply module and the CPU. Hooks are located on the sides of each bus unit. These hooks are used to connect bus units to each other and to connect bus units to the CPU.

## Connecting Bus Units to Each Other or to the CPU

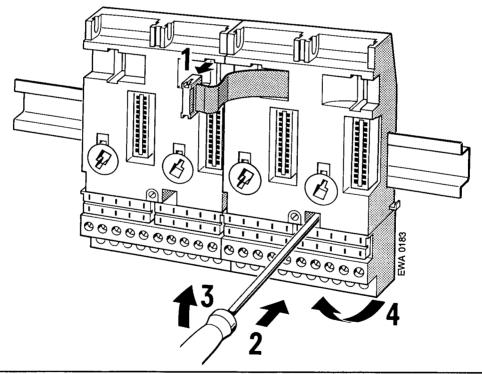

- Pull the ribbon cable connector located on the top left of the bus unit out of its holder.

- Plug the connector either into the receptacle located on the right side of the CPU or into the receptacle of the adjacent bus unit located on the left (see Figure 3-2).

#### **Removing Bus Units**

- 1. Pull the connections to the neighboring bus units or to the CPU.

- 2. Use a screwdriver to press down on the slide.

- 3. Swing the module up and out of the standard mounting rail.

Figure 3-2. Removing Bus Units

#### Plugging Input and Output Modules into the Bus Units

Before you plug in an input or output module, you must set the bus unit's coding element to match the module type.

#### Setting the Coding Element

An identification number is printed on the front plate of every I/O module. Depending on the particular module type, the number is between two and eight. There is a white mechanical coding key located on the back of each module. The position of the coding key is determined by the module type and cannot be changed. The bus unit has a mating component for each key, a white rotating coding element or "lock" (see Figure 3-3).

Use a screwdriver to set the "lock" on the bus unit to the corresponding I/O module code number.

Figure 3-3. Coding System to Prevent an Inadvertent Interchange of Modules

The 6ES5 788-8MA11 simulator module does not have a coding key. You can plug in this simulator module in place of any module.

#### Attaching I/O Modules

- 1. Hook the module onto the top of the bus unit.

- 2. Swing the module down onto the bus unit.

- 3. Press the module down firmly.

- 4. Tighten the hold-down screw on the front of the module to attach the module to the bus unit.

#### Removing I/O Modules

Remove the hold-down screw and swing the module up and out of the bus unit.

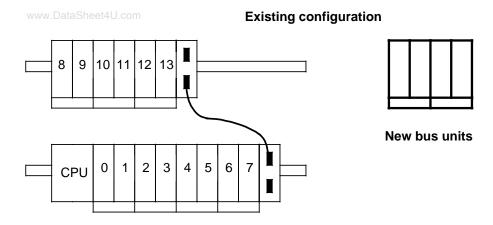

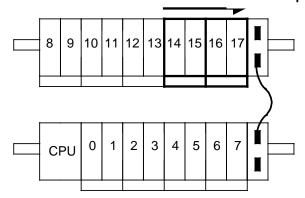

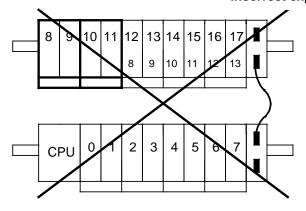

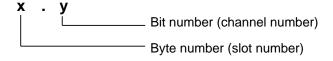

# 3.1.2 Multi-Tier Expansion

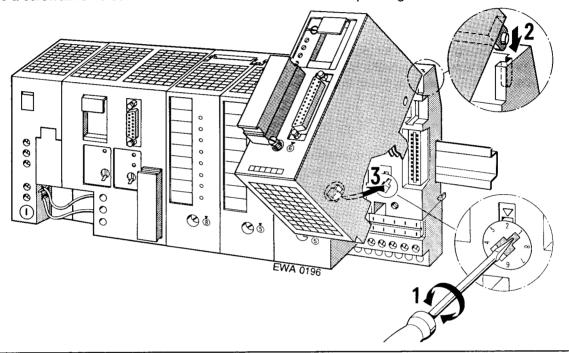

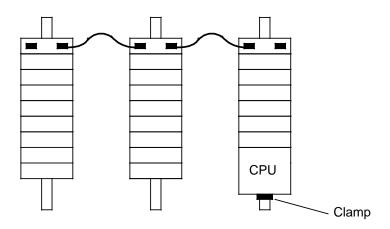

If it is not possible to have all of the modules located on one tier, you can expand the configuration up to four tiers. You may use a maximum of 16 bus units. It does not matter how many bus units are mounted on a tier. You need one interface module per tier to interconnect the tiers.

Install an interface module as you would install a bus unit. You must connect each interface module to the last bus unit via the ribbon cable.

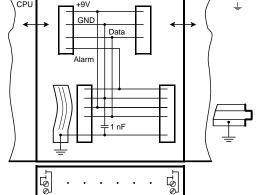

Use the IM 315 interface module for two-tier configurations. The IM 315 consists of two modules permanently connected to each other via a 0.5-m (20-in.) cable.

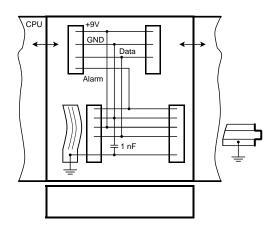

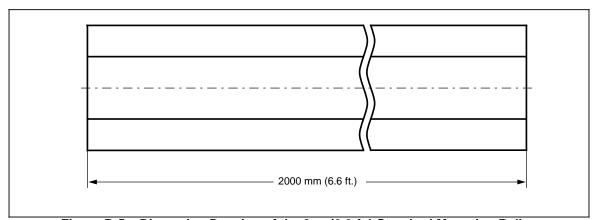

Use the IM 316 interface modules for multi-tier configurations. Use the 712-8 connecting cable to connect the IM 316 interface modules (Order No. 6ES5 712-8...).

The standard mounting rails must have a common reference potential if they are mounted in different cabinets.

Figure 3-4. Interconnecting Tiers with Interface Modules (6ES5 316-8MA12)

| Installation Guidelines | S5-100L |

|-------------------------|---------|

#### **Installing an Interface Module**

- 1. Hook the interface module to the standard mounting rail.

- 2. Swing the interface module back until the slide on the bottom snaps into place on the rail.

- 3. Use the ribbon cable to connect the module to the last bus unit.

- 4. Use connecting cable 712-8 to join the two interface modules.

- 5. Connect the cable to the "out" socket on the programmable controller tier and to the "in" socket on the expansion tier.

- 6. Securely screw the connecting cable plugs in place. Use two screws for each connecting cable plug.

#### Removing an Interface Module

- 1. Only for the IM 316: Remove the hold-down screws from the plugs and remove the connecting cable.

- 2. Remove the connecting ribbon cable from the adjacent bus unit.

- 3. Use a screwdriver to press down on the slide located on the bottom of the interface module.

- 4. Swing the module up and out of the standard mounting rail.

3-6 EWA 4NEB 812 6120-02b

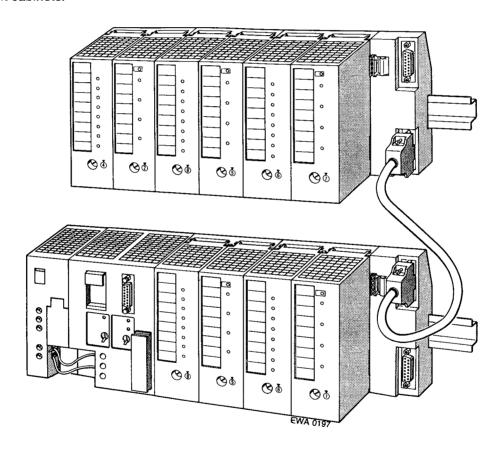

## 3.1.3 Cabinet Mounting

www.DataSheet4U.com

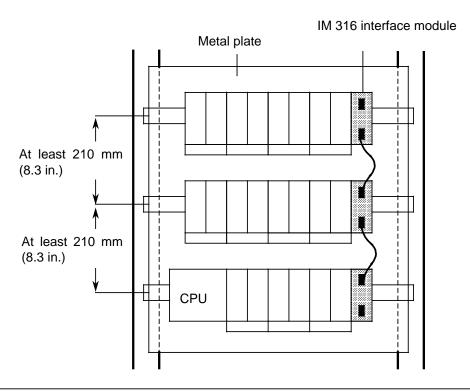

Make sure that the S5-100U, the power supply, and all modules are well grounded. Mount the S5-100U on a metal plate to help prevent noise. There should be electrical continuity between the grounded enclosure and the mounting rails. Make sure that the system is bonded to earth.

You can use the 8LW system or the 8LX system mounting plates (see Catalog NV 21).

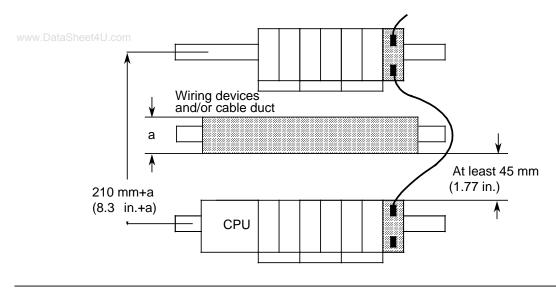

Adequate ventilation and heat dissipation are important to the proper operation of the system. You must have at least 210 mm (8.3 in.) between each mounting rail (see Figures in Appendix B) for proper ventilation.

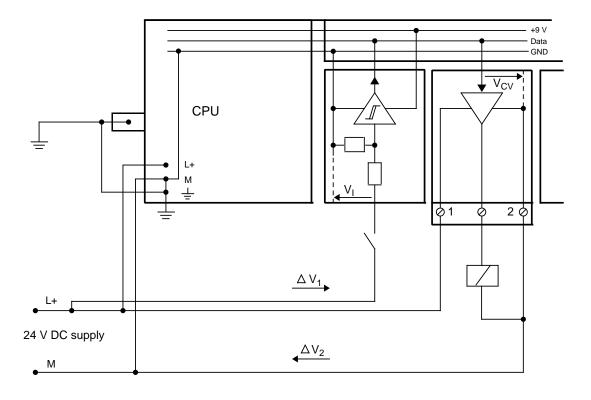

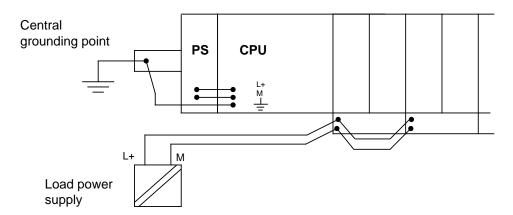

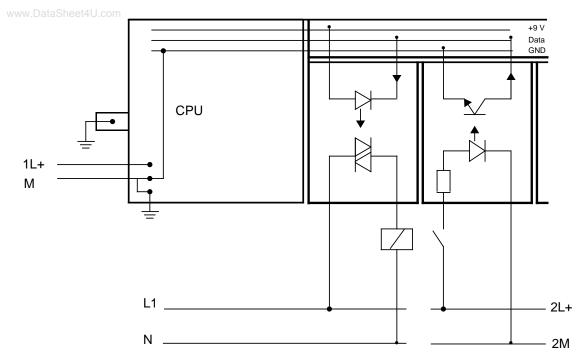

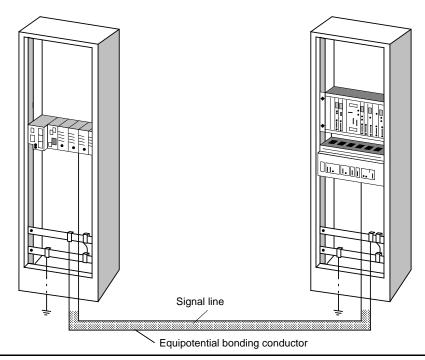

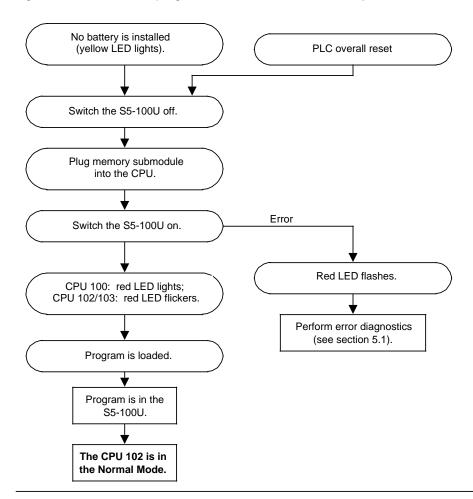

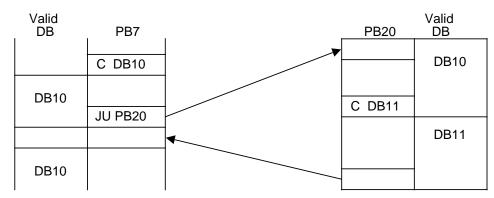

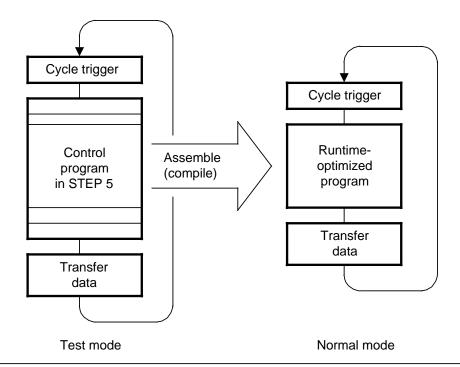

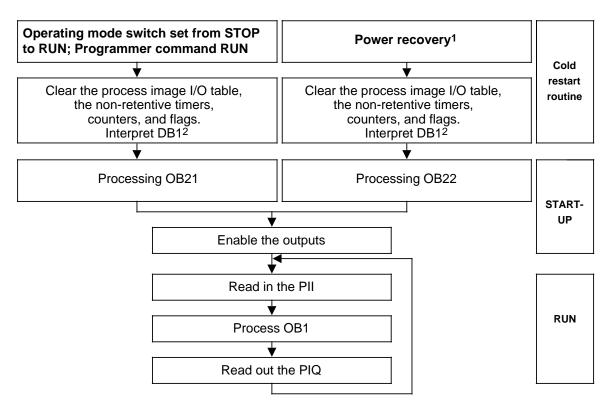

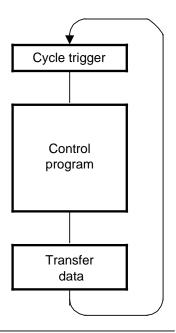

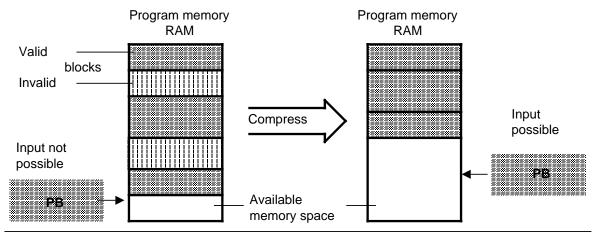

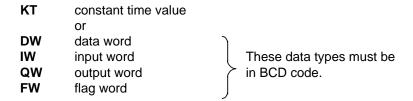

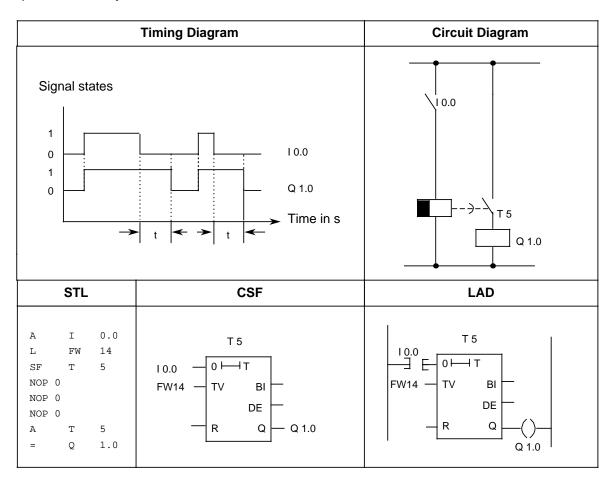

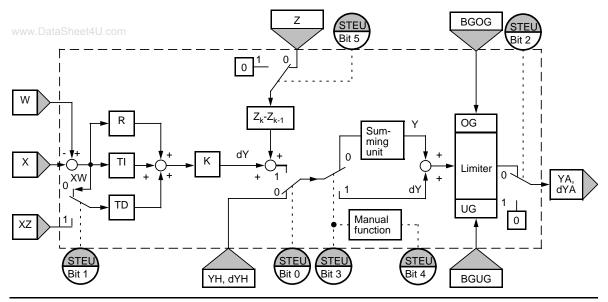

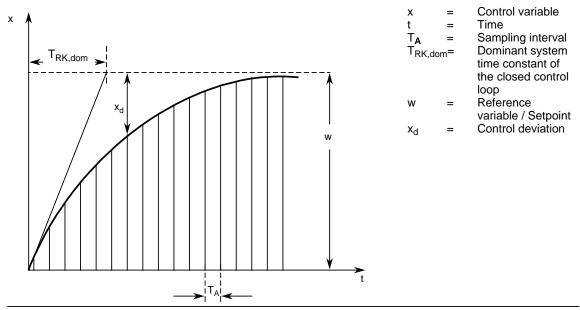

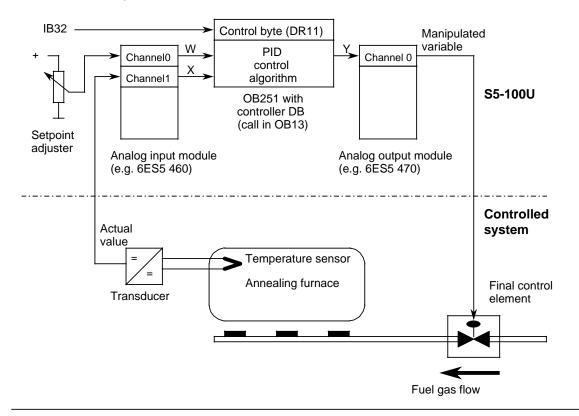

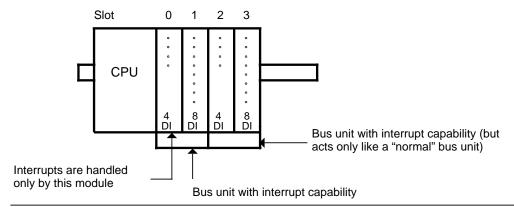

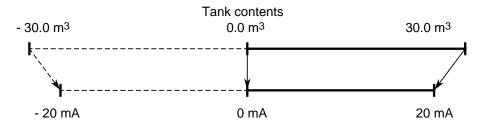

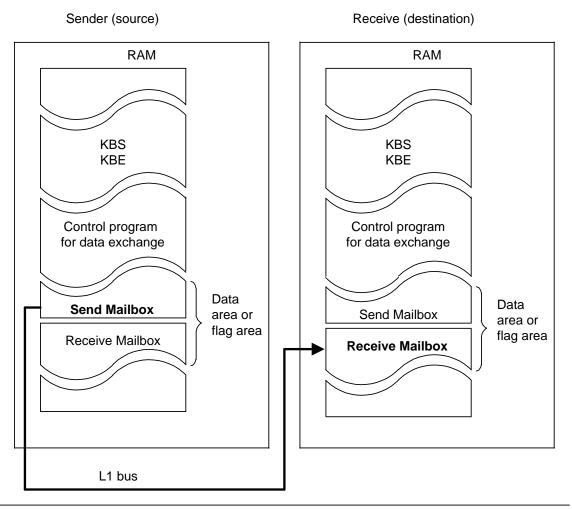

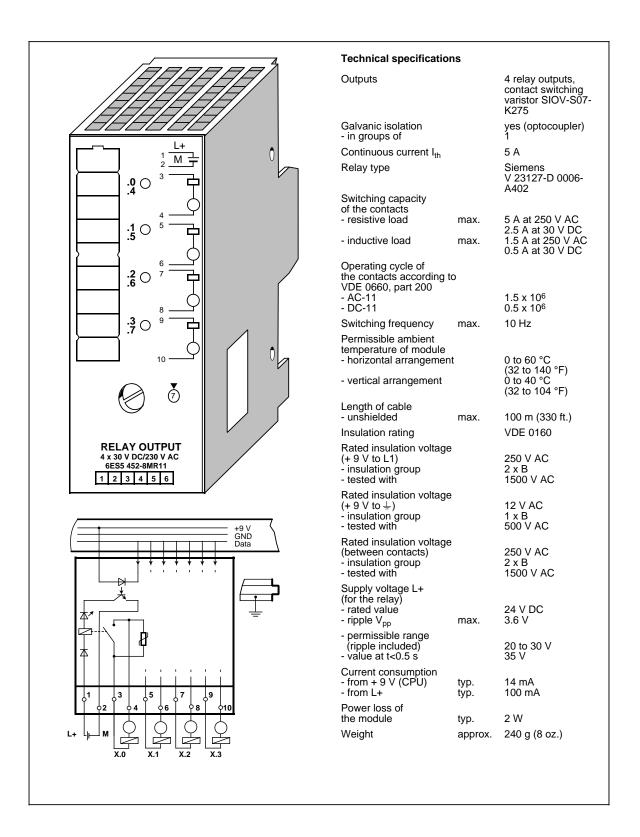

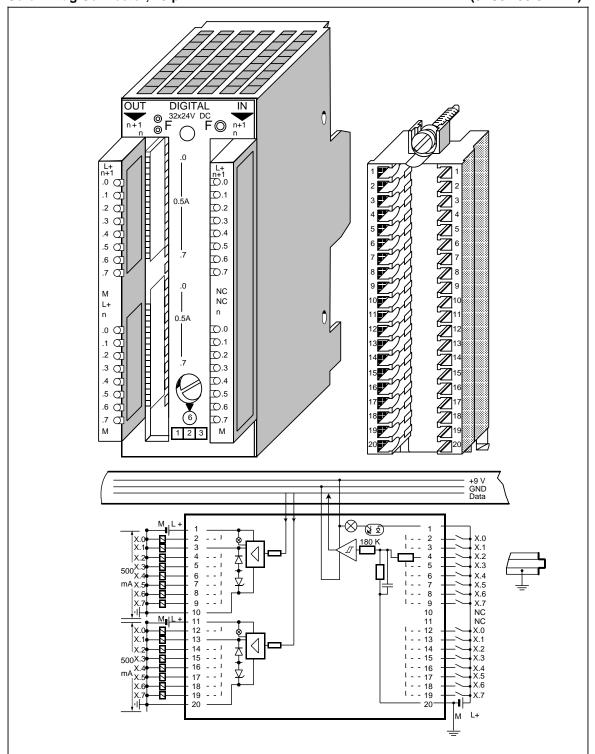

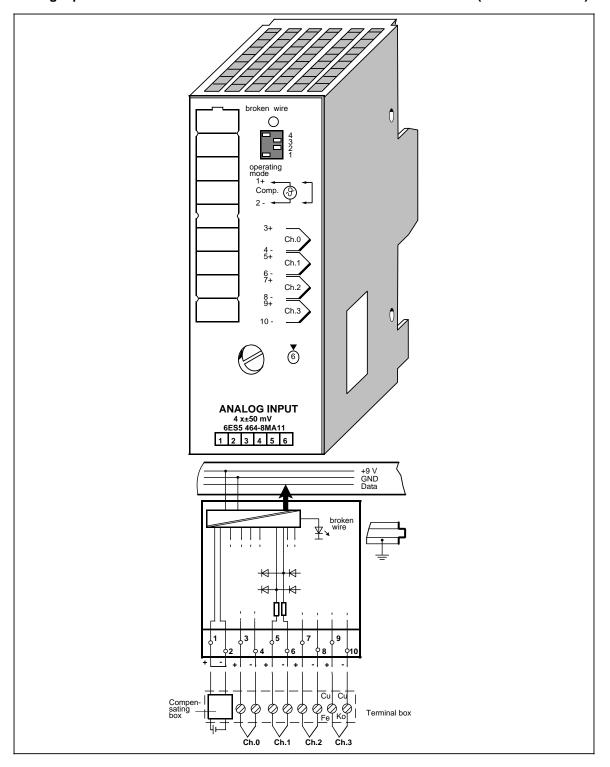

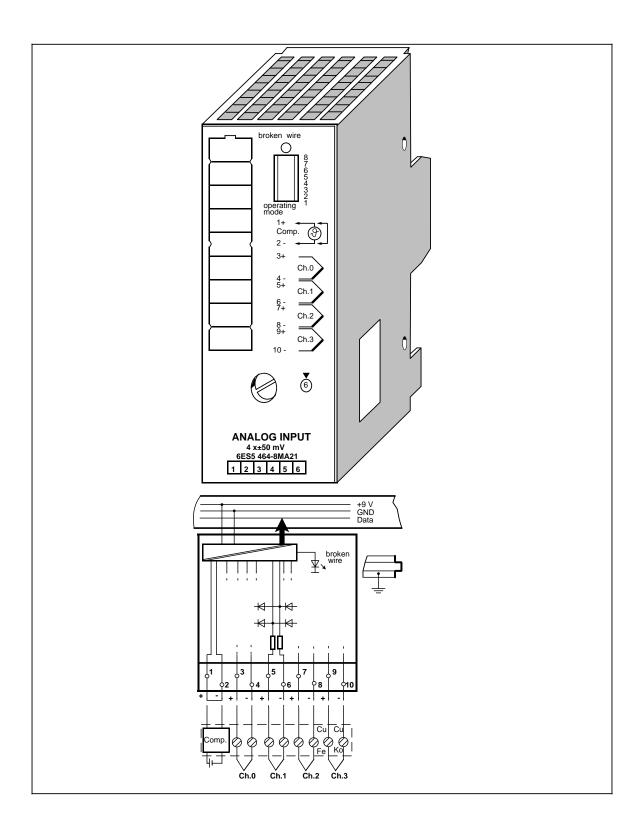

Always locate the power supply and the CPU on the lowest tier to ensure better heat dissipation. To measure cabinet ventilation, define the total heat loss by calculating the sum of all typical heat losses (see Catalog ST 52.1).