# S1R72900F00A Technical Manual

### **NOTICE**

No parts of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind aristing out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export licence from teh Ministry of International Trade and Industry or other approval from another government agency.

© SEIKO EPSON CORPORATION 2001, All rights reserved.

All other product names mentioned herein are trademarks and/or registered trademarkes of their respective companies.

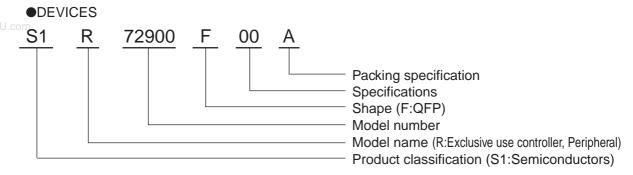

# The information of the product number change

Starting April 1, 2001 the product number has been changed as listed below. Please use the new product number when you place an order. For further information, please contact Epson sales representative.

# Configuration of product number

# **Contents**

| 1. | DESCRIPTION                          | 1  |

|----|--------------------------------------|----|

| 2. | FEATURES                             | 1  |

| 3. | BLOCK DIAGRAM                        | 2  |

| 4. | PIN LAYOUT                           | 3  |

| 5. | PIN ASSIGNMENT TABLE                 | 4  |

| 6. | PIN DESCRIPTION                      | 7  |

| 7. | FUNCTIONAL DESCRIPTION               | 9  |

|    | 7.1 Control Register                 | 9  |

|    | 7.2 Data Format                      | 24 |

|    | 7.3 Cable Port Interface             | 27 |

|    | 7.4 Link Layer Controller Interface  | 30 |

|    | 7.5 Oscillating Circuit              | 42 |

|    | 7.6 Power Down                       | 42 |

| 8. | ELECTRICAL CHARACTERISTICS           | 43 |

|    | 8.1 Absolute Maximum Ratings         | 43 |

|    | 8.2 Recommended Operating Conditions | 43 |

|    | 8.3 DC Characteristics               | 44 |

|    | 8.4 AC Characteristics               | 47 |

| 9. | EXAMPLE OF EXTERNAL CONNECTION       | 49 |

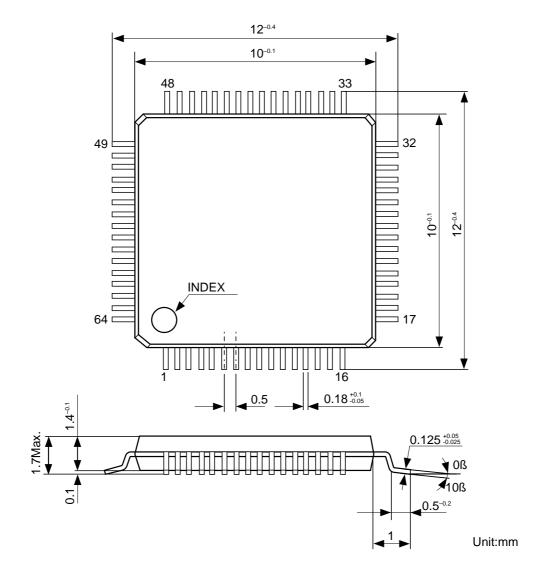

| 10 | OUTLINE DIMENSIONS                   | 50 |

### 1. DESCRIPTION

The SIR72900F00A is a physical layer IC compliant with the IEEE 1394-1995 and IEEE 1394a-2000 standards.

With the two 1394 ports, the SIR72900F00A supports transmission speeds of 400/200/100 Mbit/sec. The product incorporates a 400-MHz PLL, reference voltage generating circuit, high-speed transceiver, LINK layer interface, and a state machine circuit for bus initialization and arbitration.

www.DataSheet4II.com

### 2. FEATURES

- Complies with the IEEE 1394-1995 and IEEE 1394a-2000 standards.

- Supports transmission speeds of S400 (393.216 Mbit/sec), S200 (196.608 Mbit/sec), and S100 (98.304 Mbit/sec).

- Incorporates a 400-MHz PLL for transmission at S400/S200/S100 and 50-MHz SCLK output.

- Offers independent TpBias output for each port.

- Supports the Cable Power Status function that detects a cable power drop.

- Supports DC and AC connections of the PHY/LINK interface.

- Built-in oscillating circuit

- High-accuracy, low-amplitude differential high-speed transceiver

- Bus initialization, arbitration, port connection, and control state machine circuits

- PHY/LINK interface circuit

- High-speed DS encoder

- Supports the short bus reset function at detection of LINK layer IC power-off.

- Single 3.3-V power supply

- 64-Pin Plastic QFP

- Designed with the low-power CMOS technology.

<sup>\*</sup> This product is not radioresistant.

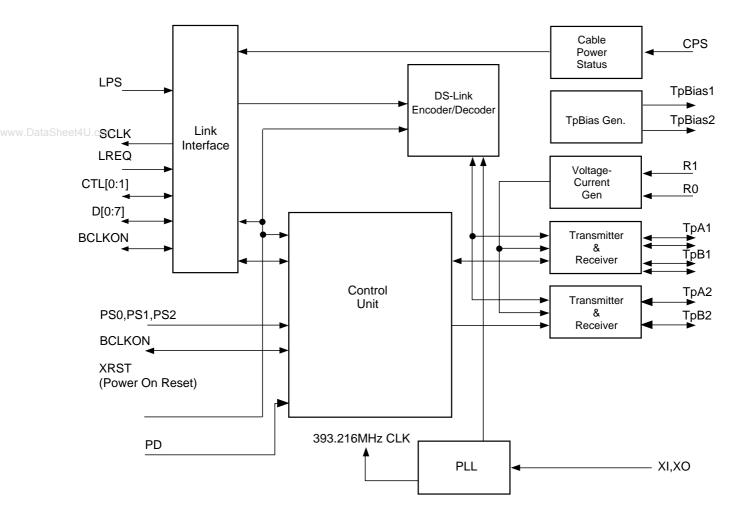

### 3. BLOCK DIAGRAM

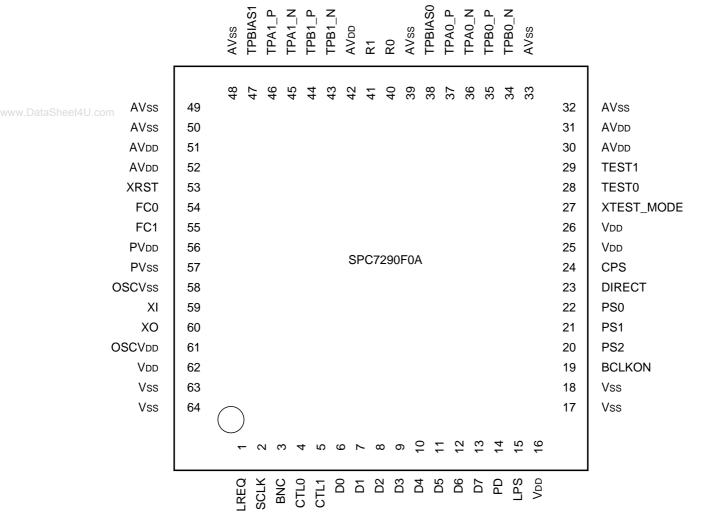

### 4. PIN LAYOUT

www.DataSheet4U.com

# **5. PIN ASSIGNMENT TABLE**

The items listed on the pin assignment table are as follows:

| PIN No.  | Pin number                                                          |  |  |  |  |  |  |

|----------|---------------------------------------------------------------------|--|--|--|--|--|--|

| PIN NAME | Pin name of the SIR72900F00A                                        |  |  |  |  |  |  |

| POWER    | Supply voltage for each I/O cell                                    |  |  |  |  |  |  |

| PLANE    | VDD: 3.3-V power supply for the digital circuit                     |  |  |  |  |  |  |

|          | AVDD: 3.3-V power supply for the analog circuit                     |  |  |  |  |  |  |

|          | PVDD: 3.3-V power supply for the PLL circuit                        |  |  |  |  |  |  |

| 4U.com   | OSCVDD: 3.3-V power supply for the oscillating circuit              |  |  |  |  |  |  |

| I/O ATTR | Type of I/O cells                                                   |  |  |  |  |  |  |

|          | I: Input pin                                                        |  |  |  |  |  |  |

|          | O: Output pin                                                       |  |  |  |  |  |  |

|          | I/O : Input/output pin                                              |  |  |  |  |  |  |

|          | P: Power pin                                                        |  |  |  |  |  |  |

| DRIVE    | Drivability of output pins                                          |  |  |  |  |  |  |

| TERM     | Resistance of the pull-up or pull-down resistor provided on the pin |  |  |  |  |  |  |

|         |            | POWER          | I/O      | DRIV           | TERM(Ω) |   |

|---------|------------|----------------|----------|----------------|---------|---|

| PIN No. | PIN NAME   | PIN NAME PLANE |          | 3              | 3.3V    |   |

|         |            |                |          | IOL            | IOH     |   |

| 1       | LREQ       | VDD            | I        | _              | _       | _ |

| 2       | SCLK       | VDD            | 0        | -6             | 6       | _ |

| 3       | BNC        | VDD            | 0        | -2             | 2       | _ |

| 4       | CTL0       | VDD            | I/O      | -6             | 6       | _ |

| 5       | CTL1       | VDD            | I/O      | -6             | 6       | _ |

| 6       | D0         | VDD            | I/O      | -6             | 6       | _ |

| 7       | D1         | VDD            | I/O      | -6             | 6       | _ |

| 8       | D2         | VDD            | I/O      | -6             | 6       | _ |

| a 🦠 i   | D3         | VDD            | I/O      | -6             | 6       | _ |

| 10      | D4         | VDD            | I/O      | -6             | 6       | _ |

| 11      | D5         | VDD            | I/O      | -6             | 6       | _ |

| 12      | D6         | VDD            | I/O      | -6             | 6       | _ |

| 13      | D7         | VDD            | I/O      | <del>-</del> 6 | 6       | _ |

| 14      | PD         | VDD            | 1/0      | _              | _       | _ |

| 15      | LPS        | VDD            | i        | _              | _       | _ |

| 16      | VDD        | VDD            | <u> </u> | _              | _       | _ |

| 17      | Vss        | Vss            | _        | _              | _       | _ |

| 18      | Vss        | Vss            | _        | _              | _       | _ |

| 19      | BCLKON     | VDD            | I/O      |                | 6       |   |

| 20      | PS2        | VDD            | I/O      | _0             | _       |   |

| 21      | PS1        | VDD            | ı<br>İ   |                |         |   |

|         | PS0        |                | -        | _              | _       | _ |

| 22      |            | VDD            |          | _              | _       | _ |

| 23      | DIRECT     | VDD            |          | _              | _       | _ |

| 24      | CPS        | VDD            | l        | _              | _       | _ |

| 25      | VDD        | VDD            | _        | _              | _       | _ |

| 26      | VDD        | VDD            |          | _              | _       | _ |

| 27      | XTEST_MODE | VDD            | l l      | _              | _       | _ |

| 28      | TEST0      | VDD            | <u> </u> | _              | _       | _ |

| 29      | TEST1      | VDD            | I        | _              | _       | _ |

| 30      | AVdd       | AVDD           | _        | _              | _       | _ |

| 31      | AVdd       | AVDD           | _        | _              | _       | _ |

| 32      | AVss       | AVss           | _        | _              | _       | _ |

| 33      | AVss       | AVss           | _        | _              | _       | _ |

| 34      | TPB0_N     | AVDD           | I/O      | _              | _       | _ |

| 35      | TPB0_P     | AVDD           | I/O      | _              | _       | _ |

| 36      | TPA0_N     | AVDD           | I/O      | _              | _       | _ |

| 37      | TPA0_P     | AVDD           | I/O      | _              | _       | _ |

| 38      | TPBIAS0    | AVDD           | 0        | _              | _       | _ |

| 39      | AVss       | AVss           | _        | _              | _       | _ |

| 40      | R0         | AVDD           | 0        | _              | _       | _ |

| 41      | R1         | AVDD           | 0        | _              | _       | _ |

| 42      | AVDD       | AVDD           | _        | _              | _       | _ |

| 43      | TPB1_N     | AVDD           | I/O      | _              | _       | _ |

| 44      | TPB1_P     | AVDD           | I/O      | _              | _       | _ |

| 45      | TPA1_N     | AVDD           | I/O      | _              | _       | _ |

| 46      | TPA1_P     | AVDD           | I/O      | _              | _       | _ |

| 47      | TPBIAS1    | AVDD           | 0        | _              | _       | _ |

| 48      | AVss       | AVss           | _        | _              | _       | _ |

www.DataSheet4H.com

|       |               | DIN 1445 | POWER  | 1/0  |      | E(mA) | TERM(Ω) |

|-------|---------------|----------|--------|------|------|-------|---------|

|       | PIN No.       | PIN NAME | PLANE  | ATTR | 3.3V |       | 3.3V    |

|       |               |          |        |      | IOL  | IOH   |         |

|       | 49            | AVss     | AVss   | _    | _    | _     | _       |

|       | 50            | AVss     | AVss   | _    | _    | _     | _       |

|       | 51            | AVDD     | AVDD   | _    | _    | _     | _       |

|       | 52            | AVDD     | AVdd   | _    | _    | _     | _       |

|       | 53            | XRST     | VDD    | I    | _    | _     | 100     |

|       | 54            | FC0      | PVdd   | _    | _    | _     | _       |

|       | 55            | FC1      | PVdd   | _    | _    | _     | _       |

|       | 56            | PVDD     | PVdd   | _    | _    | _     | _       |

| ww.Da | a <b>57</b> ° | PVss     | PVss   | _    | _    | _     | _       |

|       | 58            | OSCVss   | OSCVss | _    | _    | _     | _       |

|       | 59            | XI       | OSCVDD | I    | _    | _     | _       |

|       | 60            | XO       | OSCVDD | 0    | _    | _     | _       |

|       | 61            | OSCVDD   | OSCVDD | _    | _    | _     | _       |

|       | 62            | VDD      | VDD    | _    | _    | _     | _       |

|       | 63            | Vss      | Vss    | _    | _    | _     | _       |

|       | 64            | Vss      | Vss    | _    | _    | _     | _       |

# 6. PIN DESCRIPTION

| Pin name   | Function                                        | Pin No.                 | Pin typ.          | I/O |

|------------|-------------------------------------------------|-------------------------|-------------------|-----|

| AVDD       | Analog circuit power supply pin                 | 30,31,42,51,52          | Supply            | _   |

| AVss       | Analog circuit ground pin                       | 32,33,39,48,49,50       | Supply            | _   |

| PVDD       | PLL circuit power supply pin                    | 56                      | Supply            | _   |

| PVss       | PLL circuit ground pin                          | 57                      | Supply            | _   |

| VDD        | Digital circuit power supply pin                | 16,25,26,62             | Supply            | _   |

| Vss        | Digital circuit ground pin                      | 17,18,63,64             | Supply            | _   |

| OSCVDD     | Oscillating circuit power supply pin            | 61                      | Supply            | _   |

| OSCVss     | Oscillating circuit ground pin                  | 58                      | Supply            | _   |

| TPA0_P     | Port 0, TPA+ I/O signal                         | 37                      | Differential      | I/O |

| TPA0_N     | Port 0, TPA- I/O signal                         | 36                      | Differential      | I/O |

| TPB0_P     | Port 0, TPB+ I/O signal                         | 35                      | Differential      | I/O |

| TPB0_N     | Port 0, TPB- I/O signal                         | 34                      | Differential      | I/O |

| TPBIAS0    | Port 0, TP bias voltage supply pin              | 38                      | Supply            | 0   |

| TPA1_P     | Port 1, TPA+ I/O signal                         | 46                      | Differential      | I/O |

| TPA1_N     | Port 1, TPA- I/O signal                         | 45                      | Differential      | I/O |

| TPB1_P     | Port 1, TPB+ I/O signal                         | 44                      | Differential      | I/O |

| TPB1_N     | Port 1, TPB- I/O signal                         | 43                      | Differential      | I/O |

| TPBIAS1    | Port 1, TP bias voltage supply pin              | 47                      | Supply            | 0   |

|            | Connect 6.0k $\Omega$ (1.0%) between the        |                         | 11.7              |     |

| R1, R0     | external reference resistor connecting          | 41,40                   | Analog            | 0   |

| ,          | pins R1 and R0.                                 | ,                       | G                 |     |

|            | Power down input pin                            |                         |                   |     |

| PD         | Connect this pin to Vss during normal           | 14                      | Hysteresis        | 1   |

|            | operation.                                      |                         | ,                 |     |

|            | Bus Manager Contender/Link-On pin               |                         |                   |     |

| DOLKON     | The status of this pin determines whether       | 40                      | 01400             | 1/0 |

| BCLKON     | the bus manager function is used at the         | 19                      | CMOS              | I/O |

|            | time of hard reset. See 7.4.3.                  |                         |                   |     |

| LDEO       | Request signal from the Link layer              | 4                       | I livete se e i e |     |

| LREQ       | controller IC                                   | 1                       | Hysteresis        |     |

| CTL0, CTL1 | PHY/LINK interface bidirectional control signal | 4,5                     | Hysteresis        | I/O |

| D0 to D7   | PHY/LINK interface bidirectional data signal    | 6,7,8,9,<br>10,11,12,13 | Hysteresis        | I/O |

| 00114      | 49.152 MHz system clock to the Link             |                         |                   |     |

| SCLK       | layer controller IC                             | 2                       |                   | 0   |

|            | Link power status pin.                          |                         |                   |     |

| LPS        | A signal used to monitor whether the Link       | 15                      | Hysteresis        | 1   |

|            | layer controller IC is active.                  |                         | •                 |     |

|            | Power status pin                                |                         |                   |     |

| PS2        | These pins configure the POWER                  |                         |                   |     |

| PS1        | ·                                               |                         | CMOS              | I   |

| PS0        | PS1, and PS2 are respectively bits 21,          |                         |                   |     |

|            | 22, 23 of the Self-ID packet.                   |                         |                   |     |

|            | Configured according to the isolation           |                         |                   |     |

|            | barrier configuration between PHY and           |                         |                   |     |

| DIRECT     | LINK.                                           | 23                      | CMOS              | 1   |

|            | Connect this pin to VDD for DC or single        |                         |                   |     |

|            | capacitor AC connection.                        |                         |                   |     |

|            | 1                                               |                         |                   |     |

www.DataSheet4U.com

|                 | Pin name   | Function                                   | Pin No.    | Pin typ.    | I/O |

|-----------------|------------|--------------------------------------------|------------|-------------|-----|

|                 |            | Test pin                                   |            |             |     |

|                 | XTEST_MODE | Connect this pin to VDD during normal      | 27         | CMOS        | I   |

|                 |            | operation.                                 |            |             |     |

|                 |            | Reset pin                                  |            |             |     |

|                 |            | The SIR72900F00A is initialized when       |            |             |     |

|                 | XRST       | this pin is set to 0.                      | 53         | Hysteresis  | 1   |

|                 | ANGI       | After turning on the power supply,         | 55         | Tiysteresis | '   |

|                 |            | for at least 2ms, maintain XRST = 0.       |            |             |     |

|                 |            | Set this pin to 1 during normal operation. |            |             |     |

| D-4-01441       |            | Cable Power Status detection pin           |            |             |     |

| www.DataSheet4L | l.com      | Connect this pin to the cable power        |            |             |     |

|                 | CPS        | through a 240k $\Omega$ resistor.          | Hysteresis | I           |     |

|                 |            | Also, connect a diode (VF = 0.4V)          |            |             |     |

|                 |            | between the PHY-VDD.                       |            |             |     |

|                 |            | Signal indicating the cable status.        |            |             |     |

|                 | BNC        | Outputs HIGH when all the ports do not     | 3          | CMOS        | 0   |

|                 |            | receive bias voltage from the node on      | 3          |             | O   |

|                 |            | the other side.                            |            |             |     |

|                 |            | Connection pin for PLL filter              |            |             |     |

|                 | FC0        | The SIR72900F00A does not need             | 54         | Analog      | 0   |

|                 |            | external capacitor. Set this pin to open.  |            |             |     |

|                 |            | Connection pin for PLL filter              |            |             |     |

|                 | FC1        | The SIR72900F00A does not need             | 55         | Analog      | 0   |

|                 |            | external capacitor. Set this pin to open.  |            |             |     |

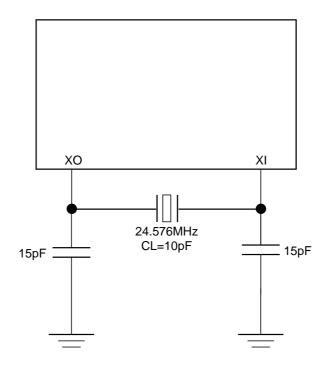

|                 | XI         | Pin for a 24.576MHz crystal oscillator     | 59         |             |     |

|                 | XO         | Pin for a 24.576MHz crystal oscillator     | 60         |             |     |

|                 |            | Test pin                                   |            |             |     |

|                 | TEST0      | Connect this pin to Vss during normal      | 28         | CMOS        | 1   |

|                 |            | operation.                                 |            |             |     |

|                 |            | Test pin                                   |            |             |     |

|                 | TEST1      | Connect this pin to Vss during normal      | 29         | CMOS        | 1   |

|                 |            | operation.                                 |            |             |     |

### 7. FUNCTIONAL DESCRIPTION

### 7.1 Control Register

### 7.1.1 Accessing the register

The registers on the SIR72900F00A are accessed from the Link layer controller IC. For details, see Section 7.4.4 Link interface.

Name **Address** 0 1 2 3 4 5 6 7 Register0 0000 Physical\_ID R PS Register1 0001 RHB **IBR** Gap\_count Register2 0010 Extended Total\_ports Register3 0011 Max\_speed Delay Register4 LCtrl Power class 0100 Contender Jitter Register5 **ISBR** Pwr fail Timeout Port event Enab accel Enab multi 0101 Watchdog Loop Register6 0110 Register7 0111 Page\_Select Port\_Select Register8 1000 1001 Register9 1010 RegisterA 1011 RegisterB 1100 RegisterC 1101 RegisterD 1110 RegisterE 1111 RegisterF

Table 7.1 Registers

### 7.1.2 Register bits

This section explains the control register bits of the SIR72900F00A. In the R/W column, R means read only and R/W means readable/writable. The Power Reset Value column shows the initial value (0 or 1) which each bit takes after power-on reset.

### 7.1.2.1 Register 0

| Address | Bit Symbol       | R/W | Power Reset Value | Description        |

|---------|------------------|-----|-------------------|--------------------|

| 0x01    | 0: RHB           | R/W | 0                 | Root Hold Bit      |

|         | 1: IBR           | R/W | 0                 | Initiate Bus Reset |

|         | 2: Gap_count [0] | R/W | 1                 | Gap Count_bit0     |

|         | 3: Gap_count [1] | R/W | 1                 | Gap Count_bit1     |

|         | 4: Gap_count [2] | R/W | 1                 | Gap Count_bit2     |

|         | 5: Gap_count [3] | R/W | 1                 | Gap Count_bit3     |

|         | 6: Gap_count [4] | R/W | 1                 | Gap Count_bit4     |

|         | 7: Gap_count [5] | R/W | 1                 | Gap Count_bit5     |

### Bits 0 to 5: Physical Node ID

This register address 00h is output as a status to the PHY/LINK interface after transmission of a Self-ID packet. These bits indicate Node IDs that were determined during a Self-ID period and they are determined when transmitting a Self-ID packet during a Self-ID period. These bits are initialized by bus reset (BR).

### Bit 6: Root Indicator

This bit is determined during a Tree-ID period and it indicates the root setting for its node.

When this bit is '1', this node is set as the root and initialized by bus reset.

### Bit 7: Cable Power Status

This bit indicates the cable power supply status reflecting the status of the CPS pin.

When this bit is '1', it indicates that the power is supplied through the cable.

### 7.1.2.2 Register 1

| Address | Bit Symbol       | R/W | Power Reset Value | Description        |

|---------|------------------|-----|-------------------|--------------------|

| 0x01    | 0: RHB           | R/W | 0                 | Root Hold Bit      |

|         | 1: IBR           | R/W | 0                 | Initiate Bus Reset |

|         | 2: Gap_count [0] | R/W | 1                 | Gap Count_bit0     |

|         | 3: Gap_count [1] | R/W | 1                 | Gap Count_bit1     |

|         | 4: Gap_count [2] | R/W | 1                 | Gap Count_bit2     |

|         | 5: Gap_count [3] | R/W | 1                 | Gap Count_bit3     |

|         | 6: Gap_count [4] | R/W | 1                 | Gap Count_bit4     |

| U.com   | 7: Gap_count [5] | R/W | 1                 | Gap Count_bit5     |

Bit 0: Root Hold Bit

This bit is set automatically by PHY configuration packet transmission.

When this bit is '1', it is a request that the node should be the root at the next bus reset.

Bit 1: Initiate Bus Reset

Setting this bit immediately issues a bus reset command.

When this bit is '1', a bus reset is issued. This bit is initialized by bus reset.

### Bits 2 to 7: Gap Count

These bits are also set automatically by PHY Configuration packet transmission indicating Gap Count values. They retain the value at the first bus reset after configuration, and are initialized at the second bus reset.

### 7.1.2.3 Register 2

| Address | Bit Symbol       | R/W | Power Reset Value | Description |

|---------|------------------|-----|-------------------|-------------|

| 0x03    | 0: Max_speed [0] | R   | 0                 | Speed       |

|         | 1: Max_speed [1] | R   | 1                 | Speed       |

|         | 2: Max_speed [2] | R   | 0                 | Speed       |

|         | 3: Reserved      | R   | 0                 |             |

|         | 4: Delay [0]     | R   | 0                 | Delay       |

|         | 5: Delay [1]     | R   | 0                 | Delay       |

|         | 6: Delay [2]     | R   | 1                 | Delay       |

|         | 7: Delay [3]     | R   | 0                 | Delay       |

Bits 0 to 2: Extended register

The register map that the SIR72900F00A supports. '111b' is read.

### Bits 3 to 7: Total of Port

The number of ports on the SIR72900F00A. Normally, 2 ('00010b') is read.

### 7.1.2.4 Register 3

| Address | Bit Symbol         | R/W              | Power Reset Value | Description  |

|---------|--------------------|------------------|-------------------|--------------|

| 0x04    | 0: LCtrl           | R/W              | 1                 | Link Control |

|         | 1: Contender       | $R/\overline{W}$ | See discription   | Contender    |

|         | 2: Jitter [0]      | R                | 0                 | Jitter       |

|         | 3: Jitter [1]      | R                | 0                 | Jitter       |

|         | 4: Jitter [2]      | R                | 0                 | Jitter       |

|         | 5: Power_class [0] | $R/\overline{W}$ | 0                 | Power Class  |

|         | 6: Power_class [1] | $R/\overline{W}$ | 0                 | Power Class  |

|         | 7: Power_class [2] | $R/\overline{W}$ | 0                 | Power Class  |

### Bits 0 to 2: Speed

The maximum transmission speed the SIR72900F00A supports. Normally, 2 ('010b') is read.

### Bit 3: Reserved

#### Bits 4 to 7: Delay

The SIR72900F00A's repeat delay in the worst cases. Normally, 2 ('0010b') is read.

The maximum repeat delay time of the SIR72900F00A is  $0.184~\mu s$ .

### 7.1.2.5 Register 4

| Address | Bit Symbol         | R/W              | Power Reset Value | Description  |

|---------|--------------------|------------------|-------------------|--------------|

| 0x04    | 0: LCtrl           | R/W              | 1                 | Link Control |

|         | 1: Contender       | $R/\overline{W}$ | See discription   | Contender    |

|         | 2: Jitter [0]      | R                | 0                 | Jitter       |

|         | 3: Jitter [1]      | R                | 0                 | Jitter       |

|         | 4: Jitter [2]      | R                | 0                 | Jitter       |

|         | 5: Power_class [0] | $R/\overline{W}$ | 0                 | Power Class  |

|         | 6: Power_class [1] | $R/\overline{W}$ | 0                 | Power Class  |

|         | 7: Power_class [2] | $R/\overline{W}$ | 0                 | Power Class  |

#### Bit 0: Link Control

This bit controls the value of the L ( $link\_active$ ) field of the Self-ID packet. The L ( $link\_active$ ) field of the Self-ID packet reflects the logical multiplication between this bit and LPS signal.

This bit is initialized to '1' as bus reset occurs.

### Bit 1: Contender

This bit reflects the c (CONTENDER) field of the Self-ID packet. This bit has the same meaning as the c (CONTENDER) field of the Self-ID packet.

This bit reflects the value of the BCLKON pin when hardware reset occurs.

#### Bits 2 to 4: Jitter

A difference between the maximum and minimum repeat delays of the SIR72900F00A. Normally, 0'000b' is read. The repeat jitter of the SIR72900F00A is 20 ns.

### Bits 5 to 7: Power Class

These bits reflect the pwr (POWER\_CLASS) field of the Self-ID packet. They have the same meaning as the pwr (POWER\_CLASS) field of the Self-ID packet.

These bits are initialized to the value of pins PS0, PS1, and PS2 when hardware reset occurs.

The relationships between the bits and pins PS0, PS1, and PS2 are as follows:

bit5:PS0(Pin22)

bit6:PS1(Pin21)

bit7:PS2(Pin20)

### 7.1.2.6 Register 5

| Address | Bit Symbol    | R/W | Power Reset Value | Description                             |

|---------|---------------|-----|-------------------|-----------------------------------------|

| 0x05    | 0: Watchdog   | R/W | 0                 | Watchdog                                |

|         | 1: ISBR       | R/W | 0                 | Initiate Short Bus Reset                |

|         | 2: Loop       | R/W | 0                 | Loop detect                             |

|         | 3: Pwr_fail   | R/W | 1                 | Cable power failure detect              |

|         | 4: Timeout    | R/W | 0                 | Arbtration state machine timeout        |

|         | 5: Port_event | R/W | 0                 | Port_event detect                       |

|         | 6: Enab_accel | R/W | 0                 | Enable arbitration acceleration         |

| l.com   | 7: Enab_multi | R/W | 0                 | Enable multi-speed packet concatenation |

SHEELAU.

### Bit 0: Watchdog

When set to '1,' this bit communicates the status of Loop, Power\_fail, and Arb\_timeout to the Link layer controller IC, regardless of the status of the PHY/LINK interface. When a resume action starts on any port, this bit sends a resume interrupt signal regardless of the value of Int\_enable.

### Bit 1: Initiate Short (Arbitrated) Bus Reset

Setting this bit to '1' issues short bus reset.

This bit is cleared when the short bus reset completes.

### Bit 2: Loop detect

When this bit is '1,' the bus is looped.

This bit is cleared when hardware reset occurs or '1' is written.

#### Bit 3: Cable power failure detect

When this bit is '1,' it means that the PC bit has changed from 1 to 0.

This bit is cleared when '1' is written.

#### Bit 4: Arbitration state machine timeout

When this bit is '1,' it means that the node had been in a state other than Tree\_IDStart longer than MAX\_ARB\_STATE\_TIME.

This bit is cleared when hardware reset occurs or '1' is written.

### Bit 5: Port\_event detect

When Int\_enable is '1,' detection of a change in the Connected, Bias, Disabled, or Fault bit sets this bit to '1.'Also, when Watchdog is '1,' a Resume process sets this bit to '1.'

This bit is cleared when hardware reset occurs or '1' is written.

#### Bit 6: Enable arbitration acceleration

Setting this bit to '1' causes Ack-acceleration arbitration and fly-by arbitration. When this bit is set to '0,' no acceleration arbitration occurs.

This bit is initialized as hardware reset occurs.

### Bit 7: Enable multi-speed packet concatenation

When this bit is set to '1,' a joint packet transmission request requires a speed code. When this bit is set to '0,' joint packet transmission is done at the same speed as the first packet transmission.

This bit is initialized as hardware reset occurs.

### 7.1.2.7 Register 6

| Address | Bit Symbol  | R/W | Power Reset Value | Description |

|---------|-------------|-----|-------------------|-------------|

| 0x06    | 0: Reserved | R   | 0                 |             |

|         | 1: Reserved | R   | 0                 |             |

|         | 2: Reserved | R   | 0                 |             |

|         | 3: Reserved | R   | 0                 |             |

|         | 4: Reserved | R   | 0                 |             |

|         | 5: Reserved | R   | 0                 |             |

|         | 6: Reserved | R   | 0                 |             |

| IU.com  | 7: Reserved | R   | 0                 |             |

Bits 0 to 7: Reserved

# 7.1.2.8 Register 7

| Address | Bit Symbol         | R/W              | Power Reset Value | Description |

|---------|--------------------|------------------|-------------------|-------------|

| 0x07    | 0: Page_select [0] | R/W              | 0                 |             |

|         | 1: Page_select [1] | $R/\overline{W}$ | 0                 |             |

|         | 2: Page_select [2] | $R/\overline{W}$ | 0                 |             |

|         | 3: Reserved        | R                | 0                 |             |

|         | 4: Port_select [0] | $R/\overline{W}$ | 0                 |             |

|         | 5: Port_select [1] | $R/\overline{W}$ | 0                 |             |

|         | 6: Port_select [2] | $R/\overline{W}$ | 0                 |             |

|         | 7: Port_select [3] | $R/\overline{W}$ | 0                 |             |

Bits 0 to 2: Page Select

These bits specify what page between 1000b and 1111b of the PHY register should be accessed.

Bit 3: Reserved

### Bits 4 to 7: Port Select

When the Page\_select bit selects Port Status Page, these bits specify what port between 1000b and 1111b of the PHY register should be accessed.

Table 7.2 Registers of Page\_Select 0

| Name       | Address | 0   | 1                       | 2     | 3          | 4     | 5         | 6    | 7        |

|------------|---------|-----|-------------------------|-------|------------|-------|-----------|------|----------|

| Register00 | 1000    | AS  | tat                     | BStat |            | Child | Connected | Bias | Disabled |

| Register01 | 1001    | Neg | Negotiated_speed Int_er |       | Int_enable | Fault |           |      |          |

| Register02 | 1010    |     |                         |       |            |       |           |      |          |

| Register03 | 1011    |     |                         |       |            |       |           |      |          |

| Register04 | 1100    |     |                         |       |            |       |           |      |          |

| Register05 | 1101    |     |                         |       |            |       |           |      |          |

| Register06 | 1110    |     |                         |       |            |       |           |      |          |

| Register07 | 1111    |     |                         |       |            |       |           |      |          |

vw.DataSheet4U.com

### 7.1.3 Page select 0 bits

### 7.1.3.1 Register 00

| Address | Bit Symbol   | R/W | Power Reset Value | Description   |

|---------|--------------|-----|-------------------|---------------|

| 0x08    | 0: Astat [0] | R   | 0                 | Status of TPA |

|         | 1: Astat [1] | R   | 0                 | Status of TPA |

|         | 2: Bstat [0] | R   | 0                 | Status of TPB |

|         | 3: Bstat [1] | R   | 0                 | Status of TPB |

|         | 4: Child     | R   | 0                 | Child         |

|         | 5: Connected | R   | 0                 | Connected     |

|         | 6: Bias      | R   | 0                 | Cable Bias    |

|         | 7: Disabled  | R/W | See description   | Port Disabled |

### Bits 0 to 1: Status of TPA

These bits indicate the status of TPA. The meaning of these bits is as follows:

'11b':Z

'01b':1

'10b':0

'00b':invalid

### Bits 2 to 3: Status of TPB

These bits indicate the status of TPB. The meaning of these bits is as follows:

'11b':Z

'01b':1

'10b':0

'00b':invalid

### Bit 4: Child

When this bit is '1,' the port is a Child. When this bit is '0,' the port is a Parent.

This bit is initialized by bus reset, and determined during a Tree-ID period.

#### Bit 5: Connected

When this bit is '1,' it indicates that the port recognizes a node is connected.

### Bit 6: Cable Bias

This bit reflects the cable bias detected at the port. When this bit is '1,' it indicates that TpBias is detected at the port.

#### Bit 7: Port Disabled

When this bit is set to '1,' the port is disabled.

This bit is initialized as hardware reset occurs.

### 7.1.3.2 Register 01

| Address | Bit Symbol              | R/W              | Power Reset Value | Description                 |

|---------|-------------------------|------------------|-------------------|-----------------------------|

| 0x09    | O: Negotiated_speed [0] | R                | 0                 | Negotiated speed            |

|         | 1: Negotiated_speed [1] | R                | 0                 | Negotiated speed            |

|         | 2: Negotiated_speed [2] | R                | 0                 | Negotiated speed            |

|         | 3: Int_enable           | R/W              | 0                 | Enable port event interrupt |

|         | 4: Fault                | $R/\overline{W}$ | 0                 | fault                       |

|         | 5: Reserved             | R                | 0                 |                             |

|         | 6: Reserved             | R                | 0                 |                             |

| U.com   | 7: Reserved             | R                | 0                 |                             |

Bits 0 to 2: Negotiated speed

These bits indicate the speed of the node connected to the port.

They are initialized by bus reset, and determined during a Self-ID period.

The meaning of these bits is as follows:

'000b': The maximum transmission speed is 100 Mbps.

'001b': The maximum transmission speed is 200 Mbps.

'010b': The maximum transmission speed is 400 Mbps.

### Bit 3: Enable port event interrupt

When this bit is set to '1,' the Port\_event bit is set to '1' when a change in the Connected, Bias, Disabled, or Fault bit occurs.

This bit is initialized as hardware reset occurs.

### Bit 4: Fault

When this bit is '1,' it indicates that an error has occurred during suspend/resume operation.

This bit is cleared when hardware reset occurs or '1' is written.

Bits 5 to 7: Reserved

### 7.1.3.3 Register 02

| Address | Bit Symbol  | R/W | Power Reset Value | Description |

|---------|-------------|-----|-------------------|-------------|

| 0x0A    | 0: Reserved | R   | 0                 |             |

|         | 1: Reserved | R   | 0                 |             |

|         | 2: Reserved | R   | 0                 |             |

|         | 3: Reserved | R   | 0                 |             |

|         | 4: Reserved | R   | 0                 |             |

|         | 5: Reserved | R   | 0                 |             |

|         | 6: Reserved | R   | 0                 |             |

|         | 7: Reserved | R   | 0                 |             |

# 7.1.3.4 Register 03

| Address | Bit Symbol  | R/W | Power Reset Value | Description |

|---------|-------------|-----|-------------------|-------------|

| 0x0B    | 0: Reserved | R   | 0                 |             |

|         | 1: Reserved | R   | 0                 |             |

|         | 2: Reserved | R   | 0                 |             |

|         | 3: Reserved | R   | 0                 |             |

|         | 4: Reserved | R   | 0                 |             |

|         | 5: Reserved | R   | 0                 |             |

|         | 6: Reserved | R   | 0                 |             |

| U.com   | 7: Reserved | R   | 0                 |             |

Bits 0 to 7: Reserved

# 7.1.3.5 Register 04

| Address | Bit Symbol  | R/W | Power Reset Value | Description |

|---------|-------------|-----|-------------------|-------------|

| 0x0C    | 0: Reserved | R   | 0                 |             |

|         | 1: Reserved | R   | 0                 |             |

|         | 2: Reserved | R   | 0                 |             |

|         | 3: Reserved | R   | 0                 |             |

|         | 4: Reserved | R   | 0                 |             |

|         | 5: Reserved | R   | 0                 |             |

|         | 6: Reserved | R   | 0                 |             |

|         | 7: Reserved | R   | 0                 |             |

Bits 0 to 7: Reserved

# 7.1.3.6 Register 05

| Address | Bit Symbol  | R/W | Power Reset Value | Description |

|---------|-------------|-----|-------------------|-------------|

| 0x0D    | 0: Reserved | R   | 0                 |             |

|         | 1: Reserved | R   | 0                 |             |

|         | 2: Reserved | R   | 0                 |             |

|         | 3: Reserved | R   | 0                 |             |

|         | 4: Reserved | R   | 0                 |             |

|         | 5: Reserved | R   | 0                 |             |

|         | 6: Reserved | R   | 0                 |             |

|         | 7: Reserved | R   | 0                 |             |

# 7.1.3.7 Register 06

| Address | Bit Symbol  | R/W | Power Reset Value | Description |

|---------|-------------|-----|-------------------|-------------|

| 0x0E    | 0: Reserved | R   | 0                 |             |

|         | 1: Reserved | R   | 0                 |             |

|         | 2: Reserved | R   | 0                 |             |

|         | 3: Reserved | R   | 0                 |             |

|         | 4: Reserved | R   | 0                 |             |

|         | 5: Reserved | R   | 0                 |             |

|         | 6: Reserved | R   | 0                 |             |

| J.com   | 7: Reserved | R   | 0                 |             |

Bits 0 to 7: Reserved

# 7.1.3.8 Register 07

| Address | Bit Symbol  | R/W | Power Reset Value | Description |

|---------|-------------|-----|-------------------|-------------|

| 0x0F    | 0: Reserved | R   | 0                 |             |

|         | 1: Reserved | R   | 0                 |             |

|         | 2: Reserved | R   | 0                 |             |

|         | 3: Reserved | R   | 0                 |             |

|         | 4: Reserved | R   | 0                 |             |

|         | 5: Reserved | R   | 0                 |             |

|         | 6: Reserved | R   | 0                 |             |

|         | 7: Reserved | R   | 0                 |             |

Table 7.3 Registers of Page\_Select 1

| Name       | Address | 0 | 1                 | 2 | 3        | 4          | 5 | 6 | 7 |  |

|------------|---------|---|-------------------|---|----------|------------|---|---|---|--|

| Register10 | 1000    |   | Complience_level  |   |          |            |   |   |   |  |

| Register11 | 1001    |   |                   |   |          |            |   |   |   |  |

| Register12 | 1010    |   | Vendor_ID [16:23] |   |          |            |   |   |   |  |

| Register13 | 1011    |   | Vendor_ID [8:15]  |   |          |            |   |   |   |  |

| Register14 | 1100    |   | Vendor_ID [0:7]   |   |          |            |   |   |   |  |

| Register15 | 1101    |   |                   |   | Product_ | ID [16:23] |   |   |   |  |

| Register16 | 1110    |   |                   |   | Product_ | ID [8:15]  |   |   |   |  |

| Register17 | 1111    |   |                   |   | Product  | _ID [0:7]  |   |   |   |  |

www DataSheet411 com

# 7.1.4 Page\_select 1 bits

# 7.1.4.1 Register 10

| Address | Bit Symbol              | R/W | Power Reset Value | Description      |

|---------|-------------------------|-----|-------------------|------------------|

| 0x08    | 0: Compliance_level [0] | R   | 0                 | Compliance_level |

|         | 1: Compliance_level [1] | R   | 0                 | Compliance_level |

|         | 2: Compliance_level [2] | R   | 0                 | Compliance_level |

|         | 3: Compliance_level [3] | R   | 0                 | Compliance_level |

|         | 4: Compliance_level [4] | R   | 0                 | Compliance_level |

|         | 5: Compliance_level [5] | R   | 0                 | Compliance_level |

|         | 6: Compliance_level [6] | R   | 0                 | Compliance_level |

|         | 7: Compliance_level [7] | R   | 1                 | Compliance_level |

Bits 0 to 7: Compliance Level

Normally, 1 ('01h') for P1394a-compliant is read.

# 7.1.4.2 Register 11

| Address | Bit Symbol  | R/W | Power Reset Value | Description |

|---------|-------------|-----|-------------------|-------------|

| 0x09    | 0: Reserved | R   | 0                 |             |

|         | 1: Reserved | R   | 0                 |             |

|         | 2: Reserved | R   | 0                 |             |

|         | 3: Reserved | R   | 0                 |             |

|         | 4: Reserved | R   | 0                 |             |

|         | 5: Reserved | R   | 0                 |             |

|         | 6: Reserved | R   | 0                 |             |

|         | 7: Reserved | R   | 0                 |             |

# 7.1.4.3 Register 12

| Address | Bit Symbol        | R/W | Power Reset Value | Description     |

|---------|-------------------|-----|-------------------|-----------------|

| 0x0A    | 0: Vendor_ID [16] | R   | 0                 | Vendor_ID_bit16 |

|         | 1: Vendor_ID [17] | R   | 0                 | Vendor_ID_bit17 |

|         | 2: Vendor_ID [18] | R   | 0                 | Vendor_ID_bit18 |

|         | 3: Vendor_ID [19] | R   | 0                 | Vendor_ID_bit19 |

|         | 4: Vendor_ID [20] | R   | 0                 | Vendor_ID_bit20 |

|         | 5: Vendor_ID [21] | R   | 0                 | Vendor_ID_bit21 |

|         | 6: Vendor_ID [22] | R   | 0                 | Vendor_ID_bit22 |

| U.com   | 7: Vendor_ID [23] | R   | 0                 | Vendor_ID_bit23 |

Bits 0 to 7: Vendor ID [16:23]

For the SIR72900F00A, '00h' is read.

# 7.1.4.4 Register 13

| Address | Bit Symbol        | R/W | Power Reset Value | Description     |

|---------|-------------------|-----|-------------------|-----------------|

| 0x0B    | 0: Vendor_ID [8]  | R   | 0                 | Vendor_ID_bit8  |

|         | 1: Vendor_ID [9]  | R   | 0                 | Vendor_ID_bit9  |

|         | 2: Vendor_ID [10] | R   | 0                 | Vendor_ID_bit10 |

|         | 3: Vendor_ID [11] | R   | 0                 | Vendor_ID_bit11 |

|         | 4: Vendor_ID [12] | R   | 0                 | Vendor_ID_bit12 |

|         | 5: Vendor_ID [13] | R   | 0                 | Vendor_ID_bit13 |

|         | 6: Vendor_ID [14] | R   | 0                 | Vendor_ID_bit14 |

|         | 7: Vendor_ID [15] | R   | 0                 | Vendor_ID_bit15 |

Bits 0 to 7: Vendor ID [8:15]

For the SIR72900F00A, '00h' is read.

# 7.1.4.5 Register 14

| Address | Bit Symbol       | R/W | Power Reset Value | Description    |

|---------|------------------|-----|-------------------|----------------|

| 0x0C    | 0: Vendor_ID [0] | R   | 0                 | Vendor_ID_bit0 |

|         | 1: Vendor_ID [1] | R   | 1                 | Vendor_ID_bit1 |

|         | 2: Vendor_ID [2] | R   | 0                 | Vendor_ID_bit2 |

|         | 3: Vendor_ID [3] | R   | 0                 | Vendor_ID_bit3 |

|         | 4: Vendor_ID [4] | R   | 1                 | Vendor_ID_bit4 |

|         | 5: Vendor_ID [5] | R   | 0                 | Vendor_ID_bit5 |

|         | 6: Vendor_ID [6] | R   | 0                 | Vendor_ID_bit6 |

|         | 7: Vendor_ID [7] | R   | 0                 | Vendor_ID_bit7 |

Bits 0 to 7: Vendor ID [0:7]

For the SIR72900F00A, '48h' is read.

# 7.1.4.6 Register 15

| Address | Bit Symbol         | R/W | Power Reset Value | Description      |

|---------|--------------------|-----|-------------------|------------------|

| 0x0D    | 0: Product_ID [16] | R   | 0                 | Product_ID_bit16 |

|         | 1: Product_ID [17] | R   | 0                 | Product_ID_bit17 |

|         | 2: Product_ID [18] | R   | 0                 | Product_ID_bit18 |

|         | 3: Product_ID [19] | R   | 0                 | Product_ID_bit19 |

|         | 4: Product_ID [20] | R   | 0                 | Product_ID_bit20 |

|         | 5: Product_ID [21] | R   | 0                 | Product_ID_bit21 |

|         | 6: Product_ID [22] | R   | 0                 | Product_ID_bit22 |

| IU.com  | 7: Product_ID [23] | R   | 0                 | Product_ID_bit23 |

Bits 0 to 7: Product ID [16:23]

For the SIR72900F00A, '00h' is read.

# 7.1.4.7 Register 16

| Address | Bit Symbol         | R/W | Power Reset Value | Description      |

|---------|--------------------|-----|-------------------|------------------|

| 0x0E    | 0: Product_ID [8]  | R   | 0                 | Product_ID_bit8  |

|         | 1: Product_ID [9]  | R   | 0                 | Product_ID_bit9  |

|         | 2: Product_ID [10] | R   | 0                 | Product_ID_bit10 |

|         | 3: Product_ID [11] | R   | 0                 | Product_ID_bit11 |

|         | 4: Product_ID [12] | R   | 0                 | Product_ID_bit12 |

|         | 5: Product_ID [13] | R   | 0                 | Product_ID_bit13 |

|         | 6: Product_ID [14] | R   | 1                 | Product_ID_bit14 |

|         | 7: Product_ID [15] | R   | 0                 | Product_ID_bit15 |

Bits 0 to 7: Product ID [8:15]

For the SIR72900F00A, '02h' is read.

# 7.1.4.8 Register 17

| Address | Bit Symbol        | R/W | Power Reset Value | Description     |

|---------|-------------------|-----|-------------------|-----------------|

| 0x0F    | 0: Product_ID [0] | R   | 0                 | Product_ID_bit0 |

|         | 1: Product_ID [1] | R   | 0                 | Product_ID_bit1 |

|         | 2: Product_ID [2] | R   | 0                 | Product_ID_bit2 |

|         | 3: Product_ID [3] | R   | 0                 | Product_ID_bit3 |

|         | 4: Product_ID [4] | R   | 0                 | Product_ID_bit4 |

|         | 5: Product_ID [5] | R   | 0                 | Product_ID_bit5 |

|         | 6: Product_ID [6] | R   | 0                 | Product_ID_bit6 |

|         | 7: Product_ID [7] | R   | 1                 | Product_ID_bit7 |

Bits 0 to 7: Product ID [0:7]

For the SIR72900F00A, '01h' is read.

Table 7.3 Registers of Page\_Select 1

| Name       | Address | 0 | 1 | 2 | 3 | 4 | 5 | 6       | 7        |

|------------|---------|---|---|---|---|---|---|---------|----------|

| Register70 | 1000    |   |   |   |   |   |   | RemSCLk | HostIsbr |

| Register71 | 1001    |   |   |   |   |   |   |         |          |

| Register72 | 1010    |   |   |   |   |   |   |         |          |

| Register73 | 1011    |   |   |   |   |   |   |         |          |

| Register74 | 1100    |   |   |   |   |   |   |         |          |

| Register75 | 1101    |   |   |   |   |   |   |         |          |

| Register76 | 1110    |   |   |   |   |   |   |         |          |

| Register77 | 1111    |   |   |   |   |   |   |         |          |

w DataSheet4II com

### 7.1.5 Page\_select 7 bits

### 7.1.5.1 Register 70

| Address | Bit Symbol  | R/W | Power Reset Value | Description |

|---------|-------------|-----|-------------------|-------------|

| 0x08    | 0: Reserved | R   | 0                 |             |

|         | 1: Reserved | R   | 0                 |             |

|         | 2: Reserved | R   | 0                 |             |

|         | 3: Reserved | R   | 0                 |             |

|         | 4: Reserved | R   | 0                 |             |

|         | 5: Reserved | R   | 0                 |             |

|         | 6: RemSCLK  | R/W | 0                 | Remain SCLK |

|         | 7: Hostlsbr | R/W | 0                 | Host Isbr   |

Bits 0 to 5: Reserved Bit 6: Remain SCLK

When this bit is set to '1,' SCLK output continues even if LPS is deasserted.

When this bit is '0,' the IC operates as per IEEE 1394a-2000.

Bit 7: Host Isbr

When this bit is '1,' the SIR72900F00A issues short bus reset when LPS is deasserted.

When this bit is '0,' the IC operates as per IEEE 1394a-2000.

### 7.1.5.2 Register 71

| Address | Bit Symbol  | R/W | Power Reset Value | Description |

|---------|-------------|-----|-------------------|-------------|

| 0x09    | 0: Reserved | R   | 0                 |             |

|         | 1: Reserved | R   | 0                 |             |

|         | 2: Reserved | R   | 0                 |             |

|         | 3: Reserved | R   | 0                 |             |

|         | 4: Reserved | R   | 0                 |             |

|         | 5: Reserved | R   | 0                 |             |

|         | 6: Reserved | R   | 0                 |             |

|         | 7: Reserved | R   | 0                 |             |

# 7.1.5.3 Register 72

| Address | Bit Symbol  | R/W | Power Reset Value | Description |

|---------|-------------|-----|-------------------|-------------|

| 0x0A    | 0: Reserved | R   | 0                 |             |

|         | 1: Reserved | R   | 0                 |             |

|         | 2: Reserved | R   | 0                 |             |

|         | 3: Reserved | R   | 0                 |             |

|         | 4: Reserved | R   | 0                 |             |

|         | 5: Reserved | R   | 0                 |             |

|         | 6: Reserved | R   | 0                 |             |

| U.com   | 7: Reserved | R   | 0                 |             |

Bits 0 to 7: Reserved

# 7.1.5.4 Register 73

| Address | Bit Symbol  | R/W | Power Reset Value | Description |

|---------|-------------|-----|-------------------|-------------|

| 0x0B    | 0: Reserved | R   | 0                 |             |

|         | 1: Reserved | R   | 0                 |             |

|         | 2: Reserved | R   | 0                 |             |

|         | 3: Reserved | R   | 0                 |             |

|         | 4: Reserved | R   | 0                 |             |

|         | 5: Reserved | R   | 0                 |             |

|         | 6: Reserved | R   | 0                 |             |

|         | 7: Reserved | R   | 0                 |             |

Bits 0 to 7: Reserved

# 7.1.5.5 Register 74

| Address | Bit Symbol  | R/W | Power Reset Value | Description |

|---------|-------------|-----|-------------------|-------------|

| 0x0C    | 0: Reserved | R   | 0                 |             |

|         | 1: Reserved | R   | 0                 |             |

|         | 2: Reserved | R   | 0                 |             |

|         | 3: Reserved | R   | 0                 |             |

|         | 4: Reserved | R   | 0                 |             |

|         | 5: Reserved | R   | 0                 |             |

|         | 6: Reserved | R   | 0                 |             |

|         | 7: Reserved | R   | 0                 |             |

# 7.1.5.6 Register 75

| Address | Bit Symbol  | R/W | Power Reset Value | Description |

|---------|-------------|-----|-------------------|-------------|

| 0x0D    | 0: Reserved | R   | 0                 |             |

|         | 1: Reserved | R   | 0                 |             |

|         | 2: Reserved | R   | 0                 |             |

|         | 3: Reserved | R   | 0                 |             |

|         | 4: Reserved | R   | 0                 |             |

|         | 5: Reserved | R   | 0                 |             |

|         | 6: Reserved | R   | 0                 |             |

| l.com   | 7: Reserved | R   | 0                 |             |

Bits 0 to 7: Reserved

# 7.1.5.7 Register 76

| Address | Bit Symbol  | R/W | Power Reset Value | Description |

|---------|-------------|-----|-------------------|-------------|

| 0x0E    | 0: Reserved | R   | 0                 |             |

|         | 1: Reserved | R   | 0                 |             |

|         | 2: Reserved | R   | 0                 |             |

|         | 3: Reserved | R   | 0                 |             |

|         | 4: Reserved | R   | 0                 |             |

|         | 5: Reserved | R   | 0                 |             |

|         | 6: Reserved | R   | 0                 |             |

|         | 7: Reserved | R   | 0                 |             |

Bits 0 to 7: Reserved

# 7.1.5.8 Register 77

| Address | Bit Symbol  | R/W | Power Reset Value | Description |

|---------|-------------|-----|-------------------|-------------|

| 0x0F    | 0: Reserved | R   | 0                 |             |

|         | 1: Reserved | R   | 0                 |             |

|         | 2: Reserved | R   | 0                 |             |

|         | 3: Reserved | R   | 0                 |             |

|         | 4: Reserved | R   | 0                 |             |

|         | 5: Reserved | R   | 0                 |             |

|         | 6: Reserved | R   | 0                 |             |

|         | 7: Reserved | R   | 0                 |             |

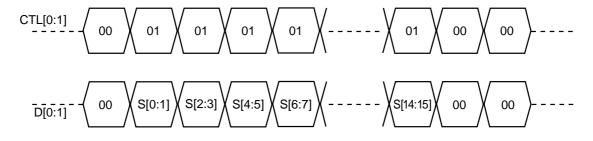

### 7.2 Data Format

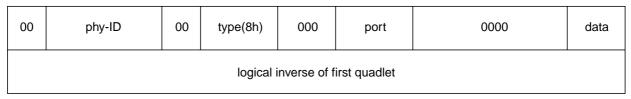

### 7.2.1 Self-ID packet

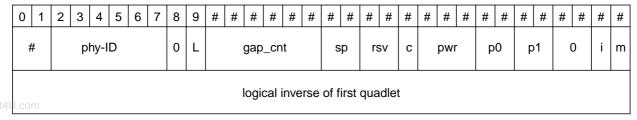

The Self-ID packets the SIR72900F00A transmits are 2-quadlet packets in the format shown in Figure 7.1. The SIR72900F00A transmits the following Self-ID packet during Self-ID period of bus initialization. The SIR72900F00A also transmits a Self-ID packet automatically as a response to a Ping packet.

Figure 7.1 Self-ID packet format

phy\_ID: physical\_ID field

Reflects the ID node of the IC.

L: LPS, LCtrl field

Reflects the logical multiplication of the LPS pin and the LCtrl bit of PHY Register 4 at the time of Self-ID packet transmission.

gap\_cnt: gap\_cnt field

Reflects the value of Gap\_Count of PHY Register 1.

sp: PHY\_SPEED field

00 = 98.304 Mbps (S100)

01 = 98.304/196.608 Mbps (S100/S200)

10 = 98.304/196.608/393.216 Mbps (S100/S200/S300)

11 = Reserved

Applicable speeds are stored. For the SIR72900F00A, this field is fixed to '10b.'

rsv: Fixed to '00b.'

C: CONTENDER field

Reflects the value of the Contender bit of PHY Register 4.

pwr: POWER CLASS field

bit21 = PSO(Pin22)

bit22 = PS1(Pin21)

bit23 = PS2(Pin20)

Reflects the Pwr bit of PHY Register 4.

The IEEE P1394a-2000 standards define this field as follows:

000 = The node does not need a power supply. The node does not repeat the power supply.

001 = The node has its own power supply and is able to supply a minimum of 15 W.

010 =The node has its own power supply and is able to supply a minimum of 30 W.

011 = The node has its own power supply and is able to supply a minimum of 45 W.

100 = The node can consume power up to 3 W from the cable. However, it does not consume any power to enable the Link or upper layers.

101 = Reserved

110 = The node can consume power up to 3 W from the cable. It can consume more power up to 3 W to enable the Link or upper layers.

111 = The node can consume power up to 3 W from the cable. It can consume more power up to 7 W to enable the Link or upper layers.

### p0, p1: Port connection status field

Indicates the port status.

11 = The port is active and connected to a child node.

10 = The port is active and connected to a parent node.

01 = The port is inactive (disabled, disconnected, or suspended).

I: initiated\_reset field

Indicates that the node has issued BusReset.

m: more\_packets field

This field is set to '1' when more than one Self-ID packet is sent. However, for the SIR72900F00A, this field is fixed to '0.'

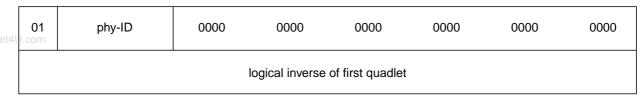

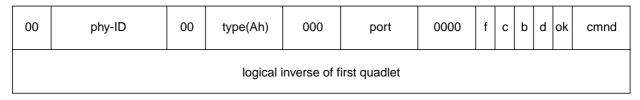

### 7.2.2 Link-on Packet

Figure 7.2 Link-on packet format

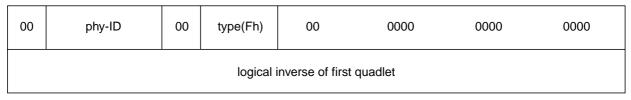

### 7.2.3 PHY Configuration Packet

| 00                               | root-ID | R | Т | gap_cnt | 0000 | 0000 | 0000 | 0000 |

|----------------------------------|---------|---|---|---------|------|------|------|------|

| logical inverse of first quadlet |         |   |   |         |      |      |      |      |

Figure 7.3 PHY Configuration packet format

### 7.2.4 Extended PHY Packet

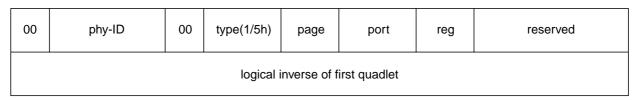

### 7.2.4.1 Ping Packet

Figure 7.4 Ping packet format

### 7.2.4.2 Remote Access Packet

Figure 7.5 Remote Access packet format

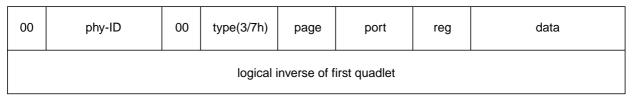

### 7.2.4.3 Remote Reply Packet

Figure 7.6 Remote Reply packet format

### 7.2.4.4 Remote Command Packet

Figure 7.7 Remote Command packet format

### 7.2.4.5 Remote Confirmation Packet

Figure 7.8 Remote Confirmation packet format

### 7.2.4.6 Resume Packet

Figure 7.9 Resume packet format

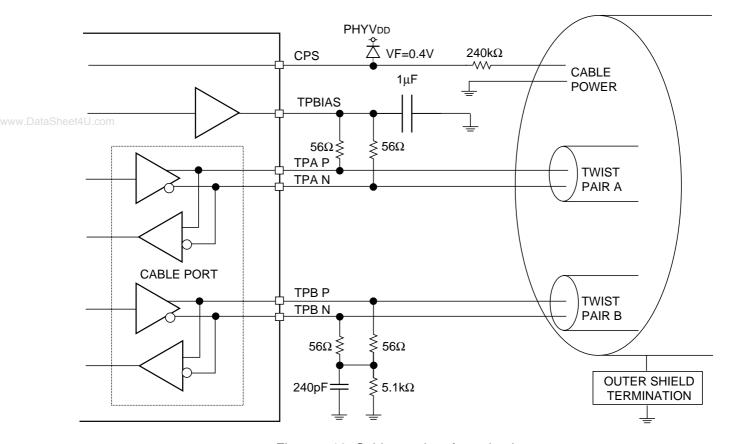

### 7.3 Cable Port Interface

### 7.3.1 Cable port interface circuit

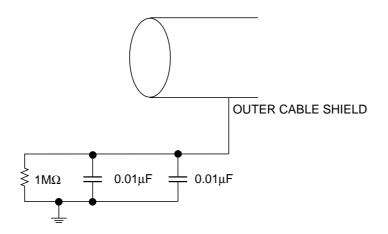

Figure 7.10 shows a circuit diagram of the cable port interface.

Figure 7.10 Cable port interface circuit

Figure 7.11 shows an example of outer shield circuit of the cable port.

Figure 7.11 Cable port outer shield circuit

#### S1R72900F00A

Cables specifically designed as per IEEE 1394 are used as media for the cable port interface. Data is transmitted through two shielded pairs of twisted cables. As shown in Figure 7.10, each twisted pair cable is connected to the TpB pair of the node to which the TpA pair of the own node.

Both TpA and TpB require two  $56\Omega$  terminating resistors appropriate to the cable impedance. Locate these terminating resistors as close to the IC pin as possible.

On the TpA side, TpBias is connected to the terminating resistor intermediate node to set inphase DC potential of the cable. To TpBias, connect a 1-µF capacitor for decoupling.

On the TpB side, connect a  $5.1k\Omega$  resistor and a 240-pF capacitor to the terminating resistor intermediate node for pull-down. The 240-pF capacitor is for decoupling.

Connect the CPS pin to the cable power through a  $240k\Omega$  resistor.

# www.DataShe743.2 Port state

The SIR72900F00A complies with the IEEE 1394a-2000 standards. The IEEE P1394a-2000 standards define the following five port states.

#### -Disabled:

A 'disabled' port does not output signals to TpBias and TpA/TpB. And the port in this state does not detect signals input to Bias and TpA/TpB. When the connection detection circuit detects a change in cable connection, this port outputs an interrupt to the upper layer if the Int\_enable bit is set.

#### -Disconnected:

A 'disconnected' port has no physical cable connection to PHY on a different node and thus does not output signals to TpBias and TpA/TpB. And the port in this state does not detect signals input to Bias and TpA/TpB.

#### -Suspended

A 'suspended' port does have physical cable connection to PHY on a different node but does not output signals to TpBias and TpA/TpB. And the port in this state does not detect signals input to TpA/TpB. On this port, only the bias detection and connection detection circuits are in operation.

#### –Resuming:

A 'resuming' port has physical cable connection to PHY on a different node and outputs signals to TpBias. On detection of bias, the port stays for a specified time and becomes active. During the resuming period, it does not detect signals input to TpA/TpB.

#### –Active:

An 'active' port has physical cable connection to PHY on a different node and outputs signals to TpBias and TpA/TpB. The port in this state detects signals input to Bias and TpA/TpB.

#### 7.3.3 Connection detecting circuit

The SIR72900F00A is equipped with a built-in connection detecting circuit. Connection detecting circuit is a circuit to detect the connected state of the cables and is effective while the port is not outputting TpBias.

#### 7.3.4 Suspend/Resume

There are two operations for the port state to transit from Active to Suspend state.

When receiving TX SUSPEND that was output by Suspend Initiator (RX SUSPEND)

The port (the Suspend Target) that received the RX SUSPEND enters the Suspend state. The node also outputs TX SUSPEND into Active ports other than the port that received RX SUSPEND, and the port is set as the Suspend Initiator. The Suspend Initiator port then also enters the Suspend state.

TX SUSPEND is transmitted until the position of this leaf node to set at the Suspend state. However, if the IEEE1394-1995 node, the Disabled port and the Suspend port are present on its way, TX SUSPEND will be transmitted to stop at their positions. Even when the port is set at Suspend state, the Fault bit is set to indicate that the Suspend state is not set normally when the Bias of the connection partner node was detected.

The conditions under which the port of the Suspend state starts the Resume operation to enter the Active state are as follows.

- The Bias of the connection partner node is detected and the Fault bit is cleared.

- -The Resume packet is received.

- -The Remote Command packet, which the Resume bits for the port were set to, is received.

If the Boundary node is not set, the other Suspended ports except this node will also start Resume operation simultaneously when the ports in the Suspend or Disconnected state start Resume operation with the Bias detected (other than Resume packet and Remote Command packet).

The Resume operation outputs TPBIAS, and it is terminated normally when the Bias of the connection partner node is detected. It then enters the Active state. However, it returns to the Suspended state to set the Fault bit, indicating that Resume operation was terminated normally if the Bias from the connection partner node cannot be detected.

When receiving the Resume Command packet which the Suspend bit for its own port was set to

The Remote Command packet is transferred two ways, from nodes other than its own node, and from the Link layer controller IC, which correspondent to the upper level layer of its own node. Either way, the Remote Confirmation packet is transferred to all ports and the PHY/LINK interface when the S1R72900F00A receives the Remote Command packet. Bus reset is then issued to all ports other than the port (Suspend Initiator) that the Suspend bit is set to, and the node enters the reset state. Simultaneously, the port which the Suspend bit is set to outputs TX SUSPEND and it then enters the Suspend state.

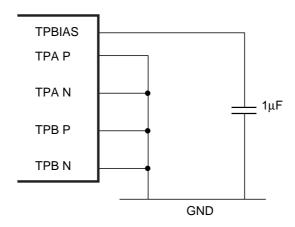

#### 7.3.5 Processing Unused Ports

If there are ports to be not used out of two SiR72009F00A cable ports, the pin should be processed as shown Figure 7-12.

Figure 7.12 Processing Unused Ports

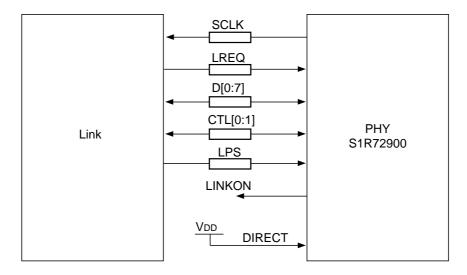

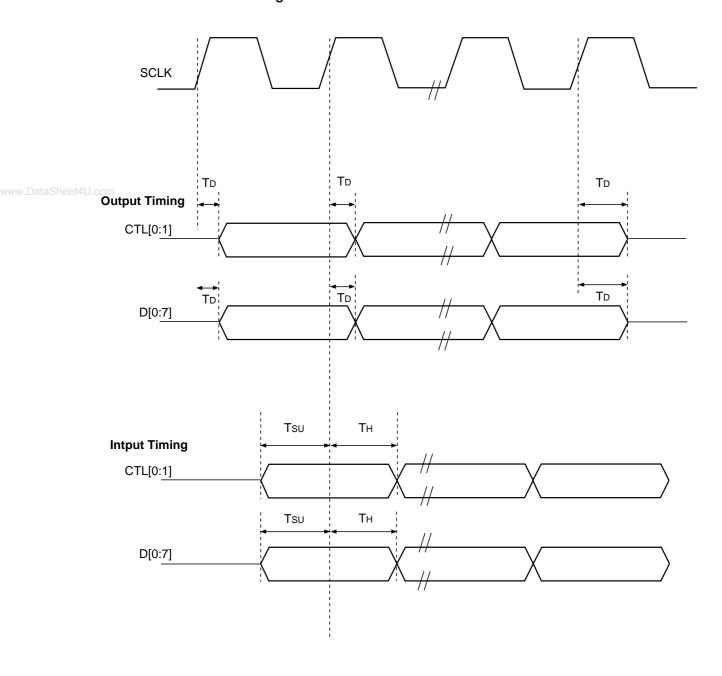

### 7.4 Link Layer Controller Interface

### 7.4.1 Connection

The SIR72900F00A can connect to a Link layer controller IC regardless of the existence of an isolation barrier. For DC connection, connect the DIRECT pin to VDD as shown in Figure 7.13.

LINKON

SCLK

LREQ

D[0:7]

CTL[0:1]

PHY

S1R72900

VDD

DIRECT

Figure 7.13 SIR72900F00A -to-Link chip connection diagram (DC connection)

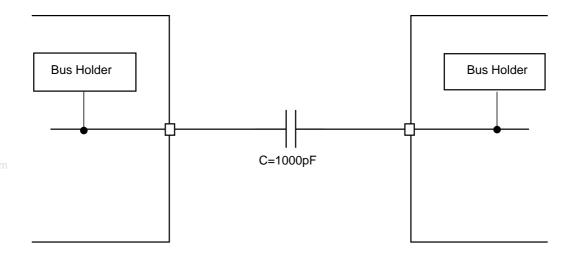

The SIR72900F00A has a bus holder circuit on the interface pin for the Link layer controller IC. This enables AC connection as shown in Figure 7.14.

For AC connection (with a single capacitor), also connect the DIRECT pin to VDD.

Figure 7.14 SIR72900F00A -to-Link chip connection diagram (AC connection)

As shown in Figure 7.15, use a 1000-pF coupling capacitor for AC connection.

\* The SIR72900F00A is not in support of the IEEE1394 specification Annex J isolation barrier.

Figure 7.15 AC coupling connection

### 7.4.2 LPS (Link Power Status)

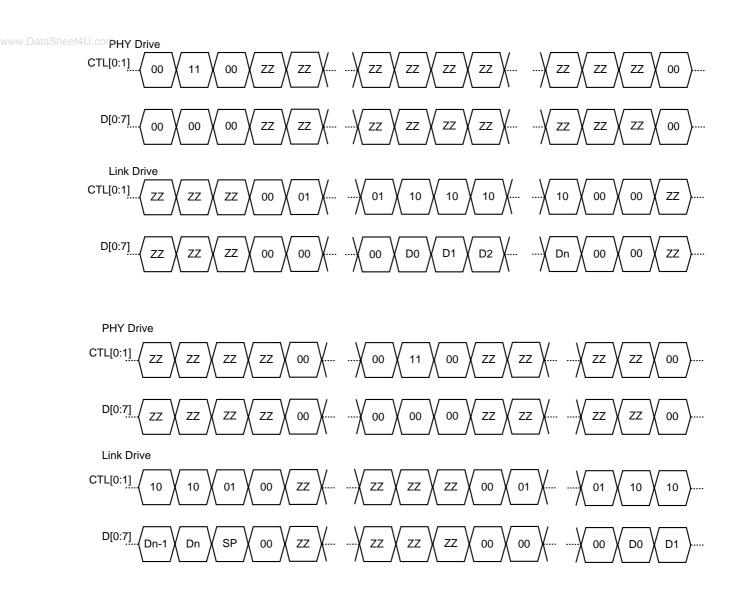

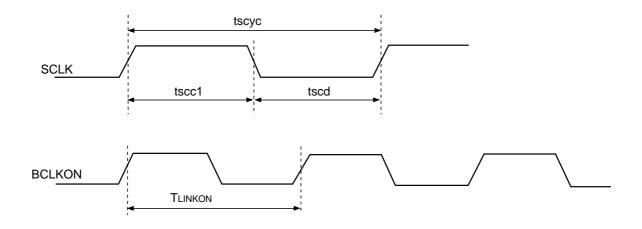

By inputting to the LPS pin, the S1R72900F00A is set to enable/disable the PHY/LINK interface. If the S1R72900F00A detects LPS = LOW during a TLPS RESET period, the PHY/LINK interface is set to the disable state to output LOW to the SCLK, CTL0-1 and D0-7. (While LOW is set when the PHY/LINK interface is DC connection, "Hi-Z" is set when it is AC connection.)

However, if Page select7 Register 70 bit 6 was set, SCLK is not terminated and continues to output a clock signal even when the PHY/LINK interface is set to disable.

If the PHY/LINK interface was reset, all bus requests and register read requests are cancelled. Also, the S1R72900F00A recognizes that the packet transfer was terminated and operates, if the Link layer controller IC reset the PHY/LINK interface during packet transfer.

When the PHY/LINK interface is set to disable period, the status output is not operated, therefore, this information is not output even after the PHY/LINK interface is set to enabled.

When the S1R72900F00A detects LPS = HIGH after the PHY/LINK interface was reset and set to disable, SCLK output starts after the disable state.

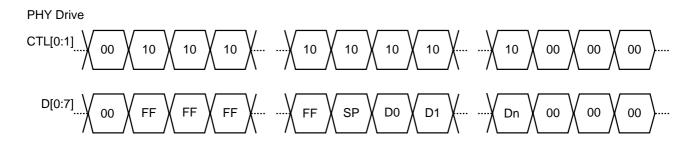

If the PHY/LINK interface uses the DC connection, the S1R72900F00A outputs LOW to the 7 SCLK cycles CTL, D after detecting LPS, and outputs Receive (CTL[0:1] = 10b, D[0.7]=ffh) for Data Prefix to the PHY/LINK interface at the 8th SCLK, returning to normal operation.

For AC connection, the S1R72900F00A outputs LOW to the 1SCLK cycle period CTL,D within 1 to 6 SCLK cycles after detecting LPS, returning to normal operation. Other periods will become "Hi-Z".

In this case, it continues to output Receive for Data Prefix to the PHY/LINK interface until packet receiving is terminated if its node is receiving a packet.

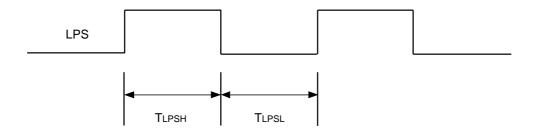

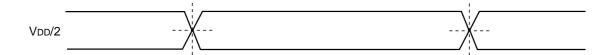

Figure 7.16 LPS waveforms in AC connection

Table 7.5 LPS timing

| Symbol                                                                                                     | Item                                                                                        |    | Max. | Unit |

|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----|------|------|

| TLPSL                                                                                                      | LPS low time (pulses)                                                                       |    | 1.0  | μm   |

| TLPSH                                                                                                      | LPS high time (pulses)                                                                      |    | 1.0  | μm   |

| TLPS_RESET                                                                                                 | The time required until the SIR72900F00A detects LPS = 0 and resets the PHY/LINK interface. |    | 2.75 | μm   |

| TLPS_DISABLE The time required until the SIR72900F00A detects LPS = 0 and disables the PHY/LINK interface. |                                                                                             | 25 | 30   | μm   |

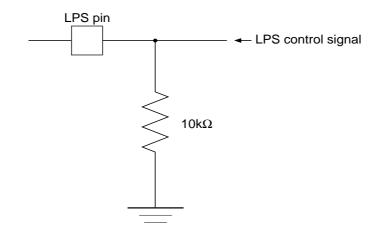

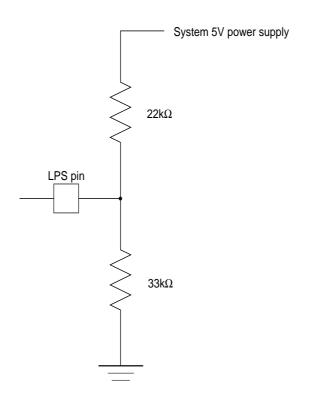

The S1R72900F00A issues short bus reset (SBR) against other nodes connected when detecting LPS = "1". This function makes cancellation possible by clearing Page select7Register 70 bit 7. A typical external circuit for the LPS pin is shown in Figures 7.17, 18 and 19.

Figure 7.17 A typical direct connection and LPS external circuit 1 (with external signal control)

Figure 7.18 A typical direct connection and LPS external circuit 2 (without external signal control)

\* The LPS control signal shown Figure 7.17 is required to be 0.8 V lower when the power supply on the upper layer compared to the Link layer is set to OFF. For example, if the LPS control signal is output from the Link layer controller IC, LPS output is required to be GND output when the Link layer controller IC power supply is set to OFF. (For VDD output, LPS = "0" may not be recognized because the VDD potential may not become 0.8V lower.)

Also, even when the system's power supply is connected to the LPS pin as shown in Figure 7.18, it is required to be 0.8V lower when the power supply on the upper layer compared to the Link layer is set to OFF. When using a 3.3V power supply for the Link layer controller IC, pay attention to the LPS connection because the VDD potential may not become 0.8V lower when the power supply is set to OFF.

$\begin{array}{c|c} & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & &$

Figure 7.19 A typical AC connection and LPS external circuit

### 7.4.3 LinkOn

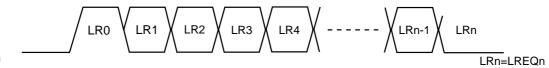

The SIR72900F00A recognizes that the Link layer controller IC is inactive when it recognizes that LPS is deasserted or the Link\_Active bit of the PHY register is '0.'