# **RTS5411E**

# USB 3.1 Super-Speed HUB Controller DATASHEET

Doc Rev. 0.93 3. Sep. 2018

#### Realtek Semiconductor Corp.

No. 2, Innovation Road II, Hsinchu Science Park, Hsinchu 300, Taiwan Tel.: +886-3-578-0211. Fax: +886-3-577-6047

www.realtek.com.tw

#### **TRADEMARKS**

Realtek is a trademark of Realtek Semiconductor Corporation. All other names mentioned in this document are trademarks/registered trademarks of their respective owners.

Realtek provides this document "as is", without warranty of any kind, neither expressed nor implied, including, but not limited to the particular purpose. Realtek may make improvements and/or changes in this manual or in the product(s) and/or the program(s) described in this manual at any time. This document could include technical inaccuracies or typographical errors.

#### **Revision History**

| Revision | Description                            | Page | Date       |

|----------|----------------------------------------|------|------------|

| 0.90     | First release                          |      | 2017/12/29 |

| 0.91     | Update 5.5 power consumption           |      | 2018/06/21 |

| 0.92     | Update 5.2 table                       |      | 2018/07/20 |

| 0.93     | Modify 5.1 Absolute Maximum Ratings    |      | 2018/09/03 |

|          | Modify 8 QFN76 Package Dimensions note |      |            |

|          | Modify 4.2 OCP pin description         |      |            |

|          | Modify 6.3 SMBUS Transfer Protocol     |      |            |

|          |                                        |      |            |

|          |                                        |      |            |

|          |                                        |      |            |

|          |                                        |      |            |

|          |                                        |      |            |

|          |                                        |      |            |

|          |                                        |      |            |

|          |                                        |      |            |

# **Table of Contents**

| 6  |

|----|

|    |

| 8  |

| 9  |

| 9  |

| 10 |

| 13 |

| 14 |

| 14 |

| 14 |

| 16 |

| 16 |

| 16 |

| 16 |

| 16 |

| 16 |

| 17 |

| 20 |

| 22 |

| 22 |

| 22 |

| 23 |

| 24 |

| 24 |

| 24 |

| 24 |

| 25 |

| 25 |

| 25 |

| 26 |

| 26 |

| 27 |

| 27 |

| 27 |

|    |

|    | 7.2.1 Supported Mode and Speed         | 2′ |

|----|----------------------------------------|----|

|    | 7.2.2 Transfer Protocol Implementation | 27 |

|    | 7.2.3 Stretching the SCK               | 2  |

|    | 7.2.4 Slave Response Timeout           | 28 |

|    | 7.3 I2C Timing                         | 28 |

| 8. | QFN-76 Package Dimensions              | 3  |

| 9. | Ordering Information                   | 3. |

|    |                                        |    |

## 1. General Description

RTS5411E is an advanced USB3.1 4-port HUB controller, which integrates USB3.1 and USB2.0 Transceivers, MCU, SIE, regulator and charger circuits into a single chip. That could dramatically reduce the system BOM cost. With high compatibility, RTS5411E is fully backward compatible to USB2.0 and USB1.1 specification which can be operated in Super-Speed, High-Speed, Full-Speed and Low-Speed.

RTS5411E provides the battery charging function for each downstream port. Besides complies with USB Battery Charging specification rev1.2, RTS5411E also provides charging function for various portable devices. Not only downstream ports can be used as charger, RTS5411E's upstream port also supports two special functions regarding the BC1.2 specification. The first one charger function of RTS5411E's upstream port is called "ACA-dock" mode. When a device which complies with ACA-dock of the BC1.2 specification is put into an ACA-Dock, it would act as a host to various USB peripherals, such as a hub, keyboard, mouse, printer, etc. However, while in ACA-dock, the device should also be able to charge at the same time. The second charger function of the RTS5411E's upstream port is called "charger detection" function. RTS5411E can recognize the BC1.2 charger mode which attached to the upstream port, including CDP, DCP and SDP. RTS5411E supports an auto detection-switch mechanism to charge portable device in suitable mode.

RTS5411E can update its firmware with an external SPI flash through flexible ISP channel. With the ISP function, it can configure lots of features and settings by the external SPI flash. The ISP function is easy to complete with just one USB cable and RTS5411E's download tool.

The features and settings of RTS5411E can also be configured by the SMBUS interface or internal eFuse.

RTS5411E has various interfaces to communicate with other components, such as GPIO, I2C, SMBUS. It's flexible for extending varieties of applications by using these interfaces.

Moreover, RTS5411E supports a special power saving function named delink mode.

It can save more power for the system when there is no device connected to the hub even though the upstream port of the RTS5411E is attached to the downstream port of the behind host or hub.

#### 2. Features

- Compliant with Universal Serial Bus 3.1 Specification Revision 1.0

- 4 downstream ports for super-speed, high-speed, full-speed and low-speed traffic.

- Backward compatible with USB specification Revision 2.0, 1.1 and 1.0.

- MTT(Multiple Transaction Translator)

- One TT for each downstream port.

- Better data throughput when multiple downstream ports act on FS concurrently.

- Support SMBUS to customize configurations

- SMBUS address is configurable by external SPI Flash or internal eFuse.

- Support I2C to configure other chips on the same platform.

- Compliant with USB Battery Charging Specification Revision 1.2 and other portable devices

- DCP Mode of BC 1.2.

- CDP Mode of BC 1.2.

- ACA-Dock functions of BC 1.2.

- Charger detection functions for upstream port's charger which complies with BC1.2.

- D+/D- Divider Modes 2.0V/2.7V, 2.7/2.0V and 2.7/2.7V.

- D+/D- 1.2V Mode.

- The Up Stream Port of the RTS5411E can detect the DSP it is connected to is a SDP, CDP, or DCP.

When the RTS5411E is connected to a charging port, it is allowed to draw more current from the DSP.

- Support Gang mode and Individual mode for downstream port.

- Support USB2.0 LPM-L1 function

- Support USB3.1 U1/U2/U3 power saving mode

- Integrated Fast 8051 microprocessor

- Support Pending HP timer, PM timers, U1/U2/LFPS exit latency which are defined in the USB3.2 spec.

- Support 12MHz Crystal clock

- Integrated 3.3V output LDO inside, the input range supports from 4.5V to 5.5V

- Integrated 1.2V output switching regulator, the input range supports from 3.1V to 5.5V.

- Support LED control function of indicating Downstream Ports transfer activity and over-current condition.

- 76-pin QFN (9 x9 mm) package

- Support Efuse to configure functions or configurations such as non-removable port, gang mode, etc.

- Support the "Delink" function for extreme power saving

- If there is no any device attached to the RTS5411E's downstream ports, the RTS5411E will disconnect itself from the downstream port of the host or another hub controller for further power saving.

The connection of the upstream port will be established automatically once there is any device attached to its downstream ports.

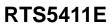

## 3. Block Diagram

#### 4. Pin Information

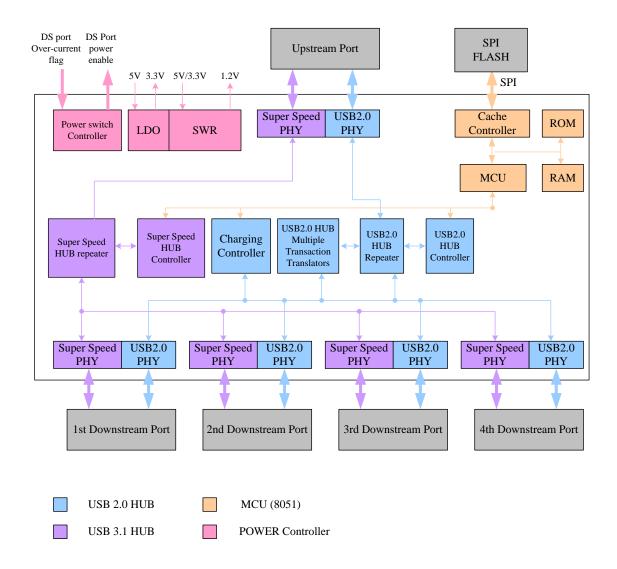

#### 4.1 Pin Assignment

The version number is shown in the location marked 'VV' and G means Green Package

### **4.2 Pin Descriptions**

| Pin Name                                  | Pin No.                    | I/O<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------|----------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                           | 1                          | Po          | wer supply                                                                                                                                                                                                                                                                                                                                                                                               |

| DV33                                      | 4,22,48,73                 | Power       | 3.3V power supply for digital circuits                                                                                                                                                                                                                                                                                                                                                                   |

| DV12                                      | 3,49,50                    | Power       | 1.2V power supply for digital circuits                                                                                                                                                                                                                                                                                                                                                                   |

| AV12                                      | 7,13,19,25,31,<br>58,64,70 | Power       | 1.2V power supply for analog circuits                                                                                                                                                                                                                                                                                                                                                                    |

| LDO_V5_IN                                 | 54                         | Power       | 5V to 3.3V LDO input.<br>Short this pin to DV33, when on-chip LDO is not used.                                                                                                                                                                                                                                                                                                                           |

| V33_OUT                                   | 55                         | Power       | 3.3V output (from internal 5V to 3.3V Low Dropout Regulator) Short this pin to DV33, when on-chip LDO is not used.                                                                                                                                                                                                                                                                                       |

| SWR_V5_IN                                 | 53                         | Power       | 5V to 1.2V SWR input Connect this pin to LDO_V5_IN if internal switching regulator isn't used.                                                                                                                                                                                                                                                                                                           |

| SWR_GND                                   | 51                         | GND         | Reference GND for 1.2V SWR                                                                                                                                                                                                                                                                                                                                                                               |

| SWR_OUT                                   | 52                         | Power       | 5V to 1.2V SWR output Left this pin floating if internal switching regulator isn't used.                                                                                                                                                                                                                                                                                                                 |

| GND                                       | 61                         | GND         | Reference ground                                                                                                                                                                                                                                                                                                                                                                                         |

| E-PAD                                     | -                          | GND         | The bottom of the package has a thermal pad. The pad shall be connected to the reference ground                                                                                                                                                                                                                                                                                                          |

|                                           |                            | Anal        | log Interface                                                                                                                                                                                                                                                                                                                                                                                            |

| RREF                                      | 1                          | I           | Connect an external resistor (6.2K ±1%) to the Reference GND                                                                                                                                                                                                                                                                                                                                             |

|                                           |                            | Sys         | stem Clock                                                                                                                                                                                                                                                                                                                                                                                               |

| XTLI                                      | 74                         | I           | 12Mhz Crystal input.                                                                                                                                                                                                                                                                                                                                                                                     |

| XTLO                                      | 75                         | 0           | 12Mhz Crystal output.                                                                                                                                                                                                                                                                                                                                                                                    |

|                                           | 1                          | LED         | Control Pins                                                                                                                                                                                                                                                                                                                                                                                             |

| GPIO0/SMBCL,<br>GPIO2/SCL,<br>GPIO4,GPIO6 | 32,34,36,38                | I/O         | General Purpose I/O. Now used for LED application to indicate Downstream Ports transmit and receive activity. The LEDs will on when there is a device connected to the corresponding port and not in suspend.  These pins have weak internal pull up resistances. Left these pins floating when unused.  The GPIO0 can be configured as a SMBus clock pin The GPIO2 can be configured as a I2C clock pin |

| GPIO1/SMBDA,<br>GPIO3/SDA,<br>GPIO5,GPIO7 | 33,35,37,39                | I/O         | General Purpose I/O. Now used for LED application to indicate Downstream Ports over-current condition. The LEDs will on when over-current condition is detected. These pins have weak internal pull up resistances. Left these pins floating when unused.  The GPIO1 can be configured as a SMBus data pin The GPIO3 can be configured as a I2C data pin                                                 |

10

## Pin Descriptions (continued)

| Pin Name                                        | Pin No.     | I/O<br>Type | Description                                                                                                                                                                                                                                                                             |

|-------------------------------------------------|-------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                 | ·           | USB Por     | t Control Pins                                                                                                                                                                                                                                                                          |

| DSP1_PWR,<br>DSP2_PWR,<br>DSP3_PWR,<br>DSP4_PWR | 40,41,42,43 | 0           | External power switch enable pin for corresponding downstream port. Active low <sup>(1)</sup> .  Left these pins floating when unused.  0: Power supply for VBUS is on.  1: Power supply for VBUS is off.                                                                               |

| OCP1,OCP2,<br>OCP3,OCP4                         | 67,10,16,28 | ı           | Over Current Protection flag for corresponding downstream port .Active low <sup>(1)</sup> .  The external pull-up resistors shall be connected to these pins.  0: Over-current condition is detected.  1: Non over-current condition is detected.                                       |

| BPWR_DET                                        | 2           | I           | Upstream VBUS power detection pin. Active High. 0: Upstream VBUS power is absent. 1: Upstream VBUS power exists.                                                                                                                                                                        |

| SPWR_DET                                        | 76          | I           | Self Power Detection pin. Active High.  0: Bus-power setting  1: Self-power setting                                                                                                                                                                                                     |

|                                                 | ·           | SPI         | Interface                                                                                                                                                                                                                                                                               |

| SCK                                             | 44          | I/O         | This is I/O bi-direction. Now used as clock output for Serial Flash memory                                                                                                                                                                                                              |

| SCS                                             | 45          | I/O         | This is I/O bi-direction. Now used as output chip select for Serial Flash memory Upon power on reset this pin is also used for pin strap option to perform code execution from internal ROM or external SPI ROM. 0:Execute codes from internal ROM . 1:Execute codes from Serial Flash. |

| MISO                                            | 46          | I/O         | This is I/O bi-direction. Now used as data input from Serial Flash memory                                                                                                                                                                                                               |

| MOSI                                            | 47          | I/O         | This is I/O bi-direction. Now used as data output to Serial Flash memory                                                                                                                                                                                                                |

<sup>(1)</sup> Active low by default. It can be configured to be active high by firmware through executing external codes.

## Pin Descriptions (continued)

| Pin Name                                                | Pin No.     | I/O<br>Type | Description                               |

|---------------------------------------------------------|-------------|-------------|-------------------------------------------|

|                                                         |             | USB3        | .1 Interface                              |

| USP_SSTX+                                               | 60          | 0           | USB3.1 SuperSpeed TX+ of Upstream Port    |

| DSP1_SSTX+,<br>DSP2_SSTX+,<br>DSP3_SSTX+,<br>DSP4_SSTX+ | 65,8,14,26  | 0           | USB3.1 SuperSpeed TX+ of Downstream Ports |

| USP_SSTX-                                               | 59          | 0           | USB3.1 SuperSpeed TX- of Upstream Port    |

| DSP1_SSTX-,<br>DSP2_SSTX-,<br>DSP3_SSTX-,<br>DSP4_SSTX- | 66,9,15,27  | 0           | USB3.1 SuperSpeed TX- of Downstream Ports |

| USP_SSRX+                                               | 63          | 1           | USB3.1 SuperSpeed RX+ of Upstream Port    |

| DSP1_SSRX+,<br>DSP2_SSRX+,<br>DSP3_SSRX+,<br>DSP4_SSRX+ | 68,11,17,29 | I           | USB3.1 SuperSpeed RX+ of Downstream Ports |

| USP_SSRX-                                               | 62          | I           | USB3.1 SuperSpeed RX- of Upstream Port    |

| DSP1_SSRX-,<br>DSP2_SSRX-,<br>DSP3_SSRX-,<br>DSP4_SSRX- | 69,12,18,30 | I           | USB3.1 SuperSpeed RX- of Downstream Ports |

|                                                         |             | USB2        | .0 Interface                              |

| USP_DP                                                  | 56          | I/O         | USB2.0 D+ signal of Upstream Port         |

| DSP1_DP,<br>DSP2_DP,<br>DSP3_DP,<br>DSP4_DP             | 71,5,20,23  | I/O         | USB2.0 D+ signal of Downstream Ports      |

| USP_DM                                                  | 57          | I/O         | USB2.0 D- signal of Upstream Port         |

| DSP1_DM,<br>DSP2_DM,<br>DSP3_DM,<br>DSP4_DM             | 72,6,21,24  | I/O         | USB2.0 D- signal of Downstream Ports      |

#### 4.3 Buffer list

#### 5V input buffer with internal 10K pull-up resistor

OCP[4:1] (2)

#### Open drain output buffer

DSP\_PWR [4:1] (1)

#### 3.3V bi-directional buffer

SCK.SCS, MISO, MOSI

#### 3.3V bi-directional buffer with internal 200K pull-up resistor

GPIO[7:0]

#### 5V input buffer

BPWR\_DET, SPWR\_DET

#### 3.3V clock interface

XTLI, XTLO

#### **USB2.0** interface

DSP\_DP [4:1], USP\_DP, DSP\_DM [4:1], USP\_DM

#### **USB3.1** interface

DSP\_SSTX+[4:1], DSP\_SSTX-[4:1], DSP\_SSRX+[4:1], DSP\_SSRX-[4:1],

USP\_SSTX+,USP\_SSTX-,USP\_SSRX+, USP\_SSRX-

#### **LDO** interface

LDO\_V5\_IN, V33\_OUT

#### **Switching Regulator interface**

SWR\_V5\_IN, SWR\_OUT

- (1) Use open drain output buffer by default when configured as active low. If configured as active high by F/W, it will use the 3.3V output buffer instead.

- (2) The pull-up resistors are only valid when the 'power switch' mode is selected.

#### 5. Electrical Characteristics

#### **5.1 Absolute Maximum Ratings**

| Parameter                             | Symbol               | Condition                      | Rating                         | Units |

|---------------------------------------|----------------------|--------------------------------|--------------------------------|-------|

| Power supply voltage                  | V <sub>5IN</sub>     |                                | 5.5                            | V     |

|                                       | $V_{AV12}, V_{DV12}$ |                                | -0.2 to 1.4                    | V     |

|                                       | V <sub>DV33</sub>    |                                | -0.5 to 4.1                    | V     |

| Input voltage <sup>(1)</sup>          | Vı                   | 3V buffer                      | -0.5 to V <sub>DV33</sub> +0.5 | V     |

|                                       |                      | 5V buffer<br>Open drain buffer | -0.5 to +6                     | V     |

| Output voltage <sup>(2)</sup>         | Vo                   |                                | -0.5 to V <sub>DV33</sub> +0.5 | V     |

| Output current (3)                    | I <sub>O</sub>       | 4mA Type (4)                   | 6                              | mA    |

|                                       |                      | 8mA Type (4)                   | 12                             | mA    |

| Storage temperature                   | T <sub>stg</sub>     |                                | -20 to +80                     | °C    |

| Latch up Current                      |                      |                                | ±400                           | mA    |

| Electrostatic Discharge Voltage (HBM) |                      |                                | ±5                             | KV    |

| Electrostatic Discharge Voltage (MM)  |                      |                                | ±150                           | V     |

| Electrostatic Discharge Voltage (CDM) |                      |                                | ±500                           | V     |

- (1) This parameter indicates voltage exceeding which damage or reduced reliability will occur when power is applied to an input pin.

- (2) This Parameter indicates voltage exceeding which damage or reduced reliability will occur when power is applied to an output pin.

- (3) This parameter indicates absolute tolerance values for DC current to prevent damage or reduced reliability when current flows out of or into output pin.

- (4) The output driving strength of all output is 4mA by default, which can be configured as 8mA by firmware through executing external codes.

#### **5.2 Recommended Operating Ranges**

| Parameter                                                                   | Symbol               | Condition            | Min. | Тур. | Max.   | Units |

|-----------------------------------------------------------------------------|----------------------|----------------------|------|------|--------|-------|

| Power supply voltage                                                        | V <sub>5IN</sub>     |                      | 4.45 | 5    | 5.25   | V     |

|                                                                             | V V                  | Active               | 1.08 | 1.2  | 1.32   | V     |

|                                                                             | $V_{AV12}, V_{DV12}$ | Disconnect / Suspend | 1.0  | 1.08 | 1.32   | V     |

|                                                                             | V <sub>DV33</sub>    |                      | 2.97 | 3.3  | 3.63   | V     |

| Available current of 3.3V power supply for external circuits <sup>(1)</sup> |                      | V <sub>5IN</sub> =5V |      |      | 150    | mA    |

| Operating ambient temperature                                               | T <sub>A</sub>       |                      | 0    |      | +70    | °C    |

| Absolute maximum junction temperature                                       | T <sub>J</sub>       |                      | 0    |      | +125   | °C    |

| Surface Temperature of body                                                 | T <sub>C</sub>       | PCB Layer:4L         | 0    |      | +118.2 | °C    |

|                                                                             |                      | PCB Layer:2L         | 0    |      | +120.7 | °C    |

(1) Load current of external circuits shouldn't exceed the max value when using on-chip LDO. It is recommended that the external circuits are limited to SPI Flash and LEDs

#### 5.3 DC Characteristics

#### 5.3.1 DC Characteristics except USB differential signals

The following specifications apply when power supply voltages are within the recommended operating ranges in section 6.2.

| Parameter                                       | Symbol          | Conditions                                             | Min.                 | Max.                 | Units |

|-------------------------------------------------|-----------------|--------------------------------------------------------|----------------------|----------------------|-------|

| Input leakage current <sup>(1)</sup>            | I <sub>I</sub>  | 3V buffer,<br>V <sub>I</sub> =V <sub>DV33</sub> or GND | -0.5                 | +0.5                 | μA    |

|                                                 |                 | 5V buffer,<br>V <sub>I</sub> =V <sub>5IN</sub> or GND  | -30                  | +30                  | μA    |

| Input High Voltage                              | V <sub>IH</sub> | 3V buffer,                                             | 2                    |                      | V     |

|                                                 |                 | 5V buffer                                              | 3.16                 |                      | V     |

| Input Low Voltage                               | V <sub>IL</sub> | 3V buffer                                              |                      | 0.8                  | V     |

|                                                 |                 | 5V buffer                                              |                      | 0.8                  | V     |

| Output High Voltage                             | V <sub>OH</sub> |                                                        | 0.9V <sub>DV33</sub> |                      | V     |

| Output Low Voltage                              | V <sub>OL</sub> |                                                        |                      | 0.1V <sub>DV33</sub> | V     |

| TRI-STATE Output Leakage Current <sup>(2)</sup> | I <sub>OZ</sub> | 3.3V buffer,<br>Vo= V <sub>DV33</sub> or GND           | -0.5                 | +0.5                 | μA    |

| Input pin Capacitance                           | C <sub>in</sub> |                                                        |                      | 10                   | рF    |

- (1) This parameter indicates the current that flows through the input pin when power supply voltage is supplied to it.

- (2) This parameter indicates the current that flows through the output pin in tri-stated when the power supply voltage is applied to it.

#### 5.3.2 USB 2.0 Interface DC Characteristics

RTS5411E conforms to DC characteristics of Universal Serial Bus 2.0 Specification. Refer to the specification for more information.

#### 5.3.3 USB 3.1 Interface DC Characteristics

RTS5411E conforms to DC characteristics of Universal Serial Bus 3.1 Specification. Refer to the specification for more information.

#### 5.4 AC Characteristics

#### 5.4.1 System Clock

The following specifications apply when power supply voltages and operating temperature are within the recommended operating ranges in section 5.2.

| Parameter       | Symbol           | Condition   | Min.    | Тур. | Max.   | Units |

|-----------------|------------------|-------------|---------|------|--------|-------|

| Clock frequency | F <sub>CLK</sub> | Crystal (1) | -100ppm | 12   | 100ppm | MHz   |

(1) Crystal used shall conform to the frequency ratings in the table over the temperature from 0°C to +70°C.

#### 5.5 Power Consumption

The following consumption value applies upon the typical condition without on-chip LDO and Switch Regulator operating. The VDD33 and VDD12 are powered externally.

$T_A$ = 25°C, VDD33( $V_{DV33}$ )= 3.3 V, VDD12( $V_{AV12}$ , $V_{DV12}$ )= 1.2 V.

| Device<br>Connection   | Condition                                                                                                                                                                   |                                             | Typical Supply Current(mA)                  |                |  |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|---------------------------------------------|----------------|--|

| Connection             |                                                                                                                                                                             | VDD12                                       | VDD33                                       | Power(mW)      |  |

| No Upstream connection | Hub is not connected to host controller.                                                                                                                                    | 0.41                                        | 2 <sup>(1)</sup><br>3.72 <sup>(2)</sup>     | 6.07<br>12.28  |  |

| Suspend                | Hub is connected to host controller both with SuperSpeed and High-Speed. SuperSpeed hub goes into U3 state and USB2.0 hub goes into L2 state                                | 0.63                                        | 4.18                                        | 14.5           |  |

| 4 LS devices           | Hub is connected to host controller both with SuperSpeed and High-Speed. Low-Speed data transfer on the four ports.                                                         | 12.7                                        | 5.7                                         | 34.3           |  |

| 4 HS devices           | Hub is connected to host controller both with SuperSpeed and High-Speed. High-Speed data transfer on the four ports.                                                        | 102                                         | 5.1                                         | 139.3          |  |

| 4 SS devices           | Hub is connected to host controller both with SuperSpeed and High-Speed. Super-Speed data transfer on the four ports. (3)                                                   | 120.5 <sup>(5)</sup><br>415 <sup>(6)</sup>  | 33.4 <sup>(5)</sup><br>40.7 <sup>(6)</sup>  | 254.8<br>632.3 |  |

| 2 SS devices           | Hub is connected to host controller both with SuperSpeed and High-Speed. Super-Speed data transfer on the two ports. (3)                                                    | 81.8 <sup>(5)</sup><br>263.4 <sup>(6)</sup> | 19.6 <sup>(5)</sup><br>23.7 <sup>(6)</sup>  | 162.8<br>394.3 |  |

| 1 SS devices           | Hub is connected to host controller both with SuperSpeed and High-Speed. Super-Speed data transfer on one port. (3)                                                         | 60.7 <sup>(5)</sup><br>174.3 <sup>(6)</sup> | 12.9 <sup>(5)</sup><br>14.68 <sup>(6)</sup> | 115.5<br>257.6 |  |

| 4 SS/HS<br>devices     | Hub is connected to host controller both with SuperSpeed and High-Speed. Four SuperSpeed hubs are connected on all ports under SuperSpeed and High-Speed data transfer. (3) | 247.5 <sup>(5)</sup><br>526 <sup>(6)</sup>  | 33.71 <sup>(5)</sup><br>40 <sup>(6)</sup>   | 408.2<br>763.2 |  |

| 2 SS/HS<br>devices     | Hub is connected to host controller both with SuperSpeed and High-Speed. Two SuperSpeed hubs are connected on all ports under SuperSpeed and High-Speed data transfer. (3)  | 163 <sup>(5)</sup><br>326 <sup>(6)</sup>    | 19.9 <sup>(5)</sup><br>22.9 <sup>(6)</sup>  | 261.3<br>308.3 |  |

- (1) Charging mode is disabled

- (2) Charging mode is enabled

- (3) CDP function is disabled. The VDD33 power consumption will also decrease by 1mA in SS devices connection when CDP function is disabled

- (4) CDP function is enabled.

- (5) The SS devices under test support U1/U2 function. When the SS devices are Idle with little data transfer. The SuperSpeed hub will keep in U1/U2 power saving status most of the time.

- (6) The SS devices under test do not support U1/U2 function. So this is the worst case for SS power consumption

The following consumption value applies upon the typical condition with on-chip LDO and Switch Regulator operating. Only VDD5 needs to be provided in this 5V mode.

TA= 25°C, VDD5( $V_{5IN}$ ) = 5 V.

| Device<br>Connection   | Connection                                                                                                                                                                  |                                              | Typical<br>Power(mW)                         |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------|

| No Upstream connection | Hub is not connected to host controller.                                                                                                                                    | 1.734 <sup>(1)</sup><br>3.784 <sup>(2)</sup> | 8.67<br>18.92                                |

| Suspend                | Hub is connected to host controller both with SuperSpeed and High-Speed. SuperSpeed hub goes into U3 state and USB2.0 hub goes into L2 state                                | 4.214                                        | 21.07                                        |

| 4 LS devices           | Hub is connected to host controller both with SuperSpeed and High-Speed. Low-Speed data transfer on the four ports.                                                         | 18.51                                        | 92.55                                        |

| 4 HS devices           | Hub is connected to host controller both with SuperSpeed and High-Speed. High-Speed data transfer on the four ports.                                                        | 39.12                                        | 195.6                                        |

| 4 SS devices           | Hub is connected to host controller both with SuperSpeed and High-Speed. Super-Speed data transfer on the four ports. (1)                                                   | 73.6 <sup>(5)</sup><br>216.6 <sup>(6)</sup>  | 368<br>1083                                  |

| 2 SS devices           | Hub is connected to host controller both with SuperSpeed and High-Speed. Super-Speed data transfer on the two ports. (1)                                                    | 46.2 <sup>(5)</sup><br>125.7 <sup>(6)</sup>  | 231<br>628.5                                 |

| 1 SS devices           | Hub is connected to host controller both with SuperSpeed and High-Speed. Super-Speed data transfer on one port. (1)                                                         | 33.1 <sup>(5)</sup><br>83.5 <sup>(6)</sup>   | 165.5<br>417.5                               |

| 4 SS/HS<br>devices     | Hub is connected to host controller both with SuperSpeed and High-Speed. Four SuperSpeed hubs are connected on all ports under SuperSpeed and High-Speed data transfer. (1) | 118.4 <sup>(5)</sup><br>256.2 <sup>(6)</sup> | 592<br>1281                                  |

| 2 SS/HS<br>devices     | Hub is connected to host controller both with SuperSpeed and High-Speed. Two SuperSpeed hubs are connected on all ports under SuperSpeed and High-Speed data transfer. (3)  | 73.5 <sup>(5)</sup><br>135.9 <sup>(6)</sup>  | 367.5 <sup>(5)</sup><br>679.5 <sup>(6)</sup> |

- (1) Charging mode is disabled

- (2) Charging mode is enabled

- (3) CDP function is disabled. The VDD33 power consumption will also decrease by 1mA in SS devices connection when CDP function is disabled

- (4) CDP function is enabled.

- (5) The SS devices under test support U1/U2 function. When the SS devices are Idle with little data transfer. The SuperSpeed hub will keep in U1/U2 power saving status most of the time.

- (6) The SS devices under test do not support U1/U2 function. So this is the worst case for SS power consumption

The following consumption value applies upon the typical condition with on-chip Switch Regulator operating. Only VDD33 needs to be provided in this 3.3V mode.

TA= 25°C, VDD33( $V_{DV33}$ ) = 3.3 V.

| Device<br>Connection   | Condition                                                                                                                                                                   | Typical<br>Supply<br>Current(mA)<br>VDD33    | Typical<br>Power(mW)                         |  |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------|--|

| No Upstream connection | Hub is not connected to host controller.                                                                                                                                    | 1.722 <sup>(1)</sup><br>3.772 <sup>(2)</sup> | 5.68<br>12.45                                |  |

| Suspend                | Hub is connected to host controller both with SuperSpeed and High-Speed. SuperSpeed hub goes into U3 state and USB2.0 hub goes into L2 state                                | 4.2                                          | 13.86                                        |  |

| 4 LS devices           | Hub is connected to host controller both with SuperSpeed and High-Speed. Low-Speed data transfer on the four ports.                                                         | 20.76                                        | 68.5                                         |  |

| 4 HS devices           | Hub is connected to host controller both with SuperSpeed and High-Speed. High-Speed data transfer on the four ports.                                                        | 50.12                                        | 165.4                                        |  |

| 4 SS devices           | Hub is connected to host controller both with SuperSpeed and High-Speed. Super-Speed data transfer on the four ports. (1)                                                   | 86.8 <sup>(5)</sup><br>304.6 <sup>(6)</sup>  | 286.4<br>1005.2                              |  |

| 2 SS devices           | Hub is connected to host controller both with SuperSpeed and High-Speed. Super-Speed data transfer on the two ports. (1)                                                    | 54.6 <sup>(5)</sup><br>163.7 <sup>(6)</sup>  | 180.2<br>540.2                               |  |

| 1 SS devices           | Hub is connected to host controller both with SuperSpeed and High-Speed. Super-Speed data transfer on one port. (1)                                                         | 38.7 <sup>(5)</sup><br>108.6 <sup>(6)</sup>  | 127.1<br>358.4                               |  |

| 4 SS/HS<br>devices     | Hub is connected to host controller both with SuperSpeed and High-Speed. Four SuperSpeed hubs are connected on all ports under SuperSpeed and High-Speed data transfer. (1) | 153.7 <sup>(5)</sup><br>360.2 <sup>(6)</sup> | 507.2<br>1188.7                              |  |

| 2 SS/HS<br>devices     | Hub is connected to host controller both with SuperSpeed and High-Speed. Two SuperSpeed hubs are connected on all ports under SuperSpeed and High-Speed data transfer. (3)  | 91.9 <sup>(5)</sup><br>180.9 <sup>(6)</sup>  | 302.3 <sup>(5)</sup><br>596.9 <sup>(6)</sup> |  |

- (1) Charging mode is disabled

- (2) Charging mode is enabled

- (3) CDP function is disabled. The VDD33 power consumption will also decrease by 1mA in SS devices connection when CDP function is disabled

- (4) CDP function is enabled.

- (5) The SS devices under test support U1/U2 function. When the SS devices are Idle with little data transfer. The SuperSpeed hub will keep in U1/U2 power saving status most of the time.

- (6) The SS devices under test do not support U1/U2 function. So this is the worst case for SS power consumption

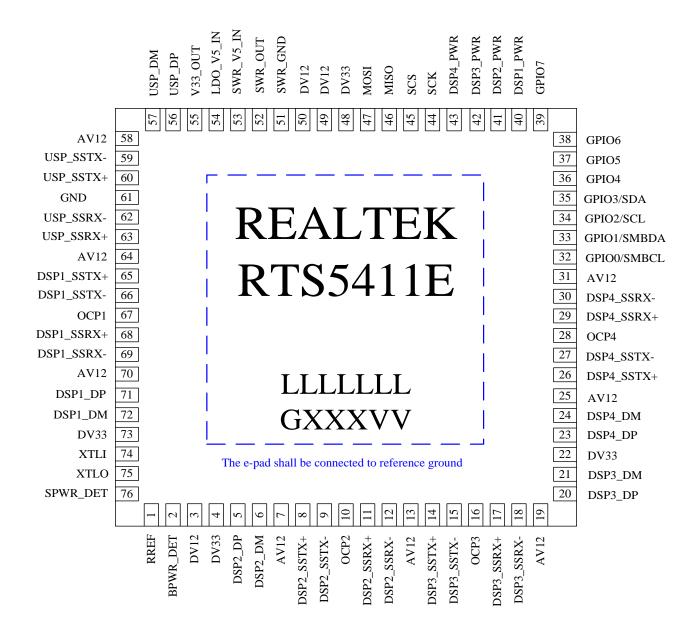

#### 5.6 Power On/Off Sequence

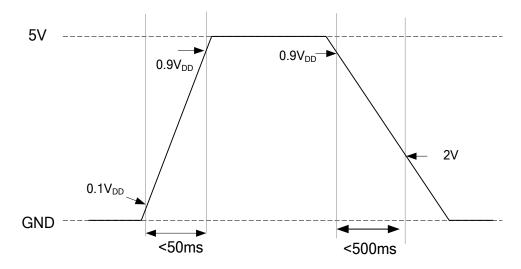

When the on-chip LDO and switch regulator are not used, both 1.2V and 3.3V power need to be provided externally. The power on/off sequence between 1.2V and 3.3V need to be noticed as in Figure 5-1. During power on, it is recommended that the point where both power supplies are stabilized should be no later than 50ms after the start of the 3.3V rising. During power off, the end of 1.2V falling should be no later than 350ms after the start of 3.3V falling. Meanwhile, the falling time (0.9V<sub>DD</sub> to 0.1V<sub>DD</sub>) of 3.3V power should be no less than 50us. During the whole process, the voltage of 3.3V power should be always above the 1.2V power.

When the 5V to 3.3V LDO is used and 1.2V power is provided externally. The power on/off sequence between 1.2V and 5V should be as the same as the sequence between 1.2V and 3.3V mentioned above.

Figure 5-1. Power On/Off Sequence when 1.2V and 3.3V are provided externally

When both 5V to 3.3V LDO and 5V to 1.2 switch regulator are used, only 5V power needs to be provided. During power on, the rising time of 5V should be less than 50ms. During power off, the falling time from 0.9V<sub>DD</sub> to 2V should be less than 500ms as in Figure 5-2.

When switch regulator is operated in 3.3V to 1.2V mode, only 3.3V power needs to be provided. The rising and falling during power on/off should comply with the timing mentioned in adjacent section above.

Figure 5-2 Power On/Off Sequence in 5V only mode

#### 6. SMBus Slave Interface

The SMBus interface of RTS5411E is default disabled by firmware after power reset. To enable the SMBus, the external SPI flash or internal eFuse related setting is needed.

#### 6.1 Pull-Up Resistor for SMBus

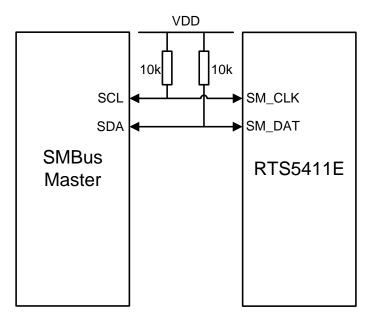

External pull-up resistors (10 k $\Omega$  recommended) are required on the SM\_DAT and SM\_CLK pins when implementing SMBus.

Figure 6-1. SMBus Slave Connection

#### 6.2 SMBus Bus Protocol

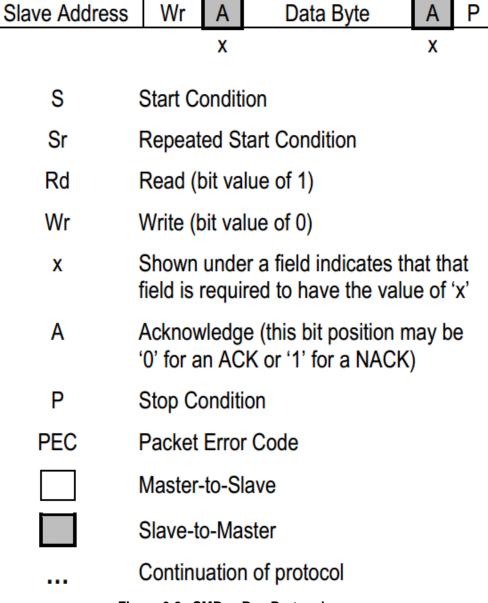

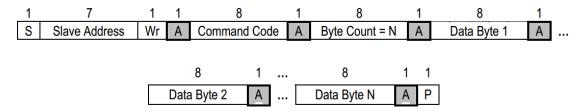

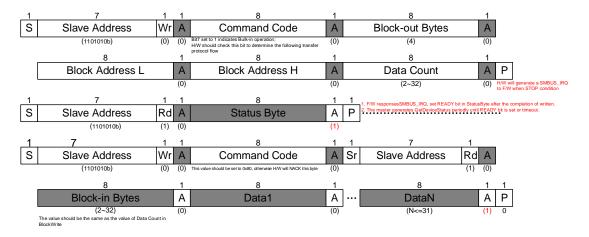

There are three **Bus Protocols** (defined in *SMBus Specification Revision 1.0*) supported by the SMBus interface of RTS5411E:

- Receive Byte

- Block Write

- Block Read

These bus protocols are shown in Figure 6-3, Figure 6-4 and Figure 6-5. The shading shown in the figures during a read or write indicates the hub is driving data on the SM\_DAT line; otherwise, host data is on the SM\_DAT line. Not all protocol elements will be present in every command. For instance, not all packets are required to include the Packet Error Code.

Note: Data bytes are transferred MSB first.

1

1

S

1

1

8

Figure 6-2. SMBus Bus Protocol

#### 6.2.1 Receive Byte

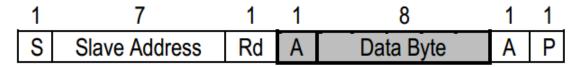

The *Receive Byte* is similar to a Send Byte, the only difference being the direction of data transfer. A simple device may have information that the host needs. It can do so with the Receive Byte protocol. The same device may accept both Send Byte and Receive Byte protocols. A NACK (a '1' in the ACK bit position) signifies the end of a read transfer.

Figure 6-3. Receive Byte

#### 6.2.2 Block Write/Block Read

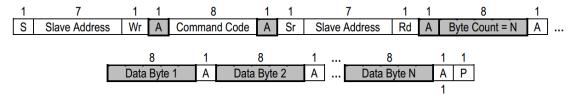

The *Block Write* begins with a slave address followed by a write bit, which is sent by I2C master. After the command code following the slave address, the I2C master sent a byte count which describes how many bytes will be transmitted later. For example, there are 20 bytes to be send by I2C master, the byte count field should be set as 20 (14h) which followed by the 20-byte data. The byte count does not include the PEC byte. The byte count may not set as zero. A Block Read or Block Write is allowed to transfer a maximum of 32 data bytes.

Figure 6-4. Block Write

A **Block Read** differs from Block Write in that the repeated START condition exists to satisfy the requirement for a change in the transfer direction. A NACK immediately preceding the STOP condition signifies the end of the read transfer.

Figure 6-5. Block Read

#### 6.3 SMBus Transfer Protocol

There are three Transfer Protocols supported by the SMBus interface of the RTS5411E:

- Get Device Status

- Block-out Transfer

- Block-in Transfer

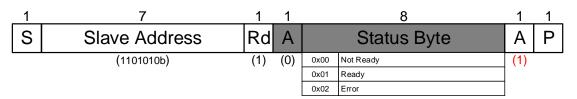

#### 6.3.1 Slave Address

The SMBus slave address of RTS5411E is default set to be 1101010b.

The value of slave address should be written to SLAVE\_ADDR register when the initialization process of the firmware, then HW will automatically compare it with the received slave address.

#### 6.3.2 Get Device Status

A *Get Device Status* is implemented by *Receive Byte*, which is used by the master to polling the transfer status for the addressed device

Figure 6-6. Get Device Status

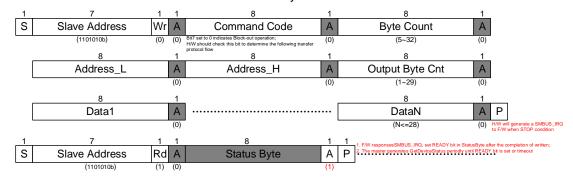

#### 6.3.3 Block-out Transfer

A **Block-out Transfer** is implemented by **Block Write** and **Receive Byte**, which is used by the master to send a block data. The maximum transfer size is 32-byte.

Figure 6-7. Block-out Transfer

#### 6.3.4 Block-in Transfer

A *Block-in Transfer* is implemented by Block Write, Block Read and Receive Byte, which is used by the master to receive a block data. The maximum transfer size is 32-byte.

Figure 6-8. Block-in Transfer

#### 6.3.5 Invalid Protocol Response Behavior

The only valid protocols are Get Device Status, Bulk-out Transfer and Bulk-in Transfer (described above), where RTS5411E only responds to the 7-bit firmware configured slave addresses (1101010b). Any invalid protocol will result ERROR bit set in Status Byte, which indicates that an error has happened.

#### 6.4 Bus Reset Sequence

The SMBus slave interface resets and returns to the idle state upon a START condition followed immediately by a STOP condition.

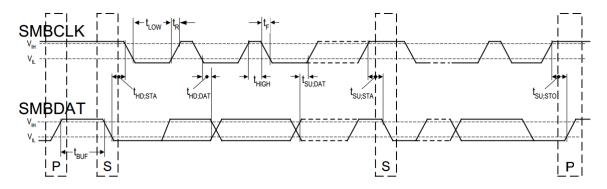

#### 6.5 SMBus Timing

The SMBus slave interface complies with the SMBus Specification Revision 1.0. See Section 2.1, AC Specifications on page 3 for more information.

Figure 6-9. SMBus Slave Time Diagram

| Symbol                | Parameter I                                                                                  |     | Limits |       |

|-----------------------|----------------------------------------------------------------------------------------------|-----|--------|-------|

| Syllibol              |                                                                                              |     | Max    | Units |

| F <sub>SMB</sub>      | SMBus Operating Frequency                                                                    | 10  | 100    | kHz   |

| $F_{BUF}$             | Bus free time between Stop and Start Condition                                               | 4.7 | -      | μs    |

| T <sub>HD:STA</sub>   | Hold time after (Repeated) Start Condition. After this period, the first clock is generated. | 4.0 | 1      | μs    |

| T <sub>SU:STA</sub>   | Repeated Start Condition setup time                                                          | 4.7 | -      | μs    |

| T <sub>SU:STO</sub>   | Stop Condition setup time                                                                    | 4.0 | -      | μs    |

| T <sub>HD:DAT</sub>   | Data hold time                                                                               | 300 | -      | ns    |

| T <sub>SU:DAT</sub>   | Data setup time                                                                              | 250 | -      | ns    |

| T <sub>TIMEOUT</sub>  | Detect clock low timeout                                                                     | 25  | 35     | ms    |

| $T_{LOW}$             | Clock low period                                                                             | 4.7 | -      | μs    |

| T <sub>HIGH</sub>     | Clock high period                                                                            | 4.0 | 50     | μs    |

| T <sub>LOW:SEXT</sub> | Cumulative clock low extend time (slave device)                                              | -   | 25     | ms    |

| T <sub>LOW:MEXT</sub> | Cumulative clock low extend time (master device)                                             | -   | 10     | ms    |

| $T_F$                 | Clock/Data Fall Time                                                                         | -   | 300    | ns    |

| $T_R$                 | Clock/Data Rise Time                                                                         | -   | 1000   | ns    |

| $T_POR$               | Time in which a device must be operational after power-on reset                              |     | 500    | ms    |

Table 6-1. SMBus AC specifications

26

#### 7. I2C Master and slave interface

#### 7.1 I2C Slave interface

The operation flow and date transaction format of I2C slave is similar with SMBus slave, reference SMBus Slave interface for reference.

#### 7.2 I2C Master interface

#### 7.2.1 Supported Mode and Speed

RTS5411E support the following three bus speed mode:

- > Standard-mode (Sm), with a bit rate up to 100 kbit/s.

- Fast-mode (Fm), with a bit rate up to 400 kbit/s.

- Fast-mode Plus (Fm+), with a bit rate up to 1 Mbit/s.

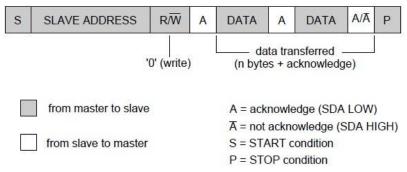

#### 7.2.2 Transfer Protocol Implementation

RTS5411E support four types transfer format

- Write

- Read

- Read Random

- Send Address

#### Write transfer

Master-transmitter transmits to slave-receiver. The transfer direction is not changed as depicted in the figure below. The slave receiver acknowledges each byte.

Figure 7-1 Write transfer format

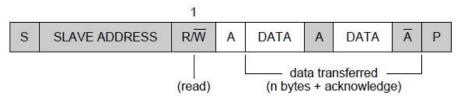

#### Read transfer

Master reads slave immediately after first byte (see Figure below). At the moment of the first acknowledge, the master-transmitter becomes a master-receiver and the slave-receiver becomes a slave-transmitter. The first byte data is still generated by the slave, and then I2C master generates subsequent acknowledges. At the end, STOP condition is generated by the master, which sends a not-acknowledge (A) just before the STOP condition.

Figure 7-2 Read transfer format

#### Read Random transfer

Read Random transfer format initiate two START condition, one is START, the other is Start repeat (Sr), during the start and Sr the transfer direction changed. During a change of direction within a transfer, the START condition and the slave address are both repeated, but with the R/W bit reversed. As describe in the figure below, the R/W bit after the first START is write and the data length n is 0 to 4 bytes. And the following start repeat R/W bit is read. The purpose of this format is to send command for the following Read operation.

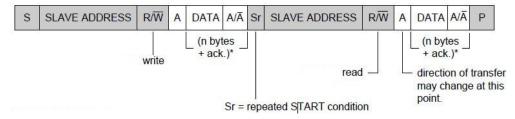

Figure 7-3 Read Random transfer format

#### **Send Address**

The Send Address transfer format is only with the slave address and without data, STOP condition following the R/W bit. This operation is used to set I2C slave device slave address.

#### 7.2.3 Stretching the SCK

RTS5411E support the I2C slave stretch SCK when the slave is busy. Besides, the hub will stretch the SCK if the memory to send or receive data being full or empty.

#### 7.2.4 Slave Response Timeout

The Slave Response Timeout is configurable for RTS5411E.

#### 7.3 I2C Timing

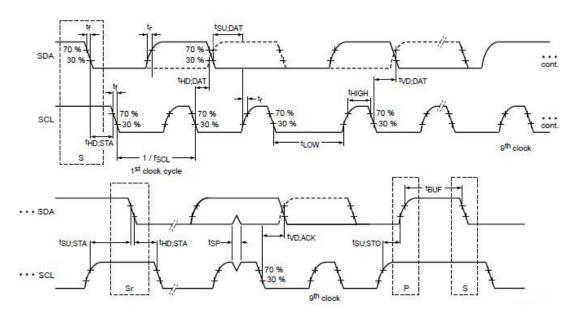

The I2C-bus timing characteristics, bus-line capacitance and noise margin are given in Table7-1. Figure 7-4 shows the timing definitions for the I2C-bus.

28

Figure 7-4 Definition of timing on the I2C bus

**Table 7-1 I2C Master Timing Specification**

| Symbol              | Parameter                                                    | Standard-mode |      | Fast-mode |     | Fast-mode<br>Plus |      | Unit |

|---------------------|--------------------------------------------------------------|---------------|------|-----------|-----|-------------------|------|------|

| •                   |                                                              | Min Max       |      | Min       | Max | Min               | Max  |      |

| $f_{SCL}$           | SCL clock<br>frequency                                       | 0             | 100  | 0         | 400 | 0                 | 1000 | kHz  |

| t <sub>HD;STA</sub> | hold<br>time(repeated)<br>START<br>condition                 | 4.0           | -    | 0.6       | -   | 0.26              | -    | μs   |

| $t_{LOW}$           | LOW period of<br>the SCL clock                               | 4.7           | -    | 1.3       | -   | 0.5               | -    | μs   |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                                 | 4.0           | -    | 0.6       | -   | 0.26              | -    | μs   |

| t <sub>SU;STA</sub> | set-up time for a<br>repeated<br>START<br>condition          | 4.7           | -    | 0.6       | -   | 0.26              | -    | μs   |

| t <sub>HD;DAT</sub> | data hold time                                               | 5.0           | -    | -         | -   | -                 | -    | μs   |

| t <sub>SU;DAT</sub> | data set-up time                                             | 250           | -    | 100       | -   | 50                | -    | ns   |

| t <sub>r</sub>      | rise time of both<br>SDA and SCL<br>signals                  | -             | 1000 | 20+0.1Cb  | 300 | -                 | 120  | ns   |

| t <sub>f</sub>      | fall tome of both<br>SDA and SCL<br>signals                  | -             | 300  | 20+0.1Cb  | 300 | -                 | 120  | ns   |

| t <sub>SU;STO</sub> | set-up tome for STOP condition                               | 4.0           | -    | 0.6       | -   | 0.26              | -    | μs   |

| t <sub>BUF</sub>    | bus free time<br>between a<br>STOP and<br>START<br>condition | 4.7           | -    | 1.3       | -   | 0.5               | -    | μs   |

| $C_{b}$             | capacitive load for each bus line | -                  | 400  | -                  | 400 | -                  | 550  | pF |

|---------------------|-----------------------------------|--------------------|------|--------------------|-----|--------------------|------|----|

| t <sub>VD;DAT</sub> | data valid time                   | -                  | 3.45 | -                  | 0.9 | -                  | 0.45 | μs |

| t <sub>VD;ACK</sub> | data valid<br>acknowledge<br>time | -                  | 3.45 | -                  | 0.9 | -                  | 0.45 | μs |

| $V_{nL}$            | noise margin at<br>LOW level      | 0.1V <sub>DD</sub> | -    | 0.1V <sub>DD</sub> | -   | 0.1V <sub>DD</sub> | -    | V  |

| $V_{nH}$            | noise margin at<br>LOW level      | $0.2V_{DD}$        | -    | $0.2V_{DD}$        | -   | $0.2V_{DD}$        | -    | V  |

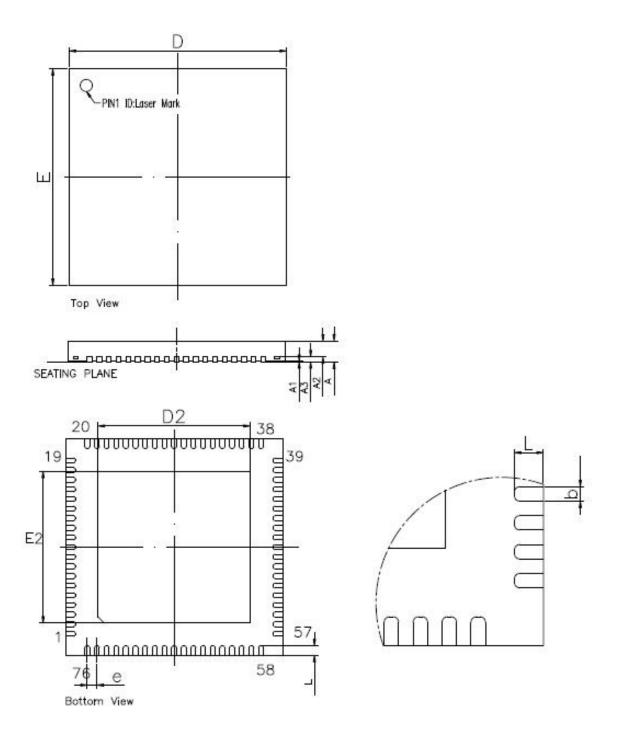

# 8. QFN-76 Package Dimensions

| Symbol                         | Dimension in mm |      |      | Dimension in inch |       |       |

|--------------------------------|-----------------|------|------|-------------------|-------|-------|

| Symbol                         | Min             | Nom  | Max  | Min               | Nom   | Max   |

| Α                              | 0.80            | 0.85 | 0.90 | 0.031             | 0.033 | 0.035 |

| $A_1$                          | 0.00            | 0.02 | 0.05 | 0.000             | 0.001 | 0.002 |

| $A_2$                          |                 | 0.65 | 0.70 |                   | 0.026 | 0.028 |

| $A_3$                          | 0.2 REF         |      |      | 0.008 REF         |       |       |

| b                              | 0.15            | 0.20 | 0.25 | 0.006             | 0.008 | 0.010 |

| D/E                            | 9.00 BSC        |      |      | 0.354 BSC         |       |       |

| D <sub>2</sub> /E <sub>2</sub> | 5.13            | 5.38 | 5.63 | 0.202             | 0.212 | 0.222 |

| е                              | 0.40 BSC        |      |      | 0.016 BSC         |       |       |

| Ĺ                              | 0.30            | 0.40 | 0.50 | 0.012             | 0.016 | 0.020 |

#### Notes:

1. CONTROLLING DIMENSION: MILLIMETER(mm).

2. REFERENCE DOCUMENTL: JEDEC MO-220.

3. BSC/REF tolerance +/-0.1mm

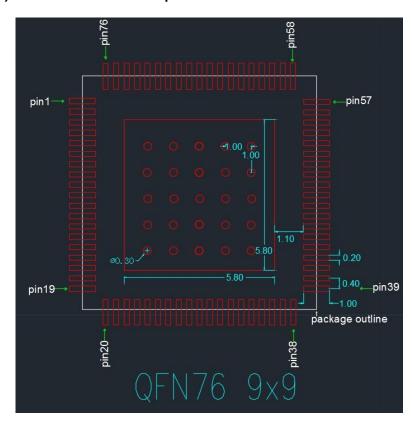

#### • QFN76 pin (9x9) recommended PCB footprint dimensions

#### Notes:

1. CONTROLLING DIMENSION: MILLIMETER(mm).

V0.93

# 9. Ordering Information

| Part Number  | Package                                 | Status       |

|--------------|-----------------------------------------|--------------|

| RTS5411E-GR  | QFN-76 Green package                    | MP available |

| RTS5411E-GRT | QFN-76 Green package with Tape and Reel | MP available |