## **High Efficiency Switching Mode Battery Charger**

### **General Description**

The RT9535B is a PWM switch mode battery charger controller to fast charge single or multiple Li-Ion, NiMH and NiCd batteries, using constant current or constant voltage control. Maximum current can be easily programmed by external resistor. The constant voltage output can support up to 22V with 0.5% accuracy.

A third control loop limits the input current drawing from the adapter during charging. This allows simultaneous operation of the equipment and fast battery charging without over loading to the adapter.

The RT9535B can charge batteries from 2.5V to 22V with dropout voltage as low as 0.4V. A logic output indicates Li-Ion full charge when current drops to 17% of the full-scale programmed charge current.

The RT9535B is available in the WQFN-24L 4x4 package.

### Features

- Fast Charging for Li-Ion, NiMH and NiCd Batteries

- Adjustable Battery Voltages from 2.5V to 22V

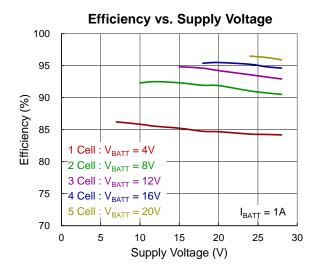

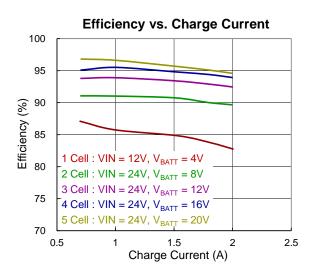

- High Efficiency : Up to 95%

- Charging Current Programmed by Resistor

- Precision 0.5% Charging Voltage Accuracy

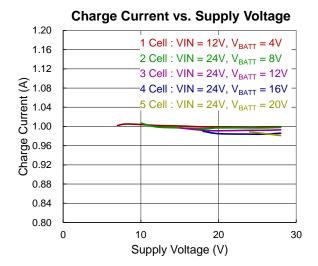

- Provide 5% Charging Current Accuracy

- Input Current Limit Maximizes Charging Rate

- 500kHz Switching Frequency

- Flag Indicates Li-Ion Charge Completion

- Auto Shutdown with Adapter Removal

- Only 10µA Battery Reverse Current when Idle

### Applications

- Notebook Computers

- Portable Instruments

- Chargers for Li-Ion, NiMH, NiCd and Lead Acid Rechargeable Batteries

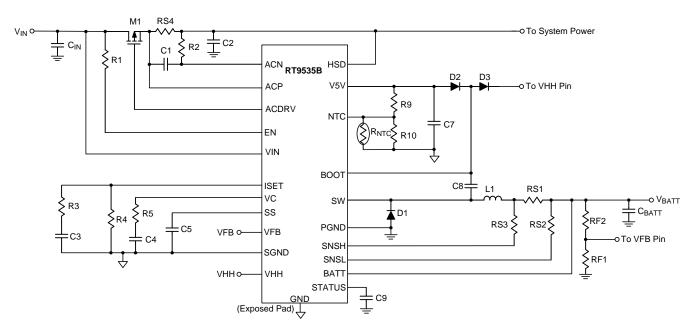

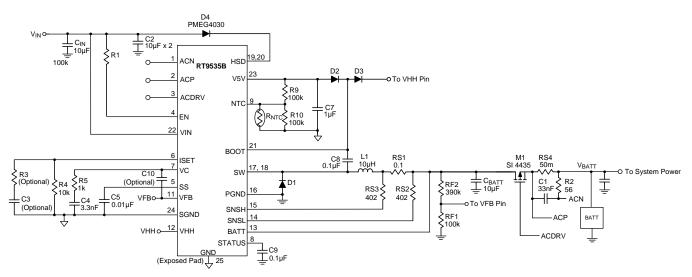

### Simplified Application Circuit

### **Ordering Information**

#### RT9535B

Package Type QW : WQFN-24L 4x4 (W-Type) (Exposed Pad-Option 1)

- Lead Plating System G : Green (Halogen Free and Pb Free)

Note :

Richtek products are :

- ► RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ► Suitable for use in SnPb or Pb-free soldering processes.

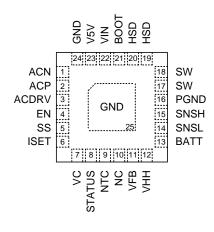

### **Pin Configurations**

### (TOP VIEW)

WQFN-24L 4x4

### **Marking Information**

21= : Product Code YMDNN : Date Code

## **Functional Pin Description**

| Pin No.             | Pin Name | Pin Function                                                                                                                                                                                                                           |

|---------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                   | ACN      | Negative Terminal to Sense Input Current. A filter is needed to filter out the 500kHz switching noise.                                                                                                                                 |

| 2                   | ACP      | Positive Terminal to Sense Input Current.                                                                                                                                                                                              |

| 3                   | ACDRV    | Drive Signal for the Gate of Input Power PFET.                                                                                                                                                                                         |

| 4                   | EN       | Enable Control Input (Active High). It must be connected to a logical voltage or pulled up to VIN with a $100k\Omega$ resistor.                                                                                                        |

| 5                   | SS       | Soft-Start Control Input. SS controls the soft-start time. Connect a capacitor from SS pin to GND to set the soft-start time.                                                                                                          |

| 6                   | ISET     | Charge Current Setting and System Loop Compensation Pin. Connect a resistor from this pin to ground to set the charge current.                                                                                                         |

| 7                   | VC       | Control Signal of the Inner Loop of the Current Mode PWM. A capacitor of at least $0.1\mu$ F with a serial resistor to GND filters out the current ripple.                                                                             |

| 8                   | STATUS   | Flag to Indicate Charge Completion. It turns to logical high when the charge current drops blew 17% of the setting charge current. A $0.1\mu$ F capacitor from STATUS to ground is needed to filter the sampled charge current ripple. |

| 9                   | NTC      | Input for an external NTC thermistor for battery temperature monitoring.                                                                                                                                                               |

| 10                  | NC       | No Internal Connection.                                                                                                                                                                                                                |

| 11                  | VFB      | Battery Voltage Feedback. Using an external resistor divider to set battery full charge voltage.                                                                                                                                       |

| 12                  | VHH      | To supply the current sense amplifier CA for very low dropout condition. It must<br>be connected as shown in the typical application circuit or connected to VIN if<br>VIN is always larger than BATT by at least 1.8V.                |

| 13                  | BATT     | Battery Voltage Sensing Input. A $10\mu F$ or larger X5R ceramic capacitor is recommended for filtering charge current ripple and stability purpose.                                                                                   |

| 14                  | SNSL     | Negative Terminal for Sensing Charge Current.                                                                                                                                                                                          |

| 15                  | SNSH     | Positive Terminal for Sensing Charge Current.                                                                                                                                                                                          |

| 16                  | PGND     | Power Ground.                                                                                                                                                                                                                          |

| 17, 18              | SW       | Switch Node. This pin switches between ground and VIN with high dv/dt rates. Care needs to be taken in the PCB layout to keep this node from coupling to other sensitive nodes.                                                        |

| 19, 20              | HSD      | Drain of Internal High-Side power N-MOSFET Switch. Connect a low ESR capacitor of $10\mu$ F or higher from this pin to ground for good bypass.                                                                                         |

| 21                  | воот     | Bootstrap Supply for the High-Side Power Switch Gate Driver and Control Circuitry. In normal operation, $V_{BOOT} \approx V_{SW} + 5V$ .                                                                                               |

| 22                  | VIN      | Input Power Supply. Connect a low ESR capacitor of $10\mu F$ or higher from this pin to ground for good bypass.                                                                                                                        |

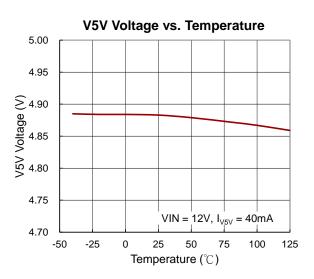

| 23                  | V5V      | Output of Internal 5V LDO. Connect a $1\mu F$ ceramic capacitor from this pin to GND for stability.                                                                                                                                    |

| 24                  | GND      | Analog Ground. Layout input capacitor and V5V capacitor to this pin as close as possible.                                                                                                                                              |

| 25<br>(Exposed Pad) | GND      | Exposed Pad. Connect the exposed pad to GND.                                                                                                                                                                                           |

Copyright © 2015 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

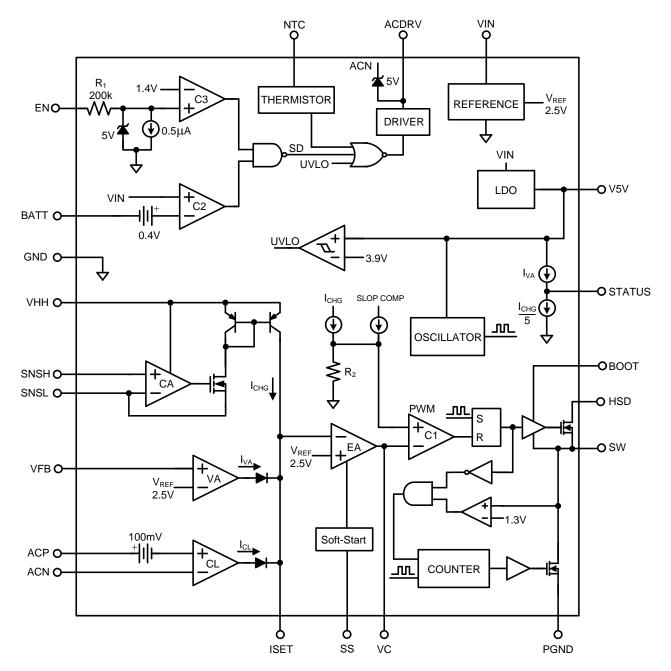

### **Function Block Diagram**

### Operation

The RT9535B is a current mode PWM step-down switching charger controller. The battery DC charge current is programmed by a resistor R4 at the ISET pin and the ratio of sense resistor RS2 over RS1 in the typical application circuit. Amplifier CA converts the charge current through RS1 to a much lower sampled current ICHG (ICHG = IBATT x RS1 / RS2) fed into the ISET pin. Amplifier EA compares the output of CA with 2.5V reference voltage and drives the PWM loop to force them to be equal. Note that ICHG has both AC and DC components. High DC accuracy is achieved with averaging filter R3 and C3 at ISET pin. ICHG is mirrored to go through R4 and generates a ramp signal that is fed to the PWM control comparator, forming the current mode inner loop. An internal LDO generates a 5V to power topside FET gate driver. For batteries like lithium that require both constant current and constant voltage charging, the 0.5% 2.5V reference and the voltage amplifier VA reduce the charge current when battery voltage reaches the normal charge voltage level. For NiMH and NiCd, VA can be used for over voltage protection.

### **CL** Amplifier

The amplifier CL monitors and limits the input current, normally from the AC adapter, to a preset level (100mV / RS4). At input current limit, CL will supply the programming current at ISET pin, thus reducing battery charging current.

#### **Charge STATUS**

When the charger is in voltage mode and the charge current level is reduced to 17%, STATUS pin will turn to logic high. This charge completion signal can be used to start a timer for charge termination. A  $0.1\mu$ F capacitor from STATUS to ground is needed to filter the sampled charging current ripple.

#### **ACDRV** Driver

The ACDRV pin drives an external P-MOSFET to avoid reverse current from battery to input supply. When input supply is removed, the RT9535B goes into a low current,  $10\mu$ A maximum, sleep mode as VIN drops below the battery voltage.

### Absolute Maximum Ratings (Note 1)

| VHH, EN to GND                                                                                | –0.3V to 36V                                        |

|-----------------------------------------------------------------------------------------------|-----------------------------------------------------|

| VIN, SW, HSD, ACN to GND                                                                      | –0.3V to 30V                                        |

| ACDRV                                                                                         | (ACN – 6V) to (ACN + 0.3V)                          |

| • ACP                                                                                         | (ACN – 0.3V) to (ACN + 0.6V)                        |

| BATT to GND                                                                                   | –0.3V to 28V                                        |

| ISET, VC, VFB, V5V to GND                                                                     | –0.3V to 6V                                         |

| • SNSL                                                                                        | (BATT – 0.3V) to (BATT + 0.3V)                      |

| • SNSH                                                                                        | (SNSL – 0.3V) to (SNSL + 0.3V)                      |

| • BOOT                                                                                        | (SW – 0.3V) to (SW + 6V)                            |

| • Power Dissipation, $P_D @ T_A = 25^{\circ}C$                                                |                                                     |

|                                                                                               |                                                     |

| WQFN-24L 4x4                                                                                  | 3.57W                                               |

| <ul><li>WQFN-24L 4x4</li><li>Package Thermal Resistance (Note 2)</li></ul>                    | 3.57W                                               |

|                                                                                               |                                                     |

| Package Thermal Resistance (Note 2)                                                           | 28°C/W                                              |

| <ul> <li>Package Thermal Resistance (Note 2)</li> <li>WQFN-24L 4x4, θ<sub>JA</sub></li> </ul> | 28°C/W<br>7°C/W                                     |

| <ul> <li>Package Thermal Resistance (Note 2)</li> <li>WQFN-24L 4x4, θ<sub>JA</sub></li></ul>  | 28°C/W<br>7°C/W<br>260°C                            |

| <ul> <li>Package Thermal Resistance (Note 2)<br/>WQFN-24L 4x4, θ<sub>JA</sub></li></ul>       | 28°C/W<br>7°C/W<br>260°C<br>150°C                   |

| <ul> <li>Package Thermal Resistance (Note 2)<br/>WQFN-24L 4x4, θ<sub>JA</sub></li></ul>       | 28°C/W<br>7°C/W<br>260°C<br>150°C                   |

| <ul> <li>Package Thermal Resistance (Note 2)<br/>WQFN-24L 4x4, θ<sub>JA</sub></li></ul>       | 28°C/W<br>7°C/W<br>260°C<br>150°C<br>–65°C to 150°C |

### Recommended Operating Conditions (Note 4)

| Supply Input Voltage       | - 4.5V to 28V    |

|----------------------------|------------------|

| Battery Voltage, VBAT      | - 2.5V to 22V    |

| Ambient Temperature Range  | - –40°C to 85°C  |

| Junction Temperature Range | - –40°C to 125°C |

### **Electrical Characteristics**

$(V_{IN} = V_{BAT} + 3V, V_{BAT}$  is the full charge voltage, pull-up EN to VIN with 100k $\Omega$  resistor,  $T_A = 25^{\circ}C$ , unless otherwise specified)

| Parameter                               | Symbol           | Test Conditions                                                              | Min | Тур | Max | Unit |  |  |

|-----------------------------------------|------------------|------------------------------------------------------------------------------|-----|-----|-----|------|--|--|

| Overall                                 | Overall          |                                                                              |     |     |     |      |  |  |

| Supply Quiescent Current                | lq               | No Charge Current                                                            | 0.5 | 1.3 | 2   | mA   |  |  |

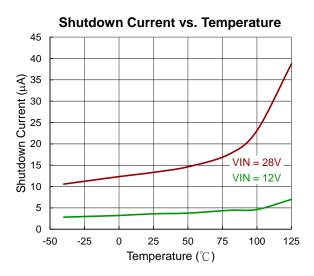

| Supply Shutdown Current                 | I <sub>SD</sub>  | V <sub>EN</sub> = 0                                                          |     |     | 12  | μΑ   |  |  |

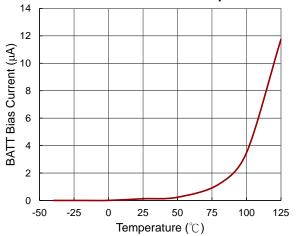

| Reverse Current from<br>Battery         | I <sub>REV</sub> | VIN Floating, $V_{EN} = 0$ , $V_{BATT} = V_{SW} = V_{SNSH} = V_{SNSL} = 20V$ |     |     | 10  | μA   |  |  |

| VIN Under-Voltage Lockout               | Vuvlo            |                                                                              | 3.6 | 3.8 | 4.3 | V    |  |  |

| VIN Under-Voltage Lockout<br>Hysteresis | VUVLO_HYS        |                                                                              |     | 300 |     | mV   |  |  |

| Parameter                                   | Symbol            | Test Conditions                                                                        | Min   | Тур   | Max   | Unit |  |

|---------------------------------------------|-------------------|----------------------------------------------------------------------------------------|-------|-------|-------|------|--|

| Reference                                   | -,                |                                                                                        | •     | - 7 P |       |      |  |

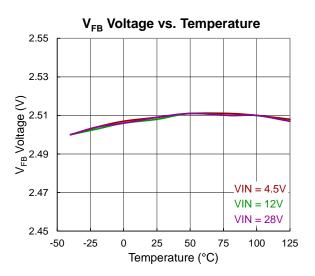

| Reference Voltage                           | V <sub>FB</sub>   |                                                                                        | 2.488 | 2.5   | 2.512 | V    |  |

| FB Bias current                             | IFB               | V <sub>FB</sub> = 2.5V                                                                 |       |       | 0.1   | μA   |  |

| Charge Current                              |                   |                                                                                        |       |       |       |      |  |

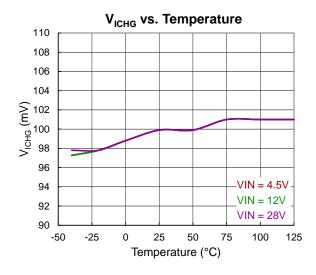

| Full-Scale Charge Current<br>Sense Voltage  | VICHG             | R4 = $10k\Omega$ , RS3 = RS2 = $402\Omega$ ,<br>Measure the Voltage Drop Across<br>RS1 | 95    | 100   | 105   | mV   |  |

| ISET Output Current                         | IISET             |                                                                                        | -1    |       |       | mA   |  |

| Termination Current Set<br>Factor           | VITM              | 1/5-Scale Charge Current when<br>STATUS from Low to High                               |       | 18    | 25    | %    |  |

| SNSL Bias Current                           | I <sub>SNSH</sub> | No Charge Current                                                                      | -36   | -12   | -6    | μΑ   |  |

| SNSH Bias Current                           | I <sub>SNSH</sub> | No Charge Current                                                                      | -36   | -12   | -6    | μΑ   |  |

| Battery Voltage                             |                   |                                                                                        |       |       |       |      |  |

| VHH Minimum Voltage with Respect to BATT    | ΔVhh              |                                                                                        |       |       | 2     | V    |  |

| VIN Minimum Voltage with<br>Respect to BATT | Vdrop             | (Note 5)                                                                               |       | 0.3   | 0.4   | V    |  |

| VHH Input Current                           | Іунн              | V <sub>IN</sub> = 28V                                                                  | 40    | 95    | 150   | μΑ   |  |

| BATT Bias Current                           | IBATT             | VEN = 0, VBATT = VSW = VSNSH =<br>VSNSL = 20V                                          |       |       | 10    | μΑ   |  |

| VC Pin Current                              | lvc               | Vvc = 0V                                                                               | -35   | -15   | -1    | μΑ   |  |

| Input Current Limit                         |                   |                                                                                        |       |       |       |      |  |

| Input Current Limit Sense<br>Voltage        | VILMT             | Measure the Voltage Drop Across<br>RS4                                                 | 95    | 100   | 105   | mV   |  |

| ACN Input Current                           | I <sub>ACN</sub>  | $V_{ACP} - V_{ACN} = 0.1V$                                                             | 8     | 16    | 34    | μΑ   |  |

| ACP Input Current                           | IACP              | VACP - VACN = 0.1V                                                                     | 25    | 50    | 80    | μΑ   |  |

| ACDRV ON Voltage                            | VACON             | Measure the Voltage<br>(V <sub>ACN</sub> – V <sub>ACDRV</sub> )                        | 4     | 5.4   | 6     | V    |  |

| ACDRV OFF Voltage                           | VACOFF            | Measure the Voltage<br>(VACN - VACDRV), VEN = 0V                                       |       |       | 0.1   | V    |  |

| ARDRV Pull-Down Current                     | I <sub>ACPD</sub> | V <sub>ACN</sub> - V <sub>ACDRV</sub> = 3.8V                                           | 5     | 10    | 30    | μΑ   |  |

| ARDRV Pull-Up Current                       | I <sub>ACPU</sub> | $V_{ACN} - V_{ACDRV} = 0.5V, V_{EN} = 0V$                                              | -10   | -5    | -2    | μΑ   |  |

| Switch Characteristics                      |                   |                                                                                        |       |       |       |      |  |

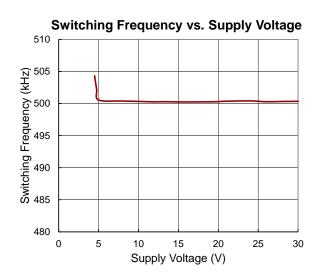

| Switching Frequency                         | fosc              |                                                                                        | 430   | 500   | 545   | kHz  |  |

| High-Side Switch<br>On-Resistance           | R <sub>ON</sub>   |                                                                                        |       | 150   |       | mΩ   |  |

| High-Side Switch leakage<br>Current         | I <sub>HSD</sub>  | $V_{HSD} = 30V, V_{EN} = 0V$                                                           |       |       | 10    | μΑ   |  |

| BOOT Leakage Current                        | I <sub>BOOT</sub> | $V_{BOOT} = 30V, V_{EN} = 0V$ (Note 5)                                                 |       | 1     |       | μΑ   |  |

| Maximum Duty                                |                   | $V_{VC} = 0V$ (Note 5)                                                                 | 95    | -     |       | %    |  |

| SW Leakage Current                          | I <sub>LKGL</sub> | $V_{SW} = 28V, V_{EN} = 0V$                                                            |       |       | 10    | μΑ   |  |

7

RICHTEK

| Parameter                           |               | Symbol           | Test Conditions                        | Min                         | Тур                         | Max                         | Unit |

|-------------------------------------|---------------|------------------|----------------------------------------|-----------------------------|-----------------------------|-----------------------------|------|

| Regulator and Logic Characteristics |               |                  |                                        |                             |                             |                             |      |

| LDO Output V                        | 'oltage       | Vldo             | 50mA Load at V5V, V <sub>VC</sub> = 0V | 4                           | 5                           | 6                           | V    |

| STATUS High                         | Voltage       |                  | STATUS Cap = 1µF                       |                             | 5                           |                             | V    |

| EN Input                            | Logic-High    | Venh             |                                        | 2.5                         |                             |                             | V    |

| Voltage                             | Logic-Low     | V <sub>ENL</sub> |                                        |                             |                             | 0.6                         |      |

| EN Input Curr                       | ent           | I <sub>EN</sub>  | $0V \le V_{EN} \le 5V$                 |                             |                             | 10                          | μΑ   |

| Soft-Start Sou                      | rcing Current | I <sub>SS</sub>  |                                        | 1.5                         | 3.3                         | 7                           | μA   |

| Thermal Com                         | parator and P | rotection        |                                        |                             |                             |                             |      |

| NTC Threshold, Cold                 |               | VCOLD            | NTC Voltage Rising, 1%<br>Hysteresis   | 73.5%<br>× V <sub>V5V</sub> | 75% ×<br>V <sub>V5V</sub>   | 76.5%<br>× V <sub>V5V</sub> | V    |

| NTC Threshold, Hot                  |               | Vнот             | NTC Voltage Rising, 1%<br>Hysteresis   | 31% ×<br>V <sub>V5V</sub>   | 32.5%<br>× V <sub>V5V</sub> | 34% ×<br>Vv5v               | V    |

| NTC Disable Threshold               |               | VDISNTC          | NTC Voltage Rising, 1%<br>Hysteresis   | 0.2% ×<br>V <sub>V5V</sub>  | 1.7% ×<br>Vv5v              | 3.2% ×<br>Vv5v              | V    |

| NTC Bias Current                    |               | INTC             |                                        |                             | 2                           | 10                          | μΑ   |

| Thermal Shutdown<br>Temperature     |               | T <sub>SD</sub>  | (Note 5)                               |                             | 160                         |                             | °C   |

| Thermal Shutdown<br>Hysteresis      |               | $\Delta T_{SD}$  | (Note 5)                               |                             | 30                          |                             | °C   |

**Note 1.** Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

**Note 2.**  $\theta_{JA}$  is measured at  $T_A = 25^{\circ}C$  on a high effective thermal conductivity four-layer test board per JEDEC 51-7.  $\theta_{JC}$  is measured at the exposed pad of the package.

Note 3. Devices are ESD sensitive. Handling precaution recommended.

Note 4. The device is not guaranteed to function outside its operating conditions.

Note 5. Guaranteed by design, not subjected to production test.

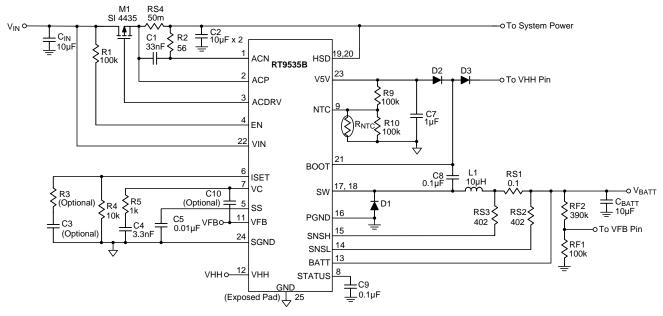

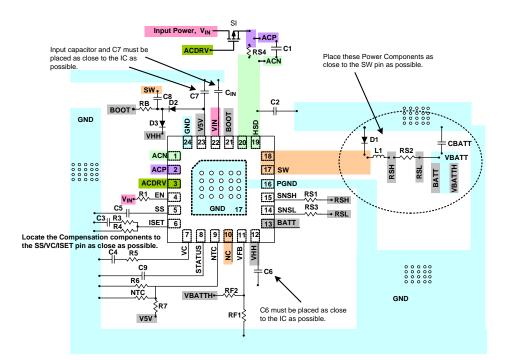

### **Typical Application Circuit**

Figure 1. System Power from VIN ( $V_{IN} = 15V$  to 28V, 3 – cell,  $I_{charge} = 1A$ )

Figure 2. System Power with VBATT (VIN = 15V to 28V, 3 - cell, if Isystem = 0.5A than IBATT = 0.5A)

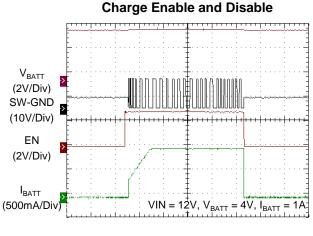

### **Typical Operating Characteristics**

Supply Current vs. Temperature

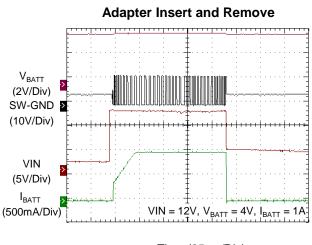

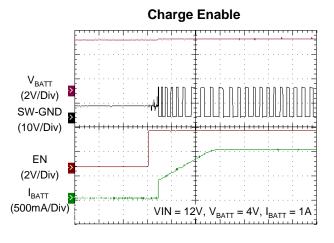

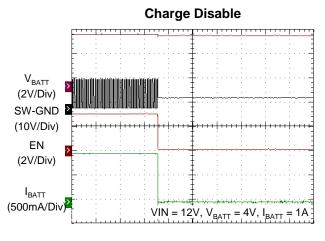

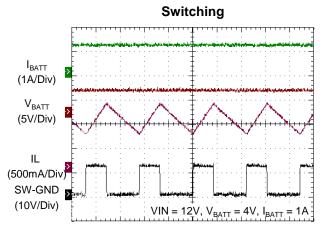

Time (25ms/Div)

BATT Bias Current vs.Temperature

Time (25ms/Div)

RICHTEK

Time (10ms/Div)

Time (10ms/Div)

Time (1 $\mu$ s/Div)

Time (10ms/Div)

= 4V, I<sub>BATT</sub>

$VIN = 12V, V_{BATT}$

(500mA/Div

SW-GND

(10V/Div)

### **Application Information**

#### Input and Output Capacitors

In the typical application circuit, the input capacitor (C2) is assumed to absorb all input switching ripple current in the converter, so it must have adequate ripple current rating. Typically, at high charging currents, the converter will operate in continuous conduction mode. In this case, the RMS current IRMSIN of the input capacitor C2 can be estimated by the equation:

IRMSIN = IBATT

$$\times \sqrt{D - D^2}$$

Where  $I_{BATT}$  is the battery charge current and D is the duty cycle. In worst case, the RMS ripple current will be equal to one half of output charging current at 50% duty cycle. For example,  $I_{BATT} = 2A$ , the maximum RMS current will be 1A. A low-ESR ceramic capacitor such as X7R or X5R is preferred for the input-decoupling capacitor and should be placed to the drain of the high-side MOSFET and source of the low-side MOSFET as close as possible. The voltage rating of the capacitor must be higher than the normal input voltage level. Above  $20\mu$ F capacitance is suggested for typical of 2A charging current.

The output capacitor ( $C_{BATT}$ ) is also assumed to absorb output switching current ripple. The general formula for capacitor current is :

$$I_{RMSCB} = \frac{V_{BATT} \times \left(1 - \frac{V_{BATT}}{V_{VIN}}\right)}{2 \times \sqrt{3} \times L1 \times f_{osc}}$$

For example,  $V_{VIN}$  = 19V,  $V_{BATT}$  = 8.4V, L1 = 10 $\mu$ H, and fosc = 475kHz, I<sub>RMS</sub> = 0.15A.

EMI considerations usually make it desirable to minimize ripple current in the battery leads. Beads or inductors may be added to increase battery impedance at the 475kHz switching frequency. Switching ripple current splits between the battery and the output capacitor depending on the ESR of the output capacitor RT9535B

and the battery impedance is raised to  $4\Omega$  with a bead or inductor, only 5% of the ripple current will flow in the battery.

#### Inductor

The inductor value will be changed for more or less current ripple. The higher the inductance, the lower the current ripple will be. As the physical size is kept the same, typically, higher inductance will result in higher series resistance and lower saturation current. A good tradeoff is to choose the inductor so that the current ripple is approximately 30% to 50% of the full-scale charge current. The inductor value is calculated as :

$$L1 = \frac{V_{BATT} \times (V_{VIN} - V_{BATT})}{V_{VIN} \times f_{OSC} \times \Delta I_L}$$

Where  $\Delta I_L$  is the inductor current ripple. For example, V<sub>VIN</sub> = 19V, choose the inductor current ripple to be 40% of the full-scale charge current in the typical application circuit for 2A, 2-cell battery charger,  $\Delta I_L$  = 0.8A, V<sub>BATT</sub> = 8.4V, calculate L1 to be 12µH. So choose L1 to be 10µH which is close to 12µH.

#### Soft-Start and Under-Voltage Lockout

The soft-start is controlled by the voltage rise time at VC pin. There are internal soft-start and external soft-start in the RT9535B. With a  $1\mu$ F capacitor, time to reach full charge current is about 60ms and it is assumed that input voltage to the charger will reach full value in less than 60ms. The capacitor can be increased if longer input start-up times are needed.

For the RT9535B, it provides Under-Voltage Lockout (UVLO) protection. If LDO output voltage is lower than 3.9V, the internal top side power FET and input power FET M1 will be cut off. This will protect the adapter from entering a quasi "latch" state where the adapter output stays in a current limited state at reduced output voltage.

and the battery impedance. If the ESR of C<sub>OUT</sub> is 0.2Ω Copyright © 2015 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

## RICHTEK

#### Adapter Current Limiting

An important feature of RT9535B is the ability to automatically adjust charge current to a level which avoids overloading the wall adapter. This allows the product to operate, and at the same time batteries are being charged without complex load management algorithms. Additionally, batteries will automatically be charged at the maximum possible rate of which the adapter is capable. This is accomplished by sensing total adapter output current and adjusting charge current downward if a preset adapter current limit is exceeded. Amplifier CL in typical application circuit senses the voltage across RS4, connected between the ACP and ACN pins. When this voltage exceeds 100mV, the amplifier will override programmed charge current to limit adapter current to 100mV/RS4. A low pass filter formed by 56 $\Omega$  and 33nF is required to eliminate switching noise.

#### **Full-Scale Charge Current Programming**

The basic formula for full-scale charge current is (see Block Diagram) :

$$I_{BATT} = \left(\frac{V_{REF}}{R4}\right) \times \left(\frac{RS2}{RS1}\right)$$

Where R4 is the total resistance from ISET pin to ground. For the sense amplifier CA biasing purpose, RS3 should have the same value as RS2 with 1% accuracy. For example, 2A full-scale charging current is needed. For low power dissipation on RS1 and enough signal to drive the amplifier CA, let RS1 = 100mV / 2A = 50m $\Omega$ . This limits RS1 power to 0.2W. Let R4 = 10k $\Omega$ , then:

$RS2 = RS3 = \frac{I_{BATT} \times R4 \times RS1}{V_{RFF}} = \frac{2A \times 10k \times 0.05}{2.5V} = 400\Omega$

Note that for charge current accuracy and noise immunity, 100mV full scale level across the sense resistor RS1 is required. Consequently, both RS2 and RS3 should be  $399\Omega$ . For for 0°C to 85°C temperature range, the minimum value for R4 is  $5.5k\Omega$ .

For for -40°C to 85°C temperature range, the minimum value for R4 is  $6k\Omega$ .

The maximum value of R4 should be lower than  $60k\Omega$ .

It is critical to have a good Kelvin connection on the current sense resistor RS1 to minimize stray resistive and inductive pickup. RS1 should have low parasitic inductance (typical 3nH or less). The layout path from RS2 and RS3 to RS1 should be kept away from the fast switching SW node. A 1nF ceramic capacitor can be used across SNSH and SNSL and be kept away from the fast switching SW node.

#### **Battery Voltage Regulation**

The RT9535B uses high-accuracy voltage bandgap and regulator for the high charging-voltage accuracy. The charge voltage is programmed via a resistor divider from the battery to ground, with the midpoint tied to the VFB pin. The voltage at the VFB pin is regulated to 2.5V, giving the following equation for the regulation voltage :

$$V_{\text{BATT}} = 2.5 \times \left(1 + \frac{\text{RF2}}{\text{RF1}}\right)$$

where RF2 is connected from VFB to the battery and RF1 is connected from VFB to GND.

#### Charging

The 2A Battery Charger (typical application circuit) charges lithium-ion batteries at a constant 2A until battery voltage reaches the setting value. The charger will then automatically go into a constant voltage mode with current decreasing to near zero over time as the battery reaches full charge.

#### **Charging Completion**

Some battery manufacturers recommend termination of constant voltage float mode after charge current has dropped below a specified level (typically around 20% of the full-scale charge current) and a further time-out period of 30 minutes to 90 minutes has elapsed. Check

with manufacturers for details. The RT9535B provides a signal at the STATUS pin when charging is in voltage mode and charge current is reduced to 17% of full-scale charge current, assuming full-scale charge current is programmed to have 100mV across the current sense resistor (VRS1).

The charge current sample  $I_{CHG}$  is compared with the output current  $I_{VA}$  of voltage amplifier VA. When the charge current drops to 17% of full-scale charge current,  $I_{CHG}$  will be equal to 20% of  $I_{VA}$  and the STATUS pin voltage will go logic high and can be used to start an external timer. When this feature is used, a capacitor of at least  $0.1\mu$ F is required at the STATUS pin to filter out the switching noise. If this feature is not used, the capacitor is not needed.

#### **Dropout Operation**

The RT9535B can charge the battery even when VIN goes as low as 2V above the combined voltages of the battery and the drops on the sense resistor as well as parasitic wiring. This low VIN sometimes forces 100% duty cycle and TG stays on for many switching cycles. While TG stays on, the voltage  $V_{BOOT}$  across the capacitor C8 drops down slowly because the current sink at BOOT pin. C8 needs to be recharged before  $V_{BOOT}$  drops too low to keep the topside switch on.

A unique design allows the RT9535B to operate under these conditions. If SW pin voltage keeps larger than 1.3V for 32 oscillation periods, topside power FET will be turned off and an internal FET will be turned on to pull SW pin down. This function refreshes V<sub>BOOT</sub> voltage to a higher value. It is important to use  $0.1\mu$ F to hold V<sub>BOOT</sub> up for a sufficient amount of time. The P-MOSFET M1 is optional and can be replaced with a diode if VIN is at least 2.5V higher than V<sub>BATT</sub>. The gate control pin ACDRV turns on M1 when V5V gets up above the under-voltage lockout level and is clamped internally to 5V below V<sub>ACN</sub>. In sleep mode, when VIN is removed, ACDRV will clamped internally to 5V below  $V_{ACN}$ . In sleep mode, when VIN is removed, ACDRV will clamp M1  $V_{SG}$  to less than 0.1V.

#### Shutdown

When adapter power is removed, VIN will drift down. As soon as VIN goes down to 0.1V above  $V_{BATT}$ , the RT9535B will go into sleep mode drawing only ~10µA from the battery. There are two ways to stop switching: pulling the EN pin low or pulling the VC pin low. Pulling the EN pin low will shut down the whole chip. Pulling the VC pin low will only stop switching and LDO stays work. Make sure there is a pull-up resistor on the EN pin even if the EN pin is not used, otherwise internal pull-down current will keep the EN pin low to shut down mode when power turns on.

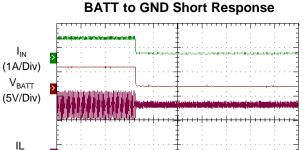

#### **Charger Protection**

If the VIN connector of typical application circuit can be instantaneously shorted to ground, the P-MOSFET M1 must be quickly turned off, otherwise, high reverse surge current might damage M1. An internal transient enhancement circuit is designed to quickly charge ACDRV pin voltage to ACN pin voltage.

Note that the RT9535B will operate even when  $V_{BATT}$  is grounded. If  $V_{BATT}$  of typical application circuit charger gets shorted to ground very quickly from a high battery voltage, slow loop response may allow charge current to build up and damage the topside N-MOSFET M2. A small diode from the EN pin to  $V_{BATT}$  will shut down switching and protect the charger.

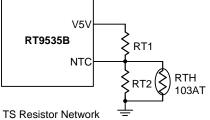

#### **Temperature Qualification**

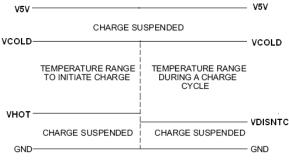

The controller RT9535B continuously monitors battery temperature by measuring the voltage between the NTC pin and GND. A negative temperature coefficient thermistor (NTC) and an external voltage divider typically develop this voltage. The controller compares this voltage against its internal thresholds to determine if charging is allowed. To initiate a charge cycle, the battery temperature must be within the VCOLD. If

## RICHTEK

battery temperature is outside of this range, the controller suspends charge and the safety timer and waits until the battery temperature is within the VCOLD to VHOT range. During the charge cycle, the battery temperature must be within the VCOLD and VDISNTC thresholds. If the battery temperature is outside of this range, the controller suspends charge and waits until the battery temperature is within the VCOLD to VHOT range. The controller suspends charge by turning off the PWM charge FETs.

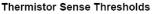

Assuming a 103AT NTC thermistor on the battery pack as shown in the below, the values of RT1 and RT2 can be determined by using the following equations:

#### **Thermal Considerations**

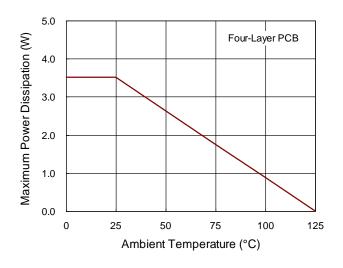

For continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula :

$\mathsf{P}_{\mathsf{D}(\mathsf{MAX})} = (\mathsf{T}_{\mathsf{J}(\mathsf{MAX})} - \mathsf{T}_{\mathsf{A}}) / \theta_{\mathsf{J}\mathsf{A}}$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating condition specifications, the maximum junction temperature is 125°C. The junction to ambient thermal resistance,  $\theta_{JA}$ , is layout dependent. For WQFN-24L 4x4 package, the thermal resistance,  $\theta_{JA}$ , is 28°C/W on a standard JEDEC 51-7 four-layer thermal test board. The maximum power dissipation at  $T_A = 25$ °C can be calculated by the following formula :

$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (28^{\circ}C/W) = 3.57W$  for WQFN-24L 4x4 package

The maximum power dissipation depends on the operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance,  $\theta_{JA}$ . The derating curve in Figure 3 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Where  $RTH_{COLD}$  and  $RTH_{HOT}$  which have defined in the spec of the 103AT NTC thermistor.

Figure 3. Derating Curve of Maximum Power Dissipation

#### Layout Consideration

Switch rise and fall times are under 20ns for maximum efficiency. To prevent radiation, the SW pin, the rectifier Schottky diode D1 and input bypass capacitor leads should be kept as short as possible. A ground plane should be used under the switching circuitry to prevent inter-plane coupling and to act as a thermal spreading path. Note that the rectifier Schottky diode D1 is probably the most heat dissipating device in the charging system. The voltage drop on a 2A Schottky diode can be 0.5V. With 50% duty cycle, the power dissipation can go as high as 0.5W. Expanded traces should be used for the diode leads for low thermal resistance. Another large heat dissipating device is probably the inductor. The fast switching high current ground path including the MOSFETs, D1 and input bypass capacitor C2 should be kept very short. Another smaller input bypass (1µF ceramic or larger paralleled with CIN) should be placed to VIN pin and GND pin as close as possible.

Figure 4. PCB Layout Guide

Copyright © 2015 Richtek Technology Corporation. All rights reserved.

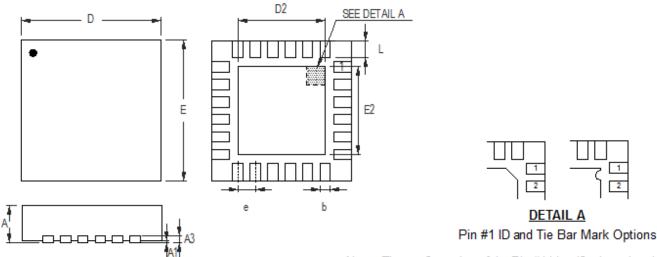

### **Outline Dimension**

Note : The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

| Symbol |          | Dimensions Ir | n Millimeters | Dimensions In Inches |       |  |

|--------|----------|---------------|---------------|----------------------|-------|--|

|        |          | Min           | Max           | Min                  | Max   |  |

|        | А        | 0.700         | 0.800         | 0.028                | 0.031 |  |

|        | A1       | 0.000         | 0.050         | 0.000                | 0.002 |  |

|        | A3       | 0.175         | 0.250         | 0.007                | 0.010 |  |

|        | b        | 0.180         | 0.300         | 0.007                | 0.012 |  |

|        | D        | 3.950         | 4.050         | 0.156                | 0.159 |  |

| D2     | Option 1 | 2.400         | 2.500         | 0.094                | 0.098 |  |

| DZ     | Option 2 | 2.650         | 2.750         | 0.104                | 0.108 |  |

| E      |          | 3.950         | 4.050         | 0.156                | 0.159 |  |

| E2     | Option 1 | 2.400         | 2.500         | 0.094                | 0.098 |  |

| ΕZ     | Option 2 | 2.650         | 2.750         | 0.104                | 0.108 |  |

| е      |          | 0.5           | 500           | 0.0                  | )20   |  |

| L      |          | 0.350         | 0.450         | 0.014                | 0.018 |  |

W-Type 24L QFN 4x4 Package

### **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C. Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

Copyright © 2015 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.