## RICHTEK

## Multi-Phase PWM Controller for K8 CPU Core Power Supply with Serial Programming Interface

### **General Description**

The RT8801B is a multi-phase synchronous buck controller which is implemented with full control functions for AMD K8 compliant CPU. The RT8801B could be operated with 2, 3 or 4 buck switching stages operating in interleaved phase set automatically. The multiphase architecture provides high output current while maintaining low power dissipation on power devices and low stress on input and output capacitors.

RT8801B is one of RichTek CPU core power solutions which integrates a specific series programming interface for the controller peration configuration. There are several registers implemented for the specific parameters configuration including VID for core power, and signal for load current indication. User can program the configuration of the parameters easily via the specific programming interface. With the implementation of RT8801B, the part provides more flexibility and feature for customers advanced segment product design.

The RT8801B applies the DCR sensing technology newly as well; with such a topology, the RT8801B extracts the DCR of output inductor as sense component to deliver a more precise load line regulation and better thermal balance for next generation processor application. For current sense setting, droop tuning, V<sub>CORE</sub> initial offset and over current protection are independent to compensation circuit of voltage loop. The feature greatly facilitates the flexibility of CPU power supply design and tuning. The DAC output of RT8801B supports AMD CPU with 6-bit VID input, precise initial value & smooth V<sub>CORE</sub> transient at VID jump. The IC monitors the V<sub>CORE</sub> voltage for over-voltage protection. Soft-start, over-current protection and programmable under-voltage lockout are also provided to assure the safety of microprocessor and power system. The RT8801B comes to the package of VQFN-32L 5x5.

#### **Features**

- Multi-Phase Power Conversion with Automatic Phase Selection

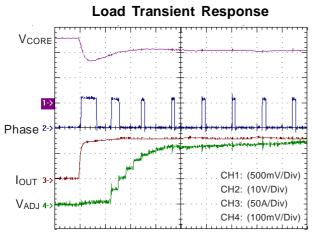

- 6-bits AMD K8 DAC Output with Active Droop Compensation for Fast Load Transient

- Smooth V<sub>CORE</sub> Transition at VID Jump

- Power Stage Thermal Balance by DCR Current Sense

- Hiccup Mode Over-Current Protection

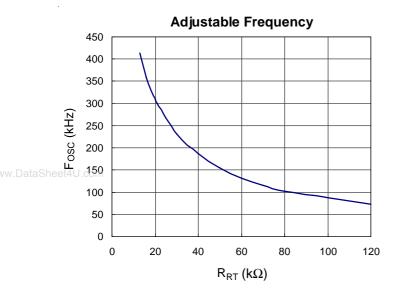

- Adjustable Switching Frequency (50kHz to 400kHz per Phase)

- Under-Voltage Lockout and Soft-Start

- High Ripple Frequency Times Channel Number

- 2-Wires Programming Interface

- Software Programmable VID

- 32-Lead VQFN Package

- RoHS Compliant and 100% Lead (Pb)-Free

### Applications

- AMD K8 compliant Processors Voltage Regulator

- Low Output Voltage, High power density DC-DC Converters

- Voltage Regulator Modules

## **Ordering Information**

RT8801B Package Type QV : VQFN-32L 5x5 (V-Type) Operating Temperature Range P : Pb Free with Commercial Standard G : Green (Halogen Free with Commer-

cial Standard)

Note :

Richtek Pb-free and Green products are :

- ►RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- Suitable for use in SnPb or Pb-free soldering processes.

- ▶100% matte tin (Sn) plating.

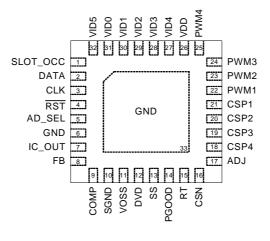

## **Pin Configurations**

(TOP VIEW)

VQFN-32L 5x5

### Registers

#### 0x00 Hi-I setting registers; Default 0x00

Bit4-0 :

| Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | VID Offset (mV) |

|------|------|------|------|------|-----------------|

| 0    | 0    | 0    | 0    | 0    | 0               |

| 0    | 0    | 0    | 0    | 1    | 25              |

| 0    | 0    | 0    | 1    | 0    | 50              |

| 0    | 0    | 0    | 1    | 1    | 75              |

| 0    | 0    | 1    | 0    | 0    | 100             |

| 0    | 0    | 1    | 0    | 1    | 125             |

| 0    | 0    | 1    | 1    | 0    | 150             |

| 0    | 0    | 1    | 1    | 1    | 175             |

| 0    | 1    | 0    | 0    | 0    | 200             |

| 0    | 1    | 0    | 0    | 1    | 225             |

| 0    | 1    | 0    | 1    | 0    | 250             |

| 0    | 1    | 0    | 1    | 1    | 275             |

| 0    | 1    | 1    | 0    | 0    | 300             |

| 0    | 1    | 1    | 0    | 1    | 325             |

| 0    | 1    | 1    | 1    | 0    | 350             |

| 0    | 1    | 1    | 1    | 1    | 375             |

| Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | VID Offset (mV) |

|------|------|------|------|------|-----------------|

| 1    | 0    | 0    | 0    | 0    | 400             |

| 1    | 0    | 0    | 0    | 1    | 425             |

| 1    | 0    | 0    | 1    | 0    | 450             |

| 1    | 0    | 0    | 1    | 1    | 475             |

| 1    | 0    | 1    | 0    | 0    | 500             |

| 1    | 0    | 1    | 0    | 1    | 525             |

| 1    | 0    | 1    | 1    | 0    | 550             |

| 1    | 0    | 1    | 1    | 1    | 575             |

| 1    | 1    | 0    | 0    | 0    | 600             |

| 1    | 1    | 0    | 0    | 1    | 625             |

| 1    | 1    | 0    | 1    | 0    | 650             |

| 1    | 1    | 0    | 1    | 1    | 675             |

| 1    | 1    | 1    | 0    | 0    | 700             |

| 1    | 1    | 1    | 0    | 1    | 725             |

| 1    | 1    | 1    | 1    | 0    | 750             |

| 1    | 1    | 1    | 1    | 1    | 800             |

#### All brandname or trademark belong to their owner respectively

DS8801B-04 August 2007

#### 0x01 Core Current. Default 0x00 (read only). The core current full scale is over current trigger point.

Bit6-0 : Show core voltage current.

#### 0x03 MISC. Default 0x04.

- Bit2 : Slot\_OCC Detection. This bit be written clear and only can be written 0.

- 0: Normal 1: Slot\_OCC ever be pulled high

- Bit1 : The reset pin ever be pull low when bit0 = 1 and only can be written 0. 0 : Never issue reset 1 : Ever issue reset

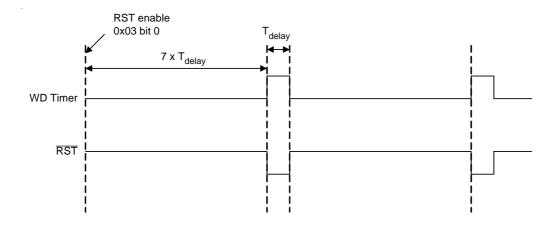

- Bit0 : Reset control. When this bit be write 1, the Watching Dog timer (Reset pin) will repeat counter 1400ms then pull low 200ms.Reset pin be pull low, if this bit = 1 will reset all registers to default exception MISC(Index 0x03).

- Sheet4U.com: Disable 1: Enable

- Note : If SLOT\_OCC pin = 1 reset all registers value to default.

#### Product information registers (Read Only)

0x13 Revision\_ID 0x00

Preliminary

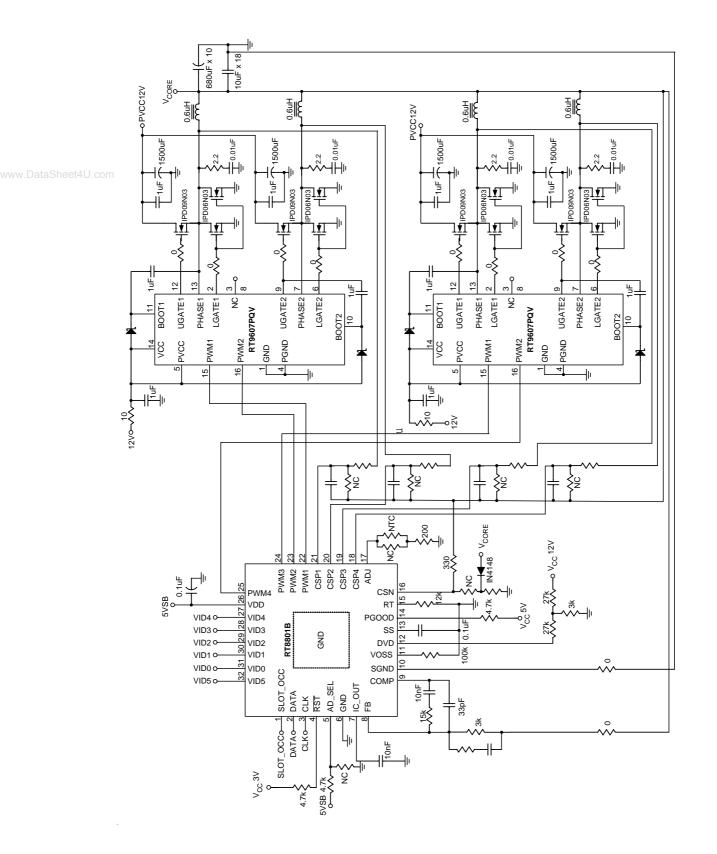

## **Typical Application Circuit**

# Functional Pin Description SLOT\_OCC (Pin 1)

CPU socket occupied; the signal is defined to indicate if the CPU has been changed/ removed and it will reset all chip. There is one register implemented for the status indication. The register will be reset when the  $V_{DD}$  power removed or CPU changed/removed. The pin is implemented as an input, TTL level, and active-low signal.

#### DATA (Pin 2), CLK (Pin 3)

2-wires programming interface.

#### RST (Pin 4)

This pin be pull low (the Watching Dog = Low), it will reset some register, when 0x03 bit 0 be setting.

#### AD\_SEL (Pin 5)

The pin select series bus address. Pin =1,Address = 0x5E & Pin = 0, Address = 0x5C.

#### GND (Pin 6)

Chip power ground.

#### IC\_OUT (Pin 7)

The pin is defined as a reference current output. A capacitor is attached to set the default Watching Dog low pluse time. Write the index 0x03 bit0 = 1 delay 7 times  $T_{delay}$  time then issue  $T_{delay}$  low pluse,

where  $T_{delay} = \frac{C_{OUT}}{I_{COUT}} \times V_{COUT}$

#### FB (Pin 8)

The pin is defined as an inverting input of internal error amplifier.

#### COMP (Pin 9)

The pin is defined as an output of the error amplifier and an input of the PWM comparator.

#### SGND (Pin 10)

Difference ground sense of  $V_{\text{CORE}}.$

#### VOSS (Pin 11)

$V_{\text{CORE}}$  initial value offset. Connect this pin to GND with a resistor to set the offset value.

#### DVD (Pin 12)

Hardware adjustable system power UVLO detection; input

pin; the internal trip threshold = 0.9V at  $V_{DVD}$  rising.

#### SS (Pin 13)

The pin is defined to set soft-start ramp rate; a capacitor is attached to set the start time interval. Pull this pin lower than 1.0V (ramp valley of saw-tooth wave in pulse width modulator) will shut the converter down.

#### PGOOD (Pin 14)

Power Good Indication. PGOOD is an open drain output. PGOOD will go high impedance when SS voltage greater than 3.7V and no fault occurs.

#### RT (Pin 15)

Default operation switching frequency setting. A resistor is attached to set the default operation frequency.

#### CSN (Pin 16)

The pin is defined to sense load current of CPU. The pin should be connected to the output node of choke.

#### ADJ (Pin 17)

Pin for active droop adjustment. An external resistor is attached to GND for load droop setting.

#### CSP1 (Pin 21), CSP2 (Pin 20), CSP3 (Pin 19), CSP4 (Pin 18)

Current sense inputs from the individual converter channels.

#### PWM1 (Pin 22), PWM2 (Pin 23), PWM3 (Pin 24), PWM4 (Pin 25)

PWM outputs for each phase switching drive.

#### VDD (Pin 26)

Chip powers supply. Connect this pin to a 5VSB or VCC5 supply.

#### VID4 (Pin 27), VID3 (Pin 28), VID2 (Pin 29), VID1 (Pin 30), VID0 (Pin 31), VID5 (Pin 32)

DAC voltage identification. The pins are internally pulled to 1.2V (pull high 50µA) if left open.

#### GND (Exposed Pad (33)]

The exposed pad must be soldered to a large PCB and connected to GND for maximum power dissipation.

Preliminary

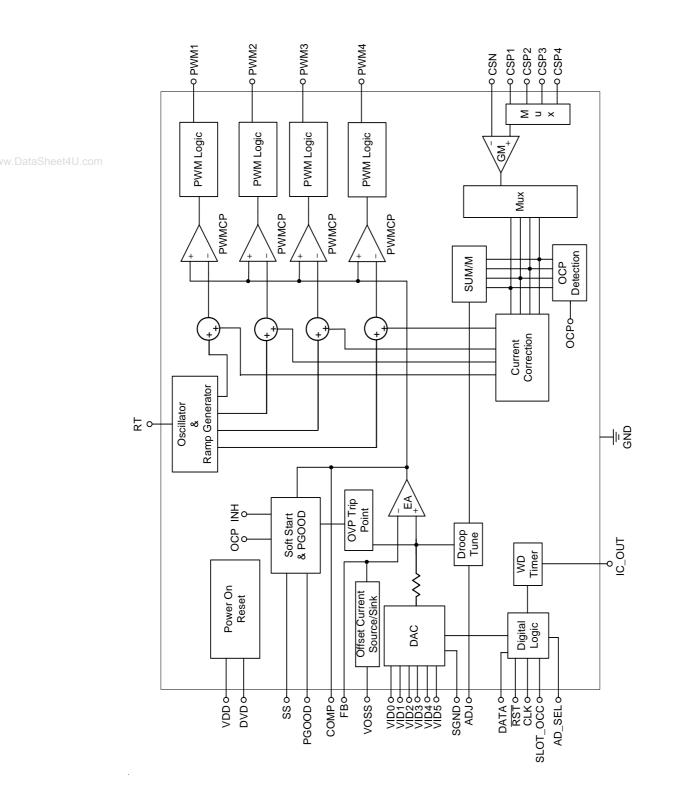

## **Function Block Diagram**

| Table 1 | . Output | Voltage | Program |

|---------|----------|---------|---------|

|---------|----------|---------|---------|

|                     | Pin Name |      |      |      |      | Neminal Output Valtage DACOUT |

|---------------------|----------|------|------|------|------|-------------------------------|

| VID5                | VID4     | VID3 | VID2 | VID1 | VID0 | Nominal Output Voltage DACOUT |

| 0                   | 0        | 0    | 0    | 0    | 0    | 1.5500                        |

| 0                   | 0        | 0    | 0    | 0    | 1    | 1.5250                        |

| 0                   | 0        | 0    | 0    | 1    | 0    | 1.5000                        |

| 0                   | 0        | 0    | 0    | 1    | 1    | 1.4750                        |

| 0                   | 0        | 0    | 1    | 0    | 0    | 1.4500                        |

| ieet4U. <b>0</b> om | 0        | 0    | 1    | 0    | 1    | 1.4250                        |

| 0                   | 0        | 0    | 1    | 1    | 0    | 1.4000                        |

| 0                   | 0        | 0    | 1    | 1    | 1    | 1.3750                        |

| 0                   | 0        | 1    | 0    | 0    | 0    | 1.3500                        |

| 0                   | 0        | 1    | 0    | 0    | 1    | 1.3250                        |

| 0                   | 0        | 1    | 0    | 1    | 0    | 1.3000                        |

| 0                   | 0        | 1    | 0    | 1    | 1    | 1.2750                        |

| 0                   | 0        | 1    | 1    | 0    | 0    | 1.2500                        |

| 0                   | 0        | 1    | 1    | 0    | 1    | 1.2250                        |

| 0                   | 0        | 1    | 1    | 1    | 0    | 1.2000                        |

| 0                   | 0        | 1    | 1    | 1    | 1    | 1.1750                        |

| 0                   | 1        | 0    | 0    | 0    | 0    | 1.1500                        |

| 0                   | 1        | 0    | 0    | 0    | 1    | 1.1250                        |

| 0                   | 1        | 0    | 0    | 1    | 0    | 1.1000                        |

| 0                   | 1        | 0    | 0    | 1    | 1    | 1.075                         |

| 0                   | 1        | 0    | 1    | 0    | 0    | 1.050                         |

| 0                   | 1        | 0    | 1    | 0    | 1    | 1.025                         |

| 0                   | 1        | 0    | 1    | 1    | 0    | 1.0000                        |

| 0                   | 1        | 0    | 1    | 1    | 1    | 0.975                         |

| 0                   | 1        | 1    | 0    | 0    | 0    | 0.950                         |

| 0                   | 1        | 1    | 0    | 0    | 1    | 0.925                         |

| 0                   | 1        | 1    | 0    | 1    | 0    | 0.900                         |

| 0                   | 1        | 1    | 0    | 1    | 1    | 0.875                         |

| 0                   | 1        | 1    | 1    | 0    | 0    | 0.850                         |

| 0                   | 1        | 1    | 1    | 0    | 1    | 0.825                         |

| 0                   | 1        | 1    | 1    | 1    | 0    | 0.800                         |

| 0                   | 1        | 1    | 1    | 1    | 1    | 0.775                         |

| 1                   | 0        | 0    | 0    | 0    | 0    | 0.7625                        |

| 1                   | 0        | 0    | 0    | 0    | 1    | 0.7500                        |

To be continued

| Table ' | 1. | Output | Voltage | Program |

|---------|----|--------|---------|---------|

|---------|----|--------|---------|---------|

|          | Pin Name   |      |      |      |      |      |                                 |

|----------|------------|------|------|------|------|------|---------------------------------|

|          | VID5       | VID4 | VID3 | VID2 | VID1 | VID0 | - Nominal Output Voltage DACOUT |

|          | 1          | 0    | 0    | 0    | 1    | 0    | 0.7375                          |

|          | 1          | 0    | 0    | 0    | 1    | 1    | 0.7250                          |

|          | 1          | 0    | 0    | 1    | 0    | 0    | 0.7125                          |

|          | 1          | 0    | 0    | 1    | 0    | 1    | 0.7000                          |

|          | 1          | 0    | 0    | 1    | 1    | 0    | 0.6875                          |

| vw.DataS | heet4U.com | 0    | 0    | 1    | 1    | 1    | 0.6750                          |

|          | 1          | 0    | 1    | 0    | 0    | 0    | 0.6625                          |

|          | 1          | 0    | 1    | 0    | 0    | 1    | 0.6500                          |

|          | 1          | 0    | 1    | 0    | 1    | 0    | 0.6375                          |

|          | 1          | 0    | 1    | 0    | 1    | 1    | 0.6250                          |

|          | 1          | 0    | 1    | 1    | 0    | 0    | 0.6125                          |

|          | 1          | 0    | 1    | 1    | 0    | 1    | 0.6000                          |

|          | 1          | 0    | 1    | 1    | 1    | 0    | 0.5875                          |

|          | 1          | 0    | 1    | 1    | 1    | 1    | 0.5750                          |

|          | 1          | 1    | 0    | 0    | 0    | 0    | 0.5625                          |

|          | 1          | 1    | 0    | 0    | 0    | 1    | 0.5500                          |

|          | 1          | 1    | 0    | 0    | 1    | 0    | 0.5375                          |

|          | 1          | 1    | 0    | 0    | 1    | 1    | 0.5250                          |

|          | 1          | 1    | 0    | 1    | 0    | 0    | 0.5125                          |

|          | 1          | 1    | 0    | 1    | 0    | 1    | 0.5000                          |

|          | 1          | 1    | 0    | 1    | 1    | 0    | 0.4875                          |

|          | 1          | 1    | 0    | 1    | 1    | 1    | 0.4750                          |

|          | 1          | 1    | 1    | 0    | 0    | 0    | 0.4625                          |

|          | 1          | 1    | 1    | 0    | 0    | 1    | 0.4500                          |

|          | 1          | 1    | 1    | 0    | 1    | 0    | 0.4375                          |

|          | 1          | 1    | 1    | 0    | 1    | 1    | 0.4250                          |

|          | 1          | 1    | 1    | 1    | 0    | 0    | 0.4125                          |

|          | 1          | 1    | 1    | 1    | 0    | 1    | 0.4000                          |

|          | 1          | 1    | 1    | 1    | 1    | 0    | 0.3875                          |

|          | 1          | 1    | 1    | 1    | 1    | 1    | 0.3750                          |

Note: (1) 0 : Connected to GND

(2) 1 : Open

8

### Absolute Maximum Ratings (Note 1)

| Supply Voltage, V <sub>DD</sub>                | 7V                                 |

|------------------------------------------------|------------------------------------|

| Input, Output or I/O Voltage                   | GND-0.3V to V <sub>DD</sub> + 0.3V |

| • Power Dissipation, $P_D @ T_A = 25^{\circ}C$ |                                    |

| VQFN-32L 5x5                                   | 2.78W                              |

| Package Thermal Resistance (Note 4)            |                                    |

| VQFN-32L 5x5, $\theta_{JA}$                    | 36°C/W                             |

| Junction Temperature                           | 150°C                              |

| Lead Temperature (Soldering, 10 sec.)          | 260°C                              |

| ase Storage Temperature Range                  | –65°C to 150°C                     |

| ESD Susceptibility (Note 2)                    |                                    |

| HBM (Human Body Mode)                          | 2kV                                |

| MM (Machine Mode)                              | 200V                               |

| Recommended Operating Conditions (Note 3)      |                                    |

| Supply Voltage, V <sub>DD</sub> | - 5V ± 10%     |

|---------------------------------|----------------|

| Ambient Temperature Range       | - 0°C to 70°C  |

| Junction Temperature Range      | - 0°C to 125°C |

### **Electrical Characteristics**

(V<sub>DD</sub> = 5V,  $T_A = 25^{\circ}C$ , unless otherwise specified)

| Parameter                    |                    | Symbol             | Test Conditions          | Min | Тур | Max | Units |

|------------------------------|--------------------|--------------------|--------------------------|-----|-----|-----|-------|

| V <sub>DD</sub> Supply Curre | nt                 |                    |                          |     |     |     | •     |

| Nominal Supply Cu            | urrent             | I <sub>DD</sub>    | PWM 1,2,3,4 Open         |     | 12  | 16  | mA    |

| Power-On Reset               |                    |                    |                          |     |     |     |       |

| POR Threshold                |                    | V <sub>DDRTH</sub> | V <sub>DD</sub> Rising   | 4.0 | 4.2 | 4.5 | V     |

| Hysteresis                   |                    | V <sub>DDHYS</sub> |                          | 0.2 | 0.5 |     | V     |

| Value Threehold              | Trip (Low to High) | V <sub>DVDTP</sub> | Enable                   | 0.8 | 0.9 | 1.0 | V     |

| V <sub>DVD</sub> Threshold   | Hysteresis         | VDVDHYS            |                          |     | 70  |     | mV    |

| Oscillator                   |                    |                    |                          |     |     |     |       |

| Free Running Frequency       |                    | fosc               | $R_{RT} = 22.5 k\Omega$  | 250 | 300 | 350 | kHz   |

| Frequency Adjustable Range   |                    | fosc_adj           |                          | 50  |     | 400 | kHz   |

| Ramp Amplitude               |                    | ΔVosc              | $R_{RT} = 22.5 k\Omega$  |     | 1.9 |     | V     |

| Ramp Valley                  |                    | V <sub>RV</sub>    |                          | 0.7 | 1.0 |     | V     |

| Maximum On-Time              | e of Each Channel  |                    |                          | 62  | 66  | 75  | %     |

| RT Pin Voltage               |                    | V <sub>RT</sub>    | R <sub>RT</sub> = 22.5kΩ | 1.7 | 1.8 | 1.9 | V     |

| Reference and D              | AC                 |                    |                          |     |     |     |       |

|                              | Accuracy           |                    | $V_{DAC} \ge 1V$         | -1  |     | +1  | %     |

| DACOUT Voltage Accuracy      |                    | $\Delta V_{DAC}$   | V <sub>DAC</sub> < 1V    | -10 |     | +10 | mV    |

| DAC (VID0-VID5) Input Low    |                    | VILDAC             |                          |     |     | 0.8 | V     |

| DAC (VID0-VID5)              | Input High         | VIHDAC             |                          | 1.4 |     |     | V     |

| Parameter                                                   | Symbol              | Test Conditions          | Min | Тур  | Max | Units |

|-------------------------------------------------------------|---------------------|--------------------------|-----|------|-----|-------|

| Offset Voltage                                              |                     |                          | -3  |      | 3   | %     |

| VOSS Pin Voltage                                            | V <sub>VOSS</sub>   | $R_{VOSS} = 100 k\Omega$ | 1.6 | 1.7  | 1.8 | V     |

| Error Amplifier                                             | -                   | •                        |     |      |     |       |

| DC Gain                                                     |                     |                          |     | 85   |     | dB    |

| Gain-Bandwidth Product                                      | GBW                 |                          |     | 10   |     | MHz   |

| Slew Rate                                                   | SR                  | COMP = 10pF              |     | 3    |     | V/µs  |

| Current Sense GM Amplifier                                  |                     | •                        |     |      |     |       |

| CSN Full Scale Source Current                               | IISPFSS             |                          | 150 |      |     | μA    |

| CSN Current for OCP                                         |                     |                          |     | 150  |     | μA    |

| Protection                                                  |                     | •                        |     |      |     |       |

| SS Current                                                  | I <sub>SS</sub>     | $V_{SS} = 1V$            | 8   | 13   | 18  | μΑ    |

| Over-Voltage Trip $\frac{V_{SEN}}{V_{DACOUT} + V_{OFFSET}}$ | $\Delta_{OVT}$      |                          | 130 | 140  | 150 | %     |

| Delay Time                                                  | ·                   |                          | ·   |      |     |       |

| WD Timer, $T_{DL}$ ( $C_L$ = 100nF)                         |                     |                          |     | 200  |     | ms    |

| WD Timer, T <sub>DH</sub> (C <sub>L</sub> = 100nF)          |                     |                          |     | 1400 |     | ms    |

| Power Good                                                  |                     |                          |     |      |     |       |

| Output Low Voltage                                          | V <sub>PGOODL</sub> | I <sub>PGOOD</sub> = 4mA |     |      | 0.2 | V     |

**Note 1.** Stresses listed as the above "Absolute Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.

Note 2. Devices are ESD sensitive. Handling precaution recommended.

Note 3. The device is not guaranteed to function outside its operating conditions.

Note 4.  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25^{\circ}C$  on a low effective thermal conductivity test board of JEDEC 51-3 thermal measurement standard.

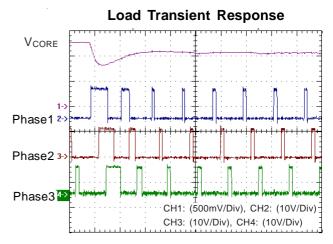

### **Typical Operating Characteristics**

Time (5µs/Div)

Time (5µs/Div)

DS8801B-04 August 2007

www.richtek.com 11

## RICHTEK

### **Application Information**

RT8801B is a multi-phase DC/DC controller that precisely regulates CPU core voltage and balances the current of different power channels. The converter consisting of RT8801B and its companion MOSFET driver RT9607/ RT9607A provides high quality CPUpower and all protection functions to meet the requirement of modern VRM.

#### Voltage Control

RT8801B senses the CPU  $V_{CORE}$  by SGND pin to sense the return of CPU to minimize the voltage drop on PCB trace at heavy load. OVP is sensed at FB pin. The internal high accuracy VID DAC provides the reference voltage for AMD K8 compliance. Control loop consists of error amplifier, multi-phase pulse width modulator, driver and power components. As conventional voltage mode PWM controller, the output voltage is locked at the V<sub>REF</sub> of error amplifier and the error signal is used as the control signal of pulse width modulator. The PWM signals of different channels are generated by comparison of EA output and split-phase sawtooth wave. Power stage transforms V<sub>IN</sub> to output by PWM signal on-time ratio.

#### **Current Balance**

RT8801B senses the inductor current via inductor's DCR for channel current balance and droop tuning. The differential sensing GM amplifier converts the voltage on the sense component (can be a sense resistor or the DCR of the inductor) to current signal into internal balance circuit.

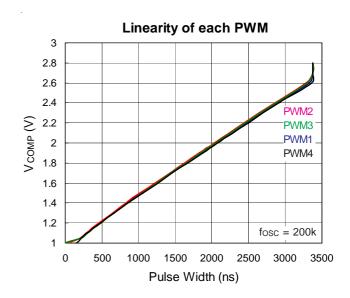

The current balance circuit sums and averages the current signals and then produces the balancing signals injected to pulse width modulator. If the current of some power channel is larger than average, the balancing signal reduces that channels pulse width to keep current balance. The use of single GM amplifier via time sharing technique to sense all inductor currents can reduce the offset errors and linearity variation between GMs. Thus it can greatly improve signal processing especially when dealing with such small signal as voltage drop across DCR.

#### Load Droop

The sensed power channel current signals regulate the reference of DAC to form an output voltage droop proportional to the load current. The droop or so call "active

voltage positioning" can reduce the output voltage ripple at load transient and the LC filter size.

#### **Fault Detection**

The chip detects FB for over voltage. The "hiccup mode" operation of over current protection is adopted to reduce the short circuit current. The inrush current at the start up is suppressed by the soft start circuit through clamping the pulse width and output voltage.

#### Phase Setting and Converter Start Up

RT8801B interfaces with companion MOSFET drivers (like RT9619, RT9607 series) for correct converter initialization. The tri-state PWM output (high, low and high impedance) senses its interface voltage when IC POR acts (both  $V_{DD}$  and DVD trip). The channel is enabled if the pin voltage is 1.2V less than  $V_{DD}$ . Tie the PWM to  $V_{DD}$  and the corresponding current sense pins to GND or left float if the channel is unused. For example, for 3-Channel application, connect PWM4 high.

#### **Current Sensing Setting**

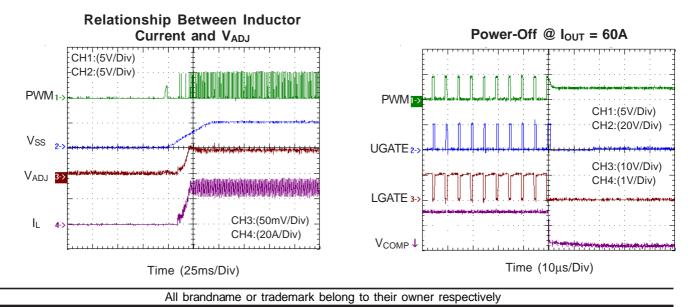

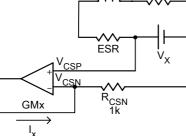

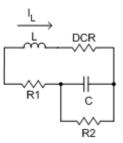

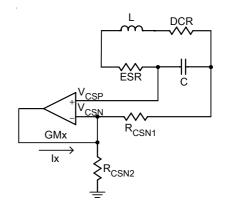

RT8801B senses the current flowing through inductor via its DCR for channel current balance and droop tuning. The differential sensing GM amplifier converts the voltage on the sense component (can be a sense resistor or the DCR of the inductor) to current signal into internal circuit (see Figure 1).

Figure 1. Current Sense Circuit

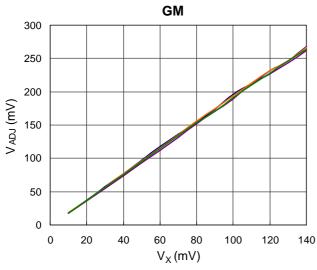

Figure 2 is the test circuit for GM. We apply test signal at GM inputs and observe its signal process output at ADJ pin. Figure 3 shows the variation of signal processing of all channels. We observe zero offsets and good linearity between phases.

Figure 3. The Linearity of GMx

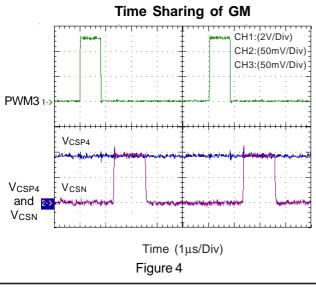

Figure 4 shows the time sharing technique of GM amplifier. We apply test signal at phase 4 and observe the waveforms at both pins of GM amplifier. The waveforms show time sharing mechanism and the perfomance of GM to hold both input pins equal when the shared time is on.

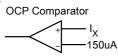

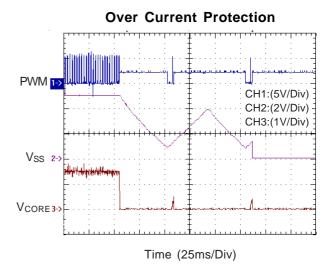

#### **Over Current Protection**

RT8801B uses an external resistor R<sub>CSN</sub> to set a programmable over current trip point. OCP comparator compares each inductor current with this reference current. RT8801B uses hiccup mode to eliminate fault detection of OCP or reduce output current when output is shorted to ground.

Figure 5. Over Current Comparator

Figure 6. Over Current Protection at steady state

#### **Current Ratio Setting**

Figure 7. Application circuit for current ratio setting

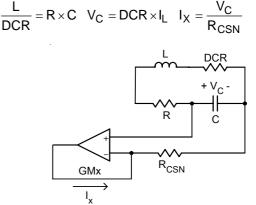

For some case with preferable current ratio instead of current balance, the corresponding technique is provided. Due to different physical environment of each channel, it is necessary to slightly adjust current loading between channels. Figure 7 shows the application circuit of GM for current ratio requirement. Applying KVL along L+DCR branch and R1+C//R2 branch:

All brandname or trademark belong to their owner respectively

14

## RICHTEK

## RT8801B

$$L\frac{dI_{L}}{dt} + DCR \times I_{L} = R_{1}(\frac{V_{C}}{R_{2}} + C\frac{dV_{C}}{dt}) + V_{C}$$

$$= R_{1}C\frac{dV_{C}}{dt} + \frac{R_{1} + R_{2}}{R_{2}}V_{C}$$

For  $V_{C} = \frac{R2}{R_{1} + R_{2}}DCR \times I_{L}$

Look for its corresponding conditions:

$$L\frac{dI_{L}}{dt} + DCR \times I_{L} = (R1//R2) \times C \times DCR \times \frac{dI_{L}}{dt} + DCR \times I_{L}$$

Thus if

$$\frac{L}{DCR} = (R1//R2) \times C$$

Then  $V_C = \frac{R2}{R1+R2} \times DCR \times I_L$

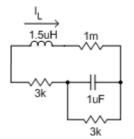

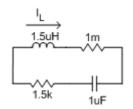

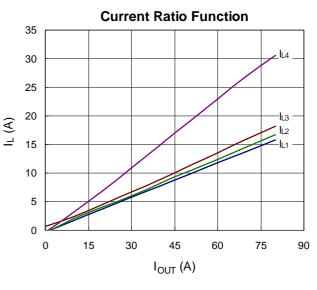

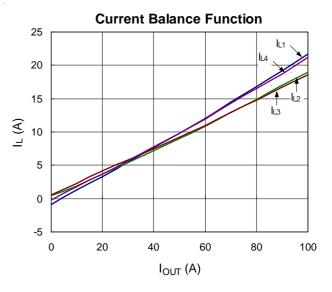

With internal current balance function, this phase would share  $(R_1+R_2)/R_2$  times current than other phases. Figure 8 & 9 show different settings for the power stages. Figure 10 shows the performance of current ratio compared with conventional current balance function in Figure 11.

Figure 8. GM4 Setting for current ratio function

Figure 9. GM1~3 Setting for current ratio function

Figure 11

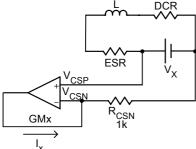

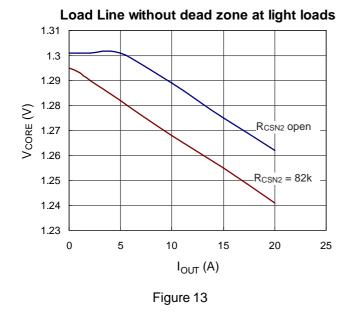

Figure 12. Application circuit of GM

For load line design, with application circuit in Figure 12, it can eliminate the dead zone of load line at light loads.

$$V_{CSP} = V_{OUT} + I_L x DCR$$

if GM holds input voltages equal, then

$$V_{CSP} = V_{CSN}$$

$$I_X = \frac{V_{CSN}}{R_{CSN2}} + \frac{I_L \times DCR}{R_{CSN1}}$$

$$= \frac{V_{OUT} + I_L \times DCR}{V_{UCON}R_{CSN2}} + \frac{I_L \times DCR}{R_{CSN1}}$$

$$= \frac{V_{OUT}}{R_{CSN2}} + \frac{I_{L} \times DCR}{R_{CSN2}} + \frac{I_{L} \times DCR}{R_{CSN1}}$$

For the lack of sinking capability of GM, R<sub>CSN2</sub> should be small enough to compensate the negative inductor valley current especially at light loads.

$$\frac{V_{CSN}}{R_{CSN2}} \geq \left| \frac{I_L \times DCR}{R_{CSN1}} \right|$$

Assume the negative inductor valley current is –5A at no load, then for

$R_{CSN1}=330\Omega,\ R_{ADJ}=160\Omega,\ V_{OUT}=1.300V$

$$\frac{1.3V}{R_{CSN2}} \ge \frac{-5A \times 1m\Omega}{330\Omega}$$

$R_{CSN2} \leq 85.8 k \Omega$

Choose  $R_{CSN2} = 82k\Omega$

#### VID on the Fly

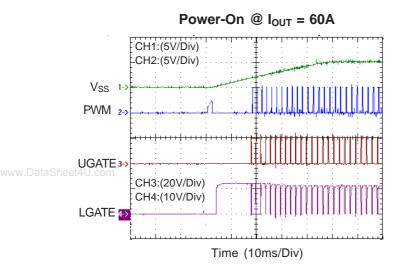

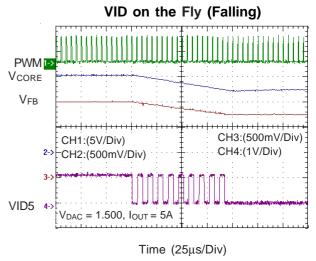

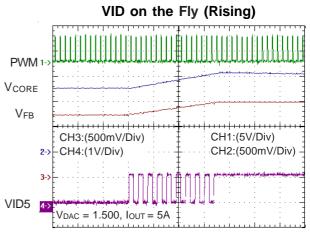

With external pull up resistors tied to VID pins, RT8801B converters different VID codes from CPU into output voltage. Figure 14 and Figure 15 show the waveforms of VID on the fly function.

Figure 14

Time (25µs/Div)

Figure 15

RICHTEK

## RT8801B

#### **Output Voltage Offset Function**

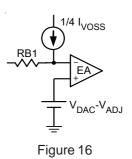

To meet Intel<sup>®</sup> requirement of initial offset of load line, RT8801B provides programmable initial offset function. External resistor  $R_{VOSS}$  and voltage source at VOSS pin generate offset currentl<sub>VOSS</sub> =  $\frac{V_{VOSS}}{R_{VOSS}}$ .

One quarter of  $I_{VOSS}$  flows through RB1 as shown in Figure 16. Error amplifier would hold the inverting pin equal to  $V_{DAC} - V_{ADJ}$ . Thus output voltage is subtracted from  $V_{DAC}$ -  $V_{ADJ}$  for a constant offset voltage.

$$V_{CORE} = V_{DAC} - V_{ADJ} - \frac{R_{FB1}}{4 \times R_{VOSS}}$$

A positive output voltage offset is possible by connecting  $R_{VOSS}$  to VDD instead of to GND. Please note that when  $R_{VOSS}$  is connected to VDD,  $V_{VOSS}$  is  $V_{DD} - 2V$  typically and half of  $I_{VOSS}$  flows through  $R_{FB1}$ .  $V_{CORE}$  is rewritten as:

$$V_{CORE} = V_{DAC} - V_{ADJ} + \frac{R_{FB1}}{R_{VOSS}}$$

#### **Error Amplifier Characteristic**

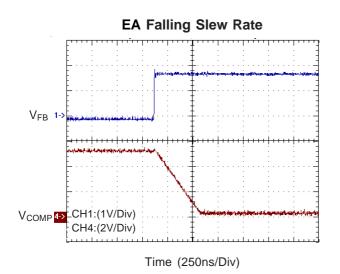

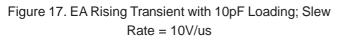

For fast response of converter to meet stringent output current transient response, RT8801B provides large slew rate capability and high gain-bandwidth performance.

Time (250ns/Div)

Figure 18. EA Falling Transient with 10pF Loading; Slew Rate = 8V/us

Figure 19. Gain-Bandwidth Measurement by signal A divided by signal B

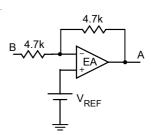

#### **PGOOD** Function

To indicate the condition of multiphase converter, RT8801 provides PGOOD signal through an open drain connection. As shown in Figure 20. PGOOD pin is externally pulled high when SS pin voltage higher than 3.7V and no fault occurs.

Figure 20

#### **Design Procedure Suggestion**

- a.Output filter pole and zero (Inductor, output capacitor value & ESR).

- b.Error amplifier compensation & sawtooth wave amplitude (compensation network).

- c.Kelvin sense for  $V_{\text{CORE}}.$

#### **Current Loop Setting**

GM amplifier S/H current (current sense component DCR, tasCSN pin external resistor value).

#### **VRM Load Line Setting**

a. Droop amplitude (ADJ pin resistor).

b.No load offset (R<sub>CSN2</sub>)

c.DAC offset voltage setting (VOSS pin & compensation network resistor RB1).

#### Power Sequence & SS

DVD pin external resistor and SS pin capacitor.

#### PCB Layout

a.Kelvin sense for current sense GM amplifier input.

b.Refer to layout guide for other items.

#### **Voltage Loop Setting**

#### **Design Example**

#### Given:

Apply for four phase converter

$V_{IN} = 12V$

$V_{CORE} = 1.5V$

$I_{LOAD (MAX)} = 100A$

$V_{DROOP} = 100 \text{mV}$  at full load (1m $\Omega$  Load Line)

OCP trip point set at 40A for each channel (S/H)

DCR =  $1m\Omega$  of inductor at  $25^{\circ}C$

$L = 1.5 \mu H$

$C_{OUT} = 8000 \mu F$  with  $5m\Omega$  equivalent ESR.

#### 1. Compensation Setting

a. Modulator Gain, Pole and Zero :

From the following formula :

Modulator Gain =  $V_{IN}/V_{RAMP}$  = 12/1.9 = 6.3 (i.e 16dB)

where  $V_{\text{RAMP}}$  : ramp amplitude of saw-tooth wave

LC Filter Pole = 1.45kHz and

ESR Zero = 3.98kHz

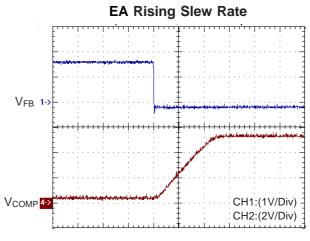

b. EA Compensation Network :

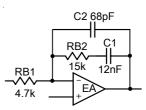

Select R1 = 4.7k, R2 = 15k, C1 = 12nF, C2 = 68pF and use the Type 2 compensation scheme shown in Figure 21. By calculation, the FZ = 0.88kHz, FP = 322kHz and Middle Band Gain is 3.19 (i.e 10.07dB).

Figure 21. Type 2 compensation network of EA

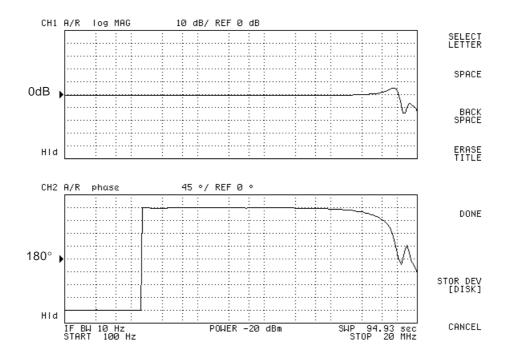

The bode plot of EA compensation is shown as Figure 22.

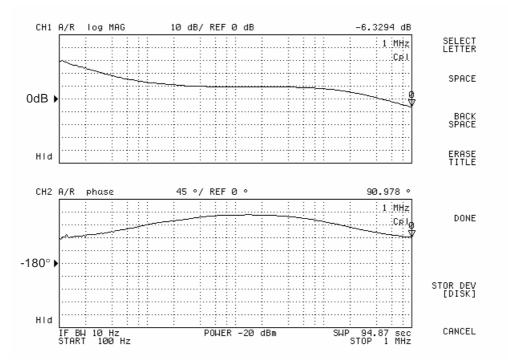

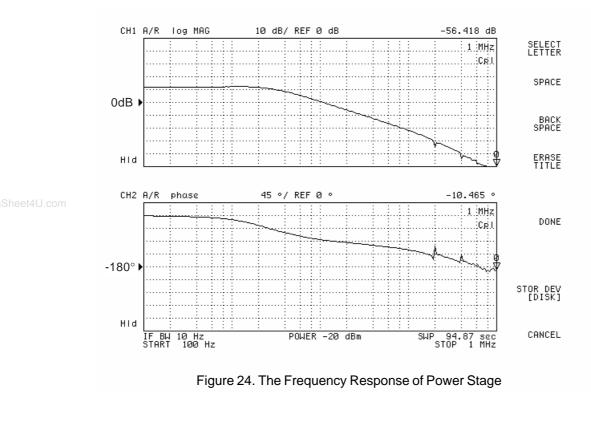

The bode plot of power stage is shown as Figure 23. The total loop gain is in Figure 24.

#### 2. Over-Current Protection Setting

Consider the temperature coefficient of copper 3900ppm/°C,

$$\frac{I_{L} \times DCR}{R_{CSN}} = 150 \,\mu A$$

$$\mathsf{R}_{\mathsf{CSN}} = \frac{40\mathsf{A} \times 1.39\mathsf{m}\Omega}{150\,\mu\mathsf{A}}$$

$R_{CSN} = 370\Omega$

#### 3. Soft-Start Capacitor Selection

For most application cases,  $0.1 \mu F$  is a good engineering value.

Figure 22. EA Frequency Response with closed loop gain set at 0db to observe gain-bandwidth product; -3dB at 10.86MHz

Figure 23. The Frequency Response of the Compensator Network

## Preliminary

## RT8801B

Figure 25. The Loop Gain of Converter

All brandname or trademark belong to their owner respectively

RICHTEK

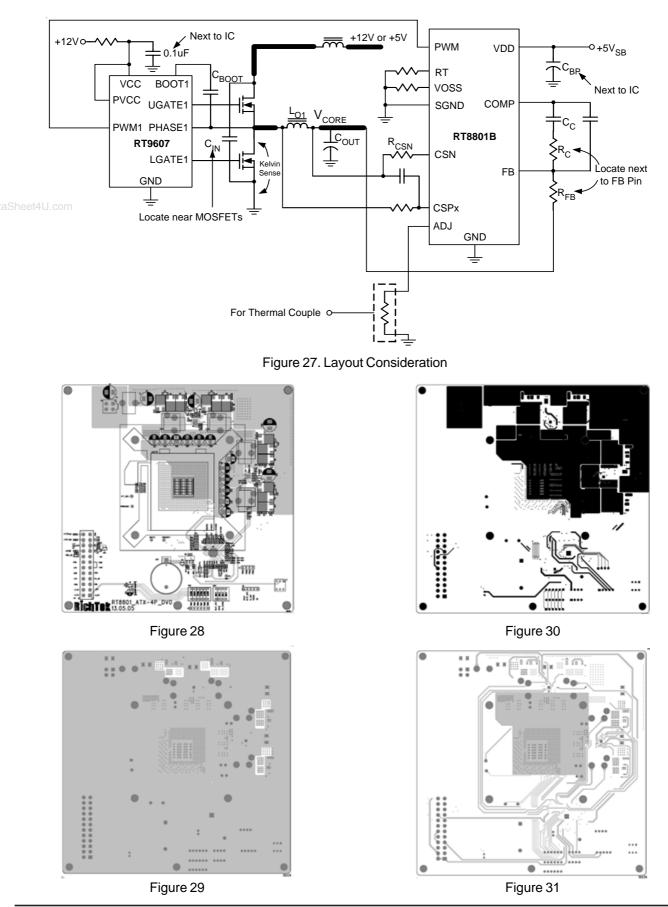

### Layout Guide

Place the high-power switching components first, and separate them from sensitive nodes.

1. Most critical path: the current sense circuit is the most sensitive part of the converter. The current sense resistors tied to CSP1,2,3,4 and CSN should be located not more than 0.5 inch from the IC and away from the noise switching nodes. The PCB trace of sense nodes should be parallel and as short as possible. Kelvin connection of the sense component (additional sense resistor or Inductor DCR) ensures the accurate stable current sensing.

### Keep well Kelvin sense to ensure the stable operation!

- 2. Switching ripple current path:

- a. Input capacitor to high side MOSFET.

- b. Low side MOSFET to output capacitor.

- c. The return path of input and output capacitor.

- d. Separate the power and signal GND.

- e. The switching nodes (the connection node of high/low side MOSFET and inductor) is the most noisy points. Keep them away from sensitive small-signal node.

- f. Reduce parasitic R, L by minimum length, enough copper thickness and avoiding of via.

- 3. MOSFET driver should be closed to MOSFET.

- 4. The compensation, bypass and other function setting components should be near the IC and away from the noisy power path.

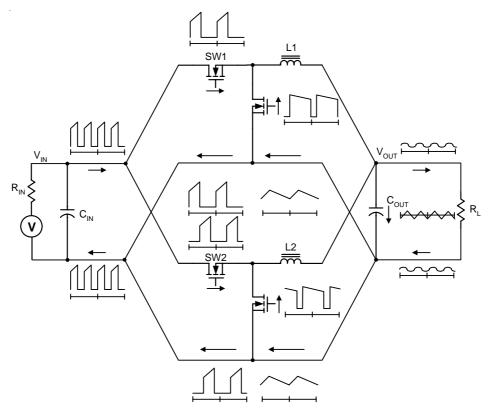

Figure 26. Power Stage Ripple Current Path

Preliminary

All brandname or trademark belong to their owner respectively

DS8801B-04 August 2007

Preliminary

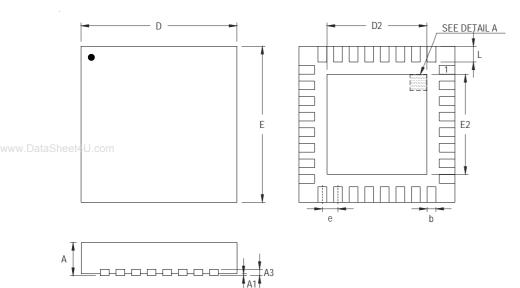

### **Outline Dimension**

#### DETAIL A Pin #1 ID and Tie Bar Mark Options

Note : The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

| Symbol | Dimensions | n Millimeters | Dimensions In Inches |       |  |

|--------|------------|---------------|----------------------|-------|--|

| Symbol | Min        | Max           | Min                  | Max   |  |

| A      | 0.800      | 1.000         | 0.031                | 0.039 |  |

| A1     | 0.000      | 0.050         | 0.000                | 0.002 |  |

| A3     | 0.175      | 0.250         | 0.007                | 0.010 |  |

| b      | 0.180      | 0.300         | 0.007                | 0.012 |  |

| D      | 4.950      | 5.050         | 0.195                | 0.199 |  |

| D2     | 3.400      | 3.750         | 0.134                | 0.148 |  |

| E      | 4.950      | 5.050         | 0.195                | 0.199 |  |

| E2     | 3.400      | 3.750         | 0.134                | 0.148 |  |

| е      | 0.5        | 0.500         |                      | )20   |  |

| L      | 0.350      | 0.450         | 0.014                | 0.018 |  |

V-Type 32L QFN 5x5 Package

#### **Richtek Technology Corporation**

Headquarter 5F, No. 20, Taiyuen Street, Chupei City Hsinchu, Taiwan, R.O.C. Tel: (8863)5526789 Fax: (8863)5526611

#### **Richtek Technology Corporation**

Taipei Office (Marketing) 8F, No. 137, Lane 235, Paochiao Road, Hsintien City Taipei County, Taiwan, R.O.C. Tel: (8862)89191466 Fax: (8862)89191465 Email: marketing@richtek.com