# RICHTEK

# Triple Channel PWM Controller with I<sup>2</sup>C Interface Control for IMVP9.2 CPU Core Power Supply

### **General Description**

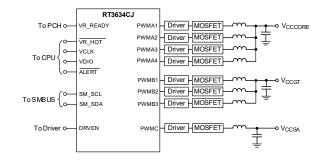

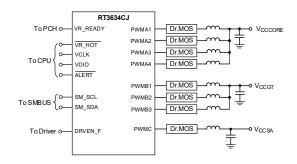

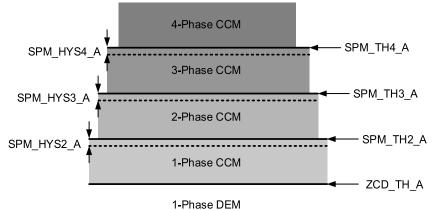

The RT3634CJ is an IMVP9.2 compliant CPU power controller which includes three voltage rails: a 4-phase synchronous buck controller for VCCCORE VR, a 3phase synchronous buck controller for VCCGT VR, and a 1-phase synchronous buck controller for VCCSA VR. The output of each rail can be configured to support the desired phase assignments up to a maximum phase count of 4 phases for VCCCORE, 3 phases for VCCGT and 1 phase for VCCSA. For example, the RT3634CJ supports output operations of 4+3+1, 4+2+1, 3+2+1, etc. The RT3634CJ adopts the Smart Phase Management (SPM) feature, to achieve maximum efficiency in all load range. Thresholds for automatic phase add/drop are user-programmable using I<sup>2</sup>C protocol interface. The RT3634CJ adopts G-NAVP<sup>TM</sup> (Green Native AVP), which is Richtek's proprietary topology derived from finite DC gain of EA amplifier with current mode control, making it easy to set the droop to meet all Intel CPU requirements of AVP (Adaptive Voltage Positioning). Based on the G-NAVP<sup>TM</sup> topology, the RT3634CJ features a new generation of quick response mechanism (Adaptive Quick Response, AQR) to optimize AVP performance during load transient and reduce output capacitors. The RT3634CJ supports mode transition function with various operating states. A serial VID (SVID) interface is built in to communicate with Intel IMVP9.2 compliant CPU. The RT3634CJ offers built-in non-volatile memory (NVM) for platform setting functions, such as ICCMAX, switching frequency or AQR trigger level. The RT3634CJ provides VR ready output signals. It also features complete fault protection functions including overvoltage (OV), overcurrent (OC), undervoltage (UV) and undervoltage lockout (UVLO). The RT3634CJ is available in the WQFN-60L 7x7 footprint package. The recommended junction temperature is -40°C to 125°C.

### Features

- Intel IMVP9.2 Compliant

- 4/3/2/1/0 Phase (VCCCORE VR) + 3/2/1/0 Phase (VCCGT VR) + 1/0 Phase (VCCSA VR) PWM Controller

- Support Multi-Source Dr.MOS

- Support Phase Doubler RT9637 for CORE Rail Up to 8-Phase Operation

- Support Application of SPS with Current Sensing by Either Current Type or Voltage Type

- Easy-Set G-NAVP<sup>™</sup> (Green Native Adaptive Voltage Positioning) Control

- 0.5% DAC Accuracy

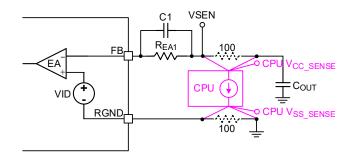

- Differential Remote Voltage Sensing

- Internal Non-Volatile Memory (NVM) to Store

Custom Configuration

- Accurate Current Balance

- Diode Emulation Mode at Light Load Condition

- Fast Transient Response-Adaptive Quick Response (AQR)

- VR Ready Indicator

- Output Current Monitor

- Protection Flag for OVP, OCP, UVP

- Support Fast V-Mode (FVM)

- Switching Frequency Setting

- Slew Rate Setting

- DVID Enhancement

- Audio Noise Suppress Function

- Zero Load-Line

- Smart Phase Management (SPM) Adjustment

- Standard I<sup>2</sup>C Protocol Interface

- Thermal Balance Adjustment

### Applications

- IMVP9.2 Intel Core Supply

- Notebook/Desktop Computer

- AVP Step-Down Converter

### **Simplified Application Circuit**

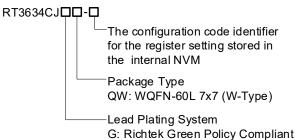

### **Ordering Information**

#### Note:

Richtek products are Richtek Green Policy compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

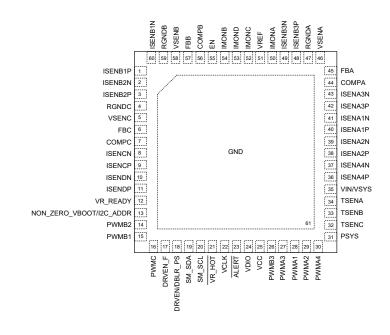

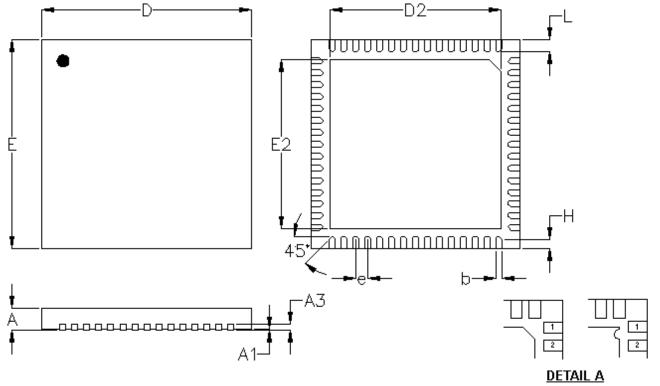

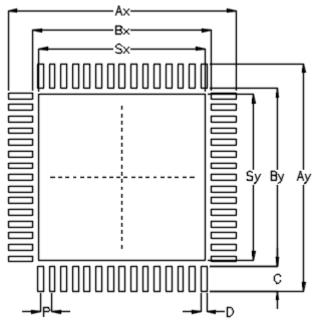

### **Pin Configuration**

**Marking Information**

RT3634CJGQW: Product Code YMDNN: Date Code

(TOP VIEW)

WQFN-60L7x7

| Copyright © 2023 Richtek Technology Corporation. All rights reserved. | RICHTEK | is a registered trademark of Richtek Technology | y Corporation. |      |

|-----------------------------------------------------------------------|---------|-------------------------------------------------|----------------|------|

| www.richtek.com                                                       |         | DS3634CJ-01                                     | November       | 2023 |

### **Functional Pin Description**

| Pin No | Pin Name                    | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | ISENB1P                     | Positive input of current-sense amplifier of phase 1 for Rail B. Connecting this pin to 5V disables Rail B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2      | ISENB2N                     | Negative input of current-sense amplifier of phase 2 for Rail B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3      | ISENB2P                     | Positive input of current-sense amplifier of phase 2 for Rail B. Connecting this pin to 5V disables phase 2 of Rail B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4      | RGNDC                       | Return ground for Rail C VR. This pin is the negative node of the differential remote voltage sensing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5      | VSENC                       | Rail C VR voltage sense input. This pin is connected to the terminal of Rail C VR output voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6      | FBC                         | Negative input of the error amplifier. This pin is for Rail C VR output voltage feedback to controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7      | COMPC                       | Rail C VR compensation. This pin is an error amplifier output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 8      | ISENCN                      | Negative input of current-sense amplifier for Rail C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9      | ISENCP                      | Positive input of current-sense amplifier for Rail C. Connecting this pin to 5V disables Rail C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 10     | ISENDN                      | Negative input of current-sense amplifier for Rail D.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 11     | ISENDP                      | Positive input of current-sense amplifier for Rail D.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 12     | VR_READY                    | VR ready indicator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 13     | NON_ZERO_VBOOT<br>/I2C_ADDR | The NON_ZERO_VBOOT/I2C_ADDR pin can enable non-zero VBOOT function, in which the default voltage is set by the SD_GD_VID register. Select the I <sup>2</sup> C slave address from 0x20 to 0x23 by connecting the resistor between this pin and GND. To enable the non-zero VBOOT for soldering check, connect the NON_ZERO_VBOOT/I2C_ADDR pin to 5V and pull the EN high. If the soldering is good, rail outputs are non-zero VBOOT. To select the I <sup>2</sup> C slave address, connect the resistor in range of 1k $\Omega$ , 20k $\Omega$ , 60.4k $\Omega$ and 121k $\Omega$ between this pin and GND for I <sup>2</sup> C slave address of 0x20, 0x21, 0x22 and 0x23 respectively. |

| 14     | PWMB2                       | PWM output of phase 2 for Rail B. The PWM tri-state level can be set from 1.16V to 2.2V by the register of 0x24.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 15     | PWMB1                       | PWM output of phase 1 for Rail B. The PWM tri-state level can be set from 1.16V to 2.2V by the register of 0x24.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 16     | PWMC                        | PWM output of Rail C. The PWM tri-state level can be set from 1.16V to 2.2V by the register of 0x24.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 17     | DRVEN_F                     | External driver mode control and the output high state is VCC. This pin will be high state when PS0~PS3 command is received and be floating state when PS4 command is received.<br>For discrete power MOSFET driver application, connecting $100k\Omega$ resister to GND is required.                                                                                                                                                                                                                                                                                                                                                                                                    |

3

www.richtek.com

| Pin No | Pin Name      | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18     | DRVEN/DBLR_PS | The DRVEN/DBLR_PS pin can be configured as driver enable pin<br>(DRVEN) or phase doubler power state pin (DBLR_PS) by the<br>configuration register.<br>As DRVEN pin for the external driver mode control, this pin will be high<br>state when PS0 to PS3 command is received and be low state when PS4<br>command is received. The output high state is VCC.<br>As DBLR_PS, which is an external driver mode control when receiving<br>PS4 command, this pin will be in high state. This pin can work with<br>RT9637 on 1 PWM drive 2 power stage. As PS0 command is received,<br>this pin will be in low state. As PS1 command is received, this pin will be<br>in floating state. As PS2/3 command is received, this pin will be in high<br>state. |

| 19     | SM_SDA        | Data line for the $I^2C$ interface. If the $I^2C$ communication is not used, connect the SM_SDA and SM_SCL pins to higher than 3.3V to achieve power saving.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 20     | SM_SCL        | Clock input for the $I^2C$ interface. If the $I^2C$ communication is not used, connect the SM_SDA and SM_SCL pins to higher than 3.3V to achieve power saving.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 21     | VR_HOT        | Thermal monitor output. (Active low).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 22     | VCLK          | Synchronous clock from the CPU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 23     | ALERT         | SVID alert. (Active low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 24     | VDIO          | VR and CPU data transmission interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 25     | VCC           | Controller power supply. Connect this pin to 5V and place a RC filter, R= $1\Omega$ and C = $4.7\mu$ F. The decoupling capacitor should be placed as close to PWM controller as possible. The recommended size of R <sub>VCC</sub> is 0603.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 26     | PWMB3         | PWM output of phase 3 for Rail B. The PWM tri-state level can be set from 1.16V to 2.2V by the register of 0x24.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 27     | PWMA3         | PWM output of phase 3 for Rail A. The PWM tri-state level can be set from 1.16V to 2.2V by the register of 0x24.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 28     | PWMA1         | PWM output of phase 1 for Rail A. The PWM tri-state level can be set from 1.16V to 2.2V by the register of 0x24.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 29     | PWMA2         | PWM output of phase 2 for Rail A. The PWM tri-state level can be set from 1.16V to 2.2V by the register of 0x24.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 30     | PWMA4         | PWM output of phase 4 for Rail A. The PWM tri-state level can be set from 1.16V to 2.2V by the register of 0x24.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

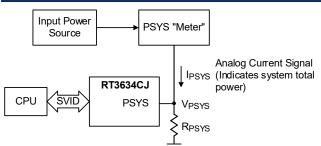

| 31     | PSYS          | System input power monitor. Place the PSYS resistor as close to the IC as possible. The PSYS function can be disabled by pulling the voltage at the PSYS pin > (VCC – $0.5V$ ). If the platform does not support PSYS function, it is recommended to connect PSYS pin to GND to avoid affecting system performance.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

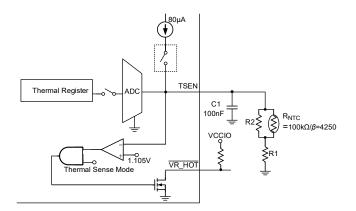

| 32     | TSENC         | Thermal sense input for Rail C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 33     | TSENB         | Thermal sense input for Rail B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 34     | TSENA         | Thermal sense input for Rail A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 35     | VIN/VSYS      | Input voltage pin. Connect a low pass filter of which time constant is at the switching frequency to this pin for setting on-time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 36     | ISENA4P       | Positive input of current-sense amplifier of phase 4 for Rail A. Connecting this pin to 5V can disable phase 4 of Rail A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

## **RT3634CJ**

| Pin No              | Pin Name | Pin Function                                                                                                                                                                                                                                                                                               |

|---------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 37                  | ISENA4N  | Negative input of current-sense amplifier of phase 4 for Rail A.                                                                                                                                                                                                                                           |

| 38                  | ISENA2P  | Positive input of current-sense amplifier of phase 2 for Rail A. Connecting this pin to 5V can disable phase 2 of Rail A.                                                                                                                                                                                  |

| 39                  | ISENA2N  | Negative input of current-sense amplifier of phase 2 for Rail A.                                                                                                                                                                                                                                           |

| 40                  | ISENA1P  | Positive input of current-sense amplifier of phase 1 for Rail A. Connecting this pin to 5V disables Rail A.                                                                                                                                                                                                |

| 41                  | ISENA1N  | Negative input of current-sense amplifier of phase 1 for Rail A.                                                                                                                                                                                                                                           |

| 42                  | ISENA3P  | Positive input of current-sense amplifier of phase 3 for Rail A. Connecting this pin to 5V can disable phase 3 of Rail A.                                                                                                                                                                                  |

| 43                  | ISENA3N  | Negative input of current-sense amplifier of phase 3 for Rail A.                                                                                                                                                                                                                                           |

| 44                  | СОМРА    | Rail A VR compensation. This pin is an error amplifier output pin.                                                                                                                                                                                                                                         |

| 45                  | FBA      | Negative input of the error amplifier. This pin is for Rail A VR output voltage feedback to controller.                                                                                                                                                                                                    |

| 46                  | VSENA    | Rail A VR voltage sense input. This pin is connected to the terminal of Rail A VR output voltage.                                                                                                                                                                                                          |

| 47                  | RGNDA    | Return ground for Rail A VR. This pin is the negative node of the differential remote voltage sensing.                                                                                                                                                                                                     |

| 48                  | ISENB3P  | Positive input of current-sense amplifier of phase 3 for Rail B. Connecting this pin to 5V can disable phase 3 of Rail B.                                                                                                                                                                                  |

| 49                  | ISENB3N  | Negative input of current-sense amplifier of phase 3 for Rail B.                                                                                                                                                                                                                                           |

| 50                  | IMONA    | Rail A VR current monitor output for controller. This pin outputs a voltage proportional to the output current.                                                                                                                                                                                            |

| 51                  | VREF     | Fixed 0.6V output reference voltage. This voltage is used to offset the output voltage of all IMON pins. When the controller shuts down or sets all rails in PS4, voltage source shuts down. An exact $0.47\mu$ F decoupling capacitor and a $3.9\Omega$ resistor must be placed between this pin and GND. |

| 52                  | IMONC    | Rail C VR current monitor output for controller. This pin outputs a voltage proportional to the output current.                                                                                                                                                                                            |

| 53                  | IMOND    | Rail D VR current monitor output for controller. This pin outputs a voltage proportional to the output current.                                                                                                                                                                                            |

| 54                  | IMONB    | Rail B VR current monitor output for controller. This pin outputs a voltage proportional to the output current.                                                                                                                                                                                            |

| 55                  | EN       | VR enable control input.                                                                                                                                                                                                                                                                                   |

| 56                  | СОМРВ    | Rail B VR compensation. This pin is an error amplifier output pin.                                                                                                                                                                                                                                         |

| 57                  | FBB      | Negative input of the error amplifier. This pin is for Rail B VR output voltage feedback to controller.                                                                                                                                                                                                    |

| 58                  | VSENB    | Rail B VR voltage sense input. This pin is connected to the terminal of Rail B VR output voltage.                                                                                                                                                                                                          |

| 59                  | RGNDB    | Return ground for Rail B VR. This pin is the negative node of the differential remote voltage sensing.                                                                                                                                                                                                     |

| 60                  | ISENB1N  | Negative input of current-sense amplifier of phase 1 for Rail B.                                                                                                                                                                                                                                           |

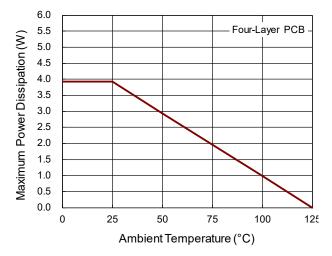

| 61<br>(Exposed Pad) | GND      | Ground. The exposed pad must be soldered to a large PCB and connected to GND for maximum power dissipation.                                                                                                                                                                                                |

Copyright © 2023 Richtek Technology Corporation. All rights reserved.

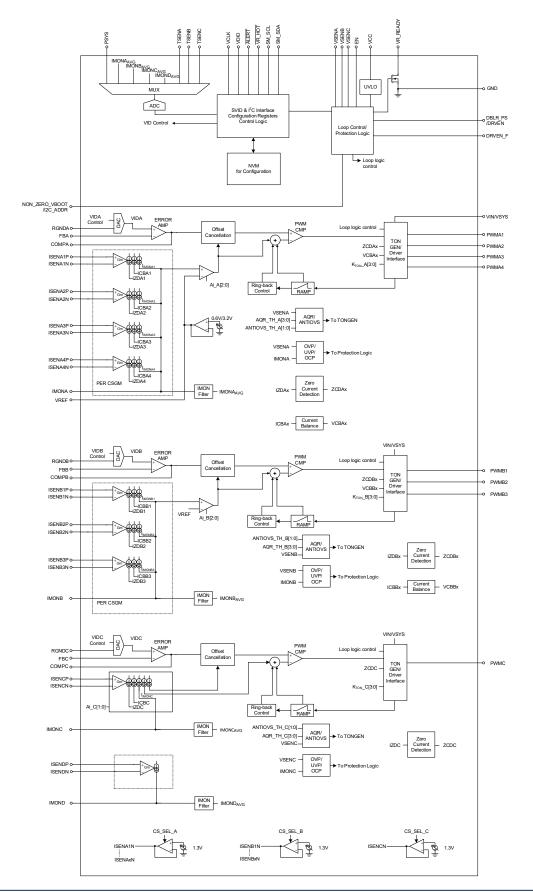

### **Functional Block Diagram**

Copyright © 2023 Richtek Technology Corporation. All rights reserved.

RICHTEK

is a registered trademark of Richtek Technology Corporation.

www.richtek.com

DS3634CJ-01

November

2023

## **RT3634CJ**

### Absolute Maximum Ratings (Note 1)

| VIN/VSYS to GND                       | 0.3V to 28V   |

|---------------------------------------|---------------|

| VCC to GND                            | 0.3V to 6.5V  |

| VDIO, VCLK, ALERT to GND              |               |

| DC                                    |               |

| < 10ns                                | 0.45V to 7.5V |

| RGNDA/B/C to GND                      | 0.3V to 0.3V  |

| Other Pins                            | 0.3V to 6.8V  |

| Lead Temperature (Soldering, 10 sec.) | 260°C         |

| Junction Temperature                  | 150°C         |

| Storage Temperature Range             | 65°C to 150°C |

### ESD Rating (Note 2)

| • + | BM ( | (Human Body | / Model) |  | 2k' | V |

|-----|------|-------------|----------|--|-----|---|

|-----|------|-------------|----------|--|-----|---|

### Recommended Operating Conditions (Note 3)

| VIN/VSYS to GND            | 4.5V to 24V   |

|----------------------------|---------------|

| Supply Input Voltage, VCC  | 4.5V to 5.5V  |

| Junction Temperature Range | 40°C to 125°C |

### Thermal Information (Note 4)

| • | WQFN-60L 7x7, θJA22    | 25.5°C/W |

|---|------------------------|----------|

| • | WQFN-60L 7x7, θJC(Top) | 13.5°C/W |

### **Electrical Characteristics**

(VCC = 5V, typical values are referenced to  $T_J = 25^{\circ}C$ , Min and Max values are referenced to  $T_J$  from  $-10^{\circ}C$  to  $105^{\circ}C$ , unless otherwise specified)

| Parameter                       | Symbol   | Test Conditions       | Min | Тур  | Мах | Unit |

|---------------------------------|----------|-----------------------|-----|------|-----|------|

| Supply Input                    | ·        | ·                     |     |      |     |      |

| Supply Voltage                  | Vcc      |                       | 4.5 | 5    | 5.5 | V    |

| Supply Current                  | lvcc     | EN = H, not switching |     | 10.7 |     | mA   |

| Supply Current at PS2<br>DACOFF | lvcc     | EN = H, not switching |     | 4.3  |     | mA   |

| Supply Current at PS3<br>DACOFF | lvcc     | EN = H, not switching |     | 1.8  |     | mA   |

| Supply Current at PS4           | IVCC_PS4 | EN = H, not switching |     | 69   |     | μA   |

| Shutdown Current                | ISHDN    | EN = L                |     | 50   |     | μA   |

| EA Amplifier                    | ·        | ·                     |     |      |     |      |

| DC Gain                         | ADC      | RL = 47kΩ             | 70  |      |     | dB   |

| Gain-Bandwidth Product          | Gвw      | CLOAD = 5pF           |     | 10   |     | MHz  |

| Para                                   | meter            | Symbol        | Test Conditions                                                                               | Min          | Тур          | Max          | Unit |

|----------------------------------------|------------------|---------------|-----------------------------------------------------------------------------------------------|--------------|--------------|--------------|------|

| Slew Rate                              |                  | SREA          | $C_{LOAD} = 10 pF$ (Gain = -4, Rf = 47k $\Omega$ , VOUT = 0.5V to 3V)                         |              | 5            |              | V/μs |

| Output Voltage                         | e Range          | VCOMP         | RL = 47kΩ                                                                                     | 0.3          |              | 3.6          | V    |

| Maximum Sou<br>Current                 | rce/Sink         | IOUTEA        | VCOMP = 2V                                                                                    |              | 5            |              | mA   |

| Current Sensi                          | ing Amplifier (I | Rail A/B/C/D) |                                                                                               |              |              |              |      |

| Impedance at                           | Positive Input   | RISENxP       |                                                                                               | 1            |              |              | MΩ   |

| CS Input Volta                         | ge               | Vcsin         | Differential voltage range of<br>DCR sense. (VCSIN = Inductor<br>current x DCR x DCR divider) | -10          |              | 80           | mV   |

| Current Sense                          | Gain Error       | Amirror       | Internal current mirror gain of<br>per phase current sense<br>IIMON/ICS,PERx                  | 1.2125       | 1.25         | 1.2875       | A/A  |

| TON Setting (                          | Rail A/B/C)      |               |                                                                                               |              |              |              |      |

| On-Time Settir                         | ng               | ton           | VIN = 19V, VID = 0.9V,<br>KTON = 2                                                            |              | 93           |              | ns   |

| Minimum Off-T                          | ime              | toff          | VID = 1V under PS1 condition                                                                  |              | 130          | 300          | ns   |

| Minimum On-T                           | ime              | ton(MIN)      |                                                                                               |              | 50           |              | ns   |

| Protections                            |                  |               |                                                                                               |              |              |              |      |

|                                        |                  | VUVLO,rise    | Rising edge                                                                                   | 4.1          |              | 4.45         | V    |

| Jndervoltage Lockout<br>Fhreshold      |                  | Vuvlo         | Falling edge                                                                                  | 3.9          |              | 4.2          | V    |

|                                        |                  | ΔVuvlo        | Rising edge hysteresis                                                                        | 100          | 170          | 250          | mV   |

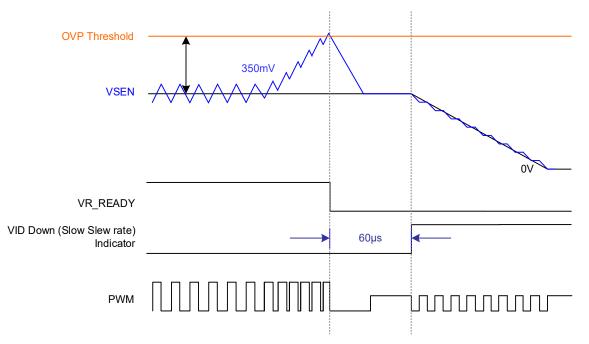

| Overvoltage P<br>Threshold             | rotection        | VROVP         | Respect to VID voltage, VID > 1V                                                              | VID +<br>320 | VID +<br>350 | VID +<br>380 | mV   |

| Theorioid                              |                  | VAOVP         | $VID \le 1V$                                                                                  | 1.3          | 1.35         | 1.4          | V    |

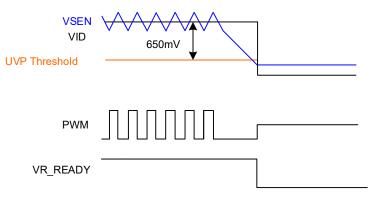

| Undervoltage I<br>Threshold            | Protection       | Vuv           | Respect to VID voltage                                                                        | -680         | -650         | -620         | mV   |

| VR Enable an                           | d VR_READY       |               |                                                                                               |              |              |              |      |

| VR EN                                  | Logic-High       | VIH_EN        |                                                                                               | 0.7          |              |              | V    |

| Threshold                              | Logic-Low        | VIL_EN        |                                                                                               |              |              | 0.3          | v    |

| Leakage Curre                          | ent of EN        | ILEAK_EN      |                                                                                               | -1           |              | 1            | μA   |

| VR_READY P<br>Voltage                  | ull Low          | VVR_READY     | IVR_READY = 10mA                                                                              |              |              | 0.13         | V    |

| Serial VID and                         | VR_HOT           |               |                                                                                               |              |              |              |      |

| VCLK, VDIO                             | Logic-High       | VIH_SVID      |                                                                                               | 0.65         |              |              | 17   |

| Input Voltage                          | Logic-Low        | VIL_SVID      |                                                                                               |              |              | 0.45         | V    |

| Leakage Curre<br>VDIO, ALERT<br>VR_HOT | -                | ILEAK_SVID    |                                                                                               | -1           |              | 1            | μA   |

Copyright © 2023 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation. www.richtek.com

| Par                                            | ameter                                         | Symbol       | Test Conditions           | Min  | Тур | Max  | Unit |

|------------------------------------------------|------------------------------------------------|--------------|---------------------------|------|-----|------|------|

|                                                |                                                | Vol_vdio     | IVDIO = 10mA              |      |     | 0.13 |      |

| Output Voltage Low of VDIO<br>/ ALERT / VR_HOT |                                                | Vol_alert    | I <sub>ALERT</sub> = 10mA |      |     | 0.13 | V    |

|                                                |                                                | VOL_VRHOT    | IVRHOT = 10mA             |      |     | 0.13 |      |

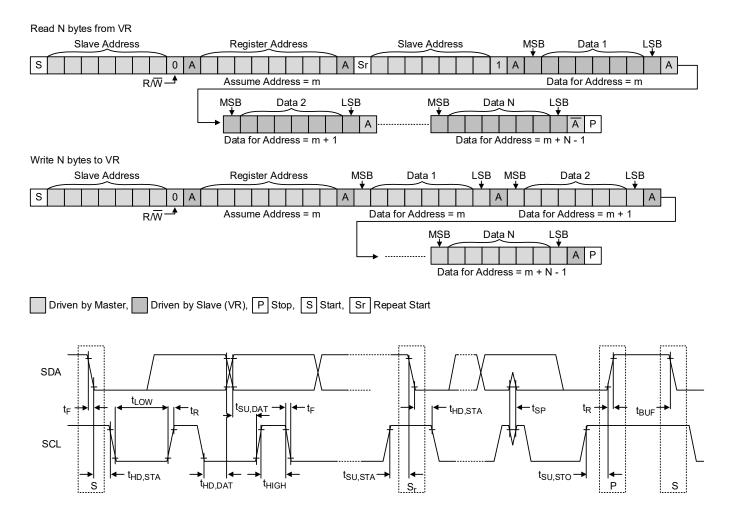

| I <sup>2</sup> C Interface                     | •                                              |              |                           |      |     |      |      |

|                                                | Logic-High                                     | VIH_I2C      |                           | 1    |     |      | V    |

| SCL, SDA                                       | SCL, SDA Logic-Low                             |              |                           |      |     | 0.6  | v    |

| Standard/Fa                                    | st Mode                                        |              |                           |      |     |      |      |

| SCL Clock R                                    | ata                                            | foot         | Standard mode             |      |     | 100  | kHz  |

| SUL CIUCK R                                    | ale                                            | fscl         | Fast mode                 |      |     | 400  | KITZ |

|                                                | epeated) Start<br>ter this period,<br>pulse is | thd_sta      |                           | 0.6  |     |      | μs   |

| Low Period C                                   | of the SCL Clock                               | tLOW         |                           | 1.3  |     |      | μs   |

| High Period (<br>Clock                         | Of the SCL                                     | tніgн        |                           | 0.6  |     |      | μs   |

| Set-Up Time<br>START Cond                      | for a Repeated<br>ition                        | tsu_sta      |                           | 0.6  |     |      | μs   |

| Data Hold Tir                                  | 20                                             | tup par      | Standard mode             | 0    |     |      |      |

| Data Hold Time                                 |                                                | thd_dat      | Fast mode                 | 0    |     | 0.9  | μs   |

| Data Set-Up                                    | Timo                                           | tou DAT      | Standard mode             | 250  |     |      | 5    |

|                                                | Time                                           | tsu_dat      | Fast mode                 | 100  |     |      | ns   |

| Set-Up Time<br>Condition                       | for STOP                                       | tsu_sto      |                           | 0.6  |     |      | μs   |

|                                                | e Between a                                    | <b>t</b> BUF |                           | 1.3  |     |      | μs   |

| Rising Time of                                 | of Both SDA and                                | to           | Standard mode             |      |     | 300  | 2    |

| SCL Signals                                    |                                                | tR           | Fast mode                 | 20   |     | 300  | ns   |

| Falling Time                                   | of Both SDA                                    | +            | Standard mode             |      |     | 300  | 2    |

| and SCL signals                                |                                                | tF           | Fast mode                 | 20   |     | 300  | ns   |

| SDA Output I<br>Current                        | _ow Sink                                       | IOL          | SDA voltage = 0.4V        | 2    |     |      | mA   |

| VREF                                           |                                                |              |                           |      |     |      |      |

| VREF Voltag                                    | e                                              | Vref         | Normal operation          | 0.59 | 0.6 | 0.61 | V    |

| VREF SPS V                                     | /oltage                                        | VREF_SPS     | Normal operation (ISEN1N) | 1.2  | 1.3 | 1.4  | V    |

#### Copyright © 2023 Richtek Technology Corporation. All rights reserved. DS3634CJ-01 November 2023

RICHTEK

| Parar                                                                                      | neter         | Symbol                               | Test Conditions                                       | Min          | Тур   | Max   | Unit    |

|--------------------------------------------------------------------------------------------|---------------|--------------------------------------|-------------------------------------------------------|--------------|-------|-------|---------|

| ADC                                                                                        |               |                                      |                                                       |              |       |       |         |

|                                                                                            |               |                                      | VIMON – VREF = 0.8V @<br>ICCMAX ≥ 80A                 |              |       |       |         |

| Digital IMON                                                                               | Rail A/B/C    | d∨imon<br>_ICCMAX                    | $V_{IMON} - V_{REF} = 0.4V$ @ 40A $\leq$ ICCMAX < 80A |              | 255   |       | Decimal |

| Set                                                                                        |               |                                      | VIMON – VREF = 0.2V @<br>ICCMAX < 40A                 |              |       |       |         |

|                                                                                            | Rail D        | dvimon<br>_ICCMAX                    | VIMON-VREF = 1.6V                                     |              | 255   |       | Decimal |

| PSYS Maximu<br>Voltage                                                                     | m Input       | PSYS                                 | VPSYS = 1.6V                                          |              | 255   |       | Decimal |

| VSYS Maximu<br>Voltage                                                                     | m Input       | VSYS                                 | VIN/VSYS = 24V                                        |              | 255   |       | Decimal |

| Average Period                                                                             | d of IMON     | timon                                |                                                       |              | 150   |       | μs      |

| Average Period                                                                             | d of TSEN     | <b>TSEN</b>                          |                                                       |              | 600   |       | μs      |

| Thermal Moni                                                                               | tor           | •                                    |                                                       |              |       |       |         |

| TSEN Voltage<br>Pull Low   ⊽R_I<br>⊽R_HOT )                                                |               |                                      | Falling                                               | 1.105        | 1.112 | 1.124 | V       |

| TSEN Voltage Threshold to<br>Pull High $\nabla R_{HOT}$ (De-<br>Asserts $\nabla R_{HOT}$ ) |               | VTSEN<br>for negative<br>temperature | Rising                                                | 1.147        | 1.154 | 1.166 | V       |

| TSEN Rises (v<br>to pull Low ALE                                                           |               | coefficient                          | ALERT = Low                                           | 1.147        | 1.154 | 1.166 | V       |

| TSEN Down (v<br>pull Low ALER                                                              | _ • • • •     |                                      | ALERT = Low                                           | 1.196        | 1.201 | 1.213 | V       |

| TSEN Voltage<br>Pull Low VR_I<br>(Asserts VR_H                                             | НОТ           |                                      | Falling                                               | 1.366        | 1.376 | 1.39  | V       |

| TSEN Voltage<br>Pull High VR_<br>(De-Asserts VF                                            | НОТ           | VTSEN for<br>positive<br>temperature | Rising                                                | 1.39         | 1.4   | 1.414 | V       |

| TSEN Ri <u>ses (\</u><br>Pull Low ALER                                                     |               | coefficient                          | ALERT = Low                                           | 1.366        | 1.376 | 1.39  | V       |

| TSEN Down <u>(\</u><br>to Pull Low Al                                                      |               |                                      | ALERT = Low                                           | 1.342        | 1.352 | 1.366 | V       |

| ITSEN                                                                                      |               |                                      |                                                       | I            |       |       |         |

| TSEN Source                                                                                | Current       | ITSEN                                | VTSEN = 1.6V                                          | 79.2         | 80    | 80.8  | μA      |

| Input Power Do                                                                             | omain Disable | Vpsys                                |                                                       | VCC<br>- 0.5 |       |       | V       |

| Voltage                                                                                    | Canability    |                                      |                                                       | 0.0          |       |       |         |

| PWM Driving                                                                                |               | Down and                             |                                                       |              | 25    |       |         |

| PWM Source F                                                                               | Resistance    | RPWM_SRC                             |                                                       |              | 25    |       | Ω       |

Copyright © 2023 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation. www.richtek.com

| Parameter              | Symbol   | Test Conditions        | Min           | Тур | Мах  | Unit |  |

|------------------------|----------|------------------------|---------------|-----|------|------|--|

| PWM Sink Resistance    | RPWM_SNK |                        |               | 10  |      | Ω    |  |

| PWM Output             |          |                        |               |     |      |      |  |

| PWMx Output High Level |          | I <sub>OUT</sub> = 4mA | VCC<br>- 0.16 |     |      | V    |  |

| PWMx Output Low Level  |          | Iout = 4mA             |               |     | 0.08 | V    |  |

**Note 1.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

Note 2. Devices are ESD sensitive. Handling precautions are recommended.

Note 3. The device is not guaranteed to function outside its operating conditions.

Note 4. For more information about thermal parameter, see the Application and Definition of Thermal Resistances report, AN061.

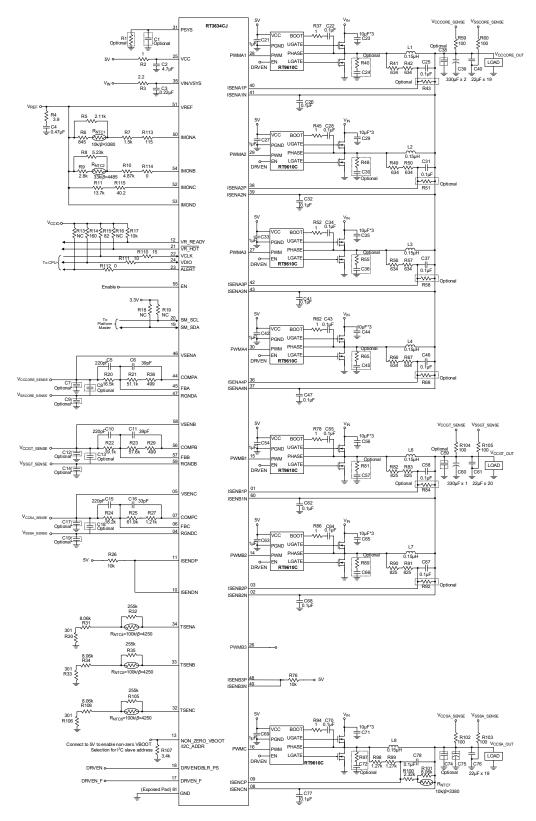

### **Typical Application Circuit**

#### Platform : MTL-H45W Performance

| $Copyright @ 2023 \ Richtek \ Technology \ Corporation. \ All \ rights \ reserved.$ |

|-------------------------------------------------------------------------------------|

| www.richtek.com                                                                     |

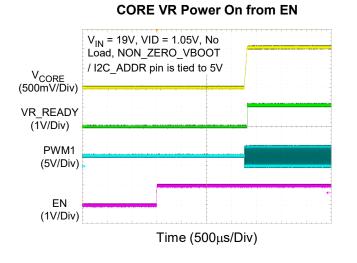

### **Typical Operating Characteristics**

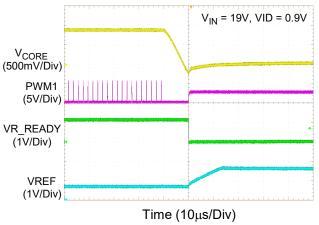

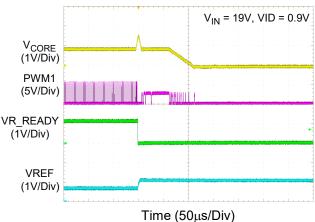

#### **CORE VR Power Off from EN** V<sub>IN</sub> = 19V, VID = 1.05V, V<sub>CORE</sub> (500mV/Div) No Load, NON\_ZERO\_VBOOT / VR READY I2C ADDR pin is tied to 5V (1V/Div) PWM1 (5V/Div) ΕN (1V/Div)

Time (50µs/Div)

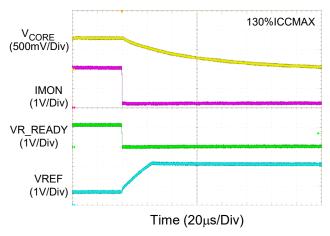

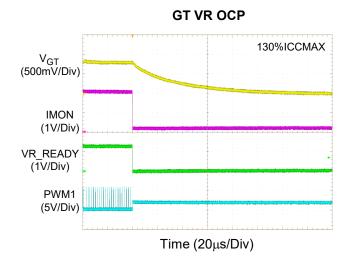

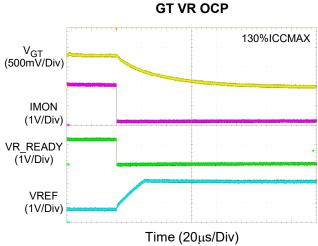

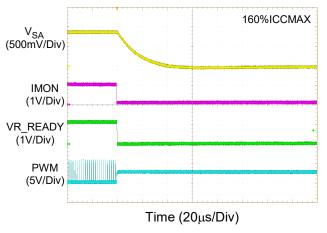

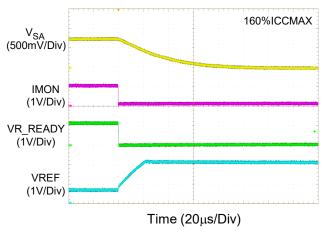

CORE VR OCP

130%ICCMAX V<sub>CORE</sub> (500mV/Div) IMON (1V/Div) VR READY (1V/Div) PWM1 (5V/Div) Time (20µs/Div)

CORE VR OCP

#### RICHTEK Copyright © 2023 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.

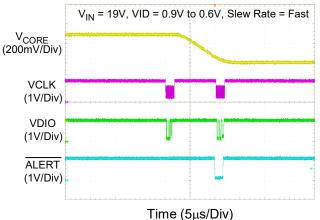

V<sub>CORE</sub> (200mV/Div)

VCLK

(1V/Div)

VDIO

ALERT

(1V/Div)

(1V/Div)

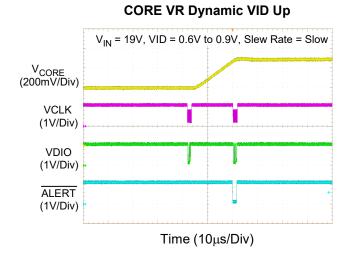

CORE VR Dynamic VID Up

V<sub>IN</sub> = 19V, VID = 0.6V to 0.9V, Slew Rate = Fast

Time (5µs/Div)

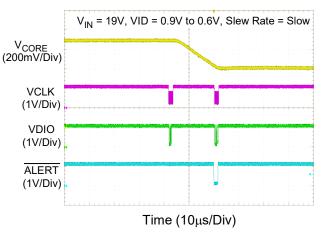

#### **CORE VR Dynamic VID Down**

**CORE VR Dynamic VID Down**

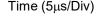

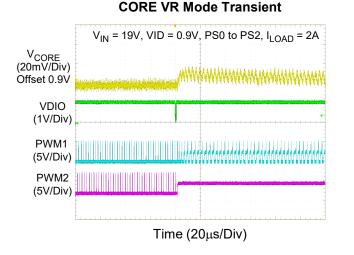

#### **CORE VR Mode Transient**

RICHTEK  $Copyright @ 2023 \ Richtek \ Technology \ Corporation. \ All \ rights \ reserved.$ is a registered trademark of Richtek Technology Corporation. www.richtek.com DS3634CJ-01

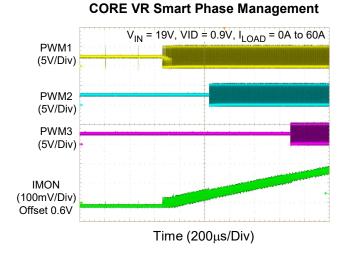

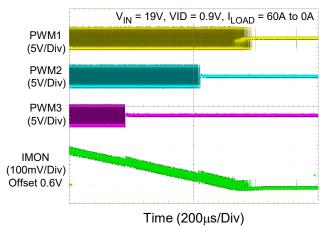

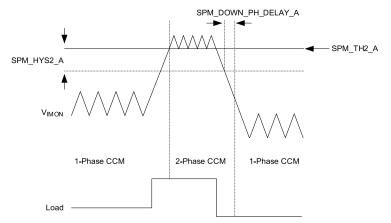

#### **CORE VR Smart Phase Management**

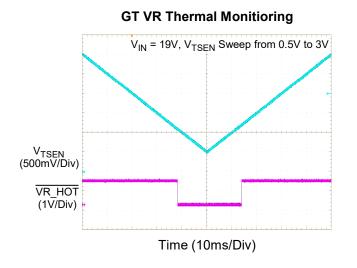

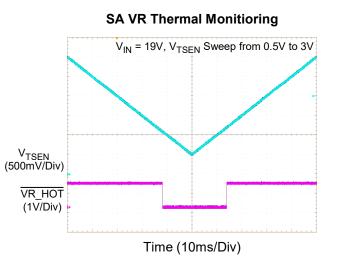

CORE VR Thermal Monitioring V<sub>IN</sub> = 19V, V<sub>TSEN</sub> Sweep from 0.5V to 3V V<sub>TSEN</sub> (500mV/Div) VR\_HOT (1V/Div) Time (10ms/Div)

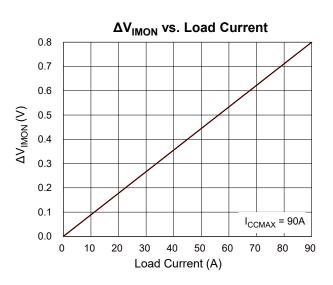

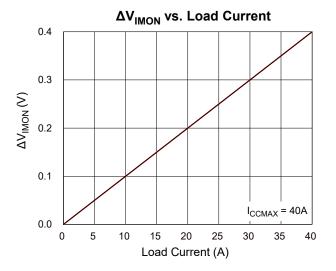

#### $\Delta V_{IMON}$ vs. Load Current 0.8 0.7 0.6 ΔV<sub>IMON</sub> (V) 0.5 0.4 0.3 0.2 0.1 $I_{CCMAX} = 180A$ 0.0 120 0 20 40 60 80 100 140 160 180 Load Current (A)

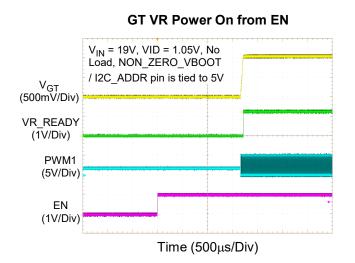

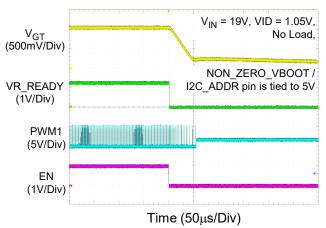

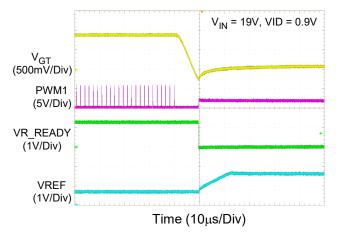

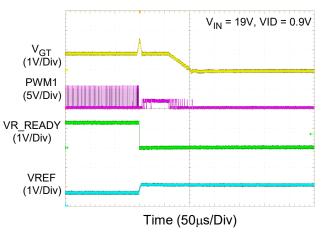

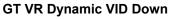

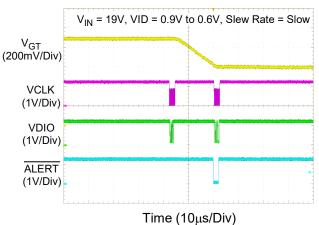

#### GT VR Power Off from EN

RICHTEK Copyright © 2023 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation. www.richtek.com DS3634CJ-01

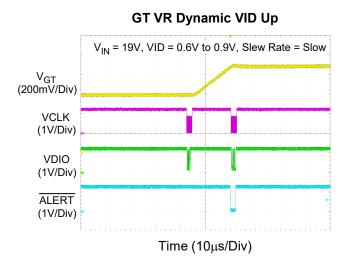

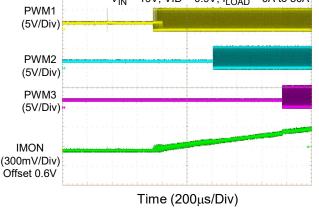

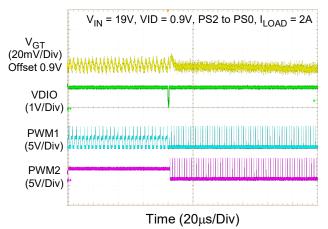

#### GT VR Mode Transient

#### GT VR Mode Transient

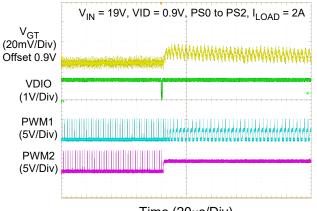

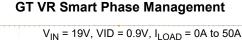

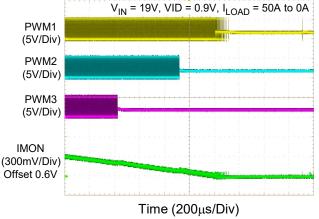

### GT VR Smart Phase Management

#### RICHTEK is a registered trademark of Richtek Technology Corporation.

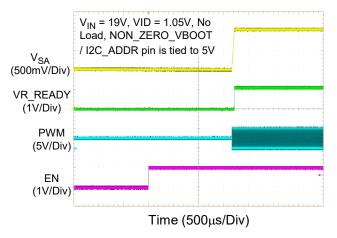

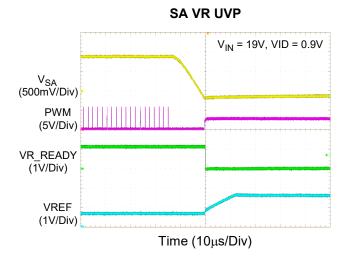

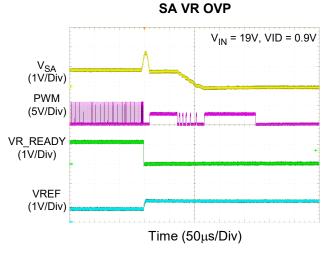

SA VR Power On from EN

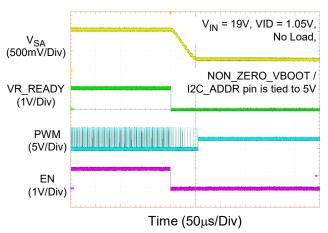

SA VR Power Off from EN

Copyright © 2023 Richtek Technology Corporation. All rights reserved.

RICHTEK

is a registered trademark of Richtek Technology Corporation.

www.richtek.com

DS3634CJ-01

November

2023

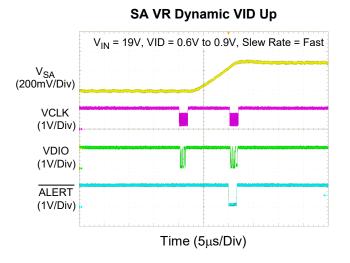

SA VR Dynamic VID Up

**RT3634CJ**

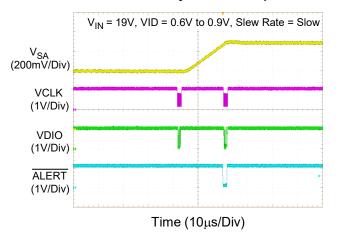

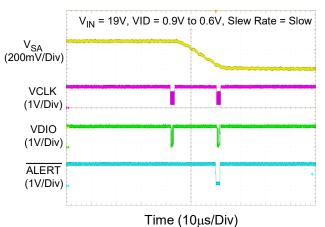

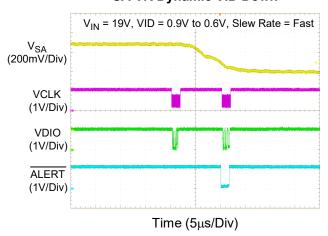

SA VR Dynamic VID Down

SA VR Dynamic VID Down

Copyright © 2023 Richtek Technology Corporation. All rights reserved.

PWM

(5V/Div)

IMON

(100mV/Div)

Offset 0.6V

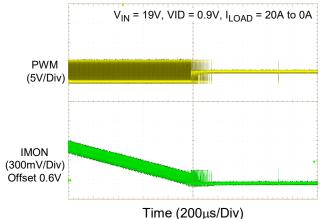

SA VR Smart Phase Management

Time (200µs/Div)

$V_{IN}$  = 19V, VID = 0.9V,  $I_{LOAD}$  = 0A to 20A

V<sub>SA</sub> (20mV/Div) Offset 0.9V VDIO (1V/Div) PWM (5V/Div) Time (50μs/Div)

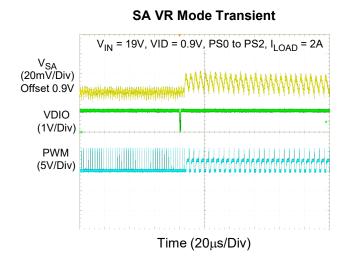

SA VR Mode Transient

SA VR Smart Phase Management

Copyright © 2023 Richtek Technology Corporation. All rights reserved.

### Operation

#### **G-NAVP<sup>TM</sup>** Control Mode

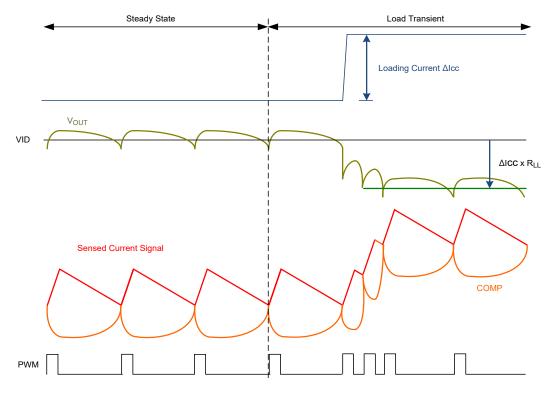

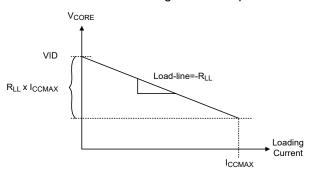

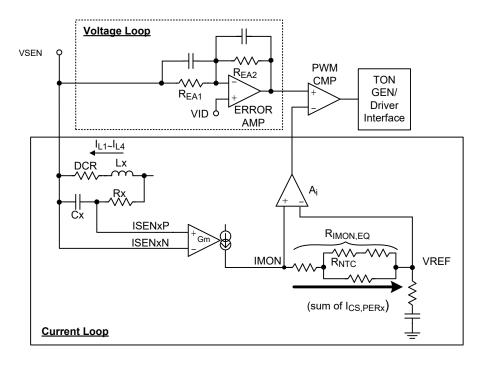

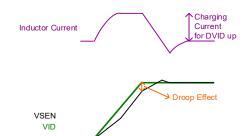

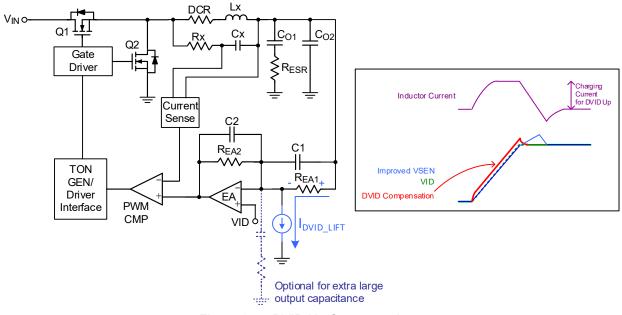

The RT3634CJ adopts G-NAVP<sup>TM</sup> (Green Native AVP), which is Richtek's proprietary topology. It is derived from current mode constant on-time control with finite DC gain of error amplifier and DC offset cancellation. The topology can achieve easy loadline design and provide high DC accuracy and fast transient response. When sensed current signal reaches sensed voltage signal, the RT3634CJ generates a PWM pulse to achieve loop modulation. Figure 1 shows the basic G-NAVP<sup>TM</sup> behavior waveforms. The COMP signal is the sensed voltage that is inverted and amplified signal of output voltage. While current loading is increasing, referring to Figure 1, COMP rises due to output voltage droop. Then rising COMP forces PWM to turn on earlier and closely. While inductor current reaches loading current, COMP enters another steady state of higher voltage, and the corresponding output voltage is in the steady state of lower voltage. The loadline, output voltage drooping by an amount proportional to loading current, is achieved.

Figure 1. G-NAVP<sup>™</sup> Behavior Waveform

## SVID Interface, Control Logic and Configuration Registers

SVID Interface receives or transmits SVID signal from/to CPU. Control Logic executes command (Read/Write registers, SetVID, SetPS) and sends related signals to control VR. Configuration Registers include function setting registers and CPU required registers.

#### **IMON Filter**

IMON Filter is used to average current signal by analog low-pass filter. It outputs IMONAVG to the MUX of ADC for current reporting.

#### MUX and ADC

The MUX supports the inputs of, TSENA, TSENB, TSENC, PSYS, IMONAAVG, IMONBAVG, IMONCAVG and IMONDAVG. The ADC converts these analog signals to digital codes for reporting or function settings.

#### UVLO

The UVLO detects the VCC voltage. As VCC exceeds threshold, controller issues POR = high and waits EN. After both POR and EN are ready, then controller is enabled.

#### Loop Control and Protection Logic

It controls power-on/off sequence, protections, power state transition, and PWM sequence.

#### DAC

The DAC generates a reference VID voltage according to the VID code sent by Control Logic. According to SetVID command, Control Logic dynamically changes VID voltage to target with required slew rate.

#### ERROR AMP

The ERROR AMP inverts and amplifies the difference between output voltage and VID with externally setting finite DC gain. The output signal is COMP for PWM trigger.

#### PER CSGM

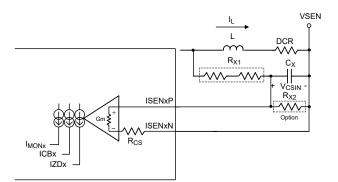

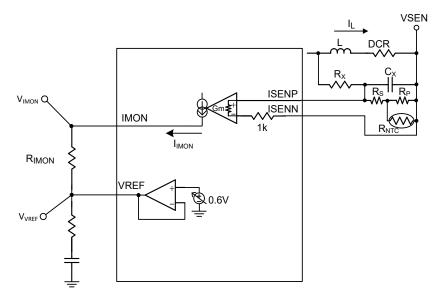

The PER CSGM senses per-phase inductor current. The outputs are used for loop response, Current Balance, Zero Current Detection, current reporting and overcurrent protection.

#### SUM CSGM

The SUM CSGM senses total inductor current with RIMON gain adjustment. SUM CSGM output current ratio can also be selected by the configuration registers. It helps wider application range of DCR and load line. SUM CSGM output is used for PWM trigger.

#### RAMP

The RAMP helps loop stability and transient response.

#### PWM CMP

The PWM comparator compares COMP signal and sum current signal based on RAMP to trigger PWM.

#### **Offset Cancellation**

The offset cancellation is based on VID, COMP voltage and current signal from SUM CSGM to control output voltage accuracy.

#### **Current Balance**

Per-phase current sense signal is compared with sensed average current. The comparison result will adjust each phase PWM width to optimize current and thermal balance.

#### **Zero Current Detection**

Detect whether each phase current crosses zero current. The result is used for DEM power saving and overshoot reduction (Anti-overshoot Function).

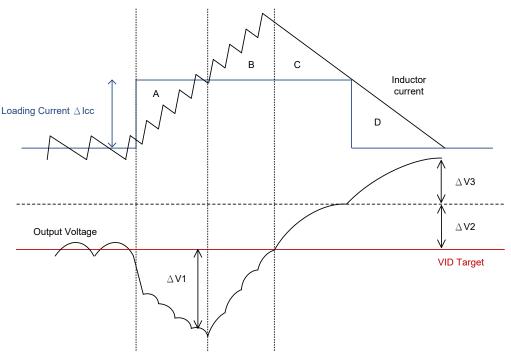

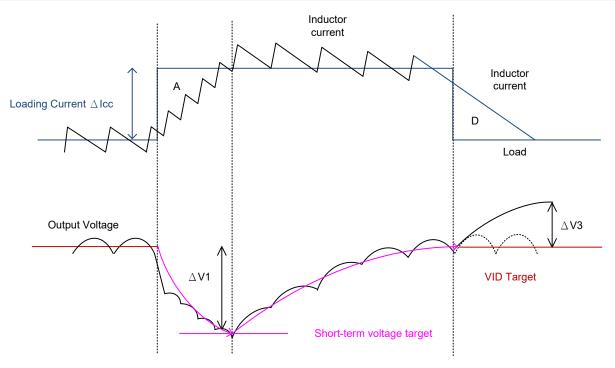

#### AQR and ANTIOVS

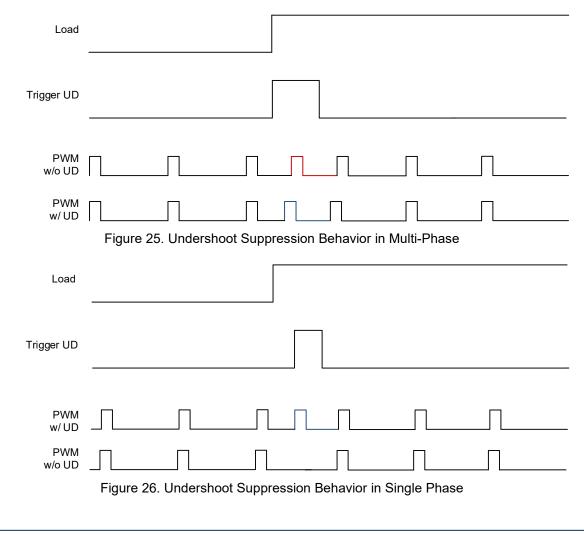

The AQR is a new generation of quick response mechanism (Adaptive Quick Response, AQR) which detects loading rising edge and allows all PWM to turn on. The PWM pulse width triggered by AQR is adaptive to loading level. The AQR trigger level can be set by the configuration registers. ANTIOVS can help overshoot reduction which detects loading falling edge and forces all PWM in tri-state until the zero current is detected.

#### **TONGEN and Driver Interface**

The PWM comparator output signal will trigger TONGEN to generate PWM pulse. The PWM sequence is controlled by Loop Control. The PWM pulse width is determined by frequency setting, current balance output and Adaptive Quick Response (AQR) settings. Once AQR is triggered, VR will allow all PWMs to turn on at the same time. Driver Interface provides high/low/tristate to drive external driver. In power saving mode, Driver Interface forces PWM in tri-state to turn off highside and low-side power MOSFETs according to Zero Current Detection output. In addition, PWM state is controlled by Protection Logic. Different protections force required PWM state.

#### OVP, UVP and OCP

Overvoltage protection/undervoltage protection/ overcurrent protection.

### **Application Information**

Richtek's component specification does not include the following information in the Application Information section. Thereby no warranty is given regarding its validity and accuracy. Customers should take responsibility to verify their own designs and reserve suitable design margin to ensure the functional suitability of their components and systems.

The RT3634CJ includes three voltage rails: a 4-phase synchronous buck controller for VCCCORE VR, a 3phase synchronous buck controller for VCCGT VR, and a 1-phase synchronous buck controller for VCCSA VR. The output of each rail can be configured to support the desired phase assignments up to a maximum phase count of 4 phases for VCCCORE, 3 phases for VCCGT and 1 phase for VCCSA. For example, output operation as a 4+3+1, 4+2+1, 3+2+1 etc, are supported. The RT3634CJ is designed to meet Intel IMVP9.2 compatible CPUs specification with a serial SVID control interface. The controller offers Multi-Time Programmable (MTP) built-in non-volatile memory (NVM) and I<sup>2</sup>C interface to store customized configuration. The RT3634CJ is used in notebook computers or desktop computers.

#### **Power-ON Sequence**

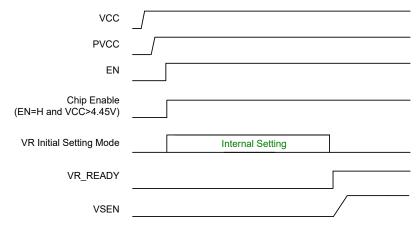

In order to confirm sufficient power supply for proper operation, the VR triggers UVLO if VCC voltage drops below 4.2V (max). UVLO protection shuts down controller and forces high-side MOSFET and low-side MOSFET off. When VCC > 4.45V (max), RT3634CJ issues POR = high and waits for EN signal. After POR = high and EN > 0.7V, controller powers on (Chip Enable = H) and starts VR internal settings, which include internal circuit offset correction and loading the data from the NVM to the configuration registers. It is suggested that the EN signal must be pulled high after the VCC is ready. Users can set multi-functions through the configuration registers by I<sup>2</sup>C interface. Figure 2 shows the typical timing of controller power-on. Driver power (PVCC) is strongly suggested to be ready after VCC. This can prevent current from flowing back to VCC from PVCC through the PWMx pin or DRVEN/DRVEN F pin.

Figure 2. Typical Timing of Controller Power-ON

## **RT3634CJ**

#### **Maximum Active Phases Number Setting**

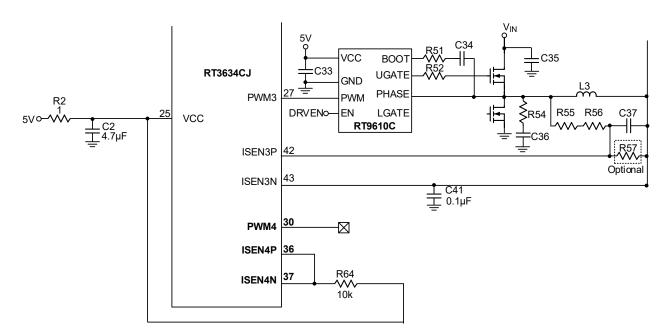

The number of active phases is determined by ISENxP voltages. The detection is only active and latched at Chip Enable rising edge (EN = H and VCC > 4.45V). While voltage at ISENxP > (VCC - 0.5V), maximum active phase number is (x-1). For example, pulling ISEN4P to VCC programs a 3-phase operation, while pulling ISEN3P to VCC programs a 2-phase operation. The unused ISENxN pins are recommended to be

connect to VCC or be floating for the application with

DCR current sensing. The unused PWMx pins are recommended to be floating. Figure 3 shows the example of the 3-phase operation in DCR current sense application. For the smart power stage (SPS) application, the unused ISENxN pins must be floating.

Figure 3. 3-Phase Operation Setting

#### Rail Disable

Pulling ISENA1P to VCC disables Rail A. It is recommended to connect the unused ISENAxN pins to VCC, and the unused PWMAx pins can be floating. Pulling ISENB1P to VCC disables Rail B. It is recommended to connect the unused ISENBxN pins to VCC, and the unused PWMBx pins can be floating. Pulling ISENCP to VCC disables Rail C. It is recommended to connect the unused ISENCN pin to VCC, and the unused PWMC pins can be floating. Pulling the unused PWMC pins can be floating. Pulling the PSYS pin to (VCC – 0.5V) disables input power domain rail D. RT3634CJ rejects any commands to the input power domain rail. It is recommended to connect the unused ISENDP pin and ISENDN pin to VCC.

#### **Acoustic Noise Suppression**

The RT3634CJ supports acoustic noise suppression function for reducing acoustic noise induced by piezoelectric effect from MLCC. As output voltage transition occurs, especially in dynamic VID, the vibrating MLCC produces acoustic noise if the vibrating frequency falls into audible band and the noise level is related to the output voltage transition amplitude  $\Delta V$ .

Therefore, the RT3634CJ adopts acoustic noise suppression function which can be enabled through the configuration register by I<sup>2</sup>C protocol interface to reduce  $\Delta V$  when SetVID down and SetVID Decay down in DEM mode.

#### **NVM Configuration Mechanism**

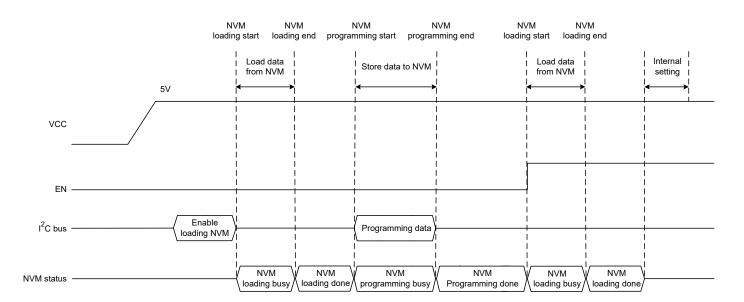

The RT3634CJ provides multiple parameters for platform setting and BOM optimization. These parameters can be set through the configuration registers via  $I^2C$ . While POR = high and enable loading NVM command is received, the VR starts loading data from the NVM to the configuration registers and function settings. Once the loading process is done, user configuration and NVM programing are available. Keep EN = L when NVM is programing. When EN > 0.7V, the VR loads the data from NVM again. After loading, VR proceeds internal setting. Figure 4 shows the simplified VR initialization and programing timing diagram. Richtek provides a Microsoft Excel-based design tool for user configuration, including unlocking, page setting and programming, etc. All setting functions are summarized in the section of Functional Register Description.

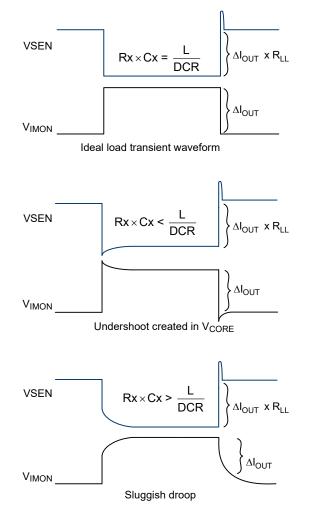

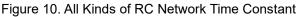

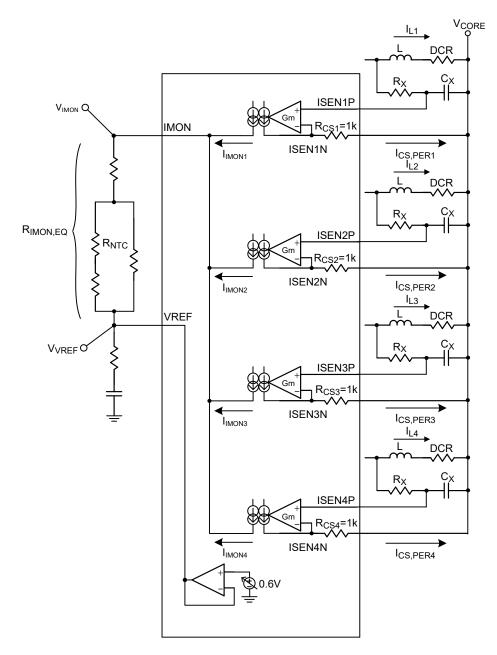

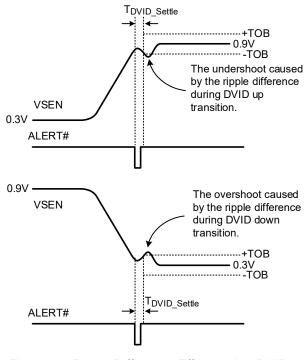

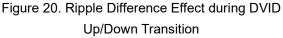

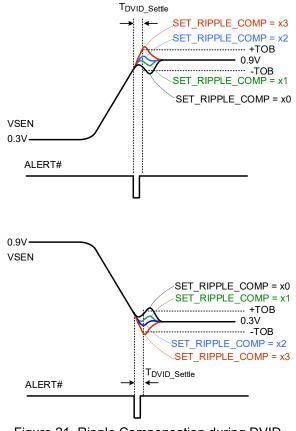

Figure 4. Simplified VR Initialization and Programing Timing Diagram