### QUAD-BAND GSM850/GSM/DCS/PCS POWER AMP MODULE

### **Typical Applications**

- 3V Quad-Band GSM Handsets

- Commercial and Consumer Systems

- Portable Battery-Powered Equipment

- GSM850, EGSM900, DCS/PCS Products

- GPRS Class 12 Compatible

### **Product Description**

The RF3133 is a high-power, high-efficiency power amplifier module with integrated power control. The device is self-contained with  $50\,\Omega$  input and output terminals. The power control function is also incorporated, eliminating the need for directional couplers, detector diodes, power control ASICs and other power control circuitry; this allows the module to be driven directly from the DAC output. The device is designed for use as the final RF amplifier in GSM850, EGSM900, DCS and PCS handheld digital cellular equipment and other applications in the 824MHz to 849MHz, 880MHz to 915MHz, 1710MHz to 1785MHz, and 1850MHz to 1910MHz bands. On-board power control provides over 37dB of control range with an analog voltage input; and, power down with a logic "low" for standby operation.

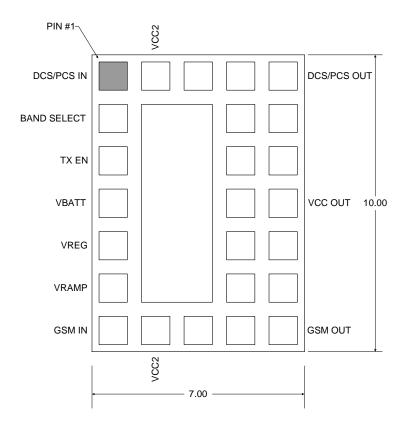

NOTES:

Shaded areas represent pin 1 location.

#### **Optimum Technology Matching® Applied**

☐ Si BJT ☐ GaAs HBT ☐ GaAs MESFET☐ Si Bi-CMOS ☐ SiGe HBT ☐ SiGe Bi-CMOS☐ InGaP/HBT ☐ GaN HEMT ☐ SiGe Bi-CMOS☐

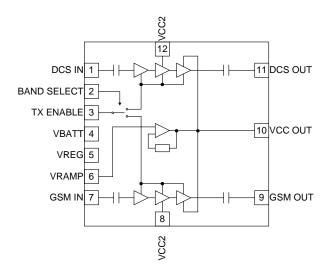

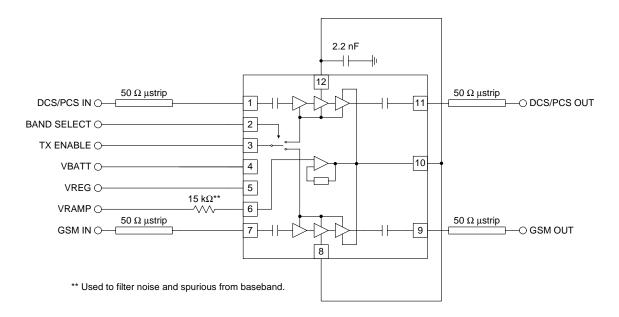

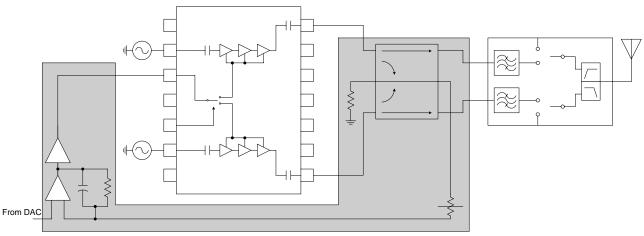

**Functional Block Diagram**

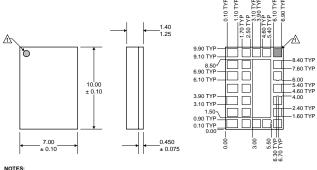

### **Package Style: Module**

### **Features**

- Complete Power Control Solution

- Single 2.9 V to 5.5 V Supply Voltage

- +35dBm GSM Output Power at 3.5V

- +33dBm DCS/PCS Output Power at 3.5V

- 55% GSM and 52% DCS/PCS η<sub>FFF</sub>

#### Ordering Information

RF3133 Quad-Band GSM850/GSM/DCS/PCS Power Amp

Module

RF3133 PCBA Fully Assembled Evaluation Board

RF Micro Devices, Inc.

Tel (336) 664 1233

7628 Thorndike Road

Fax (336) 664 0454

Greensboro, NC 27409, USA

http://www.rfmd.com

### **Absolute Maximum Ratings**

| A the country in a training or             |              |          |  |  |  |  |

|--------------------------------------------|--------------|----------|--|--|--|--|

| Parameter                                  | Rating       | Unit     |  |  |  |  |

| Supply Voltage                             | -0.3 to +6.0 | $V_{DC}$ |  |  |  |  |

| Power Control Voltage (V <sub>RAMP</sub> ) | -0.3 to +1.8 | V        |  |  |  |  |

| Input RF Power                             | +11.5        | dBm      |  |  |  |  |

| Max Duty Cycle                             | 50.0         | %        |  |  |  |  |

| Output Load VSWR                           | 10:1         |          |  |  |  |  |

| Operating Temperature                      | -20 to +85   | ℃        |  |  |  |  |

| Storage Temperature                        | -55 to +150  | ℃        |  |  |  |  |

RF Micro Devices believes the furnished information is correct and accurate at the time of this printing. However, RF Micro Devices reserves the right to make changes to its products without notice. RF Micro Devices does not assume responsibility for the use of the described product(s).

| Damamatan                           | Specification |      |      | 1124 | O and Hith and                                                |  |

|-------------------------------------|---------------|------|------|------|---------------------------------------------------------------|--|

| Parameter                           | Min.          | Тур. | Max. | Unit | Condition                                                     |  |

| Power Control V <sub>RAMP</sub>     |               |      |      |      |                                                               |  |

| Power Control "ON"                  |               |      | 1.5  | V    | Max. P <sub>OUT</sub> , Voltage supplied to the input         |  |

| Power Control "OFF"                 |               | 0.2  | 0.25 | V    | Min. P <sub>OUT</sub> , Voltage supplied to the input         |  |

| Power Control Range                 |               | 35   |      | dB   | V <sub>RAMP</sub> =0.2V to V <sub>RAMP MAX</sub>              |  |

| V <sub>RAMP</sub> Input Capacitance |               | 15   | 20   | pF   | DC to 2MHz                                                    |  |

| V <sub>RAMP</sub> Input Current     |               |      | 10   | μA   | V <sub>RAMP</sub> =V <sub>RAMP MAX</sub>                      |  |

| Turn On/Off Time                    |               |      | 2    | μS   | V <sub>RAMP</sub> =0V to V <sub>RAMP MAX</sub>                |  |

| Overall Power Supply                |               |      |      |      |                                                               |  |

| Power Supply Voltage                |               | 3.5  |      | V    | Specifications                                                |  |

|                                     | 3.0           |      | 5.5  | V    | Nominal operating limits                                      |  |

|                                     | 3.0           |      | 4.3  | V    | 50% duty cycle, Pulse width=2308μs                            |  |

| $V_{RAMP}$                          | 0.2           |      | 1.33 | V    | 50% duty cycle, 824MHz to 915MHz                              |  |

|                                     | 0.2           |      | 1.28 |      | 50% duty cycle, 1710MHz to 1910MHz                            |  |

| Power Supply Current                |               | 1    | 10   | μΑ   | P <sub>IN</sub> <-30dBm, TXEnable=Low,<br>Temp=-20°C to +85°C |  |

| V <sub>REG</sub> Voltage            | 2.7           | 2.8  | 2.9  | V    | ·                                                             |  |

| V <sub>REG</sub> Current            |               | 7    | 8    | mA   | TX Enable=High                                                |  |

| -                                   |               |      | 10   | μΑ   | TX Enable=Low                                                 |  |

| Overall Control Signals             |               |      |      |      |                                                               |  |

| Band Select "Low"                   | 0             | 0    | 0.5  | V    |                                                               |  |

| Band Select "High"                  | 1.3           | 2.0  | 3.0  | V    |                                                               |  |

| Band Select "High" Current          |               | 20   | 50   | μΑ   |                                                               |  |

| TX Enable "Low"                     | 0             | 0    | 0.5  | V    |                                                               |  |

| TX Enable "High"                    | 1.3           | 2.0  | 3.0  | V    |                                                               |  |

| TX Enable "High" Current            |               | 1    | 2    | μΑ   |                                                               |  |

Note: V<sub>RAMP</sub> Max=3/8\*V<sub>BATT</sub>+0.18≤1.5V

| Darameter                               | Specification |            | 11        | O an dition |                                                                                                                                                                 |

|-----------------------------------------|---------------|------------|-----------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                               | Min. Typ.     |            | Max. Unit |             | Condition                                                                                                                                                       |

| Overall (GSM850 Mode)                   |               |            |           |             | Temp=+25 °C, $V_{BATT}$ =3.5 V, $P_{IN}$ =+2dBm, $V_{REG}$ =2.8 V, $V_{RAMP}$ = $V_{RAMP}$ MAX, Freq=824MHz to 849MHz, 25% Duty Cycle, Pulse Width=1154 $\mu$ s |

| Operating Frequency Range               |               | 824 to 849 |           | MHz         |                                                                                                                                                                 |

| Maximum Output Power                    | +33.8         | +35.0      |           | dBm         | Temp = 25 °C, V <sub>BATT</sub> =3.5 V,                                                                                                                         |

|                                         |               |            |           |             | V <sub>RAMP</sub> =V <sub>RAMP MAX</sub>                                                                                                                        |

|                                         | +31.5         | +32.5      |           | dBm         | Temp=+85 °C, V <sub>BATT</sub> =3.0 V,                                                                                                                          |

|                                         |               |            |           |             | $V_{RAMP} = V_{RAMP MAX}$                                                                                                                                       |

| Total Current                           |               | 1.3        |           | Α           | P <sub>OUT</sub> =+31dBm                                                                                                                                        |

| Total Efficiency                        | 40            | 50         |           | %           | At P <sub>OUT MAX</sub> , V <sub>BATT</sub> =3.5V                                                                                                               |

| Input Power Range                       | 0             | +2         | +5        | dBm         | Full output power guaranteed at minimum drive level                                                                                                             |

| Output Noise Power                      |               | -86        | -82       | dBm         | RBW=100kHz, 869MHz to 879MHz,<br>$P_{OUT} \ge +5dBm$                                                                                                            |

|                                         |               | -87        | -83       | dBm         | RBW=100kHz, 879MHz to 894MHz,<br>$P_{OUT} \ge +5dBm$                                                                                                            |

| Forward Isolation 1                     |               |            | -30       | dBm         | TXEnable=Low, 0V, P <sub>IN</sub> =+5dBm                                                                                                                        |

| Forward Isolation 2                     |               |            | -2        | dBm         | TXEnable=High, P <sub>IN</sub> =+5dBm, V <sub>RAMP</sub> =0.2V                                                                                                  |

| Cross Band Isolation at 2f <sub>O</sub> |               | -18        | -13       | dBm         | V <sub>RAMP</sub> =0.2V to V <sub>RAMP MAX</sub>                                                                                                                |

| Second Harmonic                         |               | -18        | -5        | dBm         | V <sub>RAMP</sub> =0.2V to V <sub>RAMP MAX</sub>                                                                                                                |

| Third Harmonic                          |               | -28        | -15       | dBm         | V <sub>RAMP</sub> =0.2V to V <sub>RAMP MAX</sub>                                                                                                                |

| All Other Non-Harmonic Spurious         |               |            | -36       | dBm         | V <sub>RAMP</sub> =0.2V to V <sub>RAMP MAX</sub>                                                                                                                |

| Input Impedance                         |               | 50         |           | Ω           |                                                                                                                                                                 |

| Input VSWR                              |               |            | 2.5:1     |             | $V_{RAMP} = 0.2 V$ to $V_{RAMP MAX}$                                                                                                                            |

| Output Load VSWR Stability              | 8:1           |            |           |             | Spurious<-36dBm, RBW=3MHz, Set $V_{RAMP}$ where $P_{OUT} \leq 34.0$ dBm into $50\Omega$ load                                                                    |

| Output Load VSWR Ruggedness             | 10:1          |            |           |             | Set $V_{RAMP}$ where $P_{OUT} \le 34.0  dBm$ into $50 \Omega$ load. No damage or permanent degradation to part.                                                 |

| Output Load Impedance                   |               | 50         |           | Ω           | Load impedance presented at RF OUT pad                                                                                                                          |

Output Load Impedance

Note: V<sub>RAMP</sub> Max=3/8\*V<sub>BATT</sub>+0.18≤1.5V

| Parameter                              | Specification |            | Unit  | Condition |                                                                                                                                                                                                                                |

|----------------------------------------|---------------|------------|-------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                              | Min.          | Тур.       | Max.  | Unit      | Condition                                                                                                                                                                                                                      |

| Overall (EGSM900 Mode)                 |               |            |       |           | Temp=+25 °C, V <sub>BATT</sub> =3.5 V, V <sub>RAMP</sub> Max,<br>P <sub>IN</sub> =+2dBm, V <sub>RAMP</sub> =V <sub>RAMP</sub> Max,<br>V <sub>REG</sub> =2.8 V, Freq=880 MHz to 915 MHz,<br>25% Duty Cycle, Pulse Width=1154 µs |

| Operating Frequency Range              |               | 880 to 915 |       | MHz       |                                                                                                                                                                                                                                |

| Maximum Output Power                   | +34.2         | +35.0      |       | dBm       | Temp = $25$ °C, $V_{BATT}$ = $3.5$ V, $V_{RAMP}$ = $V_{RAMP}$ Max                                                                                                                                                              |

|                                        | +32.0         | +32.8      |       | dBm       | Temp=+85 °C, V <sub>BATT</sub> =3.0 V,<br>V <sub>RAMP</sub> =V <sub>RAMP</sub> Max                                                                                                                                             |

| Total Efficiency                       | 47            | 53         |       | %         | At P <sub>OUT</sub> , <sub>MAX</sub> , V <sub>BATT</sub> =3.5V                                                                                                                                                                 |

| Input Power Range                      | 0             | +2         | +5    | dBm       | SOT WARE BATT                                                                                                                                                                                                                  |

| Output Noise Power                     |               | -86        | -74   | dBm       | RBW=100kHz, 925MHz to 935MHz,<br>$P_{OUT} \ge +5dBm$                                                                                                                                                                           |

|                                        |               | -88        | -82   | dBm       | RBW=100kHz, 935MHz to 960MHz,<br>$P_{OUT} \ge +5dBm$                                                                                                                                                                           |

|                                        |               |            | -80   | dBm       | RBW=100kHz, 1805MHz to 1880MHz and 1930MHz to 1990MHz, P <sub>OUT</sub> >0dBm                                                                                                                                                  |

|                                        |               |            | -73   | dBm       | f=925MHz to 960MHz,<br>RBW=VBW=100kHz                                                                                                                                                                                          |

| Forward Isolation 1                    |               | -35        | -30   | dBm       | TX_ENABLE=0V, P <sub>IN</sub> =+5dBm                                                                                                                                                                                           |

| Forward Isolation 2                    |               |            | -2    | dBm       | TX_ENABLE=High, P <sub>IN</sub> =+5dBm,<br>V <sub>RAMP</sub> =0.2V                                                                                                                                                             |

| Crossband Isolation at 2f <sub>0</sub> |               | -28        | -20   |           | V <sub>RAMP</sub> =0.2V to V <sub>RAMP</sub> Max                                                                                                                                                                               |

| Second Harmonic                        |               | -10        | -5    | dBm       | V <sub>RAMP</sub> =0.2V to V <sub>RAMP MAX</sub>                                                                                                                                                                               |

| Third Harmonic                         |               | -21        | -15   | dBm       | V <sub>RAMP</sub> =0.2V to V <sub>RAMP MAX</sub>                                                                                                                                                                               |

| All other Non-Harmonic Spurious        |               |            | -36   | dBm       | V <sub>RAMP</sub> =0.2V to V <sub>RAMP MAX</sub>                                                                                                                                                                               |

| Input Impedance                        |               | 50         |       | Ω         | 10 4011 10 4011 10 401                                                                                                                                                                                                         |

| Input VSWR                             |               |            | 2.5:1 |           | V <sub>RAMP</sub> =0.2V to V <sub>RAMP MAX</sub>                                                                                                                                                                               |

| Output Load VSWR Stability             | 8:1           |            |       |           | Spurious<-36dBm, RBW=3MHz, Set V <sub>RAMP</sub>                                                                                                                                                                               |

|                                        |               |            |       |           | where $P_{OUT} \le 34.2 dBm$ into $50 Ω$ load                                                                                                                                                                                  |

| Output Load VSWR Ruggedness            | 10:1          |            |       |           | Set $V_{RAMP}$ where $P_{OUT} \leq 34.2 dBm$ into $50 \Omega$                                                                                                                                                                  |

|                                        |               |            |       |           | load. No damage or permanent degradation to part.                                                                                                                                                                              |

| Output Load Impedance                  |               | 50         |       | Ω         | Load impedance presented at RF OUT pad                                                                                                                                                                                         |

Note: V<sub>RAMP</sub> Max=3/8\*V<sub>BATT</sub>+0.18≤1.5V

| Doromotor                       | Specification |              | 11::4 | 0    |                                                                                                                                                                                                      |  |

|---------------------------------|---------------|--------------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parameter                       | Min.          | Тур.         | Max.  | Unit | Condition                                                                                                                                                                                            |  |

| Overall (DCS/PCS Mode)          |               |              |       |      | Temp=25°C, V <sub>BATT</sub> =3.5 V, P <sub>IN</sub> =+2dBm,<br>V <sub>REG</sub> =2.8 V, V <sub>RAMP</sub> =V <sub>RAMP</sub> Max,<br>Freq=1710MHz to 1910MHz,<br>25% Duty Cycle, Pulse Width=1154μs |  |

| Operating Frequency Range       |               | 1710 to 1910 |       | MHz  |                                                                                                                                                                                                      |  |

| Maximum Output Power            | +32.0         | +34.0        |       | dBm  | Temp=+25°C, V <sub>BATT</sub> =3.5 V, V <sub>RAMP</sub> =V <sub>RAMP</sub> Max, 1710MHz to 1785MHz                                                                                                   |  |

|                                 | +31.7         | +32.7        |       | dBm  | 1850MHz to 1910MHz                                                                                                                                                                                   |  |

|                                 | +31.0         | +31.8        |       | dBm  | Temp=+85°C, V <sub>BATT</sub> =3.0V,                                                                                                                                                                 |  |

|                                 |               |              |       |      | $V_{RAMP} = V_{RAMP} Max$ , 1710MHz to 1785MHz                                                                                                                                                       |  |

|                                 | +29.5         | +30.5        |       | dBm  | 1850MHz to 1910MHz                                                                                                                                                                                   |  |

| Total Efficiency                | 45            | 50           |       | %    | At P <sub>OUT,MAX</sub> , V <sub>BATT</sub> =3.5 V, 1710-1785 MHz                                                                                                                                    |  |

|                                 | 44            | 48           |       |      | 1850MHz to 1910MHz                                                                                                                                                                                   |  |

| Input Power Range               | 0             | +2           | +5    | dBm  |                                                                                                                                                                                                      |  |

| Output Noise Power              |               |              | -77   | dBm  | RBW=100kHz, 1805MHz to 1880MHz and 1930MHz to 1990MHz, $P_{OUT} \ge 5$ dBm,                                                                                                                          |  |

|                                 |               |              |       |      | V <sub>BATT</sub> =3.5V                                                                                                                                                                              |  |

| Forward Isolation 1             |               | -37          | -30   | dBm  | TX_ENABLE=0V, P <sub>IN</sub> =+5dBm                                                                                                                                                                 |  |

| Forward Isolation 2             |               |              | -1    | dBm  | TX_ENABLE=High, P <sub>IN</sub> =+5dBm,                                                                                                                                                              |  |

|                                 |               |              |       |      | V <sub>RAMP</sub> =0.2V                                                                                                                                                                              |  |

| Second Harmonic                 |               | -25          | -5    | dBm  | $V_{RAMP}$ =0.2V to $V_{RAMP MAX}$                                                                                                                                                                   |  |

| Third Harmonic                  |               | -30          | -15   | dBm  | $V_{RAMP}$ =0.2V to $V_{RAMP MAX}$                                                                                                                                                                   |  |

| All other Non-Harmonic Spurious |               |              | -36   | dBm  | $V_{RAMP} = 0.2 V$ to $V_{RAMP MAX}$                                                                                                                                                                 |  |

| Input Impedance                 |               | 50           |       | Ω    |                                                                                                                                                                                                      |  |

| Input VSWR                      |               | -            | 2.5   |      | $V_{RAMP}$ =0.2V to $V_{RAMP\ MAX}$                                                                                                                                                                  |  |

| Output Load VSWR Stability      | 8:1           |              |       |      | Spurious<-36dBm, RBW=3MHz, Set V <sub>RAMP</sub>                                                                                                                                                     |  |

|                                 |               |              |       |      | where $P_{OUT} \leq 32.0 dBm$ into $50\Omega$ load                                                                                                                                                   |  |

| Output Load VSWR Ruggedness     | 10:1          |              |       |      | Set $V_{RAMP}$ where $P_{OUT} \leq 32.0 dBm$ into $50 \Omega$                                                                                                                                        |  |

|                                 |               |              |       |      | load. No damage or permanent degradation to part.                                                                                                                                                    |  |

| Output Load Impedance           |               | 50           |       | Ω    | Load impedance presented at RF OUT pin                                                                                                                                                               |  |

Note: V<sub>RAMP</sub> Max=3/8\*V<sub>BATT</sub>+0.18≤1.5V

| Pin         | Function       | Description                                                                                                                                                                                                                                            | Interface Schematic |

|-------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 1           | DCS/PCS IN     | RF input to the DCS band. This is a $50\Omega$ input.                                                                                                                                                                                                  |                     |

| 2           | BAND<br>SELECT | Allows external control to select the GSM or DCS band with a logic high or low. A logic low enables the GSM band whereas a logic high enables the DCS band.                                                                                            |                     |

| 3           | TX ENABLE      | This signal enables the PA module for operation with a logic high. Once TX Enable is asserted the RF output level will increase to -2dBm.                                                                                                              |                     |

| 4           | VBATT          | Power supply for the module. This should be connected to the battery.                                                                                                                                                                                  |                     |

| 5           | VREG           | Regulated voltage input for power control function. (2.8V nom)                                                                                                                                                                                         |                     |

| 6           | VRAMP          | Ramping signal from DAC. A simple RC filter may need to be connected between the DAC output and the VRAMP input depending on the baseband selected.                                                                                                    |                     |

| 7           | GSM IN         | RF input to the GSM band. This is a $50\Omega$ input.                                                                                                                                                                                                  |                     |

| 8           | VCC2           | Controlled voltage input to driver stage for GSM bands. This voltage is part of the power control function for the module. This node must be connected to $V_{CC}$ out.                                                                                |                     |

| 9           | GSM OUT        | RF output for the GSM band. This is a $50\Omega$ output. The output load line matching is contained internal to the package.                                                                                                                           |                     |

| 10          | VCC OUT        | Controlled voltage output to feed $V_{CC2}$ . This voltage is part of the power control function for the module. It can not be connected to anything other than $V_{CC2}$ , nor can any component be placed on this node (i.e., decoupling capacitor). |                     |

| 11          | DCS/PCS<br>OUT | RF output for the DCS band. This is a $50\Omega$ output. The output load line matching is contained internal to the package.                                                                                                                           |                     |

| 12          | VCC2           | Controlled voltage input to DCS driver stage. This voltage is part of the power control function for the module. This node must be connected to $V_{\rm CC}$ out.                                                                                      |                     |

| Pkg<br>Base | GND            |                                                                                                                                                                                                                                                        |                     |

## **Pin Out**

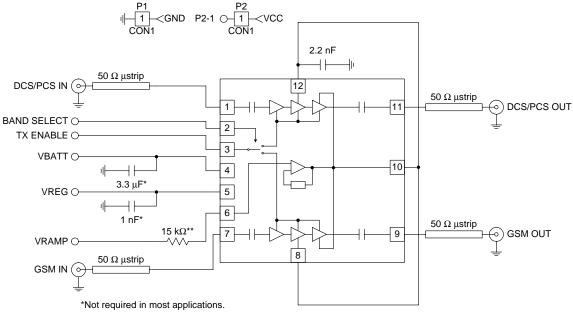

## **Application Schematic**

### **Evaluation Board Schematic**

(Download Bill of Materials from www.rfmd.com.)

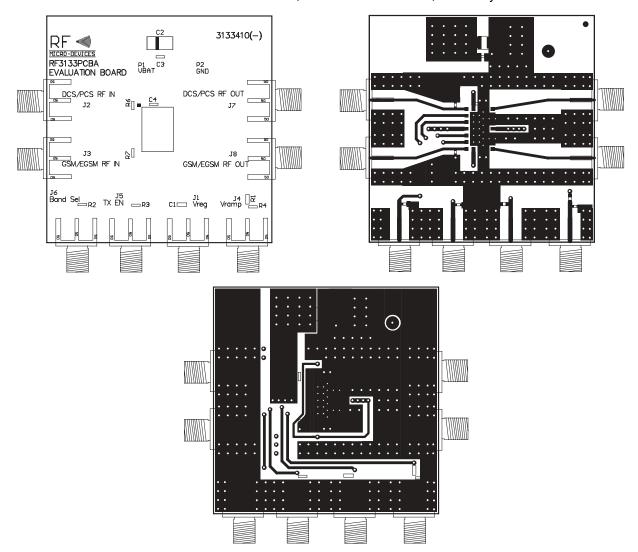

# Evaluation Board Layout Board Size 2.0" x 2.0"

Board Thickness 0.032", Board Material FR-4, Multi-Layer

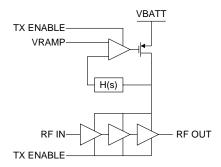

### **Theory of Operation**

#### Overview

The RF3133 is a quad-band GSM/DCS/PCS power amplifier module that incorporates an indirect closed loop method of power control. This simplifies the phone design by eliminating the need for the complicated control loop design. The indirect closed loop is fully self contained and required does not require loop optimization. It can be driven directly from the DAC output in the baseband circuit.

#### **Theory of Operation**

The indirect closed loop is essentially a closed loop method of power control that is invisible to the user. Most power control systems in GSM sense either forward power or collector/drain current. The RF3133 does not use a power detector. A high-speed control loop is incorporated to regulate the collector voltages of the amplifier while the stages are held at a constant bias. The  $V_{RAMP}$  signal is multiplied and the collector voltages are regulated to the multiplied  $V_{RAMP}$  voltage. The basic circuit is shown in the following diagram.

By regulating the power, the stages are held in saturation across all power levels. As the required output power is decreased from full power down to 0dBm, the collector voltage is also decreased. This regulation of output power is demonstrated in Equation 1 where the relationship between collector voltage and output power is shown. Although load impedance affects output power, supply fluctuations are the dominate mode of power variations. With the RF3133 regulating collector voltage, the dominant mode of power fluctuations is eliminated.

$$P_{dBm} = 10 \cdot \log \left[ \frac{(2 \cdot V_{CC} - V_{SAT})^2}{8 \cdot R_{LOAD} \cdot 10^{-3}} \right]$$

(Eq. 1)

There are several key factors to consider in the implementation of a transmitter solution for a mobile phone. Some of them are:

- Effective efficiency (η<sub>eff</sub>)

- · Current draw and system efficiency

- Power variation due to Supply Voltage

- Power variation due to frequency

- Power variation due to temperature

- Input impedance variation

- Noise power

- Loop stability

- · Loop bandwidth variations across power levels

- · Burst timing and transient spectrum trade offs

- Harmonics

Talk time and power management are key concerns in transmitter design since the power amplifier has the highest current draw in a mobile terminal. Considering only the power amplifier's efficiency does not provide a true picture for the total system efficiency. It is important to consider effective efficiency which is represented by  $\eta_{EFF}$ . ( $\eta_{EFF}$  considers the loss between the PA and antenna and is a more accurate measurement to determine how much current will be drawn in the application).  $\eta_{EFF}$  is defined by the following relationship (Equation 2):

$$\eta_{EFF} = \frac{\sum_{N=1}^{m} P_{N} - P_{IN}}{P_{DC}} \cdot 100 \tag{Eq. 2}$$

Where  $P_N$  is the sum of all positive and negative RF power,  $P_{IN}$  the input power and  $P_{DC}$  is the delivered DC power. In dB the formula becomes (Equation 3):

$$\eta_{EFF} = \frac{\frac{P_{PA} + P_{LOSS}}{10} - \frac{P_{IN}}{10}}{V_{BAT} \cdot I_{BAT} \cdot 10}$$

(Eq. 3)

Where  $P_{PA}$  is the output power from the PA,  $P_{LOSS}$  the insertion loss,  $P_{IN}$  the input power to the PA and  $P_{DC}$  the delivered DC power.

The RF3133 improves the effective efficiency by minimizing the P<sub>LOSS</sub> term in the equation. A directional coupler may introduce 0.4dB to 0.5dB loss to the transit path. To demonstrate the improvement in effective efficiency consider the following example:

#### **Conventional PA Solution:**

### **RF3133 Solution:**

The RF3133 solution improves effective efficiency 5%.

Output power does not vary due to supply voltage under normal operating conditions if  $V_{RAMP}$  is sufficiently lower than  $V_{BATT}$ . By regulating the collector voltage to the PA the voltage sensitivity is essentially eliminated. This covers most cases where the PA will be operated. However, as the battery discharges and approaches its lower power range the maximum output power from the PA will also drop slightly. In this case it is important to also decrease  $V_{RAMP}$  to prevent the power control from inducing switching transients. These transients occur as a result of the control loop slowing down and not regulating power in accordance with  $V_{RAMP}$

The switching transients due to low battery conditions are regulated by incorporating the following relationship limiting the maximum  $V_{RAMP}$  voltage (Equation 2). Although no compensation is required for typical battery conditions, the battery compensation required for extreme conditions is covered by the relationship in Equation 4. This should be added to the terminal software.

$$V_{RAMP} \le \frac{3}{8} \cdot V_{BATT} + 0.18$$

(Eq. 4)

Note: Output power is limited by battery voltage. The relationship in Equation 4 does not limit output power. Equation 4 limits the  $V_{RAMP}$  voltage to correspond with the battery voltage.

Due to reactive output matches, there are output power variations across frequency. There are a number of components that can make the effects greater or less.

The components following the power amplifier often have insertion loss variation with respect to frequency. Usually, there is some length of microstrip that follows the power amplifier. There is also a frequency response found in directional couplers due to variation in the coupling factor over frequency, as well as the sensitivity of the detector diode. Since the RF3133 does not use a directional coupler with a diode detector, these variations do not occur.

Input impedance variation is found in most GSM power amplifiers. This is due to a device phenomena where  $C_{BE}$  and  $C_{CB}$  ( $C_{GS}$  and  $C_{SG}$  for a FET) vary over the bias voltage. The same principle used to make varactors is present in the power amplifiers. The junction capacitance is a function of the bias across the junction. This produces input impedance variations as the Vapc voltage is swept. Although this could present a problem with frequency pulling the transmit VCO off frequency, most synthesizer designers use very wide loop bandwidths to quickly compensate for frequency variations due to the load variations presented to the VCO.

The RF3133 presents a very constant load to the VCO. This is because all stages of the RF3133 are run at constant bias. As a result, there is constant reactance at the base emitter and base collector junction of the input stage to the power amplifier.

Noise power in PA's where output power is controlled by changing the bias voltage is often a problem when backing off of output power. The reason is that the gain is changed in all stages and according to the noise formula (Equation 5),

$$F_{TOT} = F1 + \frac{F2 - 1}{G1} + \frac{F3 - 1}{G1 \cdot G2}$$

(Eq. 5)

the noise figure depends on noise factor and gain in all stages. Because the bias point of the RF3133 is kept constant the gain in the first stage is always high and the overall noise power is not increased when decreasing output power.

Power control loop stability often presents many challenges to transmitter design. Designing a proper power control loop involves trade-offs affecting stability, transient spectrum and burst timing.

In conventional architectures the PA gain (dB/ V) varies across different power levels, and as a result the loop bandwidth also varies. With some power amplifiers it is possible for the PA gain (control slope) to change from 100dB/V to as high as 1000dB/V. The challenge in this scenario is keeping the loop bandwidth wide enough to meet the burst mask at low slope regions which often causes instability at high slope regions.

The RF3133 loop bandwidth is determined by internal bandwidth and the RF output load and does not change with respect to power levels. This makes it easier to maintain loop stability with a high bandwidth loop since the bias voltage and collector voltage do not vary.

An often overlooked problem in PA control loops is that a delay not only decreases loop stability it also affects the burst timing when, for instance the input power from the VCO decreases (or increases) with respect to temperature or supply voltage. The burst timing then appears to shift to the right especially at low power levels. The RF3133 is insensitive to a change in input power and the burst timing is constant and requires no software compensation.

Switching transients occur when the up and down ramp of the burst is not smooth enough or suddenly changes shape. If the control slope of a PA has an inflection point within the output power range or if the slope is simply to steep it is difficult to prevent switching transients. Controlling the output power by changing the collector voltage is as earlier described based on the physical relationship between voltage swing and output power. Furthermore all stages are kept constantly biased so inflection points are nonexistent.

Harmonics are natural products of high efficiency power amplifier design. An ideal class "E" saturated power amplifier will produce a perfect square wave. Looking at the Fourier transform of a square wave reveals high harmonic content. Although this is common to all power amplifiers, there are other factors that contribute to conducted harmonic content as well. With most power control methods a peak power diode detector is used to rectify and sense forward power. Through the rectification process there is additional squaring of the waveform resulting in higher harmonics. The RF3133 address this by eliminating the need for the detector diode. Therefore the harmonics coming out of the PA should represent the maximum power of the harmonics throughout the transmit chain. This is based upon proper harmonic termination of the transmit port. The receive port termination on the T/R switch as well as the harmonic impedance from the switch itself will have an impact on harmonics. Should a problem arise, these terminations should be explored.

The RF3133 incorporates many circuits that had previously been required external to the power amplifier. The shaded area of the diagram below illustrates those components and the following table itemizes a comparison between the RF3133 Bill of Materials and a conventional solution:

| Component                      | Conventional Solution | RF3133 |

|--------------------------------|-----------------------|--------|

| Power Control ASIC             | \$0.80                | N/A    |

| Directional Coupler            | \$0.20                | N/A    |

| Buffer                         | \$0.05                | N/A    |

| Attenuator                     | \$0.05                | N/A    |

| Various Passives               | \$0.05                | N/A    |

| Mounting Yield (other than PA) | \$0.12                | N/A    |

| Total                          | \$1.27                | \$0.00 |

Note: Output power is limited by battery voltage. The relationship in Equation 4 does not limit output power. Equation 4 limits  $V_{RAMP}$  to correspond with the battery voltage.

### Traditional Triple-Band PA

\*Shaded area eliminated with Indirect Closed Loop using RFMD's Integrated Power Control Solution

### **PCB Design Requirements**

### **PCB Surface Finish**

The PCB surface finish used for RFMD's qualification process is Electroless Nickel, immersion Gold. Typical thickness is 3µinch to 8µinch Gold over 180µinch Nickel.

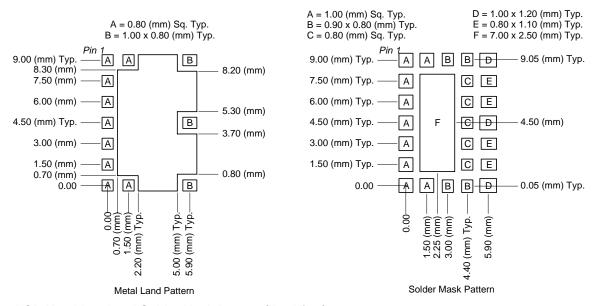

### **PCB Land Pattern Recommendation**

PCB land patterns are based on IPC-SM-782 standards when possible. The pad pattern shown has been developed and tested for optimized assembly at RFMD; however, it may require some modifications to address company specific assembly processes. The PCB land pattern has been developed to accommodate lead and package tolerances.

#### **PCB Metal Land and Solder Mask Pattern**

Figure 1. PCB Metal Land and Solder Mask Pattern (Top View)

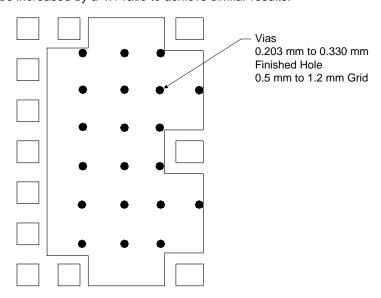

### Thermal Pad and Via Design

The PCB land pattern has been designed with a thermal pad that matches the exposed die paddle size on the bottom of the device.

Thermal vias are required in the PCB layout to effectively conduct heat away from the package. The via pattern shown has been designed to address thermal, power dissipation and electrical requirements of the device as well as accommodating routing strategies.

The Via pattern used for the RFMD qualification is based on thru-hole vias with 0.203mm to 0.330mm finished hole size on a 0.5mm to 1.2mm grid pattern with 0.025mm plating on via walls. If micro vias are used in a design, it is suggested that the quantity of vias be increased by a 4:1 ratio to achieve similar results.

Figure 2. Thermal Pad and Via Design (RFMD Qualification)

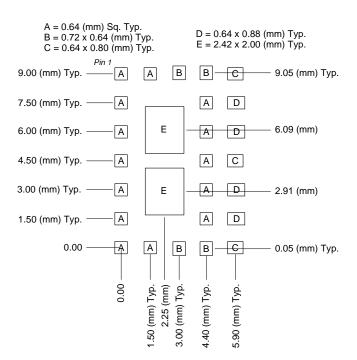

### Stencil Design Recommendation

The stencil aperture are typically designed to match the pad size shown in the PCB Solder Mask pattern and are reduced for an overall 20 percent reduction in pad area for each pad. This has yielded good solder joint results based on volumes assembled during product introduction phase.

Critical parameters to consider for successful solder paste application include:

Accurate registration of the stencil to the PCB during printing.

Good release of stencil from the PCB after paste applied. This is improved with laser cut trapezoidal openings.

Proper storage and handling of solder paste based on solder paste vendor guidelines.

Frequent cleaning of the solder paste stencil to remove residual solder paste.

Stencil material recommendations: 5mil (0.127mm) thick stainless steel, laser cut stencils with trapezoidal openings to promote easy release of solder paste.

Figure 3. Stencil Recommendation