### HIGH FREQUENCY LNA/MIXER

### Typical Applications

- WLAN or Wireless Local Loop

- Digital Communication Systems

- Spread-Spectrum Communication Systems UHF Digital and Analog Receivers

- Part of 2.4GHz Chipset

- Portable Battery-Powered Equipment

### **Product Description**

The RF2444 is a monolithic integrated UHF receiver front end suitable for 2.4GHz ISM band applications. The IC contains all of the required components to implement the RF functions of the receiver except for the passive filtering and LO generation. It contains an LNA (low-noise amplifier), a second RF amplifier and a doubly balanced mixer. The output of the LNA is made available as an output to permit the insertion of a bandpass filter between the LNA and the RF/Mixer section. The mixer outputs can be selectively disabled to allow for the IF filter to be used in the transmit mode.

Optimum Technology Matching® Applied Si BJT

Si Bi-CMOS

GaAs HBT SiGe HBT

GaAs MESFET ☐ Si CMOS

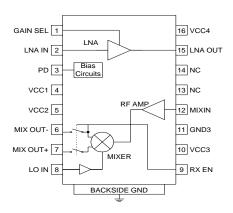

Functional Block Diagram

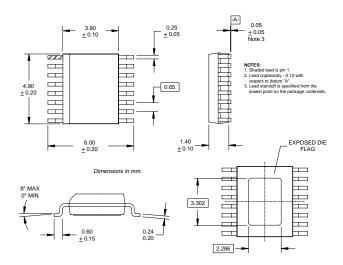

Package Style: SSOP-16 EDF Slug

### **Features**

- Single 2.7V to 3.6V Power Supply

- 2400MHz to 2500MHz Operation

- Two Gain Settings: 28dB or 12dB

- 4.5dB Cascaded NF, High Gain Mode

- 20mA DC Current Consumption

- Input IP<sub>3</sub>: -23dBm or -8dBm

### Ordering Information

RF2444 High Frequency LNA/Mixer RF2444 PCBA-H Fully Assembled Evaluation Board (2.5 GHz)

RF Micro Devices, Inc. 7625 Thorndike Road Greensboro, NC 27409, USA

Tel (336) 664 1233 Fax (336) 664 0454 http://www.rfmd.com

Rev A3 010717

**Absolute Maximum Ratings**

| Parameter                     | Rating                | Unit     |

|-------------------------------|-----------------------|----------|

| Supply Voltage                | -0.5 to 3.6           | $V_{DC}$ |

| Input LO and RF Levels        | +6                    | dBm      |

| Operating Ambient Temperature | -40 to +85            | °C       |

| Storage Temperature           | -40 to +150           | °C       |

| Moisture Sensitivity          | JEDEC Level 5 @ 220°C |          |

Refer to "Handling of PSOP and PSSOP Products" on page 16-15 for special handling information.

RF Micro Devices believes the furnished information is correct and accurate at the time of this printing. However, RF Micro Devices reserves the right to make changes to its products without notice. RF Micro Devices does not assume responsibility for the use of the described product(s).

| Daramatar                    | Specification        |              |      | 11!4     | Condition                                      |  |

|------------------------------|----------------------|--------------|------|----------|------------------------------------------------|--|

| Parameter                    | Min.                 | Тур.         | Max. | Unit     | Condition                                      |  |

| Overall                      |                      |              |      |          | T=25°C, V <sub>CC</sub> =3.3V, RF=2400 MHz,    |  |

|                              |                      |              |      |          | LO=2120MHz, -1 0 dBm                           |  |

| RF Frequency Range           |                      | 2400 to 2500 |      | MHz      |                                                |  |

| IF Frequency Range           | 10                   | 280          | 500  | MHz      |                                                |  |

| Cascade Gain                 |                      | 28           |      | dB       | IF=280MHz, GAIN SEL = 1                        |  |

|                              |                      | 12           |      | dB       | IF=280 MHz, GAIN SEL = 0                       |  |

| Cascade IP3                  |                      | -23          |      | dBm      | Referenced to the input, GAIN SEL = 1          |  |

|                              |                      | -8           |      | dBm      | Referenced to the input, GAIN SEL = 0          |  |

| Cascade Noise Figure         |                      | 4.5          |      | dB       | Single sideband, GAIN SEL = 1                  |  |

| In most DA dD                |                      | 18           |      | dB       | Single sideband, GAIN SEL = 0                  |  |

| Input P1dB                   |                      | -28          |      | dBm      | GAIN SEL = 1                                   |  |

| 1 11 4                       |                      | -14          |      | dBm      | GAIN SEL = 0                                   |  |

| LNA                          |                      |              |      |          | 0.411.051                                      |  |

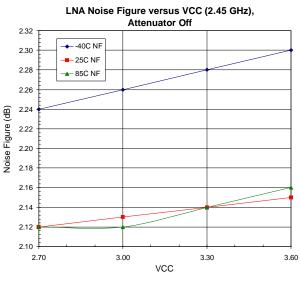

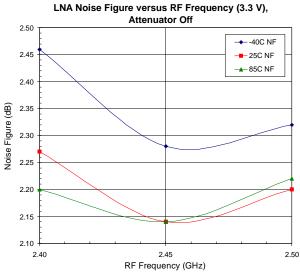

| Noise Figure                 |                      | 2.3          |      | dB       | GAIN SEL = 1                                   |  |

| 1 11/01/15                   |                      | 7            | 0.4  | dB       | GAIN SEL = 0                                   |  |

| Input VSWR                   |                      | 0            | 2:1  | -ID      | No external matching                           |  |

| Input IP3                    |                      | -3           |      | dBm      | GAIN SEL = 1                                   |  |

| Caia                         |                      | -3           |      | dBm      | GAIN SEL = 0                                   |  |

| Gain                         |                      | 10<br>-6     |      | dB<br>dB | GAIN SEL = 1<br>GAIN SEL = 0                   |  |

| Deverse legistics            |                      | -6<br>22     |      | -        | GAIN SEL = 0                                   |  |

| Reverse Isolation            |                      | 50           |      | dB<br>Ω  |                                                |  |

| Output Impedance             |                      | 50           |      | 12       |                                                |  |

| RF Amp and Mixer             |                      | 40           |      | 40       | Cinale sideband                                |  |

| Noise Figure Input Impedance |                      | 10<br>50     |      | dB<br>Ω  | Single sideband                                |  |

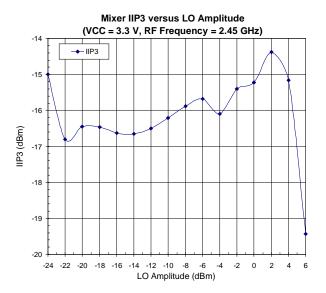

| Input IP3                    |                      | -17          |      | dBm      |                                                |  |

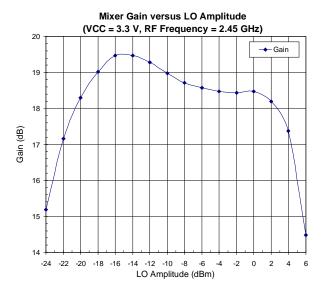

| Conversion Power Gain        |                      | -17<br>18    |      | dВ       | With Current Combiner (1kΩ between open        |  |

| Conversion Fower Gain        |                      | 10           |      | uБ       | collectors and 250 $\Omega$ single ended load) |  |

| Output Impedance             |                      | 4            |      | kΩ       | Open Collector                                 |  |

| LO Input                     |                      |              |      |          |                                                |  |

| LO Level                     | -15                  | -10          | 0    | dBm      |                                                |  |

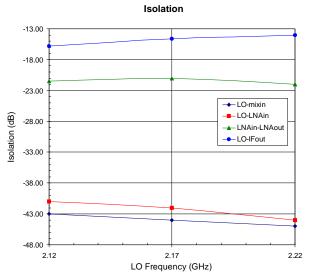

| LO to RF Rejection           |                      | 42           |      | dB       | LO input to LNA input                          |  |

| LO to IF Rejection           |                      | 15           |      | dB       | LO input to IF output                          |  |

| LO Input VSWR                |                      | -            | 2:1  |          |                                                |  |

| Power Down Control           |                      |              |      |          |                                                |  |

| Logic Controls "ON"          | V <sub>CC</sub> -0.3 |              |      | V        | Voltage at the input of RX EN, PD              |  |

| Logic Controls "OFF"         | 100 0.0              |              | 300  | mV       | and GAIN SEL                                   |  |

| Turn on Time                 |                      | 400          | 1000 | nS       | From PD Going high.                            |  |

| Turn on Time                 |                      | 100          | 200  | nS       | From RX EN Going high. PD = "1"                |  |

8-54 Rev A3 010717

| Parameter           | Specification |      |      | Unit  | Condition                        |  |

|---------------------|---------------|------|------|-------|----------------------------------|--|

| Farailletei         | Min.          | Тур. | Max. | Offic | Condition                        |  |

| Power Supply        |               |      |      |       |                                  |  |

| Voltage             | 2.7           | 3.3  | 3.6  | V     |                                  |  |

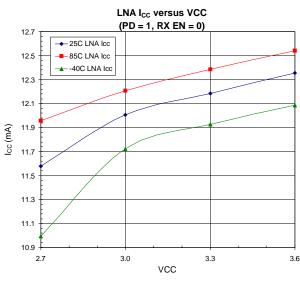

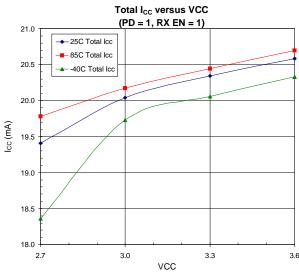

| Current Consumption |               | 20   | 26   | mA    | GAIN SEL = 1, RX EN =1, PD = 1   |  |

|                     |               | 20   | 25   | mA    | GAIN SEL = 0, RX EN =1, PD = 1   |  |

|                     |               | 12   | 16   | mA    | GAIN SEL = X, RX EN =0, PD = 1   |  |

|                     |               |      | 1    | μΑ    | GAIN SEL = X, RX EN =X, PD = $0$ |  |

| Pin | Function | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Interface Schematic  |  |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|

| 1   | GAIN SEL | LNA gain control. When GAIN SEL is >V <sub>CC</sub> -300mV, LNA gain is at 10 dB. When GAIN SEL is <300mV, the LNA gain is -6dB.                                                                                                                                                                                                                                                                                                                            | See pin 16.          |  |

| 2   | LNA IN   | This pin is NOT internally DC blocked. An external blocking capacitor must be provided if the pin is connected to a device with DC present. If a blocking capacitor is required, a value of 2pF is recommended.                                                                                                                                                                                                                                             | See pin 16.          |  |

| 3   | PD       | The power enable pin. When PD is $>$ V <sub>CC</sub> -300mV, the part is biased on. When PD is $<$ 300mV, then the part is turned off and typically draws less than 1 $\mu$ A.                                                                                                                                                                                                                                                                              |                      |  |

| 4   | VCC1     | Supply voltage for bias circuits and logic control. A 10pF external bypass capacitor is required and an additional $0.01  \mu F$ is required if no other low frequency bypass capacitors are nearby. The trace length between the pin and the bypass capacitors should be minimized. The ground side of the bypass capacitors should connect immediately to ground plane.                                                                                   |                      |  |

| 5   | VCC2     | Supply voltage for LO_Buffer. A 10pF bypass capacitor is required and an additional $0.01\mu F$ is required if there is no other low frequency bypass capacitor in the area. The trace length between the pin and the bypass capacitors should be minimized. The ground side of the bypass capacitors should connect immediately to ground plane.                                                                                                           | See pin 8.           |  |

| 6   | MIXOUT-  | The inverting open collector output of the mixer. This pin needs to be externally biased and DC isolated from other parts of the circuit. This output can drive a Balun, with MIXOUT+, to convert to unbalanced to drive a SAW filter. The Balun can be either broadband (transformer) or narrowband (discrete LC matching). Alternatively, MIXOUT+ may be used alone to drive a SAW single-ended, with an RF choke (high Z at IF) from VCC to MIXOUT       | MIX OUT+ MIX OUT-    |  |

| 7   | MIXOUT+  | The non-inverting open collector output of the mixer. This pin needs to be externally biased and DC isolated from other parts of the circuit. This output can drive a Balun, with MIXOUT+, to convert to unbalanced to drive a SAW filter. The Balun can be either broadband (transformer) or narrowband (discrete LC matching). Alternatively, MIXOUT+ may be used alone to drive a SAW single-ended, with an RF choke (high Z at IF) from VCC to MIXOUT+. | See pin 6.           |  |

| 8   | LO IN    | LO input pin. This input needs a DC blocking cap. External matching is recommended to $50\Omega$                                                                                                                                                                                                                                                                                                                                                            | VCC2                 |  |

| 9   | RX EN    | This control pin allows the mixer output pins to be put into a high impedance state. This allows the transmit signal path to share the same IF filter as the receiver.                                                                                                                                                                                                                                                                                      |                      |  |

| 10  | VCC3     | Supply voltage for mixer preamp.                                                                                                                                                                                                                                                                                                                                                                                                                            | See pin 12.          |  |

| 11  | GND3     | Ground pin for mixer preamp. This lead inductance should be kept small.                                                                                                                                                                                                                                                                                                                                                                                     | See pin 12.          |  |

| 12  | MIX IN   | Mixer RF Input port. This pin is NOT internally DC blocked. An external blocking capacitor must be provided if the pin is connected to a device with DC present. A value of >22pF is recommended. To minimize the noise figure it is recommended to have a bandpass filter before this input. This will prevent the noise at the image frequency from being converted to the IF.                                                                            | VCC3  MIX IN O  GND3 |  |

8-56 Rev A3 010717

| Pin | Function | Description                                                                                                                                                                                                                                                                              | Interface Schematic                                                       |  |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--|

| 13  | NC       |                                                                                                                                                                                                                                                                                          |                                                                           |  |

| 14  | NC       |                                                                                                                                                                                                                                                                                          |                                                                           |  |

| 15  | LNA OUT  | RF signal output for external $50\Omega$ filtering. The use of a filter here is optional but does provide for lower noise floor and better out-of-band rejection.                                                                                                                        | See pin 16.                                                               |  |

| 16  | VCC4     | Supply voltage for the LNA. This pin should be bypassed with a 10 pF capacitor to ground as close to the pin as possible. The shunt inductance from this pin to ground via the supply decoupling must be tuned to match the LNA output to $50\Omega$ at the desired operating frequency. | Microstrip  EXTERNAL  DECOUPLING  VCC4  16 dB  P15  LNA OUT  P1  GAIN SEL |  |

## Theory of Operation

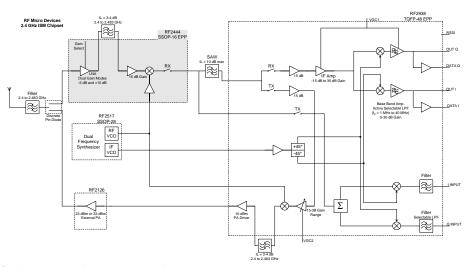

Figure 1. Entire Chipset Functional Block Diagram

The RF2444 contains the LNA/Mixer for this chipset. The LNA is made from two stages including a common emitter amplifier stage with a power gain of 13dB and an attenuator which has an insertion loss of 3dB in high gain mode, and 17dB in low gain mode. The attenuator was put after the LNA so that system noise figure degradation would be minimized. A single gain stage was used prior to the image filter to maximize IP3 which minimizes the risk of large out-of-bad signals jamming the desired signal.

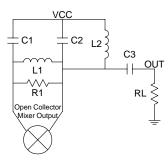

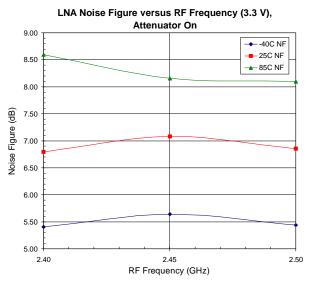

The mixer on the RF2444 is also two stages. The first stage is a common emitter amp used to boost the total power gain prior to the lossy SAW filter, to convert to a differential signal to the input of the mixer, and to improve the noise figure of the mixer. The second stage is a double balanced mixer whose output is differential open collector. It is recommended that a "current combiner" is used (as shown in figure 2) at the mixer output to maximize conversion gain, but other loads can also be used. The current combiner is used to do a differential to single ended conversion for the SAW filter. C1, C2 and L1 are used to tune the circuit for a specific IF frequency. L2 is a choke to supply DC current to the mixer that is also used as a tuning element, along with C3, to match to the SAW filter's input impedance. RL is the SAW filter's input impedance.

The mixer power conversion gain is +19dB when R1 is set to  $1k\Omega$ . The conversion gain can be adjusted up ~5dB or down ~7dB by changing the value of R1. Once R1 is chosen, L2 and C3 can be used to tune the output for the SAW filter.

Figure 2. Current Combiner for Mixer Load

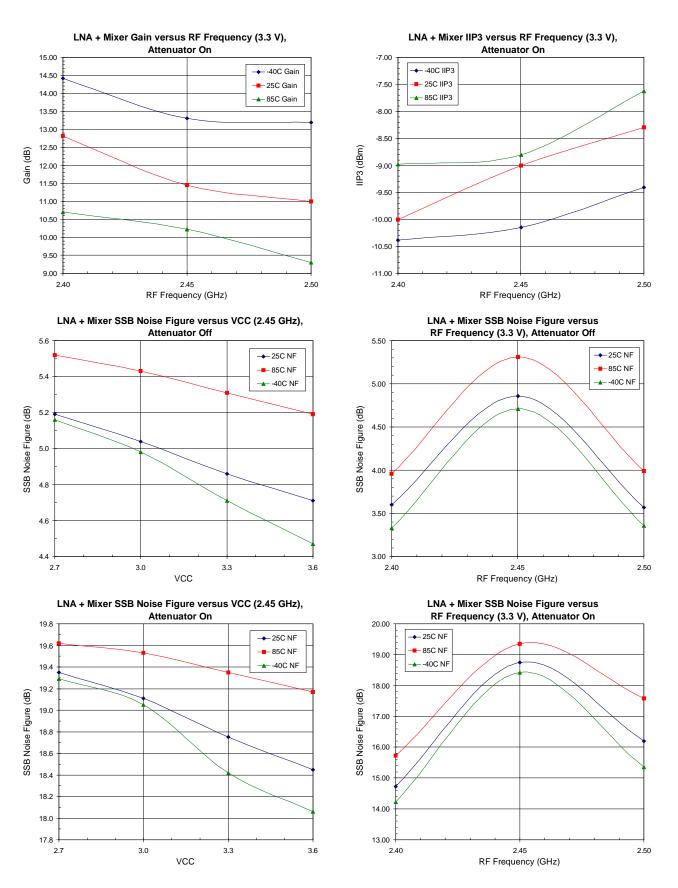

The cascaded power gain of the LNA/Mixer is 29dB, which after insertion loss in the image filter (~3dB) and IF SAW filter (~10dB), still gives 16dB of gain prior to the IF amps. Because of this, the noise figure of the IF amps should not significantly degrade system noise figure.

The LNA input should be matched for a good return loss for optimum gain and noise figure. To allow the designer to match each of these ports, 2-port s-parameter data is available for the LNA, and 1-port data is available for MIXER IN and LO IN.

Rev A3 010717

8-58

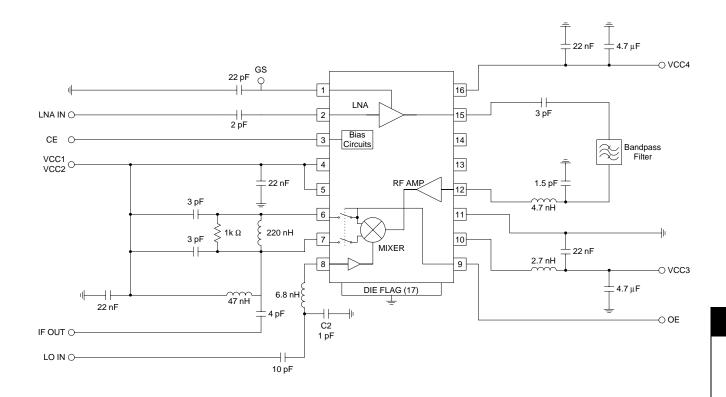

## **Application Schematic**

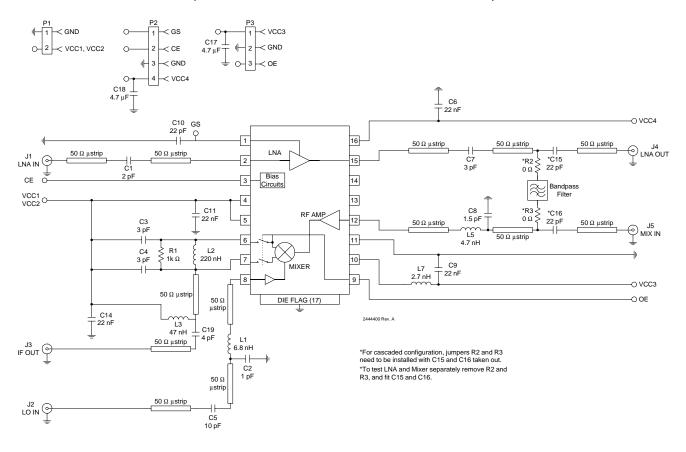

## **Evaluation Board Schematic**

(Download Bill of Materials from www.rfmd.com.)

8-60 Rev A3 010717

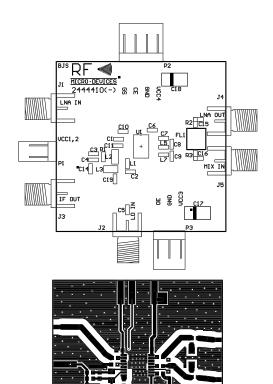

## **Evaluation Board Layout**

Board Thickness 0.031", Board Material FR-4

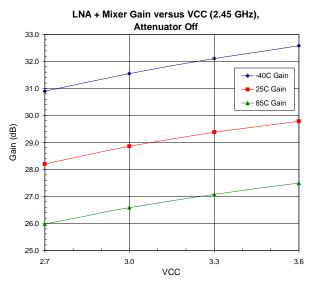

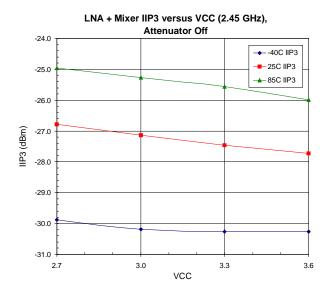

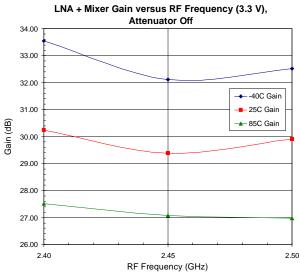

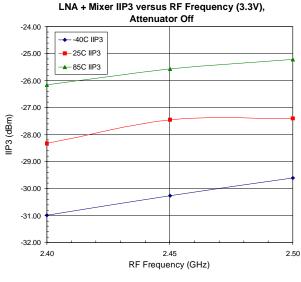

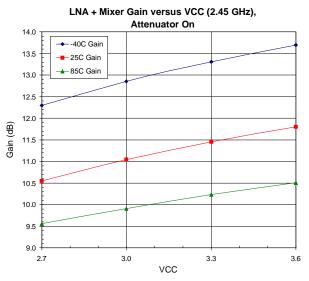

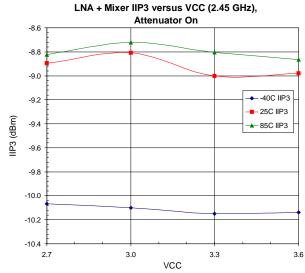

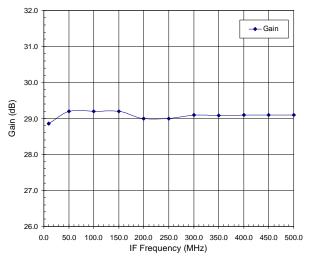

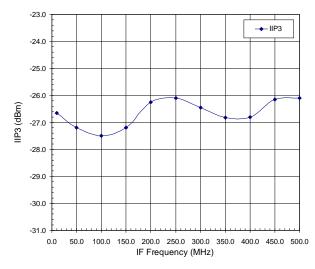

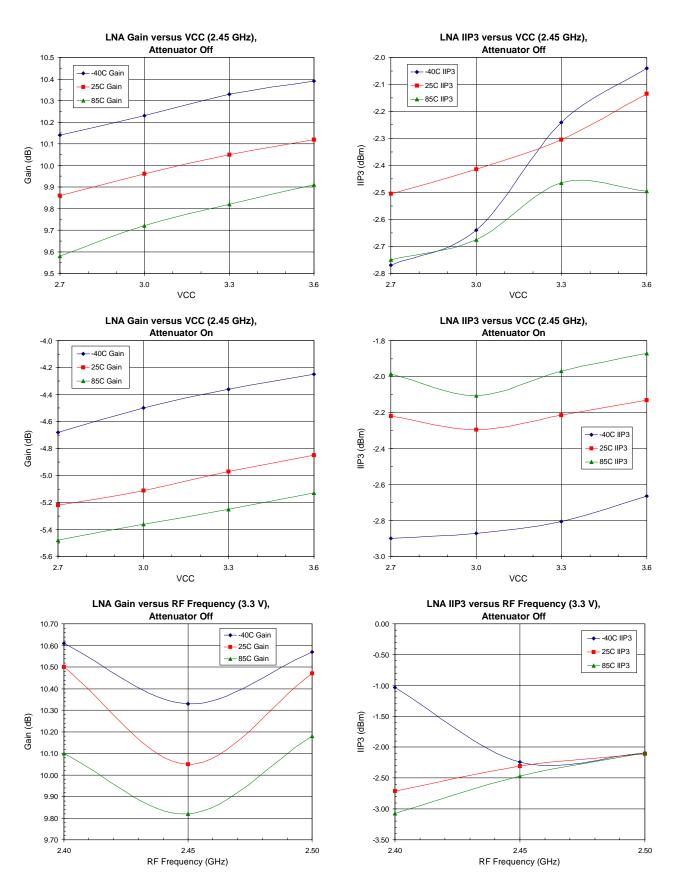

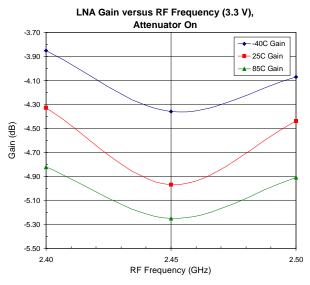

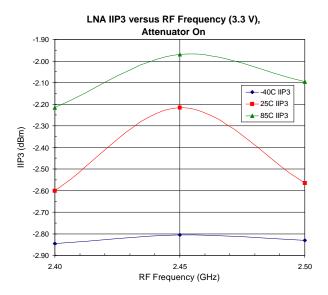

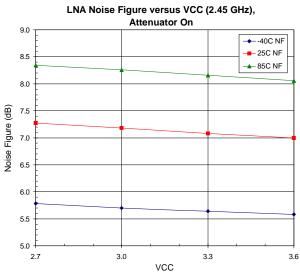

**NOTE:** In the following charts, all cascaded data measured with a bandpass filter inserted between LNA OUT and MIX IN, having cut frequencies:  $f_L$ =2400MHz,  $f_M$ =2484MHz, and insertion loss=1.2dB.

8-62 Rev A3 010717

### LNA + Mixer Gain versus IF Frequency (3.3 V)

### LNA + Mixer IIP3 versus IF Frequency (3.3 V)

8-64 Rev A3 010717

8-66 Rev A3 010717

8-68 Rev A3 010717