# R65/11EB and R65/11EAB Backpack Emulator

#### INTRODUCTION

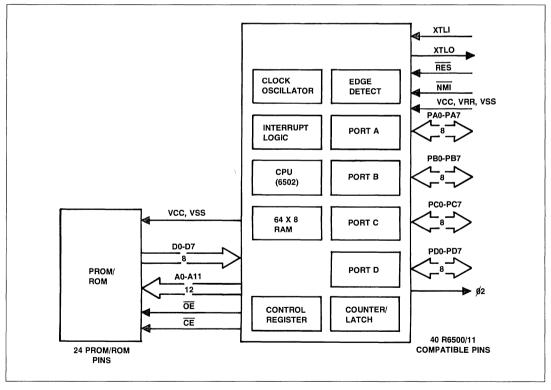

The Rockwell R65/11EB and R65/11EAB Backpack Emulator are PROM prototyping versions of the 8-bit, masked-ROM R6500/11 and R6500/15 one-chip microcomputers. Like the R6500/11, the backpack device is totally upward/downward compatible with all members of the R6500/11 family. It is designed to accept standard 5-volt, 24-pin EPROMs or ROMs directly, in a socket on top of the Emulator. This packaging concept allows a standard EPROM to be easily removed, re-programmed, then reinserted as often as desired.

The backpack devices have the same pinouts as the masked-ROM R6500/11 and R6500/15 microcomputers. These 40 pins are functionally and operationally identical to the pins on the R6500/11. The R6500/11 Microcomputer Product Description (Order No. 2119) includes a description of the interface signals and their functions. Whereas the masked-ROM R6500/11 provides 3K bytes of read-only memory, the R65/11EB will address 4K bytes of external program memory. This extra memory accommodates program patches, test programs or optional programs during breadboard and prototype development states.

#### **ORDERING INFORMATION**

#### BACKPACK EMULATOR

| Part<br>Number | Memory<br>Capacity | Compatible<br>Memories | Temperature<br>Range and Speed |

|----------------|--------------------|------------------------|--------------------------------|

| R65/11EB       | 4K × 8             | 2732                   | 0°C to 70°C<br>1 MHz           |

| R65/11EAB      | 4K × 8             | 2732A                  | 0°C to 70°C<br>2 MHz           |

#### SUPPORT PRODUCTS

| Part<br>Number | Description                                |

|----------------|--------------------------------------------|

| RDC-3101       | Low Cost Emulator (LCE) Development System |

| RDC-3030       | LCE PROM Programmer Module                 |

| RDC-309        | 1 or 2-MHz R6500/11 Personality Module     |

#### **FEATURES**

- PROM version of the R6500/11 and R6500/15

- Completely pin compatible with R6500/11 single-chip microcomputers

- Profile approaches 40-pin DIP of R6500/11

- Accepts 5 volt, 24-pin industry-standard EMPROMS—4K memories—2732, 2732A (4K bytes addressable)

- · Use as prototyping tool or for low volume production

- 4K bytes of memory capacity

- 192 × 8 static RAM

- · Separate power pin for 32 bytes of RAM

- · Software compatibility with the R6500 family

- 32 bi-directional TTL compatible I/O lines (4 ports)

- Two 16-bit programmable counter/latches with six modes (interval timer, pulse generator, event counter, pulse width measurement, asymmetrical pulse generator, and retriggerable interval timer)

- 10 interrupts (reset, non-maskable, four external edge sensitive, 2 counters, serial data received, serial data transmitted)

- Crystal or external time base

- Single +5V power supply

Note: R6500/11 describes both R6500/11 and R6500/15.

R65/11EB Backpack Emulator

## 3

#### CONFIGURATIONS

The Backpack Emulator is available in two different versions, to accommodate 1 MHz and 2 MHz speeds. Both versions provide 192 bytes of RAM and I/O, as well as 24 signals to support the external memory "backpack" socket.

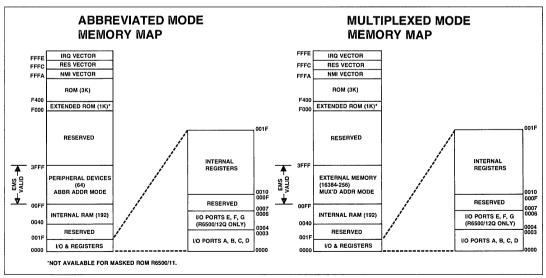

The emulator will relocate the EPROM address space to FXXX (see Memory Map). EPROM addresses FFA through FFF must contain the interrupt vectors.

#### **EXTERNAL FREQUENCY REFERENCE**

The external frequency reference may be a crystal or a clock. The R65/11EB and R65/11EAB divide the input clock by two regardless of the source.

#### I/O PORT PULLUPS

The devices have internal I/O port pull-up resistors on ports A, B, & C. Port D has push-pull drivers.

#### MODE CONTROL REGISTER

Bit 6 of the MODE CONTROL REGISTER (MCR6) must be set to 1 if Bit 7 (MCR7) is set to  $\emptyset$ . (R65/11EB and R65/11EAB only).

#### PRODUCT SUPPORT

The Backpack Emulator is just one of the products that Rockwell offers to facilitate system and program development for the R6500/11.

The Low Cost Emulator (LCE) Development System with R6500/11 Personality Module supports both hardware and software development. Complete in-circuit user emulation with the R6500/11 Personality Module allows total system test and evaluation. With the optional PROM Programmer, the LCE can also be used to program EPROMs for the development activity. When PROM programs have been finalized, the PROM device can be sent to Rockwell for masking into the 3K ROM of the R6500/11 or the 4K ROM of the R6500/15.

R65/11EB Interface Diagram

| XTLO | ₫•₁         | A7 □ 1s               | 24s  | □ v <sub>cc</sub> | 40   | $v_{ss}$ |

|------|-------------|-----------------------|------|-------------------|------|----------|

| XTLI | ☐ 2         | A6 🗖 2s               | 23s  | □ A8 □            | 39 🗀 | VRR      |

| ø2   | □ 3         | A5 □ 3s               | 22s  | ⊐ A9              | 38 🗀 | PB0      |

| PC0  | □ 4         | A4 🗗 4s               | 21s  | □ A11             | 37   | PB1      |

| PC1  | □ 5         | A3 🖯 5s               | 20s  | □ OE              | 36 🗖 | PB2      |

| PC2  | <b>□</b> 6  | A2 □ 6s               | 19s  | □ A10             | 35   | PB3      |

| PC3  | □ 7         | A1 □ 7s               | 18s  | CE                | 34   | PB4      |

| PC4  | □ 8         | A0 □ 8s               | 17s  | ⊐ <b>D7</b>       | 33 🖯 | PB5      |

| PC5  | □ 9         | D0 □ 9s               | 16s  | □ <b>D</b> 6      | 32 🗍 | PB6      |

| PC6  | 10          | D1 🗆 10s              | 15s  | □ <b>D</b> 5      | 31 🦳 | PB7      |

| PC7  | 711         | D2 🗆 11s              | 14s  | □ D4              | 30 🗂 | PA0      |

| PD7  | <b>□</b> 12 | V <sub>SS</sub> □ 12s | 13s  | □ <b>D</b> 3      | 29   | PA1      |

| PD6  | 13          | L                     |      | i                 | 28   | PA2      |

| PD5  | □ 14        | 24-PIN S              | OCKE | Γ                 | 27   | PA3      |

| PD4  | <b>15</b>   |                       |      |                   | 26   | PA4      |

| PD3  | □ 16        |                       |      |                   | 25   | PA5      |

| PD2  | <b>17</b>   |                       |      |                   | 24 🗖 | PA6      |

| PD1  | 18          |                       |      |                   | 23   | PA7      |

| PD0  | 🗍 19        |                       |      |                   | 22 🗇 | NMI      |

| RES  | 20          |                       |      |                   | 21   | $v_{cc}$ |

|      | 7           |                       |      |                   |      |          |

Pin Configuration

### BACKPACK MEMORY SIGNAL DESCRIPTION

| Oi                            |                                  |                                                                                                                                                                                                                                                                                            |

|-------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal<br>Name                | Pin No.                          | Description                                                                                                                                                                                                                                                                                |

| D0-D7                         | 9S-11S,<br>13S-17S               | Data Bus Lines. All instruction and data transfers take place on the data bus lines. The buffers driving the data bus lines have full three-state capability. Each data bus pin is connected to an input and an output buffer, with the output buffer remaining in the floating condition. |

| A0-A7<br>A8, A9<br>A10<br>A11 | 1S-8A,<br>23S, 24S<br>19S<br>21S | Address Bus Lines. The address bus lines are buffered by push/pull type drivers that can drive one standard TTL load.                                                                                                                                                                      |

| CE                            | 18S                              | Chip Enable. $\overline{\text{CE}}$ is active when the address is 8000-FFFF. This line can drive one TTL load.                                                                                                                                                                             |

| ŌĒ                            | 20S                              | Memory Enable Line. This signal provides the output enable for the memory to place information on the data bus lines. This signal is driven by an inverted $R/\overline{W}$ signal from the CPU. It can drive 1 TTL load.                                                                  |

| V <sub>cc</sub>               | 248                              | Main Power Supply $+5V$ . This pin is tied directly to pin 21 ( $V_{CC}$ ).                                                                                                                                                                                                                |

| V <sub>SS</sub>               | 12S                              | Signal and Power Ground (zero volts). This pin is tied directly to pin 40 ( $V_{\rm SS}$ ).                                                                                                                                                                                                |

### I/O AND INTERNAL REGISTER ADDRESSES

| Address<br>(Hex) | Read                          | Write                                          |  |  |

|------------------|-------------------------------|------------------------------------------------|--|--|

| 001F             |                               |                                                |  |  |

| 1E               | Lower Counter B               | Upper Latch B, Cntr B ← Latch B, CLR Flag      |  |  |

| 1D               | Upper Counter B               | Upper Latch B, Latch C←Latch B                 |  |  |

| 1C               | Lower Counter B, CLR Flag     | Lower Latch B                                  |  |  |

| 1B               |                               |                                                |  |  |

| 1A               | Lower Counter A               | Upper Latch A, Cntr A←Latch A, CLR Flag        |  |  |

| 19               | Upper Counter A               | Upper Latch A                                  |  |  |

| 18               | Lower Conter A, CLR Flag      | Lower Latch A                                  |  |  |

| 17               | Serial Receiver Data Register | Serial Transmitter Data Register               |  |  |

| 16               | Serial Comm. Status Register  | Serial Comm. Status Reg. Bits 4 & 5 only       |  |  |

| 15               | Serial Comm. Control Register | Serial Comm. Control Register                  |  |  |

| 14               | Mode Control Register         | Mode Control Register                          |  |  |

| 13               |                               |                                                |  |  |

| 12               | Interrupt Enable Register     | Interrupt Enable Register                      |  |  |

| 11               | Interrupt Flag Register       |                                                |  |  |

| 0010             | Read FF                       | Clear Int Flag (Bits 0-3 only, Write 0's only) |  |  |

| 04 thru 0F       |                               |                                                |  |  |

| 03               | Port D                        | Port D                                         |  |  |

| 02               | Port C                        | Port C                                         |  |  |

| 01               | Port B                        | Port B                                         |  |  |

| 0000             | Port A                        | Port A                                         |  |  |

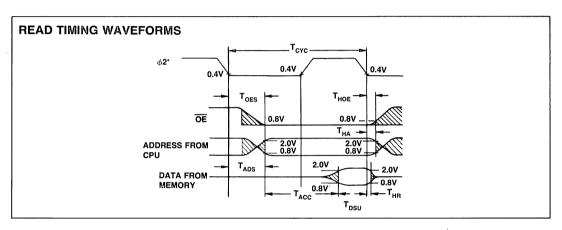

#### **READ TIMING CHARACTERISTICS**

|                               |                  | 1 MHz |      | 2 MHz |      |      |

|-------------------------------|------------------|-------|------|-------|------|------|

| Signal                        | Symbol           | Min.  | Max. | Min.  | Max. | Unit |

| OE and CE setup time from CPU | T <sub>OES</sub> | _     | 225  | _     | 140  | ns   |

| Address setup time from CPU   | T <sub>ADS</sub> | _     | 150  |       | 75   | ns   |

| Memory read access time       | T <sub>ACC</sub> |       | 700  | _     | 315  | ns   |

| Data set up time              | T <sub>DSU</sub> | 50    | _    | 35    | _    | ns   |

| Data hold time—Read           | T <sub>HR</sub>  | 10    | _    | 10    | _    | ns   |

| Address hold time             | T <sub>HA</sub>  | 30    | _    | 30    | _    | ns   |

| OE and CE hold time           | T <sub>HOE</sub> | 30    | -    | 30    | _    | ns   |

| Cycle Time                    | T <sub>CYC</sub> | 1.0   | 10.0 | 0.5   | 10.0 | μS   |

#### **ELECTRICAL CHARACTERISTICS**

(V<sub>CC</sub> = 5.0V  $\pm$  5%, V<sub>SS</sub> = 0, T<sub>A</sub> = 0°C to 70°C, unless otherwise stated)

| Characteristic                                      | Symbol           | Min  | Тур  | Max   | Unit | Test Conditions                                      |  |

|-----------------------------------------------------|------------------|------|------|-------|------|------------------------------------------------------|--|

| Input High Threshold Voltage<br>D0-D7               | V <sub>IHT</sub> | +2.0 | _    | _     | Vdc  |                                                      |  |

| Input Low Threshold Voltage<br>D0-D7                | V <sub>ILT</sub> |      | _    | +0.8  | Vdc  |                                                      |  |

| Three-State (Off State) Input Current<br>D0-D7      | I <sub>TSI</sub> | _    | _    | ± 10  | μА   | $V_{CC} = 5.25V$<br>$V_{IN} = 0.4V$ to 2.4V          |  |

| Output High Voltage<br>D0-D7, A0-A11, ŌĒ, ČĒ        | V <sub>OH</sub>  | +2.4 | _    | _     | Vdc  | $V_{CC} = 4.75V$ $I_{LOAD} = 100 \mu A$              |  |

| Output Low Voltage<br>D0-D7, A0-A11 OE, CE          | V <sub>OL</sub>  | _    | _    | + 0.4 | Vdc  | V <sub>CC</sub> = 4.75V<br>I <sub>LOAD</sub> = 1.6mA |  |

| Power Dissipation (less EPROM)                      | P <sub>D</sub>   | _    | 0.80 | 1.20  | W    |                                                      |  |

| Output Capacitance (High Impendance State)<br>D0-D7 | C <sub>OUT</sub> |      | _    | 10    | pF   | T <sub>A</sub> = 25°C<br>V <sub>IN</sub> = 0V        |  |

| Input Capacitance                                   | C <sub>IN</sub>  | _    | _    | 10    | pF   | f=1 MHz                                              |  |

| I/O Port Pull-up Resistance                         | RL               | 3.0  | 6.0  | 11.5  | kohm |                                                      |  |

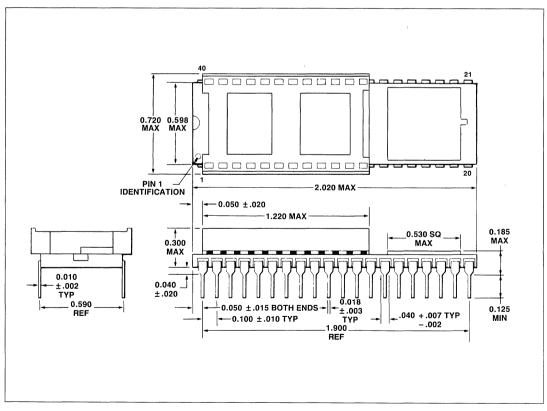

40-Pin Backpack Package