## QR0001 QuickRing<sup>™</sup> Data Stream Controller

### **General Description**

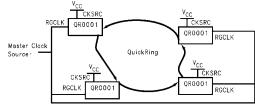

QuickRing is a point-to-point data transfer architecture designed to facilitate high speed data streams. The QuickRing architecture can be applied both inside the chassis as well as outside the chassis environments to increase data throughput. Each QR0001 QuickRing Controller node in the ring is capable of streaming up to 231 MSamples/s per signal line simultaneously, including protocol overhead. This device is intended for use in applications that handle highbandwidth data streams associated with graphics, uncompressed video, disk arrays, high-speed local area networks, multiprocessor systems, and to interconnect peripherals over a few meters of cable. The QR0001 QuickRing Controller can be used to augment the performance of traditional backplane buses in personal computers, workstations, and high-end systems. The QR0001 is useful for routing high-bandwidth streams in systems that are larger or topologically more complex than bus-based systems.

### Features

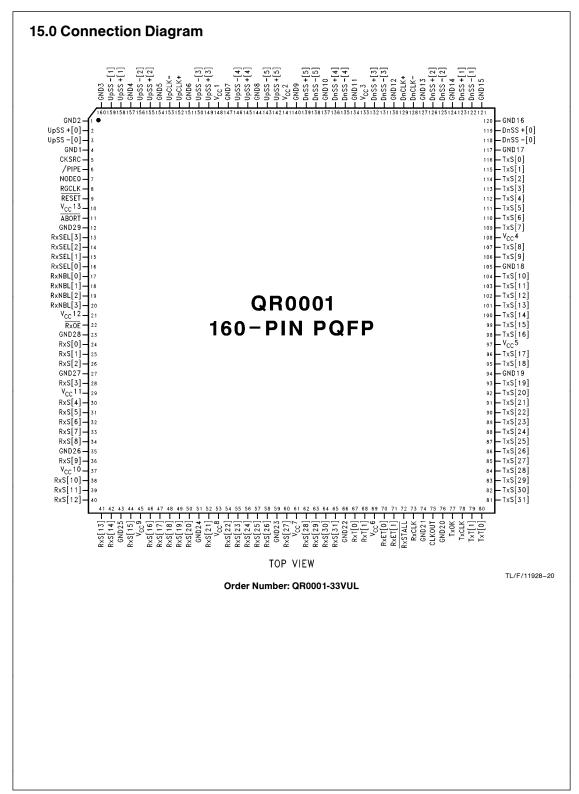

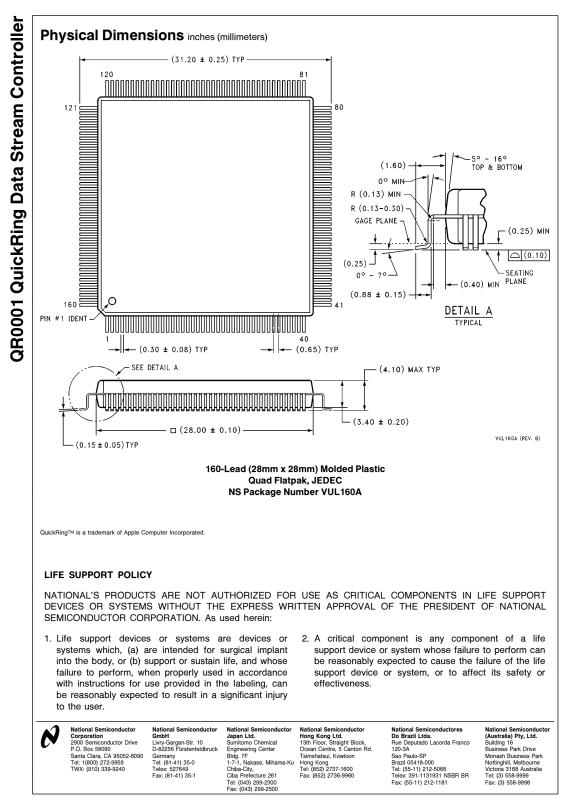

- 160-pin PQFP package

- 16 node single ring capability

- Peak theoretical rate over 1 GByte/sec for 16 node ring

QR0001 QuickRing Data Stream Controller

PRELIMINARY

October 1994

- Support for Multi-Ring topologies

- Error detection detects 1- and 2-bit errors

#### **RING INTERFACE**

- Precision PLL captures data at 231 MSamples/s max

- 33 MHz maximum ring clock frequency

- Low Voltage Differential Signaling (LVDS) ring interface (IEEE P1596.3)

#### **CLIENT INTERFACE**

- 132 MBytes/s data transfer rate at both Tx and Rx ports

- 32-bit transmit and receive data ports

- Readable internal diagnostic register

- TTL signal interface

©1995 National Semiconductor Corporation TL/F/11928

RRD-B30M75/Printed in U. S. A.

### **Table of Contents**

#### 1.0 SIGNAL DESCRIPTION

#### 2.0 BASIC STRUCTURE

#### 3.0 CLIENT INTERFACE

- 3.1 Type and Symbol Fields at the Client Ports

- 3.2 Client Transmit Port3.3 Transmit Port Timing Relationships

- 3.4 Client Receive Port

- 3.5 Receive Port Timing Relationships

3.5.1 Client Receive Port Interface Recommendations (PIPE asserted)

- 3.6 Client Interface Field Definitions

- 3.7 Client Type Fields

- 3.8 Transmit Port Head Fields

- 3.9 Receive Port Head Fields

- 3.10 Payload Symbols at the Rx and Tx Ports

- 3.11 Null Symbols at the Rx and Tx Ports

- 3.12 The HOP fields and the Uniqueness of Symbol Streams

- 3.13 Summary of Client Port Field Format

- 3.14 Readable Registers

- 3.15 Error Detection

#### 4.0 RING INTERFACE

- 4.1 Type and Symbol Field at the Ring Ports

- 4.2 Data and Frames

- 4.3 Symbol Flux on Ring

- 4.4 Data on the Ring (Head, Payload, Tail)

- 4.5 Access on the Ring (Voucher, Ticket, Abort, Null)

- 4.6 Mapping of Type, Frame, Data and EDC Code on the Ring

- 4.7 Ring Interface Field Definitions

- 4.8 Routing Symbols are Common to All Ports

- 4.9 Ring Type Fields

- 4.10 Head Symbol on the Ring

- 4.11 Payload Symbols on the Ring

- 4.12 Tail Symbol on the Ring

- 4.13 Access Symbols on the Ring

- 4.14 Summary of Ring Port Field Format

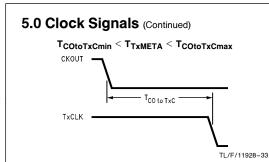

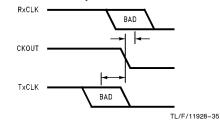

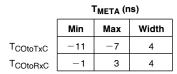

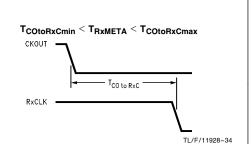

- 5.0 CLOCK SIGNALS

- 6.0 ABORT SIGNAL

- 7.0 BRIDGES

- 8.0 LITTLE/BIG ENDIAN ISSUES

- 9.0 RESET AND INITIALLZATION

- 9.1 Reset

- 9.2 Node 0 Selection and Initialization

- 9.3 Node ID Assignment

- 9.4 Sequence for Node 0

- 9.5 Sequence for All Qther Nodes on Ring

#### 10.0 QR0001 OPERATION FLOW

- 10.1 Ring Traffic Flow Priorities for DnSS port Transmissions

- 10.2 Inside the Source Node (Device Transmitting Data)

- 10.3 Summary of Source Node Actions

- 10.4 Inside the Target Node

- 10.5 Summary of Target Node Actions

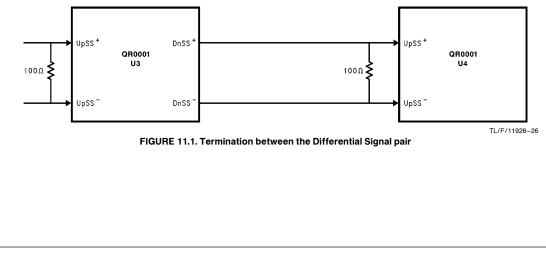

#### 11.0 BOARD CONSIDERATIONS

- 11.1 Upstream Port Signal Termination

- 11.2 QuickRing Physical Layer Details

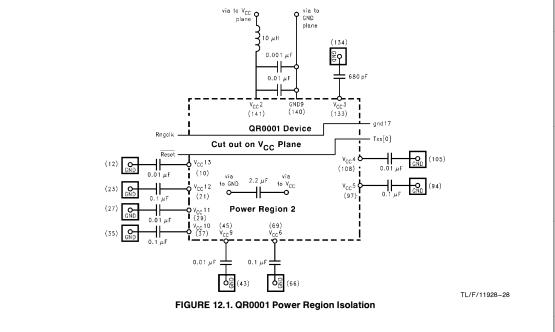

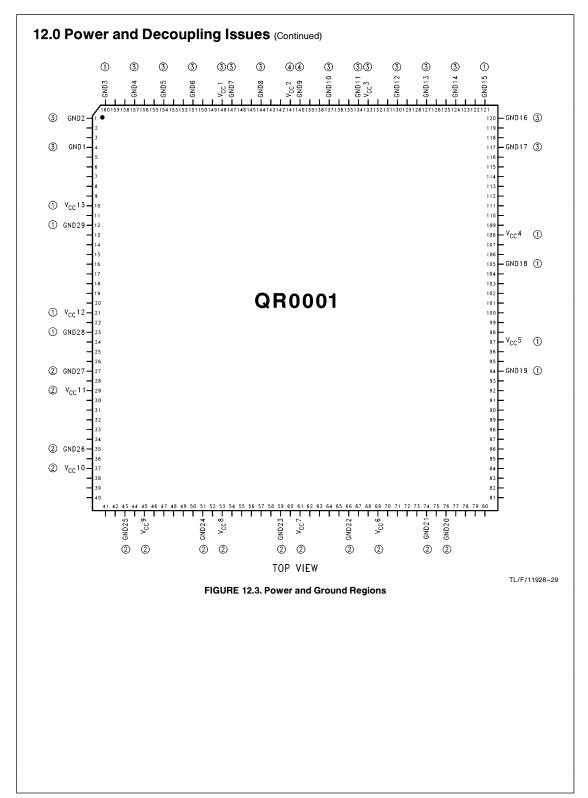

### 12.0 POWER AND DECOUPLING ISSUES

- 12.1 Power Issues

- 12.2 Decoupling Issues

- **13.0 DC ELECTRICAL CHARACTERISTICS**

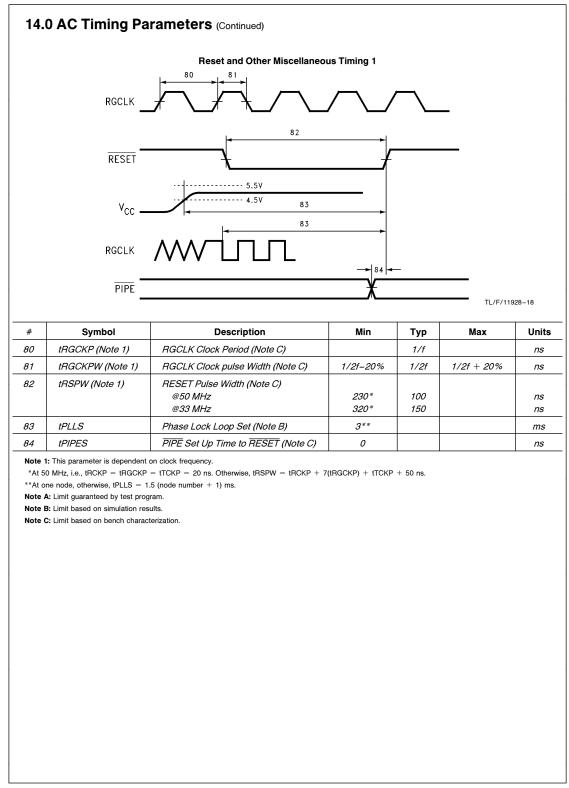

- 14.0 AC TIMING PARAMETERS

- 15.0 CONNECTION DIAGRAM

- 16.0 GLOSSARY

- **17.0 REVISION NOTES**

| Pin Name   | I/O | No. | Description                                                                                                                                                                                                                                                                                                                                                                               |

|------------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET      | I   | 1   | RESET: When this input is released, the initialization sequence begins.                                                                                                                                                                                                                                                                                                                   |

| ABORT      | 0   | 1   | ABORT: When asserted, it indicates that a failure was detected. ABORT is negated by asserting Reset                                                                                                                                                                                                                                                                                       |

| PIPE       | I   | 1   | <b>PIPE:</b> When <b>PIPE</b> is negated (non-pipelined timing), at the Client ports, both the symbol and type fields correspond to each other during the same clock cycle. When <b>PIPE</b> is asserted (pipelined timing), the timing of the Type field leads by one clock at the receive port and trails by one clock at the transmit port (The type and symbol fields are pipelined.) |

| NODE0      | Ι   | 1   | <b>NODE0:</b> When asserted, the controller is configured as having Node ID 0. Node 0 is responsible for governing the initialization process in the ring.                                                                                                                                                                                                                                |

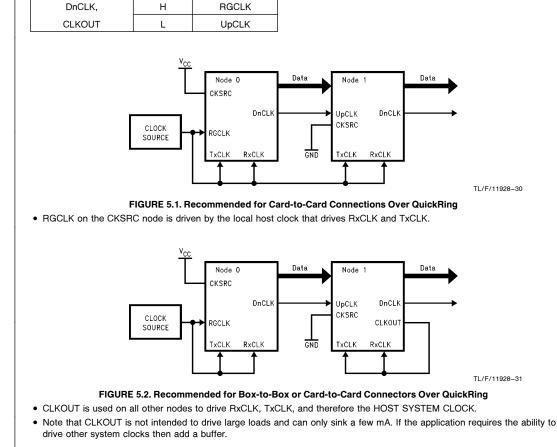

| RGCLK      | Ι   | 1   | <b>RING CLOCK:</b> This clock input is the time-base for the ring interface. A clock input should be present when the CKSRC pin is asserted. When CKSRC is negated, RGCLK should be tied low.                                                                                                                                                                                             |

| CKSRC      | Ι   | 1   | <b>CLOCK SOURCE:</b> Designates the source of the ring clock. When asserted, RGCLK is the clock source used for the Ring interface. When this pin is negated, the clock is derived from the differential UpCLK.                                                                                                                                                                           |

| CLKOUT     | 0   | 1   | <b>CLOCK OUT:</b> If CKSRC is asserted, then CLKOUT is frequency-locked to the RGCLK. If CKSRC is negated, then CLKOUT is frequency-locked to the UpCLK.                                                                                                                                                                                                                                  |

| UpCLK      | Ι   | 2   | <b>UPSTREAM CLOCK:</b> This LVDS input clock comes from the neighbor upstream node and drives the ring interface when CKSRC is negated.                                                                                                                                                                                                                                                   |

| UpSS[5:0]  | Ι   | 12  | <b>UPSTREAM SUB-SYMBOL:</b> These 6 LVDS inputs for the Ring interface carry the divided 42-bit symbo from the downstream port of the previous node.                                                                                                                                                                                                                                      |

| DnCLK      | 0   | 2   | <b>DOWNSTREAM CLOCK:</b> This LVDS output clock signal is derived from the clock that drives the Ring interface. The transitions on the DnSS are in phase with transitions on the DnCLK signal.                                                                                                                                                                                           |

| DnSS[5:0]  | 0   | 12  | <b>DOWNSTREAM SUB-SYMBOL:</b> These 6 LVDS outputs for the Ring interface carry the divided 42-bit symbol for the upstream port of the next node.                                                                                                                                                                                                                                         |

| TxCLK      | I   | 1   | <b>TRANSMIT CLOCK:</b> On the Client interface, all transmit port signals are synchronous to the rising edge of this clock.                                                                                                                                                                                                                                                               |

| TxT[1:0]   | Ι   | 2   | <b>TRANSMIT TYPE:</b> On the Client interface, this field defines (as head, data, frame or null) the contents of TxS:<br>in the previous clock cycle when PIPE is asserted, plpelined timing.<br>in the current clock cycle when PIPE is negated, non-plpelined timing.                                                                                                                   |

| TxS[31:01] | I   | 32  | TRANSMIT SYMBOL: On the Client interface, these signals form the data path of the transmit port.                                                                                                                                                                                                                                                                                          |

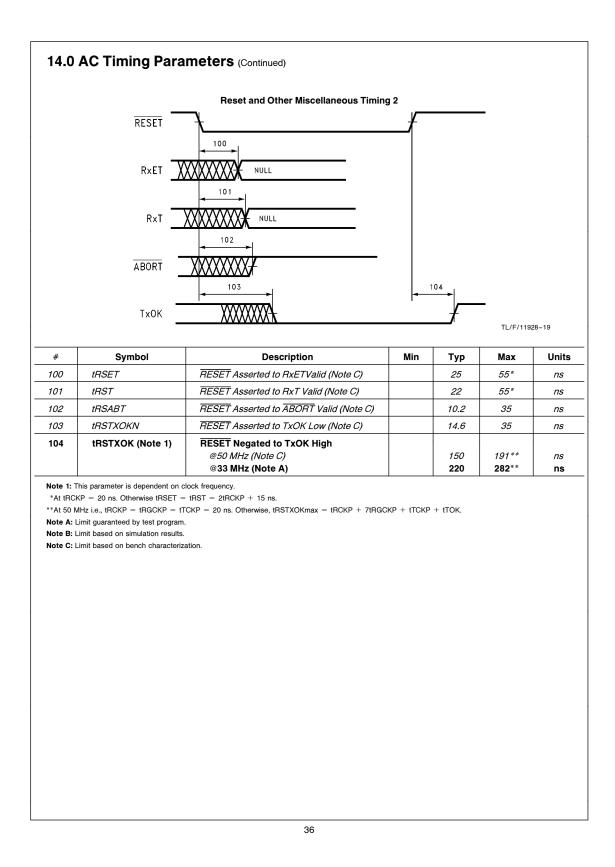

| ТхОК       | 0   | 1   | <b>TRANSMIT OKAY:</b> On the Client interface, this is the transmit port status signal. It tells the client whether or not another non-null symbol can be accepted. Loading of non-null symbols must cease within 20 symbols of the negation of TxOK. Transmission may not resume until TxOK is reasserted.                                                                               |

| RxCLK      | I   | 1   | <b>RECEIVE CLOCK:</b> On the Client interface, all receive port signals are synchronous to the rising edge o this clock. Except RxSTALL, which is sampled on the following edge of RxCLK.                                                                                                                                                                                                 |

| RxT[1:0]   | 0   | 2   | <b>RECEIVE TYPE:</b> On the Client interface, this field defines (as head, data, frame or null) the contents of RxS: in the next clock cycle for when PIPE is asserted, pipelined timing. in the current clock cycle when PIPE is negated, non-pipelined timing.                                                                                                                          |

|            | 0   | 32  | RECEIVE SYMBOL: On the Client interface, these signals form the data path of the receive port.                                                                                                                                                                                                                                                                                            |

| 1.0 Sig         | 1.0 Signal Description (Continued) |     |                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

|-----------------|------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Pin Name        | I/O                                | No. | Description                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| RxSTALL         | Ι                                  | 1   | <b>RECEIVE STALL:</b> On the Client interface, when RxSTALL is asserted:<br>When PIPE is asserted, pipelined timing: RxS shall remain for the next clock cycle.<br>When PIPE is negated, non-pipelined timing: RxT will indicate a null for the next clock cycle and RxS<br>shall remain. |  |  |  |  |  |  |  |

| RxOE            | Ι                                  | 1   | <b>RECEIVE OUTPUT ENABLE:</b> On the Client interface, when asserted, this signal enables outputs RxS[31-0]. When negated, the RxS are TRI-STATE.                                                                                                                                         |  |  |  |  |  |  |  |

| RxET[1:0]       | 0                                  | 2   | <b>RECEIVE EARLY TYPE:</b> On the Client interface, this field identifies in advance whether the information entering the Rx Port block is a head, data, frame or null.                                                                                                                   |  |  |  |  |  |  |  |

| RxNBL<br>[3:0]  | 0                                  | 4   | <b>RECEIVE NIBBLE:</b> On the Client interface, it contains one of the 16 selectable fields of two readable internal areas (Diagnostics bits, RxS driver).                                                                                                                                |  |  |  |  |  |  |  |

| RxSEL<br>[3:0]  | I                                  | 4   | <b>RECEIVE SELECT:</b> On the Client interface, selects one of the 16 fields appearing on the RxNBL. Codes from 0 to 7 select 4 bit fields at the current output driver of RxS, codes of 8 or above select internal diagnostics status bits.                                              |  |  |  |  |  |  |  |

| V <sub>CC</sub> | N/A                                | 13  | POWER PINS                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| GND             | N/A                                | 29  | GROUND PINS                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

Note 1: SignalName: The indicates that the signal is active low.

The following sections assume a 50 MHz ring clock. Note that the QR0001 has a maximum ring clock frequency of 33 MHz.

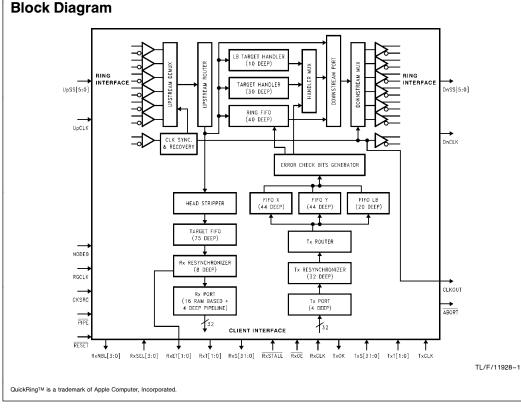

### 2.0 Basic Structure

The QuickRing Controller has two interfaces: the Ring Interface and the Client Interface. Each interface has two ports. All ports on the QR0001 are unidirectional so that incoming and outgoing data can be queued simultaneously.

### The two Ring interface ports are:

- 1. upstream port for arriving traffic,

- 2. downstream port for departing traffic.

The Ring Interface forms the link to other nodes on the point-to-point QuickRing architecture. QuickRing connects multiple nodes by attaching the upstream port of each node to the downstream port of another node. The ring ports, upstream and downstream, are 6 bits wide plus a clock. The ring interface is implemented using LVDS drivers and receivers. The Ring Interface signals are not accessible from the board except through the controller. The on board logic connects to the QR0001 controller via the Client interface.

#### The two Client Interface ports are:

- 1. the transmit port for locally generated symbol streams, and

- 2. the receive port for locally-absorbed symbol streams.

The transmit and receive ports have a 32-bit data path which use TTL compatible I/Os. The Transmit (Tx) and Receive (Rx) ports each have a separate clock plus control signals for information flow. Also, some QR0001 internal status bits can be read through the receive interface. All on board circuitry interfaces to the Client transmit and receive ports, never to the Ring ports.

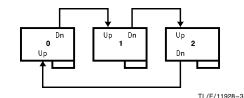

FIGURE 2.1. The QuickRing Controller has four ports

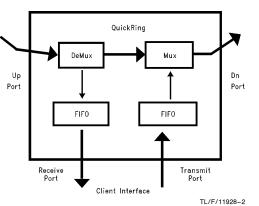

QuickRing transmits data streams between nodes on the ring. The goal of QuickRing is to pipeline data streams and not just to facilitate memory access. Imagine connecting two cards together via a FIFO chip. One card can load data into its side of the FIFO, and the other card can extract data from the other side of the FIFO. QuickRing is logically equivalent to placing a large FIFO between pairs of QuickRing nodes. Cards connected through QuickRing form a ring. Refer to *Figure 2.2*.

### 2.0 Basic Structure

FIGURE 2.2. Logical Data flow (QuickRing Virtual FIFOs)

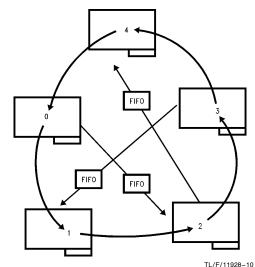

*Figure 2.3* shows that data physically moves in a ring from card to card, data traverses the ring until it arrives at the final destination. Physical data flow is unidirectional, and propagates downstream between nearest neighbors.

FIGURE 2.3. Physical Data Flow in QuickRing

opoor block tokito (Exert bit)

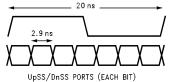

#### FIGURE 2.4. A Sub-Symbol is Multiplexed Every 2.9 ns

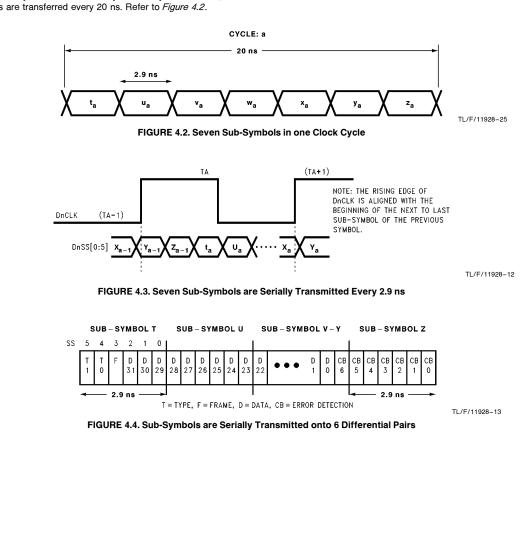

The ring, formed by connecting Up and Dn ports of adjacent QuickRing controllers, carries one 42-bit symbol every 20 ns. The 42-bit symbol is composed of:

- 32 bits of data,

- 1 Frame bit,

- 2 control bits and

- 7 bits of EDC.

To transmit 42 bits in 20 ns, QuickRing divides the 42-bit symbol into 7 sub-symbols, each sub-symbol is 6 bits wide. The controller then multiplexes the sub-symbols onto the 6 LVDS pairs on the downstream port. A 7th LVDS clock signal, at 50 MHz (maximum), accompanies every 42-bit symbol transmission. Refer to *Figure 2.4*.

### 3.0 Client Interface

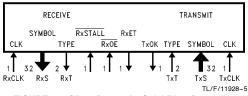

#### 3.1 Type and Symbol Fields at the Client Ports

The QuickRing client can multiplex multiple independent data streams onto and from the transmit (Tx) and receive (Rx) ports of the controller. The type fields (TxT[1:01], RxT[1:01]) distinguishes the contents of the symbol (main data) fields (TxS[31:0], RxS[31:0]). The type field identifies the nature of the symbol field information at the 32-bit ports as: head, data, frame or null.

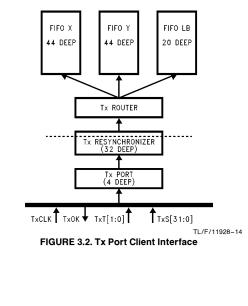

The transmit port can be thought of as the input to a bank of fast, deep FIFOs, connected to other nodes on the ring. The receive port can be treated as the output of the bank of FIFOs connected to other nodes on the ring. *Figure 3.1* illustrates the controller's client interface.

FIGURE 3.1. Client Ports of a QuickRing Controller

#### 3.2 Client Transmit Port

*Figure 3.2* shows the block diagram of the transmit port. The transmit block of QR0001 is formed by: Tx Port, Tx Resynchronizer, Tx Router, and 3 independent FIFOs. All of these blocks form the transmit pipeline.

- 1. The Tx Port is the first stage into the transmit pipeline. The Transmit port is a 4 deep pipeline.

- The Tx Resynchronizer is a 32-deep asynchronous FIFO in the path between the Tx Port and the Tx Router.

- Note: The Tx Resynchronizer will handle the frequency disconnect between the Tx Port and ring logic. This function will be implemented on the next QuickRing device—QR1001.

- 3. The Tx Router directs the streams to the appropriate channel efficiently (described later).

- 4. FIFOs X and Y are meant for handling one independent high bandwidth stream each, and the LB (Low Bandwidth) FIFO is meant for low bandwidth transmissions. The FIFOs contain the data/frame part of the client stream. (The Head information is held in a separate holding latch internally.)

The **sole** purpose of providing two normal (high bandwidth) FIFOs (X and Y) is so that the client may switch from transmitting one stream to another without slowing down or wasting available ring bandwidth during the context switch.

On release of  $\overrightarrow{\text{RESET}}$  any payload symbols at the transmit port are ignored until the first head symbol is presented at the input of the Tx Port. QR0001 always checks for consecutive heads and ignores all redundant heads. The type and symbol fields are latched internally according to the timing specified by the state of the  $\overrightarrow{\text{PIPE}}$  signal.

When the client starts a transmission, it writes a head followed by a stream of payloads. QR0001 receives these symbols through the transmit port and directs them to either the X, Y or LB FIFO. Any head symbol with the CONN (see Section 3.6) field equal to 1 is always routed to the LB FIFO, as is every payload symbol following such a head. Any other head with the CONN field equal to 0 and all payloads following such a head are routed to either the X or Y FIFO.

TI /F/11928-4

QR0001 can handle one Independent data stream through each of the X and Y FIFOs, a total of two streams at once. Even if the FIFO is not full, the FIFO will store data associated only with a single head. Multiple data streams with various heads will not be held in a single FIFO. The subsequent data streams, with different heads, will be held in the Tx pipeline, until either FIFO X or Y empties, and the data (with the different head) is allowed to further proceed in the pipeline.

The LB FIFO. Several streams with different heads can flow through the LB FIFO at one time. When several payloads are loaded, following a signal head, a head will be generated for each payload.

For all transmissions, low bandwidth or normal, QR0001 will keep TxOK asserted for as long as there is space for 20 or more symbols in the transmit pipeline. As soon as the transmit pipeline has space for **only** 20 more symbols, TxOK negates. The initial negation of TxOK indicates to the client interface that it must stop transmitting non-null symbols soon. TxOK is the only handshake mechanism at the transmit port. If TxOK asserts again, the count is voided and the client can write to the TxPort as many symbols as it wants. If TxOK negates again, the client must stop writing non-null symbols within 20 valid transactions.

The client may pause transmission at any time by presenting the null symbol code to the transmit port.

When the client interface wishes to begin transmission of a data stream, the client first writes a head (H) to the transmit port. From then on, every payload symbol (type = data or frame) sent to the transmit port is assumed to belong to the stream identified by the head. The data stream that the client writes at the transmit port is unbounded. However, if a new head is written to the transmit port, the data stream that follows is associated with the new head. If at any time the client is not prepared to transmit either a payload or a new head, a null symbol (N) may be introduced into the transmit data stream. Null symbols do not propagate into the QR0001 QuickRing controller. Logically distinct data streams can be multiplexed together and loaded into the QR0001 transmit port. The client is free to switch between source streams at its convenience, as long as it introduces a new head when the switch occurs.

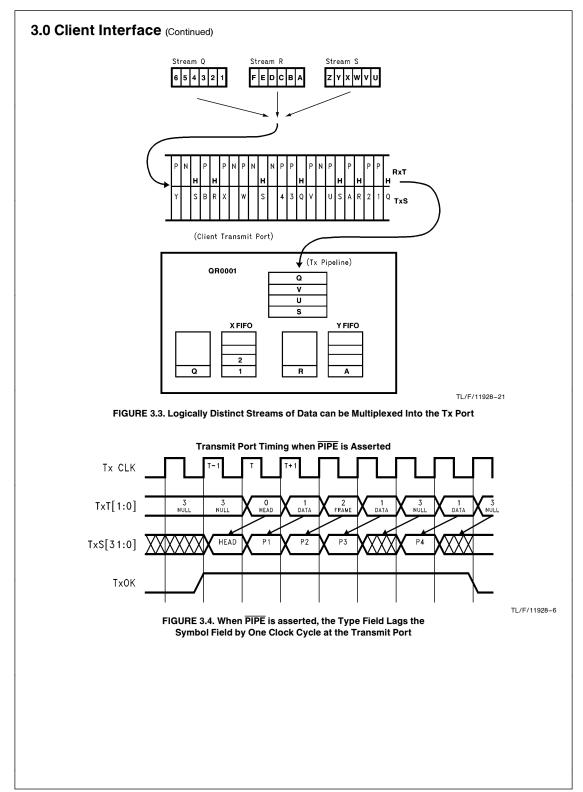

*Figure 3.3* shows how three independent streams (high bandwidth) may be multiplexed from the Client Transmit Port into the QuickRing controller. Stream Q goes first, sending 2 payloads. It is followed by 1 payload from stream R, then by 2 payloads from stream S. Two more symbols from stream Q are sent, etc.

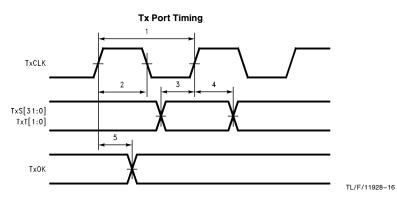

#### 3.3 Transmit Port Timing Relationships

When  $\overrightarrow{\text{PIPE}}$  is asserted (low voltage level) the type field, TxT, accompanying the symbol field, TxS, is loaded into the controller one clock cycle after the symbol that it identifies. See *Figure 3.4*. When a symbol is presented on TxS at time t, then the corresponding code is presented on TxT at time t+1. The purpose of delivering the TxT field one clock cycle after the symbol is so that a simple, synchronous state machine has one full clock cycle to compute the TxT code without using external latches on the symbol field.

When  $\overrightarrow{\text{PIPE}}$  is negated (high voltage level), the type field TxT accompanying the symbol field TxS is loaded into the controller during the same clock cycle as the symbol it identifies. Refer to *Figure 3.5*.

The TxOK function and timing remains unchanged regardless of the level of the  $\overline{\text{PIPE}}$  signal. Giving a 20 symbol warning that transmission of non-null symbols may need to cease.

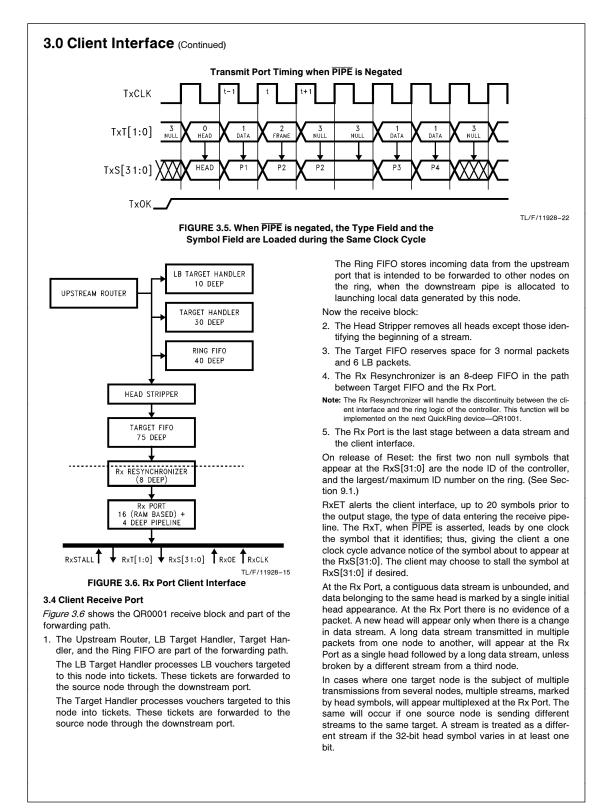

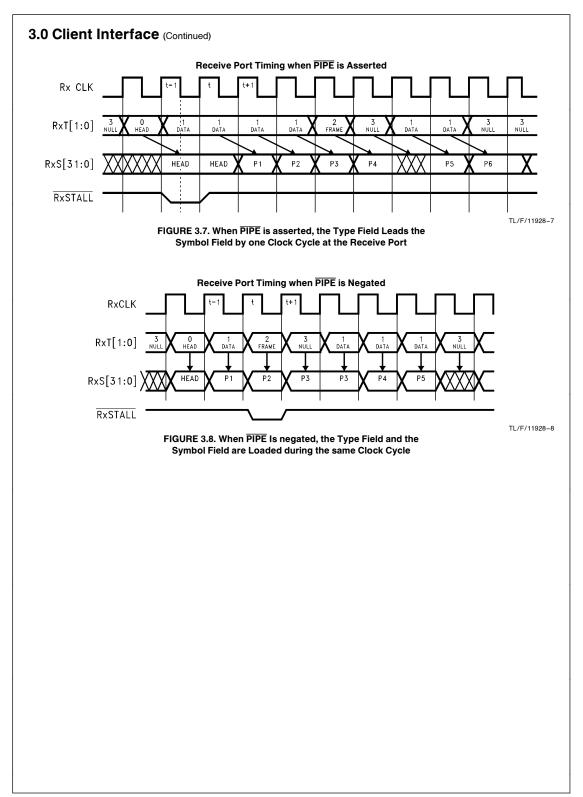

#### 3.5 Receive Port Timing Relationships

When  $\overrightarrow{\text{PIPE}}$  is asserted (low level), the type field, RxT, at time t indicates the type of symbol presented at the output, RxS, at time t+1. See *Figure 3.7*. This is true as long as  $\overrightarrow{\text{RxSTALL}}$  is negated.

If RxSTALL is asserted when PIPE is asserted (pipeline timing mode):

The RxS[31:0] output will stall at the first non-null symbol encountered in the pipeline after RxSTALL is asserted. The symbol on RxS will persist through next clock cycle unless it corresponds to a null symbol. The RxSTALL input signal is only capable of holding a nonnull symbol at the RxS output.

The client may need to examine some symbols within the symbol stream in order to determine their disposition. It is highly desirable to do so without employing added data path buffering external to the controller. QuickRing allows the client to examine the contents of the symbol at the RxS output through a combination of RxSTALL, RxSEL and RxNBL, even while the RxS output drivers may be disabled.

To further aid in the receive stream management, the symbol type field just entering the Rx Port Block of the receive pipeline is visible on RxET. Thereby the client can preview the symbol type in the receive pipeline before it appears on the RxS outputs. Thus it is possible to detect the presence of a head, data, or frame in the pipeline even if up to 19 more symbols are stored ahead of it.

When  $\overrightarrow{\text{PIPE}}$  is negated (high level), then the value of the type field RxT, TxT at time t corresponds to the value of the symbol field at the same time t. (See *Figure 3.8.*) When two QuickRing controllers are connected to form a bridge, the TxOK is connected to  $\overrightarrow{\text{RxSTALL}}$  of the other controller. (Currently, an external flip-flop may be needed to satisfy the setup/hold times.)

If  $\ensuremath{\mathsf{RxSTALL}}$  is asserted when  $\ensuremath{\mathsf{PIPE}}$  is negated (high level), at the next positive edge of clock:

- 1. RxT is forced to Null and

- 2. The RxS[31:0] persists.

To summarize the Client Port Timing:

At the Rx Port, a non-null symbol remains valid at the RxS output in the presence of  $\overline{\text{RxSTALL}}.$

At the Tx Port, when TxOK negates it indicates that the FIFO is nearly full and the client must stop transmission within 20 non-null symbols.

The  $\overrightarrow{\text{PIPE}}$  input determines how the type fields, RxT and TxT, identify a symbol as it appears at RxS and TxS respectively.

At the receive port, many different arriving streams may be multiplexed together. Every switch to a new stream context is marked by a new head symbol. The multiplexed stream that is loaded into a controller at a source node is probably different than the de-multiplexed stream that arrives at the target node.

The QuickRing protocol does not preserve the order of multiplexed streams, but it does preserve the first-in-first-out ordering of each individual stream.

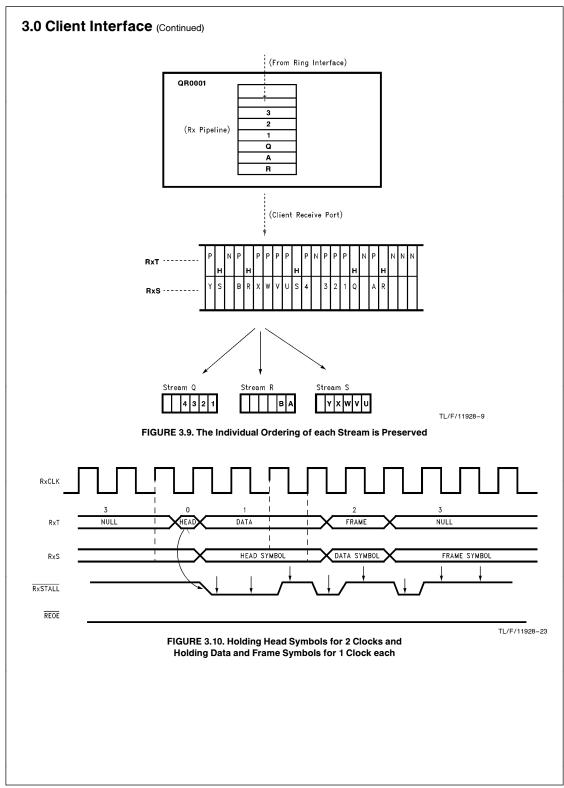

*Figure 3.3* relates to *Figure 3.9*. It shows that even though stream Q was loaded first, in *Figure 3.3*, stream R, arrives first, in *Figure 3.9*. Notice that at the output, the order within each individual stream is preserved.

## 3.5.1 Client Receive Port Interface Recommendations (PIPE asserted)

It is recommended, when interfacing to the Client Receive Port, to hold  $\overline{RxSTALL}$  negated during normal operation. When the Client interface detects a Non-Null type, it may assert  $\overline{RxSTALL}$  during the next clock cycle to stall that particular symbol and the next Non-Null type (if available). See *Figure 3.10*.

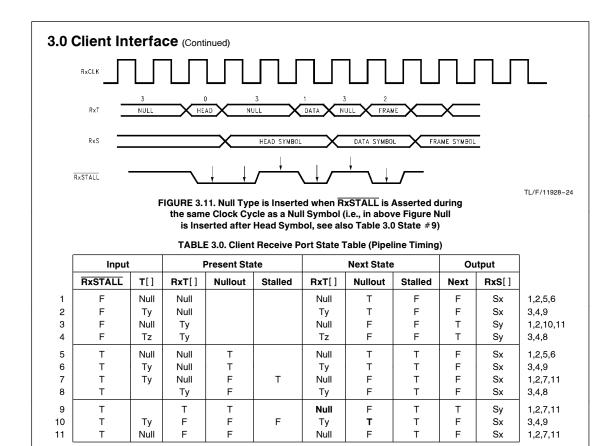

BE AWARE that if RxSTALL is asserted during a clock cycle of a NON-NULL Type that follows (later in time) a NULL type, the Receive Client interface will stall a NULL type for the next clock cycle. A Null Type will be inserted into the next clock cycle even if the Receive FIFO contains a NON-NULL type next. This could reduce the performance of the receive client interface by half. See *Figure 3.11*.

RxSTALL Chip input signal which holds non-null data at RxS[].

T[] (Not externally observable.) The type of symbol which should appear on RxT[] during the next clock cycle unless the symbol marked by RxT[] is waiting behind another stalled symbol at RxS[].

RxT[] The type code for the symbol that should appear at RxS[] during the next clock cycle, unless RxS[] is currently non-null and is being stalled by RxSTALL.

Nullout (Not externally observable.) A state variable that is set to TRUE when the current value of RxS[] is volatile—not stallable and subject to being overwritten by an arriving non-null symbol.

Stalled (Not externally observable.) A state variable that takes on the value of RxSTALL during the previous clock cycle. Next (Not externally observable.) The state machine output that loads the RxS[] output with the next non-null value in the pipeline.

RxS[] The 32-bit symbol output bus of the Receive Port.

T TRUE.

F FALSE.

Null The symbol type code representing the absence of a symbol.

Ty, Tz Symbol type codes for a non-null symbol.

Sx The value of RxS[] unchanged from the previous cycle.

Sy The new value of RxS[] whose symbol type code appeared on RxT[] during the previous clock cycle.

The state table on the previous page describes the behavior of the QR0001 Receive Port. For convenience each table row has been numbered on the left-hand side, and each of the possible next-case rows is listed on the right-hand side. Following the state table is a description of the input, output, and state variables, as well as of the entries within the state table.

Row number 9 of the state table shows that the next state always indicates a null symbol on RxT[], regardless of whether or not a non-null symbol is pending behind symbol Sy. This is an *inefficient but legal* behavior, as no symbol is lost. Unfortunately, until RxSTALL is released, the Receive Port will remain in rows 9, 7, and 11, none of which will allow the arrival of the next non-null symbol to be detected on RxT[].

Entry number 10, however, represents a condition where a non-null symbol can arrive at, and disappear from, RxS[] without the possibility of being stalled. This represents *ille-gal behavior* of the QR0001 Receive Port. Entry into the condition represented by row 10 must be handled specially or system data loss will result.

#### Workarounds for No-Stall Bug

There are three alternatives available to work around the no-stall bug: (1) Release  $\overrightarrow{RxSTALL}$  for one clock cycle only when RxT[] takes on a non-null value, leaving  $\overrightarrow{RxSTALL}$  asserted at all other times; (2) build a client system that is guaranteed not to require that any symbol remain on  $\overrightarrow{RxSI}$  for more than two clock cycles; or (3) provide an external latch to save symbols that might have been lost due to entry to row 10, and stall the next symbol in row 7 or 11 until the external latch can be read.

Alternative #1. Leave RxSTALL normally asserted. This is the easiest method. It restricts the Receive port to rows, 1, 2, 5, 6, and 9. RxSTALL is released only to enter rows 1 and 2. This is easily accomplished by releasing RxSTALL in response to each non-null value, but only when that value is no longer needed at RxS[]. RxT[] will remain non-null for only one clock cycle, and this event will have to be remembered by the client state machine. Unfortunately, because the next state result of row 9 does not update RxT[], the fastest that a client may receive data is once every other clock cycle. If there is always another symbol ready in the pipeline, then the Receive Port will toggle between rows 9 and 2, and RxS[] will be updated only on the exit from row 9.

#### TL/F/11928-32

Alternative #2. Design a client system that can always consume a received symbol within two clocks. This may be impractical, but if the client system fits this description, then there is no problem. This is because the next state of row 10 is entered in order to stall a symbol that just appeared upon the exit from row 3, and row 10 preserves the symbol for exactly one more clock cycle. Every next-case row out of row 10 will advance RxS[] to the next symbol, so the unstallable symbol always appears at RxS[] for exactly two clock cycles.

Alternative #3. Provide external storage for the volatile symbol, and stall the next symbol at RxS[] until the saved copy can be used. The only entrance to row 10 is from row 3. External logic must monitor the interface for the transition from row 3 to row 10 or 11, and must both save the unstallable symbol and hold RxSTALL asserted until the external copy can be used. This solution requires that external logic emulate the QR0001 Receive Port state machine. Although the T'[] input variable and the Nullout and Stalled state variables are not observable on output pins of the chip, it is possible to compute them externally. An external state machine can deterministically compute the previous state and the value input T'[] that helped cause it. Although this information is available one cycle late, there is time to stall the next symbol until the no-stall symbol register is being freed up.

The advantage of alternative 1 is its simplicity, if it is not necessary to receive symbols more often than once every other clock cycle. The advantage of alternative 2 is that, if it happens to describe your system (if it's free), then you will not encounter the no-stall bug. The advantage of alternative 3 is that the client can keep up with high-bandwidth received streams that deliver symbols on every clock cycle.

#### 3.6 Client Interface Field Definitions

Table 3.1 shows the symbol field definitions for the Tx and Rx ports. Refer to Section 3.13 for details.

| TABLE 3.1. Tx and Rx Port Symbol Field Definitions | 3 |

|----------------------------------------------------|---|

|----------------------------------------------------|---|

| Field                                                         | Descriptions                                                                                                                                                                                                                                                |

|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Type[1:0]                                                     | At the client ports, distinguishes head, data, frame, and null.                                                                                                                                                                                             |

| CONN[1:0]                                                     | The connection code (CON[1:0]) provides<br>two types of transmission, normal and low<br>bandwidth. Low-bandwidth streams are<br>transmitted with higher priority.                                                                                           |

| TRGT[3:0]                                                     | The target field contains the node ID of the target of the associated payload.                                                                                                                                                                              |

| SRCE[3:0]                                                     | The source field contains the node ID of the source of the associated payload.                                                                                                                                                                              |

| HOP1[3:0]<br>HOP2[3:0]<br>HOP3[3:0]<br>HOP4[3:0]<br>HOP5[3:0] | They distinguish between unique streams<br>whose source-to-target routes are<br>identical. In a multiple-ring topology, they<br>supplement source and target ID fields to<br>route streams as they hop from ring to ring<br>(See section on Ring of Rings). |

At the client ports ACCess field should be [00]. The ACC field is valid only in the ring ports. Refer to Sections 4.7 and 4.13 for more details.

Table 3.2 shows the values of the connection field (CONN[1:0]). If a LB connection is requested, QuickRing parcels the data or frame symbols presented at the Tx Port and transmits every payload in 2 symbol ring packets, 1 head and 1 payload.

**TABLE 3.2. Connection Field Definitions**

| CONN[1:0] | Name                    | Description                                                                                                                    |

|-----------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| 0         | Normal                  | Queue and accumulate<br>symbols from the same<br>stream at will, to maximize<br>system efficiency and<br>minimize system load. |

| 1         | Low Band-<br>width (LB) | Do not concatenate with<br>other data symbols from the<br>same stream. Results in two<br>symbol packets, head and<br>payload.  |

| 2         | N/A                     | Reserved                                                                                                                       |

| 3         | N/A                     | Reserved                                                                                                                       |

#### 3.7 Client Type Fields

The TxT[1:0] and RxT[1:0] fields are the type fields at the transmit and receive ports, respectively. They are encoded as shown in Table 3.3. Each 32-bit symbol written or read from the client ports is associated with one type field.

### 3.0 Client Interface (Continued) TABLE 3.3. Client Type (TxT/RxT) Field Definitions

| T [1] | T[0] | Name  | Description                                 |

|-------|------|-------|---------------------------------------------|

| 0     | 0    | Head  | Associated symbol is a head symbol          |

| 0     | 1    | Data  | Associated payload symbol is a data symbol  |

| 1     | 0    | Frame | Associated payload symbol is a frame symbol |

| 1     | 1    | Null  | No associated symbol                        |

#### 3.8 Transmit Port Head Fields

A head symbol must be loaded into the transmit port whenever the client wants to start a transmission, or when the context of the loaded symbols is switched to another stream. Redundant heads are acceptable to the controller transmit port. If multiple heads are loaded without intervening data or frame symbols, then all but the last head are ignored. The transmit port evaluates the connection, target, and all hop fields. The controller adds its own ID to the source field internally, based on the local node ID value that was set during initialization. The ACCess field is ignored and should be set to zero by the client. Table 3.4 shows the format of a head symbol that the local client must load into the Tx Port to establish a connection.

#### **TABLE 3.4. Transmit Port Head Fields**

| TxT[1:0] |       | TxS[31:0] |       |       |       |       |      |      |      |  |  |

|----------|-------|-----------|-------|-------|-------|-------|------|------|------|--|--|

| 1:0      | 31:30 | 29:28     | 27:24 | 23:20 | 19:16 | 15:12 | 11:8 | 7:4  | 3:0  |  |  |

| Туре     | Acc   | Conn      | Srce  | Trgt  | HOP   |       |      |      |      |  |  |

| [0]      | хх    | Conn      | xxxx  | Trgt  | Hop1  | Hop2  | Нор3 | Hop4 | Hop5 |  |  |

#### 3.9 Receive Port Head Fields

The receive port head symbol format contains the same fields as are found in heads at the transmit port, but are shifted from their original positions when they exit the receive port. The purpose is to support routing of streams in multiple-ring topologies. Head symbols only appear at the receive port when there is an actual change of head. Redundant head symbols are always deleted. Head symbols at the receive port hold valid information in the connection, source, target, and all hop fields. The ACCess field is undefined and should be ignored by the client.

Table 3.5 shows the format of the head field at the receive port of the controller.

**TABLE 3.5. Receive Port Head Fields**

| RxT[1:0] |       | RxS[31:0] |       |       |       |       |      |      |      |  |  |

|----------|-------|-----------|-------|-------|-------|-------|------|------|------|--|--|

| 1:0      | 31:30 | 29:28     | 27:24 | 23:20 | 19:16 | 15:12 | 11:8 | 7:4  | 3:0  |  |  |

| Туре     | Acc   | Conn      | Trgt  | HOP S |       |       |      |      | Srce |  |  |

| 0        | xx    | Conn      | Trgt  | Hop1  | Hop2  | Нор3  | Hop4 | Hop5 | Srce |  |  |

#### 3.10 Payload Symbols at the Rx and Tx Ports

Payload symbols at the transmit or receive ports follow the head symbol that identifies them. A payload consists of a sequence of data and/or frame symbols that are distinguished by a 1 or 2 in the accompanying type field, refer to Table 3.6. The identification of a frame or data symbol is

encoded in the Type field at the Tx and Rx port. If the type field has a value of 1, it is a data symbol, and if the value is 2, then it is a frame symbol. The type field at the receive port leads the symbol field that it identifies by one clock cycle, and at the transmit port it lags the symbol field by one clock, when PIPE is asserted. However, if the controller is in non-pipelined timing, PIPE is negated, the type field corresponds to the symbol at the same clock

#### TABLE 3.6. Payload Symbols at Tx/Rx Ports

| Type[1:0] | Tx/Rx S[31:0]                    |

|-----------|----------------------------------|

| 1         | DATA. User Defined Information   |

| 2         | FRAME. User Denfined Information |

#### 3.11 Null Symbols at the Rx and Tx Ports

The lack of a head symbol or payload symbol is indicated, at the Rx port, by null symbols whose type field is 3, and whose other bits are undefined outputs or don't care inputs. At the Tx port, if a head or payload is not ready to be transmitted, a null symbol code should be presented at the TxT. The value of the type fields at the client ports is as indicated in Table 3.7.

TABLE 3.7. Null Symbol Format

| Type[1:0] | Tx/Rx S[1:0]     |

|-----------|------------------|

| 3         | NULL. Don't Care |

| 3         | NULL. Don't Care |

## 3.12 The HOP fields and the Uniqueness of Symbol Streams

The identity of a symbol stream is fixed by the combination of the connection, source, target, and hop fields. If the heads of symbol streams differ in any of these fields, then they represent different symbol streams.

The symbols of a unique stream will always arrive in order. Multiple streams targeted at the same node may arrive interleaved. The interleaving will always be indicated by an appropriate head symbol, identifying the switch in stream context.

The Hop Fields were created to route packets through bridges in multiple ring topologies. In single ring topologies they have the function of identifying different streams. The hop fields can be used to distinguish between 2<sup>20</sup> different data streams in a single ring. However, in multiple ring topologies, every time a bridge is crossed, one hop field is used. Therefore, it is lost for identifying unique data streams. Table 3.8 shows the hop field locations at the transmit port and Table 3.9 shows the hop fields at the receive port.

If the particular node is a bridge to another ring, the PIPE signal should be negated, high voltage level. The HOP fields rotate the same regardless of the state of the PIPE input.

The actual rotation of the Source, Target, and HOP fields occurs at the client receive port, see Tables 3.8, 3.9. The HOP fields rotate between the Transmit Client and the Receive Client as follows (from Receive Client perspective):

Source bits (27:24) shift to bit field (3:0)

All other HOP fields (including Target field) move up one HOP field to the next more significant 4-bit positions (Ex HOP 5 moves from (3:0) → 7:4)).

Given this information the system interface should be able to determine how the Source, Target and HOP fields rotate up to a Ring of Rings architecture including 5 HOPs.

When the Client Port Receives a data stream the head contains the path taken by the stream to reach this particular target. To look at the Head and determine where the source is and how many HOPs the stream encountered requires knowledge of the ring topology. It is assumed that during the initialization process each node will build up a table of addresses of all the NODEs in the system. When a Head is received, it can be compared to the addresses in the table to determine the source of the data stream. All un-used HOP fields may be used as Stream ID.

| TABLE 3.8. | нор | Fields | at the | Tx Port |

|------------|-----|--------|--------|---------|

|            |     |        |        |         |

| 27:24 | 23:20 | 19:16 | 15:12 | 11:8  | 7:4   | 3:0   |

|-------|-------|-------|-------|-------|-------|-------|

| Srce  | Trgt  | Hop 1 | Hop 2 | Hop 3 | Hop 4 | Hop 5 |

#### TABLE 3.9. HOP Fields at the Rx Port

| 27:24 | 23:20 | 19:16 | 15:12 | 11:8  | 7:4   | 3:0  |

|-------|-------|-------|-------|-------|-------|------|

| Trgt  | Hop 1 | Hop 2 | Hop 3 | Hop 4 | Hop 5 | Srce |

| 3.0 C                                                                                      | lient Inte                          | rtace (Cor       | ntinued)       |                   |                                                          |                                  |                 |              |            |  |  |  |

|--------------------------------------------------------------------------------------------|-------------------------------------|------------------|----------------|-------------------|----------------------------------------------------------|----------------------------------|-----------------|--------------|------------|--|--|--|

| 3.13 Sur                                                                                   | nmary of Clie                       | nt Port Field F  | Formats        |                   |                                                          |                                  |                 |              |            |  |  |  |

|                                                                                            |                                     |                  | TABL           | .E 3.10. Client P | ort Fleid Form                                           | nats                             |                 |              |            |  |  |  |

|                                                                                            |                                     |                  |                | Tx Port He        | ad Field                                                 |                                  |                 |              |            |  |  |  |

| Туре                                                                                       | Acc                                 | Conn             | Srce           | Trgt              |                                                          |                                  | НОР             |              | 1          |  |  |  |

| TxT[1:0]                                                                                   | TxS[31:30]                          | TxS[29:28]       | TxS[27:24      | ] TxS[23:20]      | TxS[19:16]                                               | TxS[15:12]                       | TxS[11:8]       | TxS[7:4]     | TxS[3:0    |  |  |  |

| 0                                                                                          | XX                                  | Conn             | XXXX           | Trgt              | HOP 1                                                    | HOP 2                            | HOP 3           | HOP 4        | HOP 5      |  |  |  |

|                                                                                            |                                     |                  |                | D:: Dent Lie      | 1 5:-14                                                  |                                  |                 |              |            |  |  |  |

| Туре                                                                                       | Acc                                 | Conn             | Trgt           | Rx Port He        | ad Field                                                 | НОР                              |                 |              | Srce       |  |  |  |

| RxT[1:0]                                                                                   | RxS[31:30]                          | RxS[29:28]       | RxS[27:24      | ] RxS[23:20]      | RxS[19:16]                                               | RxS[15:12]                       | RxS[11:8]       | RxS[7:4]     | RxS[3:0    |  |  |  |

| 0                                                                                          | XX                                  | Conn             | Trgt           | HOP1              | HOP2                                                     | НОР3                             | HOP4            | HOP5         | Srce       |  |  |  |

|                                                                                            |                                     |                  |                |                   |                                                          |                                  |                 |              |            |  |  |  |

|                                                                                            |                                     |                  | Тх             | and Rx Ports Pa   | ayload Symbo                                             | ls                               |                 |              |            |  |  |  |

| T[1:0]                                                                                     | T[1:0] Tx/Rx S[31:0]                |                  |                |                   |                                                          |                                  |                 |              |            |  |  |  |

| 1                                                                                          | DATA. User Defined Information      |                  |                |                   |                                                          |                                  |                 |              |            |  |  |  |

| 2                                                                                          | 2 FRAME. User Defined Information   |                  |                |                   |                                                          |                                  |                 |              |            |  |  |  |

|                                                                                            |                                     |                  |                |                   |                                                          |                                  |                 |              |            |  |  |  |

|                                                                                            | <u> </u>                            |                  |                |                   | Port Null Sym                                            | ibols                            |                 |              |            |  |  |  |

| T[1:0]<br>3                                                                                |                                     |                  |                |                   | /Rx S[31:0]                                              |                                  |                 |              |            |  |  |  |

| 3                                                                                          |                                     |                  |                | Inui              | I. DUILL CALE                                            |                                  |                 |              |            |  |  |  |

|                                                                                            |                                     |                  |                | Node ID I         | Format                                                   |                                  |                 |              |            |  |  |  |

| RxT[1:0]                                                                                   | RxS[31:28]                          |                  |                |                   | RxS[27:                                                  | .0]                              |                 |              |            |  |  |  |

| non-null                                                                                   | Node ID                             | 111111.          |                |                   |                                                          |                                  |                 |              |            |  |  |  |

|                                                                                            |                                     |                  |                |                   |                                                          |                                  |                 |              |            |  |  |  |

|                                                                                            |                                     |                  |                | Max ID F          | ormat                                                    |                                  |                 |              |            |  |  |  |

| RxT[1:0]                                                                                   | RxS[31:28]                          |                  |                |                   | RxS[27:                                                  | 0]                               |                 |              |            |  |  |  |

| non-null                                                                                   | Max ID                              | 111111.          | <u></u>        |                   |                                                          | <u></u>                          |                 |              |            |  |  |  |

| 3.14 Re:                                                                                   | adable Regist                       | ers              |                |                   | Node ID: A                                               | ddress of the I                  | Node            |              |            |  |  |  |

|                                                                                            | nt can read th                      |                  | l registers, [ | Diagnostics       |                                                          | gest ID on the                   |                 |              |            |  |  |  |

| •                                                                                          | and Receive                         |                  |                |                   |                                                          | s: Individual bi                 | ts are set de   | pending on t | he origir: |  |  |  |

|                                                                                            | xSEL[0:3] and<br>also be read wh    |                  |                |                   | of the error.                                            |                                  |                 |              |            |  |  |  |

| selects a                                                                                  | a 4-bit field wi                    | ithin the 32-bit | t internal reg | gisters and       |                                                          | et due to an E<br>et due to an / |                 |              | t tha un   |  |  |  |

|                                                                                            | hat field on the<br>s bits [18:8] w |                  |                | 0                 | stream port.                                             |                                  | ADDIT SYTTDO    | receiveu a   | t the up   |  |  |  |

| is reset.                                                                                  |                                     |                  |                | Salert Hing       |                                                          | set due to an e                  |                 |              |            |  |  |  |

| ТА                                                                                         | BLE 3.11. Dia                       | gnostics Regi    | ister (Read    | Only)             | two consecute the ring.)                                 | utive heads. ([                  | Detected on     | the upstrear | n port o   |  |  |  |

| 31:1                                                                                       | 9 18:12                             | 2 11:8           | 7:4            | 3:0               | Bit 11 is set due to an invalid address detected (on the |                                  |                 |              |            |  |  |  |

| Resen                                                                                      | ved Syndro                          | me Error         | MaxID          | Node ID           | ring).<br>Syndrome V                                     | Word: Points t                   | o the hit in er | ror detector | t through  |  |  |  |

| Reserved Syndrome Error MaxID Node ID Syndrome Word: Points to the bit in error detected t |                                     |                  |                |                   |                                                          |                                  |                 |              | i unougn   |  |  |  |

|                                                                                            | Word<br>S[6:0                       |                  |                |                   | EDC. All zer                                             | ros if no error(                 | s).             |              |            |  |  |  |

#### TABLE 3.12. Receive Symbol Register (Read Only)

31:0

#### The most recent 32 Bits of the RxS received.

Table 3.13 gives the decode for reading the various register bits.

#### TABLE 3.13. Register Access Decode

| RxSEL[3:0] | RxNBL[3:0]         | Description    |

|------------|--------------------|----------------|

| 0          | RxS[3:0]           |                |

| 1          | RxS[7:4]           |                |

| 2          | RxS[11:8]          |                |

| 3          | RxS[15:12]         |                |

| 4          | RxS[19:16]         |                |

| 5          | RxS[23:20]         |                |

| 6          | RxS[27:24]         |                |

| 7          | RxS[31:28]         |                |

| 8          | Diagnostics[3:0]   | Node ID        |

| 9          | Diagnostics[7:4]   | No. of Nodes   |

| 10         | Diagnostics[11:8]  | Error Status   |

| 11         | Diagnostics[15:12] | Syndrome Word  |

| 12         | Diagnostics[19:16] | Syndrome Word* |

| 13         | Diagnostics[23:20] | Reserved       |

| 14         | Diagnostics[27:24] | Reserved       |

| 15         | Diagnostics[31:28] | Reserved       |

\*Note: Bit 19 is reserved.

#### 3.15 Error Detection (see also Section 3.16)

The error detection code (EDC) field, CB[6:0] provides redundant parity checking to verify symbol integrity. The QR0001 implements a modified Hamming code algorithm that provides Double Error Detection (DED).

To reduce latency effects, this version of the QR0001 provides the syndrome word that can be read from the Diagnostics register to show bit(s) detected in error.

The syndrome word, S[6:0], consists of the Ex-OR of the Incoming check bits that were sent within the packet, CB[6:0], and new generated check bits for the packet (new generated, NGCB[6:0]).

A correct EDC field is transmitted with each symbol emitted from the downstream port. Every symbol that is received at the upstream port is passed through an EDC checking circuit. Any inconsistency causes the ABORT signal to assert, and an abort symbol to be transmitted at the downstream port. EDC fields are propagated through the chip core as required to support the above described functionality. The EDC field is not visible at the client ports.

The ABORT signal will also be asserted if an illegal address or illegal sequence of symbols is detected. The symbol which triggers ABORT assertion will contiue to move along the ring until reaching its target node. This requires that the ring be reset every time an abort is detected. The initial occurrence of an abort is captured in the diagnostic register. No subsequent abort will be logged (until the ring is reset).

Table 3.14 shows the matrix of data bits. An "X" indicates the bits that are "Exclusive-ORed" to generate each particular check bit. Check bit 6 is generated by "Exclusive ORing" all data and all check bits. CB[6:0] form the syndrome word.

Given a Single or Double bit error, the code has the following properties:

- 1. If the syndrome word: S[6:0] is zero (0), then there is No Error.

- If any of the syndrome bits: S[5:0], is not zero (0), and S6 is zero, then there is a Double Error. The particular bits in error can not be determined.

- 3. If any of the syndrome bits: **S**[5:0] are not zero (0) and **S6 is one**, then there is a Single Error in either the data or the check bits.

If a single bit in S[5:0] is one and S6 is one, then the corresponding CB is in error and the data is correct.

If more than 1 bit in S[5:0] is set to one and S6 is one, then the syndrome bits point to the data bit in error. See columns of Table 3.14. S[5:0] pinpoints to the position number in the mapping diagram at which bit is in error.

If all remaining bits, S[5:0] are zero and S6 is one, then CB6 is in error.

#### 3.16 QR0001 EDC Errors and Client "Abort" Pin Functionality

A bug has been identified in the abort operation. The QR0001 ABORT signal does not match the intended operation as mentioned above. The intended operation is that the following events will cause the ABORT pin to be asserted and generate an abort symbol that will propagate around

#### TABLE 3.14. Error Detection Matrix

|               |    |                                                              |    |    |    |    |    |    |    |    |    |    |    | ;  | 35 <b>-</b> E | Bit D | ata | Wo | rd |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |

|---------------|----|--------------------------------------------------------------|----|----|----|----|----|----|----|----|----|----|----|----|---------------|-------|-----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|

| CHECK<br>BITS | 35 | 34                                                           | 33 | 32 | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21            | 20    | 19  | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 |

| CB0           | Х  |                                                              | х  |    | х  |    | Х  |    | х  | Х  |    | х  |    | Х  |               | Х     |     | х  |    | х  |    | Х  |    | х  | Х  |    | Х |   | Х |   | х | х |   | X |

| CB1           |    |                                                              | х  | Х  |    |    | Х  | Х  |    | Х  | х  |    |    | Х  | х             |       |     | х  | Х  |    |    | Х  | Х  |    | х  | Х  |   |   | Х | х |   | х | Х |   |

| CB2           |    |                                                              | х  | Х  | х  | X  |    |    |    | Х  | х  | х  | Х  |    |               |       |     | Х  | Х  | х  | X  |    |    |    | Х  | х  | х | X |   |   |   | х | X | x |

| CB3           | Х  | Х                                                            |    |    |    |    |    |    |    | Х  | х  | х  | Х  | Х  | х             | Х     | Х   |    |    |    |    |    |    |    | х  | Х  | х | Х | Х | х | Х |   |   |   |

| CB4           |    |                                                              |    |    |    |    |    |    |    | х  | х  | х  | х  | х  | х             | х     | х   | Х  | х  | х  | х  | х  | х  | Х  |    |    |   |   |   |   |   |   |   |   |

| CB5           | Х  | Х                                                            | х  | Х  | х  | Х  | Х  | Х  | х  |    |    |    |    |    |               |       |     |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |

| CB6           |    | Exclusive "OR" All Data Bits (1–35) and All Check Bits (0–5) |    |    |    |    |    |    |    |    |    |    |    |    |               |       |     |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |

the ring: EDC error, illegal sequence error and node id out of maximum range. Once an error is detected at any node and the abort symbol has circulated the ring, all diagnostic registers will log the abort symbol except for the node which generated it. That node will log the original cause of the error.

In QR0001, an EDC error does NOT cause an abort symbol to be generated on the ring and propagate to all nodes. All other abort conditions do generate the abort symbol at the downstream port. An EDC error is displayed in the diagnostic register and causes the local ABORT pin to be asserted on all nodes which detect the EDC error. The symbol in error continues to the target. Multiple nodes could log an EDC error, but unless the node detects the EDC error it will not know other nodes have seen an error.

In QR1001 (the next device in the QuickRing family of products), when an EDC error is detected, the node will assert ABORT pin. The symbol in error will continue to its target. The abort symbol will then be sent downstream. Downstream nodes may see the symbol that causes EDC errors and log it. They they will see the abort symbol and also log that in the diagnostic register. Since the ABORT pin has already been asserted by the EDC error condition, the abord symbol will have no affect on the ABORT pin.

### 4.0 Ring Interface

#### 4.1 Type and Symbol Field at the Ring Ports

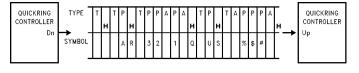

On the ring path, upstream and downstream ports, type and symbol fields organize data transmissions. Data on the ring flows in bounded streams called packets. Before data flows in the ring, packets are formed by each controller internally. Packets have one head and one or more payload symbols. Since multiple independent packets can be found inside one controller and multiplexed at the downstream port, a type field accompanies each symbol. Inside a controller, packets can be found that may originate from any other node on the system. The type field marks each symbol as a head, payload, tail, or access. *Figure 4.1* shows a typical symbol on the ring.

#### 4.2 Data and Frames

In QuickRing there are two types of payload symbols, data symbols and frame symbols, but their distinction is only of interest to the clients. The QuickRing controller does not discriminate between them, except to preserve their identity. The payload on the ring is 33 bits wide, 32 bits of normal data plus a user/client defined Frame bit as the 33rd bit. The frame bit is encoded at the client port type fields, and it is transformed into an actual bit inside QuickRing before transmission at the down stream port

The Frame bit can be used to identify a special kind of data of interest to the clients. It also can be used to designate

the beginning or end of a stream or to distinguish between data streams at the client interface.

### 4.3 Symbol Flux on Ring

At the transmit and receive ports, the length of a data stream that is uninterrupted by a head is unbounded. On the ring, upstream and downstream ports, data is bounded; there is an upper bound that gives the concept of a packet. There are two types of packets: normal and low bandwidth (LB). There is a ring protocol defining the symbol sequence. For normal packets, the maximum number of payload symbols associated with one head is fixed at 20 symbols. **The largest packet is 21 symbols in all;** however, packets may be less than 21 symbols. The LB packet consists of a Head and one payload/Tail.

#### 4.4 Data on the Ring (Head, Payload, Tail)

QuickRing transports streams of payload symbols from source nodes to target nodes through the ring interconnect. QuickRing internally assembles packets from the data that the client writes into the transmit port. This data is eventually transmitted in packets of 1 to 20 payload symbols. A head symbol precedes the packet and the last payload symbol of a packet is specially marked as the tail of that packet. The head holds the source and the destination node IDs, plus other information that uniquely identifies the stream to which the payload symbols belong.

Payload symbols consists of 32 bits of user defined information plus one 33rd user controllable Frame identifier. A payload symbol whose frame bit is set to 1 may be called a Frame symbol. Otherwise it may be referred to as a Data symbol. The Frame identifier, the logical 33rd user defined bit is mapped in SS[3] in sub-symbol t, see *Figures 4.2* and *4.3*.

#### 4.5 Access on the Ring (Voucher, Ticket, Abort, Null)

Before a source node can send a packet, permission to transmit must first be granted by the target node. To get permission to transmit, the source node sends a voucher to the target node. To grant permission to transmit, the target node sends a ticket back to the source node. This is done only in response to a voucher. When the source node sends a voucher, the target node may (1) absorb the voucher and return a ticket or (2) return the voucher. If the source receives the ticket, then it may send one packet to the target that returned the ticket. If the source received its own returned voucher, then it will sink it and retransmit the voucher after 100 clocks for a new request to transmit. The number of retries for the voucher is unlimited until the target returns a ticket. Under normal circumstances the target should return a ticket in response to a voucher, even if it must save accumulated vouchers in a queue and issue corresponding tickets with significant delays. The return of a voucher to its source should occur only if resources for queuing vouchers in the target node are exhausted.

A = ACCESS, H = HEAD, P = PAYLOAD, T = TAIL

TL/F/11928-11

FIGURE 4.1. Many streams from many nodes may be multiplexed onto the ring. Access symbols may appear Interspersed anywhere within a data packet.

### 4.0 Ring Interface (Continued)

An abort symbol identifies the occurrence of a failure such as (1) an illegal symbol sequence, (2) a corrupted symbol or (3) a node ID for which no node is present. The node that creates the abort symbol deletes it once the abort symbol has circulated the ring.

For every tick of the ring clock, every node in the ring receives one symbol at its upstream port and transmits one symbol at its downstream port. In the absence of any other symbol, a null symbol is transmitted.

## 4.6 Mapping of Type, Frame, Data and EDC Code on the Ring

On the ring path, a 42-bit symbol is transferred on every tick of the 50 MHz clock. The 42-bit symbol is divided into 7 sub-symbols, 6 bits wide. Each sub-symbol is transferred sequentially at a rate of 1 sub-symbol every 2.9 ns. In all, 42 bits are transferred every 20 ns. Refer to *Figure 4.2*.

The type field, frame bit and the 3 MSB of the data are mapped to sub-symbol t. Data [28 to 0] are mapped onto sub-symbols u to y. The EDC field, CB[6:0], is mapped onto the last two sub-symbols of y and z. See *Figure 4.4*.

Later in this data sheet reference is made only to the fields that are multiplexed onto the SS[5:0] field as they appear on UpSS and DnSS. *Figure 4.2* and *4.3* show when each bit of any symbol is transmitted or received, and in what position of the sub-symbol it appears. For example, F (Frame) appears on SS[3] during "sub-symbol t". Data 0 (D0) appears on SS[1] during "y", the sixth sub-symbol.

Note: Figure 4.3 shows that the rising edge of DnCLK is aligned with the beginning of the next to last sub-symbol of the previous symbol that gets sent out on DnSS[5:0].

### 4.0 Ring Interface (Continued)

4.7 Ring Interface Field Definitions

QuickRing organizes data with a combination of access symbols and packet symbols.

Access symbols are vouchers, tickets, nulls, and aborts. Packet symbols are those that form packets such as heads and payloads.

These symbols can also be grouped into routing symbols and payload symbols.

**Routing** symbols hold source and target addresses such as voucher and ticket for access symbols, and heads for packet symbols.

**Payload** symbols are data or frame; they hold the information the clients are trying to transmit. At the client ports, a type field [01] represents a data symbol, a type field of [10] a frame symbol. A data or frame symbol at the ring ports are distinguished by an additional frame bit. The payload symbol, frame or data, at the end of a packet is called a **tail** and it is encoded as such in the type field.

#### TABLE 4.1. Dn and Up Stream Port Symbol Field Definitions

| Field                                                         | Descriptions                                                                                                                                                                                                                                                |

|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Type[1:0]                                                     | At the ring ports, distinguishes access, head, payload and tail.                                                                                                                                                                                            |

| F                                                             | The Frame bit appears explicitly only at the upstream and downstream ports. (At the Tx and Rx ports the frame bit is encoded in the type fields.)                                                                                                           |

| ACC[1:0]                                                      | The access code (ACC[1:0]) indicates the type of access symbol on the ring. Voucher, ticket, null and abort. (Doesn't apply to Tx or Rx ports.)                                                                                                             |

| CONN[1:0]                                                     | The connection code (CON[1:0]) provides<br>to types of transmission, normal and low-<br>band-width Low-bandwidth streams are<br>transmitted with higher priority.                                                                                           |