### Single-Chip Low-Power FM Receiver for Portable Devices

### General Description

The QN8035 is a high performance, low power; full-featured single-chip stereo FM receiver designed for cell phones, MP3 players. It integrates FM receive functions, auto-seek and clear channel scan. Advanced digital architecture enables superior receiver sensitivity and crystal clear audio.

With its small footprint, minimal external component count and multiple clock frequency support, the QN8035 is easy to integrate into a variety of small form-factor low power portable applications.

### Key Features

### • Worldwide FM Band Coverage

- 60 MHz to 108 MHz full band tuning in 50/100/200 kHz step sizes

- 50/75 µs de-emphasis

#### • Ease of Integration

- Small footprint, available in MSOP10 packages

- 32.768 kHz and Multiple MHz crystal and direct clock input supported

- I<sup>2</sup>C control interface

#### • Very Low Power Consumption

- 13.1 mA typical

- VCC: 2.7~5.0V, integrated LDO, support battery direct connection

- Power saving Standby mode

- · Low shutdown leakage current

- Accommodate 1.6~3.6V digital interface

# • Direct Earphone Driving

#### • Adaptive Noise Cancellation

- Integrated adaptive noise cancellation (SNC, HCC, SM)

- Volume Control

- High Performance

- Superior sensitivity, 1.1 μV<sub>EMF</sub>

- 67dB stereo SNR, 0.04% THD

- Improved auto channel seek

- L/R separation 47dB

#### Robust Operation

- $-25^{\circ}C$  to  $+85^{\circ}C$  operation

- ESD protection on all input and output pads

- 1 KHz Tone Generator Inside

# Typical Applications

- Feature Phone / Smart Phones

- Portable Audio & Media Players

#### Netbook

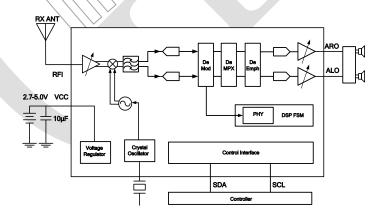

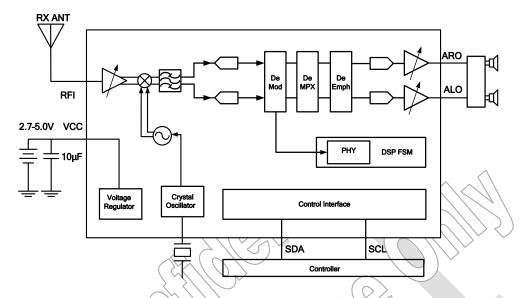

# QN8035 Functional Blocks:

Ordering Information appears at Section 6.

## **CONTENTS**

| 1 | Pin Assignment                      |

|---|-------------------------------------|

| 2 | Electrical Specifications           |

| 3 | Functional Description              |

|   | 3.1 FM Receiver                     |

|   | 3.2 Audio Processing                |

|   | 3.3 RDS/RBDS                        |

|   | 3.4 Auto Seek (CCA)                 |

| 4 | Control Interface Protocol          |

| 5 | Typical Application Schematic       |

| 6 | Ordering Information                |

| 7 | Package Description 18              |

| 8 | Solder Reflow Profile               |

|   | 8.1 Package Peak Reflow Temperature |

|   | 8.2 Classification Reflow Profiles  |

|   | 8.3 Maximum Reflow Times            |

|   |                                     |

# REVISION HISTORY

| REVISION | CHANGE DESCRIPTION                    | DATE       |

|----------|---------------------------------------|------------|

| 0.1      | Draft.                                | 2011-08-08 |

| 0.2      | Update the data from the test report. | 2011-09-02 |

| 1.0      | Release version.                      | 2011-12-20 |

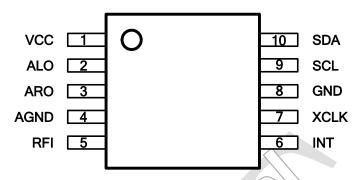

## 1 PIN ASSIGNMENT

(Top View)

Figure 1 QN8035-SANE Pin Out MSOP10

**Table 1: Pin Descriptions**

| MSOP10 | NAME | DESCRIPTION                                               |

|--------|------|-----------------------------------------------------------|

| 1      | VCC  | Voltage supply                                            |

| 2      | ALO  | Analog audio output - left channel                        |

| 3      | ARO  | Analog audio output - right channel                       |

| 4      | AGND | Ground                                                    |

| 5      | RFI  | FM Receiver RF input                                      |

| 6      | INT  | Interrupt output, active low, need pull-up externally     |

| 7      | XCLK | Clock input                                               |

| 8      | GND  | Ground                                                    |

| 9      | SCL  | Clock for I <sup>2</sup> C serial bus.                    |

| 10     | SDA  | Bi-directional data line for I <sup>2</sup> C serial bus. |

## **2 ELECTRICAL SPECIFICATIONS**

**Table 2: Absolute Maximum Ratings**

| V <sub>bat</sub> Supply voltage VCC to GND -0.3 5              | V  |

|----------------------------------------------------------------|----|

|                                                                |    |

| $V_{IO}^{-1}$ Logic signal level SCL, SDA, INT to GND -0.3 3.6 | V  |

| T <sub>s</sub> Storage temperature -55 +150                    | °C |

Notes:

1.  $V_{IO}$  is pulled up externally via resisters.

**Table 3: Recommended Operating Conditions**

| SYMBOL           | PARAMETER                   | CONDITIONS         | MIN | TYP | MAX | UNIT |

|------------------|-----------------------------|--------------------|-----|-----|-----|------|

| Vcc              | Supply voltage              | VCC to GND         | 2.7 | 3.3 | 5.0 | V    |

| $T_{A}$          | Operating temperature       |                    | -25 |     | +85 | °C   |

| RF <sub>in</sub> | RF input level <sup>1</sup> | Peak input voltage |     |     | 0.3 | V    |

| $V_{IO}^{2}$     | Digital I/O voltage         |                    | 1.6 |     | 3.6 | V    |

### Notes:

- 1. At RF input pin, RFI.

- 2. V<sub>IO</sub> is pulled up externally via resisters.

### **Table 4: DC Characteristics**

(Typical values are at Vcc = 3.3V and  $T_A = 25^{\circ}C$ ).

| SYMBOL                            | PARAMETER                          | CONDITIONS   | MIN                              | TYP  | MAX                              | UNIT |

|-----------------------------------|------------------------------------|--------------|----------------------------------|------|----------------------------------|------|

| $I_{RX}$                          | Receive mode supply current        |              |                                  | 13.1 |                                  | mA   |

| $I_{\mathrm{IDLE}}$               | Idle mode supply current           | Idle mode    |                                  | 650  |                                  | μΑ   |

| $I_{STBY}$                        | Standby mode supply current        | Standby mode |                                  | 50   |                                  | μΑ   |

| Interface                         |                                    |              |                                  |      |                                  |      |

| V <sub>OH</sub>                   | High level output voltage          |              | 0.9*V <sub>IO</sub> <sup>1</sup> |      |                                  | V    |

| V <sub>OL</sub>                   | Low level output voltage           |              |                                  |      | 0.1*V <sub>IO</sub> <sup>1</sup> | V    |

| $V_{IH}$                          | High level input voltage           |              | 1.1                              |      |                                  | V    |

| V <sub>IL</sub>                   | Low level input voltage            |              |                                  |      | 0.3                              | V    |

| Notes:<br>1. V <sub>IO</sub> is p | ulled up externally via resisters. |              |                                  |      |                                  |      |

## **Table 5: AC Characteristics**

(Typical values are at Vcc = 3.3V and  $T_A = 25^{\circ}C$ ).

| SYMBOL                                           | PARAMETERS               | CONDITIONS                  | MIN | TYP        | MAX | UNIT |

|--------------------------------------------------|--------------------------|-----------------------------|-----|------------|-----|------|

| $F_{xtal}$                                       | Clock frequency          |                             | 0.  | 032768 -40 | 1   | MHz  |

| $F_{xtal\_err}$                                  | Clock frequency accuracy | Over temperature, and aging | -50 |            | 50  | ppm  |

| Notes: 1. See also XTAL_DIV[10:0], PLL_DLT[12:0] |                          |                             |     |            |     |      |

### **Table 6: Receiver Characteristics**

(Typical values are at Vcc = 3.3V, f carrier=88 MHz and  $T_A$  = 25°C).

| SYMBOL                              | PARAMETERS                         | CONDITIONS                                                                           | MIN  | TYP  | MAX  | UNIT                 |

|-------------------------------------|------------------------------------|--------------------------------------------------------------------------------------|------|------|------|----------------------|

| $S_{RX}$                            | FM sensitivity                     | (S+N)/N = 26dB                                                                       |      | 1.1  |      | $\mu V_{\text{EMF}}$ |

| IP3                                 | Input referred IP3                 | At maximum gain                                                                      |      | 120  |      | dΒμV                 |

| Rej <sub>AM</sub>                   | AM suppression                     |                                                                                      |      | 52   |      | dB                   |

| $R_{in}$                            | RF input impedance                 | At pin RFI                                                                           |      | 5    |      | kΩ                   |

| $S_{RX\_Adj}$                       | Adjacent channel rejection         | 200 kHz offset                                                                       |      | 49   |      | dB                   |

| $S_{RX\_Alt}$                       | Alternate channel rejection        | 400 kHz offset                                                                       |      | 62   |      | dB                   |

|                                     |                                    | MONO, $\Delta f = 22.5 \text{ kHz}^1$                                                | >    | 58   |      |                      |

| $SNR_{audio\_in}$                   | Audio SNR                          | STEREO, $\Delta f = 67.5 \text{ kHz}$ , $\Delta f_{\text{pilot}} = 6.75 \text{ kHz}$ |      | 67   |      | dB                   |

|                                     |                                    | MONO, $\Delta f = 75 \text{ kHz}$                                                    |      | 0.04 | >    | %                    |

| $\mathrm{THD}_{\mathrm{audio\_in}}$ | Audio THD                          | STEREO, $\Delta f = 67.5 \text{ kHz}$ , $\Delta f_{pilot} = 6.75 \text{ kHz}$        |      | 0.03 |      | %                    |

| $\alpha_{LR\_in}$                   | L/R separation                     |                                                                                      | (5)  | 47   | 5    | dB                   |

| $Att_{Pilot}$                       | Pilot rejection                    |                                                                                      |      | 70   |      | dB                   |

| $\mathrm{B}_{\mathrm{LR}}$          | L/R channel imbalance              | L and R channel gain imbalance at 1 kHz offset from DC                               |      |      | 1    | dB                   |

| $	au_{ m emph}^{-1}$                | De-emphasis time                   | PETC = 1                                                                             | 71.3 | 75   | 78.7 | μs                   |

| $	au_{	ext{emph}}$                  | constant                           | PETC = 0                                                                             | 47.5 | 50   | 52.5 | μs                   |

| $V_{audio\_out}$                    | Audio output voltage               | Peak-Peak, single ended                                                              |      | 1    | 1    | V                    |

| $R_{LOAD}$                          | Audio output Loading<br>Resistance |                                                                                      | 32   |      |      | Ω                    |

| $C_{LOAD}$                          | Audio output loading capacitance   |                                                                                      |      |      | 20   | pF                   |

| RSSI <sub>err</sub>                 | RSSI uncertainty                   |                                                                                      | -3   |      | 3    | dB                   |

| TIID                                | Audio THD after                    | $R_{LOAD}=32\Omega$ , 1 $V_{pp}$ output                                              |      | 0.05 |      | 0/                   |

| $\mathrm{THD}_{\mathrm{driver}}$    | earphone driver                    | $R_{LOAD}=1k\Omega$ , 1 $V_{pp}$ output                                              |      | 0.03 |      | %                    |

| Notes: 1. Guarant                   | teed by design.                    |                                                                                      |      |      |      |                      |

### **Table 7: Timing Characteristics**

(Typical values are at Vcc = 3.3V and  $T_A = 25^{\circ}C$ ).

| SYMBOL                | PARAMETER                            | CONDITIONS                        | MIN | TYP | MAX | UNIT |

|-----------------------|--------------------------------------|-----------------------------------|-----|-----|-----|------|

| $	au_{	ext{pup}}$     | Chip power-up time <sup>1</sup>      | From power up to register access. |     |     | 20  | ms   |

| $	au_{\mathrm{chsw}}$ | Channel switching time <sup>1</sup>  | From any channel to any channel.  |     |     | 200 | ms   |

| Receiver T            | iming                                |                                   |     |     |     |      |

| $	au_{ m wkup}$       | Wake-up time from standby to receive | Standby to RX mode.               |     | 200 |     | ms   |

| $\tau_{tune}$         | Tune time                            | Per channel during CCA.           |     | 50  |     | ms   |

| Notes:<br>1. Guara    | anteed by design.                    |                                   |     | <   |     |      |

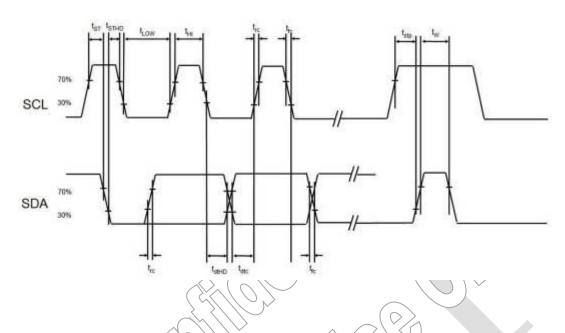

# Table 8: I<sup>2</sup>C Interface Timing Characteristics

(Typical values are at Vcc = 3.3V and  $T_A = 25^{\circ}C$ ).

| SYMBOL            | PARAMETER                                               | CONDITIONS            | MIN | TYP | MAX | UNIT |

|-------------------|---------------------------------------------------------|-----------------------|-----|-----|-----|------|

| $f_{SCL}$         | I <sup>2</sup> C clock frequency                        |                       |     |     | 400 | kHz  |

| $t_{LOW}$         | Clock Low time                                          |                       | 1.3 |     | ~   | μs   |

| $t_{\rm HI}$      | Clock High time                                         |                       | 0.6 |     |     | μs   |

| $t_{ST}$          | SCL input to SDA falling edge start <sup>1,3</sup>      |                       | 0.8 |     |     | μs   |

| t <sub>STHD</sub> | SDA falling edge to SCL falling edge start <sup>3</sup> | 3(0)                  | 0.8 |     |     | μs   |

| $t_{rc}$          | SCL rising edge <sup>3</sup>                            | Level from 30% to 70% |     |     | 300 | ns   |

| $t_{ m fc}$       | SCL falling edge <sup>3</sup>                           | Level from 70% to 30% |     |     | 300 | ns   |

| $t_{\rm dtHD}$    | SCL falling edge to next SDA rising edge <sup>3</sup>   |                       | 20  |     |     | ns   |

| $t_{ m dtc}$      | SDA rising edge to next SCL rising edge <sup>3</sup>    |                       |     |     | 900 | ns   |

| t <sub>stp</sub>  | SCL rising edge to SDA rising edge <sup>2,3</sup>       |                       | 0.6 |     |     | μs   |

| $t_{ m w}$        | Duration before restart <sup>3</sup>                    |                       | 1.3 |     |     | μs   |

| $C_b$             | SCL, SDA capacitive loading <sup>3</sup>                |                       |     | 10  |     | pF   |

#### Notes:

- 1. Start signaling of I<sup>2</sup>C interface.

- 2. Stop signaling of I<sup>2</sup>C interface.

- 3. Guaranteed by design.

Figure 2 12C Serial Control Interface Timing Diagram

### 3 FUNCTIONAL DESCRIPTION

The QN8035 is a high performance, low power, single chip FM receiver IC that supports worldwide FM broadcast band (60 to 108MHz). RDS/RBDS data service is also supported.

Figure 3 QN8035 Functional Blocks

The QN8035 integrates FM receive functions, including RF front-end circuits (LNA, Mixer and channel selective filter etc), a fully digitized FM demodulator, MPX decoder, de-emphasis and audio processing (SM, HCC, and SNC). Advanced digital architecture enables superior receiver sensitivity and crystal clear audio. The QN8035's Auto Seek function enables automatically selecting the channel of better sound quality.

The QN8035 supports a small footprint, high level of integration and multiple clock frequencies. These features make it easy to be integrated into a variety of small form-factor, low-power portable applications. Low phase noise digital synthesizers and extensive on-chip auto calibration ensures robust and consistent performance over temperature and process variations. An integrated voltage regulator enables direct connection to a Li-ion battery and provides high PSRR for superior noise suppression. A low-power IDLE and Standby mode extends battery life.

## 3.1 FM Receiver

The QN8035 receiver uses a highly digitized low-IF architecture, allowing for the elimination of external components and factory adjustments.

The received RF signal is first amplified by an integrated LNA and then down converted to an intermediate frequency (IF) via a quadrature mixer. To improve image rejection (IMR), the quadrature mixer can be programmed to be at high-side or low-side injection. An integrated IF channel filter rejects out-of-channel interference signals. AGC is also performed simultaneously to optimize the signal to noise ratio as well as linearity and interference rejection. The filtered signal is digitized and further processed with a digital FM demodulator and MPX decoder. Audio processing is then performed based on received signal quality and channel condition. Two high-quality audio DACs are integrated on chip to drive the audio output. The RDS signal will also be decoded if RDS reception is enabled.

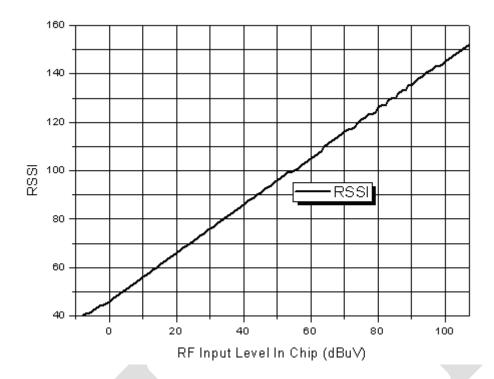

A receive signal strength indicator (RSSI) is provided and can be read from RSSIDB [7:0]. Figure 4 shows the curve of RSSI vs. different RF input levels. Auto seek utilizes RSSI to search for available channels.

The following figure is measured at FM=88MHz. The RSSI Curve is not varied by FM frequency.

Figure 4 RSSI vs RF Input

# 3.2 Audio Processing

The MPX signal after FM demodulation is comprised of left and right channel signal, pilot and RDS signal in the following way:

$m(t) = [L(t) + R(t)] + [L(t) - R(t)]\sin(4\pi ft + 2\theta_0) + \alpha\sin(2\pi ft + \theta_0) + d(t)\sin(6\pi ft + 3\theta_0)$

Here, L(t) and R(t) correspond to the audio signals on the left and right channels respectively, f=19 kHz,  $\theta$  is the initial phase of pilot tone and  $\alpha$  is the magnitude of the pilot tone, and d(t) is the RDS signal. In stereo mode, both L and R are recovered by de-MPX. In mono mode, only the L+R portion of audio signal exists. L(t) and R(t) are recovered by de-MPX.

In receive mode, stereo noise cancellation (SNC) for FM only, high cut control (HCC) and soft mute (SM) are supported. Stereo noise suppression is achieved by gradually combining the left and right signals to be a mono signal as the received signal quality degrades. SNC, HCC and SM are controlled by SNR and multipath channel estimation results. The three functions will be archived automatically in the device.

The QN8035 has an integrated mono or stereo audio status indicator. There is also a Read ST\_MO\_RX (Reg04h [0]) bit to get status. In addition, there also is a force mono function to constrain output mono in Reg00h[2].

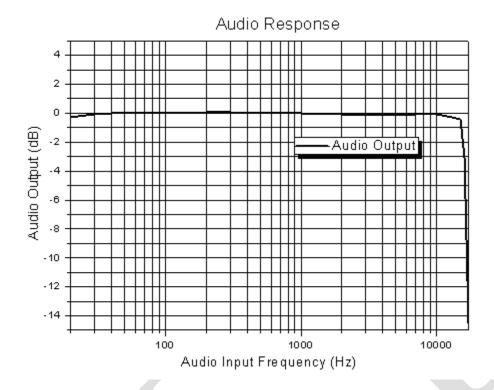

Two selectable de-emphasis time constants (75us and 50us) supported.

Figure 5 Audio Response

The audio output can be muted with the MUTE\_EN (Reg14h[7]) bit and the output can also be replaced by an internally generated 1KHz tone whenever the RFI has a RF signal input.

encoding/decoding, block synchronization, error detection and correction functions. RDS/RBDS data communicates with an external MCU through the serial control interface.

### 3.3 RDS/RBDS

The QN8035 supports RDS/RBDS data reception in FM mode, including station ID, Meta data, TMC information, etc. The integrated RDS processor performs all symbol

# 3.4 Auto Seek (CCA)

In receive mode, the QN8035 can automatically tune to stations with good signal quality. The auto seek function is referred to CCA (Clear Channel Assessment).

### 4 CONTROL INTERFACE PROTOCOL

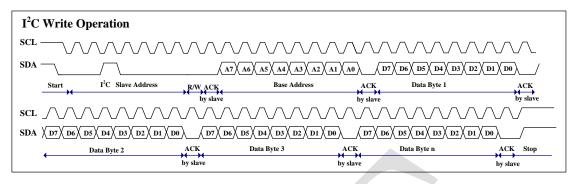

The QN8035 supports the standard I<sup>2</sup>C serial interfaces. At power-on, all register bits are set to default values.

### I<sup>2</sup>C Serial Control Interface

QN8035 provides an I<sup>2</sup>C-compatible serial interface. It consists of two wires; serial bi-directional data line (SDA) and input clock line (SCL). It operates as a slave on the bus and the slave address is 0010000. The data transfer rate on the bus is up to 400 Kbit/s.

SDA must be stable during the high period of SCL, except for start and stop conditions. SDA can only change with SCL being low. A high-to-low transition on SDA while SCL is high indicates a start condition. A low-to-high transition on SDA while SCL is high indicates a stop condition.

An I<sup>2</sup>C master initiates a data transfer by generating a start condition followed by the QN8035 slave address, MSB first, followed by a 0 to indicate a write cycle. After receiving an ACK from the QN8035 (by pulling SDA low), the master sends the sub-address of the register, or the first of a block of registers it wants to write, followed by one or more bytes of data, MSB first. The QN8035 acknowledges each byte after completion of each transfer. The I<sup>2</sup>C master terminates the write operation by generating a stop condition (P).

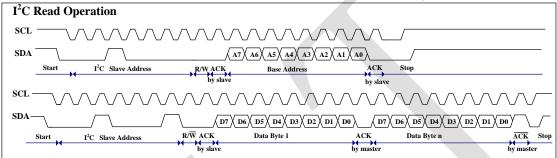

The read operation consists of two phases. The first phase is the address phase. In this phase, an  $I^2C$  master initiates a write operation to the QN8035 by generating a start condition (S) followed by the QN8035 slave address, MSB first, followed by a 0 to indicate a write cycle. After receiving ACK from the QN8035, the master sends the sub-address of the register or the first of a block of registers it wants to read. After the cycle is acknowledged, the master terminates the cycle immediately by generating a stop condition (P).

The second phase is the data phase. In this phase, an  $I^2C$  master initiates a read operation to the QN8035 by generating a start condition followed by the QN8035 slave address, MSB first, followed by a 1 to indicate a read cycle. After an acknowledge from the QN8035, the  $I^2C$  master receives one or more bytes of data from the QN8035. The  $I^2C$  master acknowledges the transfer at the end of each byte. After the last data byte to be sent has been transferred from the QN8035 to the master, the master generates a NACK followed by a stop.

The timing diagrams below illustrate both write and read operations.

Figure 6 I<sup>2</sup>C Serial Control Interface Protocol

#### Notes:

- 1. The default IC address is 0010000.

- 2. "20" for a WRITE operation, "21" for a READ operation.

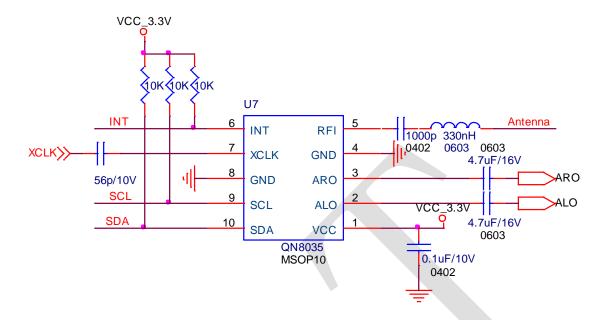

# 5 TYPICAL APPLICATION SCHEMATIC

Figure 7 Typical Application Schematic

# **6 ORDERING INFORMATION**

| Part Number | Description                                           | Package       |

|-------------|-------------------------------------------------------|---------------|

| QN8035-SANE | The QN8035-SANE is Single-Chip Low-Power FM receiver. | Body [MSOP10] |

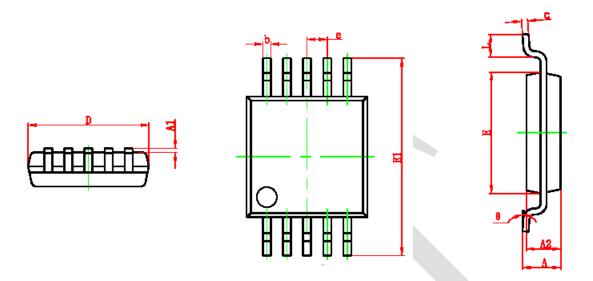

# 7 PACKAGE DESCRIPTION

# 10-Lead plastic Quad Flat, No Lead Package (ML) -Body [MSOP]

Figure 8 MSOP10 Package Outline Dimensions

| Crombal | Description               | Millimeters |         |         |  |  |

|---------|---------------------------|-------------|---------|---------|--|--|

| Symbol  | Description               | Minimum     | Nominal | Maximum |  |  |

| A       | Overall package height    | 0.820       | 0.95    | 1.100   |  |  |

| A1      | Board standoff            | 0.020       | -       | 0.150   |  |  |

| A2      | Package thickness         | 0.750       | 0.85    | 0.950   |  |  |

| b       | Lead width                | 0.180       | 0.23    | 0.280   |  |  |

| С       | Lead thickness            | 0.090       | -       | 0.230   |  |  |

| D       | Package's outside, X-axis | 2.900       | 3.00    | 3.100   |  |  |

| e       | Lead pitch                | 0.50 (BSC)  |         |         |  |  |

| Е       | Package's outside, Y-axis | 2.900       | 3.00    | 3.100   |  |  |

| E1      | Lead to lead, Y-axis      | 4.750       | 4.90    | 5.050   |  |  |

| L       | Foot length               | 0.400       | 0.60    | 0.800   |  |  |

| θ       | Foot to board angle       | 0 °         | -       | 6°      |  |  |

### **Notes:**

- 1. Pin 1 visual index feature may vary, but must be located within the area indicated in the drawing.

- 2. Dimensioning and tolerance per ASME Y 14.5M. BSC: Basic Dimension. The theoretically exact value is shown without tolerance.

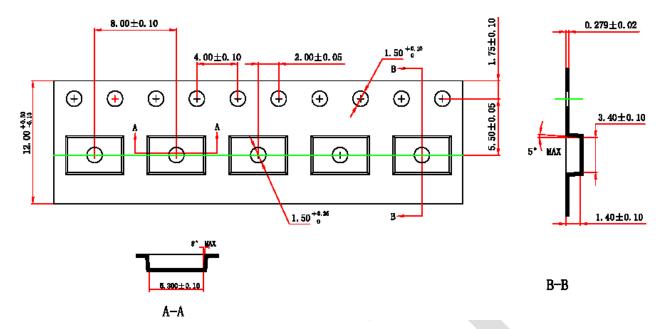

# **Carrier Tape Dimensions**

# **MSOP10 Carrier Tape**

Figure 9 MSOP10 Carrier Tape Drawing

#### **NOTES:**

- 1. 10 sprocket hole pitch cumulative tolerance <u>+</u>0.2mm maximum.

- 2. Camber not to exceed 1mm in 100mm: ≤1mm/100mm.

- 3. Pocket position relative to sprocket hole measured as true position of pocket, not pocket hole.

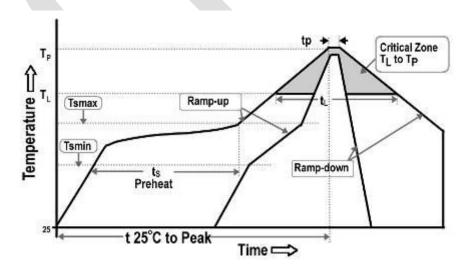

## **8 SOLDER REFLOW PROFILE**

### 8.1 Package Peak Reflow Temperature

QN8035 are assembled in a lead-free MSOP10 package. Since the geometrical size of QN8035 is  $3 \times 3 \times 0.85$  mm, the volume and thickness is in the category of volume<350 mm<sup>3</sup> and thickness<1.6 mm in Table 4-2 of IPC/JEDEC J-STD-020C. The peak reflow temperature is:

$$T_p = 260^{\circ} C$$

The temperature tolerance is  $+0^{\circ}$ C and  $-5^{\circ}$ C. Temperature is measured at the top of the package.

### 8.2 Classification Reflow Profiles

| Profile Feature                                    |                               | Specification*  |

|----------------------------------------------------|-------------------------------|-----------------|

| Average Ramp-Up Rate (tsmax to tP)                 |                               | 3°C/second max. |

| Pre-heat:                                          | Temperature Min (Tsmin)       | 150°C           |

|                                                    | Temperature Max (Tsmax)       | 200°C           |

|                                                    | Time (ts)                     | 60-180 seconds  |

| Time maintained above:                             | Temperature (T <sub>L</sub> ) | 217°C           |

|                                                    | Time (t <sub>L</sub> )        | 60-150 seconds  |

| Peak/Classification Temperature (Tp)               |                               | 260°C           |

| Time within 5°C of Actual Peak<br>Temperature (tp) |                               | 20-40 seconds   |

| Ramp-Down Rate                                     |                               | 6°C/second max. |

| Time 25°C to Peak Temperature                      |                               | 8 minutes max.  |

<sup>\*</sup>Note: All temperatures are measured at the top of the package.

Figure 1: Reflow Temperature Profile

### 8.3 Maximum Reflow Times

All package reliability tests were performed and passed with a pre-condition procedure that repeat a reflow profile, which conforms to the requirements in Section 8.2, **three** (3) times.

### **CONTACT INFORMATION**

#### **Quintic Corporation (USA)**

3211 Scott Blvd., Suite 203 Santa Clara, CA 95054 Tel: +1.408.970.8808 Fax: +1.408.970.8829

Email: <a href="mailto:support@quinticcorp.com">support@quinticcorp.com</a>

Web: <a href="mailto:www.quinticcorp.com">www.quinticcorp.com</a>

#### **Quintic Microelectronics (China)**

Building 8 B-301A Tsinghua Science Park 1st East Zhongguancun Rd, Haidian Beijing, China 100084

Tel: +86 (10) 8215-1997 Fax: +86 (10) 8215-1570 Web: <u>www.quinticcorp.com</u>

Quintic Microelectronics and Quintic are trademarks of Quintic Corporation. All Rights Reserved.