## **PXM-UIO96-2**

# SUMIT-ISM™96-Line Digital I/O with Interruptible Event Sense

#### **Features**

- SUMIT-ISM module with PCle x1 lane

- Supports 96 digital I/O lines

- Each line is capable of:

- · Bidirectional operation

- Input, Output, or Output with Read back

- · 12mA Sink Current

- Generates an interrupt on signal change-of-state

- Support for all of the 96 event sense lines

- Software selectable edge polarity

- Software enabled interrupt for each line

- · Change-of-state latched for each line

- Write-protection mask register for each 8-bit port

- PCle and USB automatic lane shifting on SUMIT-AB connectors

- PC/104 pass through connector for legacy stack

- Onboard +3.3V logic supply for I/O modules

- +5 volt only operation

- -40°C to +85°C Operation

- RoHS compliant

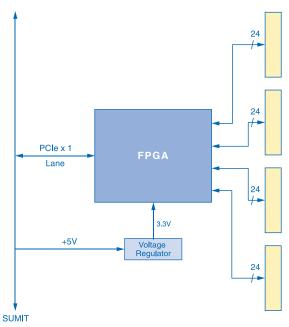

PXM-UIO96-2 Block Diagram

### **Product Description**

The PXM-UIO96-2 is a high-performance, 96-channel digital I/O controller implemented on a stackable SUMIT-AB compliant Industry Standard Module (ISM). The major feature of this card is its ability to monitor 96 lines for both rising and falling digital edge transitions, latch them and then interrupt the host processor notifying that a change-of-input status has occurred. It is based upon a Lattice Semiconductor ECP2M family FPGA with a superset of two WS16C48 Universal I/O controller cores.

**Parallel I/O Controller** - WinSystems designed the WS16C48 Universal I/O controller ASIC to support the various input/output and interrupt configurations. Each WS16C48 supports 48 digital I/O lines addressed through six contiguous registers. A six-bit Write Mask register allows the user to disable Writes on a byte basis to configure the group as a "Read Only" port.

Every I/O line is individually programmable for input, output, or output with Read back operation. The input lines are connected so the current status of its output port can be read from the corresponding input port (Read back). If the port is used as input only, then the corresponding output port bit must be cleared.

Each output channel is latched and has an open collector driver (with a pull-up resistor) capable of sinking 12mA of current. This allows direct control of up to 96 optically-isolated signal conditioning modules to a single card for high density I/O support.

## PXM-UIO96-2; 96-Line Digital I/O SUMIT-ISM Module

It directly interfaces to WinSystems' ISM-TRM-ISO-IN and ISM-TRM-ISO-OUT modules.

The controller connects directly to the stackable PCIe x1 lane on the SUMIT-A connector.

**Event Sense Operation** - The Lattice FPGA supports 96 event sense lines to generate an interrupt when an event occurs. This means that all of the digital I/O lines of the PXM-UIO96-2 can sense a positive or negative transition on the input. Transition polarity is programmable and enabled on a bit-by-bit basis. Each line's transition is latched by the event so that even short duration pulses will be recognized.

Sample drivers are downloadable for Linux, Windows XP, WES7, and C from the WinSystems' website that is supported by a wide range of operating systems including Windows®, Linux, and other x86-compatible operating systems.

| SUMIT Resources         |            |            |

|-------------------------|------------|------------|

|                         |            |            |

| Form Factor: SUMIT-ISM  |            |            |

|                         | SUMIT<br>A | SUMIT<br>B |

| PCle x1                 | 1          | - ]        |

| PCle x4                 |            | -          |

| USB                     | -          |            |

| ExpressCard             |            |            |

| LPC                     | -          |            |

| SPI / uWire             | -          |            |

| SMBus/ I <sup>2</sup> C | -          |            |

| +12V                    | -          |            |

| +5V                     | √          | V          |

| +5Vsb                   | -          | -          |

| +3.3V                   | -          | -          |

PC/104 Interface - There is a PC/104 connector for legacy applications; however, no control or data signals are wired to it. It simply feeds the signals through the connector to the next module in a stack. The PC/104 connector can be depopulated at the factory if not required.

I/O Connectors - The signals from the Lattice FPGA are wired to four, 50-pin connectors. Each connector supports 24 data lines which are alternated with 24 ground lines for reduced noise and crosstalk. Also, each connector has the +3.3 volt source wired to pin 49 to supply logic power for I/O signal conditioning modules.

Front and Back Picture of PXM-UIO96-2

### **Technical Specifications**

#### **Onboard I/O**

96 I/O Lines LVCMOS33-compatible VccIO 3.3V nominal -0.3V min; +0.8V max  $V_{IL}$  $V_{\text{IH}}$ +2.0V min; +3.6V max

12mA

#### **Power Requirements**

+5V @ TBD

#### **Connectors**

SUMIT Type AB connector (two, 52-pin) PC/104 16-bit stackthrough (feed through only)

I/O Four, 0.100" IDC

#### **Environmental**

Operational from -40°C to +85°C Non-condensing relative humidity 5% to 95% RoHS compliant Yes

#### Mechanical

**Dimensions** 3.6 x 3.8 inches (90 x 96mm) Weight 2.4 oz. (68 gm)

## **Ordering Information**

PXM-UIO96-2 96 channel SUMIT-ISM Universal

I/O module

CBL-129-4 4 ft., ribbon cable, both ends have

50-pin socket termination

WinSystems reserves the right to make changes to products and/or documentation without further notification.

Product names of other companies may be trademarks of their respective companies.