# 6Ch, 24bit, 192kHz Digital Audio Processor for Full Digital Amplifier

### **Introduction**

The PS9702B is a highly integrated system-on-chip solution for multi-channel AV systems. The PS9702B is 6 channel PCM to PWM modulator with sample rate converter and pre-amplifier functions. It features six 24-bit audio digital-to-digital converters and over-sampling digital filters, a sample rate converter, an audio DSP that functions as an on-chip pre-amplifier with equalizer, volume control, bass management, and compressor functions. The PS9702B accepts industry-standard audio data formats with 16- to 24-bit audio data. Sampling rates of up to 192 kHz are supported.

### **Features**

#### General

- 1 serial input port for 6Ch and 3 serial input ports for 2Ch (or 2 serial input ports for 6Ch)

- SPDIF receiver for 2Ch non-encoded PCM input

- Supports 16/18/20/24 bit Input

- Supports 32kHz~192kHz Input Sample Rate

- I2C or SPI control bus

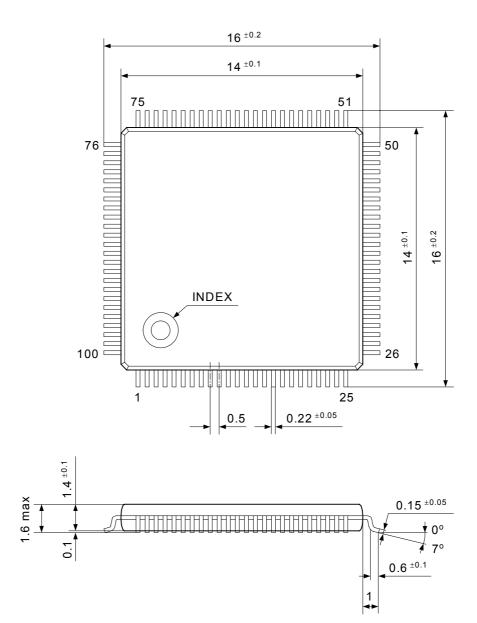

- 100 pin QFP Package

- 3.3V Single Power Supply

#### Digital Filter and Sample-rate-converter Section

- On chip Sample rate converter

- On chip Digital De-emphasis filter for CD input signal

#### **Preamplifier Section**

- Input mixing function

- Microphone mixing function

- Stereo REC output

- Parametric EQ (4 band, 1dB/step) per channel

- Tone control (±15dB, 1dB/step) per channel

- Bass management function

- Volume control (+24 ~ -70dB, 0.5dB/step) per channel

- Dynamic range compression function

- Soft and Hard Mute Functions

#### PCM-to-PWM modulator section

- 6 channel PWM Amplification output

- 95 dB Dynamic Range (typical)

#### **Application**

- DVD Receiver (DVD player plus 5.1ch Receiver)

- Integrated A/V Receiver

- HDTV sets

- Car A/V Systems

- DVD Add-On Cards for High-End PCs

- Digital Audio Workstations

- Other Multi-Channel Digital Audio Systems

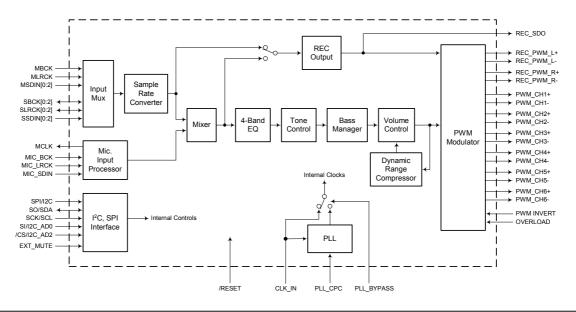

### Functional Block Diagram

# **Specifications**

### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                              | Min                   | Max  | Units |

|----------------------------------------|-----------------------|------|-------|

| Power Supply Voltage (VDD to VSS)      | V <sub>SS</sub> – 0.3 | 4.0  | V     |

| Input Current, (Any pin except Supply) | -                     | ±10  | mA    |

| Output Current (/Pin)                  | -                     | ±30  | mA    |

| Input Voltage                          | V <sub>SS</sub> – 0.5 | +7.0 | V     |

| Storage Temperature                    | -65                   | +150 | °C    |

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **RECOMMENDED OPERATING CONDITIONS**

| Parameter                         | Min                  | Тур | Max | Units |

|-----------------------------------|----------------------|-----|-----|-------|

| Power Supply Voltage (VDD to VSS) | 3.0                  | 3.3 | 3.6 | V     |

| Supply Current (VDD = 3.3V)       | -                    | 170 | -   | mA    |

| Input Voltage                     | V <sub>SS</sub> -0.5 | -   | 5.5 | V     |

| Ambient Operating Temperature     | -20                  | -   | +75 | °C    |

### **ELECTRICAL CHARACTERISTICS**

| Parameter                                               | Min            | Тур | Max  | Units      |

|---------------------------------------------------------|----------------|-----|------|------------|

| Input Leakage Current (except Pull-up, Pull-down Input) | -              | -   | 30   | μ <b>A</b> |

| High-Level Input Voltage (except Schmitt Input)         | 2.0            | -   | ı    | V          |

| Low-Level Input Voltage (except Schmitt Input)          | -              | -   | 0.8  | V          |

| High-Level Input Voltage (Schmitt Input)                | 1.39           | -   | 2.06 | V          |

| Low-Level Input Voltage (Schmitt Input)                 | 0.9            | -   | 1.46 | V          |

| High-Level Output Voltage (I <sub>O</sub> = 2mA)        | $V_{DD} - 0.4$ | -   | -    | V          |

| Low-Level Output Voltage (I <sub>O</sub> = 2mA)         | -              | -   | 0.4  | V          |

| Pull-up Resistance                                      | 20             | 50  | 100  | kΩ         |

| Pull-down Resistance                                    | 20             | 50  | 100  | kΩ         |

| Input Capacitance (f = 1MHz, V <sub>DD</sub> = 0V)      | -              | -   | 10   | pF         |

| Output Capacitance (f = 1MHz, V <sub>DD</sub> = 0V)     | -              | -   | 10   | pF         |

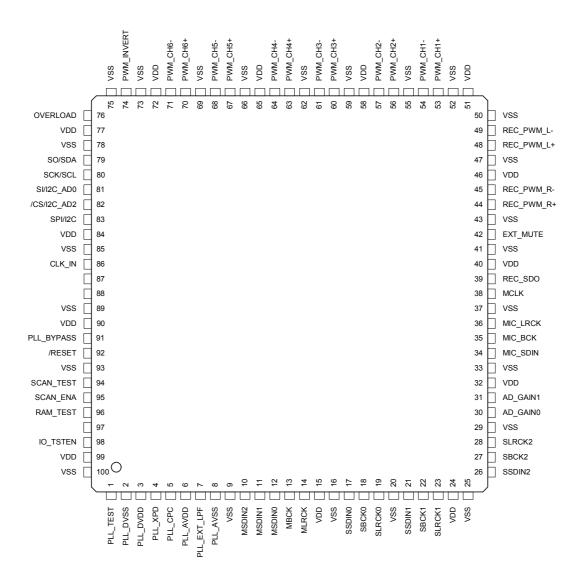

### Pin Assignment

PS9702B (100pin Plastic QFP, Top View)

# **Pin Descriptions**

| Name        | Pin NO.                                    | Туре         | Description                                                                                                                                                                                                                        |

|-------------|--------------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |                                            |              | r and Ground                                                                                                                                                                                                                       |

| PLL_AVDD    | 6                                          | Analog       | PLL analog power supply. 3.3V supply voltage.                                                                                                                                                                                      |

| I LL_AVDD   | Ü                                          | Power        | T LE arraing power supply. 5.54 supply voltage.                                                                                                                                                                                    |

| PLL_AVSS    | 8                                          | Analog       | PLL analog ground.                                                                                                                                                                                                                 |

|             |                                            | Ground       |                                                                                                                                                                                                                                    |

| PLL_DVDD    | 3                                          | PLL<br>Power | PLL peripheral digital power supply. 3.3V supply voltage.                                                                                                                                                                          |

| PLL_DVSS    | 2                                          | PLL          | PLL digital ground.                                                                                                                                                                                                                |

|             |                                            | Ground       |                                                                                                                                                                                                                                    |

| VDD         | 15, 24, 32, 40, 46,                        | Power        | Digital power supply. 3.3V supply voltage.                                                                                                                                                                                         |

|             | 51, 58, 65, 72, 77,                        |              |                                                                                                                                                                                                                                    |

|             | 84, 90, 99                                 |              |                                                                                                                                                                                                                                    |

| VSS         | 9, 16, 20, 25, 29,                         | Ground       | Digital ground.                                                                                                                                                                                                                    |

|             | 33, 37, 41, 43, 47,<br>50, 52, 55, 59, 62, |              |                                                                                                                                                                                                                                    |

|             | 66, 69, 73, 75, 78,                        |              |                                                                                                                                                                                                                                    |

|             | 85, 89, 93, 100                            |              |                                                                                                                                                                                                                                    |

|             |                                            | Syst         | em Services                                                                                                                                                                                                                        |

| /RESET      | 92                                         | I            | H/W reset signal. Active Low Schmitt-Trigger input.                                                                                                                                                                                |

|             |                                            |              | The Schmitt-Trigger input allows a slowly rising input to reset the chip reliably. The RESET signal must be asserted 'Low' during power up. De-assert 'High' for normal operation.                                                 |

| CLK_IN      | 86                                         | I            | External clock input. 12.288MHz is recommended.                                                                                                                                                                                    |

|             |                                            |              | When the PLL_BYPASS is "LOW", the external clock input from CLK_IN is used as PLL reference clock source. The external oscillator generates 12.288MHz clock and the internal PLL generates 98.304MHz (12.288MHz x 8) system clock. |

|             |                                            |              | When the PLL_BYPASS is "HIGH", the PS9702B directly uses the CLK_IN signal (98.304MHz clock) as system clock.                                                                                                                      |

| PLL_BYPASS  | 91                                         | 1            | PLL bypass path selection input. Active High.                                                                                                                                                                                      |

|             |                                            |              | Internal pull-down resistor.                                                                                                                                                                                                       |

| PLL_XPD     | 4                                          | I            | Internal PLL Power Down. Active Low.                                                                                                                                                                                               |

|             |                                            |              | Don't pull down "PLL_XPD" pin when PWM output is activated.  Internal pull-up resistor.                                                                                                                                            |

| PLL_CPC     | 5                                          |              | Internal PLL Charge Pump Current Selection input.                                                                                                                                                                                  |

| FLL_OFO     | 3                                          | '            | 'LOW' for 100uA, 'HIGH" for 50uA.                                                                                                                                                                                                  |

|             |                                            |              | Internal pull-down resistor.                                                                                                                                                                                                       |

| PLL_EXT_LPF | 7                                          | Analog       | External PLL low pass filter pin.                                                                                                                                                                                                  |

|             | P                                          | CM Audio Ir  | nput/Output Interface                                                                                                                                                                                                              |

| MBCK        | 13                                         | ı            | PCM bit clock input of main six-channel audio.                                                                                                                                                                                     |

|             |                                            |              | Schmitt-Trigger input.                                                                                                                                                                                                             |

| MLRCK       | 14                                         | I            | PCM Word clock (left-right clock) input of main six-channel audio. Schmitt-Trigger input.                                                                                                                                          |

| MSDIN[0:2]  | 12-10                                      | I            | PCM serial data input of main six-channel audio. Schmitt-Trigger input.                                                                                                                                                            |

| SBCK[0:2]   | 18, 22, 27                                 | I/O          | PCM bit clock input/output of sub-channel audio.                                                                                                                                                                                   |

| 0.2011(0.2) | 10, 22, 21                                 |              | User can select the master/slave mode of this signal.                                                                                                                                                                              |

| Name       | Pin NO.    | Туре     | Description                                                                                                                                                                                                  |  |  |

|------------|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SLRCK[0:2] | 19, 23, 28 | I/O      | PCM Word clock (left-right clock) input/output of sub-channel audio.                                                                                                                                         |  |  |

| SSDIN[0:2] | 17, 21, 26 | I        | PCM serial data input of sub-channel audio.                                                                                                                                                                  |  |  |

|            |            |          | This sub-channel data can be treated as three two-channel audio or one six-channel audio. When it is used for six-channel audio, user can select the bit clock and word clock from SBCK[0:2] and SLRCK[0:2]. |  |  |

| MCLK       | 38         | 0        | Main clock for external A/DC or D/AC. Clock frequency is 12.288MHz (fixed).                                                                                                                                  |  |  |

| MIC_BCK    | 35         | 0        | PCM bit clock output of external MIC. Bit clock frequency is 3.072MHz (48KHz x 64, fixed)                                                                                                                    |  |  |

| MIC_LRCK   | 36         | 0        | PCM Word clock (left-right clock) output of external MIC. Word clock rate is 48KHz (fixed).                                                                                                                  |  |  |

| MIC_SDIN   | 34         | I        | PCM serial data input of external MIC. Schmitt-Trigger input.                                                                                                                                                |  |  |

| REC_SDO    | 39         | 0        | PCM serial data output of record-out.                                                                                                                                                                        |  |  |

| _          |            |          | This signal is synchronized to MIC_BCK and MIC_LRCK.                                                                                                                                                         |  |  |

|            |            | PWM      | Audio Output                                                                                                                                                                                                 |  |  |

| PWM_CH1+   | 53         | 0        | Positive PWM output of channel 1. (default setting : front left channel)                                                                                                                                     |  |  |

| PWM_CH1-   | 54         | 0        | Negative PWM output of channel 1.                                                                                                                                                                            |  |  |

| PWM_CH2+   | 56         | 0        | Positive PWM output of channel 2. (default setting : front right channel)                                                                                                                                    |  |  |

| PWM_CH2-   | 57         | 0        | Negative PWM output of channel 2.                                                                                                                                                                            |  |  |

| PWM_CH3+   | 60         | 0        | Positive PWM output of channel 3. (default setting : rear left channel)                                                                                                                                      |  |  |

| PWM_CH3-   | 61         | 0        | Negative PWM output of channel 3.                                                                                                                                                                            |  |  |

| PWM_CH4+   | 63         | 0        | Positive PWM output of channel 4. (default setting : rear right channel)                                                                                                                                     |  |  |

| PWM_CH4-   | 64         | 0        | Negative PWM output of channel 4.                                                                                                                                                                            |  |  |

| PWM_CH5+   | 67         | 0        | Positive PWM output of channel 5. (default setting : center channel)                                                                                                                                         |  |  |

| PWM_CH5-   | 68         | 0        | Negative PWM output of channel 5.                                                                                                                                                                            |  |  |

| PWM_CH6+   | 70         | 0        | Positive PWM output of channel 6. (default setting: sub-woofer channel)                                                                                                                                      |  |  |

| PWM_CH6-   | 71         | 0        | Negative PWM output of channel 6.                                                                                                                                                                            |  |  |

| REC_PWM_R+ | 44         | 0        | Positive PWM output of Record-out left channel.                                                                                                                                                              |  |  |

| REC_PWM_R- | 45         | 0        | Negative PWM output of Record-out left channel.                                                                                                                                                              |  |  |

| REC_PWM_L+ | 48         | 0        | Positive PWM output of Record-out right channel.                                                                                                                                                             |  |  |

| REC_PWM_L- | 49         | 0        | Negative PWM output of Record-out right channel.                                                                                                                                                             |  |  |

|            |            | System ( | Control Interface                                                                                                                                                                                            |  |  |

| SPI/I2C    | 83         | I        | Host interface mode (SPI or I2C) selector. Assert 'HIGH' for SPI mode. De-assert 'LOW' for I2C mode. Internal pull-down resistor.                                                                            |  |  |

| SO/SDA     | 79         | I/O      | SO for SPI mode or SDA for I2C mode.                                                                                                                                                                         |  |  |

| SCK/SCL    | 80         | l        | SCK for SPI mode or SCL for I2C mode.<br>Schmitt-Trigger input.                                                                                                                                              |  |  |

| Name         | Pin NO.    | Туре      | Description                                                                                                                                                                                                        |

|--------------|------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SI/I2C_AD0   | 81         | I         | SI for SPI mode or Slave Address 0 for I2C mode.<br>Schmitt-Trigger input.<br>Internal pull-down resistor.                                                                                                         |

| /CS/I2C_AD2  | 82         | I         | Chip selector (CS) for SPI mode or Slave Address 2 for I2C mode. Schmitt-Trigger input. Internal pull-down resistor.                                                                                               |

|              |            | Special ( | Control Interface                                                                                                                                                                                                  |

| EXT_MUTE     | 42         | I         | External mute control input. Active High. Assert 'HIGH' to mute the output. Internal pull-down resistor.                                                                                                           |

| PWM_INVERT   | 74         | I         | Inverting control input of the PWM output. Active High. Assert 'HIGH' to invert the PWM output. Default is non-inverting mode. Internal pull-down resistor.                                                        |

| OVERLOAD     | 76         | I         | Power stage overload indication input.  Polarity is programmable. Schmitt-Trigger input.  When OVERLOAD is asserted, all PWM audio outputs go to "LOW" (if PWM_INVERT pin is 'LOW").  Internal pull-down resistor. |

| AD_GAIN[0:1] | 30, 31     | 0         | External A/D converter's gain control output.                                                                                                                                                                      |

|              |            | T         | est Mode                                                                                                                                                                                                           |

| PLL_TEST     | 1          | I         | Internal PLL test mode. Active High. In normal operation, it should be "LOW" or not connected. Internal pull-down resistor.                                                                                        |

| SCAN_TEST    | 94         | I         | Scan test mode selector. Active High. In normal operation, it should be "LOW" or not connected. Internal pull-down resistor.                                                                                       |

| SCAN_ENA     | 95         | I         | Scan enable. Active High. In normal operation, it should be "LOW" or not connected. Internal pull-down resistor.                                                                                                   |

| RAM_TEST     | 96         | I         | Internal SRAM test mode. Active High. In normal operation, it should be "LOW" or not connected. Internal pull-down resistor.                                                                                       |

| IO_TSTEN     | 98         | I         | I/O Test pin. Active High. In normal operation, it should be "LOW" or not connected. Internal pull-down resistor.                                                                                                  |

| NC           | 87, 88, 97 |           | Not connected pin. This pin should not be connected to any other signal.                                                                                                                                           |

<sup>\*\*</sup> All inputs and bi-directional inputs are 5 Volt tolerant. The corresponding pins can be connected to the buses that can swing between 0V and 5V. The output-only pins are not 5V tolerant and the buses they are connected to can swing only between 0V and 3.3V.

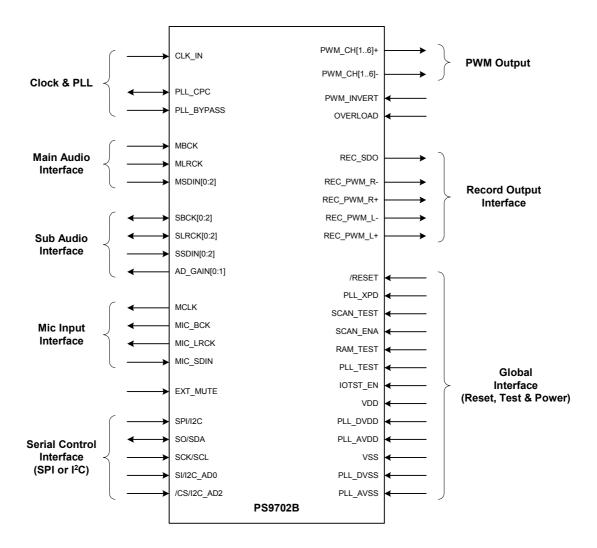

# Signal Interface Diagram

### Signal Descriptions

#### 1. Clock and Reset

The PS9702B uses 98.304MHz (48KHz x 2048) system clock internally. The PS9702B uses external 12.288MHz clock source and has x8 PLL (Phase Locked Loop) for internal system clock generation. PS9702B can select the system clock between the internally generated clock and the external input clock (In this case the external input clock must be 98.304MHz).

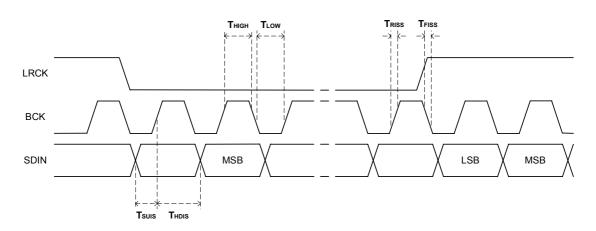

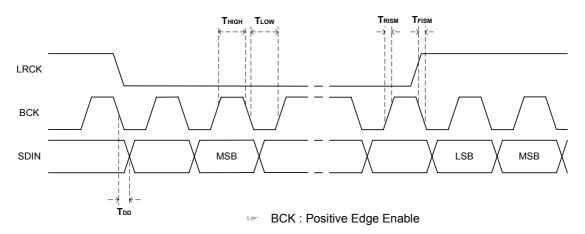

### 2. PCM Audio Input Signals

PS9702B uses serial interface for PCM audio data input using **BCK**, **LRCK**, and **DIN** pins. It has one input port for six channel audio data (named as main channel) and has three sub-input port for two channel audio data (named as sub-channel). But the three sub-input ports can be used as one six-channel audio input port.

### 3. PWM Audio Output Signals

The PS9702B converts PCM audio data to PWM audio signal. It outputs one six-channel PWM signal for main audio, one two-channel PWM signal for record-out and one additional two-channel PCM signal for record-out. All PWM signal consist of the both positive and negative PWM signals.

### 4. Control Interface Signals

The PS9702B supports internal control register I/O using both SPI and I<sup>2</sup>C. The pin **SPI/I2C** selects the control interface method. The control registers has 8-bit address space and 16-bit or 24-bit data length. All internal control registers are both readable and writable.

### 5. Special Control Signals

The PS9702B can generate only AD mode PWM signal. For more information about the Power stage driving method and BD/AD mode of PWM amplifier, refer the "PULSUS PWM Amplification application notes".

The PS9702B has Overload protection logic. When the pin **OVERLOAD** is "HIGH" (default setting, the polarity is programmable), the PS9702B goes to protection mode and all PWM outputs go to "LOW" (default setting).

### **Control Interface Protocol**

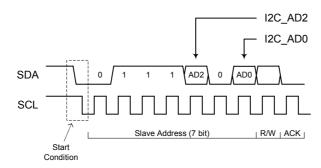

### 1. I<sup>2</sup>C Control Interface

The pin SPI/I2C selects the control interface method. When the pin SPI/I2C is grounded, the control interface method is  $I^2C$  interface.

The I<sup>2</sup>C slave address can be varied using two I<sup>2</sup>C slave address setting pin, *I2C\_AD0* and *I2C\_AD2*. The base slave address is 0x38 with *I2C\_AD0* and *I2C\_AD2* pin grounded. Figure below shows you the configuration of slave address.

| I2C_AD2 | D2 I2C_AD0 PS9702B Slave Addre |                  |  |

|---------|--------------------------------|------------------|--|

| 0       | 0                              | 0x38 (0b0111000) |  |

| 0       | 1                              | 0x39 (0b0111001) |  |

| 1       | 0                              | 0x3C (0b0111100) |  |

| 1       | 1                              | 0x3D (0b0111101) |  |

The control registers has 8-bit address space and 16-bit or 24-bit data length. If the upper two bits of register address are all HIGH, 11xx xxxx, then the data length will be three bytes (24 bits). The other case, the data length will be two bytes (16 bits).

The I<sup>2</sup>C control protocol diagram is in the next page.

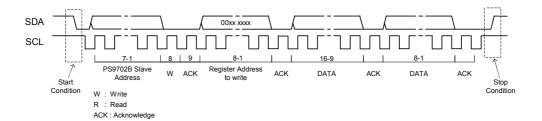

### 2Bytes Write Operation (I<sup>2</sup>C interface)

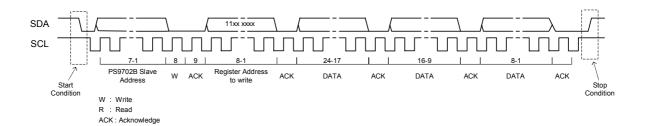

### 3Bytes Write Operation (I<sup>2</sup>C interface)

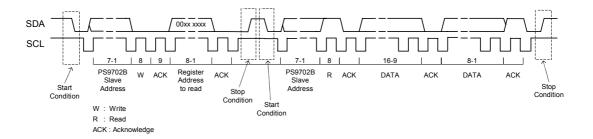

### 2Bytes Read Operation (I<sup>2</sup>C interface)

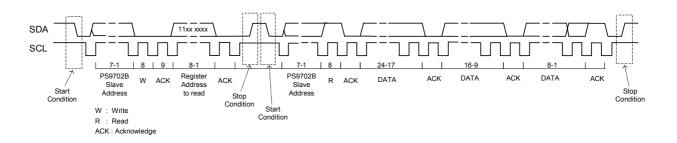

#### 3Bytes Read Operation (I<sup>2</sup>C interface)

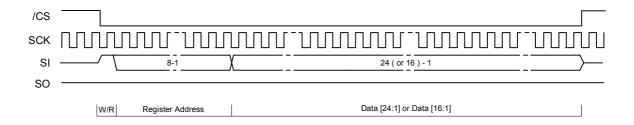

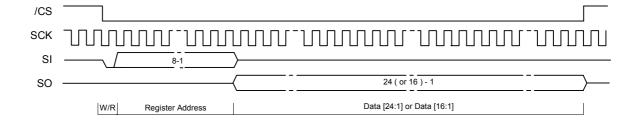

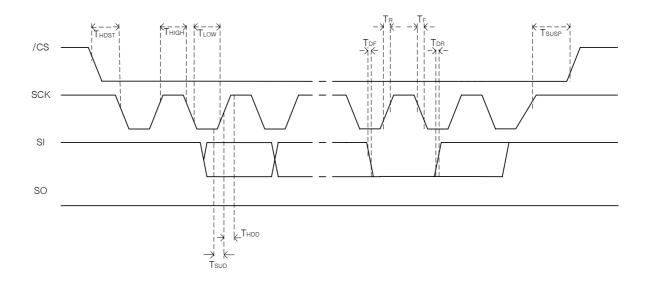

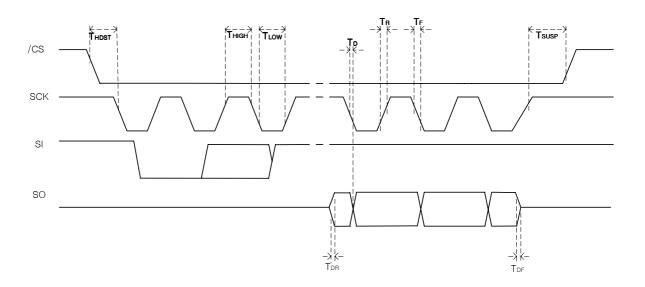

### 2. SPI Control Interface

The pin **SPI/I2C** selects the control interface method. When the pin **SPI/I2C** is connected to VCC, the control interface method is SPI interface.

SPI control protocol diagram is below.

### Write Operation (SPI interface)

### Read Operation (SPI interface)

# **Control Register Descriptions**

| Register Name | Address | Word<br>Length | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|---------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |         |                | DDC Soft Reset Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DDC_RESET     | 0x00    | 2 Bytes        | PWM output activation control register.  [0]: PWM modulator Reset control. Default = "1".  "0" = PWM On  "1" = PWM Off  [3:1]: Reserved.  [4]: SRC (Sample Rate Converter) Lock indication. Active High. Read only.  "0" = Unlock (or No signal)  "1" = Lock  [8:5]: Input sample rate indication. Read only.  "0001" = 32KHz  "0010" = 44.1KHz  "0011" = 48KHz  "0110" = 88.2KHz  "0110" = 88.2KHz  "1010" = 176.4KHz  "1011" = 192KHz  [15:9]: Not Used.  Default = 0x0XX1                                                                                                                                                                                                                       |

|               |         | Input I        | nterface Unit Configuration Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| IN_CONTROL    | 0x01    | 2 Bytes        | Serial data input interface control register.  [1:0]: BCK count. Default = "10".  "00" = 16bit, "01" = 24bit, "10" = 32bit.  [2]: BCK polarity. Default = "1".  "0" = Valid data at Negative edge  "1" = Valid data at Positive edge  [3]: Data align. "0" = Right aligned, "1" = Left aligned. Default = "1".  [4]: LRCK left high. Default = "0".  "0" = Right data when LRCK is high.  "1" = Left data when LRCK is high.  [5]: Data MSB first. "0" = LSB first, "1" = MSB first. Default = "1".  [7:6]: Data word length. Default = "11".  "00" = 16bit, "01" = 18bit, "10" = 20bit, "11" = 24bit.  [8]: I2S compatible. "1" = Compatible. Default = "1".  [15:9]: Not Used.  Default = 0x01EE |

| Register Name     | Address | Word<br>Length | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------|---------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MIC_CONTROL       | 0x02    | 2 Bytes        | MIC data input interface control register.  This register is not changable and is fixed to default value.  [8:0]: BCK count. Default = "10".  "00" = 16bit, "10" = 32bit.  [2]: BCK polarity. Default = "1".  "0" = Valid data at Negative edge.  "1" = Valid data at Positive edge.  [3]: Data align. "0" = Right aligned. "1" = Left aligned. Default = "1".  [4]: LRCK left high. Default = "0".  "0" = Right data when LRCK is high.  "1" = Left data when LRCK is high.  [5]: Data MSB first. "0" = LSB first, "1" = MSB first. Default = "1".  [7:6]: Data word length. Default = "11".  "00" = 16bit, "01" = 18bit, "10" = 20bit, "11" = 24bit.  [8]: I2S compatible. "1" = Compatible. Default = "1".  [15:9]: Not Used.  Default = 0x01EE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CHANNEL_CONFIGURE | 0x03    | 2 Bytes        | Register for serial input data port configuration.  [2:0]: I2S Input port selector. <i>Default = "100"</i> .  "000" = Sub two-channel input mode using SDIN[0], SBCK[0], and SLRCK[0].  "001" = Sub two-channel input mode using SDIN[1], SBCK[1], and SLRCK[1].  "01x" = Sub two-channel input mode using SDIN[2], SBCK[2], and SLRCK[2].  "100" = Main six-channel input mode using MBCK and MLRCK.  "101" = Sub six-channel input using SBCK[0] and SLRCK[0].  "110" = Sub six-channel input using SBCK[1] and SLRCK[1].  "111" = Sub six-channel input using SBCK[1] and SLRCK[1].  "111" = Sub six-channel input using SBCK[2] and SLRCK[2].  [4:3]: <i>Reserved</i> .  [5]: Master-slave mode selector for SBCK[0] and SLRCK[0]. <i>Default = "0"</i> .  "0" = Slave mode, "1" = Master mode.  [6]: Master-slave mode selector for SBCK[1] and SLRCK[1]. <i>Default = "0"</i> .  "0" = Slave mode, "1" = Master mode.  [7]: Master-slave mode selector for SBCK[2] and SLRCK[2]. <i>Default = "0"</i> .  "0" = Slave mode, "1" = Master mode.  [8]: I2S/SPDIF input selector. PS9702B can receive the both I2S and SPDIF input.  "0" means the input is SPDIF input.  "0" means the input is I2S input. <i>Default = "1"</i> .  [10:9]: SPDIF input port selector. <i>Default = "00"</i> .  "00" = SPDIF input from SDATA[0].  "01" = SPDIF input from SBCK[0].  "11" = SPDIF input from SDATA[0].  [15:11]: <i>Not Used</i> . <i>Default = 0x0104</i> |

| Register Name                  | Address | Word<br>Length | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|--------------------------------|---------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Volume Configuration Registers |         |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| VOLUME1_CONTROL                | 0x05    | 2 Bytes        | The PS9702B supports digital volume gain control with the resolution of 0.5dB/step. The maximum volume gain is +24dB and the minimum volume gain (except -∞dB) is -70dB. The each volume control register has 8-bit resolution. The register value 0x00 means +24dB, and the value 0xBC means -70dB. And the register value larger than 0xBC means sound mute.  Table A-1 shows the relations between the register value and volume gain.  [15:8]: PWM output Channel 1 volume.  [7:0]: PWM output Channel 2 volume.  Default = 0xBDBD (Mute) |  |  |  |  |

| VOLUME2_CONTROL                | 0x06    | 2 Bytes        | Table A-1 shows the relations between the register value and volume gain.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|                                |         |                | [15:8]: PWM output Channel 3 volume. [7:0]: PWM output Channel 4 volume.  Default = 0xBDBD (Mute)                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| VOLUME3_CONTROL                | 0x07    | 2 Bytes        | Table A-1 shows the relations between the register value and volume gain.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| V020M20_00M102                 | oxer.   | 2 Bytee        | [15:8]: PWM output Channel 5 volume. [7:0]: PWM output Channel 6 volume.  Default = 0xBDBD (Mute)                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| VOLUME4_CONTROL                | 0x08    | 2 Bytes        | Table A-1 shows the relations between the register value and volume gain.  [15:8]: Record out left volume.  [7:0]: Record out right volume.  Default = 0x3030 (0dB)                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|                                | D       | ynamic Ra      | ange Compressor Configuration Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| THRESHOLD1_CONTROL             | 0x09    | 2 Bytes        | Automatic gain control (AGC) threshold level.  The AGC threshold level is controlled in dB magnitude and it has 0.5dB/step resolution. This register has 8-bit resolution and has the same meaning of volume control register.  Table A-1 shows the relations between the register value and threshold level.  [15:8]: AGC threshold of PWM output Channel 1 and Channel 2.  [7:0]: Reserved.  Default = 0x3131 (-0.5dB)                                                                                                                      |  |  |  |  |

| THRESHOLD2_CONTROL             | 0x0A    | 2 Bytes        | Table A-1 shows the relations between the register value and threshold level.  [15:8]: AGC threshold of PWM output Channel 3.  [7:0]: AGC threshold of PWM output Channel 4.  Default = 0x3131 (-0.5dB)                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| THRESHOLD3_CONTROL             | 0x0B    | 2 Bytes        | Table A-1 shows the relations between the register value and threshold level.  [15:8]: AGC threshold of PWM output Channel 5.  [7:0]: AGC threshold of PWM output Channel 6.  Default = 0x3131 (-0.5dB)                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| Register Name | Address | Word<br>Length | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------|---------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AGC_CONTROL   | 0x11    | 2 Bytes        | AGC control register.  [3:0]: AGC attack length control value. <i>Default</i> = 0x6.  [6:4]: AGC attack height (in 0.5dB scale). <i>Default</i> = 0x3.  [15:7]: AGC release length (x 0.6667msec). <i>Default</i> = 0x180 (0.256 sec).  Default = 0xC036                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|               |         | PWM            | I Modulator Configuration Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PWM_CONTROL1  | 0x13    | 2 Bytes        | PWM modulator control register 1.  [0]: Modulation index(PCM to PWM gain). Default = "0".  "0" = 90.63%  "1" = 93.75%  [1]: Auto DC cut enable. Active high. Default = "1".  [5:2]: Reserved. Default = "0000"  [6]: Overload input signal polarity. Default = "1"  "0" = Active Low, "1" = Active High.  [11:7]: Overload sustained time.  When overload condition is detected, all PWM outputs go to shutdown during assigned time. Default = "10000" (2.73sec)  "00000" = No shutdown.  "00001" ~ "11110" = multiple of 0.17sec.  "11111" = No recovery. To recover PWM signal, set the DDC_RESET register (0x00) to "1" (PWM off) and then "0" (PWM on).  [15:12]: Reserved.  Default = 0x0842                                                                                              |

| PWM_CONTROL2  | 0x14    | 2 Bytes        | PWM modulator control register 2.  [0]: Interpolation method. "0" = Soft, "1" = Sharp. Default = "0".  [1]: Dither enable. "0" = Dither disable, "1" = Dither enable. Default = "0".  [2]: High S/N mode enable. "0" = Normal mode, "1" = High S/N mode. Default = "0".  [3]: High bandwidth Noise shaping filter enable. Default = "0".  "0" = Normal mode. "1" = High bandwidth N/S filter enable.  [7:4]: PWM Linearizer Coefficient. Default = "0000".  [9:8]: Switching Frequency. Default = "00".  "00", "11" = 384KHz  "01" = 192KHz  "10" = 96KHz.  [11:10]: Dead time between positive and negative PWM signal.  The unit is PWM clock (98.304MHz). Default = "00".  [14:12]: Modulation limit. The unit is PWM clock (98.304MHz). Default = "000".  [15]: Reserved.  Default = 0x0000 |

| Register Name  | Address | Word<br>Length | Description                                                       |                        |                                      |                  |                     |

|----------------|---------|----------------|-------------------------------------------------------------------|------------------------|--------------------------------------|------------------|---------------------|

|                |         |                | Status Monit                                                      | oring Register         |                                      |                  |                     |

| SPDIF_CONTROL  | 0x17    | 2 Bytes        | SPDIF status                                                      | register.              |                                      |                  |                     |

|                |         |                | [4:0]: Reserve                                                    | ed. Default = "00      | 0111"                                |                  |                     |

|                |         |                |                                                                   |                        | oort register. Rea                   | -                |                     |

|                |         |                |                                                                   | -                      | = No emphasis, '<br>g. "0" = Consume | -                |                     |

|                |         |                |                                                                   |                        | Copy inhibit, "1"                    |                  |                     |

|                |         |                |                                                                   | _                      | udio, "1" = Non-a                    |                  |                     |

|                |         |                | [9]: SPDIF                                                        | detected flag. "1      | 1" means the PS9                     | 702B detects to  | ne SPDIF sync-word. |

|                |         |                | [10]: Parity                                                      | error flag. "0" =      | Non error, "1" = E                   | Error.           |                     |

|                |         |                |                                                                   | =                      | ag. "0" = Max 20-                    | bit, "1" = Max 2 | 4-bit.              |

|                |         |                | [14:12]: Wo                                                       | ord length.            |                                      |                  |                     |

|                |         |                |                                                                   | Max 24                 | 0                                    | 1                |                     |

|                |         |                |                                                                   | 000                    | Default                              | Default          |                     |

|                |         |                |                                                                   | 001                    | 19                                   | 23               | _                   |

|                |         |                |                                                                   | 010                    | 18<br>17                             | 22               | _                   |

|                |         |                |                                                                   | 100                    | 16                                   | 21               | -                   |

|                |         |                |                                                                   | 101                    | 20                                   | 24               | 1                   |

|                |         |                |                                                                   | Others                 | Reserved                             | Reserved         |                     |

|                |         |                | [15]: Not Use                                                     | <br>d.                 |                                      |                  | _                   |

|                |         |                | Default = 0x0                                                     |                        |                                      |                  |                     |

| OVERLOAD_STATE | 0x18    | 2 Bytes        | Overload stat                                                     | us monitoring re       | egister.                             |                  |                     |

|                |         |                | [0]: Overload                                                     | status. Read or        | nly.                                 |                  |                     |

|                |         |                | "0" = C                                                           | verload protect        | ion is not detecte                   | d or output prot | ection is ended.    |

|                |         |                | "1" = C                                                           | verload is dete        | cted and output p                    | rotection is wor | king.               |

|                |         |                | [15:1]: Not Us                                                    | sed.                   |                                      |                  |                     |

|                |         |                | Default = 0x0                                                     | 000                    |                                      |                  |                     |

|                |         |                | Muting Cor                                                        | trol Register          |                                      |                  |                     |

| SYS_SOFT_MUTE  | 0x3C    | 2 Bytes        | System mute                                                       | control register       |                                      |                  |                     |

|                |         |                | [0]: Mute. Acti                                                   | ve high. <i>Defaul</i> | t = "1"                              |                  |                     |

|                |         |                | [1]: Soft mute function enable. Active high. <i>Default</i> = "1" |                        |                                      |                  |                     |

|                |         |                | [2]: Internal system mute monitoring bit. Read only.              |                        |                                      |                  |                     |

|                |         |                | [10:3]: Internal soft mute level counter. Read only.              |                        |                                      |                  |                     |

|                |         |                | [15:11]: Reserved.                                                |                        |                                      |                  |                     |

|                |         |                | Default = 0x0                                                     | XX7                    |                                      |                  |                     |

|                |         |                |                                                                   |                        |                                      |                  |                     |

|                |         |                |                                                                   |                        |                                      |                  |                     |

| Register Name     | Address                          | Word<br>Length | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|-------------------|----------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                   | MIC Mixer Configuration Register |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| MIC_MIX_LEVEL     | 0x81                             | 2 Bytes        | Mixing level of two microphone input.  The each mixing level value consists of mixing polarity (1-bit) and mixing level coefficient (7-bit). MSB is the mixing polarity ("0" : +, "1" : -) and LS 7-bit is the mixing level coefficient.  Table A-2 shows the relations between the register value and mixing level.  [70]: MIC0 input into Mic mixer output mixing level.  [158]: MIC1 input into Mic mixer output mixing level.  Default = 0x3030. (-6dB)                                                                                                           |  |  |  |

|                   |                                  |                | De-Emphasis Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| DE_EMPHASIS       | 0x82                             | 2 Bytes        | De-Emphasis control Register.  [0]: De-Emphasis control of Front two channel. Active high.  [15:1]: Not Used.  Default = 0x0000                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                   |                                  | Input Cha      | annel Mapping Configuration Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| INPUT_CH_MAPPING1 | 0x83                             | 2 Bytes        | Input channel Mapping Register1.  "0": Input Channel 0 (left channel data from SDIN0)  "1": Input Channel 1 (right channel data from SDIN0)  "2": Input Channel 2 (left channel data from SDIN1)  "3": Input Channel 3 (right channel data from SDIN1)  "4": Input Channel 4 (left channel data from SDIN2)  "5": Input Channel 5 (right channel data from SDIN2)  "6", "7": not used  [2:0]: Input Channel number that is linked to Left Channel.  [3]: Not Used.  [6:4]: Input Channel number that is linked to Right Channel.  [15:7]: Not Used.  Default = 0x0010 |  |  |  |

| INPUT_CH_MAPPING2 | 0x84                             | 2 Bytes        | Input channel Mapping Register2.  [2:0]: Input Channel number that is linked to Left Surround Channel.  [3]: Not Used.  [6:4]: Input Channel number that is linked to Right Surround Channel.  [7]: Not Used.  [10:8]: Input Channel number that is linked to LFE Channel.  [11]: Not Used.  [14:12]: Input Channel number that is linked to Center Channel.  [15]: Not Used.  Default = 0x5432                                                                                                                                                                       |  |  |  |

| Register Name    | Address | Word<br>Length | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|---------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |         |                | Mixer Configuration Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| LR2L_MIX_LEVEL   | 0x85    | 2 Bytes        | Left and Right into Left Mixing level register.  The each mixing level register consists of mixing polarity (1-bit) and mixing level coefficient (7-bit). MSB is the mixing polarity ("0" : +, "1" : -) and LS 7-bit is the mixing level coefficient.  Table A-2 shows the relations between the register value and mixing level.  [70]: Left channel input into Left channel output mixing level.  [158]: Right channel input into Left channel output mixing level.  Default = 0xFF24 (Mute, (+)0dB) |

| CM2L_MIX_LEVEL   | 0x86    | 2 Bytes        | Center and MIC into Left Mixing level register.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                  |         |                | [70]: Center channel input into Left channel output mixing level.  [158]: MIC input into Left channel output mixing level.                                                                                                                                                                                                                                                                                                                                                                             |

| RL2R MIX LEVEL   | 0x87    | 2 Bytes        | Default = 0xFFFF (Mute, Mute)  Right and Left into Right Mixing level register.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RL2R_WIIA_LEVEL  | UXO1    | 2 bytes        | [70]: Right channel input into Right channel output mixing level. [158]: Left channel input into Right channel output mixing level.                                                                                                                                                                                                                                                                                                                                                                    |

|                  |         |                | Default = 0xFF24 (Mute, (+)0dB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CM2R_MIX_LEVEL   | 0x88    | 2 Bytes        | Center and MIC into Right Mixing level register.  [70]: Center channel input into Right channel output mixing level.  [158]: MIC input into Right channel output mixing level.  Default = 0xFFFF (Mute, Mute)                                                                                                                                                                                                                                                                                          |

| LSL2LS_MIX_LEVEL | 0x89    | 2 Bytes        | Left Surround and Left into Left Surround Mixing level register.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                  |         |                | [70]: Left Surround channel input into Left Surround channel output mixing level.  [158]: Left channel input into Left Surround channel output mixing level.  Default = 0xFF24 (Mute, (+)0dB)                                                                                                                                                                                                                                                                                                          |

| RM2LS_MIX_LEVEL  | 0x8a    | 2 Bytes        | Right and MIC into Left Surround Mixing level register.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                  | OXGG    | 2 3 , 60       | [70]: Right channel input into Left Surround channel output mixing level.  [158]: MIC input into Left Surround channel output mixing level.  Default = 0xFFFF (Mute, Mute)                                                                                                                                                                                                                                                                                                                             |

| RSL2RS_MIX_LEVEL | 0x8b    | 2 Bytes        | Right Surround and Left into Right Surround Mixing level register.  [70]: Right Surround channel input into Right Surround channel output mixing level.  [158]: Left channel input into Right Surround channel output mixing level.  Default = 0xFF24 (Mute, (+)0dB)                                                                                                                                                                                                                                   |

| RM2RS_MIX_LEVEL  | 0x8c    | 2 Bytes        | Right and MIC into Right Surround Mixing level register.  [70]: Right channel input into Right Surround channel output mixing level.  [158]: MIC input into Right Surround channel output mixing level.  Default = 0xFFFF (Mute, Mute)                                                                                                                                                                                                                                                                 |