## VR12.5<sup>™</sup> digital multiphase controller with PMBus<sup>™</sup>

Datasheet - custom data

## Features

- PM6764: 4-phase compact digital controller

- PM6766: 6-phase compact digital controller

- Compliant to VR12.5 / 25 MHz SVID bus with programmable IMAX, TMAX, VBOOT, ADDRESS

- High-performance digital control loop (digital STVCOT™)

- Fully configurable through PMBus™

- Flexible driver/DrMOS support

- Single NTC design for TM, LL and IMON thermal compensation

- DPM dynamic phase management

- Remote sense; 0.5% V<sub>OUT</sub> accuracy with calibration

- Current sense across DCR with calibration

- Autocalibration capability for current and voltage sense

- Programmable voltage positioning

- OV, UV and FB disconnection protection

- Embedded non-volatile memory (NVM)

- Black box recorder

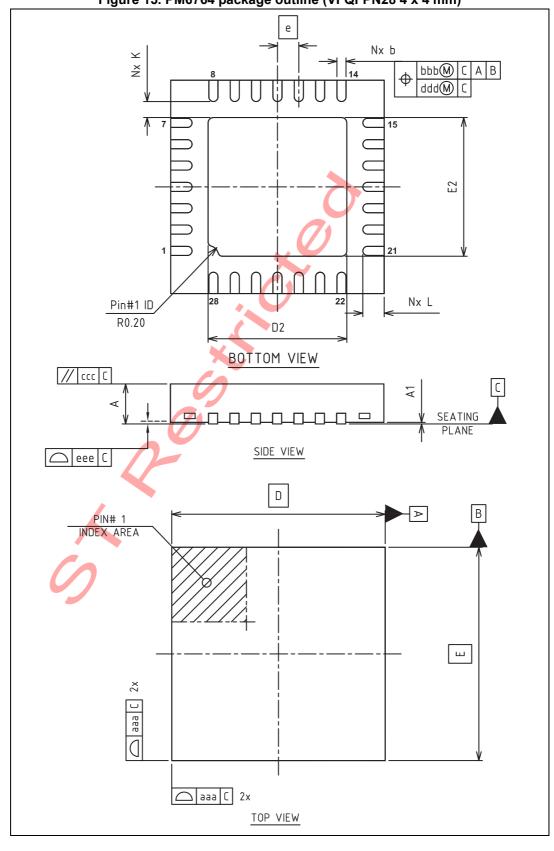

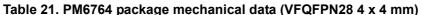

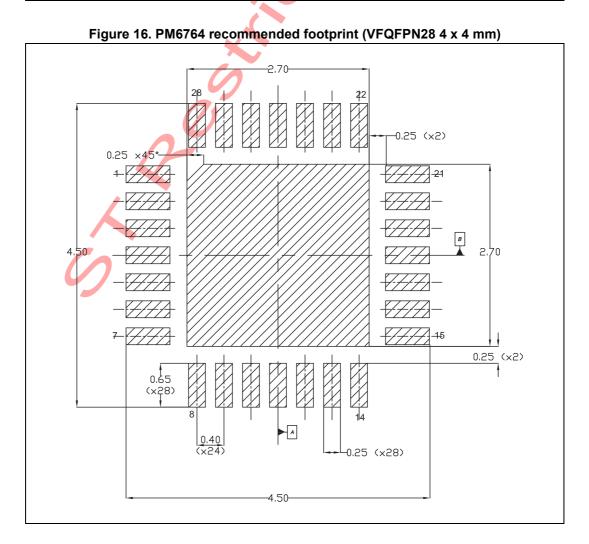

- PM6764: VFQFPN28 4 x 4 mm package

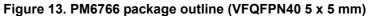

- PM6766: VFQFPN40 5 x 5 mm package

## Applications

- High current power regulation for VR12.5 based Intel<sup>®</sup> based microprocessors

- DDR memory power regulation for VR12.5 based Intel<sup>®</sup> based systems

# Description

The PM6764/66 is a high performance digital controller designed to power Intel's VR12.5 processors (PM6766) and memories (PM6764): all required parameters are programmable through a PMBus™ interface.

The device utilizes digital technology to implement all control and power management functions to provide maximum flexibility and performance. The NVM is embedded to store custom configurations.

The PM6764/66 features up to 4/6-phase programmable operation. The PM6764/66 supports power state transitions featuring VFDE, and programmable DPM maintaining the best efficiency over all loading conditions without compromising transient response. The device assures fast and independent protection against load overcurrent, under/overvoltage and feedback disconnections. The devices are available in VFQFPN28 4 x 4 mm (PM6764) and VFQFPN40 5 x 5 mm (PM6766) packages.

### Table 1. Device summary

| Order code | Package           | Packing       |

|------------|-------------------|---------------|

| PM6764TR   | VFQFPN28 4 x 4 mm | Tape and reel |

| PM6766TR   | VFQFPN40 5 x 5 mm | Tape and reel |

February 2015

1/54

This is a document intended for a specific customer. It must not be released without first contacting Division marketing.

Downloaded from Arrow.com

## Contents

| 1 | Турі | cal application circuit and block diagram |  |  |  |  |  |  |  |  |

|---|------|-------------------------------------------|--|--|--|--|--|--|--|--|

|   | 1.1  | Application circuit                       |  |  |  |  |  |  |  |  |

|   | 1.2  | Block diagram                             |  |  |  |  |  |  |  |  |

| 2 | Pin  | Pin description and connection diagrams   |  |  |  |  |  |  |  |  |

|   | 2.1  | Pin descriptions                          |  |  |  |  |  |  |  |  |

|   | 2.2  | Thermal data                              |  |  |  |  |  |  |  |  |

| 3 | Elec | trical specifications                     |  |  |  |  |  |  |  |  |

|   | 3.1  | Absolute maximum ratings 13               |  |  |  |  |  |  |  |  |

|   | 3.2  | Electrical characteristics                |  |  |  |  |  |  |  |  |

|   |      |                                           |  |  |  |  |  |  |  |  |

| 4 | Devi | ce configuration and pin strapping tables |  |  |  |  |  |  |  |  |

|   | 4.1  | Device address configuration              |  |  |  |  |  |  |  |  |

|   | 4.2  | Non-volatile memory                       |  |  |  |  |  |  |  |  |

|   | 4.3  | Device initialization and startup 17      |  |  |  |  |  |  |  |  |

|   | 4.4  | Device configuration                      |  |  |  |  |  |  |  |  |

|   | 4.5  | Device configuration procedure 21         |  |  |  |  |  |  |  |  |

|   |      |                                           |  |  |  |  |  |  |  |  |

| 5 | Devi | ce description                            |  |  |  |  |  |  |  |  |

|   | 5.1  | Output voltage positioning 22             |  |  |  |  |  |  |  |  |

|   | 5.2  | Active regulation                         |  |  |  |  |  |  |  |  |

|   | 5.3  | Inductors current reading 25              |  |  |  |  |  |  |  |  |

|   | 5.4  | Load line definition                      |  |  |  |  |  |  |  |  |

|   | 5.5  | Thermal monitor and compensation          |  |  |  |  |  |  |  |  |

|   |      | 5.5.1 Thermal monitor and VR_HOT          |  |  |  |  |  |  |  |  |

|   |      | 5.5.2 Thermal compensation                |  |  |  |  |  |  |  |  |

|   |      | 5.5.3 Thermal compensation design         |  |  |  |  |  |  |  |  |

|   | 5.6  | Dynamic VID transition support            |  |  |  |  |  |  |  |  |

|   | 5.7  | DVID optimization                         |  |  |  |  |  |  |  |  |

### ST RESTRICTED - SUBJECT TO NON-DISCLOSURE AGREEMENT - DO NOT COPY

### PM6766-PM6764

| 6 | Monit | toring and protections                            |

|---|-------|---------------------------------------------------|

|   | 6.1   | Input voltage                                     |

|   |       | 6.1.1 Output voltage                              |

|   |       | 6.1.2 Output current                              |

|   |       | 6.1.3 Configurable FAULT# indicator (PM6766 only) |

|   |       | 6.1.4 Configurable SMB ALERT#                     |

|   |       | 6.1.5 Black box recorder (BBR)                    |

| 7 | PMBı  | us™ support                                       |

|   | 7.1   | Digital control loop registers                    |

|   | 7.2   | Fault and monitoring registers 46                 |

| 8 | Packa | age information                                   |

| 9 | Revis | sion history                                      |

|   |       |                                                   |

# **1** Typical application circuit and block diagram

## 1.1 Application circuit

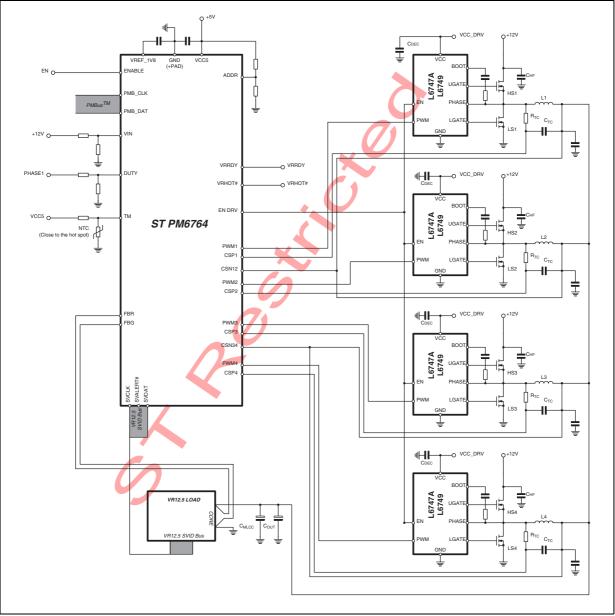

### Figure 1. Typical PM6764 phase application circuit

Typical application circuit and block diagram

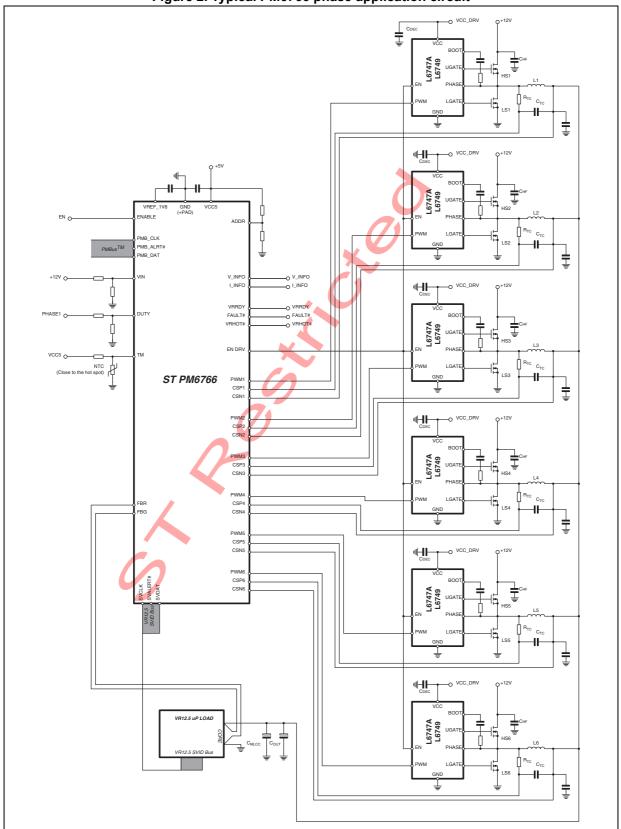

### Figure 2. Typical PM6766 phase application circuit

Typical application circuit and block diagram

PM6766-PM6764

## 1.2 Block diagram

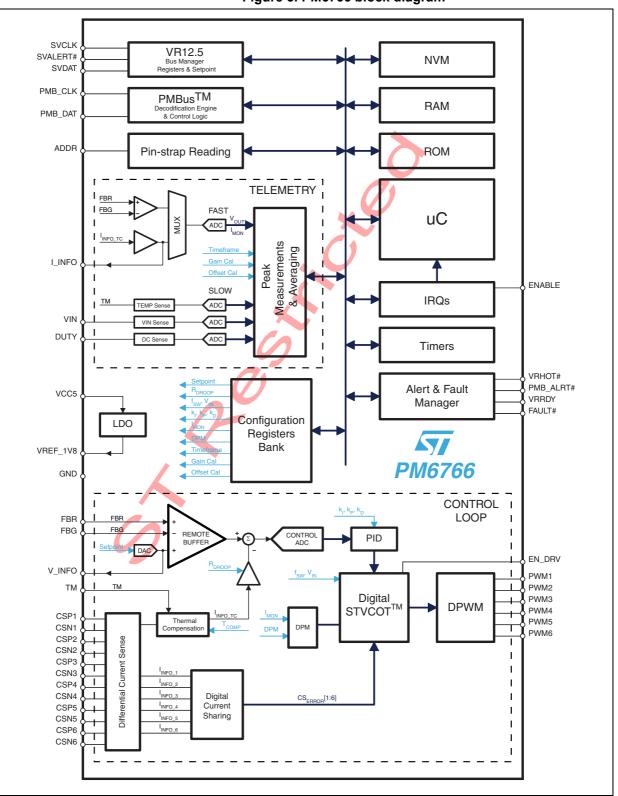

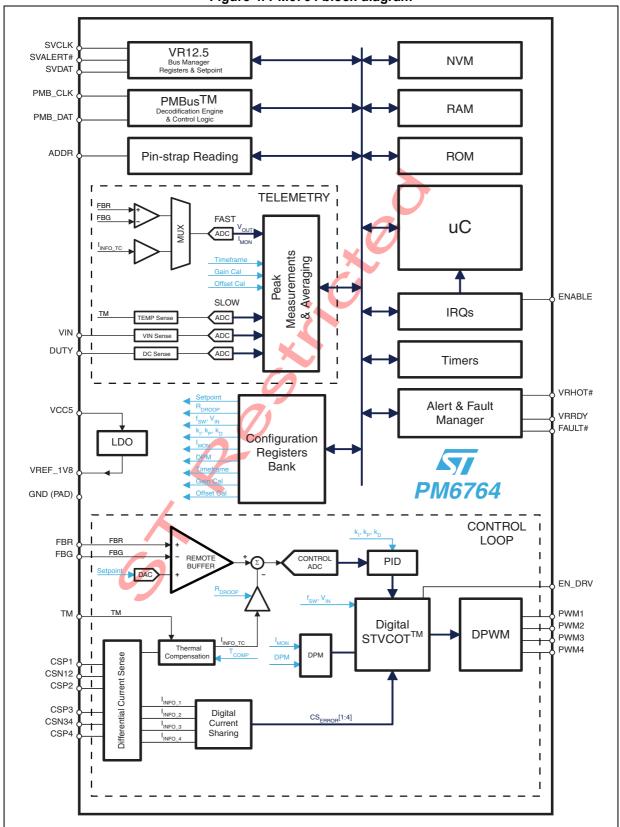

Figure 3. PM6766 block diagram

### ST RESTRICTED - SUBJECT TO NON-DISCLOSURE AGREEMENT - DO NOT COPY

PM6766-PM6764

Typical application circuit and block diagram

Figure 4. PM6764 block diagram

### Pin description and connection diagrams

PM6766-PM6764

## 2 Pin description and connection diagrams

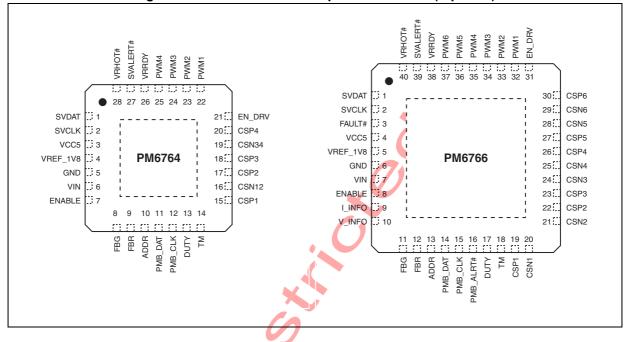

### Figure 5. PM6764 and PM6766 pin connections (top view)

## 2.1 Pin descriptions

### Table 2. Pin description

| Pin    | no.    | Name     | 1/0 | Turno              | Function                                                                                                                                                                                                                                   |

|--------|--------|----------|-----|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PM6766 | PM6764 | Name     | ÿ   | Туре               | Function                                                                                                                                                                                                                                   |

| 1      | 1      | SVDAT    | I/O | Open<br>drain      | VR12.5 bus serial data. Pull-up to an external voltage equal or lower than VREF_1V8.                                                                                                                                                       |

| 2      | 2      | SVCLK    | Ι   | Analog             | VR12.5 bus serial clock. Pull-up to an external voltage equal or lower than VREF_1V8.                                                                                                                                                      |

| 3      | N/A    | FAULT#   | 0   | Open<br>drain      | Programmable fault indicator.<br>Pulled low when triggering any selected fault. See <i>Section 6 on</i><br><i>page 31</i> for details.<br>Pull-up to an external voltage equal or lower than VCC5, if not<br>used it can be left floating. |

| 4      | 3      | VCC5     | I   | Supply             | Main IC analog power supply. Operative voltage is 5 V $\pm$ 5%. Filter with 1 $\mu\text{F}$ MLCC to GND (typ.).                                                                                                                            |

| 5      | 4      | VREF_1V8 |     | Internal<br>supply | Main IC digital power supply (LDO output).<br>It is the output of the internal LDO generating 1.8 V to supply<br>the digital portion of the IC. Filter with 0.1 $\mu$ F MLCC to GND<br>(typ.).                                             |

### Pin description and connection diagrams

### Table 2. Pin description (continued)

| Pin    | no.    | Nama      | 10  | _             | <b>F</b> ound to a                                                                                                                                                                                                               |

|--------|--------|-----------|-----|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PM6766 | PM6764 | Name      | I/O | Туре          | Function                                                                                                                                                                                                                         |

| 6      | 5      | GND       |     | Ground        | GND connection.<br>All internal references and logic are referenced to this pin. Filter<br>to VCC5 and VREF_1V8 with the proper MLCC capacitor and<br>connect to the PCB GND plane.                                              |

| 7      | 6      | VIN       | I   | Analog        | Input voltage monitor.<br>Connect to the input voltage monitor point through a divider $R_{VUP}$ / $R_{VDWN}$ to perform VIN sense through PMBus <sup>TM</sup> ( $R_{UP}$ = 121 k $\Omega$ ; $R_{DOWN}$ = 10.7 k $\Omega$ typ.). |

| 8      | 7      | ENABLE    | I   | CMOS          | Level sensitive enable pin (3.3 V compatible).<br>Pull-low to disable the device, pull-up above the turn-on<br>threshold to enable the controller.                                                                               |

| 9      | N/A    | I_INFO    | 0   | Analog        | Total output current monitor (thermally compensated). This pin is only for monitoring purposes, leave it floating or read with at least 1 $M\Omega$ impedance.                                                                   |

| 10     | N/A    | V_INFO    | 0   | Analog        | Output voltage setpoint monitor. This pin is only for monitoring purposes, leave it floating or read with at least 1 $M\Omega$ impedance.                                                                                        |

| 11     | 8      | FBG       | I   | Analog        | Remote ground sense.<br>Connect to the negative side of the load to perform remote<br>sense.                                                                                                                                     |

| 12     | 9      | FBR       | 2   | Analog        | Remote buffer positive sense.<br>Connect to the positive side of the load to perform remote<br>sense. An anti-aliasing filter embedded.                                                                                          |

| 13     | 10     | ADDR      | -   | Analog        | Connect a resistor divider to VCC5/GND in order to define PMBus <sup>TM</sup> and VR12.5 addressing. See <i>Section 4.1 on page 16</i> for details.                                                                              |

| 14     | 11     | PMB_DAT   | I/O | Open<br>drain | PMBus <sup>TM</sup> data. Pull-up to an external voltage equal or lower than VCC5.                                                                                                                                               |

| 15     | 12     | PMB_CLK   | I   | CMOS          | PMBus <sup>TM</sup> clock. Pull-up to an external voltage equal or lower than VCC5.                                                                                                                                              |

| 16     | N/A    | PMB_ALRT# | 0   | Open<br>drain | PMBus <sup>™</sup> alert. Pull-up to an external voltage equal or lower than VCC5.                                                                                                                                               |

| 17     | 13     | DUTY      | Ι   | Analog        | Duty cycle detection.<br>Connect through the resistor divider to the multiphase channel<br>1 switching node. The voltage on this pin must be equal or<br>lower than VCC5.                                                        |

### Pin description and connection diagrams

### PM6766-PM6764

| Dim    | Table 2. Pin description (continued)       Pin no. |      |     |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|--------|----------------------------------------------------|------|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|        | Name                                               |      | I/O | Туре   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| PM6766 | PM6764                                             |      |     |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 18     | 14                                                 | ТМ   | I   | Analog | Thermal monitor sensor.<br>Connect with the proper network the embedding NTC to the multiphase power section. The IC senses the power section temperature and uses the information to define the VR_HOT signal and temperature monitoring.<br>By programming the proper TCOMP gain through the PMBus <sup>TM</sup> , the IC also implements the load line and IMON thermal compensation.<br>The voltage on this pin must be equal or lower than VCC5.<br>Pull-up to VCC5 with 1 k\Omega to disable the thermal sensor.<br>See Section 5.5 on page 26 for details. |  |  |

| 19     | 15                                                 | CSP1 | Ι   | Analog | Channel 1 current sense positive input.<br>Connect through an R-C filter to the phase-side of the channel<br>1 inductor.                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 20     | 16                                                 | CSN1 | I   | Analog | Channel 1 current sense negative input.<br>Connect to the output-side of the channel 1 inductor. Filter with<br>100 nF (typ.) to GND.<br>In the PM6764, the connection is shared with the channel 2<br>(CSN12).                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 21     | 10                                                 | CSN2 | _   | Analog | Channel 2 current sense negative input.<br>Connect to the output-side of the channel 2 inductor. Filter with<br>100 nF (typ.) to GND.<br>In the PM6764, the connection is shared with the channel 1<br>(CSN12).                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 22     | 17                                                 | CSP2 | K   | Analog | Channel 2 current sense positive input.<br>Connect through an R-C filter to the phase-side of the channel 2 inductor.                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 23     | 18                                                 | CSP3 | I   | Analog | Channel 3 current sense positive input.<br>Connect through an R-C filter to the phase-side of the channel<br>3 inductor.<br>When working at < 3-phase, short to the regulated voltage.                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 24     | 19                                                 | CSN3 | I   | Analog | Channel 3 current sense negative input.<br>Connect to the output-side of the channel 3 inductor. Filter with<br>100 nF (typ) to GND.<br>In the PM6764, the connection is shared with the channel 4<br>(CSN34).                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 25     | 19                                                 | CSN4 | I   | Analog | Channel 4 current sense negative input.<br>Connect to the output-side of the channel 4 inductor. Filter with<br>100 nF (typ.) to GND.<br>In the PM6764, the connection is shared with the channel 3<br>(CSN34).                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 26     | 20                                                 | CSP4 | I   | Analog | Channel 4 current sense positive input.<br>Connect through an R-C filter to the phase-side of the channel<br>4 inductor.<br>When working at < 4-phase, short to the regulated voltage.                                                                                                                                                                                                                                                                                                                                                                            |  |  |

Table 2. Pin description (continued)

### Pin description and connection diagrams

### Table 2. Pin description (continued)

| Pin    | no.    |          |     | _             | F                                                                                                                                                                                                                                                                     |  |  |

|--------|--------|----------|-----|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PM6766 | PM6764 | Name     | I/O | Туре          | Function                                                                                                                                                                                                                                                              |  |  |

| 27     | n/a    | CSP5     | Ι   | Analog        | Channel 5 current sense positive input.<br>Connect through an R-C filter to the phase-side of the channel<br>5 inductor.<br>When working at < 5-phase, short to the regulated voltage.                                                                                |  |  |

| 28     | n/a    | CSN5     | Ι   | Analog        | Channel 5 current sense negative input.<br>Connect to the output-side of the channel 5 inductor. Filter with<br>100 nF (typ.) to GND.                                                                                                                                 |  |  |

| 29     | n/a    | CSN6     | I   | Analog        | Channel 6 current sense negative input.<br>Connect to the output-side of the channel 6 inductor. Filter with<br>100 nF (typ.) to GND.                                                                                                                                 |  |  |

| 30     | n/a    | CSP6     | I   | Analog        | Channel 6 current sense positive input.<br>Connect through an R-C filter to the phase-side of the channel<br>6 inductor.<br>When working at < 6-phase, short to the regulated voltage.                                                                                |  |  |

| 31     | 21     | EN_DRV   | 0   | CMOS          | Enable driver.<br>CMOS output driven high when the IC commands the drivers.<br>Used in conjunction with the HiZ window on the PWMx pins to<br>optimize the overall efficiency. Connect directly to the external<br>driver enable pin.                                 |  |  |

| 32     | 22     | PWM1     | 0   | Tristate      |                                                                                                                                                                                                                                                                       |  |  |

| 33     | 23     | PWM2     | 0   | Tristate      | PWM output.                                                                                                                                                                                                                                                           |  |  |

| 34     | 24     | PWM3     | 0   | Tristate      | Connect to related external driver PWM input.                                                                                                                                                                                                                         |  |  |

| 35     | 25     | PWM4     | 0   | Tristate      | During normal operations the device is able to manage HiZ status by setting and holding the PWMx pin to fixed voltage                                                                                                                                                 |  |  |

| 36     | n/a    | PWM5     | 0   | Tristate      | defined before.                                                                                                                                                                                                                                                       |  |  |

| 37     | n/a    | PWM6     | 0   | Tristate      |                                                                                                                                                                                                                                                                       |  |  |

| 38     | 26     | VRRDY    | 0   | Open<br>drain | VR ready.<br>Set free after SS has finished and pulled low when triggering<br>any protection.<br>Pull-up to an external voltage equal or lower than VCC5.<br>If not used it can be left floating.                                                                     |  |  |

| 39     | 27     | SVALERT# | 0   | Open<br>drain | VR12.5 bus alert. Pull-up to an external voltage equal or lower than VREF_1V8.                                                                                                                                                                                        |  |  |

| 40     | 28     | VRHOT#   | 0   | Open<br>drain | Voltage regulator HOT.<br>This is an alarm signal asserted by the controller when the<br>temperature sensed through the TM pin exceeds TMAX (active<br>low).<br>Pull-up to an external voltage equal or lower than VCC5.<br>See Section 5.5.1 on page 27 for details. |  |  |

| PAD    | PAD    | GND      |     |               | GND connection.<br>All internal references and logic are referenced to this pin. Filter<br>to VCC5 and VREF_1V8 with the proper MLCC capacitor and<br>connect to the PCB GND plane.                                                                                   |  |  |

### Pin description and connection diagrams

PM6766-PM6764

## 2.2 Thermal data

| Table 3. Thermal data |                                                                                          |            |      |  |  |  |

|-----------------------|------------------------------------------------------------------------------------------|------------|------|--|--|--|

| Symbol                | Parameter                                                                                | Value      | Unit |  |  |  |

| P                     | PM6766 - thermal resistance junction to ambient (device soldered on demonstration board) | 35         | °C/W |  |  |  |

| R <sub>THJA</sub>     | PM6764 - thermal resistance junction to ambient (device soldered on demonstration board) | 40         | C/W  |  |  |  |

| R <sub>THJC</sub>     | Thermal resistance junction to case                                                      | 2          | °C/W |  |  |  |

| T <sub>MAX</sub>      | Maximum junction temperature                                                             | 150        | °C   |  |  |  |

| T <sub>STG</sub>      | Storage temperature range                                                                | -40 to 150 | °C   |  |  |  |

| TJ                    | Junction temperature range                                                               | 0 to 125   | °C   |  |  |  |

\_\_\_\_\_

12/54

## 3 Electrical specifications

## 3.1 Absolute maximum ratings

### Table 4. Absolute maximum ratings<sup>(1)</sup>

| Symbol                                                   | Notes    | Value       | Unit |

|----------------------------------------------------------|----------|-------------|------|

| VCC5                                                     |          | -0.3 to 7   | V    |

| VREF_1V8                                                 | (2)      | -0.3 to 2.1 | V    |

| SVDAT, SVCLK                                             | (3)      | -0.3 to 2.1 | V    |

| CSPx, CSNx                                               | (2), (4) | -0.3 to 2.5 | V    |

| VIN, ENABLE, ADDR, PMB_DAT,<br>PMB_CLK, DUTY, TM, VRHOT# | (2)      | -0.3 to 7   | V    |

1. All voltages referenced to GND unless otherwise specified.

2. Need to be lower than VCC5 under any condition.

3. Need to be lower than VREF\_1V8 under any condition.

4. Max. differential voltage to be limited within 100 mV.

### Table 5. Recommended operative conditions<sup>(1)</sup>

| Symbol    | Parameter  | Value     | Unit |

|-----------|------------|-----------|------|

| VCC5      | 7.         | 5 +/- 10% | V    |

| VID (max) | Programmed | 2.3       | V    |

1. All voltages referenced to GND unless otherwise specified.

### Note: Absolute maximum ratings are those values beyond which damage to the device may occur. These are stress ratings only and functional operation of the device at these conditions is not implied. Operating outside maximum recommended conditions for extended periods of time may impact product reliability and result in device failures.

## 3.2 Electrical characteristics

### Table 6. Electrical characteristics

(VCC5 = 5 V, Tamb = 25 °C unless otherwise specified)

|                    | Parameter                          | Test conditions                                                     | Min.  | Тур. | Max.  | Unit |

|--------------------|------------------------------------|---------------------------------------------------------------------|-------|------|-------|------|

| Supply curre       | nt and power-on                    |                                                                     |       | L    |       |      |

|                    | Supply current                     |                                                                     |       | 60   |       | mA   |

| VCC5               | UVLO turn-on                       | VCC5 rising                                                         |       |      | 4.2   | V    |

|                    | UVLO turn-off                      | VCC5 falling                                                        | 3.5   |      |       | V    |

|                    | Voltage accuracy                   |                                                                     | 1.760 |      | 1.860 | V    |

| VREF_1V8           | Load regulation                    | I = 50 mA                                                           | 25    |      | 55    | mV   |

|                    | Current capability                 |                                                                     |       |      | 50    | mA   |

| Enable             |                                    | ×                                                                   |       |      |       |      |

|                    | Input high voltage                 | ENABLE voltage rising                                               |       |      | 0.7   | V    |

| ENABLE             | Input low voltage                  | ENABLE voltage falling                                              | 0.4   |      |       | V    |

|                    | Leakage current                    | V <sub>EN</sub> = 1.1 V                                             |       |      | 1     | μA   |

| SVI serial bu      | 5                                  |                                                                     |       |      |       |      |

| SVCLK,             | Input high voltage                 | 6                                                                   | 0.65  |      |       | V    |

| SVDAT              | Input low voltage                  |                                                                     |       |      | 0.45  | V    |

| SVALERT#           | Output low voltage                 | I <sub>SINK</sub> = 5 mA                                            |       |      | 125   | mV   |

| PMBus <sup>™</sup> |                                    |                                                                     |       |      |       |      |

| PMB CLK,           | Input high voltage                 |                                                                     | 1.75  |      |       | V    |

| PMB_DAT            | Input low voltage                  |                                                                     |       |      | 1.45  | V    |

| PMB_ALRT#          | Output low voltage                 | I <sub>SINK</sub> = 5 mA                                            |       |      | 70    | mV   |

| Reference an       | d ADC                              |                                                                     |       |      |       |      |

|                    | 0                                  | FBR to $V_{CORE}$ , FBG to $GND_{CORE}$ ;<br>VID = 1.50 V to 2.30 V | -0.5  | -    | 0.5   | %    |

| k <sub>VID</sub>   | V <sub>OUT</sub> setpoint accuracy | FBR to $V_{CORE}$ , FBG to $GND_{CORE}$ ;<br>VID = 1.00 V to 1.49 V | -8    | -    | 8     | mV   |

|                    |                                    | FBR to $V_{CORE}$ , FBG to $GND_{CORE}$ ;<br>VID < 0.99 V           | -10   | -    | 10    | mV   |

|                    |                                    | V <sub>OUT</sub> error; I <sub>LOAD</sub> = 0 A;                    | -6.5  | -    | 6.5   | mV   |

| k <sub>DROOP</sub> | LL Accuracy<br>MFR VOUT LL = 0x4D  | N <sub>PH</sub> = 6; VCSNx - VCSPx = 10 mV                          | 1.00  | 1.05 | 1.10  | -    |

|                    |                                    | N <sub>PH</sub> = 4; VCSNx - VCSPx = 10 mV                          | 1.07  | 1.13 | 1.19  | -    |

14/54

### **Electrical specifications**

|                      | Parameter                   | Test conditions                                                                                                                                         | Min. | Тур. | Max. | Unit  |

|----------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

|                      | GetReg(15h)                 | <pre>N<sub>PH</sub> = 6, (VCSPx-VCSNx) = 10 mV<br/>IMON = 0x08,<br/>TEL_IOUTMAX = 0xFF,<br/>MFR_IOUT_CAL_GAIN = 0xB4<br/>IOUT_CAL_OFFSET = 0xF72A</pre> | C2   | C8   | CE   | Hex   |

| I <sub>MON</sub> ADC | GetReg(15h)                 | N <sub>PH</sub> = 4, (VCSPx-VCSNx) = 8 mV<br>IMON = 0x16,<br>TEL_IOUTMAX = 0xCA,<br>MFR_IOUT_CAL_GAIN = 0x9C,<br>IOUT_CAL_OFFSET = 0xF750               | 47   | 4A   | 4D   | Hex   |

| VIN ADC              | READ_VIN                    | Accuracy; VIN = 1 V                                                                                                                                     | 11.9 | 12.3 | 12.7 | V     |

| DUTY ADC             | READ_DUTY_CYCLE<br>accuracy | DUTY = 25%                                                                                                                                              | -1   |      | 1    | %     |

| DVID                 | Slew rate fast, min         | DVID_SR_FAST_STEP = 0x0A                                                                                                                                |      | 20   |      | mV/μs |

| DVID                 | Slew rate slow, min         | DVID_SR_SLOW_STEP = 0x28                                                                                                                                |      | 5    |      | mV/μs |

| k <sub>CK</sub>      | Time base accuracy          |                                                                                                                                                         | -5   |      | 5    | %     |

| PWM outputs          | and ENDRV                   |                                                                                                                                                         |      |      |      |       |

|                      |                             | $PWM_HIZ = 0x00$                                                                                                                                        | 1.35 | 1.40 | 1.45 | V     |

| HiZ                  | PWM high impedance          | PWM_HIZ = 0x01                                                                                                                                          | 1.55 | 1.60 | 1.65 | V     |

| EN_DRV               | Voltage low                 | I <sub>ENDRV</sub> = -4 mA                                                                                                                              |      |      | 0.4  | V     |

| Protections          |                             |                                                                                                                                                         |      |      |      |       |

| OVP                  | Overvoltage protection      | (FBR-FBG) rising; above setpoint                                                                                                                        | 350  |      | 450  | mV    |

| FBR DISC             | FBR disconnection           | V <sub>CSN1</sub> rising, above (FBR-FBG)                                                                                                               |      | 700  |      | mV    |

| FBG DISC             | FBG disconnection           | Remote buffer output, above FBR                                                                                                                         |      | 700  |      | mV    |

| V                    | OC threshold,               | <b>N = 6</b> ; IMON = 0x06                                                                                                                              | 17.1 | 21.4 | 25.7 | mV    |

| V <sub>OC_TOT</sub>  | CSPx - CSNx                 | N = 4; IMON = 0x09                                                                                                                                      | 17.1 |      | 20.1 | mv    |

| VRRDY                | Output low voltage          | I <sub>SINK</sub> = 4 mA                                                                                                                                |      |      | 110  | mV    |

| VRHOT#               | Output low voltage          | I <sub>SINK</sub> = 4 mA                                                                                                                                |      |      | 75   | mV    |

| FAULT#               | Output low voltage          | I <sub>SINK</sub> = 4 mA                                                                                                                                |      |      | 150  | mV    |

(VCC5 = 5 V. Tamb = 25  $^{\circ}$ C unless otherwise specified)

## 4 Device configuration and pin strapping tables

The full digital architecture of the PM6766 and PM6764 devices allow to configure the behavior of the control loop, the power management and the fault handling. The configuration is stored in the embedded non-volatile memory (NVM) and can be modified using the PMBus<sup>™</sup> and VR12.5 interfaces.

The PM6764, PM6766 devices are fully compliant with the PMBus<sup>™</sup> specification part I and part II, revision 1.2 (*www.pmbus.org*). Devices are fully compatible with the PMBus<sup>™</sup> specification for read/write access in the byte, word, block mode.

The PM6764, PM6766 devices are fully compliant with the Intel<sup>®</sup> VR12.5 SVID protocol Rev1.2, document # 453513. To guarantee proper device and CPU operations, refer to this document for bus design and layout guidelines. Different platforms may require different pull-up impedance on the SVI bus. Impedance matching and spacing between SVDAT, SVCLK, and SVALERT# must be followed.

## 4.1 Device address configuration

The PMBus<sup>M</sup> and the VR12.5 slave addresses are configured at the startup of the device by reading the voltage on the ADDR pin. The proper resistor divider must be connected from the ADDR pin to the GND and VCC5 pins (see *Figure 1 on page 4* and *Figure 2 on page 5*) as per *Table 7*.

| R <sub>UP</sub> [kΩ] R <sub>DOWN</sub> [kΩ] |      | PM6                         | 764            | PM6766                      |                |  |  |

|---------------------------------------------|------|-----------------------------|----------------|-----------------------------|----------------|--|--|

|                                             |      | PMBus <sup>TM</sup> address | VR12.5 address | PMBus <sup>TM</sup> address | VR12.5 address |  |  |

| 12                                          | 13   | 0xE0                        |                |                             |                |  |  |

| 10                                          | 12   | 0xE4                        | 0x02           | 0xC0                        |                |  |  |

| 5.6                                         | 7.5  | 0xE8                        | 0x02           | UXCU                        |                |  |  |

| 4.3                                         | 6.8  | 0xEC                        |                |                             |                |  |  |

| 4.7                                         | 8.2  | 0xE2                        |                |                             |                |  |  |

| 3.9                                         | 8.2  | 0xE6                        | 0x04           | 0xC4                        |                |  |  |

| 5.1                                         | 12   | 0xEA                        | 0,04           | 0xC4                        |                |  |  |

| 4.3                                         | 12   | 0xEE                        |                |                             | 0x00           |  |  |

| 6.8                                         | 22   | 0xD0                        |                |                             | 0,00           |  |  |

| 5.6                                         | 22   | 0xD4                        | 0x06           | 0xC8                        |                |  |  |

| 4.7                                         | 22   | 0xD8                        | 0,000          | 0x08                        |                |  |  |

| 3.6                                         | 22   | 0xDC                        |                |                             |                |  |  |

| 2.7                                         | 22   | 0xD2                        |                |                             |                |  |  |

| 1.8                                         | 22   | 0xD6                        | 0x08           | 0×CC                        |                |  |  |

| 1                                           | 22   | 0xDC                        | UXUO           | 0xCC                        |                |  |  |

| 0                                           | Open | 0xDE                        |                |                             |                |  |  |

### Table 7. PM6764, PM6766 address pin-strap

16/54

### 4.2 Non-volatile memory

The PM6764, PM6766 devices have an on-board non-volatile memory that allows storing the actual configuration of the device. Furthermore, additional user data can be stored into the NVM using USER\_DATA\_00 and USER\_DATA\_01 commands (see *Table 14 on page 37*). Storing/restoring the configuration data to/from the memory is performed by the single standard PMBus<sup>™</sup> command STORE/RESTORE\_DEFAULT\_ALL. Any unintended writing can be prevented using the write protection capability enabled by the custom MFR\_PROTECT\_DEFAULT\_command.

During the design and the fine-tuning of the application, using the PM6764/66 graphical user interface, each configuration written into the device is uniquely identified by:

- An incremental revision number, MFR\_PMBUSCFG\_REVISION custom command

- A digital timestamp in ISO 8601:2004 format (YYYYMMDDHHMM), MFR PMBUSCFG TIMESTAMP L&H custom commands

- A user ID identifier, MFR\_PMBUSCFG\_USERID custom command

The embedded NVM is also used to store the status of the device when a critical fault occurs (black box recorder function).

Memory cells are qualified for 1000 read/erase/write cycles and 5 years at 85 °C data retention.

## 4.3 Device initialization and startup

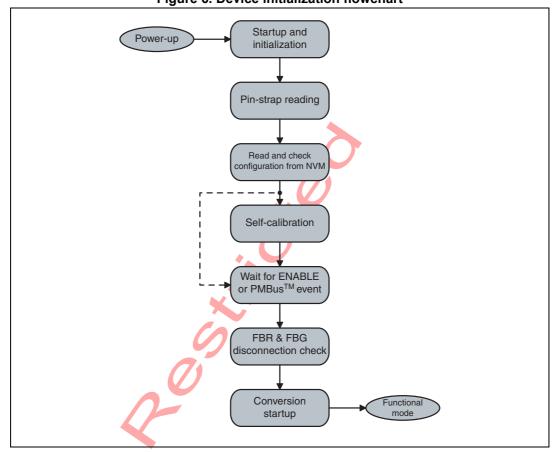

When power supply voltage greater than the UVLO threshold is applied to the device, the steps illustrated in the diagram of *Figure 6* are performed.

As soon as the supply voltage on the pin VCC5 is greater than the UVLO, the analog circuitry is started and stabilized and all the digital blocks are initialized.

Then, the voltage on the pin ADDR is read and both the PMBus<sup>TM</sup> and the VR12.5 slave addresses are calculated as per *Table* 7.

At this stage, the configuration of the device is read from the embedded NVM and written to the operating (volatile) memory. In order to ensure the validity of the current configuration, thus avoiding dangerous operating conditions, a CRC check is performed over the whole content of the non-volatile memory. If any error is detected, the power conversion is not started and the status flag "*Memory fault detected*" in the STATUS\_CML register is set.

The self-calibration nulls out any error due to the residual offsets in the output voltage and in the output current readings, resulting in improved voltage positioning and current telemetry accuracies. This procedure is fully automated and does not require neither intervention by the user, nor additional external components. If desired, the self-calibration can be disabled by setting the corresponding parameter in the configuration of the device.

The conversion startup can now be requested asserting the ENABLE pin, sending the PMBus<sup>™</sup> command OPERATION or configuring the device to the startup regardless of the previous two events. During the startup sequence, a feedback disconnection check is performed. In order to prevent possible damage to the load, the device checks if the FBR or the FBG pins are not connected to the output stage of the converter. In this case, the power conversion is stopped and the "FB disconnection" flag in the STATUS\_MFR\_SPECIFIC register is set.

### Device configuration and pin strapping tables

### PM6766-PM6764

After the completion of the soft-start, the device is fully functional and is able to manage any command sent via the PMBus<sup>™</sup> or VR12.5 digital interfaces.

## 4.4 Device configuration

The PM6764/66 devices have a dedicated system register, stored in the NVM memory, to customize the device behavior for each specific application. These registers can be programmed using dedicated PMBus<sup>™</sup> commands. The main functions of system registers are:

- Program the IMON resistor to define the overcurrent threshold (see Section 6.1.2 on page 33)

- Program the HiZ levels for HiZ on PWMx guaranteeing flexibility in driving different external drivers as well as the DrMOS ICs

- Program the DVID optimization features (See Section 5.7 on page 29)

- Program the BOOT voltage

- Program the thermal compensation of the monitored output current (See Section 5.5.2 on page 27 and following)

- Program the power managements features like phase numbers, phase shedding behavior and light load efficiency optimizations

- Calibration of the monitored input and output rails

DocID026534 Rev 3

18/54

### Device configuration and pin strapping tables

The list of supported registers is detailed in Table 8.

| Table 8. System registers |                            |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|---------------------------|----------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Register                  | Address                    | Data<br>bytes | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| Application setup         |                            |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| IMON                      | 0x00B002                   | 1             | Used to change the current monitoring resistor. See Section 6.1.2 on<br>page 33.<br>$IMON[7:0] = R_{IMON} \cdot \frac{63}{95984}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| PWM_HIZ                   | 0x00B004                   | 1             | Used to set the voltage of the PWMx when in the hi-impedance state<br>(HiZ). The supported values are:<br>0x00: 1.4 V<br>0x01: 1.6 V<br>0x02: 1.8 V<br>0x03: 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| TCOMP                     | 0x00B005                   | 1             | Used to thermally compensate the device. See Section 5.5 on page 26.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| VR12_VBOOT                | 0x0200DA                   | 1             | Used to set the BOOT voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| DVID_OPT_PARAM            | 0x00B00F<br>to<br>0x00B014 | 6             | Used to set the DVID optimization parameters. See Section 5.6 on page 28.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Power management          |                            |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| PFM_ENA_PS                | 0х00В006                   | 1             | Used to enable the PFM working mode vs. power states (PSx).<br>The supported values are:<br>0x00: PFM disabled<br>0x01: PFM enabled in PS0 only<br>0x02: PFM enabled in PS1 only<br>0x03: PFM enabled in PS1, PS0<br>0x04: PFM enabled in PS2 only<br>0x05: PFM enabled in PS2, PS0<br>0x06: PFM enabled in PS2, PS1<br>0x07: PFM enabled in PS2, PS1, PS0<br>0x08: PFM enabled in PS3 only<br>0x09: PFM enabled in PS3, PS1<br>0x0A: PFM enabled in PS3, PS1<br>0x0B: PFM enabled in PS3, PS1<br>0x0C: PFM enabled in PS3, PS2<br>0x0D: PFM enabled in PS3, PS2, PS1<br>0x0E: PFM enabled in PS3, PS2, PS1<br>0x0F: PFM enabled in PS3, PS2, PS1 |  |  |  |

| DISABLE_OCP               | 0x00B007                   | 1             | Used to enable [0x00] or disable [0x01] the HW OCP fault detection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| DPM_HYSTERESIS            | 0x00B008                   | 1             | Used to set the dynamic phase management current hysteresis [A].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| DPM_NPH_PS0               | 0x00B009                   | 1             | Used to set the nominal number of active phases in PS0 when DPM is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

### Device configuration and pin strapping tables

### PM6766-PM6764

| Register               | Address                   | Data<br>bytes | Description                                                                |  |  |  |

|------------------------|---------------------------|---------------|----------------------------------------------------------------------------|--|--|--|

| DPM_NPH_PS1            | 0x00B00A                  | 1             | Used to set the nominal number of active phases in PS1 when DPM i enabled. |  |  |  |

| DPM_NPOP               | 0x00B00B                  | 1             | Used to set the number of phases populated on the board.                   |  |  |  |

| DISABLE_OVP            | 0x00B00C                  | 1             | Used to enable [0x00] or disable [0x01] the HW OVP fault detection.        |  |  |  |

| EN_PGOOD               | 0x00B015                  | 1             | Used to enable [0x00] or disable [0x01] the PGOOD pin output.              |  |  |  |

| EN_VRRDY               | 0x00B016                  | 1             | Used to enable [0x00] or disable [0x01] the VRRDY pin output.              |  |  |  |

| Monitoring calibration | า                         |               | $\mathbf{O}$                                                               |  |  |  |

| TEL_IOUT_EXP           | 0x00B019                  | 1             | Used to set the output current readings exponent.                          |  |  |  |

| TEL_IIN_GAIN           | 0x00B01A                  | 1             | Used to set the input current readings gain correction.                    |  |  |  |

| TEL_PIN_GAIN           | 0x00B01B                  | 1             | Used to set the input power readings gain correction.                      |  |  |  |

| TEL_POUT_GAIN          | 0x00B01C                  | 1             | Used to set the output power readings gain correction.                     |  |  |  |

| TEL_VIN_GAIN           | 0x00B01D                  | 1             | Used to set the input voltage readings gain correction.                    |  |  |  |

| TEL_IOUT_MAX           | 0x00B01E                  | 1             | Used to set the output current overcurrent threshold [A].                  |  |  |  |

| TEL_IIN_OFFSET         | 0x00B01F<br>-<br>0x00B020 | 2             | Used to set the input current readings offset correction [A]               |  |  |  |

| TEL_PIN_OFFSET         | 0x00B021<br>-<br>0x00B022 | 2             | Used to set the input power readings offset correction [W].                |  |  |  |

| TEL_POUT_OFFSET        | 0x00B023<br>-<br>0x00B024 | 2             | Used to set the output power readings offset correction [W].               |  |  |  |

| TEL_VIN_OFFSET         | 0x00B025<br>-<br>0x00B026 | 2             | Used to set the input voltage readings offset correction [V].              |  |  |  |

| TEL_VIN_EXP            | 0x00B027                  | 1             | Used to set the input voltage readings exponent.                           |  |  |  |

| TEL_VOUT_EXP           | 0x00B028                  | 1             | Used to set the output voltage readings exponent.                          |  |  |  |

Table 8. System registers (continued)

### 4.5 Device configuration procedure

To program the system registers the following basic procedures can be used:

### **READ** procedure

- Write the memory location address to be read using the MFR\_MEMORY\_RD PMBus™ command.

- Read the memory location addressed using the MFR\_MEMORY\_WORD PMBus™ command

#### WRITE procedure

- Write the data to written into the memory using the MFR\_MEMORY\_WORD PMBus™ command

- Write the memory location address to be written using the *MFR\_MEMORY\_WR* PMBus™ command.

See Table 14 on page 37 for details about the MFR\_MEMORY\_RD, MFR\_MEMORY\_WR and MFR\_MEMORY\_WORD commands.

57

## 5 Device description

The PM6764, PM6766 devices are single rail controllers with a complete control logic and protections to realize a high performance step-down DC-DC voltage regulator optimized for the advanced microprocessor and memories power supply.

The controllers are based on the high performances digital STVCOT<sup>™</sup> architecture, allowing to have fast load transient response, linear with the load frequency sweep, while maintaining

a nearly constant switching frequency in the steady state allowing to minimize the output filter components.

The PM6764, PM6766 devices implement current reading across the inductor in the differential mode.

A sense resistor in series to the inductor can be also considered to improve reading precision. The current information read corrects the PWM output in order to equalize the average current carried by each phase.

In order to guarantee the load to be safe under all circumstances, a complete set of protection is available on the output voltage/current, input voltage/current, feedback disconnection, temperature, input/output powers and catastrophic fails.

Special power management features like DPM and VFDE modify the phase number and switching frequency to optimize the efficiency over the load range.

All the required parameters of both the control loop and power management features are programmable through dedicated PMBus<sup>™</sup> commands.

The PM6764, PM6766 devices are available in VFQFPN28 4 x 4 mm and VFQFPN40 5 x 5 mm packages.

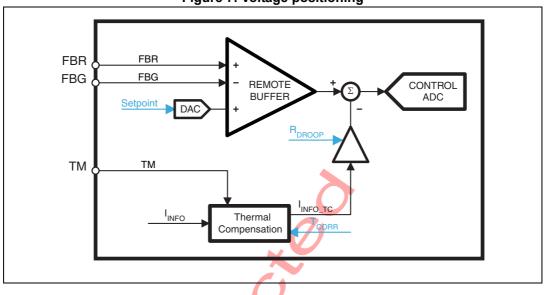

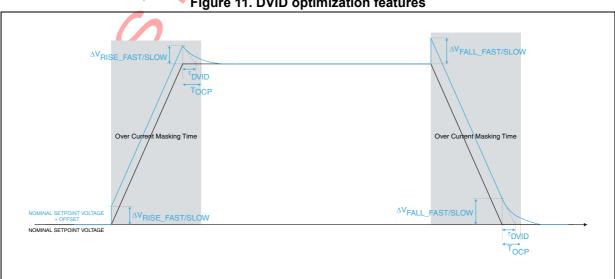

## 5.1 Output voltage positioning

Output voltage positioning is performed by programming the digital control loop parameters and droop function effect (see *Figure 7*) using the dedicated PMBus<sup>TM</sup> commands (see *Section 7.1 on page 44*). The controller reads the current delivered by monitoring the voltage drop across the DCR inductors. The total current ( $I_{INFO}$ ) is internally compensated vs. temperature variations ( $I_{INFO_TC}$ ), converted into a direct proportional voltage using the PMBus<sup>TM</sup> programmable resistor ( $R_{DROOP}$ ) and added to the remote buffer output voltage causing the output voltage to vary accordingly, thus implementing the desired load line effect. This voltage is finally converted into digital value and used by the digital control loop for the regulation.

The PM6674, PM6766 devices embed a remote-sense buffer to sense remotely the regulated voltage without any additional external components. In this way, the output voltage programmed is regulated compensating for board and socket losses. Keeping the sense traces parallel and guarded by a power plane results in the common mode coupling for any picked-up noise.

Figure 7. Voltage positioning

## 5.2 Active regulation

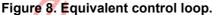

The PM6764/66 controllers implement the proprietary digital STVCOT<sup>™</sup> architecture.

During operation, the output voltage is sensed differentially and digitized by a fast analog-todigital converter (ADC). The resultant digital error signal is then fed into a digital PID compensator and then processed by the digital STVCOT<sup>™</sup> control logic.

The output of the digital loop is converted into a PWM pulse using a digital pulse width modulator (DPWM).

The digital STVCOT<sup>TM</sup> architecture can be modeled with an equivalent analog control loop and with a single-phase converter, which only difference is the equivalent inductor L/N (where each phase has an L inductor and N is the number of the configured phases). See *Figure 8*. The user can adjust the parameter for the control loop compensation by working in the digital environment or, as more convenient, working in the corresponding analog equivalent environment.

The equivalent transfer function of the control loop is:

### Equation 1

$$G_{LOOP}(s) = -GAIN \cdot \frac{Z_{OUT}(s)}{Z_{OUT}(s) + Z_{L}(s)} \cdot \frac{Z_{F}(s)}{Z_{FB}(s)} \cdot \left[1 + \frac{DCR}{R_{G}} \cdot \frac{R_{DROOP}(s)}{Z_{OUT}(s)}\right]$$

Where:

- *Z<sub>OUT</sub>*(*s*) is the impedance resulting by the parallel of the output capacitor (and its ESR) and the applied load R<sub>O</sub>

- $Z_F(s)$ ,  $Z_{FB}(s)$  are the compensation network impedances

- $Z_L(s)$  is the equivalent inductor impedance

- GAIN is the PWM transfer function. It is a constant value (= 4) once programmed the application input voltage (V<sub>IN</sub>) in the SYS\_CONFIG PMBus™ register, see *Table 15 on page 44*.

### **Device description**

The analog equivalent transfer function allows to design the control loop using the analog well known techniques and then to transform them into digital coefficients using these formulas:

#### **Equation 2**

**Equation 3**

**Equation 4**

**Equation 5**

**Equation 6**

$$\begin{split} \mathsf{K}_{\mathsf{p}} &= \frac{\mathsf{R}_{\mathsf{F}} \cdot \mathsf{C}_{\mathsf{F}} + \mathsf{C}_{\mathsf{I}} \cdot (\mathsf{R}_{\mathsf{I}} + \mathsf{R}_{\mathsf{FB}})}{\mathsf{R}_{\mathsf{FB}} \cdot (\mathsf{C}_{\mathsf{P}} + \mathsf{C}_{\mathsf{F}})} \\ \\ \mathsf{K}_{\mathsf{i}} &= \frac{1}{\mathsf{R}_{\mathsf{FB}} \cdot (\mathsf{C}_{\mathsf{P}} + \mathsf{C}_{\mathsf{F}})} \\ \\ \mathsf{K}_{\mathsf{d}} &= \frac{\mathsf{R}_{\mathsf{F}} \cdot \mathsf{C}_{\mathsf{F}} \cdot \mathsf{C}_{\mathsf{I}} \cdot \mathsf{R}_{\mathsf{FB}}}{\mathsf{R}_{\mathsf{FB}} \cdot \mathsf{C}_{\mathsf{F}}} \\ \\ \\ \tau_{\mathsf{PRE}} &= \mathsf{R}_{\mathsf{I}} \cdot \mathsf{C}_{\mathsf{I}} \\ \\ \\ \\ \tau_{\mathsf{POST}} &= \mathsf{R}_{\mathsf{F}} \cdot \left(\frac{\mathsf{C}_{\mathsf{F}} \cdot \mathsf{C}_{\mathsf{P}}}{\mathsf{C}_{\mathsf{F}} + \mathsf{C}_{\mathsf{P}}}\right) \end{split}$$

These coefficients are programmed into the PM6764/66 using the MFR\_PID and MFR\_PRECONDITIONING PMBus™ registers, see Table 16 on page 45 and Table 17 on page 46.

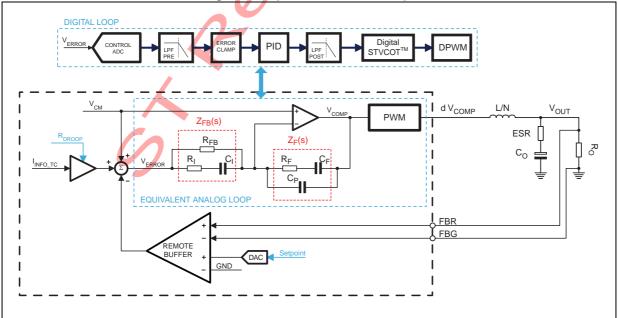

## 5.3 Inductors current reading

The PM6764/66 devices embed a flexible, differential current sense circuitry that is able to read across the inductor parasitic resistance or across a sense resistor placed in series to the inductor element. The differential current reading rejects noise and allows placing the sensing element in different locations without affecting the measurement's accuracy. The transconductance ratio is issued by the internal resistor  $R_G = 560\Omega$ . The current sense circuit always tracks the current information; to correctly reproduce the inductor current an R-C filtering network must be introduced in parallel to the sensing element. The current that flows from the CSNx pin is then given by the following equation (see *Figure 9*):

#### **Equation 7**

$$I_{CSNx} = \frac{DCR}{R_G} \cdot \frac{1 + s \cdot L DCR}{1 + s \cdot R \cdot C} \cdot I_{PHASEx}$$

Considering now to match the time constant between the inductor and the R-C filter applied (time constant mismatches cause the introduction of poles into the current reading network causing instability. In addition, it is also important for the load transient response and to let the system show resistive equivalent output impedance) it results:

#### **Equation 8**

$$\frac{L}{DCR} = R \cdot C \implies I_{CSNx} = \frac{DCR}{R_G} \cdot I_{PHASEx} = I_{INFO_X}$$

The current read through the CSPx / CSNx pairs is converted into a current  $I_{INFO_x}$  proportional to the current delivered by each phase and the information about the average current  $I_{AVG} = \Sigma I_{INFO_x} / N$  is internally built into the device (*N* is the number of working phases).

The error between the read current  $I_{INFO_x}$  and the reference  $I_{AVG}$  is then used to adjust the ON time of the PWMx signals in order to equalize the current carried by each phase.

The current sharing loop bandwidth can be adjusted with the SYS\_CONFIG PMBus<sup>TM</sup> register, see *Table 15 on page 44*. It is recommended to use R resistors not exceeding 200 k $\Omega$ .

### 5.4 Load line definition

The PM6764/66 devices introduce a dependence of the output voltage on the load current recovering a part of the drop due to the output capacitor ESR in the load transient. Introducing a dependence of the output voltage on the load current, a static error, proportional to the output current, causes the output voltage to vary according to the sensed current.

*Figure 9* shows the current sense circuit used to implement the load line. The current flowing across the inductor(s) is read through the R - C filter across the CSPx and CSNx pins. The integrated R<sub>G</sub> resistors program a transconductance gain and generate a current  $I_{INFO_X}$  proportional to the current of the phase. The sum of the  $I_{INFO_X}$  currents ( $I_{INFO}$ ) is first thermally compensated using TM information ( $I_{INFO_TM}$ ) and then converted into a direct proportional voltage using the PMBus<sup>TM</sup> programmable resistor ( $R_{DROOP}$ ). The  $R_{DROOP}$  gives the final gain to program the desired load line slope (see *Figure 7*).

Time constant matching between the inductor (L / DCR) and the current reading filter (RC) is required to implement a real equivalent output impedance of the system, so avoiding over and/or undershoot of the output voltage as a consequence of a load transient.

The output voltage characteristic vs. load current (see *Section 5.5.2* for details on thermal compensation), is then given by:

#### **Equation 9**

$$V_{OUT} = VID - R_{DROOP} \cdot I_{NFO_{TC}} = VID - R_{DROOP} \cdot \frac{DCR}{R_{DC}} \cdot I_{OUT} = VID - R_{LL} \cdot I_{OUT}$$

Where  $R_{LL}$  is the resulting load line resistance implemented by the device. The  $R_{DROOP}$  resistor can be then designed according to the  $R_{LL}$  specifications as follow:

Equation 10

$$R_{DROOP} = R_{LL} \cdot \frac{R_G}{DCR}$$

The digital droop function is programmed into the PM6764/66 using the MFR\_VOUT\_LL PMBus<sup>™</sup> register, see *Table 14 on page 37*.

## 5.5 Thermal monitor and compensation

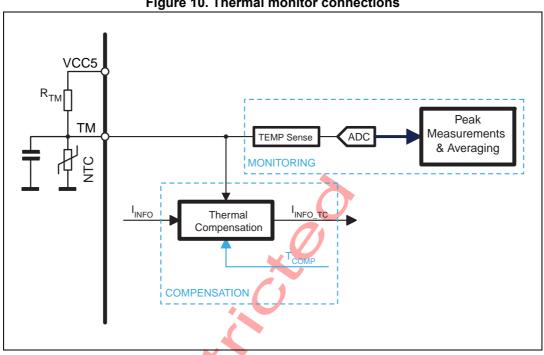

The PM6764/66 devices feature a single NTC for thermal sensing for both thermal monitoring and compensation (see *Figure 10*), allowing to optimize the overall application cost without compromising the performances:

- The thermal monitor consists in monitoring the converter temperature eventually reporting alarm by asserting the VR\_HOT signal. This is the base for the temperature reporting.

- Thermal compensation consists in compensating the inductor DCR derating with temperature so preventing drifts in any variable correlated to the DCR: voltage positioning, overcurrent and current reporting.

**Device description**

#### 5.5.1 Thermal monitor and VR HOT

The diagram for the thermal monitor is reported in Figure 10. The NTC should be placed close to the power stage hotspot in order to sense the regulator temperature. As the temperature of the power stage increases, the NTC resistive value decreases, so reducing the voltage observable at the TM pin.

A recommended NTC is the NTHS0805N02N6801HE for accurate temperature sensing and thermal compensation. A different NTC may be used: to reach the requested accuracy in temperature reporting, a proper resistive network must be used in order to match the resulting characteristic with the one coming from the recommended NTC; furthermore the internal look up table (LUT) can be reprogrammed using custom PMBus™ commands.

The voltage observed at the TM pin is internally converted and then used for the temperature reporting. When the temperature observed on the thermal sensors exceeds TMAX (programmed using the dedicated PMBus™ command), the PM6764/66 devices assert VR HOT (active low as long as the overtemperature event lasts).

#### 5.5.2 Thermal compensation

The PM6764/66 devices support DCR sensing for output voltage positioning: the same current information used for voltage positioning is used to define the overcurrent protection and the current reporting. Having imprecise and temperature dependent information leads to violation of the specification and misleading information: a positive thermal coefficient specific from the DCR needs to be compensated to get stable behavior of the converter as temperature increase. Uncompensated systems show temperature dependencies on the regulated voltage, overcurrent protection and current reporting.

The same temperature information available on the TM pin used for the thermal monitor is also used for this purpose, see Figure 10. The voltage on the TM pin is compensated changing the T<sub>COMP</sub> digital value using the dedicated PMBus™ commands, allowing to

#### Device description

correct the I<sub>INFO</sub> current used for voltage positioning (see <u>Section 5.4</u>) thus recovering the DCR temperature deviation.

### Equation 11

$I_{INFO_{TC}} = I_{INFO} \cdot k_{TC}$

Where  $K_{TC}$  is a function of  $T_{COMP}$ .

Depending on the NTC location and distance from the inductors and the available airflow, the correlation between NTC temperature and DCR temperature may be different.

$T_{COMP}$  adjustment allows to modify the gain between the sensed temperature and the correction made upon the I<sub>INFO</sub> current. Set  $T_{COMP}$  value to 0 to disable the thermal compensation (no correction is given and I<sub>DROOP</sub> TC  $\neq$  I<sub>DROOP</sub>).

### 5.5.3 Thermal compensation design

To thermally compensate the device use this procedure:

- 1. Choose the resistive network to be connected to the TM pin in order to have a voltage equal to 4 V when ambient temperature is equal to 25 °C.

- 2. Power on the converter and load the thermal design current (TDC) with the desired cooling conditions. Record the output voltage regulated as soon as the load is applied.

- Wait for the thermal steady state. Adjust the T<sub>COMP</sub> value in order to get the same output voltage recorded at the point no. 2.

## 5.6 Dynamic VID transition support

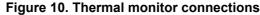

The PM6764/66 manages dynamic VID transitions that allow the output voltage to modify during normal device operation for power management purposes. OV, UV and OC signals are masked during every DVID transition and they are reactivated with proper delay to prevent from false triggering.

When changing dynamically the regulated voltage (DVID), the system needs to charge or discharge the output capacitor accordingly. This means that an extra-current  $I_{DVID}$  needs to be delivered (especially when increasing the output regulated voltage) and it must be considered when setting the overcurrent threshold of both sections. This current results:

### Equation 12