# PE23108

# **Document Category: Product Specification**

# Semi<sup>®</sup> A Murata Company

# High-Efficiency LED Backlight Driver

# **General Description**

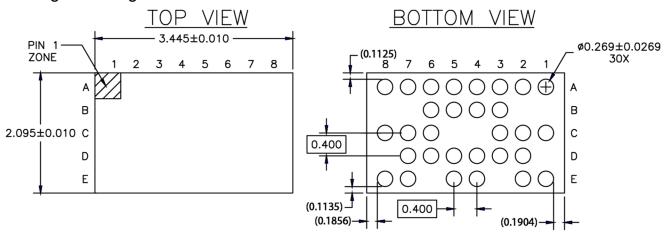

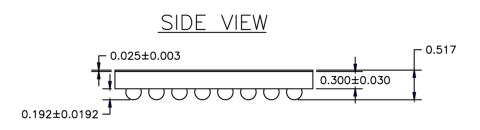

The PE23108 is an ultra-high efficiency DC-DC converter solution with integrated programmable current sinks that drive up to eight strings of LEDs. The PE23108 integrates all MOSFETs and their control and driver circuitry. With its proprietary architecture, the PE23108 provides the highest efficiency—up to 96%—possible in a compact 3.445 mm x 2.095 mm WLCSP 30-pin package. The unique two-stage architecture enables a small and low-profile solution size aligned to the needs of the latest mobile products.

#### **Features**

- Synchronous DC-DC converter with integrated FETs

- 2- and 3-cell Li-ion battery input voltage for LED boost: 4.5V to 15V

- 2.7V to 5.5V IC input voltage

- Proprietary architecture for ultra-high LED efficiency, up to 96%

- Integrated output disconnect switch

- Up to 42V output for maximum flexibility in assignment of LEDs to strings and selection of LED forward voltage

- Up to 12-bit dimming resolution with an additional 3-bit dithering

- Linear/logarithmic analog and PWM dimming for maximum flexibility and resolution

- Phase-shifted PWM dimming among active strings to minimize audible noise

- LED brightness ramp up/down control with programmable ramp rate and linear/ logarithmic ramp profiles

- 1 MHz I<sup>2</sup>C 6.0-compatible serial interface to program the brightness

- Extensive programming capability with nonvolatile memory for storing user register settings

- Eight independently enabled current sinks, up to 33 mA per current sink

- External PWM input for fine dimming resolution

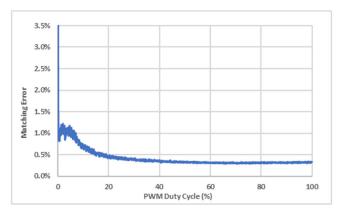

- 0.5% current matching at 20 mA per current sink

- Wide range of input and output voltages with 2x charge pump ratio

- Selectable boost switching frequency from 179 kHz to 1.43 MHz

Extensive fault protection, including boost overcurrent protection, output short circuit protection, output over-voltage protection, LED open and short protection, and thermal shutdown

# **Applications**

Typical applications for 2- and 3-cell platforms include the following:

- 8"-17" FHD/UHD + LCD backlight panels

- Ultrabooks, ultraportables, and notebooks

- 2-in-1, convertible, and detachable notebooks

- Full-size tablet computers

- LCD panels

- Ultra-thin form factor mobile platforms

# Efficiency

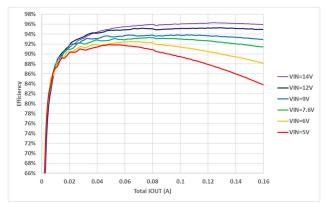

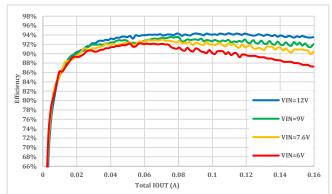

Figure 1. Typical Boost Efficiency – 8p12s, 20 mA, 715 kHz

# Application

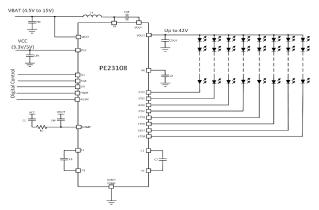

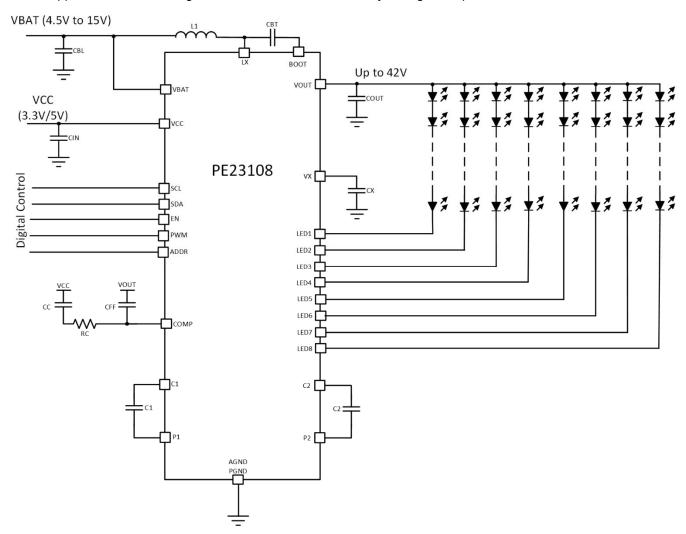

Figure 2. Typical Application Circuit

©2021-2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

# **Table of Contents**

| Features                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Applications                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Efficiency                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Application                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Absolute Maximum Ratings                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Recommended Operating Conditions                                | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Package Thermal Characteristics                                 | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Electrical Specifications                                       | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Pin Configuration                                               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Pin Descriptions                                                | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Operating Voltage Range and Charge Pump Ratio.                  | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Functional Block Diagram                                        | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Application Circuit                                             | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Typical Performance Data                                        | 14<br>14<br>15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Startup Characteristics                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Thermal Performance                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                 | ∠\                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Conditions                                                      | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Conditions  Detailed Description                                | 20<br><b>21</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Conditions  Detailed Description  Input Sequencing Requirements | 20<br><b>21</b><br>21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Conditions                                                      | 20<br>21<br>22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Detailed Description                                            | 20<br>21<br>22<br>22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Conditions                                                      | 20 21 21 22 22 23 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Detailed Description                                            | 20 21 21 22 22 23 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Conditions                                                      | 20212222232323                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Conditions                                                      | 20 21 21 22 23 23 23 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Conditions                                                      | 20 21 22 23 23 23 24 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Conditions  Detailed Description                                | 20 21 21 22 23 23 24 24 24 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Detailed Description                                            | 20 21 22 23 23 24 24 25 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Conditions  Detailed Description                                | 20 21 22 23 23 24 24 25 26 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Conditions  Detailed Description                                | 202121222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222222 |

| Detailed Description                                            | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Detailed Description                                            | 20212020212122222324242424252526272826272828282828282828282828282828282828                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Detailed Description                                            | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Detailed Description                                            | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Detailed Description                                            | 20 22 22 23 24 24 25 27 27 28 28 28 29 30 30 30 30 30 30 30 30 30 30 30 30 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Detailed Description                                            | 20 22 22 23 24 24 25 27 27 28 28 28 36 36 36 36 36 36 36 36 36 36 36 36 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Detailed Description                                            | 20 22 22 24 25 26 27 27 28 30 30 30 30 30 30 30 30 30 30 30 30 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Detailed Description                                            | 20 21 22 22 22 24 24 25 25 27 28 28 29 29 30 30 30 30 30 30 30 30 30 30 30 30 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Detailed Description                                            | 20 21 22 22 23 24 24 25 25 26 27 27 28 28 30 30 30 30 30 31 31 31 31 31 31 31 31 31 31 31 31 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Detailed Description                                            | 20 21 22 22 23 24 24 25 25 26 27 27 28 28 30 30 30 31 31 31 31 31 31 31 31 31 31 31 31 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Detailed Description                                            | 20 21 22 22 23 24 24 25 25 26 27 27 28 28 30 30 30 31 31 31 31 31 31 31 31 31 31 31 31 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Detailed Description                                            | 20 21 22 22 23 24 24 25 25 26 27 27 28 28 30 30 30 31 32 32 32 32 32 32 32 32 32 32 32 32 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Detailed Description                                            | 20 21 22 22 23 24 24 25 25 25 26 26 26 27 27 27 27 28 28 30 30 30 30 31 31 32 32 33 33 33 33 33 33 33 33 33 33 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Programming I <sup>2</sup> C Slave Address - Multiple Parts on One I                  |    |

|---------------------------------------------------------------------------------------|----|

| Ctandard Foot Foot Made Dive Protocol                                                 |    |

| Standard-, Fast-, Fast-Mode Plus Protocol<br>PE23108 I <sup>2</sup> C Update Sequence |    |

| PE23108 MTP Non-volatile Memory Description                                           | 36 |

| · ·                                                                                   |    |

| Register Maps                                                                         | 37 |

| Slave Address: 1001000 (0x48)                                                         | 37 |

| Register Configuration Parameters*                                                    | 37 |

| Detailed Register Description                                                         | 20 |

| Register COMMAND                                                                      | o  |

| Bit Assignment                                                                        |    |

| Bit Description                                                                       | 38 |

| Register CONFIG1                                                                      |    |

| Bit Assignment                                                                        |    |

| Bit Description                                                                       | 39 |

| Register FADING_SPEED                                                                 | 40 |

| Bit Assignment                                                                        |    |

| Bit Description                                                                       |    |

| Register CONFIG2                                                                      |    |

| Bit Assignment                                                                        |    |

| Bit Description                                                                       |    |

| Register LEDEN                                                                        |    |

| Bit Description                                                                       |    |

| Register WLED_ISET_LSB                                                                | 43 |

| Bit Assignment                                                                        | 43 |

| Bit Description                                                                       |    |

| Register WLED_ISET_MSB                                                                | 44 |

| Bit Assignment                                                                        |    |

| Bit Description                                                                       | 44 |

| Register CONFIG3                                                                      |    |

| Bit Assignment                                                                        |    |

| Bit Description                                                                       |    |

| Bit Assignment                                                                        |    |

| Bit Description                                                                       | 46 |

| Register FILTER_SETTINGS                                                              | 47 |

| Bit Assignment                                                                        | 47 |

| Bit Description                                                                       | 47 |

| Register VREG_IMAXTUNE                                                                | 48 |

| Bit Assignment                                                                        | 48 |

| Bit Description                                                                       | 48 |

| Register CONFIG_CP <sup>(2)</sup>                                                     | 49 |

| Bit AssignmentBit Description                                                         |    |

| Register CHKSUM0                                                                      |    |

| Bit Assignment                                                                        |    |

| Bit Description                                                                       |    |

| Register CHKSUM1                                                                      |    |

| Bit Assignment                                                                        | 50 |

| Bit Description                                                                       |    |

| Register STATUS1                                                                      |    |

| Bit Assignment                                                                        |    |

| Bit Description                                                                       |    |

| Register STATUS2                                                                      |    |

| Bit Description                                                                       |    |

| •                                                                                     |    |

| Application Schematic                                                                 | 53 |

| Application Circuit Part List                                                         | 54 |

|                                                                                       |    |

| Component Selection                                                                   | 55 |

| Efficiency Optimization                                                               |    |

| Charge Rump Canagitary (C1 and C2)                                                    | 55 |

©2021–2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

| 60 |

|----|

| 59 |

| 58 |

| 58 |

| 57 |

| 57 |

|    |

| 57 |

| 56 |

| 55 |

| 55 |

| 55 |

|    |

©2021–2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

# **Absolute Maximum Ratings**

Exceeding absolute maximum ratings listed in Table 1 could cause permanent damage. Restrict operation to the limits in Table 2. Operation between operating range maximum and absolute maximum for extended periods could reduce reliability.

#### **ESD Precautions**

When handling this device, observe the same precautions as with any other ESD-sensitive devices. Although this device contains circuitry to protect it from damage due to ESD, do not exceed the rating specified in Table 1.

Table 1. PE23108 Absolute Maximum Ratings

| Parameter                                       | Min   | Max <sup>(1)</sup> | Unit |

|-------------------------------------------------|-------|--------------------|------|

| VBAT to AGND                                    | -0.3  | 18                 | V    |

| VCC, PWM, COMP, EN, SCL, SDA, ADDR to AGND      | -0.3  | 6                  | V    |

| VOUT, C1, C2 to AGND                            | -0.3  | 45                 | V    |

| LEDx to AGND                                    | -0.3  | 40                 | V    |

| AGND to PGND                                    | -0.3  | 0.3                | V    |

| LX, VX, P1, P2, to PGND                         | -0.3  | 22                 | V    |

| VX to LX, P1, P2                                | -0.3  | 22                 | V    |

| BOOT to VBAT                                    | -18.3 | 28                 | V    |

| BOOT to LX                                      | -0.3  | 6                  | V    |

| C1, C2 to VX                                    | -0.3  | 22                 | V    |

| Storage temperature                             | -65   | 150                | °C   |

| Junction temperature (J⊺)                       | _     | 150                | °C   |

| Bump or lead temperature (soldering and reflow) | _     | 260                | °C   |

| ESD tolerance, HBM <sup>(2)</sup>               | _     | 1000               | V    |

| ESD tolerance, CDM <sup>(3)</sup>               | _     | 1000               | V    |

#### Notes:

Page 3 of 61 www.psemi.com DOC-96573-5 – (06/2025)

These "Absolute Maximum Ratings" are stress ratings only; the notation of these conditions does not imply functional operation of

the device at these or any other conditions that fall outside the range identified by the operational sections of this specification.

<sup>2.</sup> Human body model, per JEDEC standard JS-001-2017.

<sup>3.</sup> Field-induced charge device model, per JEDEC standard JESD22-C101.

# **Recommended Operating Conditions**

Table 2 lists the PE23108 recommend operating conditions. Do not operate the device outside the operating conditions listed below.

Table 2. PE23108 Recommended Operating Conditions

| Parameter                                               | Min      | Max  | Unit |

|---------------------------------------------------------|----------|------|------|

| VBAT Input Voltage Range, relative to AGND or PGND(*)   | 4.5      | 15   | V    |

| VCC Voltage Range, relative to AGND                     | 2.7      | 5.5  | V    |

| VOUT Output Voltage Range, relative to AGND PGND(*)     | 18       | 42   | V    |

| VX Boost Output Voltage Range, relative to AGND or PGND | 1.2*VBAT | 21   | V    |

| Junction temperature range (J <sub>T</sub> )            | -40      | +125 | °C   |

Note: \* VBAT and VOUT ranges must meet the valid operating regions in continuous conduction mode (CCM):  $(VBAT \le \frac{VOUT}{2.15})$

# Package Thermal Characteristics

Table 3 lists the package thermal characteristics.

Table 3. Package Thermal Characteristics (1)(2)

| Parameter                                                                                           | Max | Unit |

|-----------------------------------------------------------------------------------------------------|-----|------|

| Junction-to-ambient thermal resistance (O <sub>JA</sub> ), soldered thermal pad, connected to plane | 46  | °C/W |

| Junction-to-board thermal characterization ( $\Psi_{JB}$ )                                          | 11  | °C/W |

| Junction-to-top case thermal characterization (Ψ <sub>JC</sub> )                                    | 8   | °C/W |

#### Notes:

- 1. Package thermal characteristics and performance are measured and reported in a manner consistent with JEDEC standards JESD51-8 and JESD51-12.

- 2. Junction-to-ambient thermal resistance (O<sub>JA</sub>) is a function not only of the IC, but it is also extremely sensitive to the environment which includes, but is not limited to, board thickness, planes, copper weight/routes, and air flow. To realize the expected thermal performance, pay close attention to the board layout.

©2021-2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

Page 4 of 61 www.psemi.com DOC-96573-5 – (06/2025)

# **Electrical Specifications**

Table 4 lists the PE23108 key electrical specifications at the following conditions, unless otherwise noted. Typical values are at  $T_A = T_J = 25$  °C with 8p12s.

VBAT = 12V, VCC = 3.3V, VAGND = VPGND = 0V, VEN = 1.8V,  $T_A = T_J = -40$  °C to +85 °C

Table 4. PE23108 Electrical Specifications

| Parameter                                              | Symbol                | C                             | ond                                                          | itions            | Min | Тур | Max | Units |

|--------------------------------------------------------|-----------------------|-------------------------------|--------------------------------------------------------------|-------------------|-----|-----|-----|-------|

| Input supply                                           |                       |                               |                                                              |                   | •   |     | •   |       |

| IC input voltage range                                 | Vvcc                  | _                             |                                                              |                   | 2.7 | -   | 5.5 | V     |

| Input voltage range                                    | V <sub>VBAT</sub>     | _                             |                                                              |                   | 4.5 |     | 15  | V     |

| VCC under-voltage<br>lockout (UVLO) threshold<br>high  | Vvcc-<br>uvlo_h       | V <sub>VCC</sub> rising       |                                                              |                   | _   | ı   | 2.6 | ٧     |

| VBAT under-voltage<br>lockout (UVLO) threshold<br>high | Vvbat_uvlo<br>_H      | V <sub>VBAT</sub> rising      |                                                              |                   | _   | -   | 4.4 | ٧     |

| Under-voltage lockout                                  |                       | VBAT                          |                                                              |                   | _   | 65  | _   | >/    |

| (UVLO) hysteresis                                      | Vuvlo_HYST            | VCC                           |                                                              |                   | _   | 50  | _   | mV    |

| VCC shutdown supply current                            | lvcc_sd               | IVCC with VEN =               | = 0V                                                         |                   | -   | -   | 1   | μA    |

| VBAT shutdown supply current                           | IVBAT_SD              | IVBAT with VEN                | IVBAT with VEN = 0V                                          |                   |     | _   | 1   | μΑ    |

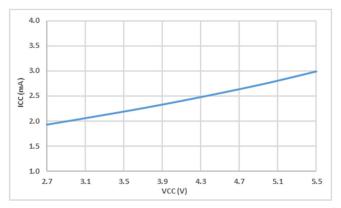

| VCC quiescent current                                  | lvcc                  |                               | EN = 1.8V, ILED = 100 μA,<br>f <sub>SW_BOOST</sub> = 715 kHz |                   |     | 2   | _   | mA    |

| Thermal shutdown threshold <sup>(3)</sup>              | T <sub>TSD</sub>      | _                             | -                                                            |                   |     | 150 | _   | °C    |

| Thermal shutdown hysteresis <sup>(3)</sup>             | T <sub>TSD_HYST</sub> | _                             | -                                                            |                   |     | 20  | _   | ů     |

| Soft start timeout duration                            | _                     | _                             |                                                              |                   | _   | 10  | _   | ms    |

| Step-up converter                                      |                       |                               |                                                              |                   |     |     |     |       |

| Output voltage range <sup>(4)</sup>                    | V <sub>OUT</sub>      | _                             |                                                              |                   | 18  | -   | 42  | V     |

| Maximum output power                                   | _                     | _                             |                                                              |                   | 6   | _   | _   | Watts |

| Boost switching                                        | f <sub>SW_BOOST</sub> | FSW_BOOST [3                  | 3:01                                                         | 0100              | _   | 715 | _   | kHz   |

| frequency range                                        | 13W_B0031             | 1011_20001 [0                 |                                                              | 1010              | _   | 286 | _   |       |

| Boost switching frequency accuracy                     | -                     | f <sub>SW_BOOST</sub> = 715 I | f <sub>SW_BOOST</sub> = 715 kHz                              |                   | -4  | _   | +4  | %     |

| Boost minimum off-time                                 | Toff_boost<br>_min    | -                             |                                                              | _                 | 170 | _   | ns  |       |

| Boost minimum on-time                                  | Ton_boost_<br>MIN     | _                             | -                                                            |                   | _   | 60  | _   | ns    |

|                                                        |                       |                               | ВО                                                           | OST_ILIM [1:0]=00 | _   | 2.0 | _   |       |

| Boost low-side switch current limit, cycle-by-         | IBOOST LIMIT          | I <sub>LX</sub> rising        | ВО                                                           | OST_ILIM [1:0]=01 | _   | 1.0 | _   | Α     |

| cycle                                                  | I IDUUS I_LIMIII      | ILA HOMY                      |                                                              | OST_ILIM [1:0]=10 | _   | 2.5 | _   |       |

|                                                        |                       |                               | ВО                                                           | OST_ILIM[ 1:0]=11 | _   | 3.0 | _   |       |

©2021–2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

Page 5 of 61 www.psemi.com DOC-96573-5 - (06/2025)

# PE23108 LED Backlight Driver

| Output over-current threshold                               | Іоит_ос                | lout rising                            |                                                            | 250  | _               | _     | mA  |

|-------------------------------------------------------------|------------------------|----------------------------------------|------------------------------------------------------------|------|-----------------|-------|-----|

|                                                             |                        |                                        | 0010                                                       | _    | 43.75           | _     |     |

| Output over-voltage                                         |                        |                                        | 0011                                                       | _    | 41.875          | _     |     |

| threshold                                                   | V <sub>OUT_OVP</sub>   | Ovp_th[3:0]                            |                                                            | _    |                 | _     | V   |

|                                                             |                        |                                        | 1111                                                       | _    | 19.375          | _     |     |

| Output over-voltage hysteresis                              | V <sub>OUT_OVP</sub> _ | _                                      |                                                            | _    | 0.35            | -     | V   |

| Accuracy of output over-<br>voltage protection<br>threshold | _                      | _                                      |                                                            | -5   | -               | 5     | %   |

| LED current sinks (LED1                                     | to LED8)               |                                        |                                                            |      |                 |       |     |

|                                                             |                        |                                        | MAX_I [4:0]=00000                                          | _    | 2               | _     |     |

| LED current full-scale                                      |                        | I <sup>2</sup> C register setting      | MAX_I [4:0]=00001                                          | _    | 3               | _     | ^   |

| output range                                                | ILED_MAX               | MAX_I[4:0]                             |                                                            | _    |                 | _     | mA  |

|                                                             |                        |                                        | MAX_I [4:0]=11111                                          | _    | 33              | _     |     |

| Minimum sink current<br>LED1–8                              | I <sub>LEDx_MIN</sub>  | IMAX programmed to mapping             | 20 mA, linear                                              | _    | 4.88            | _     | μA  |

| Leakage current                                             | ILED_LEAKAG<br>E       | LED1LED8 = 0, VC                       | OUT = 36V                                                  | _    | _               | 1     | μA  |

| LED current matching <sup>(5)</sup>                         | ILED_MATCHI<br>NG      | IMAX programmed to ILEDX programmed to |                                                            | -1   | _               | 1     | %   |

| LED current matching <sup>(5)</sup>                         | ILED_MATCHI<br>NG      |                                        | IMAX programmed to 20 mA ILEDX programmed to 2% brightness |      |                 | 2.6   | %   |

| LED current accuracy <sup>(6)</sup>                         | ILED_ACCUR<br>ACY      | IMAX programmed to ILEDX programmed to |                                                            | -2   | С               | 2     | %   |

| LED regulation voltage                                      | VLED_REGUL<br>ATION    | ILEDX programmed t                     | to 20 mA                                                   | _    | 320             | _     | mV  |

|                                                             |                        |                                        | LED_SHORT_VTH<br>[1:0] = 00                                | _    | 4.35            | _     |     |

| LED shorted string                                          |                        | V/I EDV falling                        | LED_SHORT_VTH<br>[1:0] = 01                                | -    | 4.85            | _     | V   |

| detection threshold                                         | _                      | VLEDX falling                          | LED_SHORT_VTH<br>[1:0] = 10                                | _    | 5.25            | -     | V   |

|                                                             |                        |                                        | LED_SHORT_VTH<br>[1:0] = 11                                | ı    | 5.75            | ı     |     |

| Current Ripple                                              | _                      | ILED programmed to DC LED current outp |                                                            | _    | 1               | _     | %   |

| Internal PWM dimming                                        | •                      | •                                      |                                                            |      |                 |       |     |

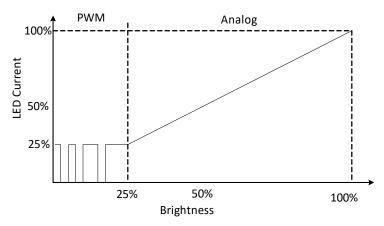

|                                                             |                        | DIM_MODE=0                             |                                                            | _    | 0               | _     |     |

|                                                             |                        |                                        | PWM_IX[1:0] = 00                                           | -    | 12.5            | _     |     |

| Transition point between internal PWM and analog            | _                      | DIM MODE=1                             | PWM_IX[1:0] = 01                                           | _    | 25<br>(default) | _     | %   |

| dimming                                                     |                        | <u>.</u>                               | PWM_IX[1:0] = 10                                           | _    | 50              | _     |     |

|                                                             |                        |                                        | PWM_IX[1:0] = 00                                           | _    | 100             | _     |     |

| LED PWM output frequency                                    | f <sub>LEDX</sub>      | PWM_DIM_FREQ[2:                        | 0]                                                         | 2.79 | _               | 22.49 | kHz |

©2021–2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

Page 6 of 61 www.psemi.com DOC-96573-5 – (06/2025)

# PE23108 LED Backlight Driver

| LED current sink minimum output pulse width   | -                     | _                                                                                   | -            | 350 | _    | ns  |

|-----------------------------------------------|-----------------------|-------------------------------------------------------------------------------------|--------------|-----|------|-----|

| Logic interface                               |                       |                                                                                     |              |     |      |     |

| EN logic input high voltage                   | V <sub>IH_EN</sub>    | -                                                                                   | 1.2          | -   | _    | V   |

| EN logic input low voltage                    | VIL_EN                | -                                                                                   | _            | _   | 0.4  | V   |

| PWM logic input high voltage                  | V <sub>IH_PWM</sub>   | -                                                                                   | 0.9          | _   | _    | ٧   |

| PWM logic input low voltage                   | VIL_PWM               | -                                                                                   | _            | _   | 0.5  | V   |

| Logic input current                           | I <sub>PWM, IEN</sub> | _                                                                                   | -1.0         | _   | 1.0  | μA  |

| ADDR input resistance                         | I_ADDR_R              | _                                                                                   | _            | 100 | _    | kΩ  |

| ADDR input high voltage                       | V <sub>IH_ADDR</sub>  | -                                                                                   | VCC-<br>0.4V | _   | _    | ٧   |

| ADDR input low voltage                        | VIL_ADDR              | -                                                                                   | _            | _   | 0.4  | V   |

| PWM pin input frequency for internal PWM mode | FIPWM                 | -                                                                                   | 0.1          | _   | 40   | kHz |

| PWM pin minimum input high pulse              | _                     | -                                                                                   | _            | 350 | _    | ns  |

| PWM pin minimum input low pulse               | -                     | -                                                                                   | _            | 350 | _    | ns  |

| PC serial interface (SCL a                    | and SDA)              |                                                                                     | •            |     |      |     |

| SDA, SCL input high voltage                   | V <sub>IH</sub>       | _                                                                                   | 1.26         | -   | 3.6  | V   |

| SDA, SCL input low voltage                    | VıL                   | -                                                                                   | _            | _   | 0.99 | ٧   |

| SDA, SCL input<br>hysteresis                  | V <sub>HYS</sub>      | -                                                                                   | _            | 0.1 | _    | ٧   |

| SDA, SCL input current                        | ISCL, ISDA            | -                                                                                   | _            | _   | 1    | μΑ  |

| SDA output low level                          | V <sub>OL</sub>       | I <sub>SDA</sub> = 20 mA                                                            | _            | ı   | 0.4  | ٧   |

| I <sup>2</sup> C interface initial wait time  |                       | Initial wait time from EN logic high to the first accepted I <sup>2</sup> C command | 1            | -   | _    | ms  |

| SDA, SCL pin capacitance                      | C <sub>I/O</sub>      | _                                                                                   | _            | -   | 10   | pF  |

| I <sup>2</sup> C interface timing chara       | cteristics fo         | r standard, fast mode, and fast mode plus                                           |              |     |      | -   |

|                                               |                       | Standard mode                                                                       | _            | _   | 100  |     |

| Serial clock frequency                        | FscL                  | Fast mode                                                                           | _            | _   | 400  | kHz |

|                                               |                       | Fast mode plus                                                                      | _            | _   | 1000 |     |

|                                               |                       | Standard mode                                                                       | 4.7          | -   | _    |     |

| Clock low period                              | t <sub>LOW</sub>      | Fast mode                                                                           | 1.3          | _   | _    | μs  |

|                                               |                       | Fast mode plus                                                                      | 0.5          | 1   | _    |     |

|                                               |                       | Standard mode                                                                       | 4            | _   | _    |     |

| Clock high period                             | 1                     |                                                                                     | 1            |     | 1    | l   |

| <b>.</b>                                      | tніgн                 | Fast mode                                                                           | 0.6          | 1   | _    | μs  |

©2021–2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

Page 7 of 61 www.psemi.com DOC-96573-5 – (06/2025)

# PE23108 LED Backlight Driver

| BUS free time between a                   |                     | Standard mode  | 4.7  | _ | _    |    |

|-------------------------------------------|---------------------|----------------|------|---|------|----|

| STOP and a START                          | t <sub>BUF</sub>    | Fast mode      | 1.3  | _ | -    | μs |

| condition                                 |                     | Fast mode plus | 0.5  | _ | _    |    |

|                                           |                     | Standard mode  | 4.7  | _ | -    |    |

| Setup time for a repeated START condition | t <sub>SU:STA</sub> | Fast mode      | 0.6  | _ | -    | μs |

| OTATA CONCINE                             |                     | Fast mode plus | 0.26 | _ | _    |    |

|                                           |                     | Standard mode  | 4    | _ | _    |    |

| Hold time for a repeated START condition  | thd:sta             | Fast mode      | 0.6  | _ | -    | μs |

| OTATO CONCINCION                          |                     | Fast mode plus | 0.26 | _ | _    |    |

|                                           |                     | Standard mode  | 4    | _ | _    |    |

| Setup time of STOP condition              | tsu:sto             | Fast mode      | 0.6  | _ | _    | μs |

| Condition                                 |                     | Fast mode plus | 0.26 | _ | _    |    |

|                                           |                     | Standard mode  | 0.25 | _ | _    |    |

| Data setup time                           | tsu:dat             | Fast mode      | 0.1  | _ | _    | μs |

|                                           |                     | Fast mode plus | 0.05 | _ | _    |    |

|                                           |                     | Standard mode  | 0    | _ | _    |    |

| Data hold time                            | thd_dat             | Fast mode      | 0    | _ | _    | μs |

|                                           |                     | Fast mode plus | 0    | _ | _    |    |

|                                           |                     | Standard mode  | _    | _ | 1    |    |

| Rise time of SCL signal                   | t <sub>RCL</sub>    | Fast mode      | 0.02 | _ | 0.3  | μs |

|                                           |                     | Fast mode plus | _    | _ | 0.12 |    |

|                                           |                     | Standard mode  | _    | _ | 0.3  |    |

| Fall time of SCL signal                   | t <sub>FCL</sub>    | Fast mode      | _    | _ | 0.3  | μs |

|                                           |                     | Fast mode plus | _    | _ | 0.12 |    |

|                                           |                     | Standard mode  | _    | _ | 1    |    |

| Rise time of SDA signal                   | t <sub>RDA</sub>    | Fast mode      | 0.02 | _ | 0.3  | μs |

|                                           |                     | Fast mode plus | _    | _ | 0.12 |    |

|                                           |                     | Standard mode  | _    | _ | 0.3  |    |

| Fall time of SDA signal2                  | t <sub>FDA</sub>    | Fast mode      | 0.02 | _ | 0.3  | μs |

|                                           |                     | Fast mode plus | 0.02 | _ | 0.12 |    |

|                                           |                     | Standard mode  | _    | _ | 3.45 |    |

| Data valid time                           | t <sub>VD</sub>     | Fast mode      | _    | _ | 0.9  | μs |

|                                           |                     | Fast mode plus | _    | _ | 0.45 |    |

|                                           |                     | Standard mode  | _    | _ | 3.45 |    |

| Data valid acknowledge time               | t <sub>VDA</sub>    | Fast mode      | _    | _ | 0.9  | μs |

| ume                                       |                     | Fast mode plus | _    | _ | 0.45 |    |

|                                           |                     | Standard mode  | _    | _ | 400  |    |

| Capacitive load for SDA and SCL           | C <sub>BUS</sub>    | Fast mode      | _    | - | 400  | pf |

| and JOL                                   |                     | Fast mode plus | _    | _ | 550  |    |

| MTP non-volatile memory write cycle time  | _                   | -              | _    | _ | 50   | ms |

|                                           |                     | -              |      |   | •    |    |

#### Notes:

- 1. Min/max specifications are 100% production tested at T<sub>A</sub>=T<sub>J</sub> = 25 °C, unless otherwise noted. Limits over the operating range are guaranteed by design.

- 2. Guaranteed by design.

©2021–2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

Page 8 of 61 www.psemi.com DOC-96573-5 - (06/2025)

- 3. Thermal shutdown is not production tested.

- 4. VBAT and VOUT ranges must meet valid operating regions when in CCM operation: ( $VBAT \leq \frac{VOUT}{2.15}$ )

- 5. The sink current matching is defined and tested as  $(I_{LED\_MAX} I_{LED\_MIN})/I_{LED\_AVG}$ .

- 6. The LED current accuracy is defined and tested as: 100\*(I<sub>LED\_AVG</sub> I<sub>LED\_Target</sub>)/I<sub>LED\_AVG</sub>.

©2021–2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

Page 9 of 61 www.psemi.com DOC-96573-5 - (06/2025)

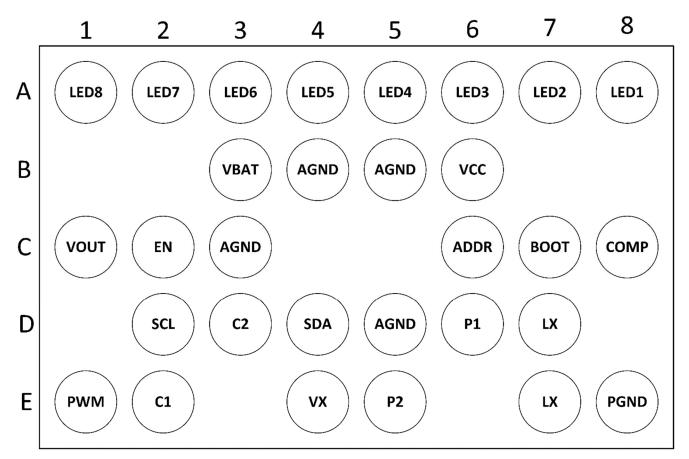

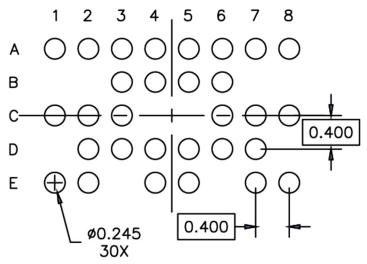

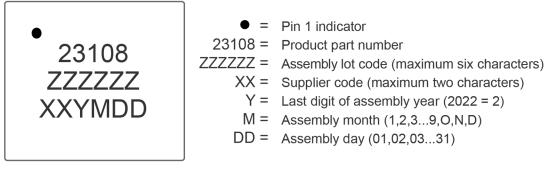

# **Pin Configuration**

This section includes the PE23108 30-pin configuration information. Figure 3 shows the pin map of this device for the 3.445 mm x 2.095 mm WLCSP package. Table 5 lists the descriptions for each pin.

Figure 3. Pin Configuration (Top View)

©2021-2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

Page 10 of 61 www.psemi.com DOC-96573-5 - (06/2025)

# Pin Descriptions

Table 5 lists the PE23108 pin descriptions. For the capacitor and inductor selection guidelines, see Component Selection on page 55.

Table 5. PE23108 Pin Descriptions

| Pin No.           | Pin Name | Description                                                                                                                                |

|-------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| A1                | LED8     | Individual LED current sink. Connect to the low side of individual LED strings.                                                            |

| A2                | LED7     | Individual LED current sink. Connect to the low side of individual LED strings.                                                            |

| A3                | LED6     | Individual LED current sink. Connect to the low side of individual LED strings.                                                            |

| A4                | LED5     | Individual LED current sink. Connect to the low side of individual LED strings.                                                            |

| A5                | LED4     | Individual LED current sink. Connect to the low side of individual LED strings.                                                            |

| A6                | LED3     | Individual LED current sink. Connect to the low side of individual LED strings.                                                            |

| A7                | LED2     | Individual LED current sink. Connect to the low side of individual LED strings.                                                            |

| A8                | LED1     | Individual LED current sink. Connect to the low side of individual LED strings.                                                            |

| B3                | VBAT     | LED boost input voltage, battery power supply pin.                                                                                         |

| B4, B5, C3,<br>D5 | AGND     | Analog and LED current sink ground, star ground to system ground plane.                                                                    |

| B6                | VCC      | IC input voltage. Connect to a 3.3V or 5V supply.                                                                                          |

| C1                | VOUT     | Power converter output voltage. Connect to the high side of all LED strings. Connect externally to four 2.2 µF 0603 capacitors.            |

| C2                | EN       | Enable input                                                                                                                               |

| C6                | ADDR     | Sets lower three bits of the I <sup>2</sup> C slave address. Tie to AGND pin for '000'. Leave floating for 010. Tie to VCC pin for 101.    |

| C7                | воот     | Bootstrap capacitor for the boost stage high side FET. Connect a 2.2 nF, 10V or higher capacitor from BOOT to LX.                          |

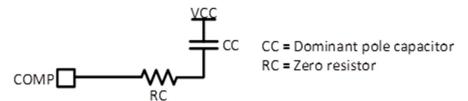

| C8                | COMP     | External compensation pin. For details, see Switching Converter Compensation on page 27.                                                   |

| D2                | SCL      | Serial clock for I <sup>2</sup> C bus.                                                                                                     |

| D3                | C2       | Charge pump fly capacitor positive node. Connect two 4.7 µF 0603 capacitors from C2 to P2.                                                 |

| D4                | SDA      | Serial data for I <sup>2</sup> C bus.                                                                                                      |

| D6                | P1       | Charge pump fly capacitor phase node. Connect two 4.7 $\mu$ F 0603 capacitors from P1 to C1.                                               |

| D7,E7             | LX       | Fully synchronous switching node for the boost power inductor, which connects between LX and input voltage VBAT.                           |

| E1                | PWM      | PWM dimming input for brightness control. If not used, connect to the VCC pin.                                                             |

| E2                | C1       | Charge pump fly capacitor positive node. Connect two 4.7 µF 0603 capacitors from C1 to P1.                                                 |

| E4                | VX       | Charge pump input node, internally driven by the output of the boost converter. Connect a 2.2 µF 0402 capacitor between this pin and PGND. |

| E5                | P2       | Charge pump fly capacitor phase node. Connect two 4.7 $\mu\text{F}$ 0603 capacitors from P2 to C2.                                         |

| E8                | PGND     | Power ground must tie externally to system ground plane. High current path.                                                                |

|                   | 1        |                                                                                                                                            |

©2021–2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

Page 11 of 61 www.psemi.com DOC-96573-5 - (06/2025)

# Operating Voltage Range and Charge Pump Ratio

The PE23108 uses a 2X charge-pump to improve efficiency. The charge pump architecture requires the battery input voltage to be less than the output voltage divided by 2.15 when boost DC-DC is operating in continuous conduction mode (CCM) condition:

$$VBAT \le \frac{VOUT}{2.15}$$

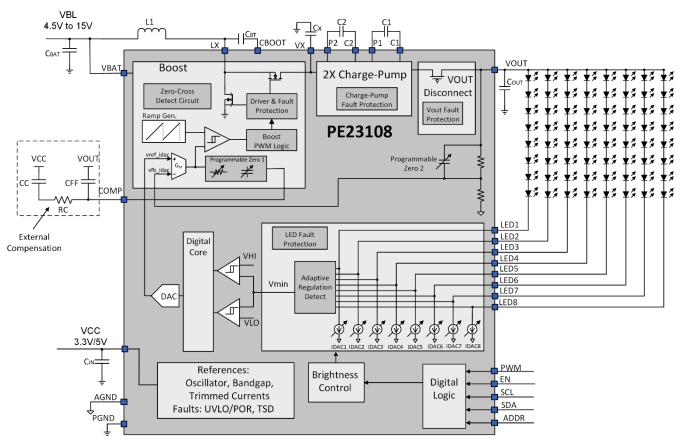

# **Functional Block Diagram**

Figure 4 shows the PE23108 functional block diagram.

Figure 4. PE23108 Functional Block Diagram

©2021–2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

Page 12 of 61 www.psemi.com DOC-96573-5 – (06/2025)

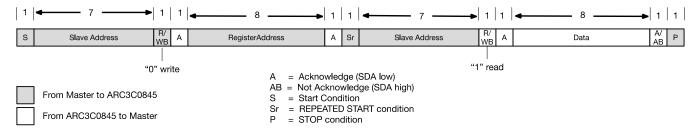

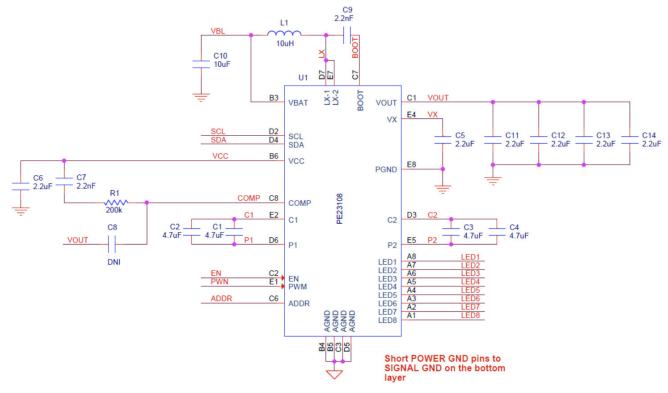

# **Application Circuit**

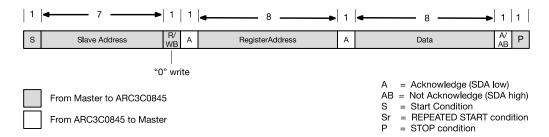

For the application circuit, star ground PGND and AGND on a system ground plane.

Figure 5. I<sup>2</sup>C Interface Application Schematic

©2021–2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

Page 13 of 61 www.psemi.com DOC-96573-5 - (06/2025)

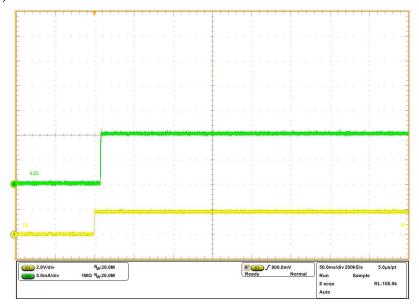

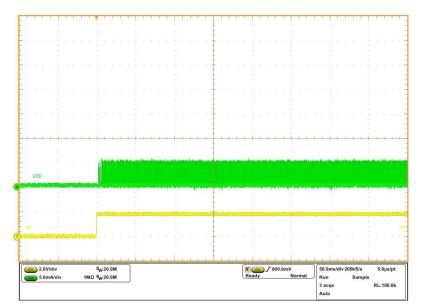

# **Typical Performance Data**

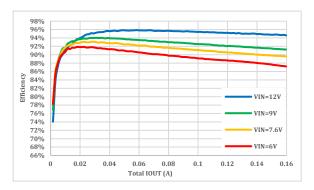

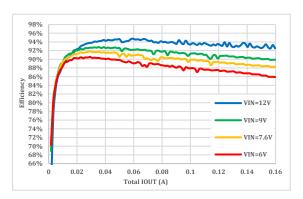

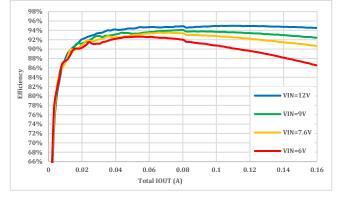

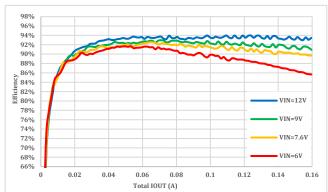

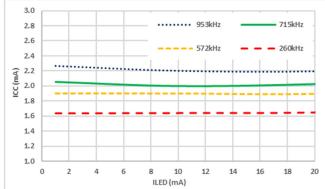

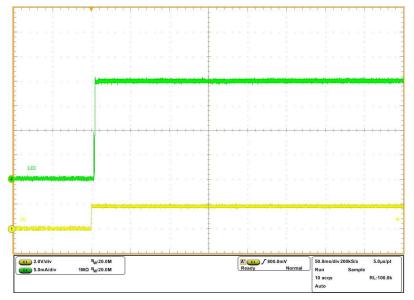

Figure 6–Figure 11 show the PE23108 typical performance data at VCC = 3.3V, VBAT = 12V, L1=10  $\mu$ H, C<sub>OUT</sub> = 4 x 2. $\mu$ F, I<sub>MAX</sub> = 20 mA, LED VF = 2.8V at 20 mA (typical), and analog dimming, unless otherwise specified.

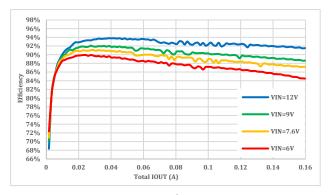

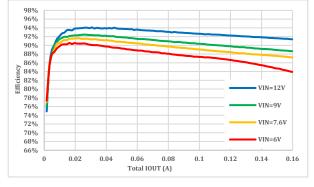

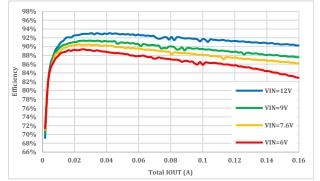

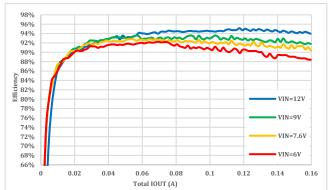

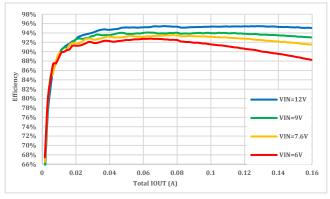

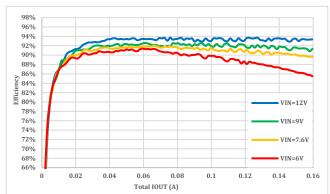

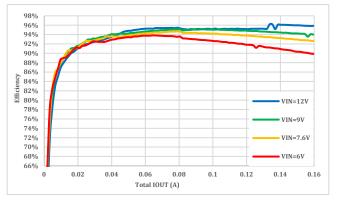

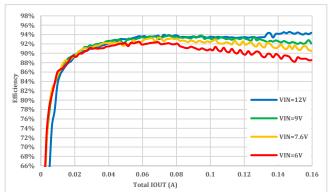

## Efficiency: 286 kHz boost switching frequency

Figure 6. 8P10S Boost Efficiency<sup>1</sup>, 10 μH Inductor

Figure 7. 8P10S System Efficiency<sup>2</sup>, 10 µH Inductor

Figure 8. 8P12S Boost Efficiency<sup>1</sup>, 10 μH Inductor

Figure 9. 8P12S System Efficiency<sup>2</sup>, 10 μH Inductor

Figure 10. 8P14S Boost Efficiency<sup>1</sup>, 10 μH Inductor

Figure 11. 8P14S System Efficiency<sup>2</sup>, 10 µH Inductor

#### Notes:

- 1. Boost Efficiency = POUT/PVBAT

- System Efficiency = (VOUT-VREG) \* IOUT / (PVBAT+PVCC), where VREG = LED regulation voltage.

©2021-2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

Page 14 of 61 www.psemi.com DOC-96573-5 – (06/2025)

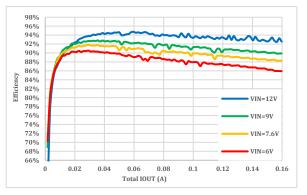

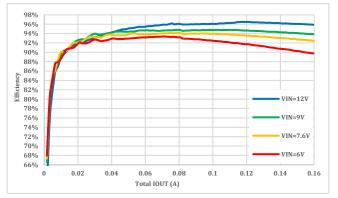

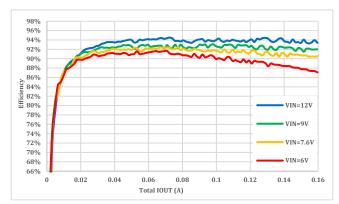

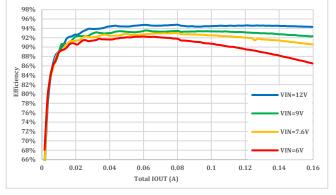

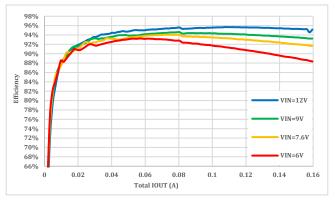

Figure 12–Figure 17 show the PE23108 typical performance data at VCC = 3.3V, VBAT = 12V, L1=10  $\mu$ H, C<sub>OUT</sub> = 4 x 2. $\mu$ F, I<sub>MAX</sub> = 20 mA, LED VF = 2.8V at 20 mA (typical), and analog dimming, unless otherwise specified.

## Efficiency: 715 kHz boost switching frequency

Figure 12. 8P10S Boost Efficiency<sup>1</sup>, 10 μH Inductor

Figure 13. 8P10S System Efficiency<sup>2</sup>, 10 μH Inductor

Figure 14. 8P12S Boost Efficiency<sup>1</sup>, 10 μH Inductor

Figure 15. 8P12S System Efficiency<sup>2</sup>, 10 μH Inductor

Figure 16. 8P14S Boost Efficiency<sup>1</sup>, 10 µH Inductor

Figure 17. 8P14S System Efficiency<sup>2</sup>, 10 μH Inductor

#### Notes:

- 1. Boost Efficiency = POUT/PVBAT

- 2. System Efficiency = (VOUT-VREG) \* IOUT / (PVBAT+PVCC), where VREG = LED regulation voltage.

©2021-2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

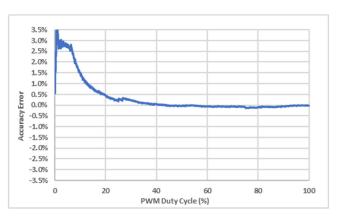

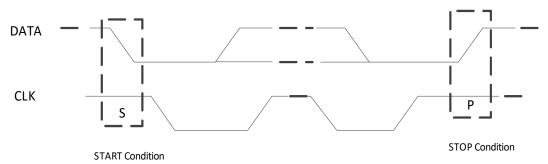

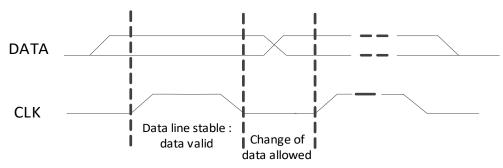

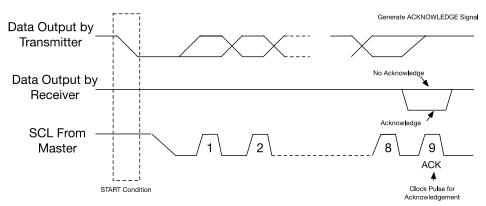

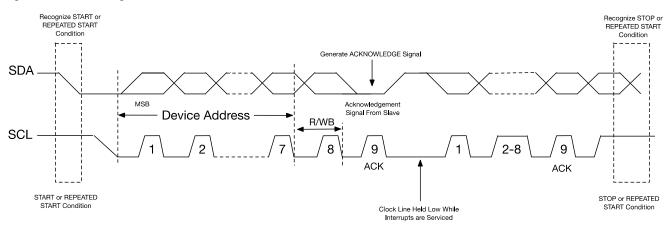

Page 15 of 61 www.psemi.com DOC-96573-5 – (06/2025)