# PDSP16330/A/B Pythagoras Processor

DS3884 ISSUE 2.1 November 1998

The PDSP16330 is a high speed digital CMOS IC that converts Cartesian data (Real and Imaginary) into Polar form (Magnitude and Phase), at rates up to 20MHz. Cartesian 16+16 bit 2's complement or Sign-Magnitude data is converted into 16 bit Phase format. The Magnitude output may be scaled in amplitude by powers of 2. The Phase output represents a full 2 x  $\pi$  field to eliminate phase ambiguities.

Polyimide is used as an inter-layer dielectric and as glassivation.

The PDSP16330 is offered in three speed grades: a basic 10MHz part (PDSP16330), a 20MHz version (PDSP16330A) and a 25MHz version (PDSP16330). A MILSTD-883 version is also detailed in a separate datasheet.

#### **FEATURES**

- 25MHz Cartesian to Polar Conversion

- 16-Bit Cartesian Inputs

- 16-Bit Magnitude Output

- 12-Bit Phase Output

- 2's Complement or Sign-Magnitude Input Formats

- Three-state Outputs and Independent

Data Enables Simplify System Interfacing

- Magnitude Scaling Facility with Overflow Flag

- Less than 400 mW Power Dissipation at 10MHz

- 84-pin PGA or 100 pin QFP Package or 84 LCC

#### **APPLICATIONS**

- Digital Signal Processing

- Digital Radio

- Radar Processing

- Sonar Processing

- Robotics

#### **ORDERING INFORMATION**

#### Commercial (0°C to +70°C)

PDSP16330A CO AC (20MHZ - PGA Package) PDSP16330B CO AC (25MHZ - PGA Package)

Industrial (-40°C to +85°C)

PDSP16330A BO AC 20MHZ - PGA Package PDSP16330A/IG/GC1R 20MHZ - GC Package PDSP16330B BO AC 25MHZ - PGA Package

Military (-55°C to +125°C)

PDSP16330A AO AC 20MHZ - PGA Package PDSP16330/MC/GC1R 10MHz - GC Package Mil 883C Screened

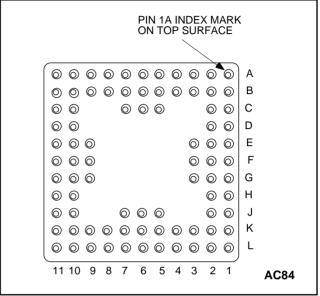

Fig.1 Pin connections - bottom view (PGA)

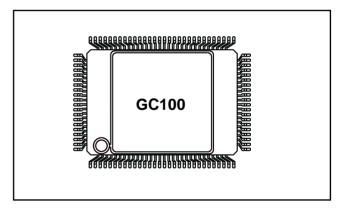

Fig.2 Pin connections - QFP Package

#### **ASSOCIATED PPODUCTS**

PDSP16112 16 X 12 Complex Multiplier

PDSP16116 16 X 16 Complex Multiplier

PDSP16318 Complex Accumulator

PDSP16350 I/Q Splitter and NCO

PDSP16510A Stand Alone FFT Processor

# PDSP16330/A/B

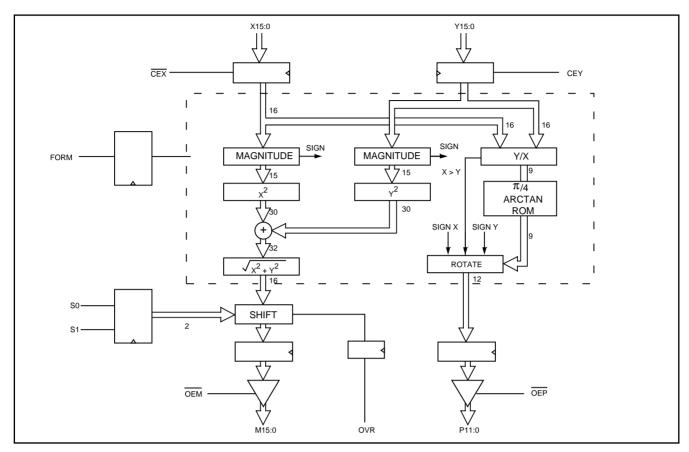

Fig.2 Block diagram

# **FUNCTIONAL DESCRIPTION**

The PDSP16330 converts incoming Cartesian Data into the equivalent Polar Values. The device accepts new 16 + 16 bit complex data every cycle, and delivers a 16 bit + 12 bit Polar equivalent after 24 clock cycles. The input data can be in 2s' Complement or Sign Magnitude format selected via the FORM input. The output is in a magnitude format for both the Magnitude output and the Phase. Phase data is zero for data with a zero Y input and positive X, and is 400 hex for zero X data and positive Y, is 800 hex for zero Y data and negative X, and is C00 hex for zero X and negative Y. The LSB weighting (bit 0) is 2 x  $\pi$ /4096 radians. The 16 bit Magnitude result may be scaled by shifting one, two, or three places in the more significant direction, effectively multiplying the Magnitude result by 2,4 or 8 respectively. Any of these shifts can under certain conditions cause an invalid result to be output from the device. Under these circumstances the OVR output will become active. The PDSP16330 has independent clock enables and three state output controls for all ports.

#### **FORM**

This input selects the format of the X and Y input data. A low level on FORM indicates that the Input data is twos' complement format (Note: input data 8000 hex is not valid in 2s' complement mode). This input refers to the format of the current Input data and may be changed on a per cycle basis if desired. The level of FORM is latched at the same time as the data to which it refers.

#### **S1-0**

These inputs select the scaling factor to be applied to the Magnitude output. They are latched by the rising edge of CLK and determine the scaling of the output in the cycle after they are loaded into the device. The scale factor applied is determined by the table. Should the scaling factor applied cause an invalid Magnitude result to be output on the M Port, then the OVR Flag will become active for the period that the M Port output is invalid.

| S1 | S0 | Scaling Factor |

|----|----|----------------|

| 0  | 0  | x1             |

| 0  | 1  | x2             |

| 1  | 0  | x4             |

| 1  | 1  | x8             |

|    |    |                |

The output number range is from 0 to 2 when the scaling factor is set at x1.

# **PIN DESCRIPTIONS**

| Symbol | Pin Name and Description                                                                                                                                                                                                                                                                                     |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK    | Clock: Common Clock to device Registers. Register contents change on the rising edge of clock.                                                                                                                                                                                                               |

|        | Both pins must be connected.                                                                                                                                                                                                                                                                                 |

| CEX    | Clock Enable: Clock Enable for X Port. The clock to the X port is enabled by a low level.                                                                                                                                                                                                                    |

| CEY    | Clock Enable: Clock Enable for Y Port The clock to the Y port is enabled by a low level.                                                                                                                                                                                                                     |

| X15-X0 | X Data Input Data presented to this input is loaded into the device by the rising edge of CLK.  X15 is the MSB                                                                                                                                                                                               |

| Y15-Y0 | Y Data Input Data presented to this input is loaded into the device by the rising edge of CLK. Y15 is the MSB                                                                                                                                                                                                |

| M15-M0 | <b>M Data Output:</b> Magnitude data generated by the device is output on this port. Data changes on the rising edge of CLK, M15 is the MSB. The weighting of M15 is determined by the Scale factor selected.                                                                                                |

| P11-P0 | <b>P Data Output:</b> Phase data generated by the device is output on this port. Data changes on the rising edge of CLK, P11 is the MSB. The weighting of P11 is $\pi$ radians.                                                                                                                              |

| OEM    | Output Enable: Output Enable for M Port. The M Port is in a high impedance state when this input is high.                                                                                                                                                                                                    |

| OEP    | Output Enable: Output Enable for P Port. The P Port is in a high impedance state when this input is high.                                                                                                                                                                                                    |

| FORM   | Format Select This input selects the format of the Cartesian Data input on the X and Y ports.  This input is latched by the rising edge of CLK, and is applied at the same time as the data to which it refers. A low !evel indicates that two's complement data is applied, a high indicates Sign-Magnitude |

| S1-S0  | Scaling Control: Control input for scaling of Magnitude Data. This input is latched by the rising edge of CLK, and determines the scaling to be applied to the Magnitude result. The Scaling is applied to the output data in the cycle following the cycle in which the control was latched.                |

| OVR    | Overflow: Overflow flag. This signal becomes active if the scaling currently selected causes an invalid value to be presented to the Magnitude output.                                                                                                                                                       |

| Vcc    | +5V supply. All Vcc pins must be connected.                                                                                                                                                                                                                                                                  |

| GND    | <b>0V supply.</b> All GND pins must be connected.                                                                                                                                                                                                                                                            |

# **INPUT DATA RANGE**

| 2's Complement | Sign Magnitude |

|----------------|----------------|

| 7FFF           | 7FFF           |

| •              |                |

|                |                |

|                |                |

| 0001           | 0001           |

| 0000           | 0000           |

| FFFF           | 8000           |

|                |                |

| •              | •              |

| •              | ·              |

| 8001           | FFF            |

# PDSP16330/A/B

## **PIN FUNCTION**

| Pin No.<br>AC | GC  | Function | Pin No.<br>AC | GC | Function | Pin No.<br>AC | GC | Function |

|---------------|-----|----------|---------------|----|----------|---------------|----|----------|

| F3            | 91  | M7       | L9            | 23 | YO       | A9            | 59 | X1       |

| G3            | 92  | M6       | L10           | 24 | CEY      | B8            | 60 | X2       |

| G1            | 93  | M5       | K9            | 25 | ČĽK      | A8            | 61 | Х3       |

| G2            | 94  | M4       | L11           | 26 | Vcc      | B6            | 62 | X4       |

| F1            | 95  | M3       | K10           | 31 | GND      | B7            | 63 | X5       |

| H1            | 96  | M2       | J10           | 32 | GND      | A7            | 64 | X6       |

| H2            | 97  | M1       | K11           | 33 | GND      | C7            | 65 | X7       |

| J1            | 98  | MO       | J11           | 34 | GND      | C6            | 66 | X8       |

| K1            | 99  | S0       | H10           | 35 | GND      | A6            | 67 | X9       |

| J2            | 100 | S1       | H11           | 36 | GND      | A5            | 68 | X10      |

| L1            | 1   | GND      | F10           | 37 | GND      | B5            | 69 | X11      |

| K2            | 6   | Vcc      | G10           | 38 | OEP      | C5            | 70 | X12      |

| K3            | 7   | FORM     | G11           | 39 | P0       | A4            | 71 | X13      |

| L2            | 8   | Y15      | G9            | 40 | P1       | B4            | 72 | X14      |

| L3            | 9   | Y14      | F9            | 41 | P2       | A3            | 73 | X15      |

| K4            | 10  | Y13      | F11           | 42 | P3       | A2            | 74 | CLK      |

| L4            | 11  | Y12      | E11           | 43 | P4       | B3            | 75 | OVR      |

| J5            | 12  | Y11      | E10           | 44 | P5       | A1            | 76 | Vcc      |

| K5            | 13  | Y10      | E9            | 45 | P6       | B2            | 81 | GND      |

| L5            | 14  | Y9       | D11           | 46 | P7       | C2            | 82 | OEM      |

| K6            | 15  | Y8       | D10           | 47 | P8       | B1            | 83 | M15      |

| J6            | 16  | Y7       | C11           | 48 | P9       | C1            | 84 | M14      |

| J7            | 17  | Y6       | B11           | 49 | P10      | D2            | 85 | M13      |

| L7            | 18  | Y5       | C10           | 50 | P11      | D1            | 86 | M12      |

| K7            | 19  | Y4       | A11           | 51 | GND      | E3            | 87 | M11      |

| L6            | 20  | Y3       | B10           | 52 | Vcc      | E2            | 88 | M10      |

| L8            | 21  | Y2       | B9            | 57 | CEX      | E1            | 89 | M9       |

| K8            | 22  | Y1       | A10           | 58 | X0       | F2            | 90 | M8       |

# **ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated): T<sub>amb</sub> (Commercial) = 0°C to + 70°C, T<sub>amb</sub> (Industrial) = -40°C to + 85°C  $V_{cc}$  (Commercial) = 5.0V  $\pm$  5%,  $V_{cc}$  (Industrial and Military) = 5.0V  $\pm$  1%, GND = 0V

# STATIC CHARACTERISTICS

| Characteristic                   | Symbol          | Value |      |                | Units | Sub-<br>group | Conditions                             |  |

|----------------------------------|-----------------|-------|------|----------------|-------|---------------|----------------------------------------|--|

| - Characteristic                 | Min. Typ. Max.  |       | Max. | <b>G</b> iiito | group |               |                                        |  |

| * Output high voltage            | V <sub>OH</sub> | 2.4   |      |                | ٧     | 1,2,3         | IOH = 3.2mA                            |  |

| * Output low voltage             | V <sub>OL</sub> |       |      | 0.6            | V     | 1,2,3         | IOL=-3.2mA                             |  |

| * Input high voltage (CMOS)      | $V_{IH}$        | 3.0   |      |                | V     | 1,2,3         | Inputs CEX, CEY and CLK only           |  |

| * Input low voltage (CMOS)       | V <sub>IL</sub> |       |      | 1.0            | V     | 1,2,3         | Inputs CEX, CEY and CLK only           |  |

| * Input high voltage (TTL)       | V <sub>IH</sub> | 2.2   |      |                | V     | 1,2,3         | All other inputs                       |  |

| * Input low voltage (TTL)        | V <sub>IL</sub> |       |      | 8.0            | V     | 1,2,3         | All other inputs                       |  |

| * Input leakage current (Note 1) | l <sub>IL</sub> | -10   |      | + 120          | μΑ    | 1,2,3         | $GND \leq V_{IN} \leq V_{CC}$          |  |

| † Input capacitance              | Ċ <sub>IN</sub> |       | 10   |                | pF    |               |                                        |  |

| Output leakage current           | l <sub>oz</sub> | -50   |      | + 50           | μΑ    | 1,2,3         | GND ≤V <sub>IN</sub> ≤ V <sub>CC</sub> |  |

| † Output SC current              | Ios             | -50   |      | 230            | mA    |               | V <sub>cc</sub> = Max                  |  |

#### NOTES

- 1. All inputs except clock inputs have high value pull-down resistors

- 2. All parameters marked \* are tested during production. Parameters marked † are guaranteed by design and characterisation.

## **SWITCHING CHARACTERISTICS**

| Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                             |                                         |                                                            |                                         | Units                                                                                     |            |                                                 |                                                                                                                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------|------------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------|------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                             | PDSP16330                               |                                                            | PDSP16330A                              |                                                                                           | PDSP16330B |                                                 | Conditions                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Min.                                                        | Max.                                    | Min.                                                       | Max.                                    | Min.                                                                                      | Max.       |                                                 |                                                                                                                                                                                                                      |

| † Input data setup to clock rising edge † Input data Hold after clock rising edge † CEX, CEY Setup to clock rising edge † CEX, CEY Hold aher clock rising edge † FORM, S1:0 Setup to clock rising edge † FORM, S1:0 Hold after clock rising edge † Clock rising edge to valid data * Clock period † Clock high time † Clock low time † Latency † OEM, OEP low to data high data valid † OEM, OEP low to data high impedance † OEM, OEP low to data high impedance † Vcc current (TTL input levels)  † Vcc current (CMOS input levels) | 15<br>2<br>30<br>0<br>15<br>7<br>5<br>100<br>25<br>25<br>24 | 40<br>24<br>30<br>30<br>30<br>30<br>110 | 12<br>2<br>12<br>0<br>12<br>2<br>5<br>50<br>15<br>15<br>24 | 25<br>24<br>25<br>25<br>25<br>25<br>180 | 12<br>2<br>12<br>0<br>12<br>2<br>5<br>40<br>15<br>15<br>24<br>25<br>25<br>25<br>25<br>225 | 25<br>24   | ns ms ms mA | 2 x LSTTL + 20pF  2 x LSTTL + 20pF 2 x LSTTL + 20pF 2 x LSTTL + 20pF 2 x LSTTL + 20pF V <sub>cc</sub> = Max Outputs unloaded Clock freq. = Max Outputs unloaded Clock freq. = Max Outputs unloaded Clock freq. = Max |

#### NOTES

- LSTTL is equivalent to I<sub>OH</sub> = 20μA, I<sub>OL</sub> = -0.4mA

Current is defined as negative into the device

- 3. CMOS input levels are defined as:  $V_{IH} = V_{DD} 0.5V$ ,  $V_{II} = +0.5V$

- 4. All parameters marked \* are tested during production.

- Parameters marked † are guaranteed by design and characterisation.

- 5. All timings are dependent on silicon speed. This speed is tested by measuring clock period. This guarantees all other timings by characterisation and design.

## **ABSOLUTE MAXIMUM RATINGS**

| Supply voltage, $V_{cc}$<br>Input voltage, $V_{IN}$<br>Output voltage, $V_{our}$<br>Clamp diode current per pin, $I_{\kappa}$ (see N | -0.5V to + 7.0V<br>-0.5V to VCC + 0.5V<br>-0.5V to VCC + 0.5V<br>ote 2) ±18mA |

|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Static discharge voltage (HMB), V <sub>STAT</sub>                                                                                    | 500V                                                                          |

| Storage temperature. T <sub>stg</sub> Ambient temperature with                                                                       | -65°C to + 150°C                                                              |

| Ambient temperature with                                                                                                             |                                                                               |

| power applied T <sub>amb</sub> :                                                                                                     |                                                                               |

| Commercial                                                                                                                           | 0°C to + 70°C                                                                 |

| Industrial                                                                                                                           | -40°C to + 85°C                                                               |

| Military                                                                                                                             | -55 °C to + 125°C                                                             |

| Package power dissipation P <sub>TOT</sub>                                                                                           | 1200mW                                                                        |

| Junction temperature                                                                                                                 | 150°C                                                                         |

## THERMAL CHARACTERISTICS

| Package Type | <i>θ</i> υc° <b>C/W</b> | <i>θ</i> JA° <b>C/W</b> |

|--------------|-------------------------|-------------------------|

| AC           | 12                      | 36                      |

| GC           | 12                      | 35                      |

## **NOTES**

- 1. Exceeding these ratings may cause permanent damage. Functional operation under these conditions is not implied.

- 2. Maximum dissipation or 1 second should not be exceeded; only one output to be tested at any one time.

- 3. Exposure to Absoulte Maximum Ratings for extended periods may affect device reliability.

# PDSP16330/A/B

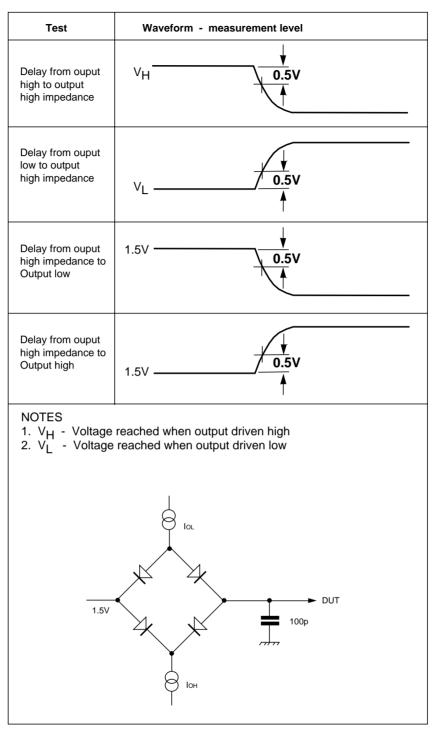

Fig.3 Three state delay measurement load

# For more information about all Zarlink products visit our Web Site at www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's I<sup>2</sup>C components conveys a licence under the Philips I<sup>2</sup>C Patent rights to use these components in and I<sup>2</sup>C System, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright Zarlink Semiconductor Inc. All Rights Reserved.

TECHNICAL DOCUMENTATION - NOT FOR RESALE