#### XENSIV™ PAS CO2 5 V sensor based on photo acoustic spectroscopy principle

#### **Features**

• Operating range: 0 ppm to 32000 ppm

• Accuracy: ±50 ppm ±5% of reading between 400 ppm and 3000 ppm

• Lifetime: 10 years for indoor mission profile

• Interface: I<sup>2</sup>C, UART, and PWM

• Package dimension: 13.8 × 14 × 7.5 mm<sup>3</sup>

• Maintenance: Maintenance-free when using ABOC feature (automatic baseline offset correction)

#### **Potential applications**

High accuracy, compact size, and SMD capability make the XENSIV™ PAS CO2 sensor ideal for indoor air quality monitoring solutions in the market with numerous potential applications.

- HVAC (heating, ventilation, air conditioning)

- · Home appliances

- · Smart home IoT devices

- In-cabin air quality monitoring unit

- Agriculture/greenhouses

#### **Description**

Infineon has leveraged its knowledge in sensors and MEMS technologies to develop a disruptive gas sensor for CO<sub>2</sub> sensing. The XENSIV™ PAS CO2 is a real CO<sub>2</sub> sensor combining NDIR technology with Infineon's high SNR MEMS microphones, allowing for state-of-the-art accuracy in an exceptionally small form factor.

The sensor is based on the photoacoustic spectroscopy (PAS) principle, where  $CO_2$  molecules within the sensor cavity absorb infrared light, generating small pressure changes that are detected by an acoustic detector.  $CO_2$  concentration is then delivered in the form of a direct ppm readout, thanks to the integrated microcontroller. Highly accurate  $CO_2$  readings are guaranteed.

| OPN number     | Package      | SP number   |  |  |

|----------------|--------------|-------------|--|--|

| PASCO2V15AUMA1 | LG-MLGA-14-2 | SP005862398 |  |  |

#### **Datasheet**

# **Table of contents**

|         | Features                                                        | 1  |

|---------|-----------------------------------------------------------------|----|

|         | Potential applications                                          | 1  |

|         | Description                                                     | 1  |

|         | Table of contents                                               |    |

| 1       | Block diagram                                                   |    |

| 2       | Pin-out diagram                                                 |    |

|         | -                                                               |    |

| 3       | Typical sensor response to CO <sub>2</sub> concentration change | 6  |

| 4       | Characteristics and parameters                                  | 7  |

| 4.1     | Specification                                                   | 7  |

| 4.1.1   | Operating range                                                 | 7  |

| 4.1.2   | Storage conditions                                              | 7  |

| 4.1.3   | Timing characteristics                                          | 8  |

| 4.1.4   | Absolute maximum ratings                                        | 10 |

| 4.1.5   | Current rating and power consumption                            | 10 |

| 4.1.6   | CO <sub>2</sub> transfer function                               | 11 |

| 4.2     | Digital interfaces                                              | 11 |

| 4.2.1   | I <sup>2</sup> C interface                                      | 11 |

| 4.2.1.1 | I <sup>2</sup> C transaction format                             | 12 |

| 4.2.1.2 | I <sup>2</sup> C timing characteristics                         | 12 |

| 4.2.2   | UART interface                                                  | 14 |

| 4.3     | Application circuit examples                                    | 15 |

| 4.3.1   | I <sup>2</sup> C application circuit example                    | 15 |

| 4.3.2   | UART application circuit example                                | 15 |

| 4.3.3   | PWM application circuit example                                 | 16 |

| 4.4     | Functional description                                          | 16 |

| 4.4.1   | Operating modes                                                 | 16 |

| 4.4.2   | Data post-processing                                            | 17 |

| 4.4.2.1 | Pressure compensation                                           | 17 |

| 4.4.2.2 | Automatic baseline offset correction                            | 17 |

| 4.4.2.3 | Forced compensation                                             | 17 |

| 4.4.2.4 | Alarm threshold                                                 | 18 |

| 4.5     | Monitoring mechanism as advanced functionality                  | 18 |

| 5       | Register map                                                    | 19 |

| 5.1     | Register map access method                                      | 19 |

| 5.2     | Register map bitfields                                          | 20 |

| 5.3     | Product and revision ID register (PROD_ID)                      | 21 |

| 5.4     | Sensor status register (SENS STS)                               | 21 |

V1.3

#### **Datasheet**

#### Table of contents

| 5.5  | Measurement period configuration registers (MEAS_RATE_H)       | 23 |

|------|----------------------------------------------------------------|----|

| 5.6  | Measurement period configuration registers (MEAS_RATE_L)       |    |

| 5.7  | Measurement mode configuration register (MEAS_CFG)             |    |

| 5.8  | CO <sub>2</sub> concentration result register (CO2PPM_H)       |    |

| 5.9  | CO <sub>2</sub> concentration result register (CO2PPM_L)       |    |

| 5.10 | Measurement status register (MEAS_STS)                         | 26 |

| 5.11 | Interrupt pin configuration register (INT_CFG)                 | 27 |

| 5.12 | Alarm threshold register (ALARM_TH_H)                          | 28 |

| 5.13 | Alarm threshold register (ALARM_TH_L)                          | 29 |

| 5.14 | Pressure compensation registers (PRES_REF_H)                   | 29 |

| 5.15 | Pressure compensation registers (PRES_REF_L)                   | 30 |

| 5.16 | Automatic baseline offset compensation reference (CALIB_REF_H) | 30 |

| 5.17 | Automatic baseline offset compensation reference (CALIB_REF_L) |    |

| 5.18 | Scratch pad register (SCRATCH_PAD)                             | 31 |

| 5.19 | Soft reset register (SENS_RST)                                 | 32 |

| 6    | Assembly instruction                                           | 33 |

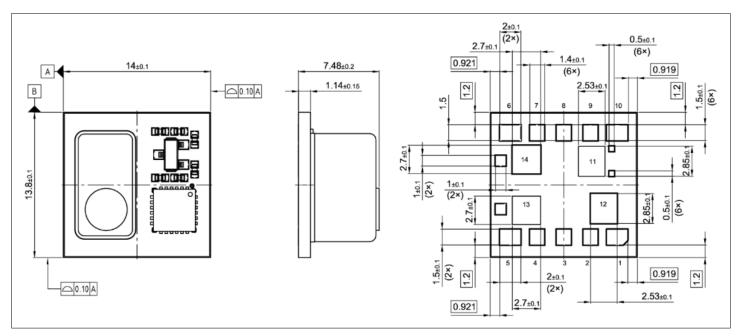

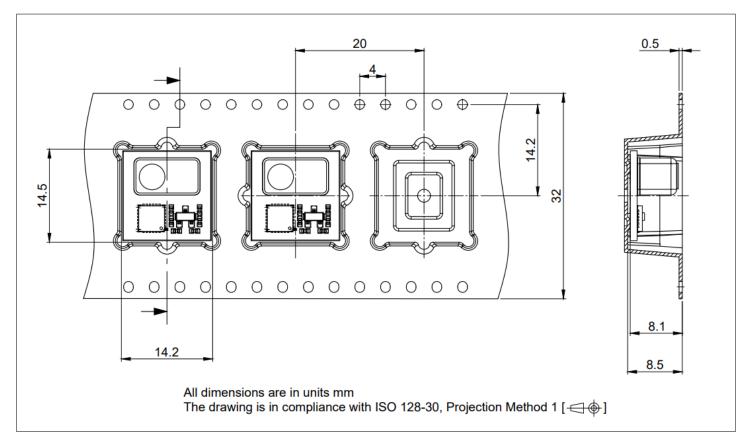

| 7    | Package dimensions and footprint                               | 34 |

| 8    | Packing for shipment                                           | 35 |

|      | Revision history                                               | 36 |

|      | Disclaimer                                                     | 37 |

V1.3

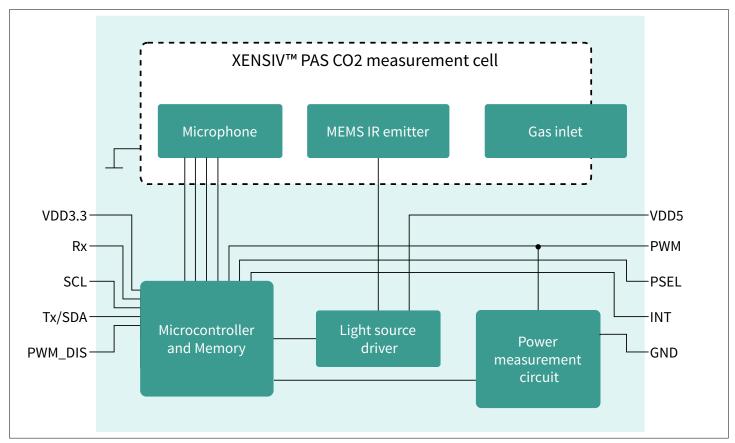

1 Block diagram

#### **Block diagram** 1

Figure 1 Block diagram of XENSIV™ PAS CO2

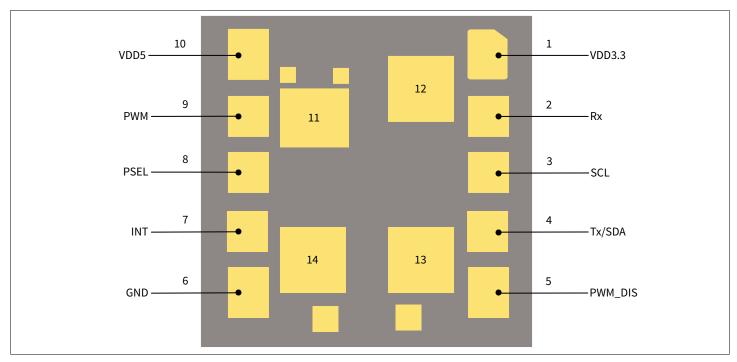

2 Pin-out diagram

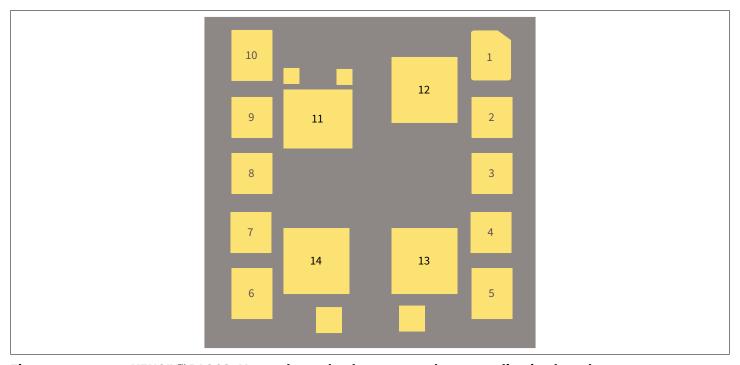

# 2 Pin-out diagram

Figure 2 Pin-out diagram (bottom view)

Table 1 Pin description

| PIN | Symbol  | Туре                 | Description                                                                  |

|-----|---------|----------------------|------------------------------------------------------------------------------|

| 1   | VDD3.3  | Power supply (3.3 V) | 3.3 V digital power supply                                                   |

| 2   | Rx      | Input/output         | UART receiver pin (3.3 V domain)                                             |

| 3   | SCL     | Input/output         | I <sup>2</sup> C clock pin (3.3 V domain)                                    |

| 4   | Tx/SDA  | Output               | UART transmitter pin (3.3 V domain)/I <sup>2</sup> C data pin (3.3 V domain) |

| 5   | PWM_DIS | Input                | PWM disable input pin (3.3 V domain)                                         |

| 6   | GND     | Ground               | Ground                                                                       |

| 7   | INT     | Output               | Interrupt output pin (3.3 V domain)                                          |

| 8   | PSEL    | Input                | Communication interface select input pin (3.3 V domain)                      |

| 9   | PWM     | Output               | PWM output pin (3.3 V domain)                                                |

| 10  | VDD5    | Power supply (5 V)   | 5 V power supply for the IR emitter                                          |

5

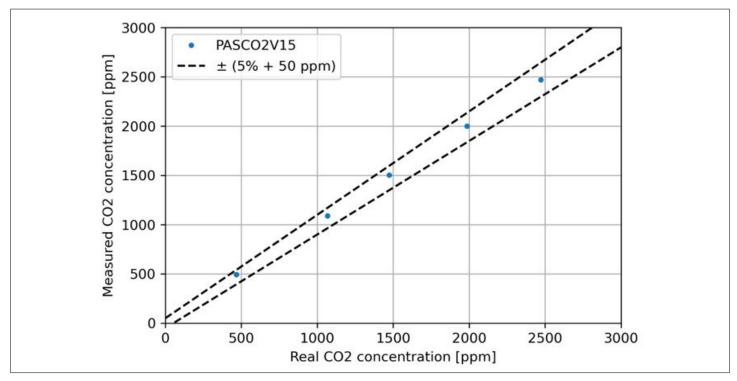

3 Typical sensor response to CO<sub>2</sub> concentration change

# 3 Typical sensor response to CO<sub>2</sub> concentration change

Measurement condition: VDD5 = 5.0 V, VDD3.3 = 3.3 V,  $T_{amb}$  = 25°C, p = 1013 hPa and % r.H. = 30%

6

Figure 3 Typical sensor response to CO<sub>2</sub> concentration change

V1.3 2024-11-27

4 Characteristics and parameters

# 4 Characteristics and parameters

# 4.1 Specification

# 4.1.1 Operating range

To ensure proper operation of the sensor, the following operating conditions must not be exceeded. All parameters specified in the subsequent sections refer to these operating conditions unless otherwise specified.

Table 2 Operating range

| Parameter                                       | Symbol           | Values | 3    |       | Unit | Note or test condition       |

|-------------------------------------------------|------------------|--------|------|-------|------|------------------------------|

|                                                 |                  | Min.   | Тур. | Max.  |      |                              |

| CO <sub>2</sub> measurement range <sup>1)</sup> | C <sub>CO2</sub> | 0      |      | 32000 | ppm  | Functional measurement range |

| Ambient temperature <sup>1)</sup>               | $T_{amb}$        | 0      |      | 50    | °C   |                              |

| Relative humidity <sup>1)</sup>                 | rH               | 0      |      | 85    | %    | Non-condensing               |

| Pressure <sup>1)</sup>                          | p                | 750    | 1013 | 1150  | hPa  |                              |

| Supply voltage <sup>1)</sup>                    | VDD3.3           | 3      | 3.3  | 3.6   | V    |                              |

|                                                 | VDD5             | 4.45   | 5    | 5.5   | V    |                              |

| Lifetime <sup>1)</sup>                          | $t_{ m life}$    |        | 10   |       | Year | Depends on mission profile   |

<sup>1)</sup> Not subject to production test. This parameter is verified by design/characterization.

# 4.1.2 Storage conditions

Storage condition refers to dry pack: packed, evacuated, desiccant<sup>1)</sup>, humidity indicator card (HIC) sealed moisture barrier bag.

Table 3 Storage condition

| Parameter                                          | Symbol                         | Values |      |      | Unit | Note or test condition  |

|----------------------------------------------------|--------------------------------|--------|------|------|------|-------------------------|

|                                                    |                                | Min.   | Тур. | Max. |      |                         |

| Storage temperature <sup>1)</sup>                  | $T_{ m storage}$               | 5      |      | 40   | °C   | <90% r.H. <sup>2)</sup> |

| Storage time <sup>1)</sup>                         | t <sub>storage</sub>           |        |      | 3    | Year |                         |

| Storage temperature during transport <sup>1)</sup> | $T_{ m storage\_transport}$    | -20    |      | 60   | °C   |                         |

| Storage time during transport <sup>1)</sup>        | t <sub>storage_transport</sub> |        |      | 10   | Day  |                         |

<sup>1)</sup> Not subject to production test. This parameter is verified by design/characterization.

<sup>2)</sup> Condensation and bedewing shall be avoided.

Number of desiccant units to be calculated according to JEDEC Standard 033.

#### **Datasheet**

4 Characteristics and parameters

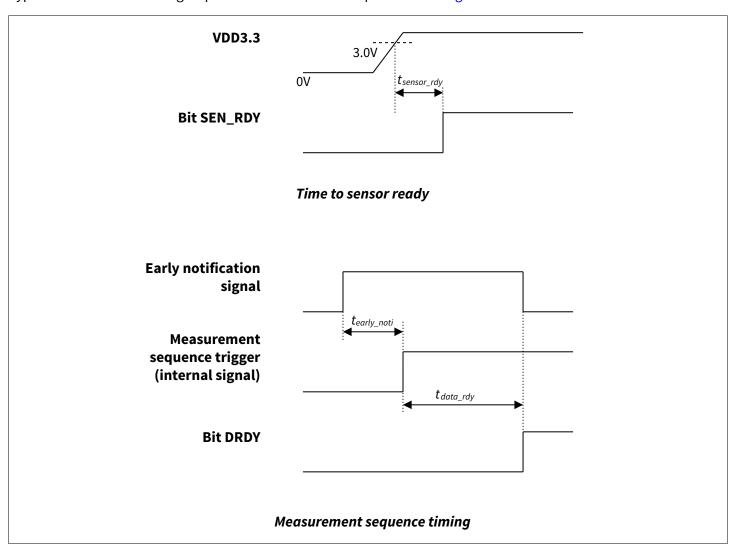

#### **Timing characteristics** 4.1.3

#### Table 4 **Timing characteristics**

| Parameter                                      | Symbol                  | Values |      |      | Unit | Note or test condition                                                |  |

|------------------------------------------------|-------------------------|--------|------|------|------|-----------------------------------------------------------------------|--|

|                                                |                         | Min.   | Тур. | Max. |      |                                                                       |  |

| Sampling time <sup>1)</sup>                    | t <sub>sampling</sub>   | 10     | 60   | 4095 | S    | Sensor accuracy may be affected when sampling rates exceed 1 meas/min |  |

| Time to sensor ready <sup>1)</sup>             | t <sub>sensor_rdy</sub> |        |      | 1    | s    |                                                                       |  |

| Time to early notification <sup>1) 2)</sup>    | t <sub>early_noti</sub> |        | 2    |      | s    |                                                                       |  |

| I <sup>2</sup> C clock frequency <sup>1)</sup> | $f_{I2C}$               |        | 100  |      | kHz  |                                                                       |  |

|                                                |                         |        | 400  |      |      |                                                                       |  |

| PWM frequency <sup>1)</sup>                    | $f_{\text{pwm}}$        |        | 80   |      | Hz   |                                                                       |  |

| UART baud rate <sup>1)</sup>                   | $f_{baud}$              |        | 9.6  |      | kbps |                                                                       |  |

Not subject to production test. This parameter is verified by design/characterization. Relevant for continuous mode of operation. 1)

<sup>2)</sup>

4 Characteristics and parameters

Typical measurement timing sequence for I<sup>2</sup>C and UART is presented in Figure 4.

9

Figure 4 Illustration of the timing characteristic parameters

4 Characteristics and parameters

# 4.1.4 Absolute maximum ratings

#### Table 5 Absolute maximum ratings

| Parameter                   | Symbol               | Values |      |      | Unit | Note or test     |

|-----------------------------|----------------------|--------|------|------|------|------------------|

|                             |                      | Min.   | Тур. | Max. |      | condition        |

| MSL level                   | MSL                  |        | 3    |      |      |                  |

| Maximum ambient temperature | T <sub>amb_max</sub> | -10    |      | 60   | °C   |                  |

| Maximum relative humidity   | rH <sub>max</sub>    | 0      |      | 95   | %    |                  |

| 5 V supply voltage          | $V_{\rm VDD5}$       | 4.45   |      | 5.5  | V    |                  |

| 3.3 V supply voltage        | V <sub>VDD3.3</sub>  | 3.0    |      | 3.6  | V    |                  |

| Reflow temperature          | T <sub>r</sub>       |        |      | 245  | °C   | JEDEC J-STD-020E |

| ESD human body model        | V <sub>ESD_HBM</sub> | -2     |      | 2    | kV   | HBM (JS001)      |

| ESD charge discharge model  | V <sub>ESD_CDM</sub> |        |      | 500  | V    | CDM (JS002)      |

Note:

Stresses above the values listed as "Absolute Maximum Ratings" may cause permanent damage to the devices. Exposure to absolute maximum rating conditions for extended period of time may affect device reliability.

# 4.1.5 Current rating and power consumption

All parameters specified in Table 5 refer to the following operating conditions unless otherwise specified: VDD3.3 = 3.3 V, VDD5 = 5.0 V,  $T_{amb}$  = 25°C, % r.H. = 30%, p = 1013 hPa.

Table 6 Current rating

| Parameter                     | Symbol                | Pin    | Values |      |      | Unit | Note or test condition |

|-------------------------------|-----------------------|--------|--------|------|------|------|------------------------|

|                               |                       |        | Min.   | Тур. | Max. |      |                        |

| Peak current <sup>1)</sup>    | I <sub>peak 5</sub>   | VDD5   |        | 265  | 290  | mA   |                        |

| Peak current <sup>1)</sup>    | I <sub>peak 3.3</sub> | VDD3.3 |        | 10   |      | mA   |                        |

| Average current <sup>1)</sup> | I <sub>avg 5</sub>    | VDD5   |        | 1    |      | mA   | At 1 meas/min          |

| Average current <sup>1)</sup> | I <sub>avg 3.3</sub>  | VDD3.3 |        | 10   |      | mA   | At 1 meas/min          |

| Average power <sup>1)</sup>   | Pavg                  |        |        | 30   |      | mW   | At 1 meas/min          |

<sup>1)</sup> Not subject to production test. This parameter is verified by design/characterization.

4 Characteristics and parameters

### 4.1.6 CO<sub>2</sub> transfer function

All parameters specified in the following sections refer to the operating conditions unless otherwise specified: VDD3.3 = 3.3 V, VDD5 = 5.0 V,  $T_{\text{amb}}$  = 25°C, % r.H. = 30%, p = 1013 hPa, and  $t_{\text{sampling}}$  = 1 meas/min.

Table 7 CO<sub>2</sub> transfer function

| Parameter                        | Symbol             | Values                 |      |                        | Unit  | Note or test condition                           |

|----------------------------------|--------------------|------------------------|------|------------------------|-------|--------------------------------------------------|

|                                  |                    | Min.                   | Тур. | Max.                   |       |                                                  |

| Accuracy <sup>1)</sup>           | Acc                | -50 ppm -5% of reading |      | +50 ppm +5% of reading | ppm   | C <sub>CO2</sub> : 400-3000 ppm                  |

| Response time <sup>2)</sup>      | t <sub>63</sub>    |                        | 55   |                        | s     |                                                  |

| Repeatability <sup>2) 3)</sup>   | R                  |                        |      | 10                     | ppm   |                                                  |

| Pressure stability <sup>2)</sup> | p <sub>error</sub> |                        | 0    |                        | %/hPa | With pressure compensation feature enabled       |

| Acoustic stability <sup>2)</sup> | SPLerror           | 3                      | 6    | 15                     | ppm   | Up to 95 dB for pink noise from 100 Hz to 10 kHz |

Accuracy verified using certified calibration gas mixtures and high-precision reference sensors. Uncertainty in calibration gas mixtures of ±2% needs to be considered. Temporary deviations in accuracy caused by assembly, rough handling or harsh environmental conditions can be compensated using forced compensation scheme (FCS) or automatic baseline offset correction (ABOC).

# 4.2 Digital interfaces

The XENSIV<sup>™</sup> PAS CO2 supports I<sup>2</sup>C, UART, and PWM. The I<sup>2</sup>C and UART interfaces are described in detail in the following chapters.

#### 4.2.1 I<sup>2</sup>C interface

The device complies with the  $I^2C$  protocol. When  $I^2C$  is selected as a serial communication interface, the device acts as an  $I^2C$  slave. The main characteristics of the interface are described below:

- Slave mode only

- I<sup>2</sup>C clock frequency: 100 kHz and 400 kHz

- 7-bit slave address: 0×28

- No CRC

- The device supports clock stretching

- 8-bit addressing mode supported (7-bit address + RW)

- Bulk read and write supported (device auto-increments automatically the address)

- Address 0×00 not supported

Further details of the protocol are covered in the separate application note.

<sup>2)</sup> Not subject to production test. This parameter is verified by design/characterization.

<sup>3)</sup> Stepwise Reaction IIR filter is enabled.

4 Characteristics and parameters

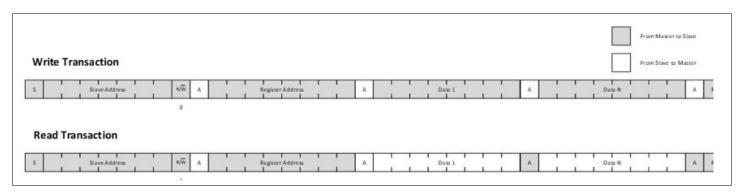

#### 4.2.1.1 I<sup>2</sup>C transaction format

The I<sup>2</sup>C transaction has the following structure: a start condition followed by four bytes followed a stop condition.

Figure 5 I<sup>2</sup>C write and read transaction

Table 8 I<sup>2</sup>C transaction

| Byte | Description     | Value                              | Comments                                                             |

|------|-----------------|------------------------------------|----------------------------------------------------------------------|

|      | Start condition |                                    |                                                                      |

| 1    | Header          | (Slave address << 1)   R/W         |                                                                      |

| 2    | First data-byte | As per user request/register value | Read: data provided by the slave<br>Write: data provided by the user |

| N+2  | Data byte N     | As per user request/register value | Read: data provided by the slave<br>Write: data provided by the user |

|      | End condition   |                                    |                                                                      |

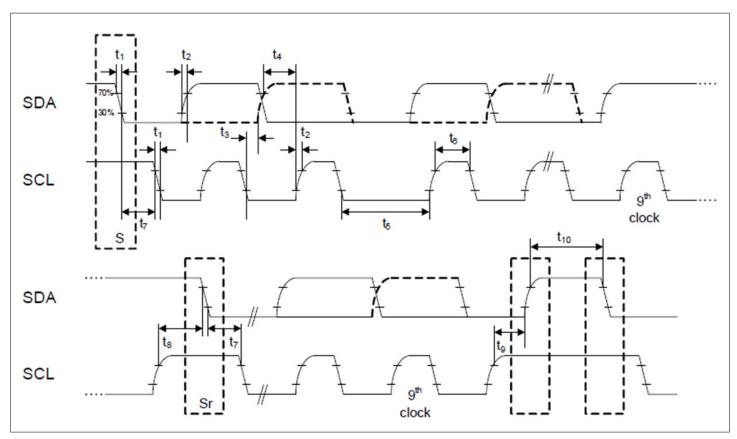

# **4.2.1.2** I<sup>2</sup>C timing characteristics

Due to the wired-AND configuration of an I<sup>2</sup>C bus system, the port drivers on the SCL and SDA signal lines need to operate in open-drain mode. The high level of these lines must be held by an external pull-up device, approximately 10 kOhm for operation at 100 kbits/s, approximately 2 kOhm for operation at 400 kbits/s.

Table 9 I<sup>2</sup>C standard mode timing

| Parameter                                  | Symbol | Values |      |      | Unit | Note or test condition |

|--------------------------------------------|--------|--------|------|------|------|------------------------|

|                                            |        | Min.   | Тур. | Max. |      |                        |

| Fall time of both SDA and SCL              | t1     |        |      | 300  | ns   |                        |

| Rise time of both SDA and SCL              | t2     |        |      | 1000 | ns   |                        |

| Data hold time                             | t3     | 0      |      |      | μs   |                        |

| Data set-up time                           | t4     | 250    |      |      | ns   |                        |

| LOW period of SCL clock                    | t5     | 4.7    |      |      | μs   |                        |

| HIGH period of SCL clock                   | t6     | 4.0    |      |      | μs   |                        |

| Hold time for a (repeated) START condition | t7     | 4.0    |      |      | μs   |                        |

| Set-up time for (repeated) START condition | t8     | 4.7    |      |      | μs   |                        |

12

(table continues...)

#### **Datasheet**

4 Characteristics and parameters

# Table 9 (continued) I<sup>2</sup>C standard mode timing

| Parameter                                        | Symbol         | Values |      |      | Unit | Note or test condition |  |

|--------------------------------------------------|----------------|--------|------|------|------|------------------------|--|

|                                                  |                | Min.   | Тур. | Max. |      |                        |  |

| Set-up time for STOP condition                   | t9             | 4.0    |      |      | μs   |                        |  |

| Bus free time between a STOP and START condition | t10            | 4.7    |      |      | μs   |                        |  |

| Capacitive load for each bus line                | C <sub>b</sub> |        |      | 400  | pF   |                        |  |

# Table 10 I<sup>2</sup>C fast mode timing

| Parameter                                        | Symbol         | Values                     |      |      | Unit | Note or test condition                                               |  |

|--------------------------------------------------|----------------|----------------------------|------|------|------|----------------------------------------------------------------------|--|

|                                                  |                | Min.                       | Тур. | Max. |      |                                                                      |  |

| Fall time of both SDA and SCL                    | t1             | 20 +<br>0.1*C <sub>b</sub> |      | 300  | ns   | C <sub>b</sub> refers to the total capacitance of one bus line in pF |  |

| Rise time of both SDA and SCL                    | t2             | 20 +<br>0.1*C <sub>b</sub> |      | 300  | ns   | C <sub>b</sub> refers to the total capacitance of one bus line in pF |  |

| Data hold time                                   | t3             | 0                          |      |      | μs   |                                                                      |  |

| Data set-up time                                 | t4             | 100                        |      |      | ns   |                                                                      |  |

| LOW period of SCL clock                          | t5             | 1.3                        |      |      | μs   |                                                                      |  |

| HIGH period of SCL clock                         | t6             | 0.6                        |      |      | μs   |                                                                      |  |

| Hold time for a (repeated) START condition       | t7             | 0.6                        |      |      | μs   |                                                                      |  |

| Set-up time for (repeated) START condition       | t8             | 0.6                        |      |      | μs   |                                                                      |  |

| Set-up time for STOP condition                   | t9             | 0.6                        |      |      | μs   |                                                                      |  |

| Bus free time between a STOP and START condition | t10            | 1.3                        |      |      | μs   |                                                                      |  |

| Capacitive load for each bus line                | C <sub>b</sub> |                            |      | 400  | pF   |                                                                      |  |

4 Characteristics and parameters

Figure 6 I<sup>2</sup>C standard and fast mode timing

#### 4.2.2 UART interface

When UART is selected as a serial communication interface, the device acts as a UART slave. The device operates via UART for point-to-point communication. Bus operation is not supported. As a result, it is recommended that the master uses a time-out mechanism. The basic format of a valid UART frame is 1 start bit, 8 data bits, no parity bit, and 1 stop bit. The master combines several UART frames into a message (read or write). The combination of master request and slave answer defines a transaction. The main characteristics of the interface are described below:

- Point to point operation no bus support

- Slave operation only

- UART clock frequency = 9.6 kHz

- Format: 1 start bit, 8 data bits, no parity bit, 1 stop bit. Supports direct connection with a terminal program

V1.3

4 Characteristics and parameters

# 4.3 Application circuit examples

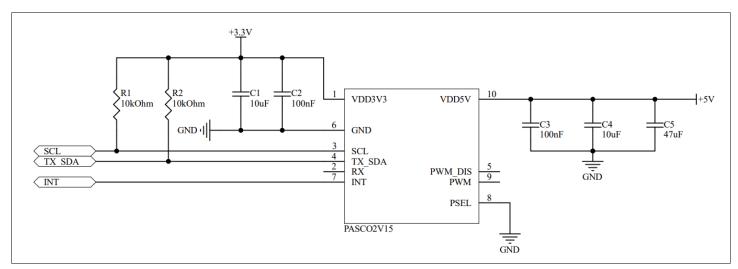

# 4.3.1 I<sup>2</sup>C application circuit example

Figure 7 Application circuit example for I<sup>2</sup>C

With this configuration, the device will start in Idle mode of operation. Internal pull up is present on PWM\_DIS pin.

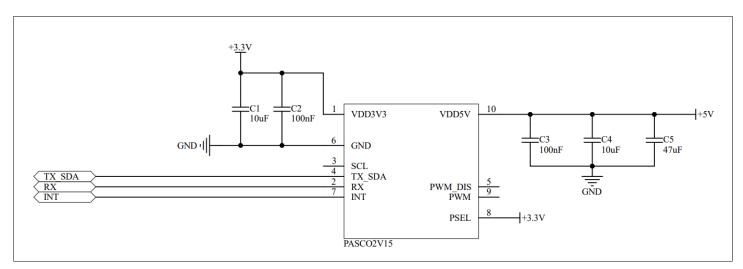

# 4.3.2 UART application circuit example

Figure 8 Application circuit example for UART

With this configuration, the device will start in Idle mode of operation. Internal pull up is present on PWM\_DIS pin.

4 Characteristics and parameters

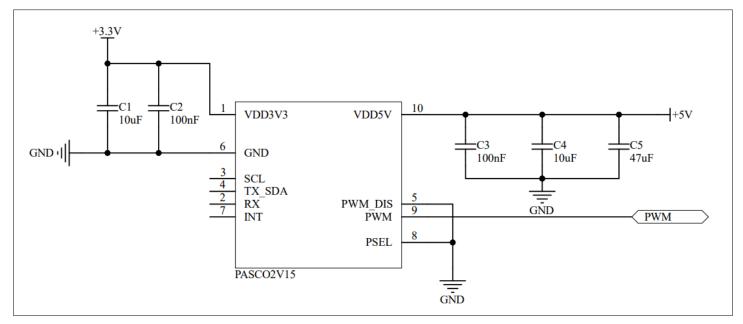

### 4.3.3 PWM application circuit example

Figure 9 Application circuit example for PWM

With this configuration, the device will start in continuous mode of operation with sampling time of 1 meas/min.

### 4.4 Functional description

This section describes the operation of the sensor while measuring CO<sub>2</sub> concentrations. At any moment, the device can be in one out of two different states: active and inactive. At active state, the CPU controlling the device is operating and can perform tasks, such as: running a measurement sequence, serving an interrupt, and so on. When the device has no specific task to perform, it goes to an inactive state. A transition from active to inactive state may occur at the end of a measurement sequence. Several events can wake up the device: the reception of a measurement request in continuous measurement mode.

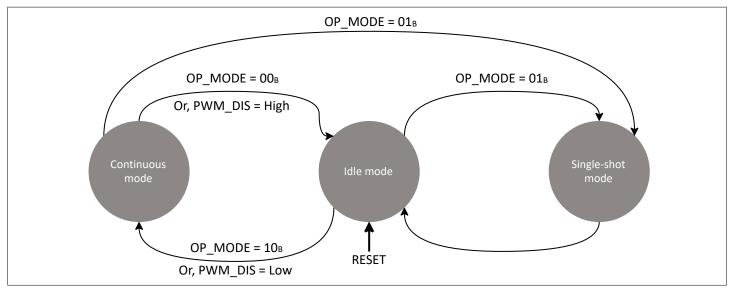

# 4.4.1 Operating modes

The operating mode can be programmed via the serial communication interface by using the bit field **MEAS\_CFG.OP\_MODE**.

The sensor module supports three operating modes:

- **Idle mode:** The device does not perform any CO<sub>2</sub> concentration measurement. The device remains inactive until it becomes active shortly to serve interrupts before going back to an inactive state

- Continuous mode: In this mode, the device periodically triggers a CO<sub>2</sub> concentration measurement sequence.

Once a measurement sequence is completed, the device goes back to an inactive state and wakes up automatically for the next measurement sequence. The measurement period is programmable from 5 s to 4095 s

- **Single-shot mode:** In this mode, the device triggers a single measurement sequence. At the end of the measurement sequence, the device goes back automatically to idle mode

# infineon

4 Characteristics and parameters

Figure 10 Operating mode transition

### 4.4.2 Data post-processing

Once the CO<sub>2</sub> concentration data has been acquired, several post-processing schemes can be applied to utilize different functionality.

### 4.4.2.1 Pressure compensation

The  $\mathrm{CO}_2$  concentration value acquired by the sensor is dependent on the external atmospheric pressure. To compensate for this effect, the application system can provide the value of the atmospheric pressure by writing into the specific registers, that is, **PRES\_REF\_H** and **PRES\_REF\_L**. At the end of a measurement sequence, the device reads the pressure value and applies for compensation on the  $\mathrm{CO}_2$  concentration value before storing it into the result registers.

#### 4.4.2.2 Automatic baseline offset correction

To correct slow drifts caused by aging during operation, the device supports automatic baseline offset compensation. Every week of operation, the device computes an offset to correct the baseline of the device. The device must be in contact with the reference concentration (for example, fresh air at 400 ppm of  $CO_2$  concentration) at least 30 minutes per operating week to make sure proper baseline compensation. The device supports different configurations for compensation. The ABOC set point may only be set between 350 and 1500 ppm.

#### 4.4.2.3 Forced compensation

Forced compensation provides a means to speed up the offset compensation process. Before forced compensation is enabled, the device shall be physically exposed to the reference  $CO_2$  concentration. The device will use the next three measurements to calculate the compensation offset. The user shall ensure constant exposure to the reference  $CO_2$  concentration during that time. It is recommended to operate at one measurement per 10 seconds while implementing the forced compensation scheme. When three measurement sequences are completed, the device automatically reconfigures itself with the newly computed offset applied to the subsequent  $CO_2$  concentration measurement results. The forced compensation offset can be stored to the non-volatile memory by using the corresponding command (SENS\_RST = 0xCF).

V1.3

#### **Datasheet**

4 Characteristics and parameters

#### 4.4.2.4 Alarm threshold

The device can be configured via interrupt to perform an alarm threshold check each time a new CO<sub>2</sub> concentration data is acquired. At the end of each measurement sequence, the computed CO<sub>2</sub> value (after all applicable offset compensations) is compared to the concatenated value in **ALARM\_TH\_H** and **ALARM\_TH\_L**. In case of a threshold violation, the sticky bit **MEAS\_STS.ALARM** is set. This also sets pin **INT** to active level due to configuration as alarm. Bit **MEAS\_STS.ALARM** is cleared by reading register **MEAS\_STS.ALARM\_CLR**.

# 4.5 Monitoring mechanism as advanced functionality

The device supports several mechanisms to monitor the correct operation of the sensor.

Table 11 Functionality description

| Mechanism                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Sensor ready status               | After each power-on reset, bit <b>SENS_STS.SEN_RDY</b> is set to confirm that the sensor has initialized correctly                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Scratchpad register               | To check the integrity of the communication layer of the serial communication interface, register <b>SCRATCH_PAD</b> can be used. This register can use this memory field to write any value and verify that the data received by the device is correct. It can also be used to verify that a soft reset has been executed, using the following sequence:  1. The user writes a non-default value to register <b>SCRATCH_PAD</b> 2. The user reads back register <b>SCRATCH_PAD</b> to verify the writ commend has |  |  |  |  |  |  |

|                                   | been correctly executed  The user writes register SCRATCH_PAD to verify the writ commend has been correctly executed  The user writes register SCRATCH_PAD to verify that it has been reset to its default value                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| VDD5V verification                | At power-up and the beginning of each measurement sequence, the device automatically measures the voltage at <b>VDD5</b> . If the measured voltage exceeds the specified operating range of the device, bit <b>SENS_STS.ORVS</b> is set. The measurement sequence is, however, completed normally. Bit <b>SENS_STS.ORVS</b> can be cleared by setting bit <b>SENS_STS.ORVS_CLR</b>                                                                                                                                 |  |  |  |  |  |  |

| Internal temperature verification | At the beginning of each measurement sequence, the device automatically measures its internal temperature. If the measured temperature exceeds the specified operating ranged of the device, sticky bit SENS_STS.ORTMP is set. The measurement sequence is, however, completed normally. Bit SENS_STS.ORTMP can be cleared by setting bit SENS_STS.ORTMP_CLR                                                                                                                                                       |  |  |  |  |  |  |

#### **Datasheet**

5 Register map

# 5 Register map

# 5.1 Register map access method

The registers that can be accessed by the user's application via the communication interfaces are covered here. Registers need to be addressed byte-wise.

Table 12 Bit access terminology

| Mode                                     | Symbol | Description                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read/Write                               | rw     | This bit or bitfield can be written or read                                                                                                                                                                                                                                                                                                                                                                    |

| Read                                     | r      | This bit or bitfield is read-only                                                                                                                                                                                                                                                                                                                                                                              |

| Write                                    | w      | This bit or bitfield is write-only (read as 0 <sub>H</sub> )                                                                                                                                                                                                                                                                                                                                                   |

| Read/Write hardware or firmware affected | rwh    | As rw, but bit or bitfield can also be modified by hardware or firmware                                                                                                                                                                                                                                                                                                                                        |

| Read hardware or firmware affected       | rh     | As r, but bit or bitfield can also be modified by hardware or firmware                                                                                                                                                                                                                                                                                                                                         |

| Sticky                                   | S      | Bits with this attribute are "sticky" in one direction. If their reset value is overwritten once they can be switched again into their reset state only by a reset operation. Software and internal logic (except reset-like functions) cannot switch this type of bit into its reset state by writing directly to the register. The sticky attribute can be combined with other functions (for example, "rh") |

| Reserved/not implemented                 | 0      | Bitfields named "0" indicate functions not implemented. They have the following behavior:  Reading these bitfields returns 0 <sub>H</sub> Writing these bitfields has no effect These bitfields are reserved. When writing, software should always set such bitfields to 0 <sub>H</sub> to preserve compatibility with future products                                                                         |

| Reserved/not defined                     | Res    | Certain bitfields or bit combinations in a bitfield can be marked as "Reserved", indicating that the behavior of the device is undefined for that combination of bits. Setting the register to such an undefined value may lead to unpredictable results. When writing, the software must always set such bitfields to legal values                                                                            |

#### **Datasheet**

5 Register map

# 5.2 Register map bitfields

#### Table 13 Register map

| Name            |         |          |                |               |              |                     |               |                 |               |       |  |

|-----------------|---------|----------|----------------|---------------|--------------|---------------------|---------------|-----------------|---------------|-------|--|

| ivaille         | Address | 7        | 6              | 5             | 4            | 3                   | 2             | 1               | 0             | Reset |  |

| PROD_ID         | 0x00    | PROD     | PROD           |               |              | REV                 |               |                 |               |       |  |

| SENS_ST<br>S    | 0x01    | SEN_RDY  | PWM_DI<br>S_ST | ORTMP         | ORVS         | ICCER               | ORTMP_<br>CLR | ORVS_CL<br>R    | ICCER_C<br>LR | 0xC0  |  |

| MEAS_RA<br>TE_H | 0x02    | 0        |                |               |              | VAL                 |               |                 |               | 0x00  |  |

| MEAS_RA<br>TE_L | 0x03    | VAL      |                |               |              |                     |               |                 |               | 0x3C  |  |

| MEAS_CF<br>G    | 0x04    | Reserved |                | PWM_O<br>UTEN | PWM_M<br>ODE | BOC_CFG             | i             | OP_MODE         | <u> </u>      | 0x24  |  |

| CO2PPM<br>_H    | 0x05    | VAL      | /AL            |               |              |                     |               |                 |               | 0x00  |  |

| CO2PPM<br>_L    | 0x06    | VAL      | VAL            |               |              |                     |               |                 |               | 0x00  |  |

| MEAS_ST<br>S    | 0x07    | 0        |                | Reserved      | DRDY         | INT_STS             | ALARM         | INT_STS<br>_CLR | ALARM_<br>CLR | 0x00  |  |

| INT_CFG         | 0x08    | 0        |                |               | INT_TYP      | INT_FUNC ALARM_ TYP |               |                 |               |       |  |

| ALARM_T<br>H_H  | 0x09    | VAL      |                |               |              |                     |               |                 |               |       |  |

| ALARM_T<br>H_L  | 0x0A    | VAL      |                |               |              |                     |               |                 |               | 0x00  |  |

| PRES_RE<br>F_H  | 0x0B    | VAL      |                |               |              |                     |               |                 |               | 0x03  |  |

| PRES_RE<br>F_L  | 0x0C    | VAL      |                |               |              |                     |               |                 |               | 0xF7  |  |

| CALIB_R<br>EF_H | 0x0D    | VAL      |                |               |              |                     |               |                 |               | 0x01  |  |

| CALIB_R<br>EF_L | 0x0E    | VAL      |                |               |              |                     |               |                 |               | 0x90  |  |

| SCRATCH<br>_PAD | 0x0F    | VAL      |                |               |              |                     |               |                 |               | 0x00  |  |

| SENS_RS         | 0x10    | SRTRG    |                |               |              |                     |               |                 |               | 0x00  |  |

#### Note:

- Registers with addresses 0x11 to 0x14 are reserved and must not be accessed. Any read or write operation to these registers will result in a communication error.

- Registers with addresses 0x15 to 0xFF are reserved and must not be accessed. Any read or write operation to these registers will result in a non-acknowledge error.

20

5 Register map

# 5.3 Product and revision ID register (PROD\_ID)

This register displays the device's product and version ID. Write accesses to this register are ignored.

PROD\_ID

Address:

Product and revision ID register

Reset value:

0x4F/0x60<sub>H</sub>

7 6 5 4 3 2 1 0

PROD

REV

| Field | Bits | Туре | Description                                                |

|-------|------|------|------------------------------------------------------------|

| PROD  | 7:5  | r    | Product ID                                                 |

|       |      |      | This bitfield indicates the product type.                  |

|       |      |      | 001 <sub>B</sub> : Reserved                                |

|       |      |      | 010 <sub>B</sub> : PASCO2V01                               |

|       |      |      | 011 <sub>B</sub> : PASCO2V15                               |

| REV   | 4:0  | r    | Revision ID                                                |

|       |      |      | This bitfield indicates the product and firmware revision. |

|       |      |      | 0001 <sub>B</sub> : Revision 1.                            |

|       |      |      | 0010 <sub>B</sub> : Revision 2.                            |

|       |      |      | 0011 <sub>B</sub> : Revision 3.                            |

|       |      |      |                                                            |

# 5.4 Sensor status register (SENS\_STS)

This register displays and controls the status of the sensor. Write accesses to the read-only bits of this register are ignored.

SENS\_STS Address:  $0x01_H$  Sensor status register Reset value:  $0xC0_H$

| 7       | 6              | 5     | 4    | 3     | 2         | 1        | 0         |

|---------|----------------|-------|------|-------|-----------|----------|-----------|

| SEN_RDY | PWM_DIS_S<br>T | ORTMP | ORVS | ICCER | ORTMP_CLR | ORVS_CLR | ICCER_CLR |

| rh      | rh             | rhe   | rhc  | rhe   | W         | 14/      | 14/       |

| Field   | Bits | Туре | Description                                                                                               |

|---------|------|------|-----------------------------------------------------------------------------------------------------------|

| SEN_RDY | 7    | rh   | Sensor ready bit                                                                                          |

|         |      |      | This bit indicates if the initialization of the sensor after power-on reset has been performed correctly. |

|         |      |      | 0 <sub>B</sub> : The sensor has not been initialized correctly.                                           |

|         |      |      | 1 <sub>B</sub> : The sensor has been initialized correctly.                                               |

(table continues...)

### **Datasheet**

# (continued)

| Field      | Bits | Туре | Description                                                                                                           |

|------------|------|------|-----------------------------------------------------------------------------------------------------------------------|

| PWM_DIS_ST | 6    | rh   | PWM_DIS pin status                                                                                                    |

|            |      |      | This bit indicates the level read at pin <b>PWM_DIS</b> .                                                             |

|            |      |      | 0 <sub>B</sub> : A low level is read at pin <b>PWM_DIS</b> .                                                          |

|            |      |      | 1 <sub>B</sub> : A high level is read at pin <b>PWM_DIS</b> .                                                         |

|            |      |      | <b>Note</b> : This bit is updated at every transition at pin <b>PWM_DIS</b> .                                         |

| ORTMP      | 5    | rhs  | Out-of-range temperature error bit (sticky bit)                                                                       |

|            |      |      | This bit indicates if a condition where the temperature has been outside the specified valid range has been detected. |

|            |      |      | 0 <sub>B</sub> : No error has occurred.                                                                               |

|            |      |      | 1 <sub>B</sub> : An error has occurred.                                                                               |

|            |      |      | This bit is cleared by setting <b>SENS_STS.ORTMP_CLR</b> .                                                            |

| ORVS       | 4    | rhs  | Out-of-range VDD5V error bit (sticky bit)                                                                             |

|            |      |      | This bit indicates if a condition where VDD5V has been outside the specified valid range has been detected.           |

|            |      |      | 0 <sub>B</sub> : No error has occurred.                                                                               |

|            |      |      | 1 <sub>B</sub> : An error has occurred.                                                                               |

|            |      |      | This bit is cleared by setting bit <b>SENS_STS.ORVS_CLR</b> .                                                         |

| ICCER      | 3    | rhs  | Communication error notification bit (sticky bit)                                                                     |

|            |      |      | This bit indicates if a non-valid command has been received by the serial communication interface.                    |

|            |      |      | 0 <sub>B</sub> : No invalid command received.                                                                         |

|            |      |      | 1 <sub>B</sub> : An invalid command has been received.                                                                |

|            |      |      | This bit is cleared by setting <b>SENS_STS.ICCER_CLR</b> .                                                            |

| ORTMP_CLR  | 2    | w    | Out-of-range temperature error clear bit Writing this bit with $1_{\mathrm{B}}$ clears the sticky bit SENS_STS.ORTMP. |

|            |      |      | This bit is read back as 0 <sub>B</sub> .                                                                             |

| ORVS_CLR   | 1    | w    | Out-of-range VDD5V error clear bit                                                                                    |

|            |      |      | Writing this bit with $1_B$ clears the sticky bit <b>SENS_STS.ORVS</b> .                                              |

|            |      |      | This bit is read back as 0 <sub>B</sub> .                                                                             |

| ICCER_CLR  | 0    | w    | Communication error clear bit                                                                                         |

|            |      |      | Writing this bit with $1_B$ clears the sticky bit <b>SENS_STS.ICCER</b> .                                             |

|            |      |      | This bit is read back as 0 <sub>B</sub> .                                                                             |

5 Register map

## 5.5 Measurement period configuration registers (MEAS\_RATE\_H)

Registers **MEAS\_RATE\_H** and **MEAS\_RATE\_L** define the measurement period used in continuous mode. The concatenation of **MEAS\_RATE\_H** (MSB) and **MEAS\_RATE\_L** (LSB) define the period. The concatenated value is coded as a two's complement signed short integer (1 bit = 1 s).

Values above  $0FFF_H$  are treated as being equal to  $FFF_H$  (4095 s). Values below  $0005_H$  are treated as being equal to  $0005_H$  (5 s). Writing a non-valid value to this field generates a communication error (bit **SENS STS.ICCER** set).

Note:

When writing to **MEAS\_RATE\_H** and **MEAS\_RATE\_L**, the new value is not immediately considered by the device. It is internally latched at the next transition from idle to continuous mode.

| MEAS_RATE_H |                 |                  |   | Address:    |   |   | 0x02 <sub>H</sub> |  |

|-------------|-----------------|------------------|---|-------------|---|---|-------------------|--|

| Measurement | period configur | ration registers | R | eset value: |   |   | 0x00 <sub>H</sub> |  |

| 7           | 6               | 5                | 4 | 3           | 2 | 1 | 0                 |  |

|             | C               | )                |   | VAL         |   |   |                   |  |

|             | rv              | N                |   | rwh         |   |   |                   |  |

| Field | Bits | Type | Description                                                                                                              |                  |  |  |  |  |

|-------|------|------|--------------------------------------------------------------------------------------------------------------------------|------------------|--|--|--|--|

| 0     | 7:4  | rw   | Reserved                                                                                                                 |                  |  |  |  |  |

|       |      |      | This bitfield shall be written with 0 <sub>H</sub> .                                                                     |                  |  |  |  |  |

| VAL   | 3:0  | rwh  | MSB of the measurement period in continuo                                                                                | ous mode         |  |  |  |  |

|       |      |      | The concatenation of this value with bitfield <b>M</b> the measurement period in continuous mode.                        |                  |  |  |  |  |

|       |      |      | Note: Values above 0F <sub>H</sub> reserved. Writing to this field generates a communic SENS_STS.ICCER set) and sets the | ation error (bit |  |  |  |  |

# 5.6 Measurement period configuration registers (MEAS\_RATE\_L)

Registers **MEAS\_RATE\_H** and **MEAS\_RATE\_L** define the measurement period used in continuous mode. The concatenation of **MEAS\_RATE\_H** (MSB) and **MEAS\_RATE\_L** (LSB) define the period. The concatenated value is coded as a two's complement signed short integer (1 bit = 1 s).

Values above  $0FFF_H$  are treated as being equal to  $FFF_H$  (4095 s). Values below  $0005_H$  are treated as being equal to  $0005_H$  (5 s). Writing a non-valid value to this field generates a communication error (bit **SENS\_STS.ICCER** set).

**Note**: When writing to **MEAS\_RATE\_H** and **MEAS\_RATE\_L**, the new value is not immediately considered by the device. It is internally latched at the next transition from idle to continuous mode.

| MEAS_RATE_L | -              |                  |   | Address:         |   |     | 0x03 <sub>H</sub> |  |

|-------------|----------------|------------------|---|------------------|---|-----|-------------------|--|

| Measurement | period configu | ration registers | R | Reset value: 0x3 |   | 2 1 |                   |  |

| 7           | 6              | 5                | 4 | 3                | 2 | 1   | 0                 |  |

|             |                |                  | V | AL               |   |     |                   |  |

rwh

#### **Datasheet**

| Field | Bits | Туре | Descript | ion                                                                                                                                                                                                        |

|-------|------|------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VAL   | 7:0  | rwh  | The cond | ne measurement period in continuous mode catenation of this value with bitfield MEAS_RATE_H.VAL he measurement period in continuous mode.                                                                  |

|       |      |      | Note:    | Values 00 <sub>H</sub> to 04 <sub>H</sub> are reserved. Writing a non-valid value to this field generates a communication error (bit <b>SENS_STS.ICCER</b> set) and sets the bitfield to 05 <sub>H</sub> . |

# 5.7 Measurement mode configuration register (MEAS\_CFG)

This register defines the operation settings of the device.

MEAS\_CFG Address: 0x04<sub>H</sub>

Measurement mode configuration register Reset value: 0x24<sub>H</sub>

| 7   | 6 | 5             | 4        | 3    | 2   | 1   | 0    |  |

|-----|---|---------------|----------|------|-----|-----|------|--|

| Res |   | PWM_OUTE<br>N | PWM_MODE | вос_ | CFG | OP_ | MODE |  |

| rwh |   | rwh           | rw       | rwh  | 1   | r   | wh   |  |

| Field     | Bits | Туре | Description                                                                                 |

|-----------|------|------|---------------------------------------------------------------------------------------------|

| Res       | 7:6  | rwh  | Reserved                                                                                    |

|           |      |      | This bitfield shall be written with $00_B$ .                                                |

| PWM_OUTEN | 5    | rwh  | PWM output software enable bit                                                              |

|           |      |      | 0 <sub>B</sub> : <b>PWM</b> output is disabled by software.                                 |

|           |      |      | 1 <sub>B</sub> : <b>PWM</b> output is enabled by software.                                  |

|           |      |      | Notes:                                                                                      |

|           |      |      | 1. The actual state of pin <b>PWM</b> depends on both                                       |

|           |      |      | MEAS_CFG.PWM_OUTEN and pin PWM_DIS.                                                         |

|           |      |      | <b>2.</b> This bit is automatically set at a high to low transition at pin <b>PWM_DIS</b> . |

| PWM_MODE  | 4    | rw   | PWM mode configuration                                                                      |

|           |      |      | 0 <sub>B</sub> : PWM single-pulse mode.                                                     |

|           |      |      | 1 <sub>B</sub> : PWM pulse-train mode.                                                      |

(table continues...)

#### **Datasheet**

5 Register map

#### (continued)

| Field   | Bits | Туре | Description                                                                                                                                                        |

|---------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BOC_CFG | 3:2  | rwh  | Baseline offset compensation configuration                                                                                                                         |

|         |      |      | 00 <sub>B</sub> : Automatic baseline offset compensation (ABOC) disabled.                                                                                          |

|         |      |      | $01_{\rm B}$ : ABOC enabled. The offset is periodically updated at each BOC computation.                                                                           |

|         |      |      | <b>Note</b> : With firmware version 2.18 an extended ABOC functionality has been introduced, including support for single shot mode.                               |

|         |      |      | 10 <sub>B</sub> : Forced compensation.                                                                                                                             |

|         |      |      | <b>Note</b> : After the forced compensation is done, device automatically reconfigures itself into ABOC (MEAS_CFG.BOC_CFG = $01_B$ ).                              |

|         |      |      | 11 <sub>B</sub> : Reserved.                                                                                                                                        |

| OP_MODE | 1:0  | rwh  | Sensor operating mode                                                                                                                                              |

|         |      |      | 00 <sub>B</sub> : Idle mode.                                                                                                                                       |

|         |      |      | $01_{\rm B}$ : Single-shot mode enabled. Writing $01_{\rm B}$ to this field triggers a single measurement sequence. This field is reset by firmware automatically. |

|         |      |      | 10 <sub>B</sub> : Continuous mode enabled.                                                                                                                         |

|         |      |      | 11 <sub>B</sub> : Reserved (as 00 <sub>B</sub> ).                                                                                                                  |

# 5.8 CO<sub>2</sub> concentration result register (CO2PPM\_H)

Registers  $CO2PPM_H$  and  $CO2PPM_L$  are used to display the result of the last  $CO_2$  concentration measurement. The concatenation of  $CO2PPM_H$  (MSB) and  $CO2PPM_L$  (LSB) define the  $CO_2$  concentration value. The concatenated  $CO_2$  concentration value is coded as a two's complement signed short integer (1 bit = 1 ppm). This field is updated at the end of each measurement sequence.

Reading register CO2PPM\_L clears bit MEAS\_STS.DRDY.

When reading the CO<sub>2</sub> concentration value, the user shall first read registers CO2PPM\_H and then CO2PPM\_L.

| CO2PPM_H                  |                   |      |    | Address:    |   |   | 0x05 <sub>H</sub> |

|---------------------------|-------------------|------|----|-------------|---|---|-------------------|

| CO <sub>2</sub> concentra | ition result regi | ster | R  | eset value: |   |   | 0x00 <sub>H</sub> |

| 7                         | 6                 | 5    | 4  | 3           | 2 | 1 | 0                 |

|                           |                   |      | VA | <b>\L</b>   |   |   |                   |

rh

| Field | Bits | Туре | Description                                                                                                     |

|-------|------|------|-----------------------------------------------------------------------------------------------------------------|

| VAL   | 7:0  | rh   | MSB of the CO <sub>2</sub> concentration value                                                                  |

|       |      |      | The concatenation of this value with bitfield ${\bf CO2PPM\_L.VAL}$ gives the ${\bf CO_2}$ concentration value. |

5 Register map

# 5.9 CO<sub>2</sub> concentration result register (CO2PPM\_L)

Registers  $CO2PPM_H$  and  $CO2PPM_L$  are used to display the result of the last  $CO_2$  concentration measurement. The concatenation of  $CO2PPM_H$  (MSB) and  $CO2PPM_L$  (LSB) define the  $CO_2$  concentration value. The concatenated  $CO_2$  concentration value is coded as a two's complement signed short integer (1 bit = 1 ppm). This field is updated at the end of each measurement sequence.

Reading register CO2PPM\_L clears bit MEAS\_STS.DRDY.

When reading the CO<sub>2</sub> concentration value, the user shall first read registers CO2PPM\_H and then CO2PPM\_L.

| CO2    | PPM_L      |                  |      |   | Address:    |   |   | 0x06 <sub>H</sub> |

|--------|------------|------------------|------|---|-------------|---|---|-------------------|

| $CO_2$ | concentrat | tion result regi | ster | R | eset value: |   |   | 0x00 <sub>H</sub> |

|        | 7          | 6                | 5    | 4 | 3           | 2 | 1 | 0                 |

|        |            |                  |      | V | AL          |   |   |                   |

|        |            |                  |      | r | h           |   |   |                   |

| Field | Bits | Туре | Description                                                                                                     |

|-------|------|------|-----------------------------------------------------------------------------------------------------------------|

| VAL   | 7:0  | rh   | LSB of the CO <sub>2</sub> concentration value                                                                  |

|       |      |      | The concatenation of this value with bitfield ${\bf CO2PPM\_H.VAL}$ gives the ${\bf CO_2}$ concentration value. |

|       |      |      | Reading this bitfield clears bit MEAS_STS.DRDY.                                                                 |

# 5.10 Measurement status register (MEAS\_STS)

This register displays the status information of the sensor. Write accesses to the read-only bits of this register are ignored.

| N | MEAS_STS      |                 |     |      | Address:     |       |                 | 0x07 <sub>H</sub> |

|---|---------------|-----------------|-----|------|--------------|-------|-----------------|-------------------|

| N | Measurement s | status register |     | F    | Reset value: |       |                 | 0x00 <sub>H</sub> |

| _ | 7             | 6               | 5   | 4    | 3            | 2     | 1               | 0                 |

|   | 0             |                 | Res | DRDY | INT_STS      | ALARM | INT_STS_CL<br>R | ALARM_CLR         |

|   | rw            | ı               | rh  | rhs  | rhs          | rhs   | W               | w                 |

| Field | Bits | Туре | Description                                                                                           |

|-------|------|------|-------------------------------------------------------------------------------------------------------|

| 0     | 7:6  | rw   | Reserved                                                                                              |

|       |      |      | This bitfield is read as 00 <sub>B</sub> .                                                            |

| Res   | 5    | rh   | Reserved                                                                                              |

|       |      |      | This bit is reserved.                                                                                 |

| DRDY  | 4    | rhs  | Data ready bit (sticky bit)                                                                           |

|       |      |      | This bit indicates if new data are available in register <b>CO2PPM_H</b> and <b>CO2PPM_L</b> .        |

|       |      |      | 0 <sub>B</sub> : No new data are available.                                                           |

|       |      |      | 1 <sub>B</sub> : Unread data are available. This bit is set at the end of every measurement sequence. |

|       |      |      | This bit is cleared by reading CO2PPM_L.                                                              |

#### **Datasheet**

5 Register map

#### (continued)

| Field       | Bits | Type | Description                                                                                                                                                 |

|-------------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INT_STS     | 3    | rhs  | INT pin status bit                                                                                                                                          |

|             |      |      | This bit indicates if pin <b>INT</b> has been latched to active state (in case of alarm or data ready).                                                     |

|             |      |      | 0 <sub>B</sub> : Pin <b>INT</b> has not been latched to active state.                                                                                       |

|             |      |      | 1 <sub>B</sub> : Pin <b>INT</b> has been latched to active state. This bit is set at the end of every measurement sequence in case of a latching condition. |

|             |      |      | This bit is cleared by setting bit <b>MEAS_STS.INT_STS_CLR</b> .                                                                                            |

| ALARM       | 2    | rhs  | Alarm notification (sticky bit)                                                                                                                             |

|             |      |      | This bit indicates if a threshold violation occurred.                                                                                                       |

|             |      |      | 0 <sub>B</sub> : No violation occurred.                                                                                                                     |

|             |      |      | 1 <sub>B</sub> : Violation occurred. This bit is set at the end of every measurement sequence in case of violation.                                         |

|             |      |      | This bit is cleared by setting bit MEAS_STS.ALARM_CLR.                                                                                                      |

| INT_STS_CLR | 1    | w    | INT pin status clear bit                                                                                                                                    |

|             |      |      | Writing this bit with $1_{B}$ clears the sticky bit <b>MEAS_STS.INT_STS</b> and forces pin <b>INT</b> to inactive level.                                    |

|             |      |      | This bit is read back as 0 <sub>B</sub> .                                                                                                                   |

| ALARM_CLR   | 0    | w    | Alarm notification clear bit                                                                                                                                |

|             |      |      | Writing this bit with $1_B$ clears the sticky bit <b>MEAS_STS.ALARM</b> .                                                                                   |

|             |      |      | This bit is read back as 0 <sub>B</sub> .                                                                                                                   |

# 5.11 Interrupt pin configuration register (INT\_CFG)

This register defines the configuration of pin **INT**.

INT\_CFG

Interrupt pin configuration register

Reset value:

7

6

5

4

3

2

1

0

INT\_TYP

INT\_FUNC

ALARM\_TYP

rw

rw

rw

| Bits | Type | Description                                                                  |  |  |  |  |

|------|------|------------------------------------------------------------------------------|--|--|--|--|

| 7:5  | rw   | Reserved                                                                     |  |  |  |  |

|      |      | This bitfield shall be written with 00 <sub>B</sub> .                        |  |  |  |  |

| 4    | rw   | Pin INT electrical configuration                                             |  |  |  |  |

|      |      | 0 <sub>B</sub> : Pin <b>INT</b> is configured as push-pull and low active.   |  |  |  |  |

|      |      | 1 <sub>B</sub> : Pin <b>INT</b> is configured as push-pull and high active.  |  |  |  |  |

|      |      | <b>Note</b> : Writing this bitfield forces pin <b>INT</b> to inactive state. |  |  |  |  |

|      | 7:5  | 7:5 rw                                                                       |  |  |  |  |

(table continues...)

#### **Datasheet**

5 Register map

#### (continued)

| Field     | Bits | Type | Description                                                                                                                                                                                                    |

|-----------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INT_FUNC  | 3:1  | rw   | Pin INT function configuration                                                                                                                                                                                 |

|           |      |      | 000 <sub>B</sub> : Pin <b>INT</b> is inactive.                                                                                                                                                                 |

|           |      |      | $001_{\rm B}$ : Pin <b>INT</b> is configured as alarm threshold violation notification pin.                                                                                                                    |

|           |      |      | 010 <sub>B</sub> : Pin <b>INT</b> is configured as data ready notification pin.                                                                                                                                |

|           |      |      | 011 <sub>B</sub> : Pin <b>INT</b> is configured as sensor busy notification pin.                                                                                                                               |

|           |      |      | $100_B$ : Pin <b>INT</b> is configured as early measurement start notification pin (this function only is available in continuous mode with <b>MEAS_CFG.OP_MODE</b> = $10_B$ , otherwise the pin is inactive). |

|           |      |      | 101 <sub>B</sub> : Reserved                                                                                                                                                                                    |

|           |      |      |                                                                                                                                                                                                                |

|           |      |      | 111 <sub>B</sub> : Reserved                                                                                                                                                                                    |

| ALARM_TYP | 0    | rw   | Alarm type configuration bit                                                                                                                                                                                   |