### **Description**

The P9225-R is a high-efficiency wireless power receiver (Rx) capable of operating in both WPC and PMA protocols. Using magnetic inductive charging technology, the receiver converts an AC power signal from a resonant tank into a regulated DC output voltage ranging from 4.5V to 5.5V. The integrated, low RDS<sub>ON</sub> synchronous rectifier and ultra-low dropout linear (LDO) regulator offers high efficiency making the product ideally suited for battery-operated applications.

The P9225-R includes an industry-leading 32-bit ARM® Cortex®-M0 microprocessor offering a high level of programmability. The P9225-R also features a programmable current limit and a patented over-voltage protection function eliminating the need for additional capacitors generally used by the receivers minimizing the external component count and cost. Together with the P9038-R transmitter ( $T_X$ ), the P9225-R is a complete wireless power system solution for power applications up to 5W.

The P9225-R is available in a 52-WLCSP package, and it is rated for 0°C to 85°C ambient operating temperature range.

## **Typical Applications**

- Headsets, tablets

- Digital cameras

- Portable media player

- Accessories

- Medical

#### **Features**

- Single-chip solution supporting up to 5W applications

- WPC-1.2.4 compliant, PMA SR1 compatible

- Patented over-voltage protection clamp eliminating external capacitors

- 82% peak DC-to-DC efficiency with P9038-R Tx

- Fully integrated synchronous rectifier with low RDS(ON) switches

- Programmable output voltage: 4.5V to 5.5V

- Embedded 32-bit ARM® Cortex®-M0 processor

- Dedicated remote temperature sensing

- Programmable current limit

- Active-low enable pin for electrical on/off

- Active-high End-of-Charge input pin

- Open-drain interrupt flag

- Support for I2C interface

- 0°C to +85°C ambient operating temperature range

- 52-WLCSP (2.64 × 3.94 mm; 0.4mm pitch)

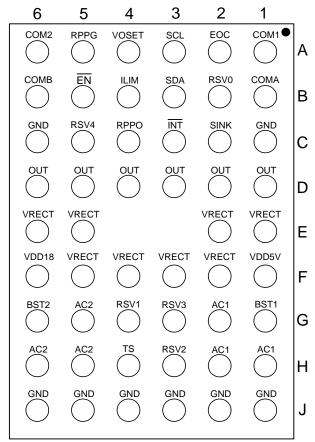

## **Typical Application Circuit**

## **Contents**

| <ul><li>2.</li><li>3.</li></ul> | Pin Descriptions                                                       |    |

|---------------------------------|------------------------------------------------------------------------|----|

|                                 | ŭ                                                                      | ρ  |

|                                 | Thermal Characteristics                                                |    |

| 4.                              | Thermal Characteristics                                                | 9  |

| 5.                              | Electrical Characteristics                                             | 9  |

| 6.                              | Typical Performance Characteristics                                    | 12 |

| 7.                              | Functional Block Diagram                                               | 15 |

| 8.                              | Theory of Operation                                                    | 16 |

|                                 | 8.1 LDO – Low Dropout Regulators                                       | 16 |

|                                 | 8.2 Setting the Output Voltage – VOSET                                 | 16 |

|                                 | 8.3 SINK Pin                                                           | 17 |

|                                 | 8.4 Rectifier Voltage – VRECT                                          | 17 |

|                                 | 8.5 Over-Current Limit – ILIM                                          | 17 |

|                                 | 8.6 Interrupt Function – INT                                           | 17 |

|                                 | 8.7 Enable Pin – EN                                                    | 18 |

|                                 | 8.8 Thermal Protection                                                 | 18 |

|                                 | 8.9 External Temperature Sensing – TS                                  | 18 |

|                                 | 8.10 End of Charge – EOC                                               | 18 |

|                                 | 8.11 Received Power Packet Offset and Gain Calibration – RPPO and RPPG | 18 |

|                                 | 8.12 Advanced Foreign Object Detection (FOD)                           | 19 |

| 9.                              | Communication Interface                                                | 20 |

|                                 | 9.1 Modulation/Communication                                           | 20 |

|                                 | 9.2 Byte Encoding for ASK                                              | 20 |

|                                 | 9.3 Packet Structure                                                   | 20 |

| 10.                             | WPC Mode Characteristics                                               | 21 |

|                                 | 10.1 Selection Phase or Startup                                        | 21 |

|                                 | 10.2 Ping Phase (Digital Ping)                                         | 22 |

|                                 | 10.3 Identification and Configuration Phase                            | 22 |

|                                 | 10.4 Power Transfer Phase                                              | 22 |

| 11.                             | Functional Registers                                                   | 23 |

| 12.                             | I2C Access Description                                                 | 28 |

| 13.                             | Application Information                                                | 29 |

|                                 | 13.1 Power Dissipation and Thermal Requirements                        | 29 |

|                                 | 13.2 Recommended Coils                                                 | 30 |

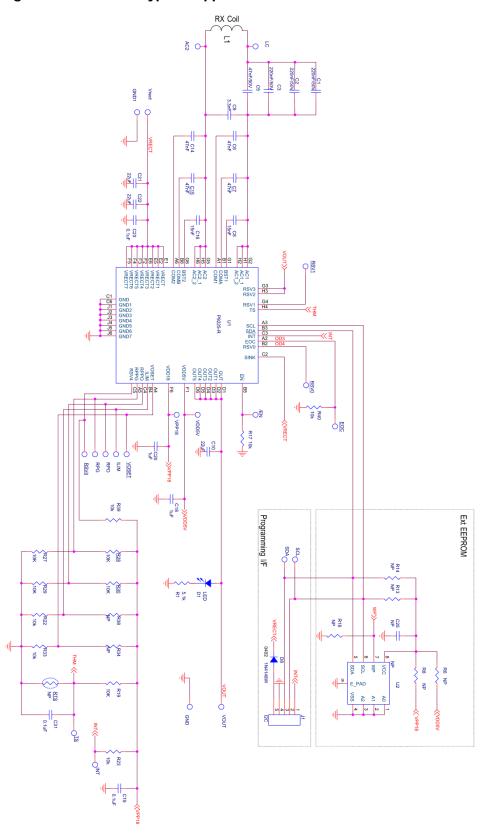

|                                 | 13.3 Typical Application Schematic                                     | 31 |

|                                 | 13.4 Bill of Materials (BOM)                                           | 32 |

| 14.                             | Package Outline Drawings                                               | 33 |

| 15.                             | Special Notes: WLCSP-52 (AHG52) Package Assembly                       | 33 |

| 16. N              | Marking Diagram                                                  | 33 |

|--------------------|------------------------------------------------------------------|----|

| 17. C              | Ordering Information                                             | 33 |

| 18. F              | Revision History                                                 | 34 |

| List               | t of Figures                                                     |    |

| Figure             | 1. Pin Assignments – Bottom View                                 | 5  |

| Figure             | 2. Efficiency vs Output Load: V <sub>OUT</sub> = 5.5V            | 12 |

| Figure             | 3. V <sub>OUT</sub> vs Output Load: V <sub>OUT</sub> = 5.5V      | 12 |

| Figure             | 4. Efficiency vs Output Load: V <sub>OUT</sub> = 5V              | 12 |

| Figure             | 5. V <sub>OUT</sub> vs Output Load: V <sub>OUT</sub> = 5V        | 12 |

| Figure             | 6. Efficiency vs Output Load: V <sub>OUT</sub> = 4.5V            | 12 |

| Figure             | 7. V <sub>OUT</sub> vs Output Load: V <sub>OUT</sub> = 4.5V      | 12 |

| Figure             | 8. Rectified Voltage vs Output Load                              | 13 |

| Figure             | 9. Load Transient: V <sub>OUT</sub> = 5.5V, 0A → 1.2A            | 13 |

| Figure             | 10. Load Transient: V <sub>OUT</sub> = 5.5V, 1.2A → 0A           | 13 |

| Figure             | 11. Load Transient: V <sub>OUT</sub> = 5V, 0A → 1.2A             | 13 |

| Figure             | 12. Load Transient: V <sub>OUT</sub> = 5V, 1.2A → 0A             | 13 |

| Figure             | 13. Load Transient: V <sub>OUT</sub> = 4.5V, 0A → 1.2A           | 14 |

| Figure             | 14. Load Transient: V <sub>OUT</sub> = 4.5V, 1.2A → 0A           | 14 |

| Figure             | 15. Functional Block Diagram                                     | 15 |

| Figure             | 16. Bit Encoding Scheme                                          | 20 |

| Figure             | 17. Byte Encoding Scheme                                         | 20 |

| Figure             | 18. Communication Packet Structure                               | 20 |

| Figure             | 19. State Diagram for WPC Baseline Power Profile (BPP) Operation | 21 |

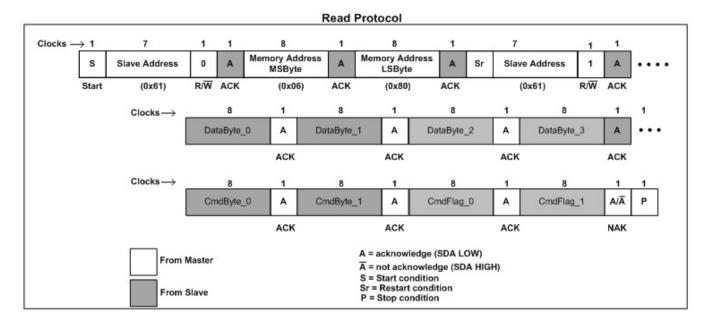

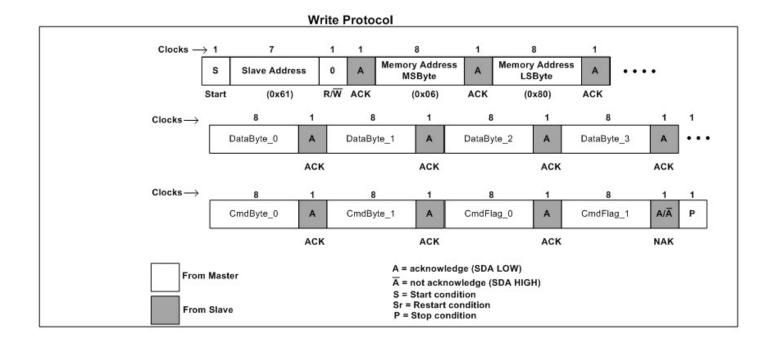

| -                  | 20. I2C Access Read Protocol                                     |    |

| Figure             | 21. I2C Access Write Protocol                                    | 28 |

| Figure             | 22. P9225-R Typical Application Schematic                        | 31 |

| List               | t of Tables                                                      |    |

| Table '            | 1. Pin Descriptions                                              | 6  |

| Table 2            | 2. Absolute Maximum Ratings                                      | 8  |

| Table 3            | 3. ESD Information                                               | 8  |

| Table 4            | 4. Package Thermal Information                                   | 9  |

| Table !            | 5. Electrical Characteristics                                    | 9  |

| Table (            | 6. Setting the Output Voltage                                    | 16 |

| Table              | 7. Setting the Current Limit                                     | 17 |

| Table 8            |                                                                  |    |

| Table <sup>4</sup> | 9. Device Identification Register                                | 23 |

| Table 1            | 10. Firmware Major Revision                                      |    |

|                    | ·                                                                |    |

| Table 11. | Firmware Minor Revision                          | 23 |

|-----------|--------------------------------------------------|----|

| Table 12. | Status Registers                                 | 23 |

| Table 13. | Interrupt Status Registers                       | 24 |

| Table 14. | Interrupt Enable Registers                       | 24 |

| Table 15. | Battery Charge Status                            | 25 |

|           | End Power Transfer                               |    |

| Table 17. | Read Register – Output Voltage                   | 25 |

| Table 18. | Read Register – VRECT Voltage                    | 25 |

|           | Read Register – I <sub>OUT</sub> Current         |    |

| Table 20. | Read Register – Die Temperature                  | 26 |

| Table 21. | Read Register – Operating Frequency              | 26 |

| Table 22. | Command Register                                 | 26 |

| Table 23. | Clear Interrupt Bits                             | 27 |

| Table 24. | WPC Power Transfer Phase Indicator Register      | 27 |

| Table 25. | Recommended Coil Manufacturers                   | 30 |

| Table 26. | P9225-R MM Evaluation Kit V1.0 Bill of Materials | 32 |

|           |                                                  |    |

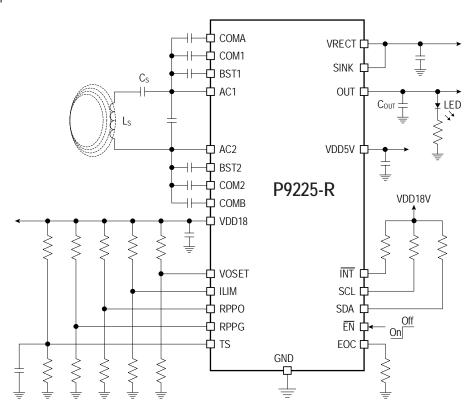

## 1. Pin Assignments

Figure 1. Pin Assignments - Bottom View

**Bottom View**

# 2. Pin Descriptions

Table 1. Pin Descriptions

| Pins                              | Name  | Туре         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------|-------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1                                | COM1  | Output       | Open-drain output used to communicate with the transmitter. Connect a 47nF capacitor from AC1 to COM1.                                                                                                                                                                                                                                                                                                                                                                                                  |

| A2                                | EOC   | Input        | Active-HIGH End-of-Charge input pin. When connected to logic HIGH, the device sends an End Power Transfer (i.e., charge complete) packet to the transmitter to terminate power delivery and shuts down. Use a $10k\Omega$ resistor to GND to pull this pin down to logic LOW by default.                                                                                                                                                                                                                |

| А3                                | SCL   | Input        | Serial clock line. Open-drain pin. Connect this pin to a $5.1  k\Omega$ resistor to VDD18 pin if I2C access by external AP is used. Otherwise, this pin can be left floating.                                                                                                                                                                                                                                                                                                                           |

| A4                                | VOSET | Input        | Programming pin for setting the output voltage. Connect this pin to the center tap of the external resistor divider to set the output voltage. For more information, refer to section 8.2 for different output voltage settings.                                                                                                                                                                                                                                                                        |

| A5                                | RPPG  | Input        | Received Power Packet Gain (RPPG) calibration pin for foreign object detection (FOD) tuning. Connect this pin to the center tap of the external resistor divider to set the gain of the FOD. The FOD is disabled by connecting RPPG and RPPO to GND. Do not leave this pin floating.                                                                                                                                                                                                                    |

| A6                                | COM2  | Output       | Open-drain output used to communicate with the transmitter. Connect a 47nF capacitor from AC2 to COM2.                                                                                                                                                                                                                                                                                                                                                                                                  |

| B1                                | COMA  | Output       | Open-drain output used to communicate with the transmitter. Connect a 47nF capacitor from AC2 to COMA. If PMA mode is not used, this pin can be left floating.                                                                                                                                                                                                                                                                                                                                          |

| B2                                | RSV0  | -            | Reserved pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| В3                                | SDA   | Input/Output | Serial data line. Open-drain pin. Connect this pin to a $5.1\mathrm{k}\Omega$ resistor to VDD18 pin if I2C access by external AP is used. Otherwise, this pin can be left floating.                                                                                                                                                                                                                                                                                                                     |

| B4                                | ILIM  | Input        | Programmable over-current limit pin. Connect this pin to the center tap of a resistor divider to set the current limit. For more information about the current limit function, see section 8.5.                                                                                                                                                                                                                                                                                                         |

| B5                                | ĒN    | Input        | Active-LOW enable pin. Pulling this pin to logic HIGH forces the device into Shut Down Mode. When connected to logic LOW, the device is enabled. Do not leave this pin floating.                                                                                                                                                                                                                                                                                                                        |

| В6                                | COMB  | Output       | Open-drain output used to communicate with the transmitter. Connect a 47nF capacitor from AC2 to COMB. If PMA mode is not used, this pin can be left floating.                                                                                                                                                                                                                                                                                                                                          |

| C1, C6, J1, J2,<br>J3, J4, J5, J6 | GND   | GND          | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| C2                                | SINK  | Output       | Open-drain output for controlling the rectifier clamp. Short this pin to the VRECT pin.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| C3                                | ĪNT   | Output       | Interrupt flag pin. This is an open-drain output that signals fault interrupts. It is pulled LOW if any of these faults exist: an over-voltage is detected, an over-current condition is detected, the die temperature exceeds 140°C, or an external over-temperature condition is detected on the TS pin. It is also asserted LOW when $\overline{\text{EN}}$ is HIGH. Connect to VDD18 through a $10\text{k}\Omega$ resistor. See section 8.6 for additional conditions affecting the interrupt flag. |

| C4                                | RPPO  | Input        | Received Power Packet Offset (RPPO) calibration pin for FOD tuning. Connect this pin to the center tap of the external resistor divider to set the offset of the FOD. The FOD is disabled by connecting RPPG and RPPO to GND. Do not leave this pin floating.                                                                                                                                                                                                                                           |

| C5                                | RSV4  | Input        | Reserved. This pin must be connected to a 10kΩ resistor to the VDD18 pin.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Pins                              | Name  | Туре   | Function                                                                                                                                                                                                                                                     |  |

|-----------------------------------|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| D1, D2, D3,<br>D4, D5, D6         | OUT   | Output | Regulated output voltage pins. On each of these pins, connect a $22\mu F$ capacitor to GND. The default voltage is set to 5V when the VOSET pin is pulled up to VDD18 pin through a $10k\Omega$ resister. For more information about VOSET, see section 8.2. |  |

| E1, E2, E5, E6,<br>F2, F3, F4, F5 | VRECT | Output | Output voltage of the synchronous rectifier bridge. On each of these pins, connect two 22µF capacitors and a 0.1µF capacitor in parallel to GND. The rectifier voltage dynamically changes as the load changes.                                              |  |

| F1                                | VDD5V | Output | Internal 5V regulator output voltage for internal use. Connect a $1\mu F$ capacitor from this pin to ground. Do not load the pin.                                                                                                                            |  |

| F6                                | VDD18 | Output | Internal 1.8V regulator output voltage. Connect a 1µF capacitor from this pin to ground. Do not load the pin.                                                                                                                                                |  |

| G1                                | BST1  | Output | Boost capacitor for driving the high-side switch of the internal rectifier. Connect a 15nF capacitor from the AC1 pin to BST1.                                                                                                                               |  |

| G2, H1, H2                        | AC1   | Input  | AC input power. Connect these pins to the resonant capacitance C <sub>S</sub> (C1, C2, C3, and C5 in Figure 22).                                                                                                                                             |  |

| G3                                | RSV3  | -      | Reserved pin. This pin must be connected to OUT pin.                                                                                                                                                                                                         |  |

| G4                                | RSV1  | -      | Reserved pin.                                                                                                                                                                                                                                                |  |

| G5, H5, H6                        | AC2   | Input  | AC input power. Connect to the Rx coil (L1 in Figure 22).                                                                                                                                                                                                    |  |

| G6                                | BST2  | Output | Boost capacitor for driving the HIGH-side switch of the internal rectifier. Connect a 15nF capacitor from the AC2 pin to BST2.                                                                                                                               |  |

| H3                                | RSV2  | -      | Reserved pin. This pin must be connected to the OUT pin.                                                                                                                                                                                                     |  |

| H4                                | TS    | Input  | Remote temperature sensor for over-temperature shutdown. Connect to the NTC thermistor network. If not used, connect this pin to VDD18 pin through the $10k\Omega$ resistor.                                                                                 |  |

## 3. Absolute Maximum Ratings

Stresses greater than those listed as absolute maximum ratings in Table 2 could cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods might affect reliability.

Table 2. Absolute Maximum Ratings

| Symbol/Pins <sup>[a], [d]</sup>          | Parameter                    | Conditions | Minimum <sup>[b]</sup> | Maximum <sup>[b]</sup> | Units |

|------------------------------------------|------------------------------|------------|------------------------|------------------------|-------|

| AC1 [c], AC2 [c], COM1, COM2, COMA, COMB | Absolute Maximum Pin Voltage |            | -0.3                   | 20                     | V     |

| EN                                       | Absolute Maximum Pin Voltage |            | -0.3                   | 28                     | V     |

| SINK, VRECT                              | Absolute Maximum Pin Voltage |            | -0.3                   | 24                     | V     |

| ILIM, RPPG, RPPO, VDD18, VOSET           | Absolute Maximum Pin Voltage |            | -0.3                   | 2                      | V     |

| ĪNT, SCL, SDA, TS, VDD5V, EOC            | Absolute Maximum Pin Voltage |            | -0.3                   | 6                      | V     |

| BST1                                     | Absolute Maximum Pin Voltage |            | -0.3                   | AC1+6                  | V     |

| BST2                                     | Absolute Maximum Pin Voltage |            | -0.3                   | AC2+6                  | V     |

| OUT                                      | Absolute Maximum Pin Voltage |            | -0.3                   | 14.4                   | V     |

| SINK                                     | Maximum Pin Current          |            | _                      | 1                      | А     |

| COM1, COM2                               | Maximum RMS Pin Current      |            | _                      | 500                    | mA    |

| AC1, AC2                                 | Maximum RMS Pin Current      |            | _                      | 2                      | А     |

<sup>[</sup>a] Absolute maximum ratings are not provided for reserved pins (RSV0, RSV1, RSV2, RSV3, and RSV4). These pins are not used in the application.

Table 3. ESD Information

| Test Model | Test Model Pins                      |     | Units |

|------------|--------------------------------------|-----|-------|

| LIDM       | All pins except RSV0, RSV1, and RSV4 | 2   | kV    |

| HBM        | RSV2 and RSV3 pins                   | 1   | kV    |

| CDM        | All pins                             | 500 | V     |

<sup>[</sup>b] All voltages are referenced to ground unless otherwise noted.

<sup>[</sup>c] During synchronous rectifier dead time, the voltage on the AC1 and AC2 pins is developed by current across the internal power FET's body diodes, and it might be lower than -0.3 V. This is normal behavior and does not negatively impact the functionality or reliability of the product.

<sup>[</sup>d] For the test conditions for the absolute maximum ratings specifications, the P9225-R chip characterization for the operating ambient temperature (T<sub>AMB</sub>) specification has been performed down to -10°C only. Design simulation indicates normal operation down to -45°C. Limited bench functionality tests normal operation down to -40°C.

### 4. Thermal Characteristics

#### **Table 4. Package Thermal Information**

Note: This thermal rating was calculated on a JEDEC 51 standard 4-layer board with dimensions 76.2 x 114.3 mm in still-air conditions.

| Symbol            | Description                                     | WLCSP Rating 8 Thermal Balls | Units |

|-------------------|-------------------------------------------------|------------------------------|-------|

| ӨЈА               | Thermal Resistance, Junction to Ambient [a]     | 47                           | °C/W  |

| θυс               | Thermal Resistance, Junction to Case            | 0.202                        | °C/W  |

| <b>Ө</b> ЈВ       | Thermal Resistance, Junction to Board           | 4.36                         | °C/W  |

| TJ                | Operating Junction Temperature <sup>[a]</sup>   | -5 to +125                   | °C    |

| Тамв              | Ambient Operating Temperature [a]               | 0 to +85                     | °C    |

| T <sub>STOR</sub> | Storage Temperature                             | -55 to +150                  | °C    |

| Твимр             | Maximum Soldering Temperature (Reflow, Pb-Free) | 260                          | °C    |

<sup>[</sup>a] The maximum power dissipation is  $P_{D(MAX)} = (T_{J(MAX)} - T_{AMB}) / \theta_{JA}$  where  $T_{J(MAX)}$  is 125°C. Exceeding the maximum allowable power dissipation will result in excessive die temperature, and the device will enter thermal shutdown.

### 5. Electrical Characteristics

#### Table 5. Electrical Characteristics

Note: Unless otherwise noted, VRECT = 5.5V;  $C_{OUT}$  = 4.7 $\mu$ F;  $\overline{EN}$  = LOW; and  $T_J$  = 0°C to 125°C. Typical values are at 25°C.

Note: See important table notes at the end of this table.

| Symbol               | Description                   | Conditions                                   | Minimum | Typical | Maximum | Units |  |  |

|----------------------|-------------------------------|----------------------------------------------|---------|---------|---------|-------|--|--|

| Under-Voltage Lo     | Under-Voltage Lock-Out (UVLO) |                                              |         |         |         |       |  |  |

| Vuvlo_Rising         | UVLO Rising                   | Rising voltage on VRECT                      |         | 2.9     | 2.98    | V     |  |  |

| Vuvlo_HYS            | UVLO Hysteresis               | VRECT falling                                |         | 200     |         | mV    |  |  |

| Over-Voltage Pro     | tection                       |                                              |         |         |         |       |  |  |

| V <sub>OVP-DC</sub>  | DC Over-Voltage Protection    | Rising voltage on VRECT                      |         | 12      |         | V     |  |  |

| V <sub>OVP-HYS</sub> | Over-Voltage Hysteresis       |                                              |         | 1       |         | V     |  |  |

| Quiescent Curre      | nt                            |                                              |         |         |         |       |  |  |

| lactive_suply        | Supply Current                | EN = LOW, No load; VRECT = 5.5V              |         | 3.0     |         | mA    |  |  |

| I <sub>SHD</sub>     | Shut Down Mode Current        | EN = HIGH, VRECT = 5.5V                      |         | 500     |         | μΑ    |  |  |

| VDD18 Voltage        | VDD18 Voltage                 |                                              |         |         |         |       |  |  |

| V <sub>VDD18</sub>   | VDD18 Pin Output Voltage [a]  | $I_{VDD18} = 10$ mA, $C_{VDD18} = 1$ $\mu$ F | 1.62    | 1.8     | 1.98    | V     |  |  |

| VDD5V Voltage        | VDD5V Voltage                 |                                              |         |         |         |       |  |  |

| V <sub>VDD5V</sub>   | VDD5V Pin Output Voltage [a]  | $I_{VDD5V} = 10$ mA, $C_{VDD5V} = 1\mu$ F    | 4.5     | 5       | 5.5     | V     |  |  |

| Symbol               | Description                              | Conditions                                      | Minimum | Typical | Maximum | Units |

|----------------------|------------------------------------------|-------------------------------------------------|---------|---------|---------|-------|

| Low Drop-Out         | (LDO) Regulator                          |                                                 | -       |         |         |       |

| I <sub>OUT_MAX</sub> | Maximum Output Current                   |                                                 |         | 1.25    |         | Α     |

| V <sub>OUT_5V</sub>  | 5V Output Voltage                        | VOSET= 1.8V, VRECT=5.5V                         |         | 5       |         | V     |

| Analog to Digit      | al Converter                             |                                                 |         |         |         |       |

| N                    | Resolution                               |                                                 |         | 12      |         | Bit   |

| f <sub>SAMPLE</sub>  | Sampling Rate                            |                                                 |         | 67.5    |         | kSa/s |

| Channel              | Number of Channels                       |                                                 |         | 8       |         |       |

| V <sub>IN,FS</sub>   | Full-Scale Input Voltage                 |                                                 |         | 2.1     |         | V     |

| EN Pin               |                                          |                                                 |         |         |         |       |

| V <sub>IH_EN</sub>   | Input Threshold HIGH                     |                                                 | 1.4     |         |         | V     |

| V <sub>IL_EN</sub>   | Input Threshold LOW                      |                                                 |         |         | 0.25    | V     |

| l <sub>IL_EN</sub>   | Input Current LOW                        | V <sub>EN</sub> = 0V                            | -1      |         | 1       | μA    |

| lih_en               | Input Current HIGH                       | V <sub>EN</sub> = 5V                            |         | 2.5     |         | μA    |

| EOC pin              |                                          |                                                 |         |         |         |       |

| V <sub>IH_EOC</sub>  | Input Threshold HIGH                     |                                                 | 1.4     |         |         | V     |

| V <sub>IL_EOC</sub>  | Input Threshold LOW                      |                                                 |         |         | 0.7     | V     |

| I <sub>IL_EOC</sub>  | Input Current LOW                        | V <sub>EOC</sub> = 0V                           | -1      |         | 1       | μΑ    |

| I <sub>IH_EOC</sub>  | Input Current HIGH                       | V <sub>EOC</sub> = 1.8V                         | -1      |         | 1       | μA    |

| VOSET, ILIM, T       | S, RPPO, RPPG                            |                                                 |         |         |         |       |

| I <sub>IL</sub>      | Input Current LOW                        | VVOSET, VILIM, VTS, VRPPO, VRPPG = 0V           | -1      |         | 1       | μΑ    |

| I <sub>IH</sub>      | Input Current HIGH                       | VVOSET, VILIM, VTS, VRPPO, VRPPG = 1.8V         | -1      |         | 1       | μΑ    |

| INT pin              |                                          |                                                 |         |         |         |       |

| I <sub>LKG</sub>     | Input Leakage Current                    | V <sub>INT</sub> = 0V and 5V                    | -1      |         | 1       | μΑ    |

| Vol                  | Output Logic LOW                         | $I_{OL} = 8mA$                                  |         |         | 0.36    | V     |

| I2C Interface -      | SCL, SDA                                 |                                                 |         |         |         |       |

| VIL                  | Input Threshold LOW                      |                                                 |         |         | 0.7     | V     |

| VIH                  | Input Threshold HIGH                     |                                                 | 1.4     |         |         | V     |

| I <sub>LKG</sub>     | Input Leakage Current                    | V <sub>SCL</sub> , V <sub>SDA</sub> = 0V and 5V | -1      |         | 1       | μΑ    |

| V <sub>OL</sub>      | Output Logic LOW                         | I <sub>OL</sub> = 8mA                           |         |         | 0.36    | V     |

| fscl                 | Clock Frequency                          |                                                 |         |         | 400     | kHz   |

| thd,sta              | Hold Time (Repeated) for START Condition |                                                 | 0.6     |         |         | μs    |

| thd:dat              | Data Hold Time                           |                                                 | 0       |         |         | ns    |

| tLOW                 | Clock Low Period                         |                                                 | 1.3     |         |         | μs    |

| tніgн                | Clock High Period                        |                                                 | 0.6     |         |         | μs    |

| Symbol           | Description                                    | Conditions            | Minimum | Typical | Maximum | Units |

|------------------|------------------------------------------------|-----------------------|---------|---------|---------|-------|

| tsu:sta          | Set-up Time for Repeated START Condition       |                       | 0.6     |         |         | μs    |

| tBUF             | Bus-Free Time Between STOP and START Condition |                       | 1.3     |         |         | μs    |

| Св               | Capacitive Load for SCL and SDA                |                       |         | 150     |         | pF    |

| Cı               | SCL, SDA Input<br>Capacitance                  |                       |         | 5       |         | pF    |

| Thermal Shutdown |                                                |                       |         |         |         |       |

| т                | TI 101 11                                      | Rising <sup>[b]</sup> |         | 140     |         | °C    |

| T <sub>SD</sub>  | Thermal Shutdown                               | Falling               |         | 120     |         | °C    |

<sup>[</sup>a] Do not externally load. For internal biasing only.

<sup>[</sup>b] If the die temperature exceeds 130°C, the *Thermal\_SHTDN\_Status* flag is set and an End Power Transfer (EPT) packet is sent (see Table 12).

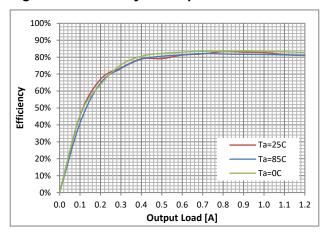

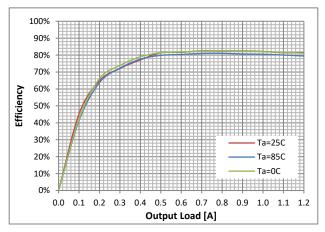

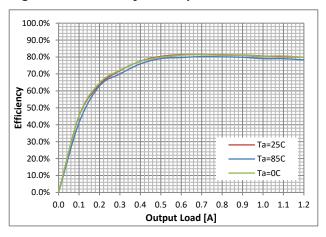

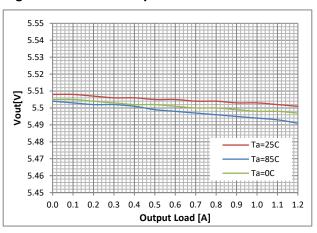

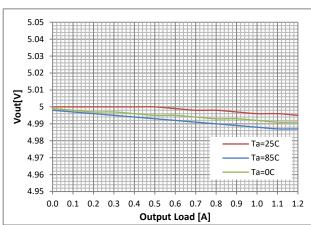

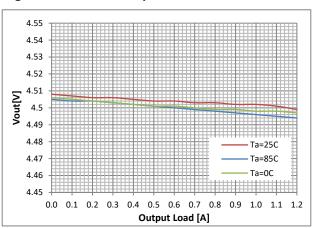

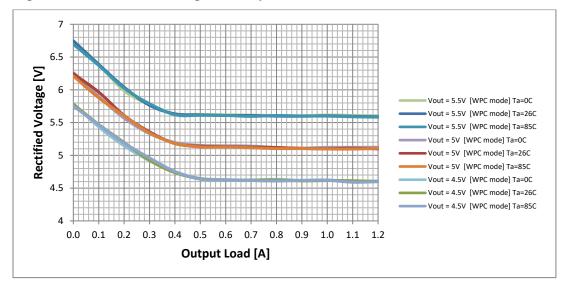

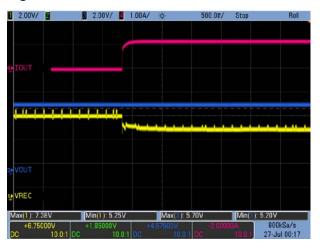

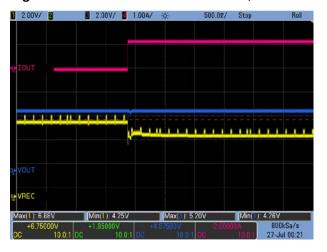

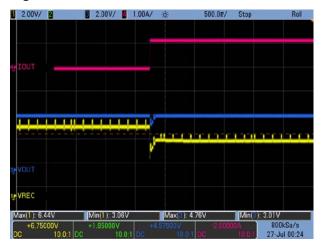

## 6. Typical Performance Characteristics

The performance characteristics curves were taken using the P9038-R transmitter in WPC Mode.

Figure 2. Efficiency vs Output Load: Vout = 5.5V

Figure 4. Efficiency vs Output Load: Vout = 5V

Figure 6. Efficiency vs Output Load: Vout = 4.5V

Figure 3. Vout vs Output Load: Vout = 5.5V

Figure 5. V<sub>OUT</sub> vs Output Load: V<sub>OUT</sub> = 5V

Figure 7. V<sub>OUT</sub> vs Output Load: V<sub>OUT</sub> = 4.5V

Figure 8. Rectified Voltage vs Output Load

Figure 9. Load Transient: Vout = 5.5V, 0A → 1.2A Figure 10. Load Transient: Vout = 5.5V, 1.2A → 0A

Figure 11. Load Transient: Vout = 5V, 0A → 1.2A

Figure 12. Load Transient: Vout = 5V, 1.2A → 0A

Figure 13. Load Transient: Vout = 4.5V, 0A → 1.2A

Figure 14. Load Transient: Vout = 4.5V, 1.2A → 0A

# 7. Functional Block Diagram

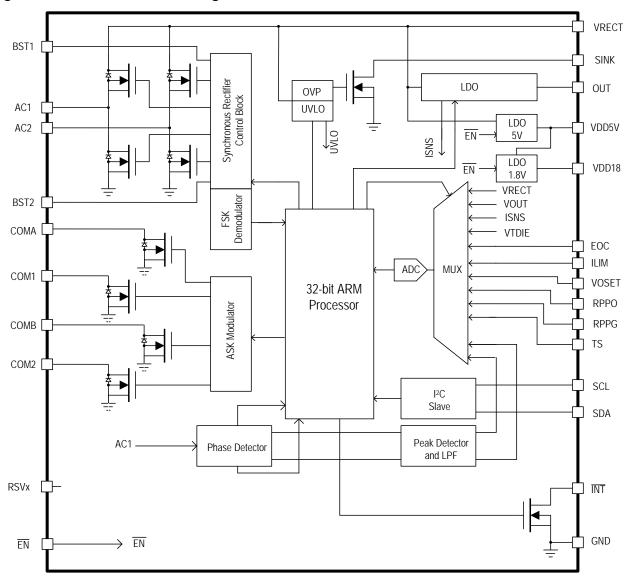

Figure 15. Functional Block Diagram

## 8. Theory of Operation

The P9225-R is a highly-integrated, wireless power receiver targeted for 5W applications supporting both WPC and PMA standards. The device integrates a full-wave synchronous rectifier, low-dropout (LDO) linear regulator, and a 32-bit ARM®-based M0 processor to manage all of the digital control required to comply with the WPC-1.2.4 and PMA communication protocols. Using the near-field inductive power transfer, the receiver converts the AC signal to DC voltage using the integrated synchronous rectifier. The capacitor connected to the output of the rectifier smooths the full-wave rectified voltage into a DC voltage. After the internal biasing circuit is enabled, the "Synchronous Rectifier Control" block operates the switches of the rectifier in various modes to maintain reliable connections and optimal efficiency.

The rectifier voltage and the output current are sampled periodically and digitized by the analog-to-digital converter (ADC). The digital equivalents of the voltage and current are supplied to the internal control logic, which determines whether the loading conditions on the VRECT pin indicate that a change in the operating point is required. If the load is heavy enough and brings the voltage at VRECT below its target, the transmitter is instructed to increase the transmit power. If the voltage at VRECT is higher than its target, the transmitter is instructed to lower the transmit power. The P9225-R will modulate the load or coil voltage to send the instructions to the transmitter in WPC Mode. To maximize efficiency, the voltage at VRECT is programmed to decrease as the LDO's load current increases. The internal temperature is continuously monitored to ensure proper operation.

In the event that the VRECT voltage increases above 12V, Control Error Packets will be sent to the transmitter in an attempt to bring the rectifier voltage back to a safe operating voltage level while simultaneously clamping the incoming energy using the open-drain SINK pin for VRECT linear clamping. The clamp is released when the VRECT voltage falls below V<sub>OVP-DC</sub> minus V<sub>OVP-HC</sub> (see Table 5).

The receiver utilizes IDT's proprietary voltage clamping scheme, which limits the maximum voltage at the rectifier pin to 12V, reducing the voltage rating on the output capacitors while eliminating the need for over-voltage protection (OVP) capacitors. As a result, it provides a small application area, making it an industry-leading wireless power receiver for high power density applications. Combined with the P9038-R transmitter, the P9225-R is a complete wireless power system solution.

### 8.1 LDO - Low Dropout Regulators

The P9225-R has three low-dropout linear regulators. The main regulator provides the power required by the battery charger, and the output voltage can be set in the range of 4.5V to 5.5V. For more information about setting the output voltage, see section 8.2. It is important to connect a 22µF ceramic capacitance to the OUT pin.

The other two regulators, VDD5V and VDD18, bias the internal circuitry of the receiver. These LDOs must have local  $1\mu$ F ceramic capacitors placed as close as possible to the pins.

## 8.2 Setting the Output Voltage - VOSET

The output voltage on the P9225-R is programmed by connecting the center tap of the external resistors R34 and R33 to the VOSET pin as shown in the application schematic in Figure 22.

The default output voltage is set to 5V in the P9225-R Evaluation Board provided in the P9225-R Evaluation Kit. Table 6 shows the resistor combination values for the target output voltage settings.

| Table 6. | Setting | the O | )utput | Voltage |

|----------|---------|-------|--------|---------|

|----------|---------|-------|--------|---------|

| R34  | R33            | Output Voltage |

|------|----------------|----------------|

| 10kΩ | OPEN           | 4.5V           |

| 10kΩ | 49.9k <b>Ω</b> | 4.6V           |

| 10kΩ | 34 <b>kΩ</b>   | 4.7V           |

| 10kΩ | 20k <b>Ω</b>   | 4.8V           |

| 10kΩ | 14.7kΩ         | 4.9V           |

| OPEN | 10kΩ           | 5.0V           |

| R34           | R33  | Output Voltage |

|---------------|------|----------------|

| 10 <b>k</b> Ω | 10kΩ | 5.1V           |

| 14.7kΩ        | 10kΩ | 5.2V           |

| 20k <b>Ω</b>  | 10kΩ | 5.3V           |

| 34kΩ          | 10kΩ | 5.4V           |

| 49.9kΩ        | 10kΩ | 5.5V           |

#### 8.3 SINK Pin

The P9225-R has an internal automatic DC clamping to protect the device in the event of high-voltage transients. The VRECT pin must be shorted to SINK.

## 8.4 Rectifier Voltage - VRECT

The P9225-R uses a high-efficiency synchronous rectifier to convert the AC signal from the coil to a DC signal on the VRECT pin. During startup, the rectifier operates as a passive diode bridge. Once the voltage on VRECT exceeds the under-voltage lock-out (UVLO) level (see Table 5), the rectifier will switch into full synchronous bridge rectifier mode. A total capacitance of 44µF is recommended to minimize the output voltage ripple.

#### 8.5 Over-Current Limit - ILIM

The P9225-R has a programmable current-limit function for protecting the device in the event of an over-current or short-circuit fault condition. When the output current exceeds the programmed threshold, the P9225-R will limit the load current by reducing the output voltage. The current limit should be set to 120% of the target maximum output current.

Connect the ILIM pin to the center tap of a resistor divider to set the current limit. Table 7 shows the resistor combination values for the resistor divider for the ILIM setting. The default ILIM is set to 1.2A in the P9225-R Evaluation Board.

Table 7. Setting the Current Limit

| R38          | R22          | ILIM |

|--------------|--------------|------|

| 10kΩ         | 47kΩ         | 0.8A |

| 10kΩ         | 22k <b>Ω</b> | 0.9A |

| 10kΩ         | OPEN         | 1.0A |

| 10k <b>Ω</b> | 10 <b>kΩ</b> | 1.1A |

| OPEN         | 10 <b>kΩ</b> | 1.2A |

## 8.6 Interrupt Function - INT

The P9225-R provides an open-drain, active-LOW interrupt output pin. It is asserted LOW when  $\overline{\text{EN}}$  is HIGH or any of the following fault conditions have been triggered: the die temperature exceeds 140°C, the external thermistor measurement exceeds the threshold (see section 8.9), or an over-current (OC) or over-voltage (OV) condition is detected (see sections 8.5 and 8 respectively).

During normal operation, the  $\overline{\text{INT}}$  pin is pulled HIGH. This pin can be connected to the interrupt pin of a microcontroller. The fault condition triggering the interrupt flag is available in the I2C interrupt register (see Table 13).

#### 8.7 Enable Pin – $\overline{EN}$

The P9225-R can be disabled by applying a logic HIGH to the  $\overline{\text{EN}}$  pin. When the  $\overline{\text{EN}}$  pin is pulled HIGH, the device is in Shut-Down Mode. Connecting the  $\overline{\text{EN}}$  pin to logic LOW activates the device.

#### 8.8 Thermal Protection

The P9225-R integrates thermal shutdown circuitry to prevent damage resulting from excessive thermal stress. The thermal protection will shut down the receiver if the die temperature exceeds 140°C. If the die temperature exceeds 130°C, the *Thermal\_SHTDN\_Status* flag is set and an End Power Transfer (EPT) packet is sent in order to lower the temperature.

### 8.9 External Temperature Sensing - TS

The P9225-R has a temperature sensor input, TS, which can be used to monitor an external temperature by using a thermistor. The TS pin voltage calculation is described by Equation 1.

$$V_{TS} = V_{VDD18} \times \frac{NTC}{R + NTC}$$

Equation 1

where NTC is the thermistor's resistance and R is the pull-up resistor connected to the VDD18 pin.

The over–temperature shutdown is triggered when the TS pin voltage is lower than 0.6V.

### 8.10 End of Charge - EOC

The End-of-Charge (EOC) pin is an active HIGH logic input, which can be used with an application processor or charger IC in battery management applications. When asserted, the receiver issues an End Power Transfer (EPT) packet to the transmitter terminating power transfer.

#### 8.11 Received Power Packet Offset and Gain Calibration - RPPO and RPPG

The Received Power Packet Offset (RPPO) and Received Power Packet Gain (RPPG) calibrations utilize dedicated pins for tuning foreign object detection (FOD).

Received Power =  $Gain \times Power + Offset$  Equation 2

Power = Calculated Rx Power with Default Setting (in mW) Equation 3

$$Gain = \frac{ADC_{RPPG}}{1755}$$

where  $ADC_{RPPG} = INT \left[ \frac{V_{RPPG}}{2 \text{ 1V}} \times 4095 \right]$

Equation 4

Offset =

$$ADC_{RPPO}$$

– 1755 (in mW)

where  $ADC_{RPPO}$  = INT  $\left[\frac{V_{RPPO}}{2 \text{ tV}} \times 4095\right]$

To use the default FOD setting, set Gain to 1 and Offset to 0. That is equivalent to 0.9V at both RPPO and RPPG pins. To disable the FOD, the RPPO and RPPG pins must be pulled down to GND.

### 8.12 Advanced Foreign Object Detection (FOD)

When metallic objects are exposed to an alternating magnetic field, eddy currents cause such objects to heat up. Examples of such parasitic metal objects are coins, keys, paper clips, etc. The amount of heating depends on the strength of the coupled magnetic field, as well as on the characteristics of the object, such as its resistivity, size, and shape. In a wireless power transfer system, the heating manifests itself as a power loss, and therefore a reduction in power-transfer efficiency. Moreover, if no appropriate measures are taken, the heating could be sufficient that the foreign object could become heated to an undesirable temperature.

During the power transfer phase, the receiver periodically will communicate to the transmitter the amount of power received by means of a Received Power Packet. The transmitter will compare this power with the amount of power transmitted during the same time period. If there is a significant unexplained loss of power, then the transmitter will shut off power delivery because a possible foreign object might be absorbing too much energy.

For a WPC system to perform this function with sufficient accuracy, both the transmitter and receiver must account for and compensate for all of their known losses. Such losses could be due to resistive losses or nearby metals that are part of the transmitter or receiver, etc. Because the system accurately measures its power and accounts for all known losses, it can thereby detect foreign objects because they cause an unknown loss. The WPC specification requires that a power receiver must report to the power transmitter its received power ( $P_{PR}$ ) in a Received-Power Packet (RPP). The maximum value of the received power accuracy  $P_{\Delta}$  depends on the maximum power of the power receiver as defined in Table 8.

The power receiver must determine its  $P_{PR}$  with an accuracy of  $\pm P_{\Delta}$ , and report its received power as  $P_{RECEIVED} = P_{PR} + P_{\Delta}$ . This means that the reported received power is always greater than or equal to the transmitted power ( $P_{PT}$ ) if there is no foreign object (FO) present on the interface surface.

Table 8. Maximum Estimated Power Loss

| Maximum Power [W] | Maximum <b>P∆</b> [mW] |

|-------------------|------------------------|

| 5                 | 350                    |

The compensation algorithm includes values that are programmable via either the I2C interface or OTP (one-time programmable) bits. Programmability is necessary so that the calibration settings can be optimized to match the power transfer characteristics of each particular WPC system to include the power losses of the transmit and receive coils, battery, shielding, and case materials under no-load to full-load conditions. The values are based on the comparison of the received power against a reference power curve so that any foreign object can be sensed when the received power is different from the expected system power.

### 9. Communication Interface

#### 9.1 Modulation/Communication

Receiver-to-transmitter communication is accomplished by modulating the load seen by the receiver's inductor; the communication is purely digital and logic 1's and 0's ride on top of the power signal that exists between the two coils. Modulation is done with amplitude-shift keying (ASK) modulation using internal switches to connect external capacitors from AC1 and AC2 to ground (see Figure 15) with a bit rate of 2Kbps. To the transmitter, this appears as an impedance change, which results in measurable variations of the transmitter's output waveform. The power transmitter detects this as a modulation of coil current/voltage to receive the packets.

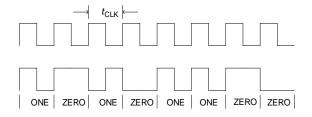

As required by the WPC, the P9225-R uses a differential bi-phase encoding scheme to modulate data bits onto the power signal. A clock frequency of 2kHz is used for this purpose. A logic ONE bit is encoded using two narrow transitions, whereas a logic ZERO bit is encoded using one wider transition as shown below:

Figure 16. Bit Encoding Scheme

### 9.2 Byte Encoding for ASK

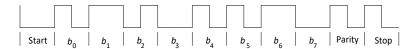

Each byte in the communication packet comprises 11 bits in an asynchronous serial format, as shown in Figure 17.

Figure 17. Byte Encoding Scheme

Each byte has a start bit, 8 data bits, a parity bit, and a single stop bit.

#### 9.3 Packet Structure

The P9225-R communicates with the base station via communication packets. Each communication packet has the following structure:

Figure 18. Communication Packet Structure

| Preamble | Header | Message | Checksum |

|----------|--------|---------|----------|

|----------|--------|---------|----------|

### 10. WPC Mode Characteristics

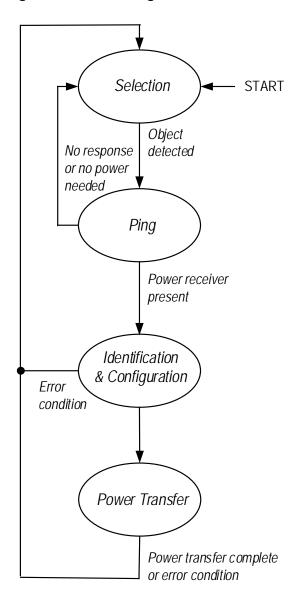

Figure 19. State Diagram for WPC Baseline Power Profile (BPP) Operation

## 10.1 Selection Phase or Startup

In the selection phase, the power transmitter determines if it will proceed to the ping phase after detecting the placement of an object. In this phase, the power transmitter typically monitors the interface surface for the placement and removal of objects using a small measurement signal. This measurement signal should not wake up a power receiver that is positioned on the interface surface.

### 10.2 Ping Phase (Digital Ping)

In the ping phase, the power transmitter will transmit power and will detect the response from a possible power receiver. This response ensures the power transmitter that it is dealing with a power receiver rather than some unknown object. When a mobile device containing the P9225-R is placed on a WPC "Qi" charging pad, it responds to the application of a power signal by rectifying this power signal. When the voltage on VRECT is greater than the UVLO threshold, then the internal bandgaps, reference voltage, and internal voltage regulators (5V and 1.8V) are turned on, and the microcontroller's startup is initiated enabling the WPC communication protocol.

If the power transmitter correctly receives a signal strength packet, the power transmitter proceeds to the identification and configuration phase of the power transfer, maintaining the power signal output.

## 10.3 Identification and Configuration Phase

The identification and configuration phase is the part of the protocol that the power transmitter executes in order to identify the power receiver and establish a default power transfer contract. This protocol extends the digital ping in order to enable the power receiver to communicate the relevant information.

In this phase, the power receiver identifies itself by sending its identification packet and provides information for a default power transfer contract by sending the configuration packet.

#### 10.4 Power Transfer Phase

In this phase, the P9225-R controls the power transfer by means of the following control data packets:

- Control Error Packets

- Received Power Packet (RPP, FOD-related)

- End Power Transfer (EPT) Packet

Once the identification and configuration phase is completed, the transmitter initiates the power transfer mode. The P9225-R control circuit measures the rectifier voltage and sends error packets to the transmitter to adjust the rectifier voltage to the level required to maximize the efficiency of the linear regulator and to send to the transmitter the Received Power Packet for foreign object detection (FOD) to guarantee safe, efficient power transfer.

In the event of an EPT issued by the application, the P9225-R continuously sends EPT packets until the transmitter removes the power and the rectified voltage on the receiver side drops below the UVLO threshold.

## 11. Functional Registers

The following tables provide the address locations, field names, available operations (R or RW), default values, and functional descriptions of all the internally accessible registers contained within the P9225-R. The default I2C slave address is  $61_{\text{HEX}}$ .

Table 9. Device Identification Register

| Address and Bit           | Register Field Name | R/W | Default           | Function and Description |

|---------------------------|---------------------|-----|-------------------|--------------------------|

| 0000 <sub>HEX</sub> [7:0] | Part_number_L       | R   | 25нех             | Chip ID low byte         |

| 0001 <sub>HEX</sub> [7:0] | Part_number_H       | R   | 92 <sub>HEX</sub> | Chip ID high byte        |

#### Table 10. Firmware Major Revision

| Address and Bit           | Register Field Name | R/W | Default           | Function and Description          |

|---------------------------|---------------------|-----|-------------------|-----------------------------------|

| 0004 <sub>HEX</sub> [7:0] | FW_Major_Rev_L      | R   | 01 <sub>HEX</sub> | Major firmware revision low byte  |

| 0005 <sub>HEX</sub> [7:0] | FW_Major_Rev_H      | R   | 00 <sub>HEX</sub> | Major firmware revision high byte |

#### **Table 11. Firmware Minor Revision**

| Address and Bit           | Register Field Name | R/W | Default           | Function and Description          |

|---------------------------|---------------------|-----|-------------------|-----------------------------------|

| 0006нех [7:0]             | FW_Minor_Rev_L      | R   | 27 <sub>HEX</sub> | Minor firmware revision low byte  |

| 0007 <sub>HEX</sub> [7:0] | FW_Minor_Rev_H      | R   | 04 <sub>HEX</sub> | Minor firmware revision high byte |

#### **Table 12. Status Registers**

| Address and Bit           | Register Field Name  | R/W | Default          | Function and Description                                                                                                                                    |

|---------------------------|----------------------|-----|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0034нех [7]               | Vout_Status          | R   | OBIN             | "0" output voltage is off.                                                                                                                                  |

|                           |                      |     |                  | "1" output voltage is on.                                                                                                                                   |

| 0034 <sub>HEX</sub> [6]   | Reserved             | R   | O <sub>BIN</sub> |                                                                                                                                                             |

| 0034 <sub>НЕХ</sub> [5]   | Reserved             | R   | OBIN             |                                                                                                                                                             |

| 0034 <sub>нех</sub> [4]   | Reserved             | R   | OBIN             |                                                                                                                                                             |

| 0034 <sub>нех</sub> [3]   | Reserved             | R   | OBIN             |                                                                                                                                                             |

| 0034нех [2]               | Thermal_SHTDN_Status | R   | OBIN             | "0" indicates no over-temperature condition exists.                                                                                                         |

|                           |                      |     |                  | "1" indicates that the die temperature exceeds 130°C or the NTC is less than 0.6V. The P9225-R sends an End Power Transfer (EPT) packet to the transmitter. |

| 0034 <sub>HEX</sub> [1]   | VRECT_OV_ Status     | R   | OBIN             | "1" indicates rectifier exceeds 20V for V <sub>OUT</sub> =12. The P9225-R sends an End Power Transfer (EPT) packet to the transmitter.                      |

| 0034 <sub>HEX</sub> [0]   | Current_Limit_Status | R   | O <sub>BIN</sub> | "1" indicates current limit has been exceeded. The P9225-R sends an End Power Transfer (EPT) packet to the transmitter.                                     |

| 0035 <sub>нех</sub> [7:0] | Reserved             | R   | 00нех            |                                                                                                                                                             |

**Table 13. Interrupt Status Registers**

| Address and Bit           | Register Field Name  | R/W | Default          | Function and Description                               |

|---------------------------|----------------------|-----|------------------|--------------------------------------------------------|

| 0036 <sub>нех</sub> [7]   | INT_Vout_Status      | R   | O <sub>BIN</sub> | "0" output voltage has not changed.                    |

|                           |                      |     |                  | "1" output voltage changed.                            |

| 0036нех [6]               | Reserved             | R   | OBIN             |                                                        |

| 0036 <sub>НЕХ</sub> [5]   | Reserved             | R   | OBIN             |                                                        |

| 0036нех [4]               | Reserved             | R   | OBIN             |                                                        |

| 0036нех [3]               | Reserved             | R   | OBIN             |                                                        |

| 0036нех [2]               | INT_OVER_TEMP_Status | R   | OBIN             | "1" indicates over-temperature condition exists.       |

| 0036 <sub>нех</sub> [1]   | INT_VRECT_OV_Status  | R   | OBIN             | "1" indicates rectifier over-voltage condition exists. |

| 0036нех [0]               | INT_OC_Limit_Status  | R   | OBIN             | "1" indicates current limit has been exceeded.         |

| 0037 <sub>HEX</sub> [7:0] | Reserved             | R   | 00нех            |                                                        |

Note: If any bit in the *Interrupt Status* register  $36_{HEX}$  is "1" and the corresponding bit in the *Interrupt Enable* register  $38_{HEX}$  is set to "1," the  $\overline{INT}$  pin will be pulled down indicating an interrupt event has occurred.

**Table 14. Interrupt Enable Registers**

| Address and Bit         | Register Field Name    | R/W | Default           | Function and Description                        |

|-------------------------|------------------------|-----|-------------------|-------------------------------------------------|

| 0038 <sub>нех</sub> [7] | Vout_Status_INT_EN     | RW  | O <sub>BIN</sub>  | "0" disables the INT_Vout_Status interrupt.     |

|                         |                        |     |                   | "1" enables the interrupt.                      |

| 0038нех [6]             | Reserved               | R   | OBIN              |                                                 |

| 0038нех [5]             | Reserved               | R   | OBIN              |                                                 |

| 0038нех [4]             | Reserved               | R   | OBIN              |                                                 |

| 0038нех [3]             | Reserved               | R   | OBIN              |                                                 |

| 0038нех [2]             | OVER_TEMP_INT_EN       | RW  | O <sub>BIN</sub>  | "0" disables the INT_OVER_TEMP interrupt.       |

|                         |                        |     |                   | "1" enables the interrupt.                      |

| 0038нех [1]             | VRECT_OV_INT_EN        | RW  | O <sub>BIN</sub>  | "0" disables the INT_VRECT_OV interrupt.        |

|                         |                        |     |                   | "1" enables the interrupt.                      |

| 0038нех [0]             | OC_Limit_Status_INT_EN | RW  | OBIN              | "0" disables the INT_OC_Limit_Status interrupt. |

|                         |                        |     |                   | "1" enables the interrupt.                      |

| 0039нех [7:0]           | Reserved               | RW  | 00 <sub>HEX</sub> |                                                 |

#### **Table 15. Battery Charge Status**

| Address and Bit           | Register Field Name | R/W | Default           | Function and Description                                                                                                                                                        |

|---------------------------|---------------------|-----|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 003A <sub>HEX</sub> [7:0] | Batt_Charg_status   | R/W | 00 <sub>HEX</sub> | The application processor loads the battery charge status in this register. This value is sent to the transmitter when bit 4 of register 004E <sub>HEX</sub> is set to "1." [a] |

<sup>[</sup>a] Firmware only forwards the data from the application processor to transmitter.

#### Table 16. End Power Transfer

The application processor initiates the End Power Transfer (EPT).

| Address and Bit | Register Field Name | R/W | Default | Function and Description                                                                                                                                             |

|-----------------|---------------------|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 003Внех [7:0]   | EPT_Code            | R/W | 00нех   | The application processor loads the EPT code value in this register. This value is sent to the transmitter when bit 3 of register $004E_{\text{HEX}}$ is set to "1." |

### Table 17. Read Register - Output Voltage

$$V_{OUT} = \frac{ADC\_VOUT * 6 * 2.1}{4095}$$

| Address and Bit           | Register Field Name | R/W | Default          | Function and Description |  |

|---------------------------|---------------------|-----|------------------|--------------------------|--|

| 003Снех [7:0]             | ADC_VOUT [7:0]      | R   | Онех             | 8 LSB of VOUT ADC value. |  |

| 003D <sub>HEX</sub> [7:4] | Reserved            | R   | 0 <sub>HEX</sub> | Reserved.                |  |

| 003D <sub>HEX</sub> [3:0] | ADC_VOUT [11:8]     | R   | O <sub>HEX</sub> | 4 MSB of VOUT ADC value. |  |

#### Table 18. Read Register - VRECT Voltage

$$VRECT = \frac{ADC\_VRECT * 10 * 2.1}{4095}$$

| Address and Bit           | Register Field Name | R/W | Default | Function and Description  |

|---------------------------|---------------------|-----|---------|---------------------------|

| 0040 <sub>HEX</sub> [7:0] | ADC_VRECT [7:0]     | R   | -       | 8 LSB of VRECT ADC value. |

| 0041 <sub>HEX</sub> [7:4] | Reserved            | R   | Онех    | Reserved                  |

| 0041 <sub>HEX</sub> [3:0] | ADC_VRECT [11:8]    | R   | -       | 4 MSB of VRECT ADC value. |

#### Table 19. Read Register - I<sub>OUT</sub> Current

$$I_{OUT} = \frac{RX\_IOUT * 2 * 2.1}{4095}$$

| Address and Bit           | Register Field Name | R/W                     | Default                                                | Function and Description             |  |

|---------------------------|---------------------|-------------------------|--------------------------------------------------------|--------------------------------------|--|

| 0044 <sub>HEX</sub> [7:0] | RX_IOUT [7:0]       | R <sub>HEX</sub> – 8 LS |                                                        | 8 LSB of IOUT. Output current in mA. |  |

| 0045 <sub>HEX</sub> [7:0] | RX_IOUT [15:8]      | R <sub>HEX</sub>        | R <sub>HEX</sub> – 8 MSB of IOUT. Output current in mA |                                      |  |

#### Table 20. Read Register - Die Temperature

$T_{DIE} = (ADC\_Die\_Temp - 1350) \frac{83}{444} - 273$  where  $ADC\_Die\_Temp = 12$  bits from  $ADC\_Die\_Temp\_H$  and  $ADC\_Die\_Temp\_L$ .

| Address and Bit           | Register Field Name | R/W | Default                                     | Function and Description                |  |

|---------------------------|---------------------|-----|---------------------------------------------|-----------------------------------------|--|

| 0046 <sub>НЕХ</sub> [7:0] | ADC_Die_Temp_L      | R   | R – 8 LSB of current die temperature in °C. |                                         |  |

| 0047 <sub>HEX</sub> [7:4] | Reserved            | R   | Онех                                        | Reserved                                |  |

| 0047 <sub>HEX</sub> [3:0] | ADC_Die_Temp_H      | R   | _                                           | 4 MSB of current die temperature in °C. |  |

#### Table 21. Read Register - Operating Frequency

$$f_{OP} = \frac{64 * 6000}{OP\_FREQ [15:0]}$$

| Address and Bit           | Register Field Name | R/W | Default                                | Function and Description               |

|---------------------------|---------------------|-----|----------------------------------------|----------------------------------------|

| 0048 <sub>HEX</sub> [7:0] | OP_FREQ[7:0]        | R   | -                                      | 8 LSB AC signal frequency on the coil. |

| 0049 <sub>HEX</sub> [7:0] | OP_FREQ[15:8]       | R   | 8 MSB AC signal frequency on the coil. |                                        |

#### **Table 22. Command Register**

| Address and Bit           | Register Field Name     | R/W | Default          | Function and Description                                                                                                                                                                              |  |

|---------------------------|-------------------------|-----|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 004E <sub>нех</sub> [7:6] | Reserved                | R   | Онех             | Reserved.                                                                                                                                                                                             |  |

| 004E <sub>HEX</sub> [5]   | Clear_Interrupt         | RW  | O <sub>BIN</sub> | If application processor sets this bit to "1," the P9225-R clears the interrupt pin.                                                                                                                  |  |

| 004E <sub>HEX</sub> [4]   | Send Batt Charge status | R   | O <sub>BIN</sub> | If the application processor sets this bit to "1," the P9225-R sends the battery charge status (see <code>Batt_Charg_status</code> in Table 15).                                                      |  |

| 004Енех [3]               | Send_End_Power_Transfer | RW  | OBIN             | If application processor sets this bit to "1," the P9225-R sends the End Power Transfer packet (defined in the EPT_Code register shown in Table 16) to the transmitter and then sets this bit to "0." |  |

| 004E <sub>HEX</sub> [2]   | Reserved                | R   | O <sub>BIN</sub> | Reserved.                                                                                                                                                                                             |  |

| 004E <sub>HEX</sub> [1]   | Toggle_LDO_On-OFF       | RW  | O <sub>BIN</sub> | If application processor sets this bit to "1," the P9225-R toggles the LDO output once (from ON to OFF or from OFF to ON), and then sets this bit to "0."                                             |  |

| 004E <sub>HEX</sub> [0]   | Reserved                | R   | O <sub>BIN</sub> | Reserved.                                                                                                                                                                                             |  |

**Table 23. Clear Interrupt Bits**

| Address and Bit         | Register or Bit Field Name | R/W | Default          | Function and Description                                                                                                                                                                                                                                                     |

|-------------------------|----------------------------|-----|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0056 <sub>HEX</sub> [7] | Clear_Vout_Changed_Bit     | RW  | O <sub>BIN</sub> | "1" clears the <i>INT_Vout_Status</i> bit in register 0036 <sub>HEX</sub> (refer to Table 13). Register 0036 <sub>HEX</sub> is updated after the application processor resets the interrupt pin by writing "1" to bit 5 of register 004E <sub>HEX</sub> (refer to Table 22). |

| 0056 <sub>НЕХ</sub> [6] | Reserved                   | RW  | O <sub>BIN</sub> |                                                                                                                                                                                                                                                                              |

| 0056нех [5]             | Reserved                   | RW  | OBIN             |                                                                                                                                                                                                                                                                              |