# Model Name: P424KVN01.0

Issue Date: 2023/09/11

(\*)Preliminary Specifications(\*)Final Specifications

| Customer Signature | Date | ADP Display+                                                   | Date |  |

|--------------------|------|----------------------------------------------------------------|------|--|

| Approved By        |      | Approval By PM Director  Albert Lai                            |      |  |

| Note               |      | Reviewed By RD Director  Lamy Chen  Reviewed By Project Leader |      |  |

|                    |      | Simon Chung  ———————————————————————————————————               |      |  |

# **Contents**

| 1.   | Ge           | neral Description                                  | ວ    |  |  |  |  |

|------|--------------|----------------------------------------------------|------|--|--|--|--|

| 2.   | Ab           | solute Maximum Ratings                             | 7    |  |  |  |  |

| 3.   | Op           | tical Specification                                | 8    |  |  |  |  |

| 4.   | Inte         | erface Specification                               | . 12 |  |  |  |  |

| 4.1  | I            | nput power                                         | . 12 |  |  |  |  |

| 4.2  | I            | nput Connection                                    | . 13 |  |  |  |  |

| 4.2  | <b>.1</b> Co | onnector Type                                      | . 13 |  |  |  |  |

| 4.2  | <b>.2</b> Co | onnector Pin Assignment                            | . 13 |  |  |  |  |

| 4.3  | I            | nput Data Format                                   | . 15 |  |  |  |  |

|      | 4.3          | LCD Pixel Format                                   | . 15 |  |  |  |  |

|      | 4.3          | eDP Data Format                                    | . 16 |  |  |  |  |

|      | 4.3          | 8.3 Color Input Data Reference                     | . 17 |  |  |  |  |

| 5.   | Sig          | gnal Timing Specification                          | . 19 |  |  |  |  |

|      | 5.1          | .1. Timing table                                   | . 19 |  |  |  |  |

|      | 5.1          | .2. Input Timing Diagram                           | . 20 |  |  |  |  |

| 5.2  | I            | nput interface characteristics                     | . 22 |  |  |  |  |

| 5.4  | F            | Power Sequence for LCD                             | . 26 |  |  |  |  |

| 6.   | Ва           | cklight Specification                              | . 28 |  |  |  |  |

| 6.1  | E            | Electrical specification                           | . 28 |  |  |  |  |

| 6.2  | I            | nput Pin Assignment                                | . 29 |  |  |  |  |

| 6.3  | F            | Power Sequence for Backlight                       | . 31 |  |  |  |  |

| 7.   | Me           | chanical Characteristics                           | . 32 |  |  |  |  |

| 8.   | Re           | liability Test Items                               | . 35 |  |  |  |  |

| 9.   | Inte         | ernational Standard                                | . 36 |  |  |  |  |

| 9.1  | 5            | Safety                                             | . 36 |  |  |  |  |

| 9.2  | E            | EMC                                                | . 36 |  |  |  |  |

| 10.  | Pa           | cking                                              | . 37 |  |  |  |  |

| 10.  | 1 [          | Definition of Label                                | . 37 |  |  |  |  |

| 10.  | 2 F          | Pallet and Shipment Information                    | . 39 |  |  |  |  |

| 11.  | Pre          | ecautions                                          | . 40 |  |  |  |  |

| 11.  | 1. N         | Mounting Precautions                               | . 40 |  |  |  |  |

| 11.2 | 2. (         | Operating Precautions                              | . 40 |  |  |  |  |

| 11.3 | 3. (         | Operating Condition for Public Information Display | . 41 |  |  |  |  |

| 11.4 | 4. E         | l. Electrostatic Discharge Control41               |      |  |  |  |  |

| 11.5.        | Precautions for Strong Light Exposure         | 42                                    |

|--------------|-----------------------------------------------|---------------------------------------|

| 11.6.        | Storage                                       | 42                                    |

| 11.7.        | Handling Precautions for Protection Film      | 42                                    |

|              | Dust Resistance                               |                                       |

| 12. <i>A</i> | Appendix I : Content Format                   | 44                                    |

|              | Appendix II: Tartan (42.4" pixel arrangement) |                                       |

|              |                                               | · · · · · · · · · · · · · · · · · · · |

# **Record of Revision**

| Version | Date       | Page | Description    |

|---------|------------|------|----------------|

| 1.0     | 2023/09/11 | All  | First released |

|         |            |      |                |

|         |            |      |                |

|         |            |      |                |

|         |            |      |                |

|         |            |      |                |

|         |            |      |                |

|         |            |      |                |

|         |            |      |                |

|         |            |      |                |

|         |            |      |                |

|         |            |      |                |

|         |            |      |                |

|         |            |      |                |

|         |            |      |                |

|         |            |      |                |

|         |            |      |                |

|         |            |      |                |

|         | _          |      |                |

|         |            |      |                |

|         |            |      |                |

|         |            |      |                |

## 1. General Description

This specification applies to the 42.4 inch Color TFT-LCD Module P424KVN01.0 This LCD module has a TFT active matrix type liquid crystal panel 3840 x 320 pixels, and diagonal size of 42.4 inch. This module supports 3840 x 2160 mode. Each pixel is divided into Red, Green and Blue sub-pixels or dots which are arranged in vertical stripes. Gray scale or the brightness of the sub-pixel color is determined with a 10-bit gray scale signal for each dot.

P424KVN01.0 has been designed to apply the 4 lane eDP interface method. It is intended to support displays where high brightness, wide viewing angle, high color saturation, and high color depth are very important. Special material applied into this model are:

Liquid crystal: Advanced wide temperature LC(-40°C~110°C)

Polarizer: Wide temperature polarizer (95°C)

#### \* General Information

| Items                  | Specification                     | Unit   | Note                           |

|------------------------|-----------------------------------|--------|--------------------------------|

| Active Screen Size     | 42.4                              | inch   |                                |

| Display Area           | 1073.8 (H) x 89.5 (V)             | mm     |                                |

| Outline Dimension      | 1096.58 (H) x112.28 (V) x 25.0(D) | mm     | D: front bezel to D/B cover    |

| Driver Element         | a-Si TFT active matrix            |        |                                |

| Display Colors         | 8 bit + FRC                       | Colors |                                |

| Number of Pixels       | 3840x320                          | Pixel  |                                |

| Pixel Pitch            | 0.279 (H) x 0.279 (W)             | mm     |                                |

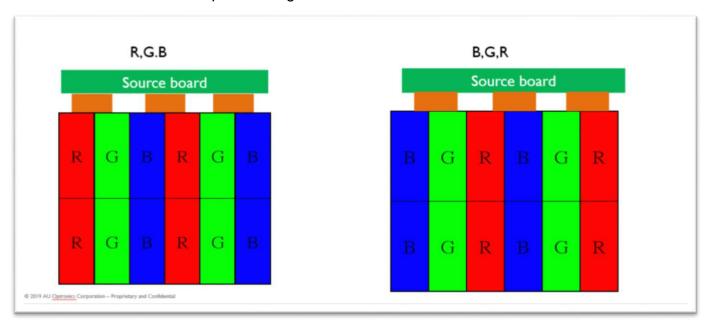

| Divol Arrangement      | DCD/ BCD vertical atrina          |        | See 13 Appendix II for details |

| Pixel Arrangement      | RGB/ BGR vertical stripe          |        | Page 42                        |

| Display Operation Mode | Normally Black                    |        |                                |

| Surface Treatment      | Anti-Glare 28%                    |        |                                |

| Rotate Function        | Unachievable                      |        | Note 1                         |

| Display Orientation    | Portrait/Landscape Enabled        |        | Note 2                         |

| Operating Time         | 24/7                              |        | See Chapter 11.3 for details   |

| Frame Rate             | 60                                | Hz     | See Chapter 5.1 for details    |

| LED Life               | 50K                               | hours  | See Chapter 6.1 for details    |

Note 1: Rotate Function refers to LCD display could be able to rotate. This function does not work in this model.

#### Note 2:

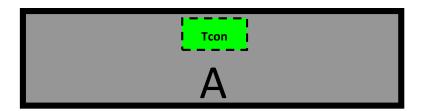

- (1) Landscape Mode: The default placement is T-Con Side on the lower side and the image is shown upright via viewing from the front.

- (2) Portrait Mode: The default placement is that T-Con side has to be placed on the right side via viewing from the front.

### Landscape (Front view)

## Portrait (Front view)

## 2. Absolute Maximum Ratings

The followings are maximum values which, if exceeded, may cause faulty operation or damage to the unit

| Item                      | Symbol          | Min  | Max | Unit   | Conditions |

|---------------------------|-----------------|------|-----|--------|------------|

| Logic/LCD Drive Voltage   | V <sub>DD</sub> | -0.3 | 14  | [Volt] | Note 1     |

| Input Voltage of Signal   | Vin             | -0.3 | 4   | [Volt] | Note 1     |

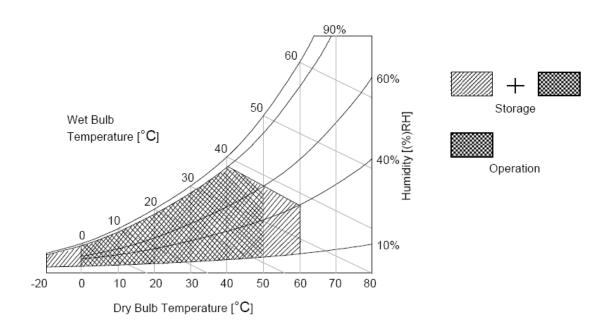

| Operating Temperature     | TOP             | 0    | 50  | [°C]   | Note 2     |

| Operating Humidity        | НОР             | 10   | 90  | [%RH]  | Note 2     |

| Storage Temperature       | TST             | -20  | +60 | [°C]   | Note 2     |

| Storage Humidity          | HST             | 10   | 90  | [%RH]  | Note 2     |

| Panel Surface Temperature | PST             |      | 65  | [°C]   | Note 3     |

Note 1: Duration:50 msec.

Note 2 : Maximum Wet-Bulb should be 39 □ and No condensation.

The relative humidity must not exceed 90% non-condensing at temperatures of  $40\Box$  or less. At temperatures greater than  $40\Box$ , the wet bulb temperature must not exceed  $39\Box$ .

Note 3: Surface temperature is measured at 60°C Dry condition

# 3. Optical Specification

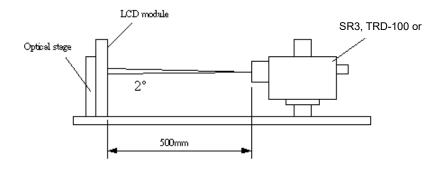

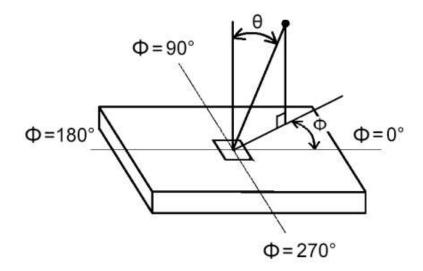

Optical characteristics are determined after the unit has been 'ON' and stable for approximately 45 minutes in a dark environment at 25°C. The values specified are at an approximate distance 500 mm from the LCD surface at a viewing angle of  $\phi$  and  $\theta$  equal to  $0^{\circ}$ .

Fig.1 presents additional information concerning the measurement equipment and method.

| D                         | Comple al      |         | Values |           | 11                | Nistas |

|---------------------------|----------------|---------|--------|-----------|-------------------|--------|

| Parameter                 | Symbol         | Min.    | Тур.   | Max       | Unit              | Notes  |

| Contrast Ratio            | CR             | 3200    | 4000   |           |                   | 1      |

| Surface Luminance (White) | Lwh            | 560     | 700    |           | cd/m <sup>2</sup> | 2      |

| Luminance Variation       | δwhite(9P)     |         |        | 1.33      |                   | 3      |

| Response Time (G to G)    | Тү             |         | 8      | 16        | ms                | 4      |

| Color Gamut               | NTSC           | 67.5    | 72     |           | %                 |        |

| Gamma                     | Gma            | 1.9     | 2.2    | 2.5       |                   |        |

| Color Coordinates         |                |         |        |           |                   |        |

| Red                       | R <sub>X</sub> |         | 0.653  |           |                   |        |

|                           | R <sub>Y</sub> |         | 0.337  |           |                   |        |

| Green                     | G <sub>X</sub> |         | 0.321  |           |                   |        |

|                           | G <sub>Y</sub> | T 0.02  | 0.618  | T 10.02   |                   |        |

| Blue                      | Bx             | Typ0.03 | 0.150  | Тур.+0.03 |                   |        |

|                           | B <sub>Y</sub> |         | 0.070  |           |                   |        |

| White                     | Wx             |         | 0.313  |           |                   |        |

|                           | WY             |         | 0.329  |           |                   |        |

| Viewing Angle             |                |         |        |           |                   | 5      |

| x axis, right(φ=0°)       | θr             | 85      | 89     |           | degree            |        |

| x axis, left(φ=180°)      | θι             | 85      | 89     |           | degree            |        |

| y axis, up(φ=90°)         | $\theta_{u}$   | 85      | 89     |           | degree            |        |

| y axis, down (φ=270°)     | θ <sub>d</sub> | 85      | 89     |           | degree            |        |

#### Note:

1. Contrast Ratio (CR) is defined mathematically as:

$$\label{eq:contrast_Ratio} \textbf{Surface Luminance of $L_{on5}$} \\ \textbf{Surface Luminance of $L_{off5}$}$$

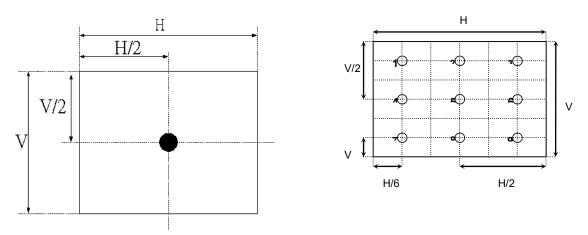

- 2. Surface luminance is luminance value at point 5 across the LCD surface 50cm from the surface with all pixels displaying white. From more information see FIG 2. LED current I<sub>F</sub> = typical value (without driver board), LED input VDDB =24V, I<sub>DDB</sub>. = Typical value (with driver board), L<sub>WH</sub>=Lon5 where Lon5 is the luminance with all pixels displaying white at center 5 location.

- 3. The variation in surface luminance, δWHITE is defined (center of Screen) as: δ<sub>WHITE(9P)</sub>= Maximum(L<sub>on1</sub>, L<sub>on2</sub>,...,L<sub>on9</sub>)/ Minimum(L<sub>on1</sub>, L<sub>on2</sub>,...L<sub>on9</sub>)

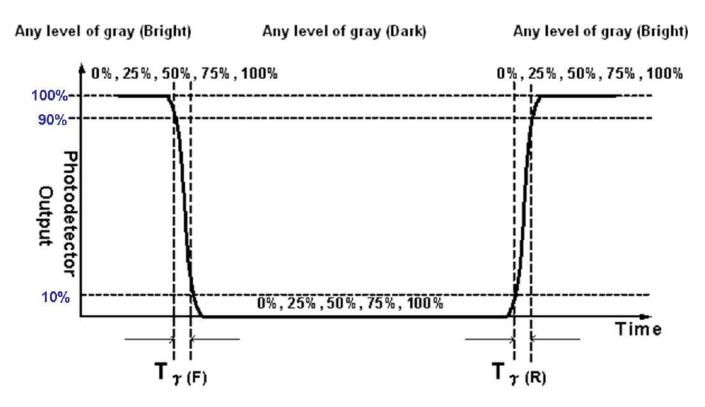

- 4. Response time  $T_{\gamma}$  is the average time required for display transition by switching the input signal for five luminance ratio (0%,25%,50%,75%,100% brightness matrix) and is based on Frame rate = 60Hz to optimize.

| Me    | easured   |            |             | Target      |             |             |

|-------|-----------|------------|-------------|-------------|-------------|-------------|

| Resp  | onse Time | 0%         | 25%         | 50%         | 75%         | 100%        |

|       | 0%        |            | 0% to 25%   | 0% to 50%   | 0% to 75%   | 0% to 100%  |

|       | 25%       | 25% to 0%  |             | 25% to 50%  | 25% to 75%  | 25% to 100% |

| Start | 50%       | 50% to 0%  | 50% to 25%  |             | 50% to 75%  | 50% to 100% |

|       | 75%       | 75% to 0%  | 75% to 25%  | 75% to 50%  |             | 75% to 100% |

|       | 100%      | 100% to 0% | 100% to 25% | 100% to 50% | 100% to 75% |             |

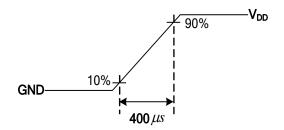

T<sub>Y</sub> is determined by 10% to 90% brightness difference of rising or falling period. (As illustrated)

The response time is defined as the following figure and shall be measured by switching the input signal for "any level of gray(bright)" and "any level of gray(dark)".

#### FIG. 2 Luminance

5. Viewing angle is the angle at which the contrast ratio is greater than 10. The angles are determined for the horizontal or x axis and the vertical or y axis with respect to the z axis which is normal to the LCD surface. For more information see FIG3.

## FIG.3 Viewing Angle

# 4. Interface Specification

#### 4.1 Input power

The P424KVN01.0 module requires power inputs which are employed to power the LCD electronics and to drive the TFT array and liquid crystal.

| Item                       | Symbol          | Min.              | Тур. | Max  | Unit | Note |   |

|----------------------------|-----------------|-------------------|------|------|------|------|---|

| Power Supply Input Voltage |                 | $V_{DD}$          | 10.8 | 12   | 13.2 | V    | 1 |

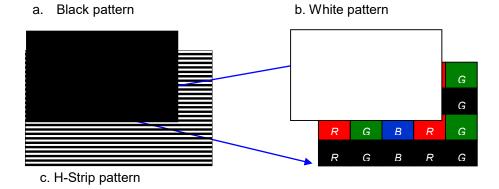

|                            | Black pattern   |                   | -    | 0.59 | 0.66 | Α    |   |

| Power Supply Input Current | White pattern   | I <sub>DD</sub>   | -    | 0.59 | 0.66 | Α    |   |

|                            | H-strip pattern |                   | -    | 0.62 | 0.69 | Α    | 2 |

|                            | Black pattern   |                   | -    | 7.08 | 7.13 | Watt | 2 |

| Power Consumption          | White pattern   | Pc                | -    | 7.08 | 7.13 | Watt |   |

|                            | H-strip pattern |                   | -    | 7.44 | 7.45 | Watt |   |

| Inrush Current             |                 | I <sub>RUSH</sub> |      |      | 5    | Α    | 3 |

**Note1.** The ripple voltage should be fewer than 5% of VDD.

Note2. Test Condition:

- (1)  $V_{DD}$  = 12.0V, (2)  $F_{V}$  = 60Hz, (3)  $F_{C}$   $F_{C}$

- (5) Power dissipation check pattern. (Only for power design)

**Note3.** Measurement condition : Rising time = 400us

## 4.2 Input Connection

## **4.2.1** Connector Type

|                      | Manufacturer | P-TW∕∩      | IAF           | STARCONN          |

|----------------------|--------------|-------------|---------------|-------------------|

| TFT-LCD<br>Connector | Part Number  | 187059-5122 | FI-RTE51SZ-HF | 115E51-0000RA-M3- |

|                      |              |             |               | R                 |

## **4.2.2** Connector Pin Assignment

| PIN# | Symbol      | Description                                       | Remark |

|------|-------------|---------------------------------------------------|--------|

| 1    | VDD         | Power +12V                                        | 1      |

| 2    | VDD         | Power +12V                                        |        |

| 3    | VDD         | Power +12V                                        |        |

| 4    | VDD         | Power +12V                                        |        |

| 5    | VDD         | Power +12V                                        |        |

| 6    | VDD         | Power +12V                                        |        |

| 7    | VDD         | Power +12V                                        |        |

| 8    | VDD         | Power +12V                                        |        |

| 9    | NC          | No connection (for ADP test only. Do not connect) | 2      |

| 10   | NC          | No connection (for ADP test only. Do not connect) | 2      |

| 11   | NC          | No connection (for ADP test only. Do not connect) | 2      |

| 12   | NC          | No connection (for ADP test only. Do not connect) | 2      |

| 13   | NC          | No connection (for ADP test only. Do not connect) | 2      |

| 14   | NC          | No connection (for ADP test only. Do not connect) | 2      |

| 15   | NC          | No connection (for ADP test only. Do not connect) | 2      |

| 16   | NC          | No connection (for ADP test only. Do not connect) | 2      |

| 17   | GND         | Ground                                            |        |

| 18   | 1st Lane3_N | Negative eDP differential data input              |        |

| 19   | 1st Lane3_P | Positive eDP differential data input              |        |

| 20   | GND         | Ground                                            |        |

| 21   | 1st Lane2_N | Negative eDP differential data input              |        |

| 22   | 1st Lane2_P | Positive eDP differential data input              |        |

| 23   | GND         | Ground                                            |        |

| 24   | 1st Lane1_N | Negative eDP differential data input              |        |

| 25   | 1st Lane1_P | Positive eDP differential data input              |        |

| 26   | GND         | Ground                                            |        |

| 27   | 1st Lane0_N | Negative eDP differential data input              |        |

| 28 | 1st Lane0 P  | Positive eDP differential data input              |   |

|----|--------------|---------------------------------------------------|---|

| 29 | GND          | Ground                                            |   |

| 30 | 1st AUX_CH_P | Positive AUX Channel differential data input      |   |

| 31 | 1st AUX CH N | Negative AUX Channel differential data input      |   |

| 32 | GND          | Ground                                            |   |

| 33 | NC           | No connection (for ADP test only. Do not connect) | 2 |

| 34 | GND          | Ground                                            |   |

| 35 | NC           | No connection (for ADP test only. Do not connect) | 2 |

| 36 | NC           | No connection (for ADP test only. Do not connect) | 2 |

| 37 | GND          | Ground                                            |   |

| 38 | NC           | No connection (for ADP test only. Do not connect) | 2 |

| 39 | NC           | No connection (for ADP test only. Do not connect) | 2 |

| 40 | GND          | Ground                                            |   |

| 41 | NC           | No connection (for ADP test only. Do not connect) | 2 |

| 42 | NC           | No connection (for ADP test only. Do not connect) | 2 |

| 43 | GND          | Ground                                            |   |

| 44 | NC           | No connection (for ADP test only. Do not connect) | 2 |

| 45 | NC           | No connection (for ADP test only. Do not connect) | 2 |

| 46 | GND          | Ground                                            |   |

| 47 | NC           | No connection (for ADP test only. Do not connect) | 2 |

| 48 | NC           | No connection (for ADP test only. Do not connect) | 2 |

| 49 | GND          | Ground                                            |   |

| 50 | HPD          | Hot plug detection                                |   |

| 51 | NC           | No connection (for ADP test only. Do not connect) | 2 |

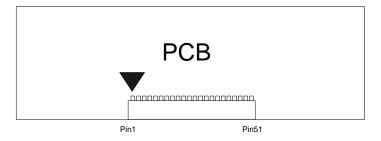

Note1. Pin number start from the left side as the following figure.

Note2. Please leave this pin unoccupied. It cannot be connected with any signal (Low/GND/High.....etc).

## 4.3 Input Data Format

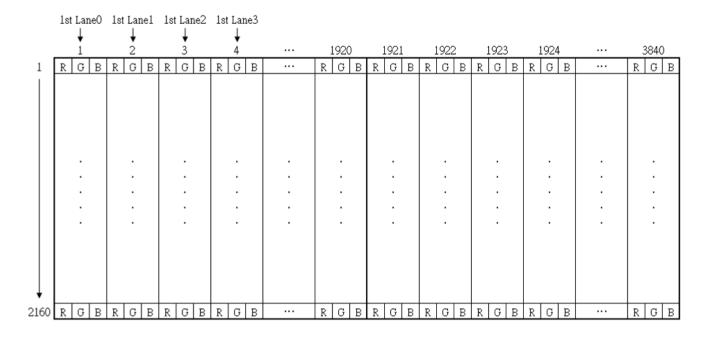

#### 4.3.1 LCD Pixel Format

Following figure show the relationship between the input signals and LCD pixel

format

Note: The module used 4 Lanes eDP interface.

1<sup>st</sup> port:

1<sup>st</sup> Lane0: 1+4n pixel

1<sup>st</sup> Lane1: 2+4n pixel

1<sup>st</sup> Lane2: 3+4n pixel

1<sup>st</sup> Lane3: 4+4n pixel

## 4.3.2 eDP Data Format

# For 10bit data input

| 1st Lanc0       | 1st Lane1       | 1st Lanc2       | 1st Lane3       |

|-----------------|-----------------|-----------------|-----------------|

| R1-9:2          | R2-9:2          | R3-9:2          | R4-9:2          |

| R1-1:0/G1-9:4   | R2-1:0/G2-9:4   | R3-1:0K33-9:4   | R4-1:0IG4-9:4   |

| G1-3:0/B1-9:6   | G2-3:0IB2-9:6   | G3-3:0(B3-9:6   | G4-3:0/B4-9:6   |

| B1-5:0R5-9:8    | B2-5:0IR6-9:8   | B3-5:0IR7-9:8   | B4-5:0IR8-9:8   |

| R5-7x0          | R6-7:0          | R7-7:0          | R8-7:0          |

| G5-9:2          | G6-9:2          | G7-9:2          | G8-9:2          |

| G5-1:0/B5-9:4   | G6-1:0IB6-9:4   | G7-1:0(87-9:4   | G8-1:0fB8-9:4   |

| B5-3:0/R9-9:6   | B6-3x0R10-9:6   | B7-3:0/R11-9:6  | B8-3:0fR12-9:6  |

| R9-5:0(G9-9:8   | R10-5:0(G10-9:8 | R11-5:00711-9:8 | R12-5:0(G12-9:8 |

| G9-7:0          | G10-7:0         | G11-7:0         | G12-7:0         |

| B9-9:2          | B10-9:2         | B11-9:2         | B12-9:2         |

| B9-1:0R13-9:4   | B10-1:0R14-9:4  | B11-1:0IR15-9;4 | B12-1:0R16-9:4  |

| R13-3:0(G13-9:6 | R14-3:0/G14-9:6 | R15-3:00G15-9:6 | R16-3x0lG16-9:6 |

| G13-5:0/B13-9:8 | G14-5:0/B14-9:8 | G15-5;0(B15-9:8 | G16-5:0/B16-9:8 |

| B13-7:0         | B14-7:0         | B15-7:0         | B16-7:0         |

| +               |                 |                 | 4               |

| *               | *3              | 29              | *               |

|                 | *               |                 |                 |

| 9               | - 9             |                 | 4               |

| +               | 4.5             |                 |                 |

## 4.3.3 Color Input Data Reference

The following table is for color versus input data (10bits ). The higher the gray level, the brighter the color.10bits

|       |               |          |    |    |    |                               |    |    |    |    |    |    |     |    | Col | or In      | put [      | )ata |    |        |    |    |    |    |    |     |    |     |    |    |    |       |

|-------|---------------|----------|----|----|----|-------------------------------|----|----|----|----|----|----|-----|----|-----|------------|------------|------|----|--------|----|----|----|----|----|-----|----|-----|----|----|----|-------|

| Color | Gary<br>Level | RED data |    |    |    | GREEN data<br>(MSB:G9,LSB:G0) |    |    |    |    |    |    |     |    |     | dat<br>LSE | a<br>3:B0) | ų.   |    | Remark |    |    |    |    |    |     |    |     |    |    |    |       |

| Į,    |               | R9       | R8 | R7 | R6 | R5                            | R4 | R3 | R2 | R1 | RO | G9 | G8  | G7 | G6  | G5         | G4         | G3   | G2 | G1     | G0 | 89 | 88 | B7 | В6 | B5  | В4 | В3  | B2 | 81 | ВО |       |

| Black | (0.00)        | 0        | 0  | 0  | 0  | 0                             | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0  | 0   | 0          | 0          | 0    | 0  | 0      | 0  | 0  | 0  | 0  | 0  | 0   | 0  | 0   | 0  | 0  | 0  |       |

| White | 550           | 1        | 1  | 1  | 1  | 1                             | 1  | 1  | 1  | 1  | 1  | 1  | 1   | 1  | 1   | 1          | 1          | 1    | 1  | 1      | 1  | 1  | 1  | 1  | 1  | 1   | 1  | 1   | 1  | 1  | 1  |       |

| L511  | 323           | 0        | 1  | 1  | 1  | 1                             | 1  | 1  | 1  | 1  | 1  | 0  | 1   | 1  | 1   | 1          | 1          | 1    | 1  | 1      | 1  | 0  | 1  | 1  | 1  | 1   | 1  | 1   | 1  | 1  | 1  |       |

|       | LO            | 0        | 0  | 0  | 0  | 0                             | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0  | 0   | 0          | 0          | 0    | 0  | 0      | 0  | 0  | 0  | 0  | 0  | 0   | 0  | 0   | 0  | 0  | 0  | Black |

| Red   |               | 8        | 1  | i  | 1  | ă                             | 1  | 18 | 1  | 1  | :  | ï  | i   | 1  | 1   | 8          | :          | 175  | î  | 1      | 1  | i  | 1  | :  | 1  | 1   | 12 | 1   | t  | 1  | 1  |       |

|       | L1023         | 1        | 1  | 1  | 1  | 1                             | 1  | 1  | 1  | 1  | 1  | 0  | 0   | 0  | 0   | 0          | 0          | 0    | 0  | 0      | 0  | 0  | 0  | 0  | 0  | 0   | 0  | 0   | 0  | 0  | 0  |       |

|       | LO            | 0        | 0  | 0  | 0  | 0                             | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0. | .0  | 0          | 0          | 0    | 0. | 0      | 0  | 0  | 0  | 0  | 0  | 0   | 0  | 0   | 0  | 0  | 0  | Black |

| Green | 2             |          | 9  | 1  |    | 8                             | :  |    | 1  | Ŧ  | i  | 4  | 199 | 1  |     | 6          | 1          | 17   | 1  | 1      | Ξ. | 4  | 1  | :  | 4  | 1   | 1  | :   | 1  | į  |    |       |

|       | L1023         | 0        | 0  | 0  | 0  | 0                             | 0  | 0  | 0  | 0  | 0  | 1  | 1   | 1  | 1   | 1          | 1          | 1    | 1  | 1      | 1. | 0  | 0  | 0  | 0  | 0   | 0  | 0   | 0  | 0  | 0  |       |

|       | LO            | 0        | 0  | 0  | 0  | 0                             | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0  | 0   | 0          | 0          | 0    | 0  | 0      | 0  | 0  | 0  | 0  | 0  | 0   | 0  | 0   | 0  | 0  | 0  | Black |

| Blue  | 35            | :        | 3  | 5  | 4  | ः                             | ī. | 2  | 20 | 3  | :  | *  | ः   | :  | 1   | 200        | ÷          | 3    | ÷  | :      | 21 | 8  | 4  | 11 | 28 | \$3 | 10 |     | #  | 往  | 10 |       |

|       | L1023         | 0        | 0  | 0  | 0  | 0                             | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0  | 0   | 0          | 0          | 0    | 0  | 0      | 0  | 1  | 1  | 1  | 1  | 1   | 1  | i19 | 1  | 1  | 1  |       |

# 5. Signal Timing Specification

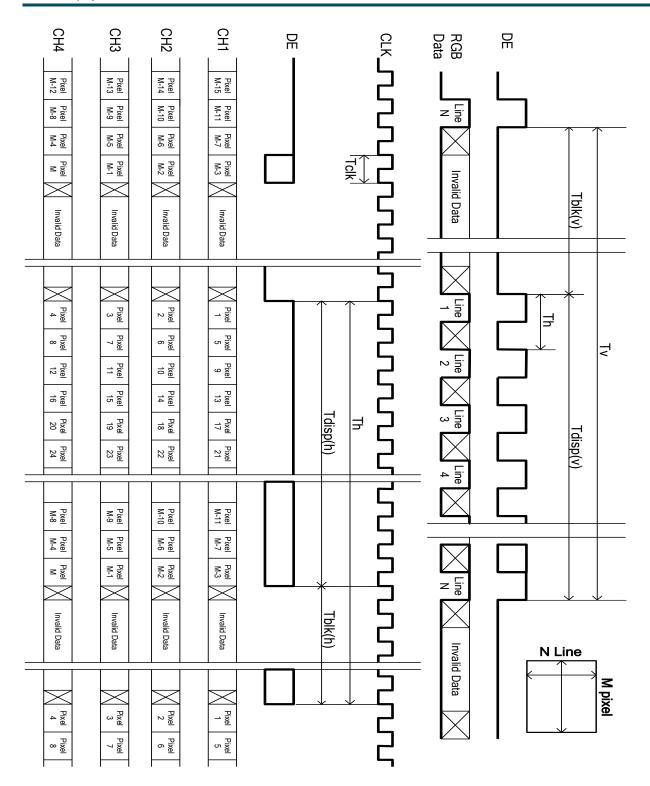

This is the signal timing required at the input of the user connector. All of the interface signal timing should be satisfied with the following specifications for its proper operation.

## 5.1.1. Timing table

The input timing is shown as the following table.

| Symbol    | Description      |           | Min. | Тур.  | Мах.  | Unit | Remark   |

|-----------|------------------|-----------|------|-------|-------|------|----------|

| Tv        |                  | Period    | 2200 | 2250  | 2715  | Th   |          |

| Tdisp (v) |                  | Active    | 2160 | 2160  | 2160  | Th   |          |

| Tblk (v)  | Vertical Section | Blanking  | 40   | 90    | 555   | Th   |          |

| _         |                  | _         | 47   | 60    | 63    |      | Note 3-4 |

| Fv        |                  | Frequency |      |       |       | Hz   | Note 3-7 |

| Th        |                  | Period    | 4000 | 4040  | 4080  | Tclk |          |

| Tdisp (h) | Horizontal       | Active    | 3840 | 3840  | 3840  | Tclk |          |

| Tblk (h)  | Section          | Blanking  | 160  | 200   | 240   | Tclk |          |

| Fh        |                  | Frequency | 120  | 135   | 139.2 | kHz  | Note 3-5 |

| Tclk      | Divol Clock      | Period    | 2.08 | 1.8   | 1.79  | ns   | 1/Fclk   |

| Fclk      | Pixel Clock      | Frequency | 480  | 545.4 | 556.8 | MHz  | Note 3-6 |

|           | Link Rate per L  | ane       |      | 5.4   |       | Gbps |          |

*Note 3-4:* The optimal Vertical Frequency is 60 ~ 63 Hz for best picture quality.

Note 3-5: The equation is listed as following. Please don't exceed the above recommended value.

$$Fh(Typ.) = Fclk(Typ.) / Th(Typ.)$$

$$Fh (Max.) = Fclk (Max.) / Th (Min.)$$

Note 3-6: The equation is listed as following. Please don't exceed the above recommended value.

1st Lane N & 2nd Lane N skew < 200ns

Fclk (Typ.) = Fv (Typ.) x Th (Typ.) x Tv (Typ.)

Fclk (Min. )

$$\leq$$

Fv x Th x Tv  $\leq$  Fclk (Max.)

Note 3-7: The equation is listed as following. Please don't exceed the above recommended value.

$$Fv = Fclk(Typ.) / (Tv x Th)$$

### 5.1.2. Input Timing Diagram

## 5.2 Input interface characteristics

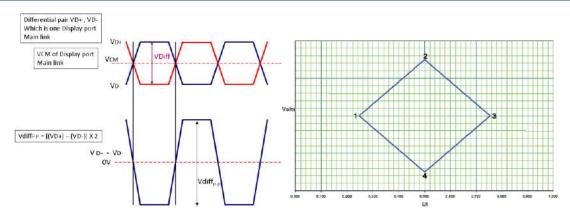

eDP Specification (Follow as VESA DisplayPort Standard Version 1.1 support 5.4Gbps)

## a. DisplayPort main link signal:

|                       | DisplayPort main link                      |     |     |     |      |

|-----------------------|--------------------------------------------|-----|-----|-----|------|

|                       |                                            | Min | Тур | Max | unit |

| Frequency             | Main link Frequency                        | -   | 5.4 | -   | Gbps |

| UI                    | Unit Interval                              | -   | 185 | -   | ps   |

| VCM                   | RX input DC Common Mode Voltage            | -   | 0   | -   | V    |

| VDiff <sub>P-P</sub>  | Peak-to-peak Voltage at a receiving Device | 70  |     |     | mV   |

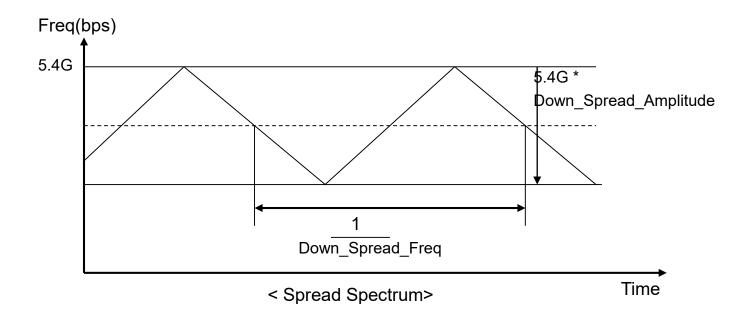

| Down_Spread_Freq      | Link clock down spread frequency           | 30  | -   | 33  | KHz  |

| Down_Spread_Amplitude | Link clock down spread amplitude           | -   | -   | 0.5 | %    |

| Point | Time(UI)    | Voltage |

|-------|-------------|---------|

| 1     | 0.310       | 0       |

| 2     | 0.375~0.625 | 35mV    |

| 3     | 0.690       | 0       |

| 4     | 0.375~0.625 | -35mV   |

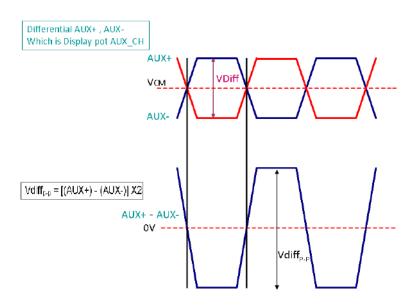

b. DisplayPort AUX\_CH signal:

|                      | DisplayPort AUX_CH                             |      |     |      |      |

|----------------------|------------------------------------------------|------|-----|------|------|

|                      |                                                | Min  | Тур | Max  | unit |

| VCM                  | AUX DC Common Mode Voltage                     | 0    | -   | 2.0  | V    |

| VDiff <sub>P-P</sub> | AUX Peak-to-peak voltage at a receiving device | 0.27 | _   | 1.36 | V    |

## c. DisplayPort VHPD signal:

|      | DisplayPort VHPD |      |     |     |      |

|------|------------------|------|-----|-----|------|

|      |                  | Min  | Тур | Max | unit |

| VHPD | HPD Voltage      | 2.25 | 1   | 3.6 | V    |

|                     | LRX-SKEW-INTRA_PAIR            |     |     |     |      |

|---------------------|--------------------------------|-----|-----|-----|------|

|                     |                                | Min | Тур | Max | unit |

| LRX-SKEW-INTRA_PAIR | Lane Intra-pair Skew Tolerance | -   | -   | 50  | ps   |

## e. Inter-Pair Skew

|                     | LRX-SKEW-INTER_PAIR                  |     |     |      |      |  |  |  |  |  |  |

|---------------------|--------------------------------------|-----|-----|------|------|--|--|--|--|--|--|

|                     |                                      | Min | Тур | Max  | unit |  |  |  |  |  |  |

| LRX-SKEW-INTER_PAIR | Lane-to-Lane Skew at RX package pins | -   | -   | 5200 | ps   |  |  |  |  |  |  |

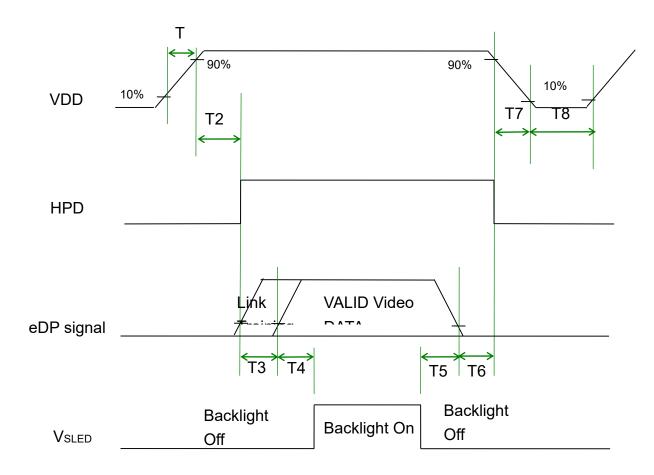

## 5.4 Power Sequence for LCD

VDD power,eDP signal and backlight on/off sequence are as following. eDP signals from any system shall be Hi-Z state when VDD is off.

Power Sequence Timing

| Symbol |     | Value        |     | Unit | Remark              |

|--------|-----|--------------|-----|------|---------------------|

|        |     | <del>-</del> |     |      |                     |

| T1     | 0.5 | -            | 10  | [ms] |                     |

|        | 0   |              |     |      | Sink device AUX CH  |

| T2     |     | -            | 550 | [ms] | must be operational |

|        |     |              |     |      | upon HPD high.      |

| T3 | 0   | - | -   | [ms]    | Note 1 |

|----|-----|---|-----|---------|--------|

| T4 | 500 | - | -   | [ms]    |        |

| T5 | 100 | - | -   | [ms]    |        |

| T6 | 0   |   | 200 | [ms]    | Note 2 |

|    | O   |   | 200 | [1113]  | Note 3 |

| T7 | 0   |   | 200 | [100.0] | Note 3 |

| T7 | 0   | _ | 200 | [ms]    | Note 4 |

Note 1 During T3 period, eDP link training time by customer's system.

Note 2: Recommend setting T6 = 0ms to avoid electronic noise when VDD is off.

Note 3: During T6 and T7 period, please keep the level of input eDP signals with Hi-Z state.

Note 4: Voltage of VDD must decay smoothly after power-off.(customer system decide this value)

## 6. Backlight Specification

#### 6.1 Electrical specification

|    | Item                                       | S                   | ymbol            | Condition      | Min    | Тур      | Max  | Unit | Note |

|----|--------------------------------------------|---------------------|------------------|----------------|--------|----------|------|------|------|

| 1  | Power Supply Input Voltage                 | V                   | /DDB             | -              | 22.8   | 24       | 25.2 | V    | -    |

| 2  | Power Supply Input Current                 |                     | I <sub>DDB</sub> | VDDB=24V       |        | 1.18     | 1.4  | Α    | 1    |

| 3  | Power Consumption                          |                     | P <sub>DDB</sub> | VDDB=24V       |        | 28.3     | 33.6 | Watt | 1    |

| 4  | Inrush Current                             |                     | Irush            | VDDB=24V       |        |          | TBD  | Α    | 2    |

| 5  | Control signal voltage                     | V                   | Hi               | VDDB=24V       | 2      | -        | 3.3  | V    | -    |

| 3  | Control signal voltage                     | V <sub>Signal</sub> | Low              | VDDB-24V       | 0      | -        | 0.8  | V    | 3    |

| 6  | Control signal current                     |                     | Signal           | VDDB=24V       | -      | -        | 1.5  | mA   | -    |

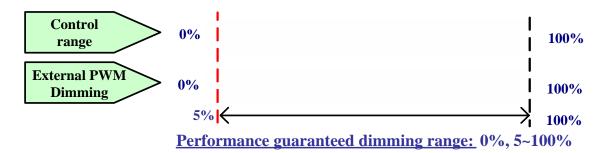

| 7  | External PWM Duty ratio (input duty ratio) | D_                  | EPWM             | VDDB=24V       | 5      | -        | 100  | %    | 4    |

| 8  | External PWM<br>Frequency                  | F_                  | EPWM             | VDDB=24V       | 120    |          | 960  | Hz   | 4    |

| 9  | DET status signal                          | DET                 | н                | VDDB=24V       | Оре    | en Colle | ctor | V    | 5    |

| 9  | DET status signal                          | ושכו                | Lo               | V D D D - 24 V | 0      | -        | 0.8  | V    | 5    |

| 10 | Input Impedance                            | Rin                 |                  | VDDB=24V       | 300    |          |      | Kohm | -    |

| 11 | LED MTTF                                   | L                   | TLED             | -              | 50,000 |          | -    | Hr   | 6    |

Note 1: Dimming ratio= 100%, (Ta=25±5□, Turn on for 45minutes)

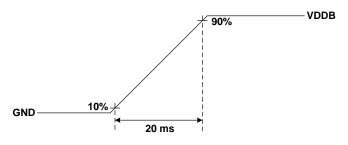

Note 2: MAX input current while DB turn on, measurement condition VDDB rising time=20ms(VDDB: 10%~90%)

Note 3: When BLU off ( VDDB = 24V , VBLON = 0V) , IDDB (max) = 0.1A

Note 4: Less than 5% dimming control is functional well and no backlight shutdown happened

Note 5: Normal: 0~0.8V; Abnormal: Open collector

Note 6: The lifetime (MTTF) is defined as the time which luminance of LED is 50% compared to its original value. [Operating condition: Continuous operating at Ta = 25±2□, for single LED only]

### 6.2 Input Pin Assignment

The P424KVN01.0 module requires [1 power input (14-pin)]

LED DB connector: CI0114M1HRL-NH(CviLux)

| Pin | Symbol | Description                | Note |

|-----|--------|----------------------------|------|

| 1   | VDDB   | Power Supply Input Voltage |      |

| 2   | VDDB   | Power Supply Input Voltage |      |

| 3   | VDDB   | Power Supply Input Voltage |      |

| 4   | VDDB   | Power Supply Input Voltage |      |

| 5   | VDDB   | Power Supply Input Voltage |      |

| 6   | GND    | Ground                     |      |

| 7   | GND    | Ground                     |      |

| 8   | GND    | Ground                     |      |

| 9   | GND    | Ground                     |      |

| 10  | GND    | Ground                     |      |

| 11  | DET    | BLU status detection:      | 1    |

| 12  | VBLON  | BLU On-Off control:        | 2,3  |

| 13  | NC     | NC                         | 4    |

| 14  | PDIM   | External PWM               | 2, 5 |

#### Note1. DET status

| DET            | BLU status |  |

|----------------|------------|--|

| 0 ~ 0.8V       | Normal     |  |

| Open collector | Abnormal   |  |

Recommend pull high R > 10K ohm, pull high voltage VDD = 3.3V

#### Note2. input control signal threshold voltage definition

| Item                         | Symbol | Min. | Тур. | Max. | Unit |

|------------------------------|--------|------|------|------|------|

| Input High Threshold Voltage | VIH    | 2    | -    | 3.3  | V    |

| Input Low Threshold Voltage  | VIL    | 0    | -    | 0.8  | V    |

#### Note3. VBLON

Mode selection

| VBLON     | Note   |

|-----------|--------|

| H or OPEN | BL On  |

| L         | BL Off |

Note4. Please leave this pin unoccupied. It cannot be connected by any signal (Low/GND/High).

#### Note5. PDIM

PWM Dimming range:

External PWM function dimming ratio 0%~100%, Judge condition as below:

- (1) Backlight module must be lighted ON normally.

- (2) All protection function must work normally.

- (3) Uniformity and flicker could be guaranteed at External PWM function dimming ratio 5%~100%

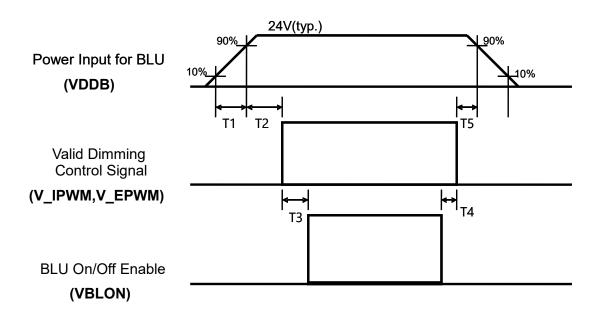

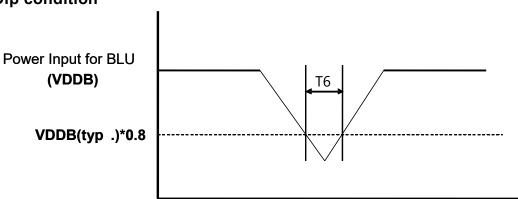

## 6.3 Power Sequence for Backlight

| Parameter | Min | Тур | Max  | Units |

|-----------|-----|-----|------|-------|

| T1        | 20  | -   | -    | ms *1 |

| T2        | 0   | -   | -    | ms    |

| Т3        | 300 |     |      | ms    |

| T4        | 300 | -   | -    | ms    |

| T5        | 0   | -   | -    | ms    |

| Т6        |     | -   | 1000 | ms*2  |

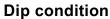

Note:1. T6 describes VDDB dip condition and VDDB couldn't lower than 10% VDDB.

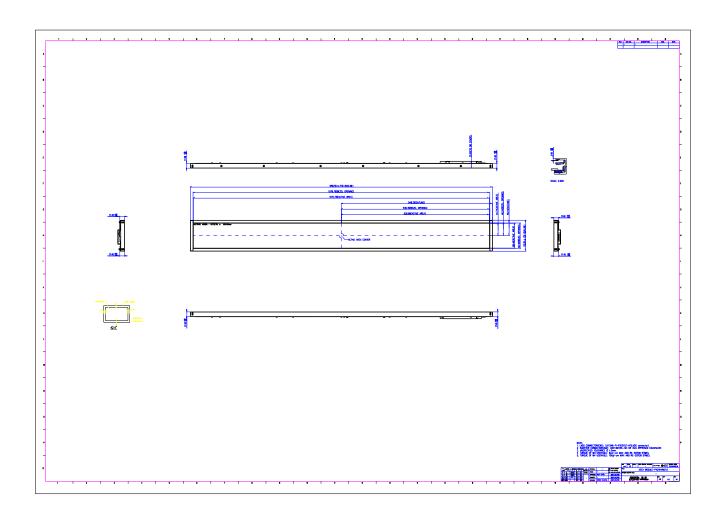

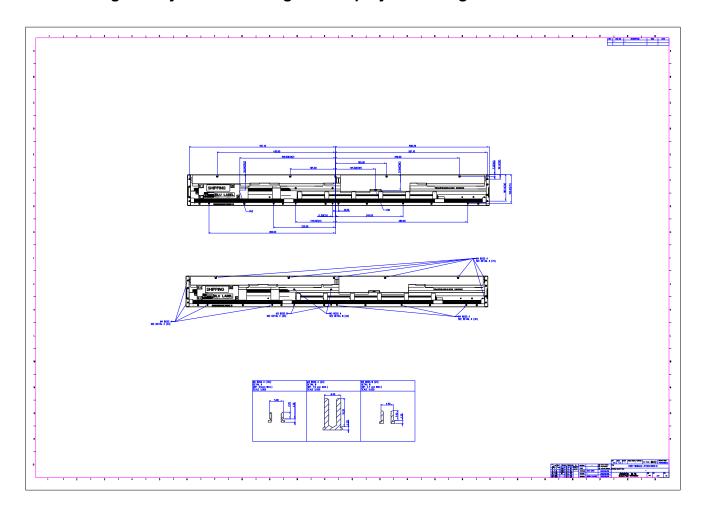

# 7. Mechanical Characteristics

The contents provide general mechanical characteristics for the model P424KVN01.0. In addition, the figures in the next page are detailed mechanical drawing of the LCD.

| ŀ                 | tem           | Dimension              | Unit | Note                      |

|-------------------|---------------|------------------------|------|---------------------------|

|                   | Horizontal    | 1096.58                | mm   |                           |

|                   | Vertical      | 112.28                 | mm   |                           |

|                   | Depth (Dmin)  | 10.7                   | mm   | Front bezel to Back Bezel |

| Outline Dimension | Depth (Dmax)  | 25                     | mm   | Front Bezel to DB         |

|                   | Bezel opening | 1076.78(H) x 92.48 (V) | mm   | Cover                     |

|                   | Bezel Width   | 9.9/9.9/9.9/9.9        | mm   | U/D/L/R                   |

|                   | Display Area  | 1073.8 (H) x 89.5 (V)  | mm   |                           |

| Weight            | 1.9           |                        | Kg   |                           |

# Front View (Draft, Reference Only)

.

# **Back View (Draft, Reference Only)**

This Drawing is subject to be changed after project kicking off.

# 8. Reliability Test Items

|   | Test Item C                          |         | Condition                                                             |

|---|--------------------------------------|---------|-----------------------------------------------------------------------|

| 1 | High temperature storage test        | 3       | 60°C, 500hrs                                                          |

| 2 | Low temperature storage test 3       |         | -20°C, 500hrs                                                         |

| 3 | High temperature operation test      | 3       | 50°C, 500hrs                                                          |

| 4 | Low temperature operation test       | 3       | -10°C, 500hrs                                                         |

| 5 | Vibration test (With carton) 1( PKG) |         | Random wave (1.04Grms 2~200Hz)  Duration : X,Y,Z 20min per axes       |

| 6 | Drop test (With carton)              | 1( PKG) | Height: 457cm  Direction: 1-comer ⋅ 3-edges ⋅ 6-flats ∘ (ASTMD4169-I) |

### 9. International Standard

#### 9.1 Safety

- (1) UL 62368-1 : Audio/video, information and communication technology equipment Part 1: Safety requirements

- (2) IEC 62368-1 : Audio/video, information and communication technology equipment –Part 1: Safety requirements

- (3) EN 62368-1 : Audio/video, information and communication technology equipment –Part 1: Safety requirements

#### 9.2 EMC

- (1) ANSI C63.4 "Methods of Measurement of Radio-Noise Emissions from Low-Voltage Electrical and Electrical Equipment in the Range of 9kHz to 40GHz. "American National standards Institute(ANSI), 1992

- (2) C.I.S.P.R "Limits and Methods of Measurement of Radio Interface Characteristics of Information Technology Equipment." International Special committee on Radio Interference.

- (3) EN 55022 "Limits and Methods of Measurement of Radio Interface Characteristics of Information Technology Equipment." European Committee for Electrotechnical Standardization. (CENELEC), 1998

## 10. Packing

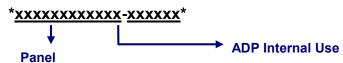

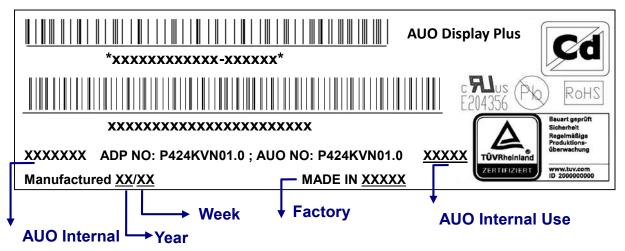

#### 10.1 Definition of Label

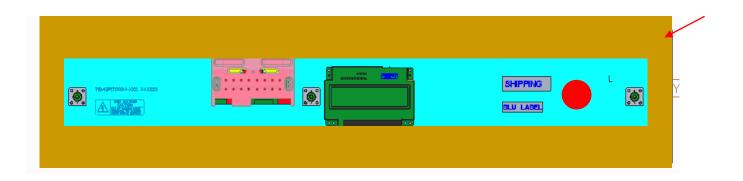

#### A. Panel Label:

#### **Green mark description**

- (1) For Pb Free Product, ADP will add (Pb) for identification.

- (2) For RoHs compatible products, ADP will add RoHS for identification.

Note: The green Mark will be present only when the green documents have been ready by ADP internal green team. (definition of green design follows the ADP green design checklist.)

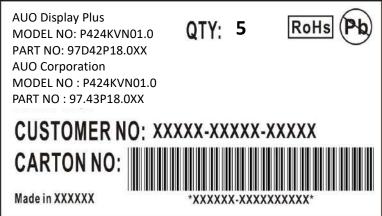

#### **B. Carton Label:**

The label is on the carton as shown below: (Example)

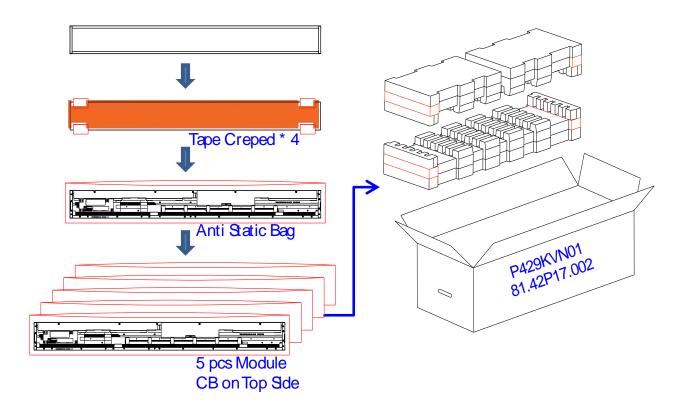

### **Packing Methods**

This following packing information is subject to be changed after project kicking off.

## 10.2 Pallet and Shipment Information

This following packing information is subject to be changed after project kicking off.

|   | Itam                 |                      | Dealing Demark    |             |                                 |

|---|----------------------|----------------------|-------------------|-------------|---------------------------------|

|   | Item                 | Qty.                 | Dimension         | Weight (kg) | Packing Remark                  |

| 1 | Packing BOX          | 5pcs/box             | 1180*360*361mm    | 15          |                                 |

| 2 | Pallet               | 1                    | 1 1200*1100*138mm |             |                                 |

| 3 | Boxes per Pallet     | 9 boxes/pallet (3*3) |                   |             | Sea->Double Pallet              |

| 4 | Panels per Pallet    | 45pcs/pallet         |                   |             | Sea->Double Pallet              |

|   | Pallet after packing | 1 1200*1100*1221mm   |                   | 149.5       | 40DC <sup>,</sup> Double Pallet |

#### 11. Precautions

Please pay attention to the followings when you use this TFT LCD module.

#### 11.1. Mounting Precautions

- (1) You must mount a module using holes arranged in four corners or four sides.

- (2) You should consider the mounting structure so that uneven force (ex. twisted stress) is not applied to module. And the case on which a module is mounted should have sufficient strength so that external force is not transmitted directly to the module.

- (3) Please attach the surface transparent protective plate to the surface in order to protect the polarizer. Transparent protective plate should have sufficient strength in order to the resist external force.

- (4) You should adopt radiation structure to satisfy the temperature specification.

- (5) Acetic acid type and chlorine type materials for the cover case are not desirable because the former generates corrosive gas of attacking the polarizer at high temperature and the latter cause circuit broken by electro-chemical reaction.

- (6) Do not touch, push or rub the exposed polarizer with glass, tweezers or anything harder than HB pencil lead. And please do not rub with dust clothes with chemical treatment. Do not touch the surface of polarizer for bare hand or greasy cloth. (Some cosmetics are detrimental to the polarizer.)

- (7) When the surface becomes dusty, please wipe gently with absorbent cotton or other soft materials like chamois soaks with petroleum benzene. Normal-hexane is recommended for cleaning the adhesives used to attach front/ rear polarizer. Do not use acetone, toluene and alcohol because they cause chemical damage to the polarizer.

- (8) Wipe off saliva or water drops as soon as possible. Their long time contact with polarizer causes deformations and color fading.

- (9) Do not open the case because inside circuits do not have sufficient strength.

#### 11.2. Operating Precautions

- (1) The spike noise causes the mis-operation of circuits. It should be lower than following voltage: V=±200mV(Over and under shoot voltage)

- (2) Response time depends on the temperature. (In lower temperature, it becomes longer.)

- (3) Brightness depends on the temperature. (In lower temperature, it may become lower.) And in lower temperature, response time (required time that brightness is stable after turned on) becomes longer.

- (4) Be careful for condensation at sudden temperature change. Condensation makes damage to polarizer or electrical contacted parts. And after fading condensation, smear or spot will occur.

- (5) When fixed patterns are displayed for a long time, remnant image is likely to occur.

- (6) Module has high frequency circuits. Sufficient suppression to the electromagnetic

interference shall be done by system manufacturers. Grounding and shielding methods may be important to minimize the interface.

(7) The conductive material and signal cables are kept away from LED driver inductor to prevent abnormal display, sound noise and temperature rising.

#### 11.3. Operating Condition for Public Information Display

The device listed in the product specification is designed and manufactured for PID (Public Information Display) application. To optimize module's lifetime and function, below operating usages are required.

- (1) Normal operating condition

- A. Operating temperature: -20~60 □

- B. Operating humidity: 10~90%

- C. Display pattern: dynamic pattern (Real display).Note) Long-term static display would cause image sticking.

- (2) Operation usage to protect against image sticking due to long-term static display.

- A. Suitable operating time: under 24 hours a day

- B. Liquid Crystal refresh time is required. Cycling display between 5 minutes' information (static) display and 10 seconds' moving image.

- C. Periodically change background and character (image) color.

- D. Avoid combination of background and character with large different luminance.

- (3) Periodically adopt one of the following actions after long time display.

- A. Running the screen saver (motion picture or black pattern)

- B. Power off the system for a while

- (4) LCD system is required to place in well-ventilated environment. Adapting active cooling system is highly recommended.

- (5) Product reliability and functions are only guaranteed when the product is used under right operation usages. If product will be used in extreme conditions, such as high temperature/ humidity, display stationary patterns, or long operation time etc..., it is strongly recommended to contact ADP for filed application engineering advice. Otherwise, its reliability and function may not be guaranteed. Extreme conditions are commonly found at airports, transit stations, banks, stock market and controlling systems.

#### 11.4. Electrostatic Discharge Control

Since a module is composed of electronic circuits, it is not strong to electrostatic discharge. Make certain that treatment persons are connected to ground through wristband etc. And don't touch interface pin directly.

#### 11.5. Precautions for Strong Light Exposure

- (1) Strong light exposure causes degradation of polarizer and color filter.

- (2) To keep display function well as a digital signage application, especially the component of TFT is very sensitive to sunlight, it is necessary to set up blocking device protecting panel from radiation of ambient environment.

#### 11.6. Storage

When storing modules as spares for a long time, the following precautions are necessary.

- (1) Store them in a dark place. Do not expose the module to sunlight or fluorescent light. Keep the temperature between 5□ and 35□ at normal humidity.

- (2) The polarizer surface should not come in contact with any other object. It is recommended that they be stored in the container in which they were shipped.

- (3) Storage condition is guaranteed under packing conditions.

- (4) The phase transition of Liquid Crystal in the condition of the low or high storage temperature will be recovered when the LCD module returns to the normal condition.

#### 11.7. Handling Precautions for Protection Film

- (1) The protection film is attached to the bezel with a small masking tape. When the protection film is peeled off, static electricity is generated between the film and polarizer. This should be peeled off slowly and carefully by people who are electrically grounded and with well ion-blown equipment or in such a condition, etc.

- (2) When the module with protection film attached is stored for a long time, sometimes there remains a very small amount of glue still on the bezel after the protection film is peeled off.

- (3) You can remove the glue easily. When the glue remains on the bezel or its vestige is recognized, please wipe them off with absorbent cotton waste or other soft material like chamois soaked with normal-hexane.

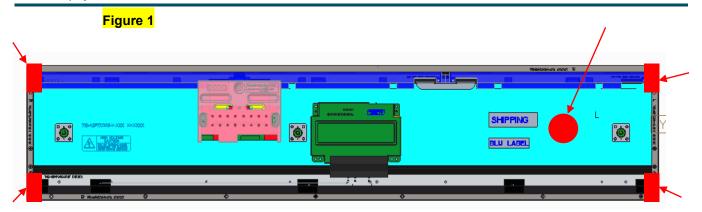

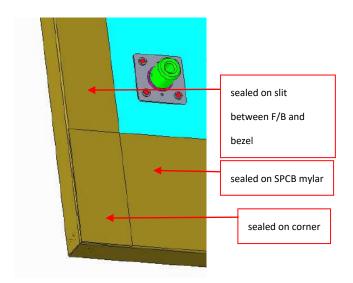

#### 11.8. Dust Resistance

- ADP module dust test is conducted with marked holes (see Figure 1) sealed to comply with JIS

- Module users should design set with these holes used/sealed (if not used) or covered by set

mechanism to prevent dust from entering. The ADP testing procedure cannot replicate all

different real world scenarios, module users should apply set dust resistance solution to meet

users' requirement.

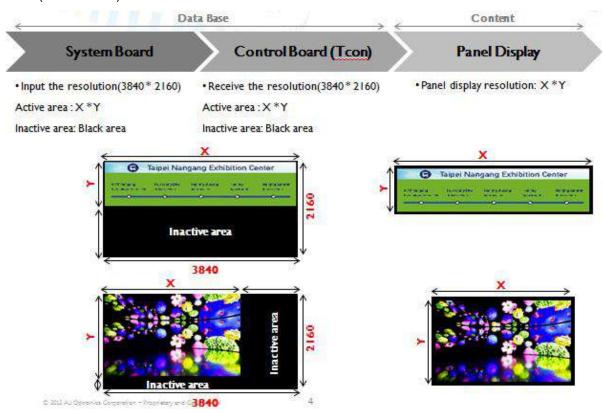

# 12. Appendix I: Content Format

UHD (3840 x 2160) / eDP interface

# 13. Appendix II: Tartan (42.4" pixel arrangement)

- To maximize the production capacity for 42.4", there are two types of pixel arrangement designs. One is (R,G,B) and the other is (B,G,R).

- There are two kinds pixel arrangement LCM for P424KVN01.0