# **OS81210**

# Intelligent Network Interface Controller for 50 Mbit/s Automotive Networks

#### Features

- Complete 50 Mbit/s synchronous network interface

- · Embedded network management functions

- Network protection mode

- Hardware & application watchdog timer

- Intelligent muting

- Diagnostics

- Fallback Operation

- · IEEE MAC addressing and Ethernet channel

- Universal Serial Bus (USB) Port supports USB 2.0 High-speed upstream data transfers using either:

- USB 2.0 physical layer

- High-Speed Inter-Chip (HSIC) physical layer

- Media Local Bus (MediaLB<sup>®</sup>) Port

- Eases inter-chip communication and streaming

- MediaLB 3-pin interface at speeds up to 1024xFs

- I<sup>2</sup>C<sup>™</sup> Control Port inter-chip message exchange

- Streaming Port supports synchronous, fixed latency data exchange for a variety of serial audio formats including time-division multiplex (TDM) and pulse density modulation (PDM)

- SPI Port supports asynchronous and control packets

- General Purpose I/O (GPIO) Port

- Remote control and configuration for operation without a local External Host Controller.

- I<sup>2</sup>C (master) message tunneling

- GPIO port control

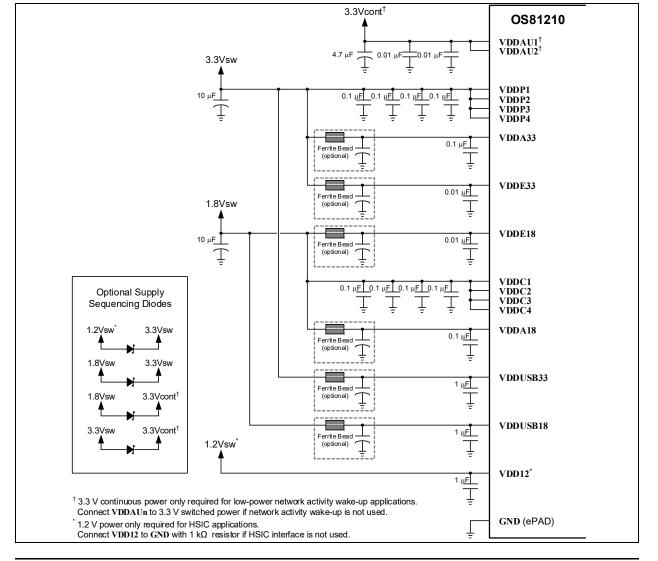

- Operating voltages 3.3 V/1.8 V (and 1.2 V for HSIC)

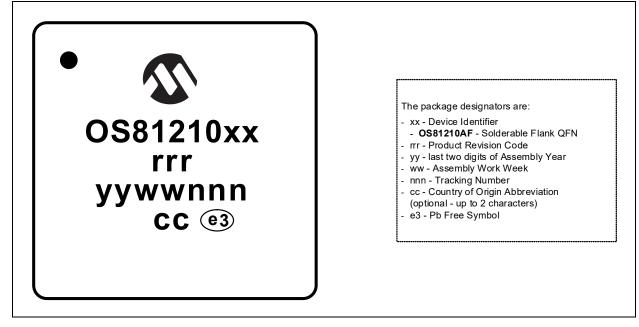

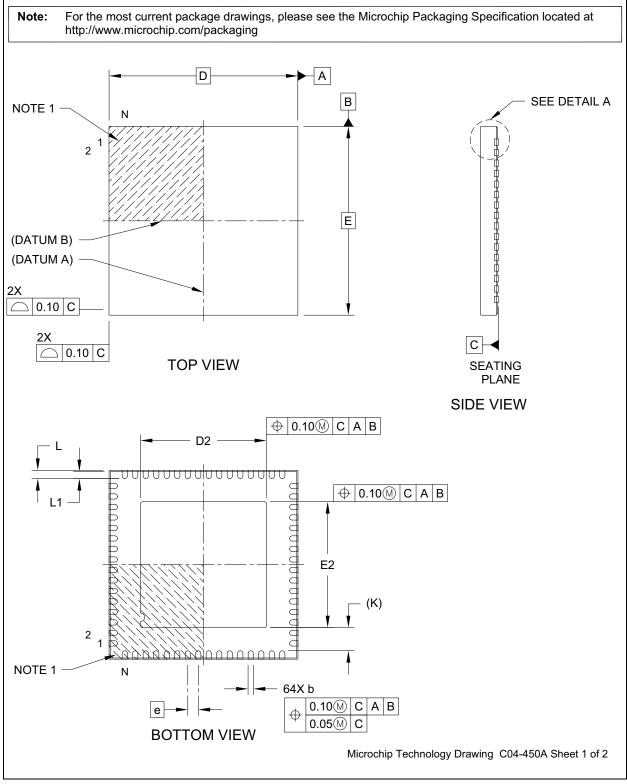

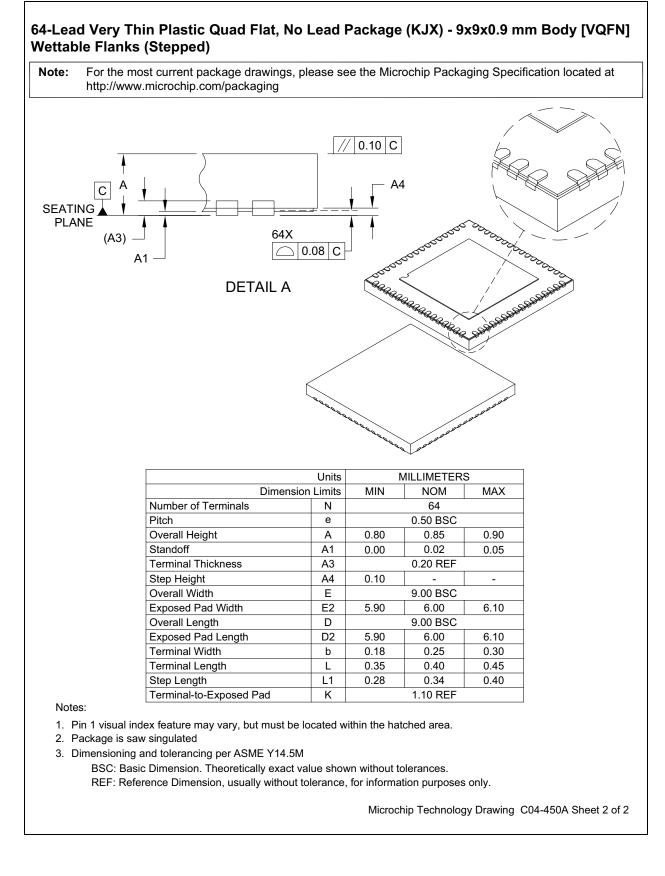

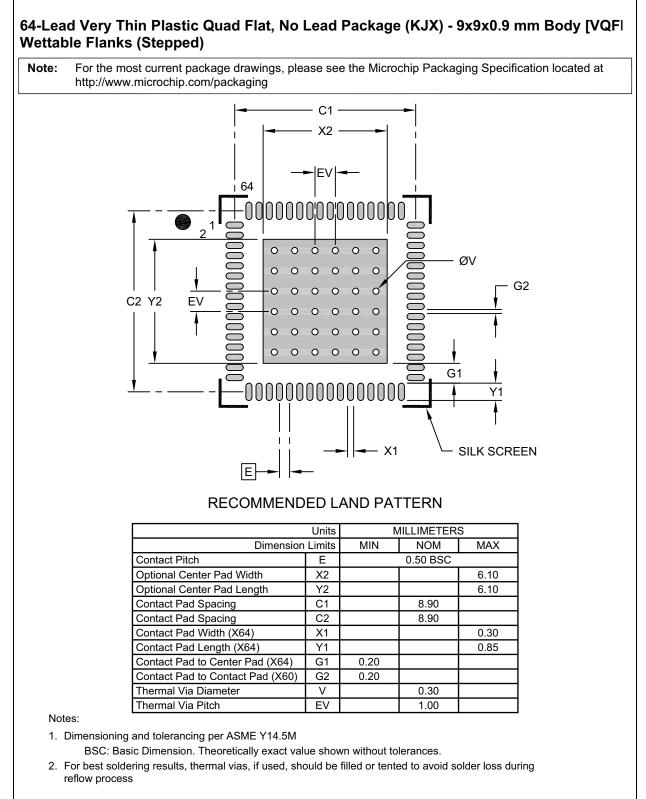

- · Available in 64-pin QFN package with exposed pad

- -40 to +125 °C junction temperature

#### Conformity

• This document applies to hardware revision B2B

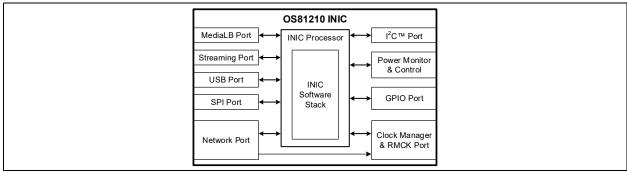

#### FIGURE: OS81210 BLOCK DIAGRAM

• Automotive infotainment network nodes including head unit, instrument cluster, amplifier, and rear seat entertainment.

#### **General Description**

The OS81210 is a highly integrated *Intelligent Network Interface Controller* (INIC) for 50 Mbit/s INICnet-based automotive networks with a transformer-less balanced media physical layer (bPHY) optimized for unshielded twisted pair (UTP) copper wire.

The INIC provides encapsulation of all low-level functions necessary to develop a network-compliant device, significantly simplifying network implementation in a node. Integration of the *INIC Software Stack* into the INIC provides network-compliant real-time behavior. The *INIC Software Stack* significantly relieves the External Host Controller (EHC) from real-time processing tasks. Supervision of the application is also provided, including a protection mode that is entered when an application is not present (i.e. start-up) or the EHC malfunctions. This protection mode prevents application malfunctions from influencing the integrity of the network and the system.

When the EHC is engaged, a message-based interface, as opposed to a register-based interface, is available for communication with INIC. A unified and centralized network management software stack (UNICENS) is available for the EHC to build a complete, lean, system solution.

The INIC conforms to the ISO 21806 standard developed by the International Organization for Standardization ( $ISO^{(B)}$ ).

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS300000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# TABLE OF CONTENTS

| 1    | OS81210 PINOUT                           | 5   |

|------|------------------------------------------|-----|

| 2    | EQUIVALENT SCHEMATICS FOR PINS           | 9   |

| 3    | OVERVIEW                                 | 11  |

| 4    | INIC PROCESSOR                           | 22  |

| 5    | I <sup>2</sup> C PORT                    |     |

| 6    | MediaLB PORT                             |     |

| 7    | STREAMING PORT                           |     |

| 8    | USB PORT                                 | 41  |

| 9    | SPI PORT                                 | 43  |

| 10   | EXTERNAL POWER MANAGEMENT                | 61  |

| 11   | CLOCK MANAGER                            |     |

| 12   | RMCK PORT                                |     |

| 13   | GENERAL PURPOSE INPUT/OUTPUT (GPIO) PORT | 65  |

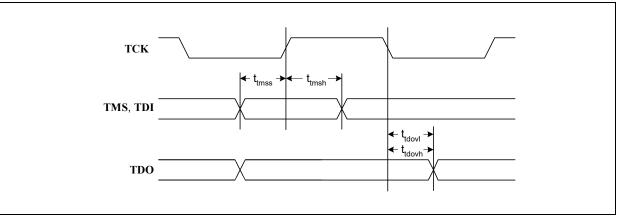

| 14   | JTAG PORT                                | 68  |

| 15   | ELECTRICAL CHARACTERISTICS               | 71  |

| 16   | APPLICATION INFORMATION                  |     |

| 17   | PACKAGING INFORMATION                    | 103 |

| APPE | NDIX A REFERENCES                        | 107 |

| APPE | ENDIX B REVISION HISTORY                 |     |

| APPE | NDIX C LIST OF ACRONYMS                  | 110 |

| APPE | NDIX D LIST OF TABLES                    |     |

| APPE | NDIX E LIST OF FIGURES                   | 112 |

# Conventions

The following abbreviations and symbols are used to improve readability.

| Example                 | Description                                                                                                                                                    |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIT                     | Name of a single bit within a field                                                                                                                            |

| FIELD.BIT               | Name of a single bit (BIT) in FIELD                                                                                                                            |

| ху                      | Range from x to y, inclusive                                                                                                                                   |

| BITS[m:n]               | Groups of bits from m to n, inclusive                                                                                                                          |

| PIN                     | Pin Name                                                                                                                                                       |

| SIGNAL                  | Signal Name                                                                                                                                                    |

| msb, lsb                | Most significant bit, least significant bit                                                                                                                    |

| MSB, LSB                | Most significant byte, least significant byte                                                                                                                  |

| zzzzb                   | Binary number (value zzzz)                                                                                                                                     |

| 0xzzz                   | Hexadecimal number (value zzz)                                                                                                                                 |

| zzh                     | Hexadecimal number (value zz)                                                                                                                                  |

| rsvd                    | Reserved memory location. Must write 0, read value indeterminate                                                                                               |

| code                    | Instruction code, or API function or parameter                                                                                                                 |

| Multi Word Name         | Used for multiple words that are considered a single unit, such as:<br>Resource Allocate message, or Connection Label, or Decrement Stack Pointer instruction. |

| Section Name            | Emphasis, Reference, Section or Document name.                                                                                                                 |

| VAL                     | Over-bar indicates active low pin or register bit                                                                                                              |

| х                       | Don't care                                                                                                                                                     |

| <parameter></parameter> | <> indicate a Parameter is optional or is only used under some conditions                                                                                      |

| {,Parameter}            | Braces indicate Parameter(s) that repeat one or more times.                                                                                                    |

| [Parameter]             | Brackets indicate a nested Parameter. This Parameter is not real and actually decodes into one or more real parameters.                                        |

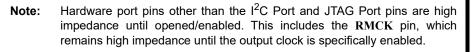

# 1.0 OS81210 PINOUT

Input pins must not be left floating; therefore, they must be driven, have pull-ups or pull-downs, or connected directly to a power pin or ground.

Digital pins that can be configured as outputs (i.e., pin types  $D_{OUT}$ ,  $D_{OUTD}$ ,  $D_{OUTZ}$ ,  $D_{I/O}$ , and  $D_{I/OD}$ ) are high impedance during power-up/reset. The pin types shown in Table 1-1 are the values after power-up/reset.

| TABLE 1-1: | <b>OS81210 PIN ALLOCATION TABLE</b> |

|------------|-------------------------------------|

|------------|-------------------------------------|

| Pin | Name                | Туре             | HW Port | Description                                           |

|-----|---------------------|------------------|---------|-------------------------------------------------------|

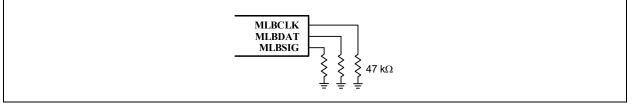

| 1   | MLBCLK <sup>2</sup> | D <sub>OUT</sub> | MediaLB | Singled-ended Clock line for MediaLB 3-pin Interface  |

| 2   | MLBSIG <sup>2</sup> | D <sub>I/O</sub> | MediaLB | Singled-ended Signal line for MediaLB 3-pin Interface |

| 3   | MLBDAT <sup>2</sup> | D <sub>I/O</sub> | MediaLB | Singled-ended Data line for MediaLB 3-pin Interface   |

| 4   | VDDP1               |                  |         | 3.3 V periphery power supply (digital)                |

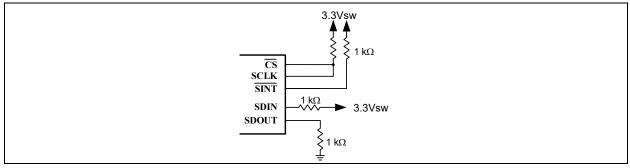

| 5   | SDIN                | D <sub>IN</sub>  | SPI     | Data In (MOSI - Master Out, Slave In)                 |

| 5   | GP3                 | D <sub>I/O</sub> | GPIO    | General Purpose Input/Output 3                        |

| 6   | SDOUT               | D <sub>OUT</sub> | SPI     | Data Out (MISO - Master In, Slave Out)                |

| 0   | GP4                 | D <sub>I/O</sub> | GPIO    | General Purpose Input/Output 4                        |

Note 1: Pull-up resistor required.

| Pin | Name                | Туре              | HW Port | Description                                                                                                                                                                                                                                                                   |

|-----|---------------------|-------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _   | SCLK                | D <sub>IN</sub>   | SPI     | Clock                                                                                                                                                                                                                                                                         |

| 7   | GP5                 | D <sub>I/O</sub>  | GPIO    | General Purpose Input/Output 5                                                                                                                                                                                                                                                |

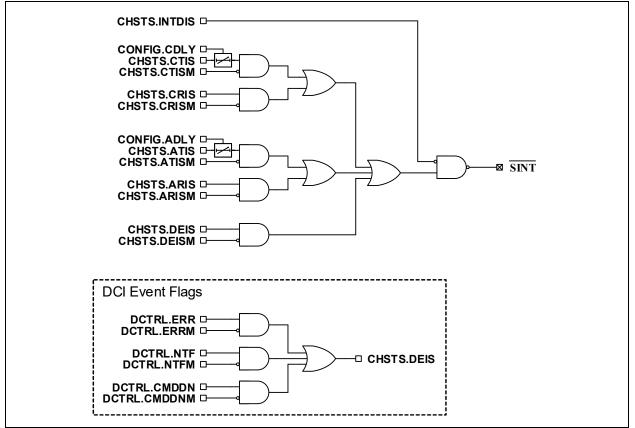

| -   | SINT                | D <sub>OUT</sub>  | SPI     | Interrupt (active low)                                                                                                                                                                                                                                                        |

| 8   | GP6                 | D <sub>I/O</sub>  | GPIO    | General Purpose Input/Output 6                                                                                                                                                                                                                                                |

| •   | CS                  | D <sub>IN</sub>   | SPI     | Chip Select (active low)                                                                                                                                                                                                                                                      |

| 9   | GP7                 | D <sub>I/O</sub>  | GPIO    | General Purpose Input/Output 7                                                                                                                                                                                                                                                |

| 10  | VDDC1               |                   |         | 1.8 V core power supply (digital)                                                                                                                                                                                                                                             |

| 11  | TMS <sup>1</sup>    | D <sub>IN</sub>   | JTAG    | Test Mode Select                                                                                                                                                                                                                                                              |

| 40  | TDO <sup>1</sup>    | D <sub>OUTZ</sub> | JTAG    | Test Data Output                                                                                                                                                                                                                                                              |

| 12  | DINT <sup>1</sup>   | D <sub>OUTD</sub> |         | Debug Interrupt (active low)                                                                                                                                                                                                                                                  |

| 40  | TDI <sup>1</sup>    | D <sub>IN</sub>   | JTAG    | Test Data Input                                                                                                                                                                                                                                                               |

| 13  | DSDA <sup>1</sup>   | D <sub>I/OD</sub> |         | Debug Data                                                                                                                                                                                                                                                                    |

|     | TCK <sup>1</sup>    | D <sub>IN</sub>   | JTAG    | Test Clock Input                                                                                                                                                                                                                                                              |

| 14  | DSCL <sup>1</sup>   | D <sub>I/OD</sub> |         | Debug Clock                                                                                                                                                                                                                                                                   |

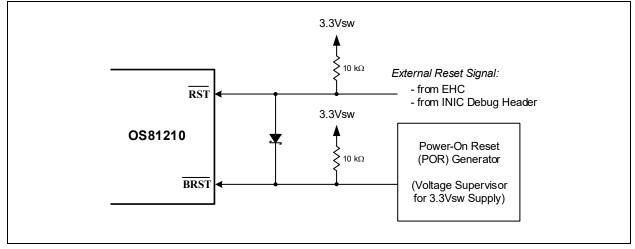

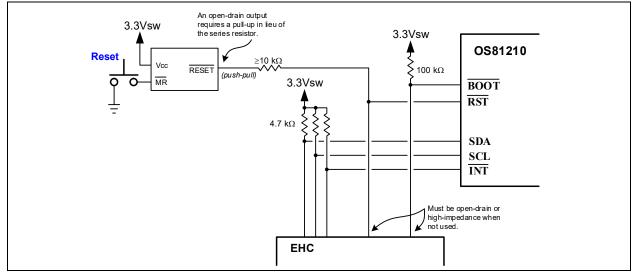

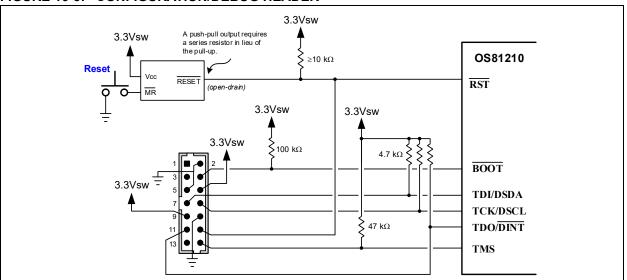

| 15  | RST                 | D <sub>IN</sub>   |         | Hardware Reset Input (active low). (Pull-up resistor to <b>VDDPn</b> supply should be used when not driven high by an external device. A series resistor should be used in lieu of the pull-up when always driven by an external device.)                                     |

| 16  | GP10                | D <sub>I/O</sub>  | GPIO    | General Purpose Input/Output 10                                                                                                                                                                                                                                               |

| 17  | GP13                | D <sub>I/O</sub>  | GPIO    | General Purpose Input/Output 13                                                                                                                                                                                                                                               |

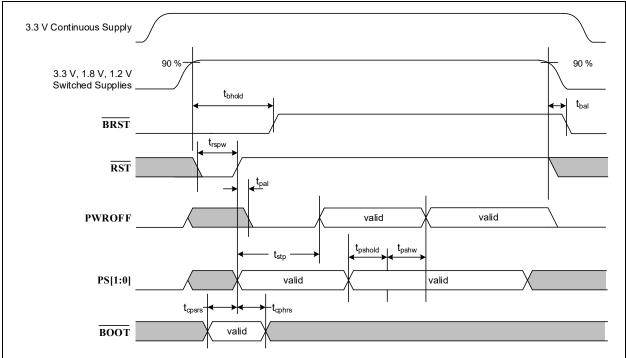

| 18  | PWROFF <sup>1</sup> | D <sub>OUTD</sub> |         | External Power Management Power-Down Indicator. This pin is driven<br>low by INIC after initialization. When high, indicates that the INIC<br>Processor is ready to be shut down. A pull-up resistor is required when<br>used. If not used, this pin may be left unconnected. |

| 19  | MUTE <sup>1</sup>   | D <sub>OUTD</sub> |         | Mute Indicator Output. A pull-up resistor is required when used. If not used, this pin may be left unconnected.                                                                                                                                                               |

|     | GP8                 | D <sub>I/O</sub>  | GPIO    | General Purpose Input/Output 8                                                                                                                                                                                                                                                |

|     | ERR                 | D <sub>OUT</sub>  | Network | Network Error Indicator Output. This pin is driven high when the network<br>is unlocked. When low, this pin indicates the INIC is locked to the<br>network.                                                                                                                   |

| 20  | BOOT <sup>1</sup>   | D <sub>IN</sub>   |         | Configuration Pin. This pin is attached to the configuration/debug<br>header and used by the Microchip INICkit Tool [3] to load initial<br>configuration data into INIC. May also be connected to the EHC to allow<br>in-system configuration of the INIC.                    |

| 21  | VDDC2               |                   |         | 1.8 V core power supply (digital)                                                                                                                                                                                                                                             |

| 22  | VDDP2               |                   |         | 3.3 V periphery power supply (digital)                                                                                                                                                                                                                                        |

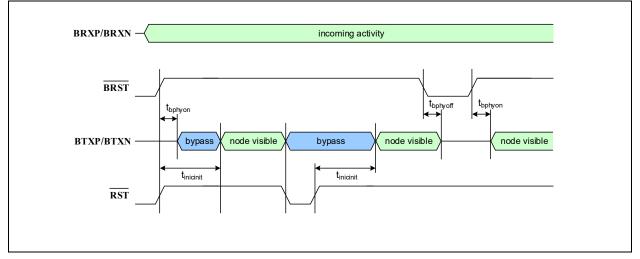

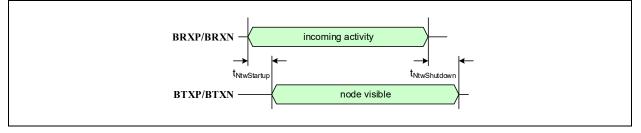

| 23  | BTXP                | A <sub>I/O</sub>  | Network | Positive (differential) bPHY network transmitter output                                                                                                                                                                                                                       |

| 24  | BTXN                | A <sub>I/O</sub>  | Network | Negative (differential) bPHY network transmitter output                                                                                                                                                                                                                       |

| 25  | VDDAU1              |                   |         | 3.3 V continuous power supply (analog)                                                                                                                                                                                                                                        |

| 26  | VDDE18              |                   |         | 1.8 V bPHY power supply (analog)                                                                                                                                                                                                                                              |

| 27  | VDDE33              | 1                 |         | 3.3 V bPHY power supply (analog)                                                                                                                                                                                                                                              |

| 28  | BRST <sup>1</sup>   | A <sub>I/O</sub>  | Network | Hardware Reset Input (active low) for the Balanced Media Physical<br>Layer. When asserted, the transmitter output is disabled. A pull-up<br>resistor to <b>VDDPn</b> is required.                                                                                             |

| 29  | BRXN                | A <sub>I/O</sub>  | Network | Negative (differential) bPHY network receiver input                                                                                                                                                                                                                           |

| 30  | BRXP                | A <sub>I/O</sub>  | Network | Positive (differential) bPHY network receiver input                                                                                                                                                                                                                           |

| 31  | NC                  | 1/0               |         | No Connect. This pin must be left open and floating.                                                                                                                                                                                                                          |

# TABLE 1-1: OS81210 PIN ALLOCATION TABLE (CONTINUED)

Note 1: Pull-up resistor required.

| Pin | Name               | Туре              | HW Port          | Description                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|-----|--------------------|-------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 32  | VDDAU2             |                   |                  | 3.3 V continuous power supply (analog)                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 33  | VDDA33             |                   |                  | 3.3 V power supply (analog)                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 34  | VDDA18             |                   |                  | 1.8 V power supply (analog)                                                                                                                                                                                                                                                                                                                                   |  |  |  |

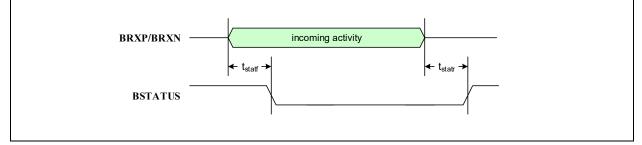

|     |                    |                   |                  | bPHY Network Activity Status Output used during wake-up:                                                                                                                                                                                                                                                                                                      |  |  |  |

| 35  | BSTATUS            | D <sub>OUT</sub>  | Network          | - Driven low when a valid signal is detected                                                                                                                                                                                                                                                                                                                  |  |  |  |

|     |                    |                   |                  | - Driven high to VDDAUn when a qualified signal is not present                                                                                                                                                                                                                                                                                                |  |  |  |

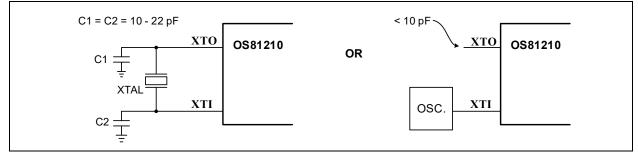

| 36  | ХТО                | A <sub>I/O</sub>  |                  | Crystal Oscillator Output                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 37  | XTI                | A <sub>I/O</sub>  |                  | Crystal Oscillator Input or External CMOS Clock Input                                                                                                                                                                                                                                                                                                         |  |  |  |

| 38  | PS0                | D <sub>IN</sub>   |                  | External Power Management Status Bit 0                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 30  | GP1                | D <sub>I/O</sub>  | GPIO             | General Purpose Input/Output 1                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 20  | PS1                | D <sub>IN</sub>   |                  | External Power Management Status Bit 1                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 39  | GP2                | D <sub>I/O</sub>  | GPIO             | General Purpose Input/Output 2                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 40  | GP12               | D <sub>I/O</sub>  | GPIO             | General Purpose Input/Output 12                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 41  | GP14               | D <sub>I/O</sub>  | GPIO             | General Purpose Input/Output 14                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 42  | VDDC3              | ., 0              |                  | 1.8 V core power supply (digital)                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 43  | VDDP3              |                   |                  | 3.3 V periphery power supply (digital)                                                                                                                                                                                                                                                                                                                        |  |  |  |

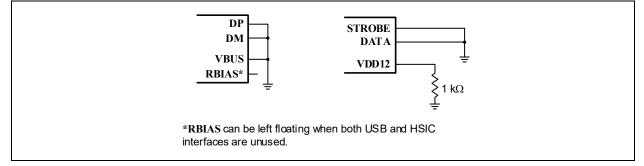

| 44  | STROBE             |                   | USB              | Strobe line for HSIC physical interface. Connect to GND when HSIC is                                                                                                                                                                                                                                                                                          |  |  |  |

| 44  | STRUBE             | D <sub>I/O</sub>  | 058              | not used.                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 45  | DATA               | D <sub>I/O</sub>  | USB              | Data line for HSIC physical interface. Connect to GND when HSIC is used.                                                                                                                                                                                                                                                                                      |  |  |  |

| 46  | VDD12              |                   |                  | 1.2 V power supply for HSIC physical interface transceiver. Connect to GND through a 1 k $\Omega$ resistor when HSIC is not used.                                                                                                                                                                                                                             |  |  |  |

| 47  | DM                 | A <sub>I/O</sub>  | USB              | Negative (differential) data line for USB physical interface. Connect to GND when the USB physical interface is not used.                                                                                                                                                                                                                                     |  |  |  |

| 48  | DP                 | A <sub>I/O</sub>  | USB              | Positive (differential) data line for USB physical interface. Connect to <b>GND</b> when the USB physical interface is not used.                                                                                                                                                                                                                              |  |  |  |

| 49  | VDDUSB33           |                   |                  | 3.3 V USB power supply (analog)                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 50  | RBIAS <sup>2</sup> | A <sub>I/O</sub>  | USB              | Connect to GND through a 12 k $\Omega$ resistor (0.5 %, 1/16 W, $\leq \pm$ 100 ppm<br>This pin may be left unconnected when both the USB and HSIC physical<br>interfaces are not used.                                                                                                                                                                        |  |  |  |

| 51  | VDDUSB18           |                   |                  | 1.8 V USB power supply (analog)                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 52  | VBUS               | D <sub>IN</sub>   | USB              | USB Bus Power State Indicator Input. The application should drive this pin high when an external USB Host Controller is present. Note that thi pin is not 5 V tolerant and must not be connected directly to USB bus power. This signal is ignored when using the HSIC physical interface. Connect to <b>GND</b> when the USB physical interface is not used. |  |  |  |

| 53  | RMCK               | D <sub>OUT</sub>  | RMCK             | Recovered Master Clock Output                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|     |                    |                   | l <sup>2</sup> C | Interrupt (active low). Indicates a service request from the EHC when                                                                                                                                                                                                                                                                                         |  |  |  |

| 54  |                    | D <sub>OUTD</sub> |                  | the Control Port is operating as an I <sup>2</sup> C slave.                                                                                                                                                                                                                                                                                                   |  |  |  |

|     | GP0                | D <sub>I/O</sub>  | GPIO             | General Purpose Input/Output 0                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 55  | SCL <sup>1</sup>   | D <sub>I/OD</sub> | l <sup>2</sup> C | Clock                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 56  | SDA <sup>1</sup>   | D <sub>I/OD</sub> | l <sup>2</sup> C | Data                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 57  | VDDC4              |                   |                  | 1.8 V core power supply (digital)                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 58  | VDDP4              |                   |                  | 3.3 V periphery power supply (digital)                                                                                                                                                                                                                                                                                                                        |  |  |  |

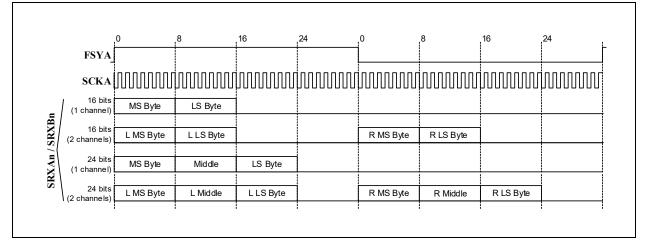

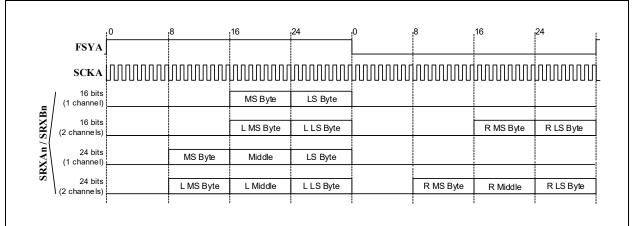

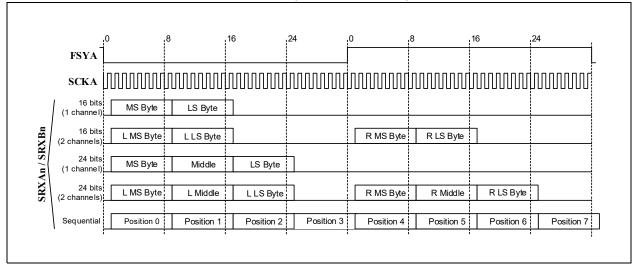

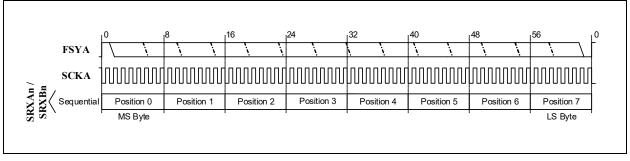

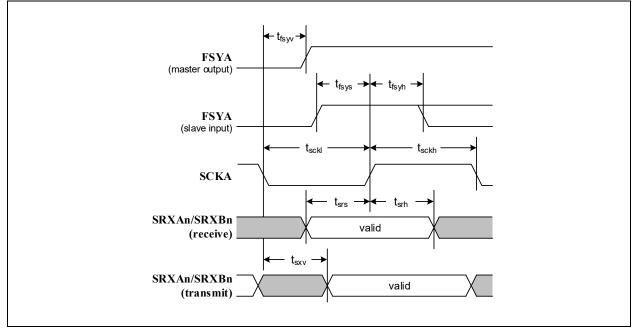

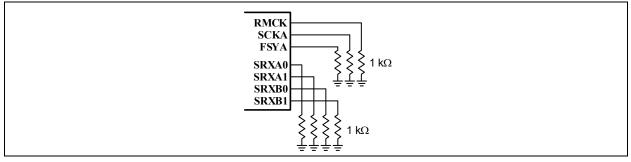

| 59  | FSYA               | D <sub>I/O</sub>  | Streaming        | Frame Sync for Streaming Port A and B                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 60  | SCKA               | D <sub>I/O</sub>  | Streaming        | Bit Clock for Streaming Port A and B                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 61  | SRXA0              | D <sub>I/O</sub>  | Streaming        | Data I/O Signal 0 for Streaming Port A                                                                                                                                                                                                                                                                                                                        |  |  |  |

TABLE 1-1: OS81210 PIN ALLOCATION TABLE (CONTINUED)

Note 1: Pull-up resistor required.

| Pin  | Name  | Туре             | HW Port   | Description                                                                                                                                                     |

|------|-------|------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 62   | SRXA1 | D <sub>I/O</sub> | Streaming | Data I/O Signal 1 for Streaming Port A                                                                                                                          |

| 63   | SRXB0 | D <sub>I/O</sub> | Streaming | Data I/O Signal 0 for Streaming Port B                                                                                                                          |

| 64   | SRXB1 | D <sub>I/O</sub> | Streaming | Data I/O Signal 1 for Streaming Port B                                                                                                                          |

| ePAD | GND   |                  |           | The exposed paddle on the bottom side of the QFN package is the primary ground for the OS81210 and must be connected to ground on the PCB for proper operation. |

TABLE 1-1: OS81210 PIN ALLOCATION TABLE (CONTINUED)

**Note 1:** Pull-up resistor required.

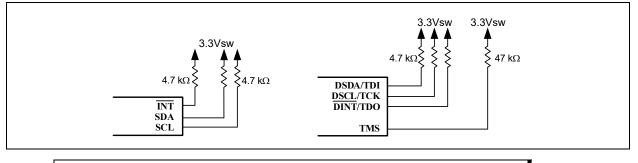

# 2.0 EQUIVALENT SCHEMATICS FOR PINS

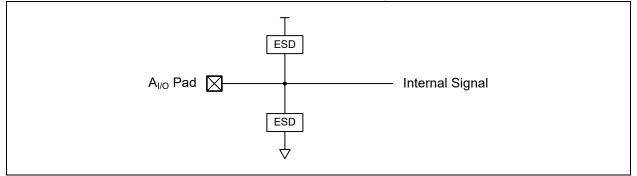

#### FIGURE 2-1: PIN-EQUIVALENT FOR ANALOG I/O PIN - AI/O

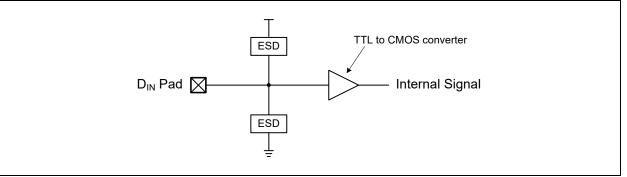

#### FIGURE 2-2: PIN-EQUIVALENT FOR DIGITAL INPUT PIN - DIN

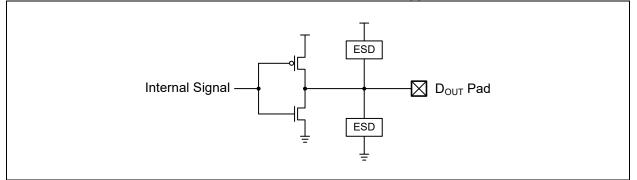

## FIGURE 2-3: PIN-EQUIVALENT FOR DIGITAL OUTPUT PIN - DOUT

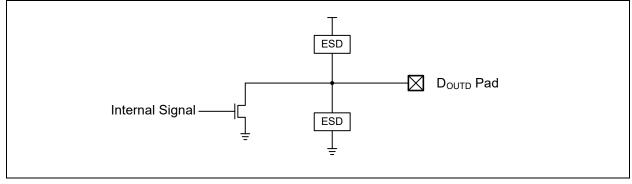

# FIGURE 2-4: PIN-EQUIVALENT FOR OPEN-DRAIN DIGITAL OUTPUT PIN - DOUTD

# OS81210

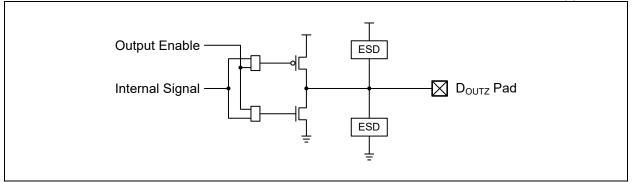

#### FIGURE 2-5: PIN-EQUIVALENT FOR DIGITAL OUTPUT PIN WITH HIGH-Z CONTROL - DOUTZ

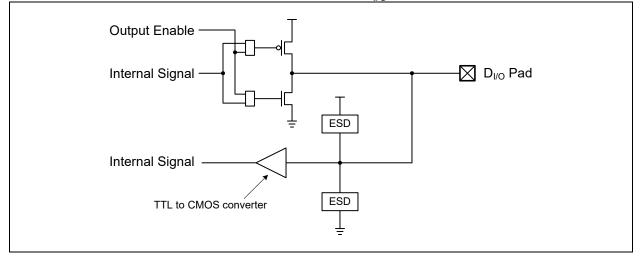

#### FIGURE 2-6: PIN-EQUIVALENT FOR DIGITAL I/O PIN - DI/O

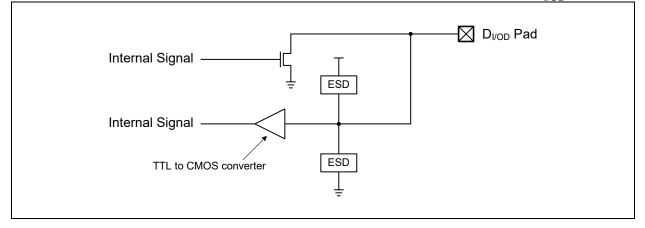

#### FIGURE 2-7: PIN-EQUIVALENT FOR DIGITAL INPUT/OPEN-DRAIN OUTPUT PIN - DI/OD

#### 3.0 OVERVIEW

**Note:** This Data Sheet is designed to be used in conjunction with the INIC Interface Specification [4] to provide a complete reference for the operation and use of the OS81210.

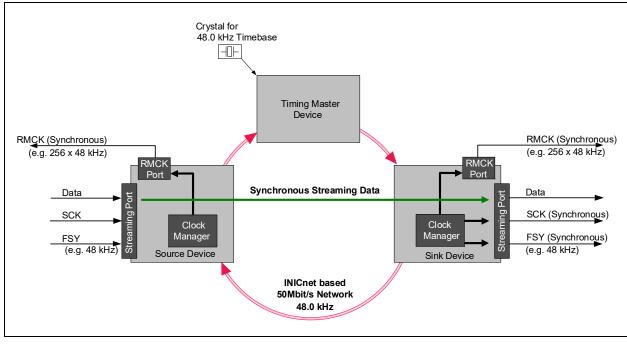

The OS81210 is a network transceiver device belonging to the Microchip *Intelligent Network Interface Controller* (INIC) family. The OS81210 INIC creates a time division multiplexed synchronous network by transmitting 128 bytes frames at a 48 kHz frame rate (Fs) yielding a 49.2 Mbit/s data rate. A network of Electronic Control Units (ECUs) based on INICs creates an INICnet network. INICnet can be configured and managed at the application level by the provided UNICENS software stack. Alternatively, the MOST NetServices software stack can be used to create a MOST compliant network.

There are two major differences between a MOST compliant network and a UNICENS based network, besides meeting the requirements of the MOST Specification. First, the configuration of the network and routing of streaming data on a UNICENS network is done by one central node. In a MOST network, the configuration is distributed among the nodes, with each node being responsible for connecting to a network resource under the direction of the local EHC. Since UNICENS does this configuration under a single node (Root Node), it enables a new class of nodes, called Slim Nodes (Remote Nodes) that do not require a local processor. Second, the MOST Specification describes a dedicated control channel and a specific MOST message format for messages between applications. Whereas in a UNICENS network, it is assumed that application messages between nodes will be transmitted over the Ethernet channel in the form of IP messages using an OEM defined protocol such as SOME/IP, MQTT, or any other OEM defined protocol.

All relevant network management functions are handled on-chip, providing a complete system interface to the physical layer components. Minimal additional components are required due to the high-level of integration. An on-chip PLL with ultra-low jitter guarantees accurate audio and video transmission and clock recovery over a wide frequency range.

A typical network node consists of the physical layer devices connected to the network, the OS81210 to handle the lowlevel protocols, and an *External Host Controller* (EHC) for the mid- to high-level functions. This architecture eliminates the need for the user to implement the lower protocol levels required by the ISO 21806 (Parts 1-7): 2020 – Road Vehicles – Media Oriented Systems Transport (MOST) Specifications [1], the ISO 21806 (Parts 14-15): 2021 – Road Vehicles – Media Oriented Systems Transport (MOST) Lean Application Layer Specification [2], or the UNICENS stack, thereby drastically shrinking development time. Network management functions are off-loaded from the programmer, allowing full concentration on the application being developed. Depending on the embedded firmware, the functions and API of the low-level protocol can vary. Refer to the INIC Interface Specification [4] for more information. Figure 3-1 illustrates the OS81210 with the protocol stack implementation.

#### 3.1 Network

To minimize costs, the network supports a peer-to-peer methodology, eliminating excessive hardware overhead such as a hub (although hub-based architectures can also be implemented). In addition to handling network interface and communication management functions, the OS81210 INIC also handles all of the important low-level network management functions such as node position sensing (Plug-and-Play), start up, and shut down. Other features include error reporting, fail-safe operation, and channel allocation. Placing these features in hardware off-loads the EHC, allowing it to focus on higher-level network functions.

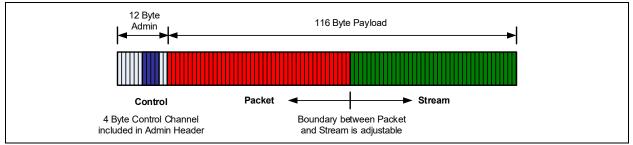

The network implements multiple simultaneous data transport methods operating across a single medium. Once bandwidth is allocated, each data transport method operates independently (not affecting the others), providing a robust, dependable, and deterministic system architecture. The OS81210 INIC supports all of the network data transport methods, including:

- · Control consists of a single control channel

- Asynchronous (Packet) consists of a single packet channel

- · Synchronous Streaming consists of one or more synchronous streaming channels

- · Isochronous Streaming consists of one or more isochronous channels

The network frame's channel boundaries are shown in Figure 3-2.

#### FIGURE 3-2: NETWORK FRAME CHANNELS

#### 3.1.1 CONTROL

The INIC has a unique 4 byte (1.5 Mbit/s data rate) control channel shared by all network nodes. Applications use this channel to transmit control messages between nodes. These control messages from the EHC application are referred to as *Application Control Frames*. *Application Control Frames* are transported as ICMs, RCMs, or MCMs between an EHC driver and a INIC peripheral port (i.e. I<sup>2</sup>C, MediaLB, USB, or SPI). *Application Control Frames* are then transported as *Control Frames* on the network's control channel. Any network node that needs to transmit a *Control Frame* on the network must arbitrate for the control channel. The arbitration is handled by INIC. UNICENS and NetServices libraries provide API commands to send and receive *Application Control Frames* which abstracts the internal INIC software stack from the application.

The INIC automatically monitors the control channel on the Network Port and uses information in the header to determine whether the node is the intended receiver of the *Control Frame*. When a *Control Frame* is to be received (e.g. node address match), it is buffered within the INIC and made available to the application via one of the OS81210 peripheral hardware ports that supports RCM or MCM traffic (see Table 3-1).

#### 3.1.2 ASYNCHRONOUS (PACKET)

The INIC has a single asynchronous packet channel with an adjustable bandwidth that is shared by all network nodes. Applications use this channel to transmit large data packets (e.g. navigation maps) in bursts to other network nodes. These data packets from the EHC application are referred to as *MHP Frames* or *Ethernet Frames*. *MHP Frames* or *Ethernet Frames* are transported as MEPs (Meta Ethernet Packets) or MDPs (*Meta Data Packets*) from the EHC driver to the INIC peripheral port (MediaLB, USB, or SPI) where the message is then converted into a *Packet Frame* or *Ethernet Data Frame* to be sent across the network to the intended node. Any network node that needs to transmit a *Packet Frame* or *Ethernet Data Frame* can arbitrate for the packet channel. The arbitration is handled by INIC.

The INIC automatically monitors the packet channel on the Network Port and uses information in the *MHP Frame* or *Ethernet Frame* header to determine whether the node is the intended receiver (e.g. node address match). When a frame on the packet channel is to be received, the appropriate *MHP Frame* or *Ethernet Frame* is buffered within the INIC and made available as an MDP or MEP on one of the OS81210 peripheral ports that support MDP or MEP traffic (see Table 3-1).

#### 3.1.3 SYNCHRONOUS STREAMING

The *Synchronous Streaming transport method* can consist of multiple synchronous streaming channels, each transporting raw, real-time synchronous data (e.g. audio, video). The data on a synchronous streaming channel is sourced by a single transmitting node that has been granted channel bandwidth. Synchronous streaming channels are broadcast, making the data available for reception by one or more sink nodes.

For high-speed synchronous data, INIC acts like a cross-point switch to connect synchronous streaming channels to sources/sinks attached to OS81210 hardware ports that support synchronous data (see Table 3-1).

#### 3.1.4 ISOCHRONOUS STREAMING

The *Isochronous Streaming transport method* can consist of multiple isochronous channels, each transporting data that is sourced by a single transmitting node (no arbitration) that has been granted channel bandwidth. Isochronous channels are broadcast, making the data available for reception by one or more sink nodes.

Streaming data is transported across isochronous channels, albeit in a *structured* format. Various streaming data structures can be transmitted across an isochronous channel, including:

- DiscreteFrame Isochronous (DFI) Streaming Phase

- A/V Packetized (AVP) Isochronous Streaming Packets

- Quality of Service (QoS) IP Streaming Packets

#### 3.1.4.1 DiscreteFrame Isochronous Phase

A *DiscreteFrame Isochronous* (DFI) phase channel transports the *clock phase component* (also referred to as DFI phase), which includes the phase information necessary to regenerate a specific clock frequency, asynchronous to the network, on the sink node. DFI phase is typically used in association with A/V Packetized (AVP) isochronous to transfer video clock data from the source encoder to the sink decoder. OS81210 hardware ports that support the exchange of DFI phase are shown in Table 3-1.

#### 3.1.4.2 A/V Packetized (AVP) Isochronous Streaming Packets

*A/V Packetized* (AVP) isochronous streaming packets are used to transmit streaming data in an application-specific format (e.g. MPEG2-TS 188 bytes). Sink nodes access the data using a locally generated clock that is independent of the network frame rate, as well as the frame rate used by the node sourcing the AVP packets. OS81210 hardware ports that support the exchange of AVP packets are shown in Table 3-1.

#### 3.1.4.3 Quality of Service (QoS) IP Streaming Packets

An isochronous channel can be used to transport *Ethernet Data Frames* over *dedicated* network bandwidth. In such a system, the *Ethernet Data Frames* are sourced by a single transmitting node that has been granted channel bandwidth. Although the same *Ethernet Data Frames* could alternatively be transmitted across the packet channel, arbitration prior to each packet transmission would be required. *Ethernet Data Frames* exchanged across an isochronous channel are referred to as *QoS Frames*, and are intended for Internet Protocol (IP) message applications.

*QoS Frames* are transmitted in a streaming, broadcast fashion, which makes the *QoS Frame* stream available for reception by one or more sink nodes. However, unlike sink nodes receiving messages on the asynchronous packet channel, nodes that need to sink *QoS Frames* must first be properly configured by the application for reception on a specific channel.

Once the INIC is attached to a network channel that transmits *QoS Frames*, the destination address in the packet headers is ignored and the *QoS Frame* is always received.

Due to the streaming nature of this data transport, received packets are not buffered in their entirety within INIC; rather, an internal circular buffer is used to route the stream of *QoS Frames* to the OS81210 hardware port that supports and is configured for *QoS Frame* reception (see Table 3-1).

#### 3.2 INIC Processor

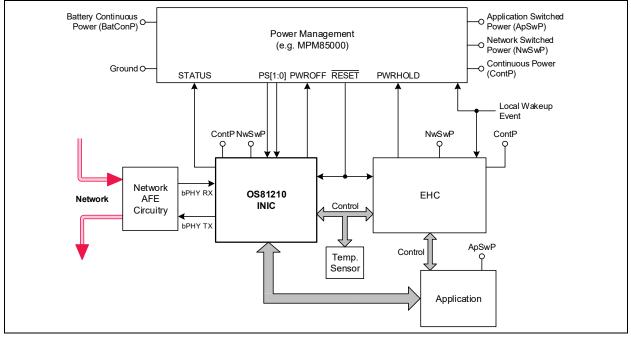

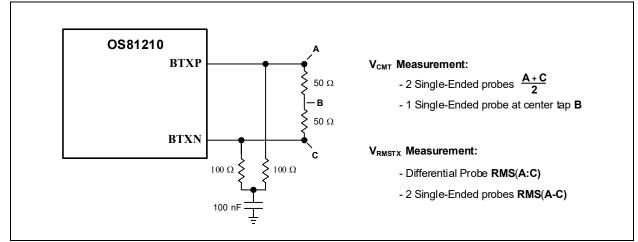

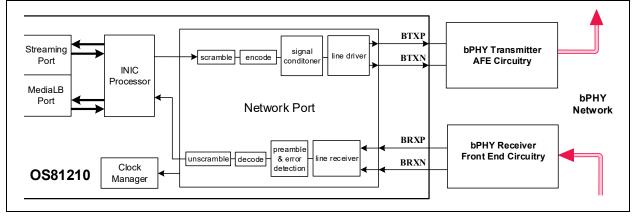

The INIC Processor manages the transfer of data between the network and other hardware ports. The Network Port connects the INIC Processor to the network using the OS81210 network transmit and receive pins (BTXP/BTXN and BRXP/BRXN) to exchange data over the bPHY interface. The bPHY interface of the OS81210 requires external *Analog Front-End (AFE)* circuitry to connect the INIC Processor to the balanced media network and increase system immunity to EMI.

Working in conjunction with the Clock Manager, the Network Port recovers the network clock, decodes received data, and passes the data to the INIC Processor. The INIC Processor then routes data to the appropriate destinations on and off the chip.

The network frame to be transmitted by the OS81210 is constructed by the INIC Processor by combining incoming network data from the Network Port with outgoing data from other on-chip resources. The Network Port then encodes the data for network transmission.

The *INIC Software Stack* runs on the INIC Processor and configures the Network Port at power-up, which allows the network to become operational without any external protocol stack. This has been accomplished by placing all the lower layers of the ISO protocol stack inside of the device. Table 3-1 illustrates the position of the *INIC Software Stack* within the ISO software model.

Each network node contains a general set of functions to manage the network. These functions are split with the INIC managing the low-level functions and the EHC managing the higher-level functions.

The INIC also contains functions used to configure the chip. This includes the setup of hardware ports and the usage of network bandwidth for transporting streaming data.

The upper levels of the network protocol must be implemented by an EHC that is capable of processing the user application with the minimal overhead imposed by the INIC API. During real-time operation, the EHC and the *INIC Software Stack* within the INIC Processor communicate using control messages via the I<sup>2</sup>C, SPI, MediaLB, or USB Ports.

#### 3.3 Hardware Ports

Each OS81210 hardware port transports different network data types. Table 3-1 shows the data types that can be transported across each hardware interface.

|                       | ІСМ         | RCM,<br>MCM | MEP,<br>MDP | Synchronous<br>Data | DFI<br>Phase | AVP Packets | QoS<br>(MEP) |

|-----------------------|-------------|-------------|-------------|---------------------|--------------|-------------|--------------|

| Peripheral Hard       | dware Ports | :           |             |                     |              |             |              |

| MediaLB               | х           | Х           | Х           | Х                   | Х            | х           | х            |

| Streaming             |             |             |             | Х                   |              |             |              |

| RMCK                  |             |             |             | Х                   |              |             |              |

| USB                   | х           | Х           | Х           | Х                   |              | Х           |              |

| SPI                   | х           | Х           | Х           |                     |              |             |              |

| I <sup>2</sup> C Port | х           | Х           |             |                     |              |             |              |

| Network Port:         |             |             |             |                     |              |             |              |

| Network<br>Channel    | Control     | Control     | Packet      | Synchronous         | Isochronous  | Isochronous | Isochronous  |

|                       |             | Х           | Х           | Х                   | Х            | Х           | Х            |

TABLE 3-1:HARDWARE PORT DATA TRANSPORT

Using the OS81210 API, a *socket* is created for each data stream transported across a hardware port. The specific data type to be exchanged is specified when creating the socket. Data routing between hardware ports is setup when sockets of like data types are linked together. For more information on sockets, refer to the INIC Interface Specification [4].

#### 3.3.1 NETWORK PORT

The Network Port receiver is over-sampled at a high-frequency and data is recovered by a digital state machine. When the port is configured as a timing-slave, the OS81210 recovers the network clock, which the Clock Manager then uses to generate other internal clocks. When the port is configured as the timing-master, the internal clocks and the network clock are generated by the Clock Manager based on an external crystal (XTI/XTO). The Network Port transmitter works in conjunction with the INIC Processor to encode data for network transmission.

After reset, the OS81210 automatically interacts with the network, performing all necessary low-level network management functions. This enables the EHC to configure its interface to the OS81210 when the application is ready.

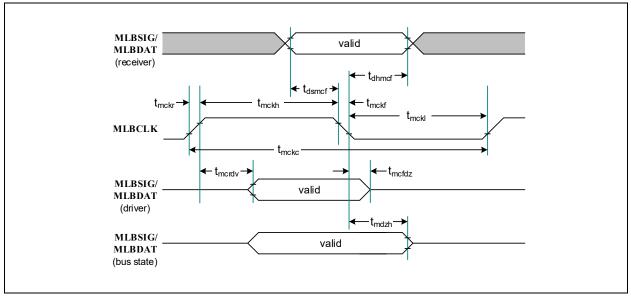

#### 3.3.2 MediaLB PORT

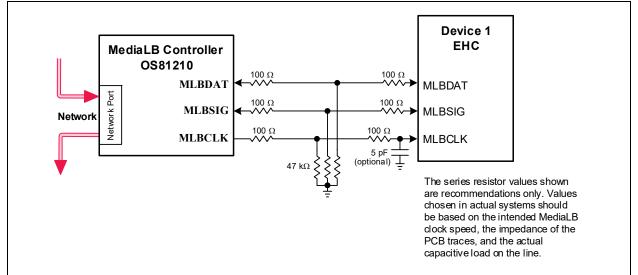

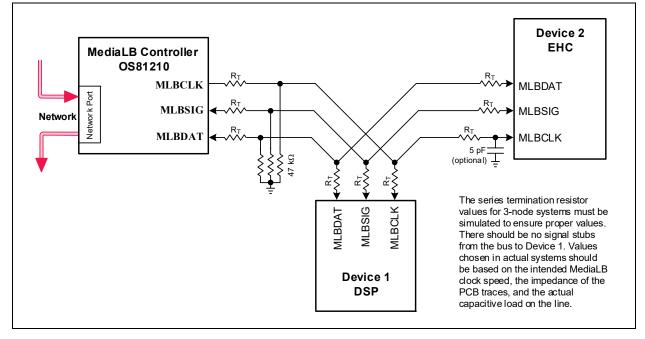

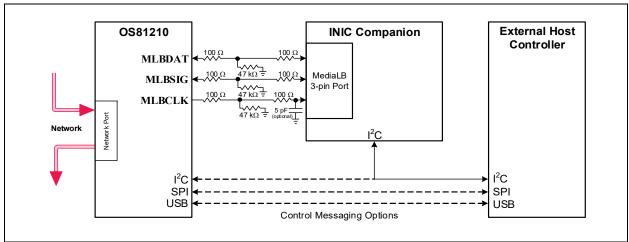

The MediaLB Port supports communication between the EHC and the OS81210 INIC by means of the *Media Local Bus* (MediaLB) protocol. MediaLB provides a low cost, easy to implement hardware interface that standardizes and simplifies network application development. MediaLB has one bus master, referred to as the *MediaLB Controller* (or simply *Controller*), which is always the OS81210. All other connected components (including the EHC) are known as *MediaLB Devices* (or simply *Devices*). MediaLB Device functionality is a subset of Controller functionality; the Controller (OS81210) functions as a Device when it is receiving data from other connected components.

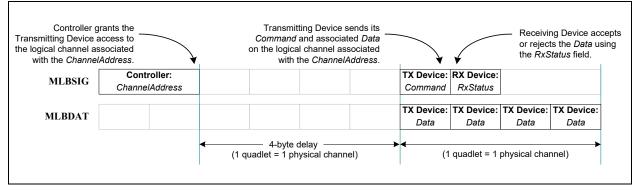

The OS81210 supports the MediaLB protocol with a single-ended MediaLB 3-pin interface. This interface supports the exchange of network data types, including: control messages, asynchronous packets, synchronous data, DFI phase, QoS packets, and AVP packets. The transmitting Device sends data on a dedicated data line, while information about the data is simultaneously transported on an independent signal information line.

When using the MediaLB 3-pin interface, the OS81210 MediaLB Port output clock is configurable as 256×Fs (12.288 MHz at 48 kHz), 512×Fs (24.576 MHz at 48 kHz), or 1024×Fs (49.152 MHz at 48 kHz). When configured for 256×Fs, the OS81210 can transmit and receive up to 28 bytes (7 quadlets) per frame of data. When configured for 1024×Fs, the OS81210 can transmit and receive up to 124 bytes (31 quadlets) per frame of data.

MediaLB is a token-passing bus, where the Controller manages the token and generates the data clock. The Controller passes the token by sending out a *ChannelAddress* on the signal information line. The *ChannelAddresses* are pre-assigned by the board integrator and are associated with a specific transmitting Device and receiving Device. Once the transmit-

ting Device associated with the *ChannelAddress* is granted bus access, it can send one quadlet of data on the MediaLB data line after a defined time delay. The Device provides information about the data being transmitted by simultaneously sending out a command on the signal information line. After receiving the *ChannelAddress*, the receiving Device must decide whether to receive the associated message or reject it. A status byte from the receiving Device is placed on the signal information line, one byte after the command from the sending Device is received. Once per network frame, the Controller generates a unique pattern (*FRAMESYNC*) on the signal information line. This defines the MediaLB frame edge, as well as the byte boundary of signal and data lines for all Devices.

Since MediaLB is a high-speed bus, connections to external devices should be implemented in hardware and not *bit-banged* on generic ports. A MediaLB Device interface, in the form of VHDL code, is available from Microchip. For more information about the Media Local Bus, refer to the MediaLB Specification [5].

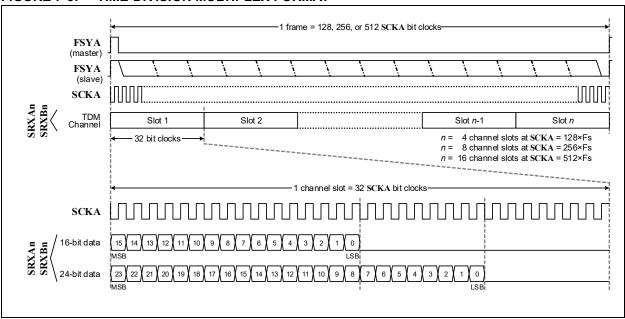

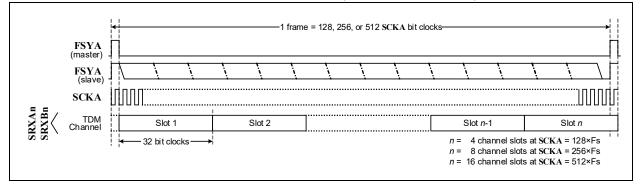

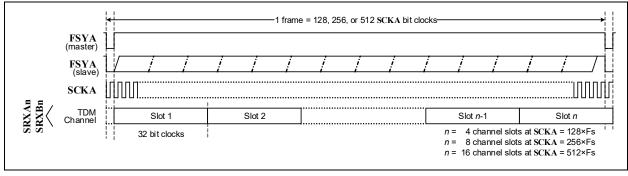

#### 3.3.3 STREAMING PORT

The Streaming Port provides a gateway for synchronous data exchange between the OS81210 and external legacy devices. The OS81210 Streaming Port supports four serial data pins sharing a common synchronization signal and bit clock. The data formats supported by the Streaming Port are compatible with industry-standard serial interfaces found on many ADCs, DACs and other devices.

#### 3.3.4 RMCK PORT

The RMCK Port is a hardware interface controlled by the internal Clock Manager. This port provides a single clock output (RMCK) that is synchronous to the network frame rate (Fs). The RMCK Port is typically used in conjunction with the Streaming Port to exchange synchronous data over the network. The RMCK output is used to synchronize external application devices (e.g. ADC or DAC) to the common network timebase.

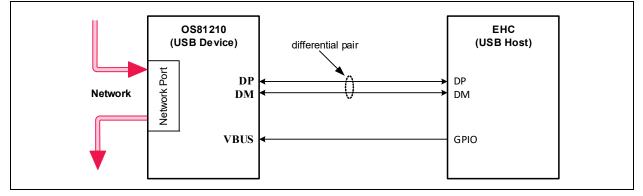

#### 3.3.5 USB PORT

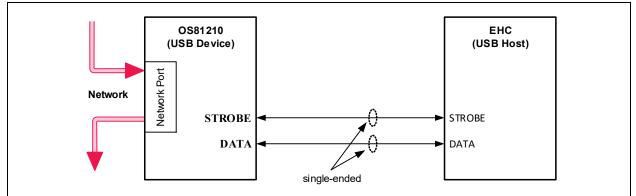

The USB Port allows connection to the OS81210 (USB Device) by an EHC (USB Host Controller) and supports on-PCB upstream USB 2.0 high-speed bulk transfers using either a standard USB 2.0 physical interface or a *High-Speed Inter-Chip* (HSIC) physical interface at a rate of 480 Mbit/s. The USB Port provides access to the network via an interface commonly found in consumer applications. This is especially useful for microcontrollers that do not support the typical interfaces found in an automotive application (e.g. MediaLB).

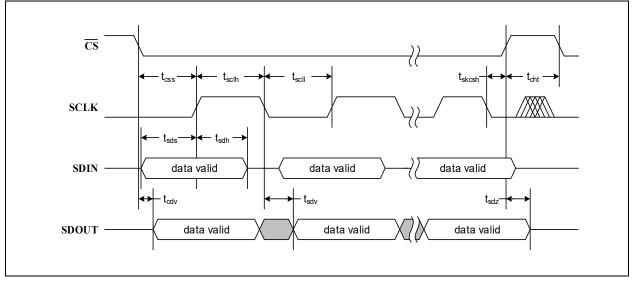

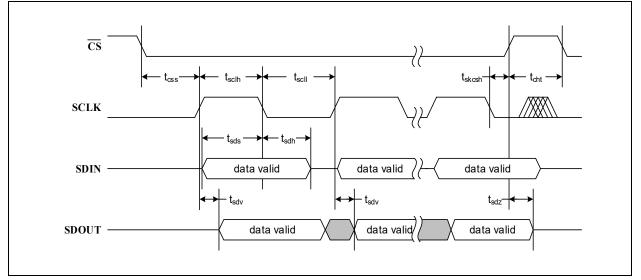

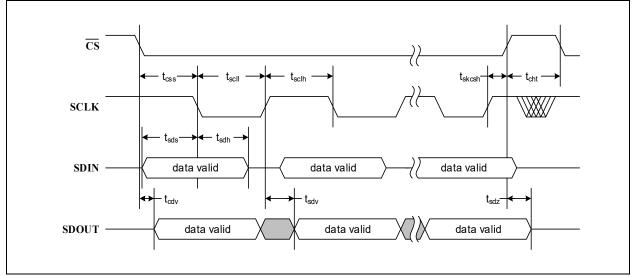

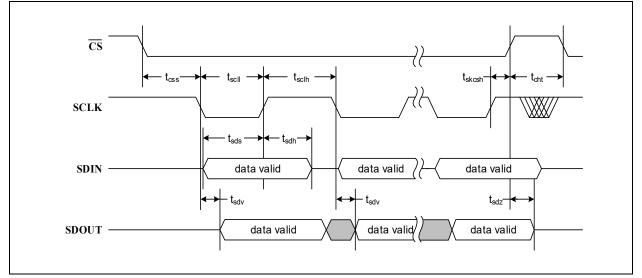

#### 3.3.6 SPI PORT

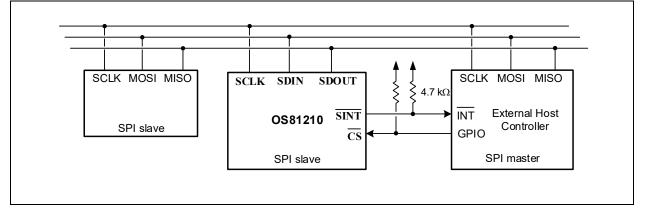

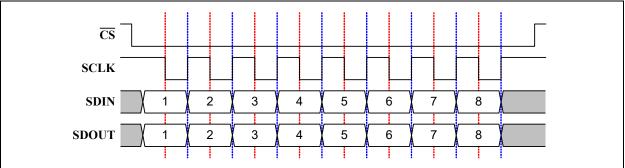

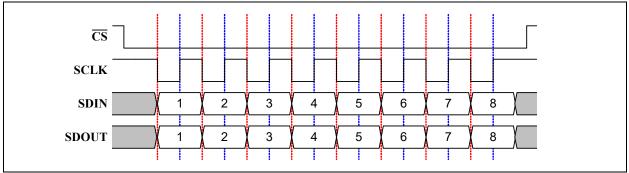

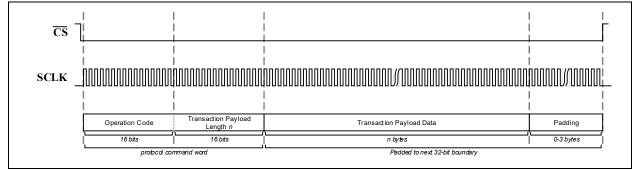

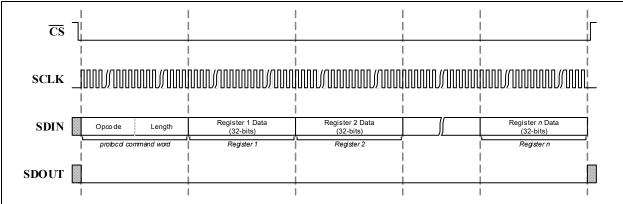

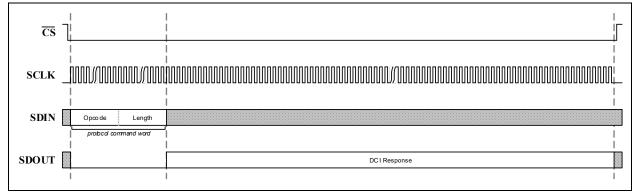

The Serial Peripheral Interface (SPI) Port supports the transmission of asynchronous and control packets over an interface that is compatible with many microprocessors, data converters and other devices. When the SPI Port is enabled, it operates as an SPI bus slave.

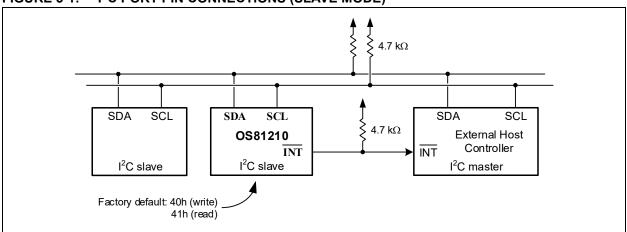

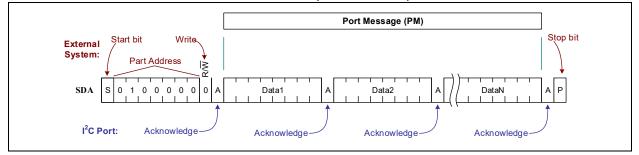

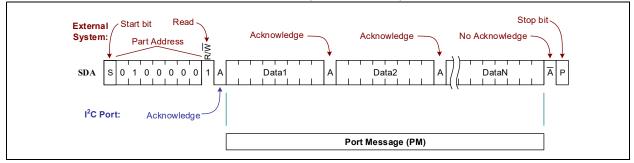

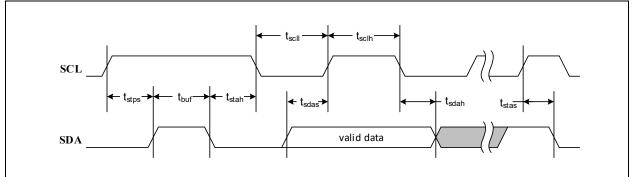

#### 3.3.7 I<sup>2</sup>C PORT

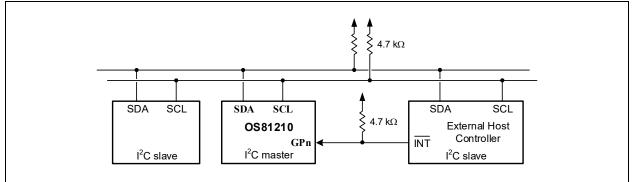

Using the default *INIC Configuration String*, the I<sup>2</sup>C Port operates as a bus slave and supports control message (such as ICMs, RCMs, and MCMs) exchange. An interrupt pin (INT) is used to notify the EHC when the I<sup>2</sup>C Port requires service (e.g. control message received). While the EHC can communicate with the OS81210 over the I<sup>2</sup>C Port alone, the I<sup>2</sup>C Port data rate limits the throughput on the Application Layer. Application performance can be maximized by using either the MediaLB Port, SPI Port, or USB Port which also supports the exchange of control messages.

The OS81210 I<sup>2</sup>C Port may be configured as an I<sup>2</sup>C master by changing the settings in the *INIC Configuration String*. In master mode, the OS81210 performs read and write operations with on-board I<sup>2</sup>C slave devices based on remote commands received from the network.

#### 3.3.8 GPIO PORT

Depending on the *INIC Configuration String* settings and firmware loaded in OS81210, the *General Purpose Input/Output* (GPIO) Port may be available to support various external operations. Some of the OS81210 hardware ports may not be available when the GPIO Port is used.

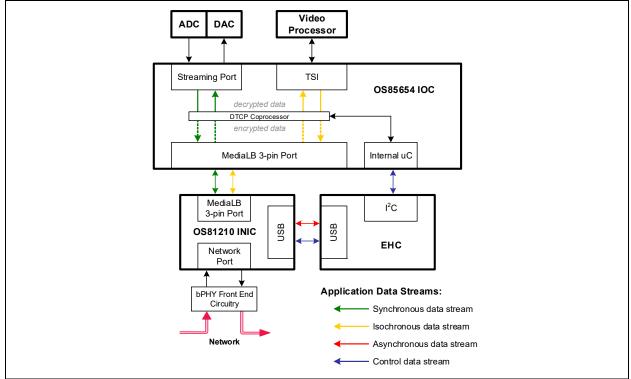

#### 3.3.9 PORT EXPANSION

Devices belonging to the Microchip *I/O Companion* (IOC) family can be used as companions to INIC to provide additional features and hardware ports to the application. When an IOC is used as a companion to the OS81210 INICs, the MediaLB bus is typically the medium used to exchange data between the two devices. Data exchanged over MediaLB is routed to IOC hardware interfaces on which external devices may reside (e.g. ADC, DSP, video displays, etc.). The OS85654 IOC, as depicted in Figure 3-3, is a high-performance routing engine that supports I/O expansion and provides a *Digital Transmission Content Protection* (DTCP) coprocessor. The primary function of the OS85654 is the routing of data streams between various hardware ports, while the integrated DTCP coprocessor provides optional encryption/decryption of data streams routed through the IOC device. Various services are available to support full *Authentication and Key Exchange* (AKE) implementation. For applications that do not require DTCP, the OS85656 IOC provides the same functionality as the OS85654, albeit without the DTCP coprocessor.

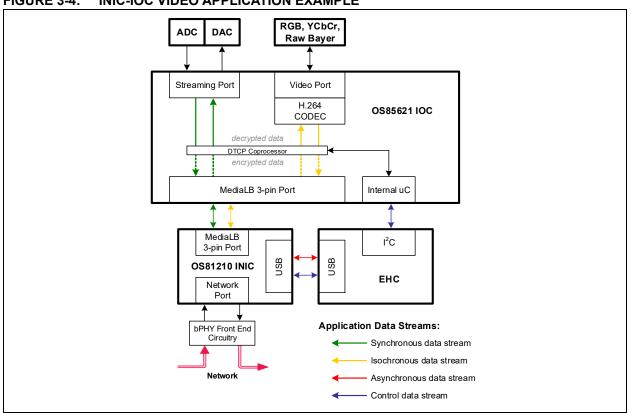

Applications supporting video benefit from the OS85621 IOC with its integrated low-latency H.264 CODEC, industry standard video I/O part, and DTCP coprocessor. See Figure 3-4. Applications not requiring content protection may instead utilize the OS85623, which provides the same functionality as the OS85621 but does not include the DTCP coprocessor.

Contact Microchip for more information about the I/O Companion family of devices.

FIGURE 3-3: INIC-IOC DTCP APPLICATION EXAMPLE

#### FIGURE 3-4: INIC-IOC VIDEO APPLICATION EXAMPLE

#### 3.4 Centralized Network Diagnostics and Fallback Operation

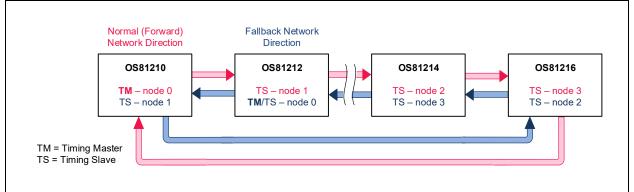

The OS81210 network interface includes an embedded feature allowing the data path to reverse the direction of communication (receive on the **BTXP/BTXN** pins and transmit on the **BRXP/BRXN** pin). This reversal of direction enables two special modes of operation: isolation of cable faults if the normal ring is broken, and a special simplex mode of operation called Fallback Operation that can be used for fault-tolerant network operation.

#### 3.4.1 CENTRALIZED NETWORK DIAGNOSTICS

Centralized Network Diagnostics are used to collect diagnostic information from nodes in the network such as cable link connections in case normal operation is not possible due to a break in the ring architecture. These diagnostics are executed by the Timing Master (*Root Node*) over a control channel therefore requiring no additional cable wiring such as an electrical control line. All other nodes are *Remote Nodes* which do not require any additional hardware (EHC) or logic. For more information on triggering Central Network Diagnostics, please refer to the INIC Interface Specification [4].

#### 3.4.2 FALLBACK OPERATION

The Fallback Operation mode allows a segment of the network to operate in the reverse direction even if the ring is damaged. This feature can be used to implement an emergency call (eCall) feature (e.g. react to a network physical interruption) or to implement a simplex daisy chain network topology for simple microphone applications. This mode is intended for applications required to sustain synchronous streaming data and limited control communication during a fault state. In this mode, the direction of communication is reversed and a new node will negotiate to become the Timing Master. Nodes that are required to operate in this fault-tolerant mode must enable Fallback Operation in the *INIC Configuration String*. If enabled, further parameters must be set allowing nodes permission to become the new timing master or a timing slave, or react only as a timing slave during Fallback Operation. Additionally, these nodes can be configured to automatically stream synchronous data on pre-defined channels when Fallback Operation begins. This enables the transfer of streaming data with no application firmware required.

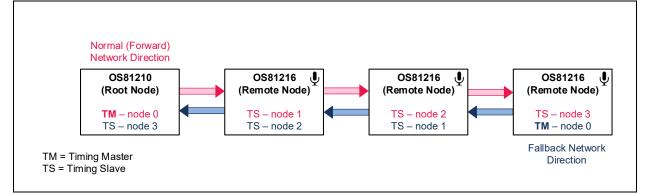

A normal forward network direction example is shown in Figure 3-5. If the network is broken between nodes 1 and 2, Fallback Operation can be initiated and ultimately the furthermost node upstream of the break allowed to become a Timing Master will take over (Forward network node 1 would become Fallback node 0). For more information on Fallback Operation, please see the INIC Interface Specification [4].

Fallback Operation can also be used to implement a limited simplex daisy chain network which can automatically stream synchronous data in one direction. This feature is useful to create a simple microphone network. Only streaming data can be transmitted during the Fallback Operation mode. Each node must be statically configured via the *INIC Configuration String* to operate in Fallback Operation and use a predetermined channel to transmit streaming data. In Figure 3-6, the *Root Node* (forward network direction timing master node 0) will start the network and begin the negotiation phase. The network direction is reversed, and the previous forward direction timing slave node 3 becomes the timing master node 0 in Fallback Operation. Once the negotiation timer as expired, streaming data will begin transmitting over each microphone's channel in the Fallback Network direction to the *Root Node*. This limited simplex daisy chain mode enables the creation of a completely statically defined network that operates without further configuration following a single startup command.

For more information on Fallback Operation, please see the INIC Interface Specification [4].

#### FIGURE 3-6: SIMPLEX DAISY CHAIN MICROPHONE NETWORK EXAMPLE

#### 3.5 MOST NetServices

In addition to a generic automotive network, the OS81210 can be used to implement a MOST network. To accelerate development of MOST network applications that use the OS81210, Microchip offers the MOST NetServices API, which provides a seamless software interface between INIC and the EHC. The division of services between the OS81210 INIC and the EHC in a MOST network is illustrated in Figure 3-1. A software library is available to provide all services that are relevant for:

- exchanging application data on a MOST network,

- managing hardware port data connections (e.g. sockets),

- · managing high-level system tasks, and

- · using control messages to access INIC for specific operations.

The MOST NetServices code incorporated into the EHC is divided into two distinct components: *Basic Services* and *Applications Socket*.

The *Basic Services* component includes message management, configuration management, and state control and supervision. It provides the facilities that enable direct communication with INIC through an interface to a low-level driver that is independent of the hardware port used. Formatted messages are sent and received by the low-level driver across the interface between the EHC and INIC.

The Applications Socket component resides on top of Basic Services and provides the functions required to implement the full FBlock NetBlock on the node. This component also contains a command interpreter, which provides a simple API for developing application FBlocks (e.g. FBlock AudioAmp).

MOST NetServices code is modular, allowing it to be customized for a particular application. Implemented in ANSI C, the MOST NetServices API can be adapted for individual requirements through configuration files.

With respect to the ISO communications model (shown in Figure 3-1):

- The OS81210 is connected to the bPHY *balanced media physical layer* with external passive front-end components.

- The OS81210 supports the Data Link Layer up to a portion of the Session Layer.

- The EHC must provide the remaining portion of the *Session Layer*, the *Presentation Layer*, and the *Application Layer*. When the MOST NetServices code is integrated:

- the Basic Services component provides the remaining portion of the Session Layer, and

- the Applications Socket component provides the Presentation Layer and a portion of the Application Layer.

The INIC Interface Specification [4] defines the FBlocks (and all associated functions) that are supported by the OS81210.

#### 3.6 Unified Centralized Network Stack (UNICENS)

The Unified Centralized Network Stack (UNICENS) is an alternative to NetServices simplifying the handling of a complex, heterogeneous infotainment network. While NetServices is required to be implemented and running on every node of the system, UNICENS only needs to be implemented on a single *Root Node*. UNICENS provides centralized control and management for the entire network.

The network may be either statically or dynamically configured by UNICENS. In a static configuration, UNICENS scans the network on startup to discover the nodes, remotely configuring and controlling each node via *Control Frames*. A Remote Host Controller (RHC) may be implemented at a *Remote Node*, but is not required thereby significantly reducing hardware cost. This allows the network software to be centralized into the *Root Node* EHC, reducing system complexity and development cycles. UNICENS controls hardware at the *Remote Node*s through remote I<sup>2</sup>C messages and GPIO control.

The OS81210 is ideal for implementation in the *Root Node* with its integrated USB Port. The OS81212, OS81214, and OS81216 are optimized for use in *Remote Nodes* with or without a Remote Host Controller (RHC).

More information regarding UNICENS may be obtained upon request from Microchip.

#### 3.7 Operating System Drivers

Drivers are available which aid integration of the INIC with operating systems being used in many complex systems. For example, Microchip has made an INIC device driver available within the Linux<sup>®1</sup> mainline kernel.

The Linux driver for INIC implements each of the network data types presenting them to the application in standard programming interfaces. Synchronous streaming channels are implemented as Advanced Linux Sound Architecture (ALSA) hardware and appear as standard audio sources and sinks. A/V Packetized data channels are accessed using the Video4Linux2 (V4L2) application framework. The network Ethernet channel appears as a standard Ethernet interface. Control channels are accessed as a standard character device. The standard presentation of network data channels greatly simplifies application programming effort.

Contact Microchip for more information regarding the INIC driver, including the Linux kernel driver for INIC.

<sup>1.</sup>Linux<sup>®</sup> is the registered trademark of Linus Torvalds in the U.S. and other countries.

# 4.0 INIC PROCESSOR

The OS81210 is a valid network node even without an attached EHC, due to the on-chip INIC Processor. The *INIC Software Stack*, running on the INIC Processor, provides a message-based interface that is easily implemented in a high-level language. This message-based interface not only simplifies the interface between the application and the network, but allows the EHC software to be completely driven by message events. Using the INIC API, as described in the INIC Interface Specification [4], the EHC has access to the same functionality that would be available on a register-based interface, but the programmer is spared the effort of making software align with the chip architecture. Much of the INIC application interface is common across INIC chips, minimizing the effort of upgrading the software for different application platforms. The power-up default settings of the INIC Processor, such as timing-master/timing-slave functionality and other configuration options, can be changed through the *Customer Configuration Interface* (see Section 16.6 "Configuration and Debug").

Partitioning the node architecture between INIC and the EHC results in an efficient implementation, allowing INIC to respond to many network events without intervention by the EHC. Network initialization is optimized, not requiring the network transceiver at each node to wait for the Application Layer to respond. Application software runs efficiently since the number of interrupts to the EHC is minimized. Interaction between the EHC and INIC can be further reduced if the EHC enables notification for INIC properties.

#### 4.1 Data Exchange

General information on data exchange with the OS81210 is given below. Refer to the INIC Interface Specification [4] for more detailed information. The INIC Message Interface consists of two virtual paths - the Configuration Interface which handles message to control INIC itself and the Application Interface which is used to pass application specific messages between nodes.

#### 4.1.1 CONFIGURATION DATA

The OS81210 Configuration Interface is used for message-based data exchange between INIC and the EHC.

These messages transferred between the local INIC and the EHC via the MediaLB Port, SPI Port, USB Port, or I<sup>2</sup>C Port are called *Application Control Frames*. *Application Control Frames* can be routed to the local INIC for control and configuration, or through the INIC and across the network for controlling and configuring remote INIC nodes.

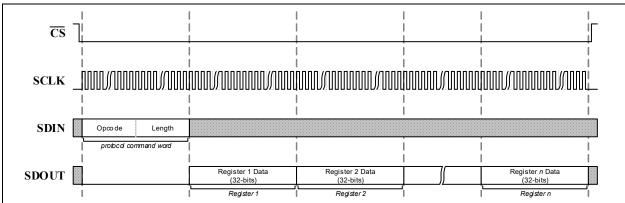

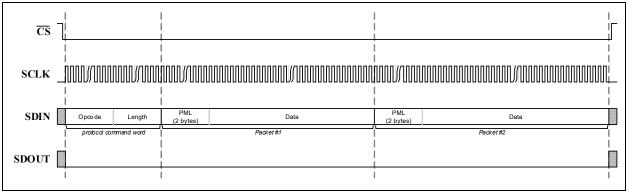

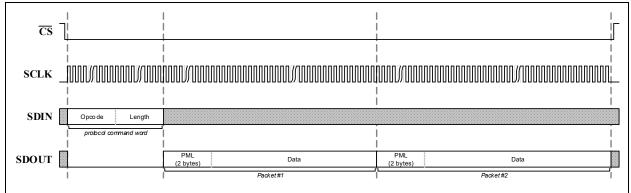

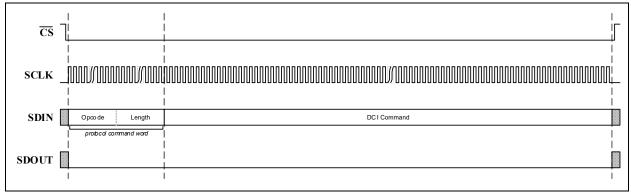

Application Control Frames exchanged between the local EHC and the internal *INIC Software Stack* are called *INIC Control Messages* (ICMs). *Remote Control Messages* (RCMs) are similar to ICMs with the exception that they are routed through the local INIC to remote INIC nodes for configuration and network management purposes.