32-BIT ARM926EJ-S BASED MCU

# NUC910ABN 32-bit ARM926EJ-S Based Microcontroller Product Data Sheet

The information described in this document is the exclusive intellectual property of Nuvoton Technology Corporation and shall not be reproduced without permission from Nuvoton. Nuvoton is providing this document only for reference purposes of ARM926-based system design. Nuvoton assumes no responsibility for errors or omissions. All data and specifications are subject to change without notice.. For additional information or questions, please contact: Nuvoton Technology Corporation.

## 32-BIT ARM926EJ-S BASED MCU

### **Table of Contents**

| 1  | GENERAL DESCRIPTION                          |        |

|----|----------------------------------------------|--------|

| 2  | FEATURES                                     |        |

| 3  | PIN DIAGRAM                                  | 12     |

| 4  | PIN ASSIGNMENT                               |        |

| 5  | PIN DESCRIPTION                              | 21     |

| 5  | .1 PIN DESCRIPTION FOR INTERFACE             | 21     |

| 5  | .2 GPIO SHARE PIN DESCRIPTION                |        |

| 6  | FUNCTIONAL BLOCK                             | 32     |

| 7  | FUNCTIONAL DESCRIPTION                       |        |

| 7  | .1 ARM926EJ-S CPU CORE                       | 22     |

| -  | .2 System Manager                            |        |

|    | 7.2.1 Overview                               |        |

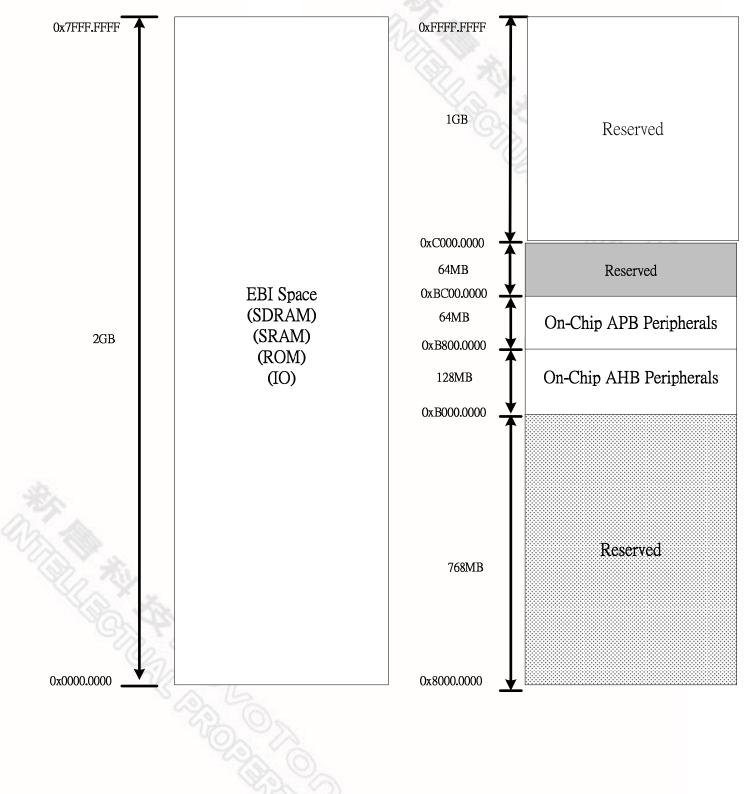

|    | 7.2.2 System Memory Map                      |        |

|    | 7.2.3 Address Bus Generation                 |        |

|    | 7.2.4 AHB Bus Arbitration                    |        |

|    | 7.2.4.1 Fixed Priority Mode                  |        |

|    | 7.2.4.2 Rotate Priority Mode                 |        |

|    | 7.2.5 Power-On Setting                       |        |

|    | 7.2.6 System Booting                         |        |

|    | 7.2.7 System Global Control Registers Map    |        |

| 7  | .3 CLOCK CONTROLLER                          |        |

|    | 7.3.1 Power management                       |        |

|    | 7.3.2 Clock Control Registers Map            |        |

|    | .4 External Bus Interface                    |        |

| 15 | 7.4.1 Overview                               |        |

|    | 7.4.2 Functional Description                 |        |

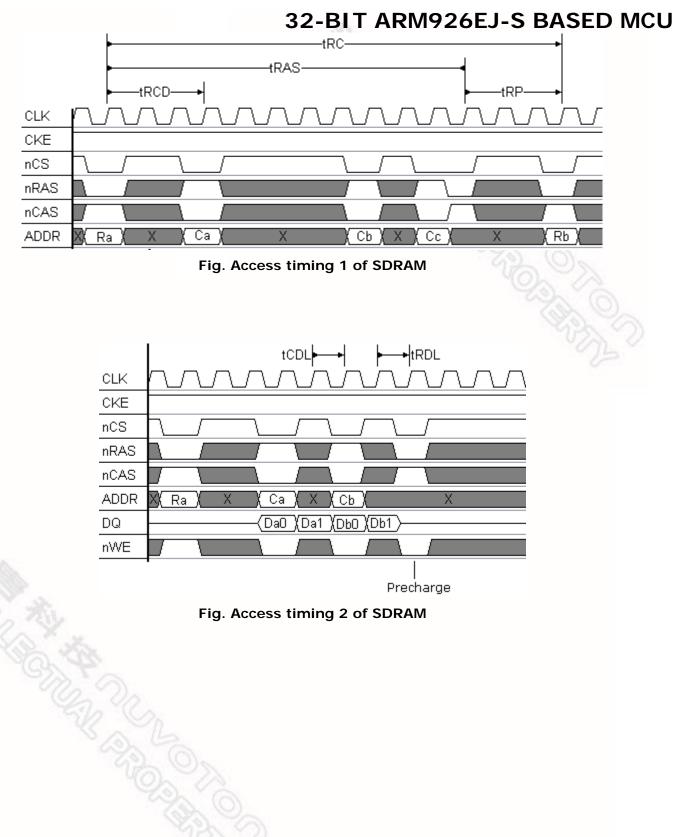

|    | 7.4.2.1 SDRAM Controller                     |        |

|    | 7.4.2.2 SDRAM Components Supported           |        |

|    | 7.4.2.3 AHB Bus Address Mapping to SDRAM Bus |        |

|    | 7.4.2.4 SDRAM Power-Up Sequence              |        |

|    | 7.4.3 EBI Register Mapping                   |        |

|    | 7.4.4 EBI Register Details                   |        |

| 7  | .5 ETHERNET MAC CONTROLLER                   |        |

|    | EMC Descriptors                              |        |

|    | 7.5.1.1 Rx Buffer Descriptor                 |        |

|    | 7.5.1.2 Tx Buffer Descriptor                 |        |

|    | 7.5.2 EMC Register Mapping                   |        |

|    | 7.5.3 EMC Register Details                   |        |

|    | 7.5.4 Operation Notes                        |        |

| 7  | .6 GDMA CONTROLLER                           |        |

|    | Publication Poleace Date: Jun. 1             | 0 2010 |

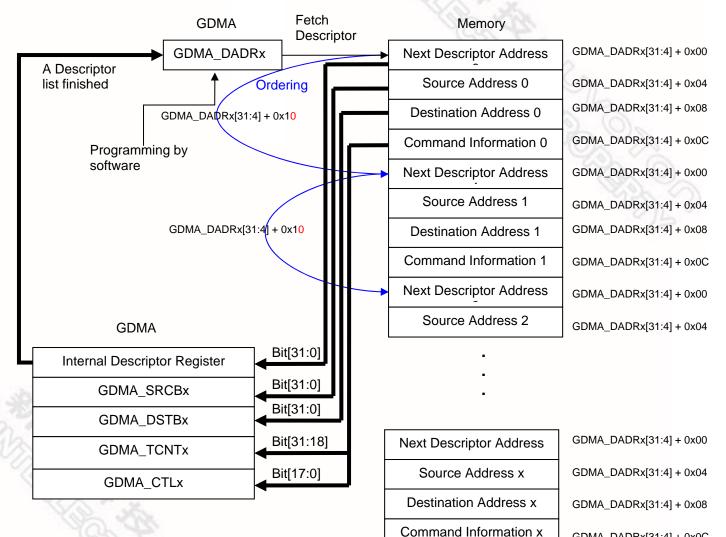

| 7.6.1                | Overview & Features                        | 151 |

|----------------------|--------------------------------------------|-----|

| 7.6.2                | GDMA Non-Descriptor Functional Description |     |

| 7.6.3                | GDMA Descriptor Functional Description     |     |

| 7.6.3.1              | Descriptor Fetch Function                  | 153 |

|                      | Ordering function in Descriptor fetch mode |     |

| 7.6.3.3              | Channel Reset                              | 156 |

| 7.6.3.4              | Non-Descriptor Fetch Function              | 156 |

| 7.6.4                | GDMA Register Map                          | 157 |

| 7.7 USB              | HOST CONTROLLER (USBH)                     | 1/5 |

| 7.7.1                | Register Mapping                           | 176 |

| 7.7.2                | Register Details                           | 1/8 |

|                      | 2.0 Device Controller                      |     |

| 7.8.1                | USB Device Register Group Summary          |     |

| 7.8.2                | USB Device Control Registers Map           |     |

| 7.8.3                | USB Device Control Registers               |     |

|                      | Controller (DMAC)                          |     |

| 7.9.1                | DMA Controller Registers Map               |     |

| 7.9.2                | DMAC Registers                             |     |

|                      | Memory Interface Controller (FMI)          |     |

| 7.10.1               | FMI Controller Registers Map               |     |

| 7.10.2               | Register Details                           |     |

|                      | DISPLAY INTERFACE CONTROLLER (LCM)         |     |

| 7.11.1               | LCD Controller Function Description        |     |

| 7.11.1.1             |                                            |     |

| 7.11.1.2<br>7.11.1.3 |                                            |     |

| 7.11.1.4             |                                            |     |

| 7.11.2               | LCD Controller Register Map                |     |

| 7.11.3               | LCD Controller Register                    |     |

|                      | CONTROLLER                                 |     |

| 7.12.1               | IIS Interface                              |     |

| 7.12.2               | AC97 Interface                             |     |

| 7.12.3               | Audio Controller Register Map              |     |

|                      | I INTERFACE CONTROLLER                     |     |

| 7.13.1               | ATAPI Interface Controller Registers Map   |     |

|                      | ATA Control Registers                      |     |

|                      | GRAPHIC ENGINE                             |     |

|                      | 2-D Graphic Engine Control Registers Map   |     |

| 7.14.2               | 2-D Graphic Engine Control Registers       |     |

|                      | CONTROLLER.                                |     |

|                      | UART Feature Description                   |     |

| 7.15.1.1             |                                            |     |

| 7.15.1.2             |                                            |     |

| 7.15.1.3             | 3 UART2                                    | 468 |

| 7.15.1.4             |                                            |     |

| 7.15.1.5             |                                            |     |

| 7.15.2               | UART Control Registers Map                 |     |

|                      | R Controller                               |     |

| 7.16.1               | General Timer Controller                   |     |

| 7.16.2               | Watchdog Timer                             |     |

| 7.16.3               | Timer Control Registers Map                |     |

|                      | Publication Release Date: Jun. 18, 2       | 010 |

| 7.17.2 AIC Registers Map               |                                         |

|----------------------------------------|-----------------------------------------|

| 7.18 GENERAL-PURPOSE INPUT/OUTPUT (G   | PIO)                                    |

| 7.18.1 Overview                        |                                         |

| 7.18.2 GPIO Multiplexed Functions      | s Table                                 |

| 7.18.3 GPIO Control Registers Ma       | 0                                       |

|                                        |                                         |

| 7.19.1 RTC Register Mapping            |                                         |

| 7.20 SMART CARD HOST INTERFACE (SC)    |                                         |

| 7.20.1 SC Register Map                 |                                         |

|                                        | CONTROLLER                              |

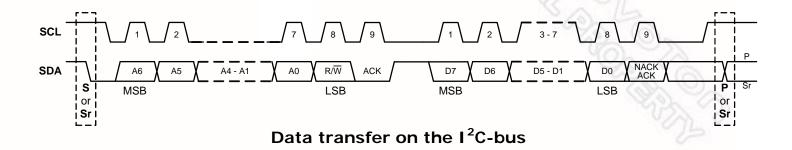

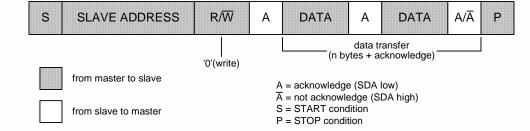

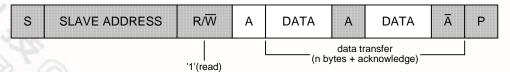

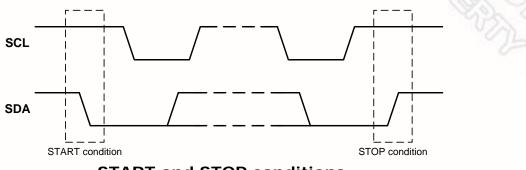

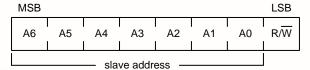

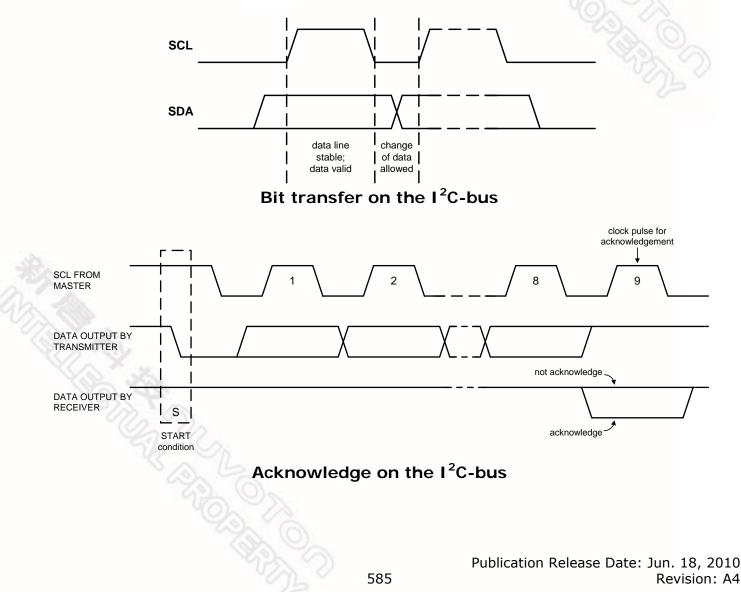

| 7.21.1 $I^2C$ Protocol                 |                                         |

| 7.21.2 I2C Serial Interface Contro     | I Registers Map                         |

| 7.22 UNIVERSAL SERIAL INTERFACE CONTRO | DLLER (USI)                             |

|                                        |                                         |

|                                        |                                         |

|                                        |                                         |

|                                        |                                         |

| 0                                      | Reload Automatically                    |

|                                        |                                         |

|                                        |                                         |

|                                        | e                                       |

| ,                                      | e                                       |

| <b>a</b> 1                             |                                         |

| 7.24 KEYPAD INTERFACE (KPI)            |                                         |

|                                        | Мар                                     |

|                                        |                                         |

|                                        |                                         |

|                                        | ce Register Map                         |

|                                        | C)                                      |

|                                        |                                         |

|                                        |                                         |

|                                        | Screen                                  |

|                                        |                                         |

|                                        |                                         |

|                                        |                                         |

| 8 ELECTRICAL SPECIFICATIONS            |                                         |

| 8.1 ABSOLUTE MAXIMUM RATINGS           |                                         |

| 8.2 DC SPECIFICATIONS                  |                                         |

|                                        |                                         |

| 8.2.2 USB Low-/Full-Speed DC E         | lectrical Specifications651             |

|                                        | ical Specifications651                  |

| 8.3 AC SPECIFICATIONS                  |                                         |

| 8.3.1 RESET AC Characteristics         |                                         |

| 8.3.2 Clock Input Characteristics      |                                         |

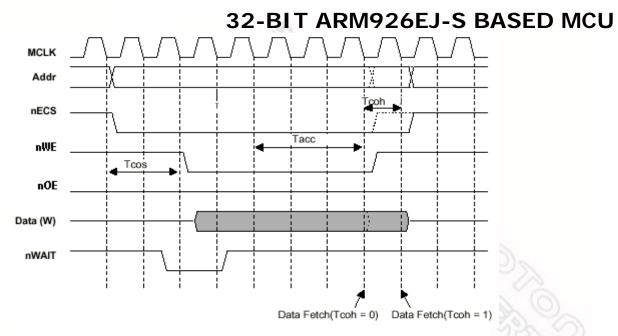

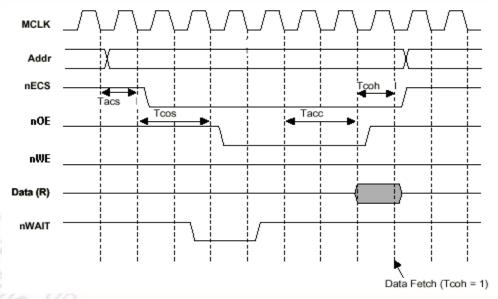

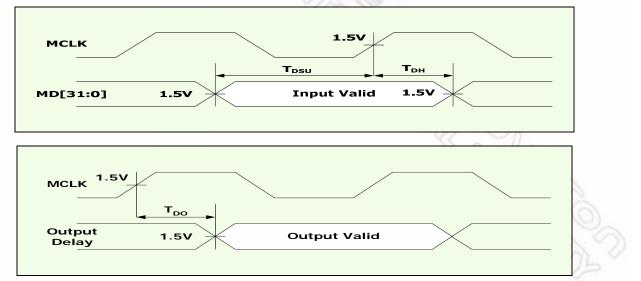

| 8.3.3 EBI/SDRAM Interface AC C         | haracteristics                          |

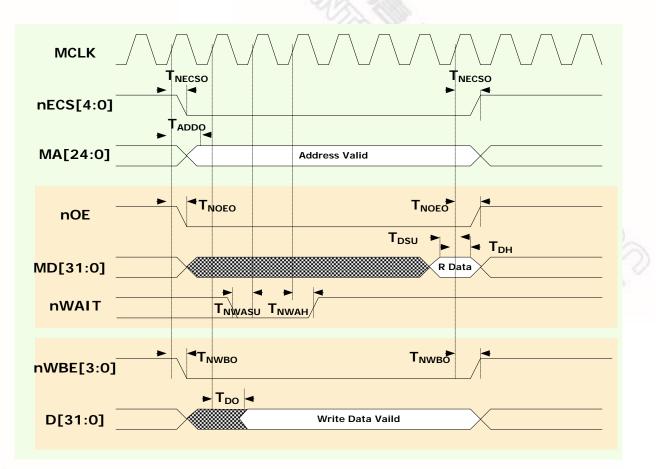

| 8.3.4 EBI(ROM/SRAM/External I/         | O) AC Characteristics654                |

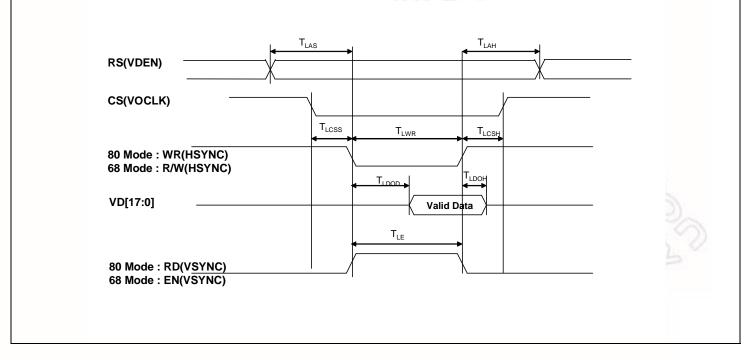

| 8.3.5 LCD Interface: MPU Type A        | C Characteristics                       |

| 023                                    | Publication Release Date: Jun. 18, 2010 |

|                                        |                                         |

9

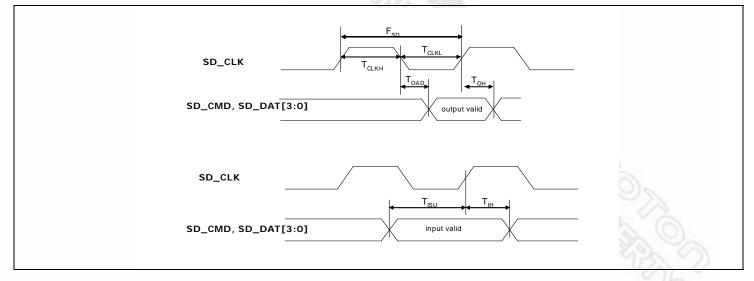

|    | 8.3.6  | SD Host Interface AC Characteristics           | 656 |

|----|--------|------------------------------------------------|-----|

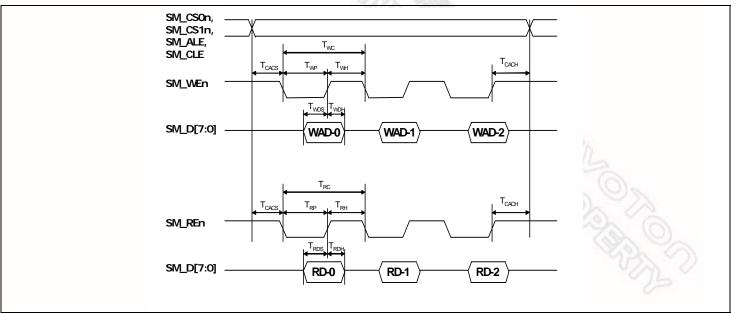

|    | 8.3.7  | NAND Flash Memory Interface AC Characteristics | 657 |

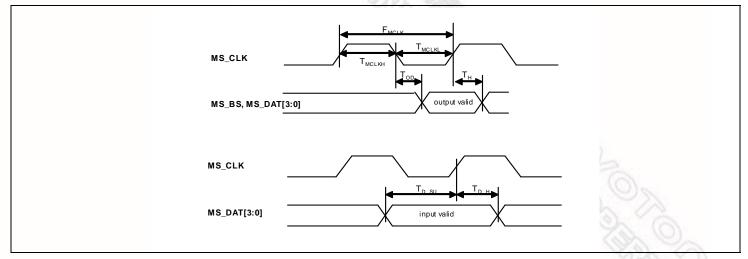

|    | 8.3.8  | Memory Stick Interface AC Characteristics      | 659 |

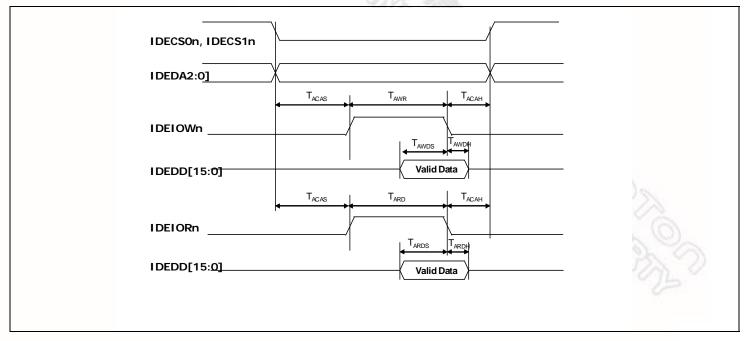

|    | 8.3.9  | ATAPI Interface AC Characteristic              | 660 |

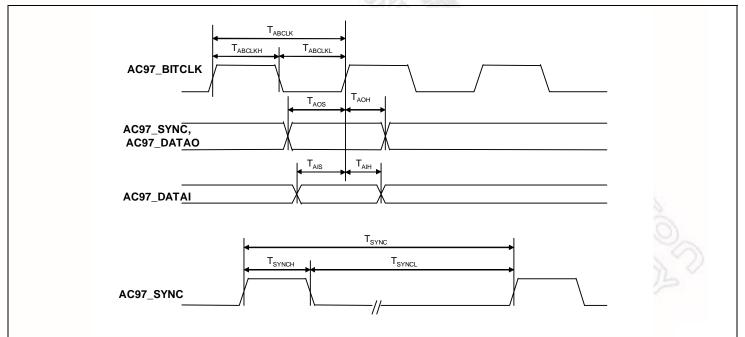

|    | 8.3.10 | Audio AC-Link Interface AC Characteristics     | 661 |

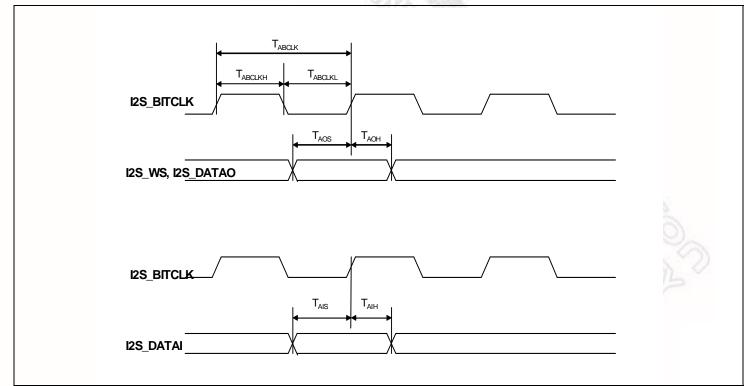

|    | 8.3.11 | Audio I2S Interface AC Characteristics         |     |

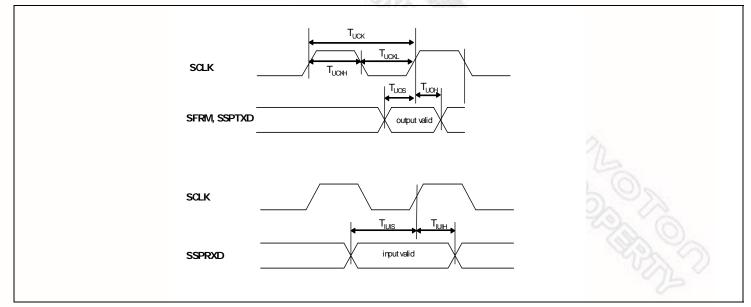

|    | 8.3.12 | USI(SPI/MW) Interface AC Characteristics       | 663 |

|    | 8.3.13 | USB Transceiver AC Characteristics             | 664 |

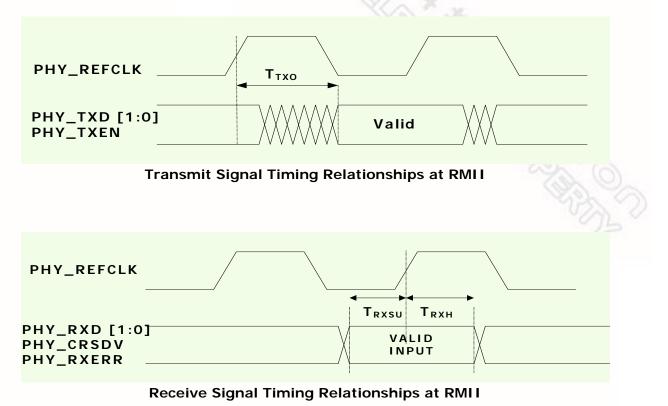

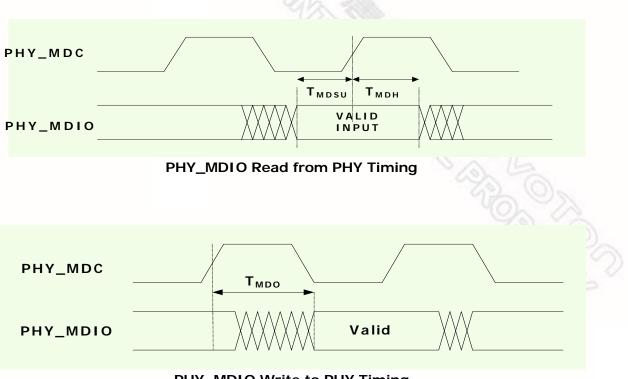

|    | 8.3.14 | EMC RMII AC Characteristics                    | 665 |

| 9  | PACKAG | E SPECIFICATIONS                               | 667 |

| 10 | REVIS  | ION HISTORY                                    | 668 |

### 32-BIT ARM926EJ-S BASED MCU

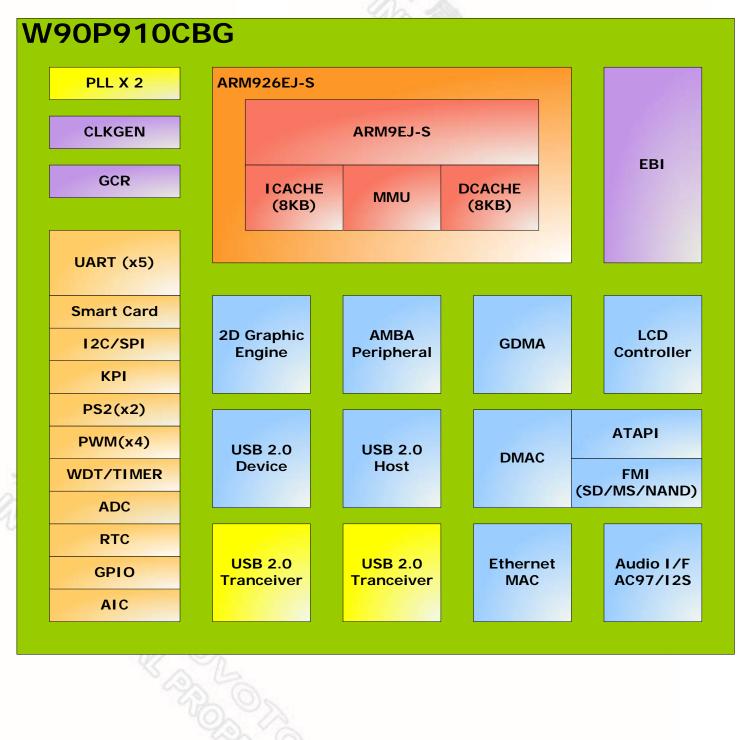

## **1** General Description

This chip is built around an outstanding CPU core: the 16/32 ARM926EJ-S RISC processor designed by Advanced RISC Machines, Ltd. The ARM926EJ-S core, offers 8K-byte I-cache and 8K-byte D-cache with MMU, is a low power, general-purpose integrated circuits. One 10/100 Mb MAC of Ethernet controller is builtin to reduce total system cost. A TFT type LCD controller, ADC touch screen controller and 2D graphics engine with various integrated on chip functions, this micro-controller is suitable for a high end, high performance and low cost related products as well as general purpose applications.

The following integrated on-chip functions are described in detail in this document.

|                    | MAIN FUNCTION                                   |

|--------------------|-------------------------------------------------|

| CPU                | • ARM926EJ-S                                    |

| Platform           | Programmable PLL System Clock Synthesizer       |

|                    | AMBA Peripherals                                |

|                    | Timer, Watchdog Timer                           |

|                    | Advanced Interrupt Controller                   |

|                    | General DMA Controller                          |

|                    | External Bus Interface Controller               |

| Networking         | Ethernet MAC Controller                         |

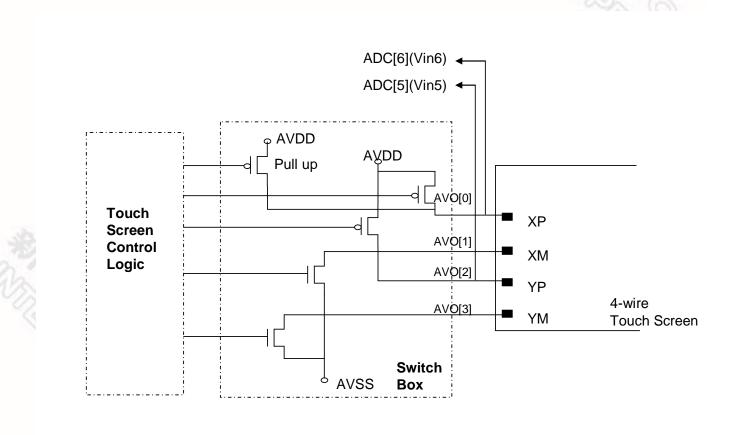

| Analog             | 10-bit ADC (Touch Screen)                       |

| Display Interface  | LCD Controller                                  |

| Graphics           | 2D Graphic Engine                               |

| Audio Interface    | 2-Channel I2S Controller                        |

|                    | 2-Channel AC97 Controller                       |

| USB Interface      | USB 1.1/2.0 High/Full/Low Speed Host Controller |

|                    | USB 2.0 High/Full Speed Device Controller       |

| Storage Interface  | NAND Flash Controller with ECC1/ECC4            |

|                    | SD/SDIO/MMC Controller                          |

|                    | Memory Stick (MS) Controller                    |

|                    | ATAPI Controller                                |

|                    | Smart Card Controller                           |

| Peripheral & Misc. | • GPIO                                          |

| are say            | 4-Channel PWM                                   |

|                    | UART/HS-UART                                    |

|                    | USI (SPI/uWire)                                 |

|                    | I2C (Master) Controller                         |

|                    | Keypad Scan Controller                          |

|                    | RTC (Real Time Clock)                           |

|                    | PS2 Controller                                  |

|                    | PCI Controller                                  |

## 32-BIT ARM926EJ-S BASED MCU

## 2 Features

#### Architecture

- Efficient and powerful ARM926EJ-S core with fully 16/32-bit RISC architecture

- Little Endian mode supported

- 8K-byte I-cache and 8K-byte D-cache with MMU

- Cost-effective JTAG-based debug solution

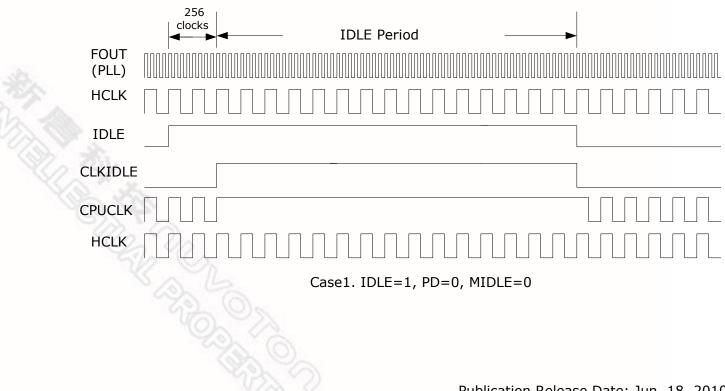

#### Power management

- Programmable clock enable for individual peripherals

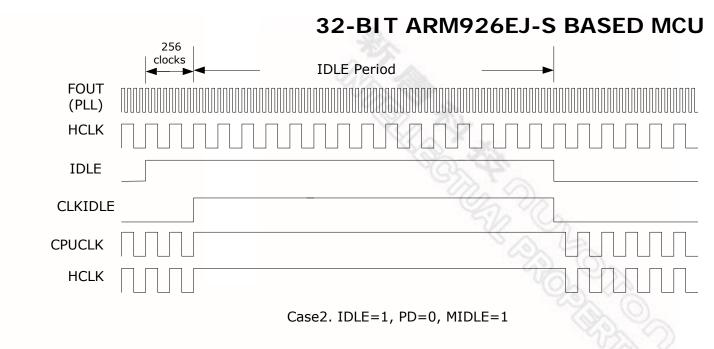

- IDLE mode to halt ARM Core and keep peripheral working

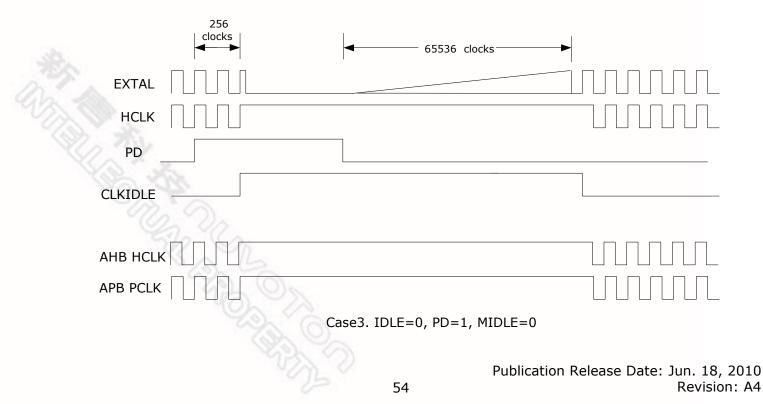

- Power-Down mode to stop all clocks included external crystal oscillator.

- Exit IDLE/Power-Down by interrupts

- Wakeup by interrupt, USB device, and RTC

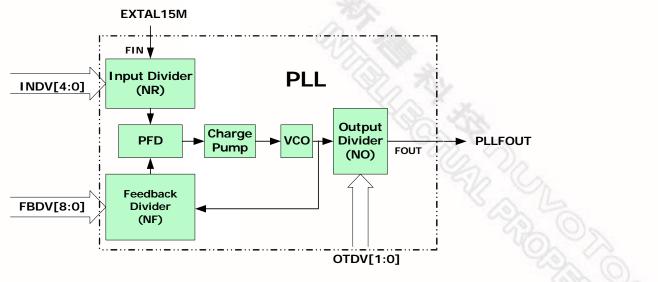

#### Two PLLs

- The external clock can be multiplied by on-chip PLL to provide high frequency system clock

- The input frequency range is 4-30MHz; 15MHz is preferred.

- Programmable clock frequency

#### Advanced Interrupt Controller

- 31 interrupt sources, including 8 external interrupt sources

- Programmable normal or fast interrupt mode (IRQ, FIQ)

- Programmable as either edge-triggered or level-sensitive for 8 external interrupt sources

- Programmable as either low-active or high-active for 8 external interrupt sources

- Priority methodology is encoded to allow for interrupt daisy-chaining

- Automatically mask out the lower priority interrupt during interrupt nesting

- Automatically clear the interrupt flag when the interrupt source is programmed to be edge-triggered

#### **General DMA Controller**

- 2-channel General DMA for memory-to-memory data transfers without CPU intervention

- Support two external DMA request

- Increments or decrements a source or destination address in 8-bit, 16-bit or 32-bit data transfers

- 8-data burst mode

### **External Bus Interface**

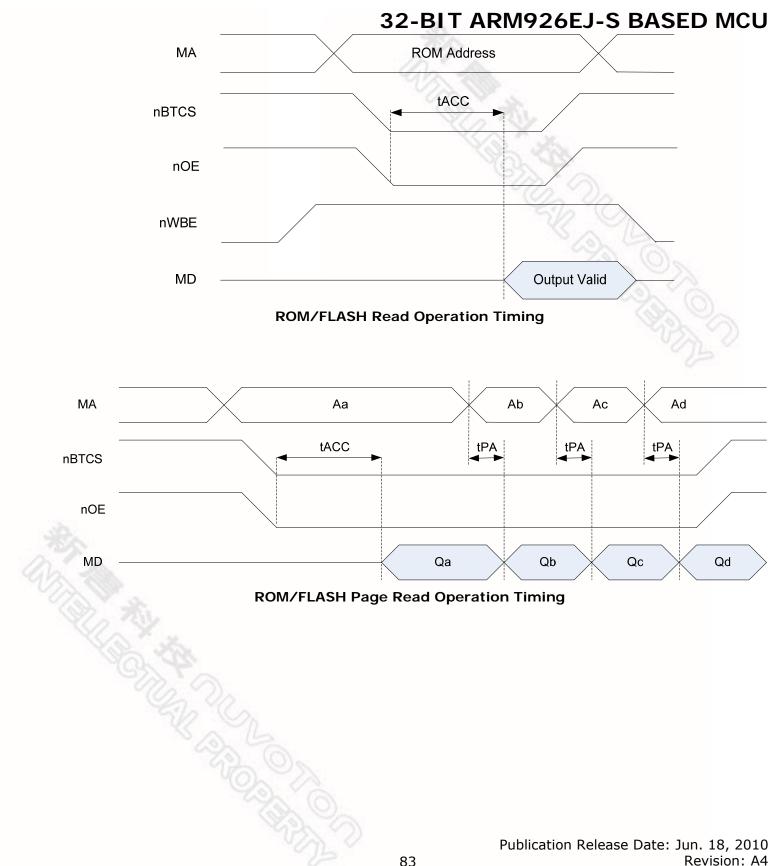

- 8/16/32-bit external bus support for ROM/SRAM, flash memory, SDRAM and external I/Os

- Programmable access cycle (0-7 wait cycle)

- Four-word depth write buffer

### 32-BIT ARM926EJ-S BASED MCU

#### **Ethernet MAC Controller**

- 100/10-Mbps operation

- DMA engine with burst mode

- MAC Tx/Rx buffers (256 bytes Tx, 256 bytes Rx)

- Full compliance with IEEE standard 802.3

- RMII interface only

- Station Management Signaling

- On-Chip CAM (up to 16 destination addresses)

- Full-duplex mode with PAUSE feature

- Long/short packet modes

#### ADC Interface

- Power supply voltage: 3.3V

- 8 analog input with voltage range: 0 3.3 volts

- Touch screen semi-auto/auto conversion modes supported

- Waiting for trigger mode supports

- standby mode supports

- 4-level voltage detector

#### **LCD Controller**

- Support the 8/12/16/18/24-bit data interface to connect with 80/68 series MPU type LCM module

- Convert RGB-565, RGB-888X, YUV-422 display data to RGB-444, RGB-565, RGB-666, RGB-888, YUV-422 color format for display output

- Support CCIR-656( with vsync / hsync / data enable sync signal ) 8/16-bit YUV data output format to connect with external TV encoder

- Support 8/16 bpp OSD data with Image overlay function to facilitate the diverse graphic UI.

- Support linear 1X 8X image scaling up function.

- Support Picture-In-Picture display function

- Support hardware cursor.

#### 2-D Graphics Engine

- Color depth 8-bit/16-bit/32-bit in RGB domain or RGB332/RGB565/RGB888 are supported

- Contains 2D Bit Block Transfer (BitBLT) functions as defined in Microsoft GDI. It includes HostBLT, Pattern BLT, Color/Font Expanding BLT, Transparent BLT, Tile BLT, Block Move BLT, Copy File BLT, Color/Font Expansion, and Rectangle Fill, etc.

- Supports fore/background colors and all Microsoft 256 ternary raster-operation codes (ROP)

- Clipping window can be defined as inside or outside clipping

- Implements the alpha-blending function for source/destination picture overlaying

- Fast Bresenham line drawing algorithm is used to draw solid/textured lines

- Supports rectangular border or frame drawing

- Supports picture re-sizing by 1/255 ~ 254/255 down-scaling and 1 ~ 1.996 up-scaling (1+254/255).

- Supports object rotations in different degrees, that is L45/L90/R45/R90/M180/F180/X180, where

- L45/L90 means rotate left 45/90 degrees,

- R45/R90 means rotate right 45/90 degrees,

- M180 means mirror (flop),

- ▶ F180 means up-side-down (flip) and X180 for rotations by 180 degrees

### 32-BIT ARM926EJ-S BASED MCU

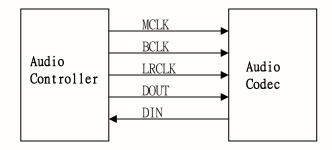

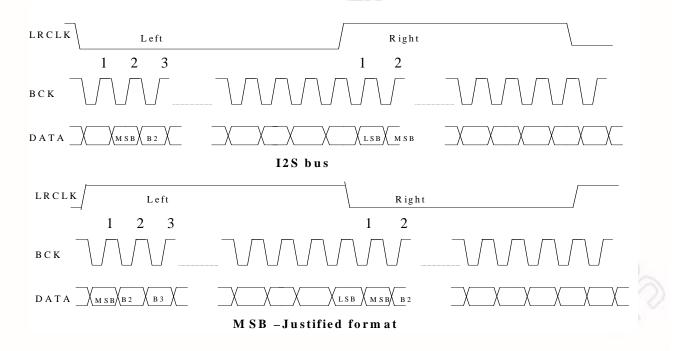

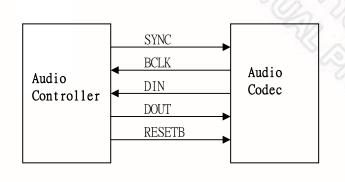

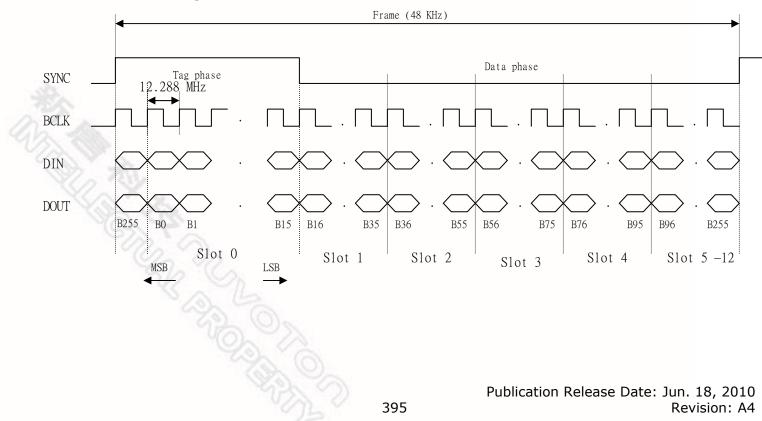

#### 2-Channel AC97/I2S Controller

- Support I2S interface.

- Support AC97 interface.

- Built-in an 8x32 bits internal buffer.

- Support DMA function for data transfer between internal buffer and system memory.

- Support 16-bit I2S and MSB-justified format.

#### USB Host Controller with transceiver

- Fully compliant with USB Revision 2.0 specification.

- Enhanced Host Controller Interface (EHCI) Revision 1.0 compatible.

- Open Host Controller Interface (OHCI) Revision 1.0 compatible. •

- Supports high-speed (480Mbps), full-speed (12Mbps) and low-speed (1.5Mbps) USB devices. •

- Supports Control, Bulk, Interrupt, Isochronous and Split transfers.

- Built-in DMA for real-time data transfer. •

- Support two ports (one port transceiver is shared with USB Device Controller)

#### USB Device Controller with transceiver

- Compliant with USB version 2.0 specification. •

- Software control for device remote-wakeup.

- Supports 6 configurable IN/OUT endpoints in addition to Control Endpoint. Each of these endpoints can • be configures as IN or OUT with Isochronous, Bulk or Interrupt transfer.

- Three different modes of operation of an in-endpoint (Auto validation mode, manual validation mode, Flv mode.

- Supports Endpoint Maximum Packet Size up to 1024 bytes.

### ATAPI Interface Controller

- ATAPI I/O Interface, ATA/ATAPI-6 compatible

- Provide register transfer mode for read/write device command block registers •

- Provide PIO data transfer mode •

- Provide Multiword DMA data transfer mode

- Provide Ultra-DMA data transfer mode

#### Flash Memory Interface (FMI)

- Directly connect to Secure Digital (SD, MMC and SDIO) flash memory card, Memory Stick (Memory stick PRO) and NAND type flash memory.

- Supports DMA function to accelerate the data transfer between the internal buffer, external SDRAM, and flash memory card.

- Two 512 bytes internal buffers are embedded inside Charles and the second second

### 32-BIT ARM926EJ-S BASED MCU

### Smart Card Host Interface (SCHI)

- ISO-7816 compliant

- PC/SC T=0, T=1 compliant

- 16-byte transmitter FIFO and 16-byte receiver FIFO

- FIFO threshold interrupt to optimize system performance

- Programmable transmission clock frequency

- Versatile baud rate configuration

- UART-like register file structure

- General-purpose C4, C8 channels

#### PS2 Host Interface

- PS2 compatible keyboard or mouse interface

- Half-Duplex Bi-directional synchronous serial interface using op-drain outputs for clock and data

- Odd parity generation and checking

#### I 2C Master

- Compatible with I<sup>2</sup>C standard, support master mode only

- Multi Master Operation

- Clock stretching and wait state generation

- Provide multi-byte transmit operation, up to 4 bytes can be transmitted in a single transfer

- Software programmable acknowledge bit

- Arbitration lost interrupt, with automatic transfer cancellation

- Start/Stop/Repeated Start/Acknowledge generation

- Start/Stop/Repeated Start detection

- Bus busy detection

- Supports 7 bit addressing mode

- Software mode I<sup>2</sup>C

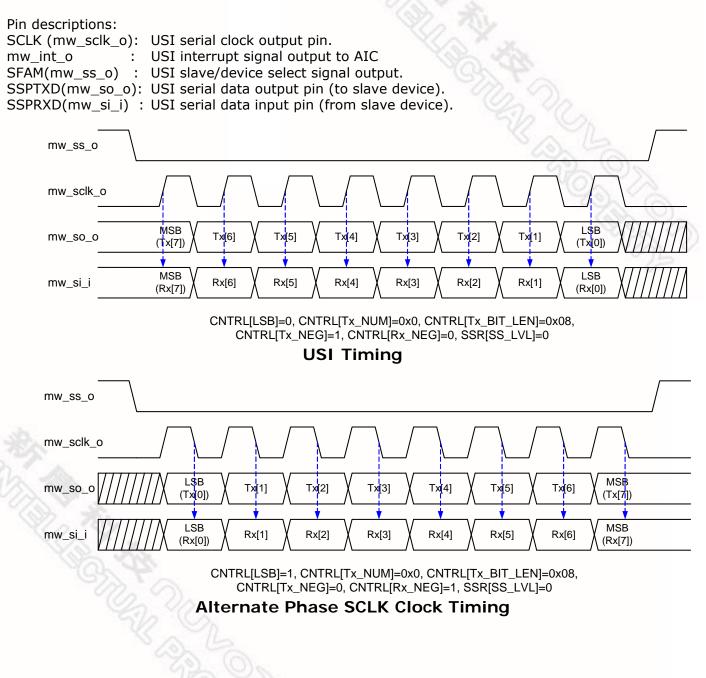

### Universal Serial Interface (USI)

- Support MICROWIRE/SPI master mode

- Support full/half duplex synchronous serial data transfer

- Variable length of transfer word up to 32 bits

- Provide burst mode operation, transmit/receive can be executed up to four times in one transfer

- MSB or LSB first data transfer

- Receive and Transmit on both rising or falling edge of serial clock independently

#### UART

- Five UART (serial I/O) blocks with interrupt-based operation

- Support for 5-bit, 6-bit, 7-bit or 8-bit serial data transmit and receive

- Programmable baud rates

- 1,1<sup>1</sup>/<sub>2</sub> or 2 stop bits

- Odd or even parity

- Break generation and detection

- Parity, overrun and framing error detection

- X16 clock mode

- Support for Bluetooth, IrDA, Micro-printer control and two debug ports

### 32-BIT ARM926EJ-S BASED MCU

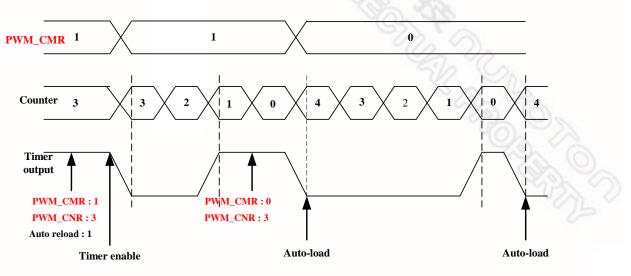

#### Timers

- Five programmable 24-bit timers with 8-bit pre-scalar

- One programmable 20-bit Watchdog timer

- One-short mode, period mode or toggle mode operation

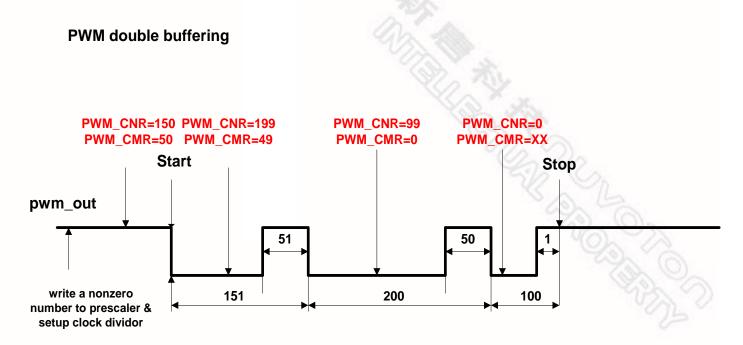

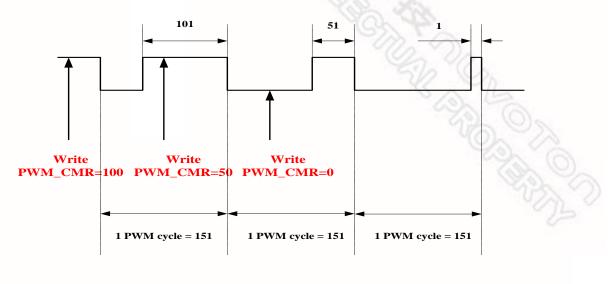

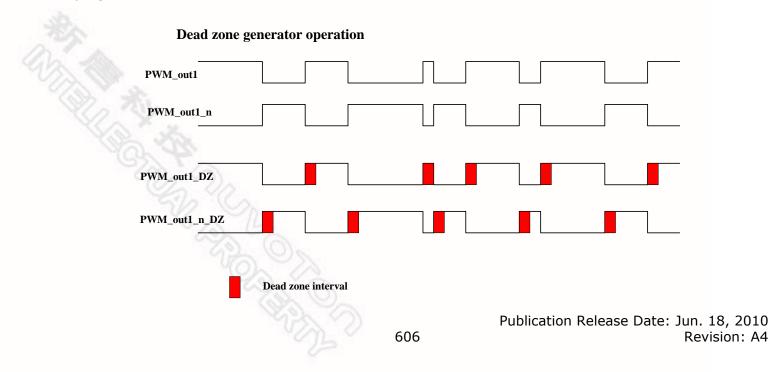

#### 4-Channel PWM

- Four 16-bit timers

- Two 8-bit pre-scalars & Two 4-bit divider

- Programmable duty control of output waveform (PWM)

- Auto reload mode or one-shot pulse mode

- Dead-zone generator

#### Real Time Clock (RTC)

- Time counter (second, minute, hour) and calendar counter (day, month, year)

- Alarm register (second, minute, hour, day, month, year)

- 12 or 24-hour mode selectable

- Recognize leap year automatically

- Day of the week counter

- Frequency compensate register (FCR)

- Beside FCR, all clock and alarm data expressed in BCD code

- Support tick time interrupt

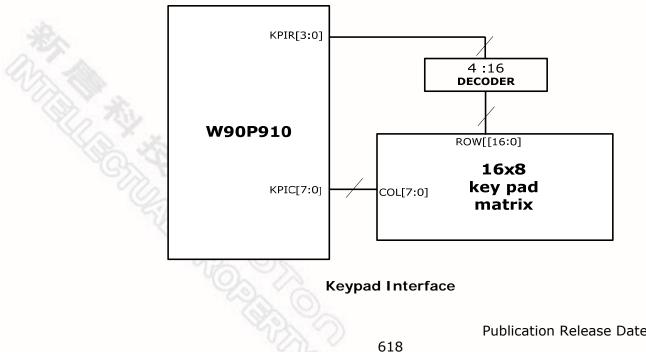

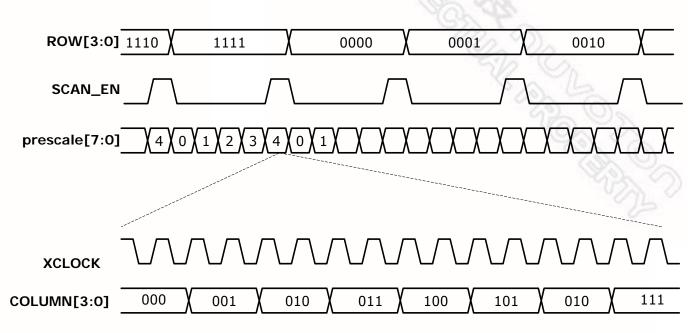

#### Keypad Scan Interface

- Scan up to 16x8 with an external 4 to 16 decoder; or 4x8 array without auxiliary component

- Programmable de-bounce time

- One or two keys scan with interrupt and three keys reset function.

- Support low power wakeup function

#### Programmable I/Os

- Pins individually configurable to input, output or I/O mode for dedicated signals

- I/O ports are Programmable and Configurable for Multiple functions

#### **Operation Voltage Range**

- VDD18 for IO Buffer: 1.8V+/-10%

- VDD33 for Core Logic: 3.3V+/-10%

- USBVDDC0/USBVDDC1/USBVDDT0/USBVDDT1 for USB: 3.3V+/-5%

- AVDD33 for ADC: 3.3V+/-10%

- RTCVDD18 for RTC: 1.8V+/-10%

- PLLVDD18 for PLL: 1.8V+/-10%

#### **Operation Temperature Range**

• -40°C ~ +85°C

#### **Operating Frequency**

Up to 200 MHz for ARM926EJ-S CPU

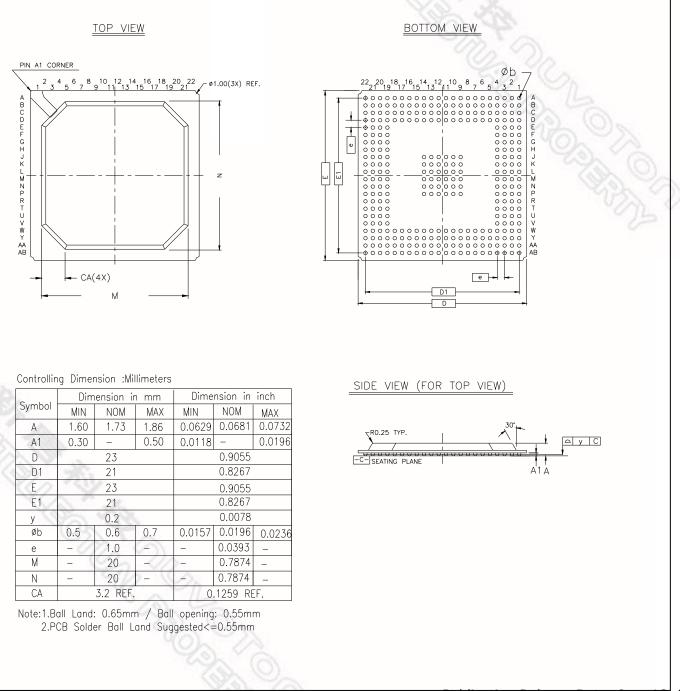

#### Package Type

324-ball PBGA, Pb free, Halogen free

### 32-BIT ARM926EJ-S BASED MCU

## 3 Pin Diagram

### NUC910ABN Pin Diagram

| N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | B Column Later                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    | 1        | 2         | 3         | 4         | 5        | 6        | 7        | 8        | 9        | 10       | 11       | 12        | 13     | 14         | 15        | 16        | 17        | 18        | 19        | 20       | 21      | 22       |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----------|-----------|-----------|-----------|----------|----------|----------|----------|----------|----------|----------|-----------|--------|------------|-----------|-----------|-----------|-----------|-----------|----------|---------|----------|----|

| No.       N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | C Rate <th< th=""><th>A</th><th>NC</th><th>XTAL48M0</th><th>EXTAL48MC</th><th>HDS</th><th>DPO</th><th>DN0</th><th>USBVSSCO</th><th>DPI</th><th>DNI</th><th>USBVSSCI</th><th>XTAL48MI</th><th>EXTAL48M1</th><th>RXDO</th><th>AC97_SYNC</th><th>PHY_RX[1]</th><th>'HY_REFCL</th><th>PHY_TX[1]</th><th>IRQ[3]</th><th>IRQ[0]</th><th>RXD4</th><th>DSR3</th><th>VDD33</th><th>A</th></th<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | A  | NC       | XTAL48M0  | EXTAL48MC | HDS       | DPO      | DN0      | USBVSSCO | DPI      | DNI      | USBVSSCI | XTAL48MI | EXTAL48M1 | RXDO   | AC97_SYNC  | PHY_RX[1] | 'HY_REFCL | PHY_TX[1] | IRQ[3]    | IRQ[0]    | RXD4     | DSR3    | VDD33    | A  |

| N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Normal and any                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | в  | SCL[0]   | nWDT      | nRESET    | USBVSSTO  | USBVSSTO | USBVSSTO | NC       | USBVSSTI | USBVSST1 | USBVSSTI | NC       | RXD1      | TXD0   | AC97_BITCL | PHY_RX[0] | PHY_TXEN  | PHY_TX[0] | IRQ[2]    | RXD3      | TXD3     | DTR3    | SC1_CLK  | в  |

| No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | с  | SCL[1]   | SDA[0]    | VDD33     | NC        | USBVDDTO | NC       | USBVDDC0 | REXTI    | USBYDDCI | OVI      | UPWR     | CTSI      | TXD1   | AC97_DATO  | AC97_DATI | PHY_RXERI | PHY_MDIO  | IRQ[1]    | TXD4      | VDD33    | SD_CD   | GP10(7)  | с  |

| A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | D  | IDECSIn  | (DECS0n   | SDA[1]    | VDD33     | rextô    | USBVDDTO | USBVDDTI | USBVDDTI | VDD33    | UPWRI    | rxd2     | TXD2      | RTSI   | VDD33      |           | PHY_CRSDV | PHY_MDC   | NC        | VDD33     | SD_DAT3  | GP10[9] | GPIO[10] | D  |

| A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Е  | IDEINTRQ | IDEDA[2]  | IDEDA[1]  | IDEDA[0]  |          |          |          |          |          |          |          |           |        |            |           |           |           |           | SD_CLK    | SD_DAT0  | SD_DAT1 | SD_DAT2  | Е  |

| A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | F  | IDEIOWn  | IDEIORn   | IDEIORDY  | IDEDMACKs |          |          |          |          |          |          |          |           |        |            |           |           |           |           | SM_D(5)   | SM_D[6]  | SM_D[7] | SD_CMD   | F  |

| Marka for the state of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | G  | IDED[2]  | IDED[1]   | IDED(0)   | IDEMARQ   |          |          |          |          |          |          |          |           |        |            |           |           |           |           | SM_D(1)   | SM_D[2]  | SM_D[3] | SM_D[4]  | G  |

| $ \mathbf{v} = \mathbf{v} + \mathbf{v} +$ | A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | н  | IDED[6]  | IDED(5)   | IDED[4]   | IDED[3]   |          |          |          |          |          |          |          |           |        |            |           |           |           |           | SM_Ren    | SM_WPn   | SM_RBn  | SM_D[0]  | н  |