### **32-BIT ARM7TDMI-BASED MCU**

# NUC745 16/32-bit ARM microcontroller Product Data Sheet

### Table of Contents-

| 1. | GENE   | RAL DE | SCRIPTION                                | 1    |

|----|--------|--------|------------------------------------------|------|

| 2. | FEATU  | JRES   |                                          | 2    |

| 3. |        |        | Л                                        |      |

| 4. | PIN AS | SIGNM  | /ENT                                     | 8    |

| 5. | PIN DE | SCRIP  | PTION                                    | 13   |

| 6. | FUNC   | TIONAL | DESCRIPTION                              | 24   |

|    | 6.1    | ARM7   | TDMI CPU CORE                            | 24   |

|    | 6.2    |        | n Manager                                |      |

|    |        | 6.2.1  | Overview                                 | 25   |

|    |        | 6.2.2  | System Memory Map                        | 25   |

|    |        | 6.2.3  | Address Bus Generation                   | 28   |

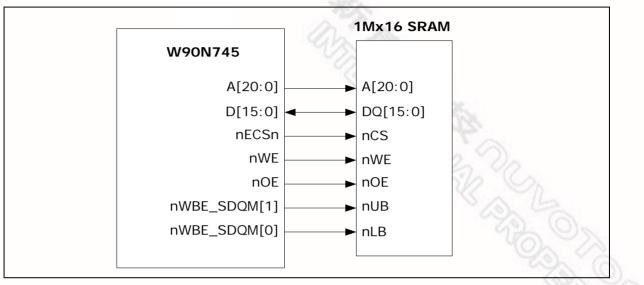

|    |        | 6.2.4  | Data Bus Connection with External Memory | 28   |

|    |        | 6.2.5  | Bus Arbitration                          | 37   |

|    |        | 6.2.6  | Power Management                         | 38   |

|    |        | 6.2.7  | Power-On Setting                         | 41   |

|    |        | 6.2.8  | System Manager Control Registers Map     | 41   |

|    | 6.3    | Extern | al Bus Interface                         | 56   |

|    |        | 6.3.1  | EBI Overview                             | 56   |

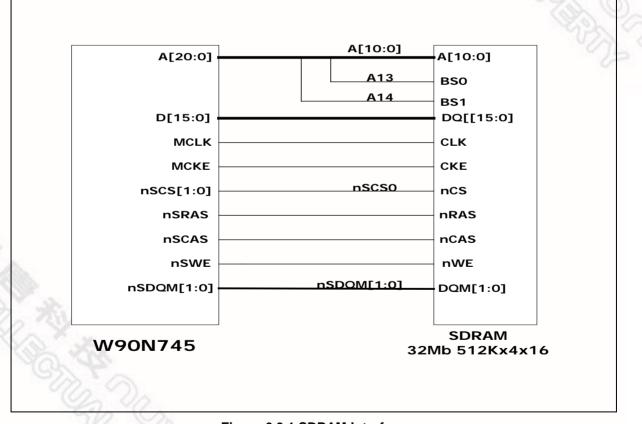

|    |        | 6.3.2  | SDRAM Controller                         | 56   |

|    |        | 6.3.3  | EBI Control Registers Map                | 60   |

|    | 6.4    | Cache  | Controller                               | 79   |

|    |        | 6.4.1  | On-Chip RAM                              | 79   |

|    |        | 6.4.2  | Non-Cacheable Area                       | 79   |

|    |        | 6.4.3  | Instruction Cache                        | 80   |

|    |        | 6.4.4  | Data Cache                               | 82   |

|    |        | 6.4.5  | Write Buffer                             | 84   |

|    |        | 6.4.6  | Cache Control Registers Map              | 84   |

|    | 6.5    | Ethern | et MAC Controller                        | 92   |

|    |        | 6.5.1  | EMC Functional Description               | 93   |

|    |        | 6.5.2  | EMC Register Mapping                     | .103 |

|    | 6.6    | GDMA   | A Controller                             | 158  |

|    |        | 6.6.1  | GDMA Functional Description              | .158 |

|    |        | 6.6.2  | GDMA Register Map                        | .159 |

|    | 6.7    | USB H  | lost Controller                          | 168  |

|    |        | 6.7.1  | USB Host Functional Description          | .168 |

|    |        | 6.7.2  | USB Host Controller Registers Map        | .169 |

|    | 6.8    | USB D  | Device Controller                        | 192  |

|    |        |        |                                          |      |

|      | 6.8.1                 | USB Endpoints                                           | 192   |

|------|-----------------------|---------------------------------------------------------|-------|

|      | 6.8.2                 | Standard Device Request                                 | 192   |

|      | 6.8.3                 | USB Device Register Description                         | 192   |

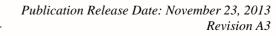

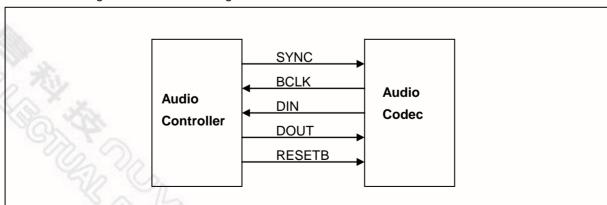

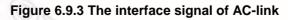

| 6.9  | Audio (               | Controller                                              | . 231 |

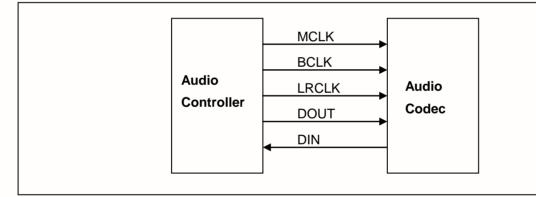

|      | 6.9.1                 | I <sup>2</sup> S Interface                              | 231   |

|      | 6.9.2                 | AC97 Interface                                          | 232   |

|      | 6.9.3                 | Audio Controller Register Map                           | 235   |

| 6.10 | Univers               | sal Asynchronous Receiver/Transmitter Controller        | . 254 |

|      | 6.10.1                | UARTO                                                   |       |

|      | 6.10.2                | UART1                                                   | 256   |

|      | 6.10.3                | UART2                                                   | 258   |

|      | 6.10.4                | UART3                                                   | 260   |

|      | 6.10.5                | General UART Controller                                 | 261   |

|      | 6.10.6                | High speed UART Controller                              | 274   |

| 6.11 | Timer/                | Watchdog Controller                                     | . 288 |

|      | 6.11.1                | General Timer Controller                                | 288   |

|      | 6.11.2                | Watchdog Timer                                          | 288   |

|      | 6.11.3                | Timer Control Registers Map                             | 288   |

| 6.12 | Advand                | ced Interrupt Controller                                | . 296 |

|      | 6.12.1                | Interrupt Sources                                       | 297   |

|      | 6.12.2                | AIC Registers Map                                       | 300   |

| 6.13 | Genera                | al-Purpose Input/Output                                 | . 313 |

|      | 6.13.1                | GPIO Register Description                               | 315   |

|      | 6.13.2                | GPIO Register Description                               | 316   |

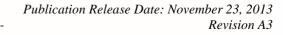

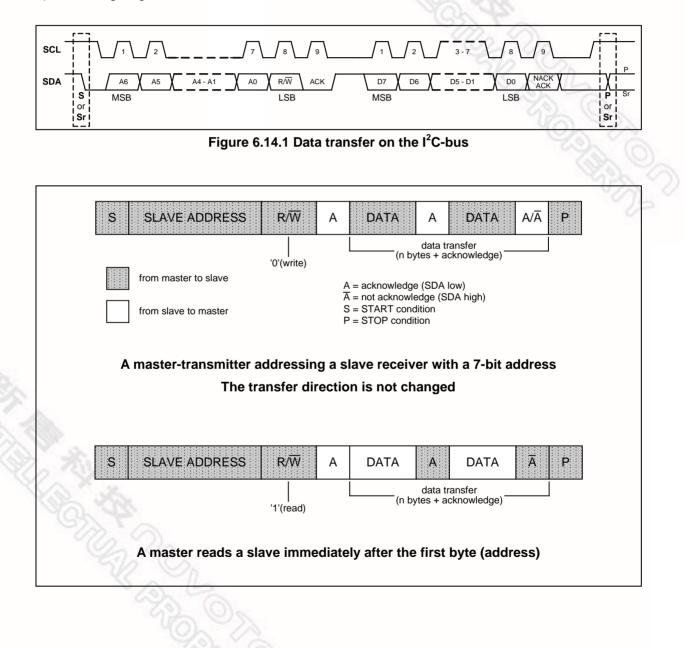

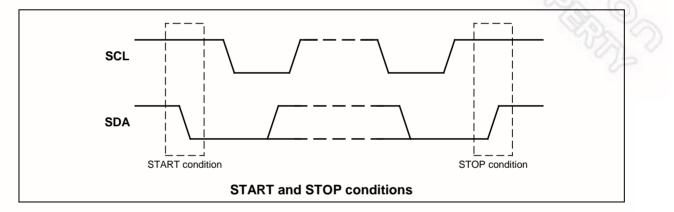

| 6.14 | I <sup>2</sup> C Inte | erface                                                  | . 337 |

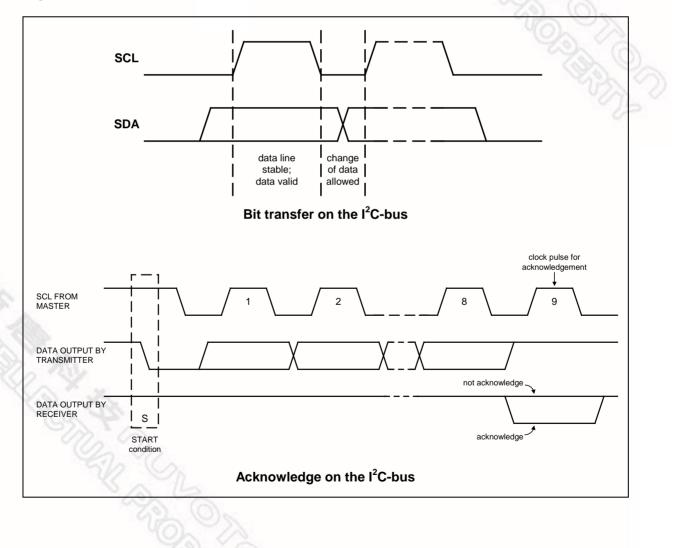

|      | 6.14.1                | I <sup>2</sup> C Protocol                               | 338   |

|      | 6.14.2                | I <sup>2</sup> C Serial Interface Control Registers Map | 341   |

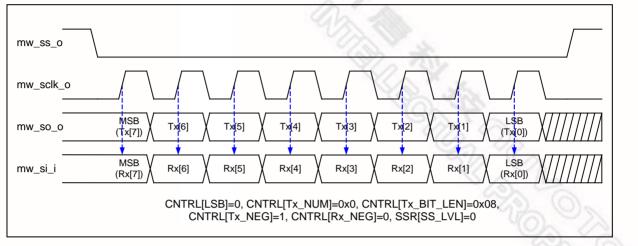

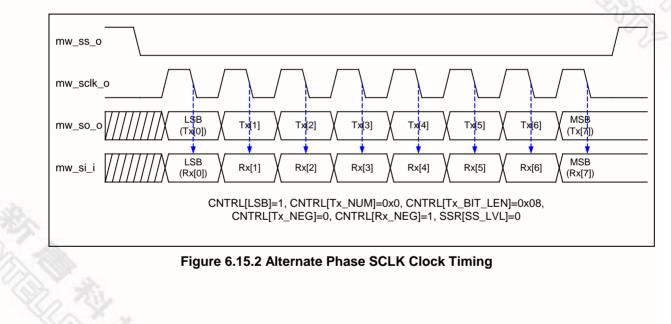

| 6.15 | Univer                | sal Serial Interface                                    | . 348 |

|      | 6.15.1                | USI Timing Diagram                                      | 349   |

|      | 6.15.2                | USI Registers Map                                       | 350   |

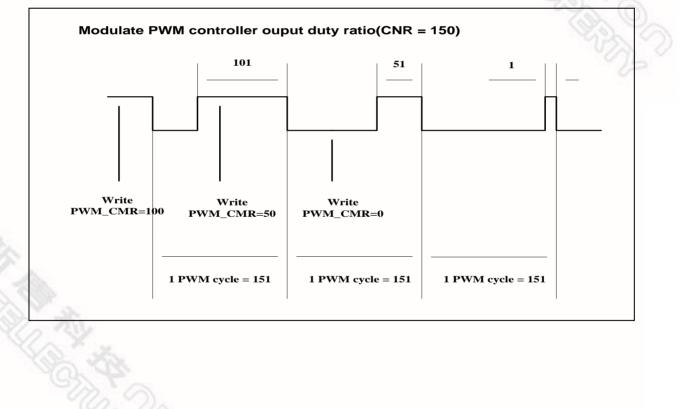

| 6.16 | PWM.                  |                                                         | . 357 |

|      | 6.16.1                | PWM Double Buffering and Reload Automatically           |       |

|      | 6.16.2                | Modulate Duty Ratio                                     | 358   |

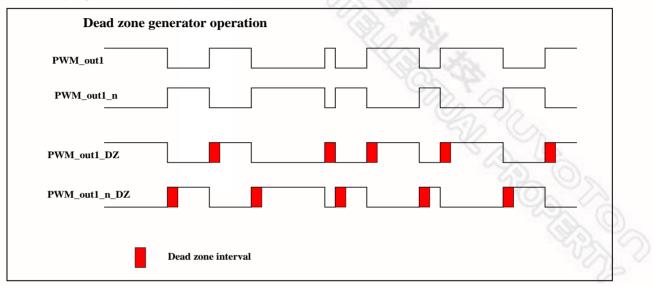

|      | 6.16.3                | Dead Zone Generator                                     | 359   |

|      | 6.16.4                | PWM Timer Start Procedure                               | 359   |

|      | 6.16.5                | PWM Timer Stop Procedure                                | 359   |

|      | 6.16.6                | PWM Register Map                                        | 360   |

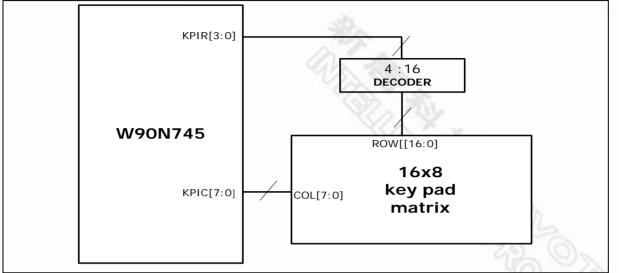

| 6.17 | Keypad                | d Interface                                             | . 370 |

|      | 6.17.1                | Keypad Interface Register Map                           | 371   |

|      | 6.17.2                | Register Description                                    | 372   |

|      |                       |                                                         |       |

Publication Release Date: November 23, 2013 Revision A3

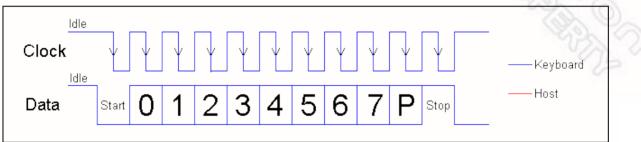

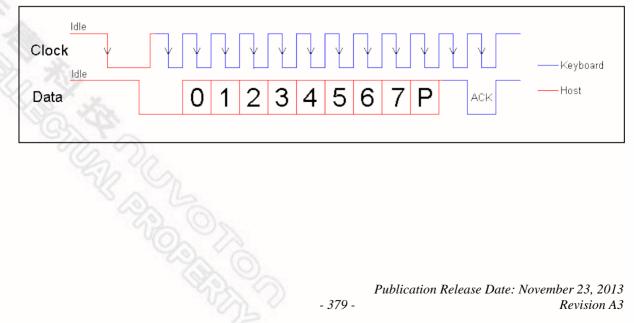

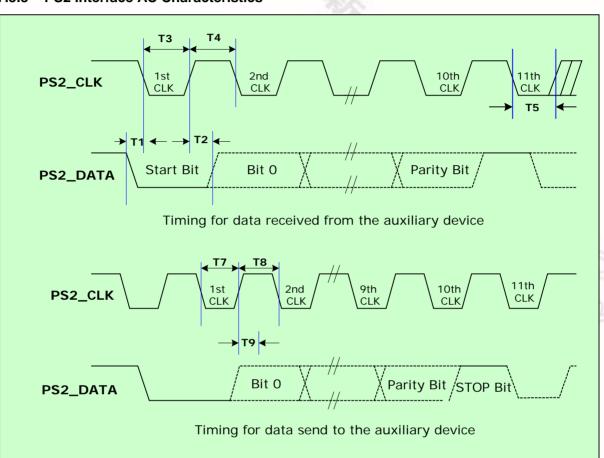

|     | 6.18  | PS2 Host Interface Controller                        | 379 |

|-----|-------|------------------------------------------------------|-----|

|     |       | 6.18.1 PS2 Host Controller Interface Register Map    |     |

|     |       | 6.18.2 Register Description                          |     |

| 7.  | ELEC  | RICAL SPECIFICATIONS                                 | 385 |

|     | 7.1   | Absolute Maximum Ratings                             |     |

|     | 7.2   | DC Specifications                                    | 385 |

|     |       | 7.2.1 Digital DC Characteristics                     |     |

|     |       | 7.2.2 USB Transceiver DC Characteristics             |     |

|     | 7.3   | AC Specifications                                    | 388 |

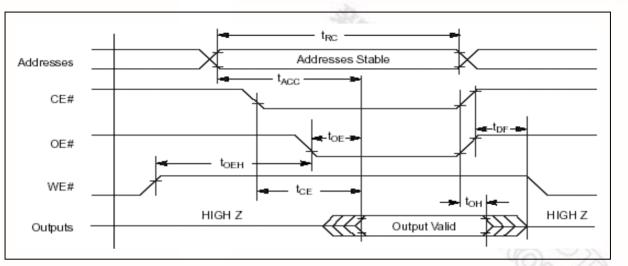

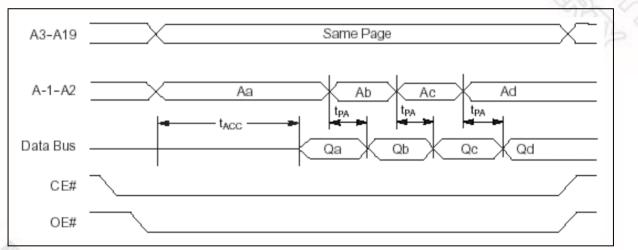

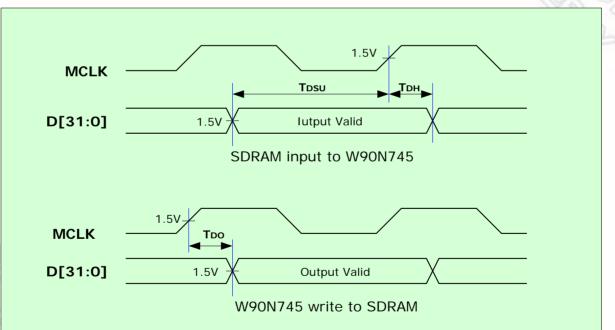

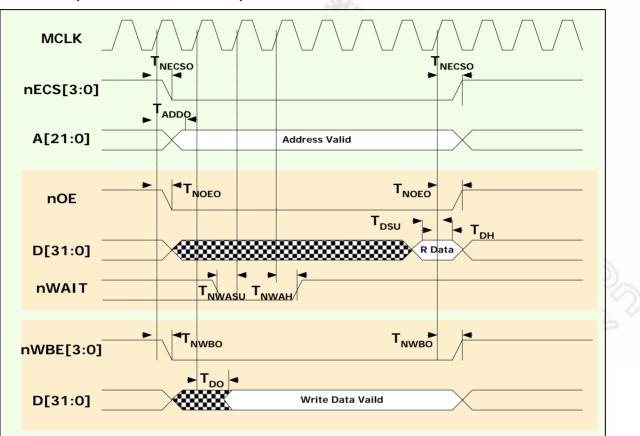

|     |       | 7.3.1 EBI/SDRAM Interface AC Characteristics         |     |

|     |       | 7.3.2 EBI/(ROM/SRAM/External I/O) AC Characteristics |     |

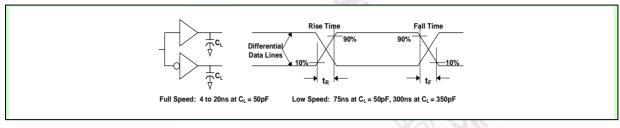

|     |       | 7.3.3 USB Transceiver AC Characteristics             |     |

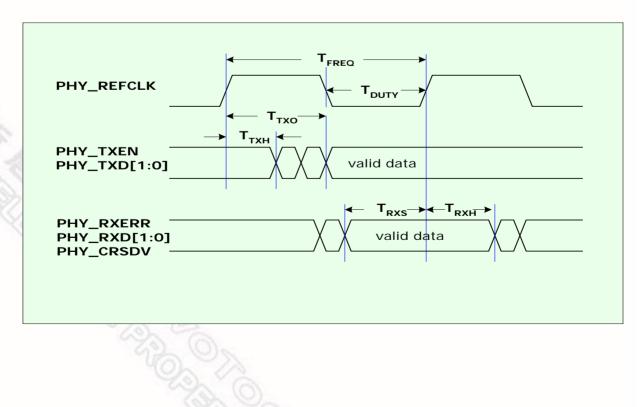

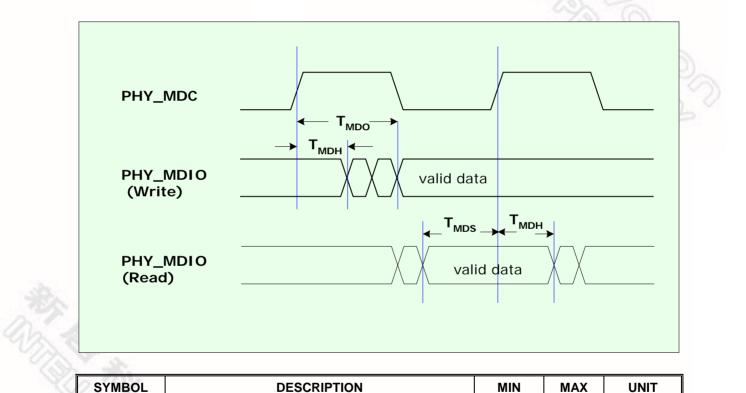

|     |       | 7.3.4 EMC RMII AC Characteristics                    |     |

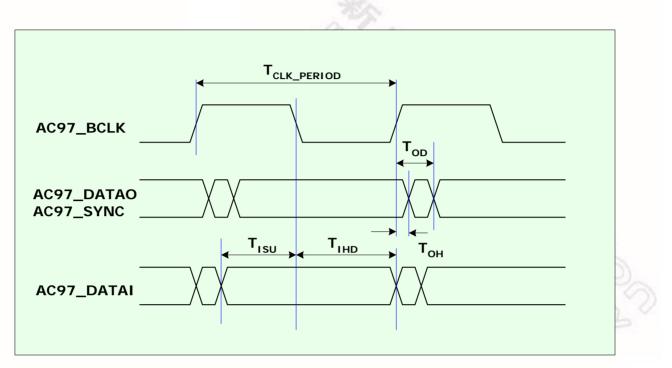

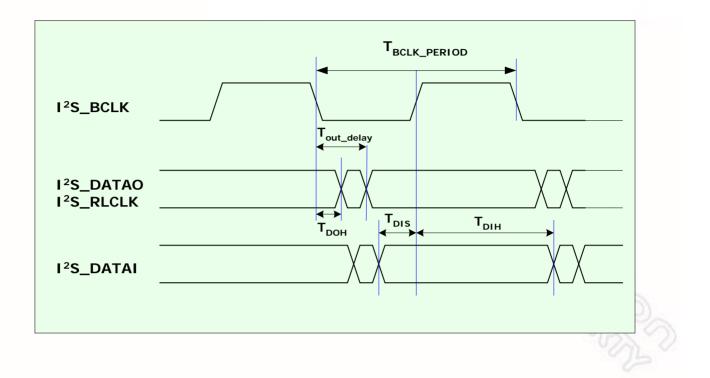

|     |       | 7.3.5 AC97/I2S Interface AC Characteristics          |     |

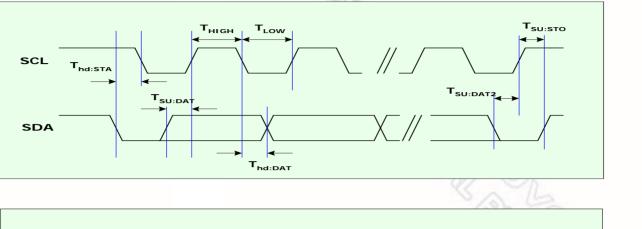

|     |       | 7.3.6 I <sup>2</sup> C Interface AC Characteristics  |     |

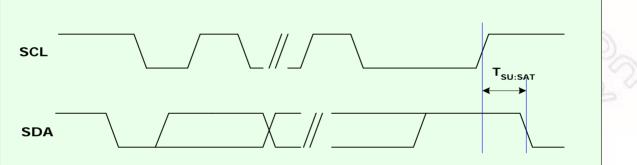

|     |       | 7.3.7 USI Interface AC Characteristics               |     |

|     |       | 7.3.8 PS2 Interface AC Characteristics               |     |

| 8.  | ORDE  | RING INFORMATION                                     | 398 |

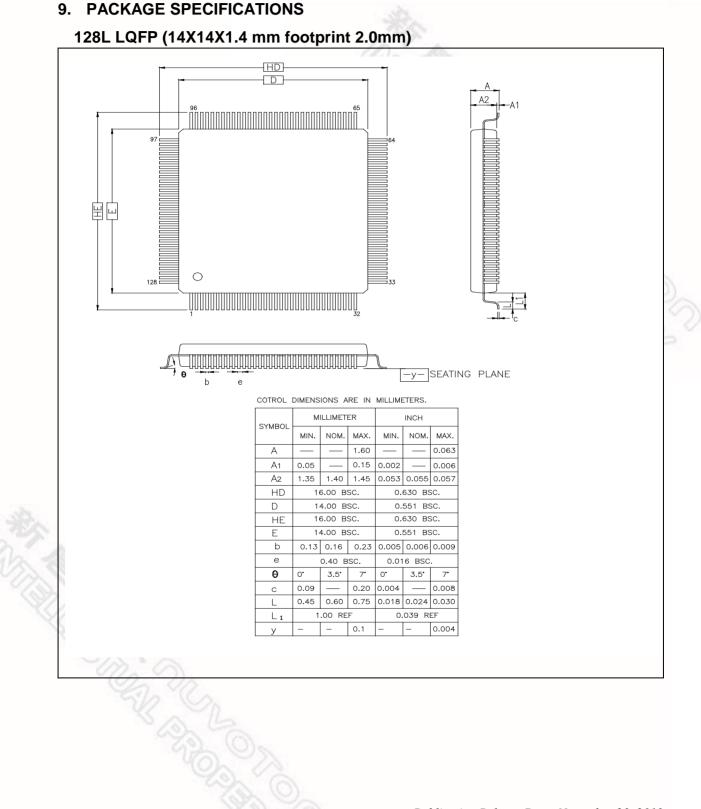

| 9.  | PACK  | GE SPECIFICATIONS                                    | 399 |

| 10. | APPE  | IDIX A: NUC745 REGISTERS MAPPING TABLE               | 400 |

| 11. | REVIS | ON HISTORY                                           | 415 |

Publication Release Date: November 23, 2013 Revision A3

- III -

### 1. GENERAL DESCRIPTION

The NUC745 is built around an outstanding CPU core, the 16/32 ARM7TDMI RISC processor which designed by Advanced RISC Machines, Ltd. It offers 4K-byte I-cache/SRAM and 4K-byte D-cache/SRAM, is a low power, general purpose integrated circuits. Its simple, elegant, and fully static design is particularly suitable for cost sensitive and power sensitive applications.

One 100/10 Mbit MAC of Ethernet controller is built-in to reduce total system cost.

The NUC745 also provides one USB 1.1 host controller, one USB 1.1 device controller, one AC97/I<sup>2</sup>S controller, one 2-channel GDMA, four independent UARTs, one watchdog timer, two 24-bit timers with 8-bit pre-scale, up to 31 programmable I/O ports, PS2 keyboard controller and an advanced interrupt controller. The external bus interface (EBI) controller provides for SDRAM, ROM/SRAM, flash memory and I/O devices. The system manager includes an internal 32-bit system bus arbiter and a PLL clock controller.

With a wide range of serial communication and Ethernet interfaces, the NUC745 is suitable for communication gateways as well as many other general purpose applications.

- 1 -

### nuvoTon

### 2. FEATURES

#### Architecture

- Fully 16/32-bit RISC architecture

- Little/Big-Endian mode supported

- Efficient and powerful ARM7TDMI core

- Cost-effective JTAG-based debug solution

#### **External Bus Interface**

- 8/16-bit external bus support for ROM/SRAM, flash memory, SDRAM and external I/Os

- Support for SDRAM

- Programmable access cycle (0-7 wait cycle)

- Four-word depth write buffer for SDRAM write data

- Cost-effective memory-to-peripheral DMA interface

#### Instruction and Data Cache

- Two-way, set-associative, 4K-byte I-cache and 4K-byte D-cache

- Support for LRU (Least Recently Used) protocol

- Cache can be configured as internal SRAM

- Support cache lock function

### **Ethernet MAC Controller**

- DMA engine with burst mode

- MAC Tx/Rx buffers (256 bytes Tx, 256 bytes Rx)

- Data alignment logic

- Endian translation

- 100/10 Mbit per second operation

- Full compliance with IEEE standard 802.3

- RMII interface only

- Station Management Signaling

- On-chip CAM (up to 16 destination addresses)

- Full-duplex mode with PAUSE feature

- Long/short packet modes

- PAD generation

- 2 -

# nuvoTon

#### **DMA Controller**

- 2-channel general DMA for memory-to-memory data transfers without CPU intervention

- Initialed by a software or external DMA request

- Increments or decrements a source or destination address in 8-bit, 16-bit or 32-bit data transfers

- 4-data burst mode

### UART

- Four UART (serial I/O) blocks with interrupt-based operation

- Support for 5-bit, 6-bit, 7-bit or 8-bit serial data transmit and receive

- Programmable baud rates

- 1, 1/2 or 2 stop bits

- Odd or even parity

- Break generation and detection

- Parity, overrun and framing error detection

- X16 clock mode

- UART1 supports Bluetooth, and UART2 supports IrDA1.0 SIR

### Timers

- Two programmable 24-bit timers with 8-bit pre-scaler

- One programmable 20 bit with selectable additional 8-bit prescaler watchdog timer

- One-shot mode, periodical mode or toggle mode operation

### Programmable I/Os

- 31 programmable I/O ports

- Pins individually configurable to input, output or I/O mode for dedicated signals

- I/O ports are configurable for multiple functions

### **Advanced Interrupt Controller**

- 24 interrupt sources, including 4 external interrupt sources

- Programmable normal or fast interrupt mode (IRQ, FIQ)

- Programmable as either edge-triggered or level-sensitive for 4 external interrupt sources

- Programmable as either low-active or high-active for 4 external interrupt sources

- Priority methodology is encoded to allow for interrupt daisy-chaining

- Automatically mask out the lower priority interrupt during interrupt nesting

- 3 -

## nuvoTon

#### **USB Host Controller**

- USB 1.1 compliant

- Compatible with Open HCI 1.0 specification

- Supports low-speed and full speed devices

- Build-in DMA for real time data transfer

- · Two on-chip USB transceivers with one optionally shared with USB device controller

#### **USB Device Controller**

- USB 1.1 compliant

- Support four USB endpoints including one control endpoint and 3 configurable endpoints for rich

USB functions

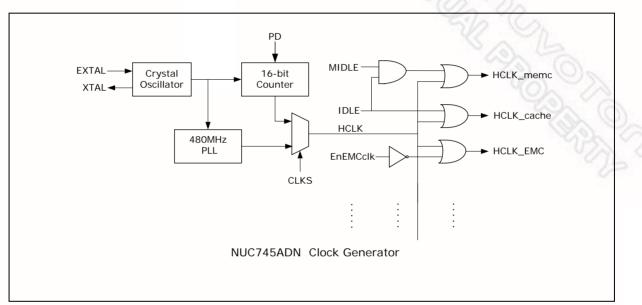

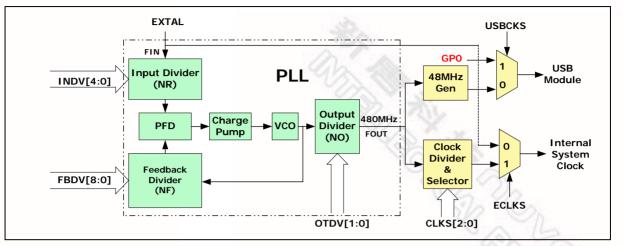

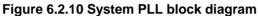

#### **Two PLLs**

- The external clock can be multiplied by on-chip PLL to provide high frequency system clock

- The input frequency range is 3-30MHz; 15MHz is preferred.

- One PLL for both CPU and USB host/device controller

- One PLL for audio I<sup>2</sup>S 12.288/16.934MHz clock source

- Programmable clock frequency

#### 4-Channel PWM

- Four 16-bit timers with PWM

- Two 8-bit pre-scalers & Two 4-bit dividers

- Programmable duty control of output waveform (PWM)

- Auto reload mode or one-shot pulse mode

- Dead-zone generator

### I<sup>2</sup>C Master

- 2-channel I<sup>2</sup>C

- Compatible with Philips I<sup>2</sup>C standard, support master mode only

- Support multi master operation

- Clock stretching and wait state generation

- Provide multi-byte transmit operation, up to 4 bytes can be transmitted in a single transfer

- Software programmable acknowledge bit

- Arbitration lost interrupt, with automatic transfer cancellation

- Start/Stop/Repeated Start/Acknowledge generation

- Start/Stop/Repeated Start detection

- Bus busy detection

- 4 -

# nuvoTon

- Supports 7 bit addressing mode

- Software mode I<sup>2</sup>C

### **Universal Serial Interface (USI)**

- 1-channel USI

- Support USI (Microwire/SPI) master mode

- Full duplex synchronous serial data transfer

- Variable length of transfer word up to 32 bits

- Provide burst mode operation, transmit/receive can be executed up to four times in one transfer

- MSB or LSB first data transfer

- Rx and Tx on both rising or falling edge of serial clock independently

- Two slave/device select lines

- Fully static synchronous design with one clock domain

### 2-Channel AC97/I<sup>2</sup>S Audio Codec Host Interface

- AHB master port and an AHB slave port are offered in audio controller.

- Always 8-beat incrementing burst

- Always bus lock when 8-beat incrementing burst

- When reach middle and end address of destination address, a DMA\_IRQ is requested to CPU automatically

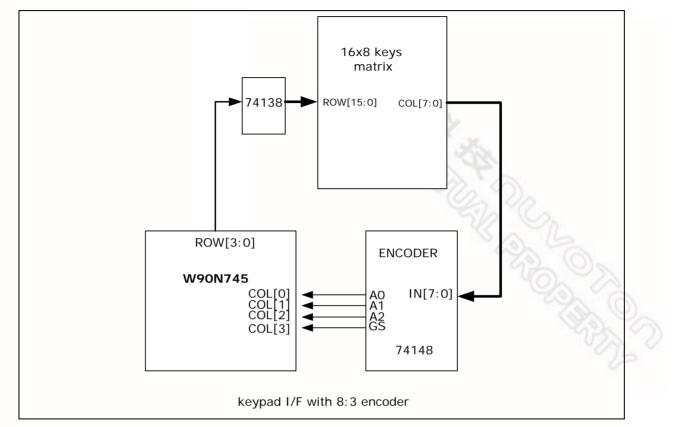

### **KeyPad Scan Interface**

- Scan up to 16 rows by 8 columns with an external 4 to 16 decoder and 4x8 array without auxiliary component

- Programmable debounce time

- One or two keys scan with interrupt and three keys reset function.

- Wakeup CPU from IDEL/Power Down mode

### **PS2 Host Interface**

- APB slave consisted of PS2 protocol.

- Connect IBM keyboard or bar-code reader through PS2 interface.

- Provide hardware scan code to ASCII translation

- 5 -

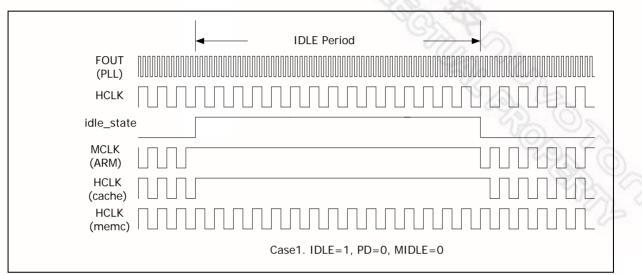

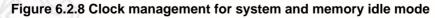

#### **Power management**

- Programmable clock enables for individual peripheral

- IDLE mode to halt ARM core and keep peripheral working

- Power-Down mode to stop all clocks included external crystal oscillator.

- Exit IDLE by all interrupts

- Exit Power-Down by keypad, USB device and external interrupts

#### **Operation Voltage Range**

- 3.0 ~ 3.6 V for IO buffer

- 1.62 ~ 1.98 V for core logic

#### **Operation Temperature Range**

• TBD

### **Operating Frequency**

• Up to 80 MHz

#### Package Type

• 128-pin LQFP

- 6 -

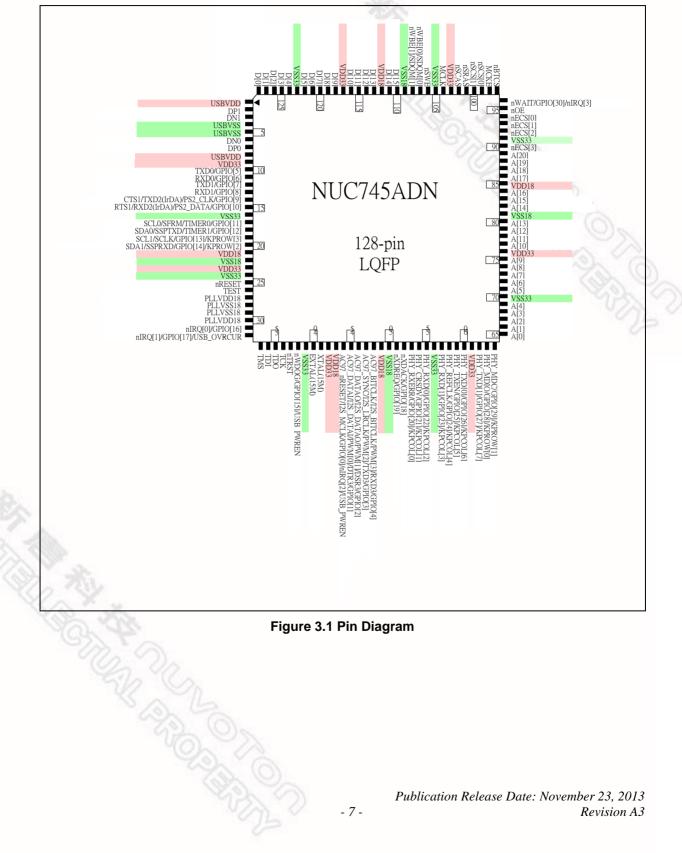

### 3. PIN DIAGRAM

### 4. PIN ASSIGNMENT

Table 4.1 NUC745 Pins Assignment

| PIN NAME                           | 128-PIN LQFP                    |

|------------------------------------|---------------------------------|

| Clock & Reset                      | ( 3 pins )                      |

| EXTAL (15M)                        | 40                              |

| XTAL (15M)                         | 41                              |

| nRESET                             | 25                              |

| JTAG Interface                     | ( 5 pins )                      |

| TMS                                | 33                              |

| TDI                                | 34                              |

| TDO                                | 35                              |

| ТСК                                | 36                              |

| nTRST                              | 37 37                           |

| External Bus Interface             | ( 53 pins )                     |

| A [20:0]                           | 89-86,84-82,80-77,75-71,69-65   |

| D [15:0]                           | 110-111,113-116,118-122,124-128 |

| nWBE [1;0] /<br>SDQM [1:0]         | 108,107                         |

| nSCS [1:0]                         | 100,99                          |

| nSRAS                              | 101                             |

| nSCAS                              | 102                             |

| MCKE                               | 98                              |

| nSWE                               | 106                             |

| MCLK                               | 104                             |

| nWAIT /<br>GPIO [30] /<br>nIRQ [3] | 96                              |

| nBTCS                              | 97                              |

| nECS [3:0]                         | 90,92-94                        |

| nOE                                | 95                              |

Table 4.1 NUC745 Pins Assignment, continued

| PIN NAME                        | 128-PIN LQFP |

|---------------------------------|--------------|

| Ethernet Interface              | ( 10 pins )  |

| PHY_MDC /                       |              |

| GPIO [29] /                     | 64           |

| KPROW [1]                       |              |

| PHY_MDIO /                      | X C X        |

| GPIO [28] /                     | 63           |

| KPROW [0]                       |              |

| PHY_TXD [1:0] /                 | Con On       |

| GPIO [27:26] /                  | 62,60        |

| KPCOL [7:6]                     |              |

| PHY_TXEN /                      | 20.0         |

| GPIO [25] /                     | 59           |

| KPCOL [5]                       |              |

| PHY_REFCLK /                    | - 7.0        |

| GPIO [24] /                     | 58           |

| KPCOL [4]                       |              |

| PHY_RXD [1:0] /                 |              |

| GPIO [23:22] /                  | 57,55        |

| KPCOL [3:2]                     |              |

| PHY_CRSDV /                     |              |

| GPIO [21] /                     | 54           |

| KPCOL [1]                       |              |

| PHY_RXERR /                     |              |

| GPIO [20] /                     | 53           |

| KPCOL [0]                       |              |

| AC97/I <sup>2</sup> S/PWM/UART3 | ( 5 pins )   |

| AC97_nRESET /                   |              |

| I2S_MCLK /                      |              |

| GPIO [0] /                      | 44           |

| nIRQ [2] /                      |              |

| USB_PWREN                       |              |

- 9 -

Table 4.1 NUC745 Pins Assignment, continued

|                                 | 128-PIN LQFP |

|---------------------------------|--------------|

| AC97/I <sup>2</sup> S/PWM/UART3 | ( 5 pins )   |

| AC97_DATAI /                    |              |

| I2S_DATAI /                     |              |

| PWM [0] /                       | 45           |

| DTR3/                           | No P St.     |

| GPIO [1]                        | 1962 607     |

| AC97_DATAO /                    | G22 Tra      |

| I <sup>2</sup> S_DATAO /        |              |

| PWM [1] /                       | 46           |

| DSR3/                           |              |

| GPIO [2]                        |              |

| AC97_SYNC /                     | S22 (0)      |

| I <sup>2</sup> S_LRCLK /        | (O) /        |

| PWM [2] /                       | 47           |

| TXD3/                           |              |

| GPIO [3]                        | 15           |

| AC97_BITCLK /                   |              |

| I <sup>2</sup> S_BITCLK /       |              |

| PWM [3] /                       | 48           |

| RXD3                            |              |

| GPIO [4]                        |              |

| USB Interface                   | ( 4 pins )   |

| DP0                             | 7            |

| DN 0                            | 6            |

| DP1                             | 2            |

| DN1                             | 3            |

| Miscellaneous                   | ( 7 pins )   |

| nIRQ [1] /                      |              |

| GPIO [17] /                     | 32           |

| USB_OVRCUR                      |              |

| nIRQ [0] /                      | 31           |

| GPIO [16]                       | 51           |

| nWDOG /                         |              |

| GPIO [15] /                     | 38           |

|                                 |              |

| USB_PWREN<br>TEST               | 26           |

Table 4.1 NUC745 Pins Assignment, continued

| PIN NAME                     | 128-PIN LQFP |

|------------------------------|--------------|

| I <sup>2</sup> C/USI(SPI/MW) | ( 4 pins )   |

| SCL0 /                       |              |

| SFRM /                       | 17           |

| TIMER0 /                     |              |

| GPIO [11]                    |              |

| SDA0 /                       |              |

| SSPTXD /                     | 18           |

| TIMER1 /                     |              |

| GPIO [12]                    |              |

| SCL1 /                       |              |

| SCLK /                       | 19           |

| GPIO [13] /                  |              |

| KPROW [3]                    |              |

| SDA1 /                       |              |

| SSPRXD /                     | 20           |

| GPIO [14] /                  |              |

| KPROW [2]                    |              |

| UART0/UART1/UART2/PS2        | ( 6 pins )   |

|                              | 10           |

| GPIO [5]                     |              |

| RXD0 /                       | 11           |

| GPIO [6]                     |              |

| TXD1 /                       | 12           |

| GPIO [7]                     |              |

| RXD1 /                       | 13           |

| GPIO [8]                     |              |

| CTS1 /                       |              |

| TXD2(IrDA) /<br>PS2_CLK /    | 14           |

|                              |              |

| GPIO [9]                     |              |

| RTS1/                        |              |

| RXD2(IrDA) /                 | 15           |

| PS2_DATA /<br>GPIO [10]      |              |

Table 4.1 NUC745 Pins Assignment, continued

| PIN NAME     | 128-PIN LQFP              |  |

|--------------|---------------------------|--|

| XDMA         | ( 2 pins )                |  |

| nXDREQ /     | 51                        |  |

| GPIO [19] /  | 51                        |  |

| nXDACK /     | 52                        |  |

| GPIO [18] /  | 32                        |  |

| Power/Ground | ( 36 pins )               |  |

| VDD18        | 21,43,49,85,112           |  |

| VSS18        | 22,50,81,109              |  |

| VDD33        | 9,23,42,61,76,103,117     |  |

| VSS33        | 16,24,39,56,70,91,105,123 |  |

| USBVDD       | 1,8                       |  |

| USBVSS       | 4,5                       |  |

| PLLVDD18     | 27,30                     |  |

| PLLVSS18     | 28,29                     |  |

- 12 -

### 5. PIN DESCRIPTION

| Table 5.1 | NUC745 Pins | Description |

|-----------|-------------|-------------|

|-----------|-------------|-------------|

| 15MHz External Clock / Crystal Input         15MHz Crystal Output         System Reset, active-low         JTAG Test Mode Select, internal pull-up with 70K ohm         JTAG Test Data in, internal pull-up with 70K ohm         JTAG Test Data out         JTAG Test Clock, internal pull-down with 58K ohm |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15MHz Crystal Output         System Reset, active-low         JTAG Test Mode Select, internal pull-up with 70K ohm         JTAG Test Data in, internal pull-up with 70K ohm         JTAG Test Data out                                                                                                       |

| System Reset, active-low         JTAG Test Mode Select, internal pull-up with 70K ohm         JTAG Test Data in, internal pull-up with 70K ohm         JTAG Test Data out                                                                                                                                    |

| JTAG Test Mode Select, internal pull-up with 70K ohm<br>JTAG Test Data in, internal pull-up with 70K ohm<br>JTAG Test Data out                                                                                                                                                                               |

| JTAG Test Data in, internal pull-up with 70K ohm<br>JTAG Test Data out                                                                                                                                                                                                                                       |

| JTAG Test Data in, internal pull-up with 70K ohm<br>JTAG Test Data out                                                                                                                                                                                                                                       |

| JTAG Test Data out                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                              |

| JTAG Test Clock, internal pull-down with 58K ohm                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                              |

| JTAG Reset, active-low, internal pull-up with 70K ohm                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                              |

| Address Bus (MSB) of external memory and IO devices.                                                                                                                                                                                                                                                         |

| Address Bus of external memory and IO devices.                                                                                                                                                                                                                                                               |

| Data Bus (LSB) of external memory and IO device. The internal pull-up resistors are turned on when D[15:0] is in input mode.                                                                                                                                                                                 |

| Write Byte Enable for specific device (nECS [1:0]).                                                                                                                                                                                                                                                          |

| Data Bus Mask signal for SDRAM (nSCS [1:0]), active-low.                                                                                                                                                                                                                                                     |

| SDRAM chip select for two external banks, active-low.                                                                                                                                                                                                                                                        |

| Row Address Strobe for SDRAM, active-low.                                                                                                                                                                                                                                                                    |

| Column Address Strobe for SDRAM, active-low.                                                                                                                                                                                                                                                                 |

| SDRAM Clock Enable, active-high                                                                                                                                                                                                                                                                              |

| SDRAM Write Enable, active-low                                                                                                                                                                                                                                                                               |

| System Master Clock Out, SDRAM clock, output with slew-rate control                                                                                                                                                                                                                                          |

| External Wait, active-low. This pin indicates that the external devices need more active cycle during access operation.<br>General Programmable In/Out Port GPIO[30]. If memory and IO devices in EBI                                                                                                        |

| do not need wait request, it can be configured as GPIO[30] or nIRQ3.                                                                                                                                                                                                                                         |

| ROM/Flash Chip Select, active-low.                                                                                                                                                                                                                                                                           |

| External I/O Chip Select, active-low.                                                                                                                                                                                                                                                                        |

| ROM/Flash, External Memory Output Enable, active-low.                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                              |

Table 5.1 NUC745 Pins Description, continued

| PIN NAME                                         | IO TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ethernet Interfac                                | е       |                                                                                                                                                                                                                                                                                                                                                                      |

| PHY_MDC /<br>GPIO [29] /<br>KPROW [1]            | IOU     | RMII Management Data Clock for Ethernet. It is the reference clock of MDIO<br>Each MDIO data will be latched at the rising edge of MDC clock.<br>General Programmable In/Out Port [29]<br>Keypad ROW[1] scan output.                                                                                                                                                 |

| PHY_MDIO /<br>GPIO [28] /<br>KPROW [0]           | Ю       | RMII Management Data I/O for Ethernet. It is used to transfer RMII contro<br>and status information between PHY and MAC.<br>General Programmable In/Out Port [28]<br>Keypad ROW[0] scan output.                                                                                                                                                                      |

| PHY_TXD [1:0] /<br>GPIO [27:26] /<br>KPCOL [7:6] | IOU     | 2-bit Transmit Data bus for Ethernet.<br>General programmable In/Out Port [27:26]<br>Keypad column input [7:6], active low                                                                                                                                                                                                                                           |

| PHY_TXEN /<br>GPIO [25] /<br>KPCOL [5]           | IOU     | PHY_TXEN shall be asserted synchronously with the first 2-bit of the preamble and shall remain asserted while all di-bits to be transmitted are presented. Of course, it is synchronized with PHY_REFCLK. General Programmable In/Out Port [25] Keypad column input [5], active low                                                                                  |

| PHY_REFCLK /<br>GPIO [24] /<br>KPCOL [4]         | IOS     | Reference Clock. The clock shall be 50MHz +/- 50 ppm with minimum 35% duty cycle at high or low state.<br>General Programmable In/Out port [24]<br>Keypad column input [4], active low                                                                                                                                                                               |

| PHY_RXD [1:0] /<br>GPIO [23:22] /<br>KPCOL [3:2] | IOS     | 2-bit Receive Data bus for Ethernet.<br>General Programmable In/Out Port [23:22]<br>Keypad column input [3:2], active low                                                                                                                                                                                                                                            |

| PHY_CRSDV /<br>GPIO [21] /<br>KPCOL [1]          | IOS     | Carrier Sense / Receive Data Valid for Ethernet. The PHY_CRSDV shall be<br>asserted by PHY when the receive medium is non-idle. Loss of carrier sha<br>result in the de-assertion of PHY_CRSDV synchronous to the cycle of<br>PHY_REFCLK, and only on 2-bit receive data boundaries.<br>General Programmable In/Out port [21]<br>Keypad column input [1], active low |

| PHY_RXERR /<br>GPIO [20] /                       | IOS     | Receive Data Error for Ethernet. It indicates a data error detected by PHY.The assertion should be lasted for longer than a period of PHY_REFCLK. When PHY_RXERR is asserted, the MAC will report a CRC error. General programmable In/Out port [20] Keypad column input [0], active low                                                                             |

Table 5.1 NUC745 Pins Description, continued

| PIN NAME                  | IO TYPE | DESCRIPTION                                                            |  |  |

|---------------------------|---------|------------------------------------------------------------------------|--|--|

| AC97/I2S/PWM/UA           | RT3     |                                                                        |  |  |

| AC97_nRESET /             |         | AC97 CODEC Host Interface RESET Output.                                |  |  |

| I <sup>2</sup> S_MCLK /   |         | I <sup>2</sup> S CODEC Host Interface System Clock Output.             |  |  |

| GPIO [0] /                | IOU     | General Purpose In/Out port [0]                                        |  |  |

| nIRQ [2] /                |         | External interrupt request.                                            |  |  |

| USB_PWREN                 |         | USB host power enable output                                           |  |  |

| AC97_DATAI /              |         | AC97 CODEC Host Interface Data Input.                                  |  |  |

| I <sup>2</sup> S_DATAI /  |         | I <sup>2</sup> S CODEC Host Interface Data Input.                      |  |  |

| PWM [0] /                 | IOU     | PWM Channel 0 output.                                                  |  |  |

| DTR3/                     |         | Data Terminal Ready for UART3.                                         |  |  |

| GPIO [1]                  |         | General Purpose In /Out port [1]                                       |  |  |

| AC97_DATAO /              |         | AC97 CODEC Host Interface Data Output.                                 |  |  |

| I <sup>2</sup> S_DATAO /  |         | I <sup>2</sup> S CODEC Host Interface Data Output.                     |  |  |

| PWM [1] /                 | IOU     | PWM Channel 1 output.                                                  |  |  |

| DSR3/                     |         | Data Set Ready for UART3.                                              |  |  |

| GPIO [2]                  |         | General Purpose In/Out port [2]                                        |  |  |

| AC97_SYNC /               |         | AC97 CODEC Host Interface Synchronous Pulse Output.                    |  |  |

| I <sup>2</sup> S_LRCLK /  |         | I <sup>2</sup> S CODEC Host Interface Left/Right Channel Select Clock. |  |  |

| PWM [2] /                 | IOU     | PWM Channel 2 output.                                                  |  |  |

| TXD3/                     |         | Transmit Data for UART3.                                               |  |  |

| GPIO [3]                  |         | General Purpose In/Out port [3]                                        |  |  |

| AC97_BITCLK /             |         | AC97 CODEC Host Interface Bit Clock Input.                             |  |  |

| I <sup>2</sup> S_BITCLK / |         | I <sup>2</sup> S CODEC Host Interface Bit Clock.                       |  |  |

| PWM [3] /                 | IOS     | PWM Channel 3 output.                                                  |  |  |

| RXD3 /                    |         | Receive Data for UART3.                                                |  |  |

| GPIO [4]                  |         | General Purpose In/Out port [4].                                       |  |  |

| USB Interface             |         |                                                                        |  |  |

| DP0                       | IO      | Differential Positive USB IO signal                                    |  |  |

| DN0                       | IO      | Differential Negative USB IO signal                                    |  |  |

| DP1                       | IO      | Differential Positive USB IO signal                                    |  |  |

| DN1                       | IO      | Differential Negative USB IO signal                                    |  |  |

| Miscellaneous             |         |                                                                        |  |  |

| nIRQ [1:0] /              |         | External Interrupt Request                                             |  |  |

| GPIO [17:16] /            | IOU     | General Purpose I/O                                                    |  |  |

| USB_OVRCUR                | 100     |                                                                        |  |  |

| Carl Mar                  |         | nIRQ1 is used as USB host over-current detection input                 |  |  |

| nWDOG /                   |         | Watchdog Timer Timeout Flag and Keypad 3-keys reset output, active low |  |  |

| GPIO [15] /               | IOU     | General Purpose In/output                                              |  |  |

| USB_PWREN<br>TEST         |         | USB host power switch enable output                                    |  |  |

|                           | IDS     | This test pin must be short to ground or left unconnected              |  |  |

St. All

|                         | IO TYPE | DESCRIPTION                                                  |

|-------------------------|---------|--------------------------------------------------------------|

| I <sup>2</sup> C/USI    |         |                                                              |

| SCL0 /                  |         | I <sup>2</sup> C Serial Clock Line 0.                        |

| SFRM /                  |         | USI Serial Frame.                                            |

| TIMER0 /                | IOU     | Timer0 time out output.                                      |

| GPIO [11]               |         | General Purpose In/Out port [11].                            |

| SDA0 /                  |         | I <sup>2</sup> C Serial Data Line 0                          |

| SSPTXD /                |         | USI Serial Transmit Data                                     |

| TIMER1 /                | IOU     | Timer1 time out output                                       |

| GPIO [12]               |         | General Purpose In/Out port [12]                             |

| SCL1 /                  |         | I <sup>2</sup> C Serial Clock Line 1                         |

| SCLK /                  |         | USI Serial Clock                                             |

| GPIO [13] /             | IOU     | General Purpose In/Out port [13]                             |

| KPROW [3]               |         | Keypad row scan output [3]                                   |

| SDA1 /                  |         | $I^2$ C Serial Data Line 1                                   |

| SSPRXD /                |         | USI Serial Receive Data                                      |

| GPIO [14] /             | IDU     |                                                              |

|                         |         | General Purpose In/Out port [14]                             |

| KPROW [2]               | DTO     | Keypad scan output [2]                                       |

| UARTO/UART1/UA          | R12     | LIADTO Transmit Data                                         |

| TXD0 /                  | IOU     | UART0 Transmit Data.                                         |

| GPIO [5]                |         | General Purpose In/Out [5]                                   |

| RXD0 /                  | IOU     | UART0 Receive Data.                                          |

| GPIO [6]                |         | General Purpose In/Out [6]                                   |

| TXD1 /                  | IOU     | UART1 Transmit Data.                                         |

| GPIO [7]                |         | General Purpose In/Out [7]                                   |

| RXD1 /                  | IOU     | UART1 Receive Data.                                          |

| GPIO [8]                |         | General Purpose In/Out [8]                                   |

| CTS1/                   |         | UART1 Clear To Send for Bluetooth application                |

| TXD2(IrDA) /            | IOU     | UART2 Transmit Data supporting SIR IrDA.                     |

| PS2_CLK /               |         | PS2 Interface Clock Input/Output                             |

| GPIO [9]                |         | General Purpose In/Out [9]                                   |

| RTS1/                   |         | UART1 Request To Send for Bluetooth application              |

| RXD2(IrDA) /            | IOU     | UART2 Receive Data supporting SIR IrDA.                      |

| PS2_DATA /              |         | PS2 Interface Bi-Directional Data Line.                      |

| GPIO [10]               |         | General Purpose In/Out [10]                                  |

|                         |         |                                                              |

| nXDREQ /                | IO      | External DMA Request.                                        |

| GPIO [19] /<br>nXDACK / |         | General Purpose In/Out [19]<br>External DMA Acknowledgement. |

| INDAGK /                | IO      | General Purpose In/Out [18]                                  |

Table 5.1 NUC745 Pins Description, continued

Table 5.1 NUC745 Pins Description, continued

| PIN NAME     | ΙΟ ΤΥΡΕ | DESCRIPTION              |

|--------------|---------|--------------------------|

| Power/Ground |         |                          |

| VDD18        | Р       | Core Logic power (1.8V)  |

| VSS18        | G       | Core Logic ground (0V)   |

| VDD33        | Р       | IO Buffer power (3.3V)   |

| VSS33        | G       | IO Buffer ground (0V)    |

| USBVDD       | Р       | USB power (3.3V)         |

| USBVSS       | G       | USB ground (0V)          |

| DVDD18       | Р       | PLL Digital power (1.8V) |

| DVSS18       | G       | PLL Digital ground (0V)  |

| AVDD18       | Р       | PLL Analog power (1.8V)  |

| AVSS18       | G       | PLL Analog ground (0V)   |

- 17 -

| PIN NO.                        | DEFAULT  | FUNCTION0    | FUNCTION1             | FUNCTION2 | FUNCTION:  |  |  |  |  |  |  |  |

|--------------------------------|----------|--------------|-----------------------|-----------|------------|--|--|--|--|--|--|--|

|                                |          | USB1.1 Host/ | Device Interface      |           |            |  |  |  |  |  |  |  |

| 1                              | USBVDD   | USBVDD       |                       |           | -          |  |  |  |  |  |  |  |

| 2                              | DP1      | DP1          |                       | 15        | -          |  |  |  |  |  |  |  |

| 3                              | DN1      | DN1          | - X.                  | XJ        | -          |  |  |  |  |  |  |  |

| 4                              | USBVSS   | USBVSS       | - 3                   | 0.00      | -          |  |  |  |  |  |  |  |

| 5                              | USBVSS   | USBVSS       | -                     | 00:00     | -          |  |  |  |  |  |  |  |

| 6                              | DN0      | DN0          | -                     | 4 Con 19  | 2 -        |  |  |  |  |  |  |  |

| 7                              | DP0      | DP0          | -                     |           | -n-        |  |  |  |  |  |  |  |

| 8                              | USBVDD   | USBVDD       | -                     | - 49      | 6 6        |  |  |  |  |  |  |  |

| 9                              | VDD33    | VDD33        | -                     | - 1       | 6.2        |  |  |  |  |  |  |  |

| UART[2:0]/PS2 Interface        |          |              |                       |           |            |  |  |  |  |  |  |  |

| 10                             | GPIO[5]  | GPIO[5]      | UART_TXD0             | -         | (Q))       |  |  |  |  |  |  |  |

| 11                             | GPIO[6]  | GPIO[6]      | UART_RXD0             | -         | 102        |  |  |  |  |  |  |  |

| 12                             | GPIO[7]  | GPIO[7]      | UART_TXD1             | -         | -          |  |  |  |  |  |  |  |

| 13                             | GPIO[8]  | GPIO[8]      | UART_RXD1             | -         | -          |  |  |  |  |  |  |  |

| 14                             | GPIO[9]  | GPIO[9]      | UART_TXD2             | UART_CTS1 | PS2_CLK    |  |  |  |  |  |  |  |

| 15                             | GPIO[10] | GPIO[10]     | UART_RXD2             | UART_RTS1 | PS2_DATA   |  |  |  |  |  |  |  |

| 16                             | VSS33    | VSS33        | -                     | -         | -          |  |  |  |  |  |  |  |

| I <sup>2</sup> C/USI Interface |          |              |                       |           |            |  |  |  |  |  |  |  |

| 17                             | GPIO[11] | GPIO[11]     | I <sup>2</sup> C_SCL0 | SSP_FRAM  | TIMER0     |  |  |  |  |  |  |  |

| 18                             | GPI0[12] | GPIO[12]     | I <sup>2</sup> C_SDA0 | SSP_TXD   | TIMER1     |  |  |  |  |  |  |  |

| 19                             | GPIO[13] | GPIO[13]     | I <sup>2</sup> C_SCL1 | SSP_SCLK  | KPI_ROW[3] |  |  |  |  |  |  |  |

| 20                             | GPIO[14] | GPIO[14]     | I <sup>2</sup> C_SDA1 | SSP_RXD   | KPI_ROW[2  |  |  |  |  |  |  |  |

| 21                             | VDD18    | VDD18        | -                     | -         | -          |  |  |  |  |  |  |  |

| 22                             | VSS18    | VSS18        | -                     | -         | -          |  |  |  |  |  |  |  |

| 23                             | VDD33    | VDD33        | -                     | -         | -          |  |  |  |  |  |  |  |

| 24                             | VSS33    | VSS33        | -                     | -         | -          |  |  |  |  |  |  |  |

|                                |          | System R     | eset & TEST           |           |            |  |  |  |  |  |  |  |

| 25                             | nRESET   | nRESET       | -                     | -         | -          |  |  |  |  |  |  |  |

| 26                             | TEST     | TEST         | -                     | -         | -          |  |  |  |  |  |  |  |

### Table 5.2 NUC745 128-pin LQFP Multi-function List

Table 5.2 NUC745 128-pin LQFP Multi-function List, continued

| PIN NO.    | DEFAULT            | FUNCTION0                | FUNCTION1                                   | FUNCTION2  | FUNCTION3 |  |

|------------|--------------------|--------------------------|---------------------------------------------|------------|-----------|--|

|            |                    | AC97/I <sup>2</sup> S/PW | M/UART3 Interface                           |            | •         |  |

| 44         | GPIO[0]            | GPIO[0]                  | AC97_nRESET<br>or<br>I <sup>2</sup> SMCLK   | nIRQ [2]   | USB_PWREN |  |

| 45         | GPIO[1]            | GPIO[1]                  | AC97_DATAI<br>or<br>I <sup>2</sup> SDATAI   | PWM0       | UART_DTR3 |  |

| 46         | 46 GPIO[2] GPIO[2] |                          | AC97_DATAO<br>or<br>I <sup>2</sup> SDATAO   | PWM1       | UART_DSR3 |  |

| 47 GPIO[3] |                    | GPIO[3]                  | AC97_SYNC<br>or<br>I <sup>2</sup> SLRCLK    | PWM2       | UART_TXD3 |  |

| 48         | GPIO[4]            | GPIO[4]                  | AC97_BITCLK<br>or<br>I <sup>2</sup> SBITCLK | PWM3       | UART_RXD3 |  |

| 49         | VDD18              | VDD18                    | -                                           | -          | -         |  |

| 50         | VSS18              | VSS18                    | -                                           | -          | -         |  |

|            |                    | XD                       | MAREQ                                       | T          | Т         |  |

| 51         | GPIO[19]           | GPIO[19]                 | nXDREQ                                      | -          | -         |  |

| 52         | GPIO[18]           | GPIO[18]                 | nXDACK                                      | -          | -         |  |

| Г          |                    |                          | II/KeyPad Interface                         | 1          | 1         |  |

| 53         | GPIO[20]           | GPIO[20]                 | PHY_RXERR                                   | KPI_COL[0] | -         |  |

| 54         | GPIO[21]           | GPIO[21]                 | PHY_CRSDV                                   | KPI_COL[1] | -         |  |

| 55         | GPIO[22]           | GPIO[22]                 | PHY_RXD[0]                                  | KPI_COL[2] | -         |  |

| 56         | VSS33              | VSS33                    | -                                           | -          | -         |  |

| 57         | GPIO[23]           | GPIO[23]                 | PHY_RXD[1]                                  | KPI_COL[3] | -         |  |

| 58         | GPIO[24]           | GPIO[24]                 | PHY_REFCLK                                  | KPI_COL[4] | -         |  |

| 59         | GPIO[25]           | GPIO[25]                 | PHY_TXEN                                    | KPI_COL[5] | -         |  |

| 60         | GPIO[26]           | GPIO[26]                 | PHY_TXD[0]                                  | KPI_COL[6] | -         |  |

| 61         | VDD33              | VDD33                    | -                                           | -          | -         |  |

| 62         | GPIO[27]           | GPIO[27]                 | PHY_TXD[1]                                  | KPI_COL[7] | -         |  |

| 63         | GPIO[28]           | GPIO[28]                 | PHY_MDIO                                    | KPI_ROW[0] |           |  |

| 64         | GPIO[29]           | GPIO[29]                 | PHY_MDC                                     | KPI_ROW[1] |           |  |

Table 5.2 NUC745 128-pin LQFP Multi-function List, continued

Publication Release Date: November 23, 2013 Revision A3

- 20 -

| PIN<br>NO. | DEFAULT | FUNCTION0  | FUNCTION1          | FUNCTION2                              | FUNCTION |  |

|------------|---------|------------|--------------------|----------------------------------------|----------|--|

|            |         | Memory Add | lress/Data/Control |                                        | •        |  |

| 65         | A[0]    | A[0]       | C.S.Y              | 100                                    | -        |  |

| 66         | A[1]    | A[1]       | <u> </u>           | X                                      | -        |  |

| 67         | A[2]    | A[2]       | - 33               | S SR                                   | -        |  |

| 68         | A[3]    | A[3]       | -                  | 5 TA                                   | -        |  |

| 69         | A[4]    | A[4]       | -                  | "On "V                                 | 2        |  |

| 70         | VSS33   | VSS33      | -                  | 20                                     | on-      |  |

| 71         | A[5]    | A[5]       | -                  | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | A CA     |  |

| 72         | A[6]    | A[6]       | -                  | - ~                                    | 600      |  |

| 73         | A[7]    | A[7]       | -                  | -                                      | YON Y    |  |

| 74         | A[8]    | A[8]       | -                  | -                                      | (Y)      |  |

| 75         | A[9]    | A[9]       | -                  | -                                      | - 02     |  |

| 76         | VDD33   | VDD33      | -                  | -                                      | -        |  |

| 77         | A[10]   | A[10]      | -                  | -                                      | -        |  |

| 78         | A[11]   | A[11]      | -                  | -                                      | -        |  |

| 79         | A[12]   | A[12]      | -                  | -                                      | -        |  |

| 80         | A[13]   | A[13]      | -                  | -                                      | -        |  |

| 81         | VSS18   | VSS18      | -                  | -                                      | -        |  |

| 82         | A[14]   | A[14]      | -                  | -                                      | -        |  |

| 83         | A[15]   | A[15]      | -                  | -                                      | -        |  |

| 84         | A[16]   | A[16]      | -                  | -                                      | -        |  |

| 85         | VDD18   | VDD18      | -                  | -                                      | -        |  |

| 86         | A[17]   | A[17]      | -                  | -                                      | -        |  |

| 87         | A[18]   | A[18]      | -                  | -                                      | -        |  |

| 88         | A[19]   | A[19]      | -                  | -                                      | -        |  |

| 89         | A[20]   | A[20]      | -                  | -                                      | -        |  |

| 90         | nECS[3] | nECS[3]    | -                  | -                                      | -        |  |

| 91         | VSS33   | VSS33      | -                  | -                                      | -        |  |

Table 5.2 NUC745 128-pin LQFP Multi-function List, continued

- 21 -

| PIN<br>NO. | DEFAULT      | FUNCTION0       | FUNCTION1        | FUNCTION2 | FUNCTION3 |  |

|------------|--------------|-----------------|------------------|-----------|-----------|--|

|            |              | Memory Addre    | ess/Data/Control | •         |           |  |

| 92         | nECS[2]      | nECS[2]         | S S S            | - 26      | -         |  |

| 93         | nECS[1]      | nECS[1]         | ×97.             | IX.       | -         |  |

| 94         | nECS[0]      | nECS[0]         | - 20             | 5 23      | -         |  |

| 95         | nOE          | nOE             | -                | ST A      | -         |  |

| 96         | nWAIT        | GPIO[30]        | nWAIT            | nIRQ [3]  | D         |  |

| 97         | nBTCS        | nBTCS           | -                | 20        | 20 -      |  |

| 98         | MCKE         | MCKE            | -                | ~```      | 5         |  |

| 99         | nSCS[0]      | nSCS[0]         | -                | - 9       | 202       |  |

| 100        | nSCS[1]      | nSCS[1]         | -                | -         | 20.0      |  |

| 101        | nSRAS        | nSRAS           | -                | -         | 200       |  |

| 102        | nSCAS        | nSCAS           | -                | -         | -15       |  |

| 103        | VDD33        | VDD33           | -                | -         | - 18      |  |

| 104        | MCLK         | MCLK            | -                | -         | -         |  |

| 105        | VSS33        | VSS33           | -                | -         | -         |  |

| 106        | nSWE         | nSWE            | -                | -         | -         |  |

| 107        | nWBE/SDQM[0] | nWBE or SDQM[0] |                  |           |           |  |

| 108        | nWBE/SDQM[1] | nWBE or SDQM[1] |                  |           |           |  |

| 109        | VSS18        | VSS18           | -                | -         | -         |  |

| 110        | D[15]        | D[15]           | -                | -         | -         |  |

| 111        | D[14]        | D[14]           | -                | -         | -         |  |

| 112        | VDD18        | VDD18           | -                | -         | -         |  |

| 113        | D[13]        | D[13]           | -                | -         | -         |  |

| 114        | D[12]        | D[12]           | -                | -         | -         |  |

| 115        | D[11]        | D[11]           | -                | -         | -         |  |

| 116        | D[10]        | D[10]           | -                | -         | -         |  |

| 117        | VDD33        | VDD33           | -                | -         | -         |  |

| 118        | D[9]         | D[9]            | -                | -         | -         |  |

| 119        | D[8]         | D[8]            | -                | -         | -         |  |

| 120        | D[7]         | D[7]            | -                | -         | -         |  |

Table 5.2 NUC745 128-pin LQFP Multi-function List, continued

- 22 -

| PIN NO. | DEFAULT                     | FUNCTION0 | FUNCTION1 | FUNCTION2 | FUNCTION3 |  |  |  |  |  |  |  |  |

|---------|-----------------------------|-----------|-----------|-----------|-----------|--|--|--|--|--|--|--|--|

|         | Memory Address/Data/Control |           |           |           |           |  |  |  |  |  |  |  |  |

| 121     | D[6]                        | D[6]      | NY CO     |           | -         |  |  |  |  |  |  |  |  |

| 122     | D[5]                        | D[5]      | S.        | - 18 C    | -         |  |  |  |  |  |  |  |  |

| 123     | VSS33                       | VSS33     | - 10      | Xat       | -         |  |  |  |  |  |  |  |  |

| 124     | D[4]                        | D[4]      | - 19      | 2.00      | -         |  |  |  |  |  |  |  |  |

| 125     | D[3]                        | D[3]      | -         | 10:00     | -         |  |  |  |  |  |  |  |  |

| 126     | D[2]                        | D[2]      | -         | Sho (     | Co        |  |  |  |  |  |  |  |  |

| 127     | D[1]                        | D[1]      | -         | 500       | 15        |  |  |  |  |  |  |  |  |

| 128     | D[0]                        | D[0]      | -         | - ~2      | 0.00      |  |  |  |  |  |  |  |  |

Table 5.2 NUC745 128-pin LQFP Multi-function List, continued

### 6. FUNCTIONAL DESCRIPTION

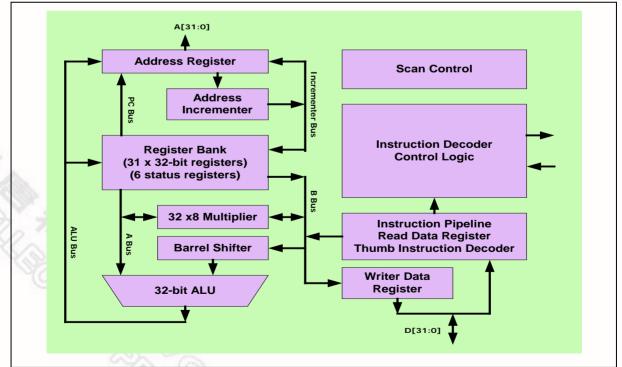

### 6.1 ARM7TDMI CPU CORE

The ARM7TDMI CPU core is a member of the Advanced RISC Machines (ARM) family of generalpurpose 32-bit microprocessors, which offer high performance for very low power consumption. The architecture is based on Reduced Instruction Set Computer (RISC) principles, and the instruction set and related decode mechanism are much simpler than those of micro-programmed Complex Instruction Set Computers. Pipelining is employed so that all parts of the processing and memory systems can operate continuously. The high instruction throughput and impressive real-time interrupt response are the major benefits.

The ARM7TDMI CPU core has two instruction sets:

- (1) The standard 32-bit ARM set

- (2) A 16-bit THUMB set

The THUMB set's 16-bit instruction length allows it to approach twice the density of standard ARM core while retaining most of the ARM's performance advantage over a traditional 16-bit processor using 16-bit registers. THUMB instructions operate with the standard ARM register configuration, allowing excellent interoperability between ARM and THUMB states. Each 16-bit THUMB instruction has a corresponding 32-bit ARM instruction with the same effect on the processor model.

ARM7TDMI CPU core has 31 x 32-bit registers. At any one time, 16 sets are visible; the other registers are used to speed up exception processing. All the register specified in ARM instructions can address any of the 16 registers. The CPU also supports 5 types of exception, such as two levels of interrupt, memory aborts, attempted execution of an undefined instruction and software interrupts.

Figure 6.1.1 ARM7TDMI CPU Core Block Diagram

### 6.2 System Manager

#### 6.2.1 Overview

The NUC745 system manager has the following functions.

- System memory map

- Data bus connection with external memory

- Product identifier register

- Bus arbitration

- PLL module

- Clock select and power saving control register

- Power-On setting

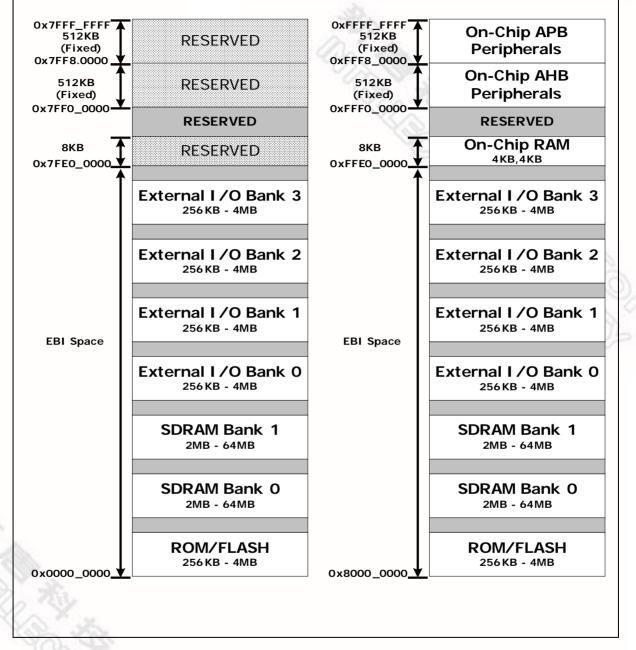

### 6.2.2 System Memory Map

NUC745 provides 2G bytes cacheable address space and the other 2G bytes are non-cacheable. The On-Chip Peripherals bank is on 1M bytes top of the space (0xFFF0\_0000 – 0xFFF\_FFF) and the On-Chip RAM bank's start address is 0xFFE0.0000, the other banks can be located anywhere (cacheable space:0x0000\_0000~0x7FDF\_FFF) if Cache ON; non-cacheable space: 0x8000\_0000~0xFFDF\_FFF).

The size and location of each bank is determined by the register settings for "current bank base address pointer" and "current bank size". Please note that when setting the bank control registers, the address boundaries of consecutive banks must not overlap.

Except On-Chip Peripherals and On-Chip RAM, the start address of each memory bank is not fixed. You can use bank control registers to assign a specific bank start address by setting the bank's base pointer (13 bits). The address resolution is 256K bytes. The bank's start address is defined as "base pointer << 18" and the bank's size is "current bank size".

In the event of an access requested to an address outside any programmed bank size, an abort signal is generated. The maximum accessible memory size of each external IO bank is 4M bytes (by word format), and 64M bytes on each SDRAM bank.

Figure 6.2.1 System Memory Map

Publication Release Date: November 23, 2013 Revision A3

- 26 -

| Table 6.2.1 On-Chip Peripherals Memory Map |                                                                       |  |  |  |  |  |  |  |

|--------------------------------------------|-----------------------------------------------------------------------|--|--|--|--|--|--|--|

| BASE ADDRESS                               | DESCRIPTION                                                           |  |  |  |  |  |  |  |

|                                            | AHB Peripherals                                                       |  |  |  |  |  |  |  |

| 0xFFF0_0000                                | Product Identifier Register (PDID)                                    |  |  |  |  |  |  |  |

| 0xFFF0_0004                                | Arbitration Control Register (ARBCON)                                 |  |  |  |  |  |  |  |

| 0xFFF0_0008                                | PLL Control Register 0(PLLCON0)                                       |  |  |  |  |  |  |  |

| 0xFFF0_000C                                | Clock Select Register (CLKSEL)                                        |  |  |  |  |  |  |  |

| 0xFFF0_0010                                | PLL Control Register 1 (PLLCON1)                                      |  |  |  |  |  |  |  |

| 0xFFF0_0014                                | Audio I <sup>2</sup> S Clock Control Register (I <sup>2</sup> SCKCON) |  |  |  |  |  |  |  |

| 0xFFF0_0020                                | IRQ Wakeup Control Register (IRQWAKEUPCON)                            |  |  |  |  |  |  |  |

| 0xFFF0_0024                                | IRQ Wakeup Flag Register (IRQWAKEFLAG)                                |  |  |  |  |  |  |  |

| 0xFFF0_0028                                | Power Manager Control Register (PMCON)                                |  |  |  |  |  |  |  |

| 0xFFF0_0030                                | USB Transceiver Control Register (USBTXRCON)                          |  |  |  |  |  |  |  |

| 0xFFF0_1000                                | EBI Control Register (EBICON) Control Registers                       |  |  |  |  |  |  |  |

| 0xFFF0_1004                                | ROM/FLASH (ROMCON) Control Registers                                  |  |  |  |  |  |  |  |

| 0xFFF0_1008                                | SDRAM bank 0 – 1 Control Registers                                    |  |  |  |  |  |  |  |

| 0xFFF0_1018                                | External I/O 0 – 3 Control Registers                                  |  |  |  |  |  |  |  |

| 0xFFF0_2000                                | Cache Controller Control Registers                                    |  |  |  |  |  |  |  |

| 0xFFF0_3000                                | Ethernet MAC Controller Control Registers                             |  |  |  |  |  |  |  |

| 0xFFF0_4000                                | GDMA 0 – 1 Control Registers                                          |  |  |  |  |  |  |  |

| 0xFFF0_5000                                | USB Host Controller Control Registers                                 |  |  |  |  |  |  |  |

| 0xFFF0_6000                                | USB Device Controller Control Registers                               |  |  |  |  |  |  |  |

| 0xFFF0_9000                                | AC97/I <sup>2</sup> S Controller Control Registers                    |  |  |  |  |  |  |  |

|                                            | APB Peripherals                                                       |  |  |  |  |  |  |  |

| 0xFFF8_0000                                | UART 0 (Tx, RX for console)                                           |  |  |  |  |  |  |  |

| 0xFFF8_0100                                | UART 1 (Tx, Rx, for bluetooth)                                        |  |  |  |  |  |  |  |

| 0xFFF8_0200                                | UART 2 (bluetooth CTS, RTS/ IrDA Tx, Rx)                              |  |  |  |  |  |  |  |

| 0xFFF8_0300                                | UART 3 (micro-print DTR, DTS, Tx, Rx)                                 |  |  |  |  |  |  |  |

| 0xFFF8_1000                                | Timer 0 – 1, WDOG Timer                                               |  |  |  |  |  |  |  |

| 0xFFF8_2000                                | Interrupt Controller                                                  |  |  |  |  |  |  |  |

| 0xFFF8_3000                                | GPIO                                                                  |  |  |  |  |  |  |  |

| 0xFFF8_6000                                | l <sup>2</sup> C-0 Control Registers                                  |  |  |  |  |  |  |  |

| 0xFFF8_6100                                | I <sup>2</sup> C-1 Control Registers                                  |  |  |  |  |  |  |  |

| 0xFFF8_6200                                | USI Control Registers                                                 |  |  |  |  |  |  |  |

| 0xFFF8_7000                                | Pulse Width Modulation (PWM) Control Registers                        |  |  |  |  |  |  |  |

| 0xFFF8_8000                                | KeyPad Interface Control Register (KPI)                               |  |  |  |  |  |  |  |

| 0xFFF8_9000                                | PS2 Control Registers                                                 |  |  |  |  |  |  |  |

### Table 6.2.1 On-Chip Peripherals Memory Map

- 27 -

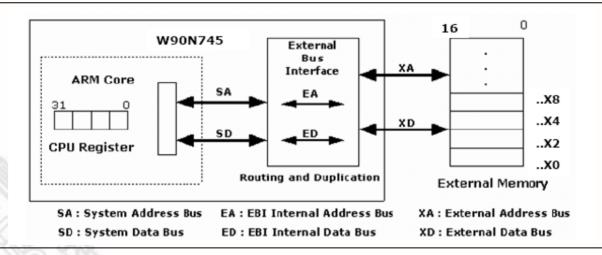

### 6.2.3 Address Bus Generation

The NUC745 address bus generation is depended on the required data bus width of each memory bank. The data bus width is determined by **DBWD** bits in each bank's control register.

The maximum accessible memory size of each external IO bank is 4M bytes.

| DATA BUS | EXTERNAL ADDRESS PINS  |                                |

|----------|------------------------|--------------------------------|

| WIDTH    | A [20:0]               | MAXIMUM ACCESSIBLE MEMORY SIZE |

| 8-bit    | A20 – A0<br>(Internal) | 2M bytes                       |

| 16-bit   | A21 – A1<br>(Internal) | 2M half-words                  |

#### Table 6.2.2 Address Bus Generation Guidelines

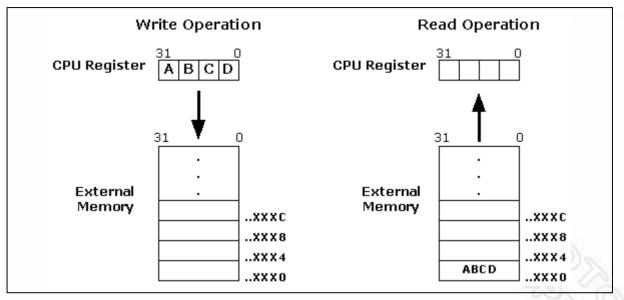

### 6.2.4 Data Bus Connection with External Memory

#### 6.2.4.1. Memory formats

The NUC745 can be configured as big endian or little endian mode by pull up or down the external data bus D14 pin. If D14 is pull up, then it is a little endian mode, otherwise, it is a big endian mode.

### Little endian

In little endian format, the lowest addressed byte in a word is considered the least significant byte of the word and the highest addressed byte is the most significant. So the byte at address 0 of the memory system connects to data lines 7 through 0.

For a word aligned address A, Figure 6.2.2 shows how the half-word at addresses A and A+2, and the bytes at addresses A, A+1, A+2, and A+3 map on to each other when **D14** pin is High.

| 15 | 14                                      | 13 | 12 | 11   | 10  | 9   | 8  | 7  | 6   | 5    | 4   | 3 | 2 | 1 | 0 |

|----|-----------------------------------------|----|----|------|-----|-----|----|----|-----|------|-----|---|---|---|---|

|    | Half-word at address A                  |    |    |      |     |     |    |    |     |      |     |   |   |   |   |

|    |                                         |    | ł  | lali | f-w | ord | at | ad | dre | SS . | A+2 | 2 |   |   |   |

| E  | Byte at address A+1 Byte at address A   |    |    |      |     |     |    |    |     |      |     |   |   |   |   |

| E  | Byte at address A+3 Byte at address A+2 |    |    |      |     |     |    |    |     |      |     | 2 |   |   |   |

Figure 6.2.2 Little endian addresses of bytes and half-words within half words

- 28 -

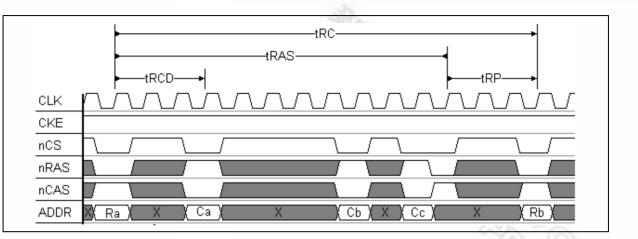

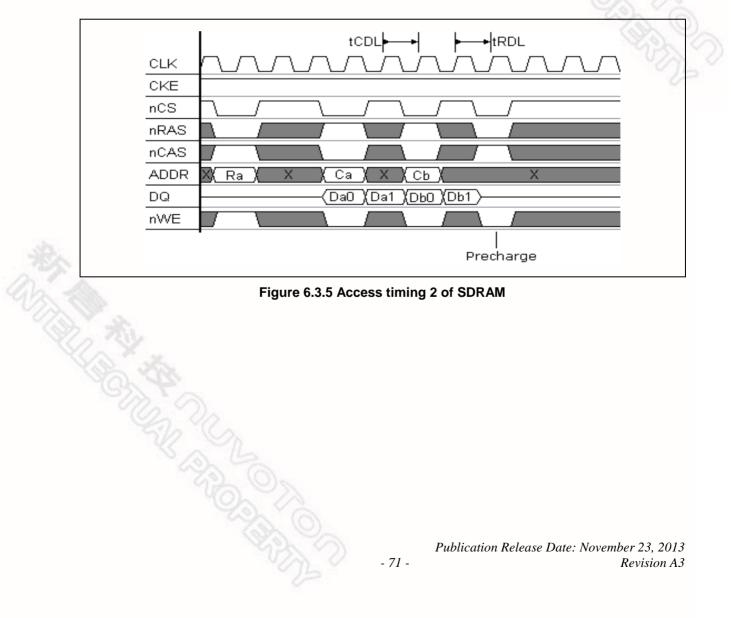

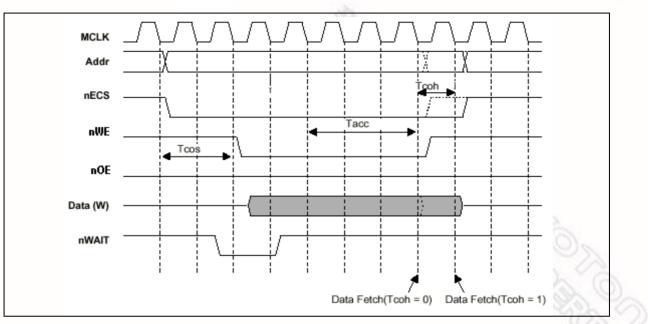

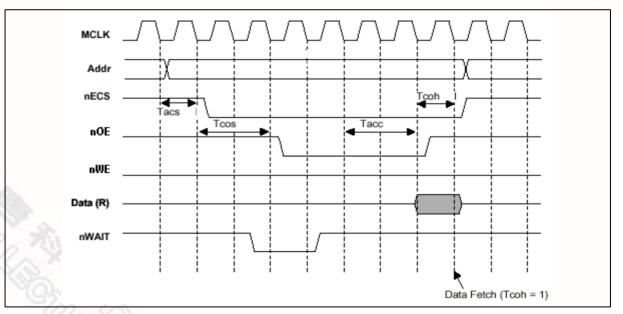

### **Big endian**