# NU1619: High Efficiency, High Integration Wireless Power Receiver/Transmitter

#### 1 Features

- Integrated 28V high-efficiency synchronous rectifier

- Integrated Low-Dropout LDO to Provide Regulated Output Programmable V<sub>out</sub> from 3.5V to 20V with 40mV step

- Programmable I<sub>out</sub> regulation from 0.1A to 2.2A with 20mA step

- Local thermal loop to dynamically regulate output power

- Integrated full bridge inverter and PWM control

- Programmable FOD gain and offset

- 1.8V reference voltage output

- V5V supply path management

- Robust OVP, OCP, OTP, and SCP

- 10 Bits ADC for voltage, current and temperature measurement

- Integrated 32Bit MCU

- I<sup>2</sup>C programmability

- In-system programmability

- Bi-directional communications ASK + FSK

- INT Output

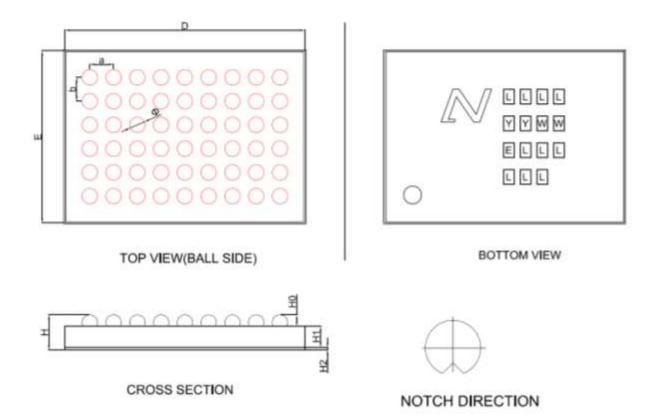

- 54-WCSP 2.90mm x 4.04mm, 0.4mm pitch

### 2 Applications

- WPC 15W EPP Compliant Receiver with Maximum 40W Received Power

- WPC 5W BPP Compliant Transmitter with Maximum 10W Transmit Power

- Wireless Power Receiver for Smartphones, Power Bank

- Receiver with Custom Defined FSK and ASK Communication

- Wireless Power Receiver for Medical, Industrial and Consumer Equipment

#### 3 Descriptions

NU1619 is a highly integrated and highly efficient wireless power receiver. It integrates a synchronous rectifier designed for a wide frequency range and a programable low dropout regulator for the optimal system efficiency. The regulator can provide a wide range regulated voltage or current output; both can be programmable through an I2C interface. NU1619 can conduct bi-directional communication with a transmitter system through ASK and FSK. The communication is compliant with WPC.

NU1619 can also be operated as a transmitter (Tx) to charge another receiver. Only few external components are needed and maximum 10W power can be transferred.

NU1619's flexibility is provided by an on-chip 32Bit MCU which can customize and optimize the device for various applications and custom needs. The programmability includes output power, bidirectional communication scheme, system protection, status reporting and error reporting.

NU1619 also includes standard protection functions such as input under-voltage lockout, short-circuit protection, overvoltage protection and thermal shutdown. These provisions further enhance the reliability of the system solution.

The device is housed in a compact 2.90mm×4.04mm WCSP package.

This document contains confidential and proprietary information of NuVolta. Any information in this document is prohibited from being used, reproduced or disseminated to any third party in any form and/or through any means without the prior written consent of NuVolta. **ALL RIGHTS RESERVED.**

### Content

| 1 Features                                       | 1  |

|--------------------------------------------------|----|

| 2 Applications                                   | 1  |

| 3 Descriptions                                   | 1  |

| 4 Pin Configuration and Functions                | 3  |

| 5 Specifications                                 | 5  |

| 5.1 Absolute Maximum Ratings                     | 5  |

| 5.2 ESD Ratings                                  | 5  |

| 5.3 Recommended Operating Condition              | 5  |

| 5.4 Package Thermal Ratings                      | 5  |

| 5.5 Electrical Characteristics                   | 6  |

| 6 Register Maps                                  | 8  |

| 6.1 General Purpose Registers (Read Only)        | 8  |

| 6.2 General Purpose Registers (Read/Write)       | 8  |

| 6.3 Start-up Mode Control Registers (Read/Write) | 8  |

| 6.4 Chip ID Registers (DTM Read Only)            | 8  |

| 7 Functional Block Diagram                       | 9  |

| 8 Typical Characteristics                        | 10 |

| 9 Application Descriptions                       | 12 |

| 9.1 System Overview                              | 12 |

| 9.2 Power Supply                                 | 12 |

| 9.3 Synchronous Rectifier                        | 13 |

| 9.4 Output LDO                                   | 13 |

| 9.5 Over-Voltage Protection                      | 13 |

| 9.6 Over-Current Protection                      | 13 |

| 9.7 ADC                                          | 14 |

| 9.8 I <sup>2</sup> C, INT                        | 14 |

| 9.9 Inverter control of Tx Mode                  | 14 |

| 9.10 Digital Demodulation                        | 15 |

| 10 Layout Guidelines                             | 15 |

| 11 Typical Application Circuit                   | 18 |

| 12 Package Information                           | 18 |

| 13 Mechanical Data                               | 19 |

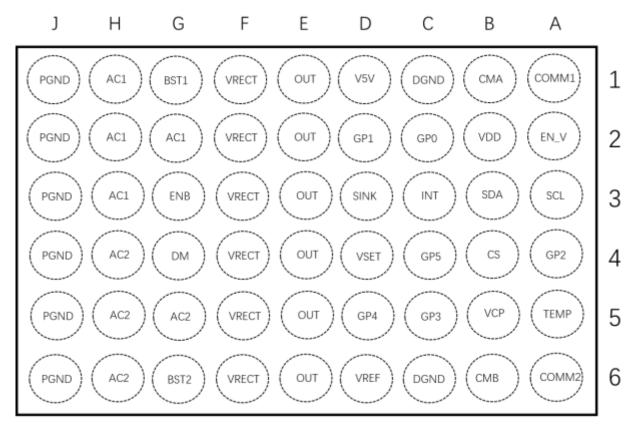

### **4 Pin Configuration and Functions**

Figure 1. NU1619-WCSP Top View

| Pin    |           | 1/0                                                      | D                                                              |

|--------|-----------|----------------------------------------------------------|----------------------------------------------------------------|

| Name   | No.       | I/0                                                      | Description                                                    |

| COMM1/ | A1/       | 0                                                        | Open-drain output used to communicate with the                 |

| COMM2  | A6        |                                                          | transmitter. Connect a capacitor between this pin and          |

|        |           |                                                          | AC1/AC2.                                                       |

| CMA/   | B1/       | 0                                                        | Open-drain output used to communicate with the                 |

| CMB    | В6        |                                                          | transmitter. Connect a capacitor between this pin and          |

|        |           |                                                          | AC1/AC2.                                                       |

| DGND   | C1/C6     | GND                                                      | Digital Ground.                                                |

| V5V    | D1        | P 5V LDO output for IC internal use. Connect a capacitor |                                                                |

| V 3 V  | DI        | Г                                                        | between this pin and DGND.                                     |

| OUT    | E1~E6     | P                                                        | Regulated output voltage pin in Rx mode. Connect capacitor     |

|        |           |                                                          | between this pin and ground.                                   |

|        |           |                                                          | This will be power input pin in Tx mode.                       |

| VRECT  | F1~F6     | P                                                        | Output of the synchronous rectifier. Connect capacitor         |

|        |           |                                                          | between this pin and ground.                                   |

| BST1/  | G1/       | I/O                                                      | Supply rail for the high-side gate driver. Connect a capacitor |

| BST2   | G6        |                                                          | between this pin and AC1/AC2.                                  |

| AC1    | H1~H3, G2 | P                                                        | AC input power. Connect to the resonant circuit of L and C.    |

V1.0 www.icgan.com -3- lin@icgan.com

| AC2       | H4~H6, G5 | P   |                                                           |

|-----------|-----------|-----|-----------------------------------------------------------|

| PGND      | J1~J6     | GND | Power Ground.                                             |

| EN_V      | A2        | I   | Enable the external supply connected the VDD pin.         |

| VDD       | B2        | P   | The External power supply pin. When EN_V= high, this PIN  |

|           |           |     | will be connected to the internal circuit as the supply.  |

| GP0       | C2        | I/O | General purpose logic IO pin.                             |

| GP1/      | D2        | I/O | High power logic output pin can provide 30mA max current  |

| VPON/ADC1 |           |     | as push pull output. Analog input pin.                    |

| SCL       | A3        | I   | I2C clock pin.                                            |

| SDA       | В3        | I/O | I2C data pin. Open-drain output.                          |

| INT       | C3        | 0   | Interrupt output. Open-drain output.                      |

| SINK      | D3        | 0   | Open-drain output for controlling the rectifier clamp.    |

|           |           |     | Connect a resistor between this pin and the VRECT pin.    |

| ENB       | G3        | I   | Chip enable pin. Low logic active.                        |

| GP2       | A4        | 0   | General purpose logic Output PIN.                         |

| CS        | B4        | I   | Tx mode current sense PIN.                                |

| GP5       | C4        | I/O | Reserved                                                  |

| VSET/ADC2 | D4        | I/O | General purpose analog IO PIN, and analog input           |

| DM        | G4        | I   | Tx mode demodulation input PIN.                           |

| TEMP/ADC3 | A5        | T   | NTC input pin for external temperature sense. Connect NTC |

| TEMP/ADC3 | AS        | 1   | and a small cap in parallel between this pin and DGND.    |

| VCP       | B5        | P   | Driver supply of OUT LDO.                                 |

| GP3       | C5        | 0   | General purpose logic Output PIN.                         |

| GP4/ADC0  | D5        | I/O | General purpose logic output PIN, and Analog input.       |

| VREF      | D6        | 0   | Output 1.8V reference voltage.                            |

|           |           | _   |                                                           |

## **5 Specifications**

## **5.1 Absolute Maximum Ratings**

| Pins                                           | Rating            | Units |

|------------------------------------------------|-------------------|-------|

| SCL, SDA, DM                                   | -0.3~6            | V     |

| EN_V, V5V, VDD, TEMP, VSET, ENB,               |                   |       |

| GP0~GP5                                        |                   |       |

| VRECT, SINK, CMA, CMB, COMM1, COMM2,           | -0.3~30           | V     |

| AC1, AC2                                       |                   |       |

| VREF                                           | -0.3~2.8          | V     |

| INT                                            | -0.3~6            | V     |

| VCP                                            | -0.3~35           | V     |

| VRECT to OUT                                   | 22                | V     |

| BST1, BST2                                     | -0.3~AC1+6, AC2+6 | V     |

| OUT, CS                                        | -0.3~22           | V     |

| Max Current on SINK                            | 1                 | A     |

| Max Current on COMM1/COMM2                     | 1                 | A     |

| Max Current on CM1A/CM2B                       | 1                 | A     |

| Max Current on AC1/AC2                         | 5                 | A     |

| Maximum OUT output current                     | 2.5               | A     |

| Operating Junction Temperature, T <sub>J</sub> | -40~125           | οС    |

| Ambient Operating Temperature, T <sub>A</sub>  | -40~85            | οС    |

| Storage Temperature, T <sub>stg</sub>          | -55~125           | ٥C    |

## **5.2 ESD Ratings**

| Test Model           | Pins                        | Ratings | UNIT |

|----------------------|-----------------------------|---------|------|

| Human Dady Madal     | All pins except CMA and CMB | +/-2000 | V    |

| Human Body Model     | CMA, CMB pins               | +/-1000 | V    |

| Charged Device Model | All pins                    | +/-500  | V    |

### **5.3 Recommended Operating Condition**

|                        | Max | UNIT |

|------------------------|-----|------|

| OUT to PGND Voltage    | 20  | V    |

| OUT PIN Output Current | 2.1 | A    |

### **5.4 Package Thermal Ratings**

|                                              |    | UNIT |

|----------------------------------------------|----|------|

| Junction-to-ambient thermal resistance, Roja | 40 | °C/W |

### **5.5 Electrical Characteristics**

$V_{RECT}$ =19V,  $T_j$ =-40 °C to 125°C (unless otherwise noted)

| ]                                               | PARAMETERS                                     | TEST<br>CONDITIONS                                                           | MIN   | TYP   | MAX   | UNIT |

|-------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------|-------|-------|-------|------|

| Power supp                                      | oly                                            |                                                                              |       |       |       | l.   |

| V <sub>V5V</sub>                                | Vvsv Under-voltage lock<br>out threshold       | Vvsv ramps up <sup>[a]</sup>                                                 | -5%   | 3.2   | +5%   | V    |

| Vv5v_hys                                        | Vvsv Under-voltage lock out hysteresis voltage | V <sub>V5V</sub> ramps<br>down <sup>[a]</sup>                                |       | 250   |       | mV   |

| VRECT_OVP_HA<br>RD                              | Over-voltage threshold for safety              | V <sub>RECT</sub> ramps up                                                   | -5%   | 27    | +5%   | V    |

| V <sub>HYS_OVP_HAR</sub>                        | Over-voltage hysteresis for safety             | V <sub>RECT</sub> ramps down                                                 |       | 0.35  |       | V    |

| VRECT_OVP_SO FT                                 | Soft Over-voltage threshold                    | V <sub>RECT</sub> ramps up                                                   | -5%   | 18.7  | +5%   | V    |

| VHYS_OVP_SOF                                    | Soft Over-voltage hysteresis                   | VRECT ramps down                                                             |       | 0.5   |       | V    |

| V <sub>RECT_OVP1</sub>                          | Over-voltage threshold level 1                 | V <sub>RECT</sub> ramps up <sup>[b]</sup>                                    | -5%   | 19.4  | +5%   | V    |

| VHYS_OVP1 Small Over-voltage hysteresis level 1 |                                                | V <sub>RECT</sub> ramps<br>down <sup>[c]</sup>                               |       | 0.3   |       | V    |

| Big Over-voltage<br>hysteresis leve1            |                                                | V <sub>RECT</sub> ramps down <sup>[c]</sup>                                  |       | 6     |       | V    |

| I <sub>Q_RECT</sub>                             | Quiescent operating current into VRECT         | ENB=low, EN_V=low no load, no switching                                      |       | 5.5   |       | mA   |

| Isd_rect                                        | Shutdown current into VRECT                    | ENB=high, EN_V=low                                                           |       | 2.6   |       | mA   |

| OUTPUT RI                                       | <br>EGULATION (POWER DCD                       | <br>OC)                                                                      |       |       |       |      |

| Vout                                            | Output voltage range                           |                                                                              | 3.5   |       | 20    | V    |

| Vout_step                                       | Output voltage step                            | Vout=3.5V to 20V                                                             |       | 20    |       | mV   |

| VOUT_REG                                        | Output voltage regulation                      | VRECT=Vout+0.3V,<br>Vout=18V, Iout=1A                                        | 17.46 | 18    | 18.54 | V    |

|                                                 |                                                | V <sub>RECT</sub> =Vout+0.3V,<br>V <sub>OUT</sub> =12V, I <sub>OUT</sub> =1A | 11.64 | 12    | 12.36 |      |

| Isense_rx_k                                     | RX current sense gain                          | I <sub>OUT</sub> =0.8A to 1.6A,                                              |       | 1.004 |       |      |

| Isense_rx_os                                    | RX current sense offset                        | I <sub>OUT</sub> =0.8A to 1.6A                                               |       | 1.637 |       | mA   |

| I <sub>SENSE_TX_K</sub>                         | Tx current sense gain                          | I <sub>OUT</sub> =0.8A to 1.6A,                                              |       | 1.008 |       |      |

| I <sub>SENSE_TX_OS</sub>                        | TX current sense offset                        | I <sub>OUT</sub> =0.8A to 1.6A                                               |       | 1.0   |       | mA   |

V1.0 www.icgan.com -6- lin@icgan.com

| ILIM_RANGE                   | Current limit range                                          |                            | 0.1  |     | 2.2  | A   |

|------------------------------|--------------------------------------------------------------|----------------------------|------|-----|------|-----|

| ILIM_STEP                    | Current limit step                                           |                            |      | 20  |      | mA  |

| I <sub>LIM_acc</sub>         | Current limit accuracy                                       |                            | -10% | 0   | 10%  |     |

|                              |                                                              |                            |      |     |      |     |

| External Po                  | ower supply                                                  |                            |      |     |      |     |

| $V_{\text{UVLO\_VDD}}$       | V <sub>DD</sub> Under-voltage lock out threshold             | V <sub>DD</sub> ramps up   | -5%  | 3.2 | +5%  | V   |

| $V_{\text{UVLO\_VDD\_H}}$ YS | V <sub>DD</sub> Under-voltage lock<br>out hysteresis voltage | V <sub>DD</sub> ramps down |      | 250 |      | mV  |

| I <sub>Q_VDD</sub>           | Quiescent operating current into V <sub>DD</sub>             | ENB=low,<br>EN_V=high      |      | 4.8 |      | mA  |

| I <sub>SD_VDD</sub>          | Shutdown current into $V_{\text{DD}}$                        | ENB=high,<br>EN_V=low      |      |     | 1    | uA  |

|                              |                                                              |                            |      |     |      |     |

| LOW POWI                     | ER LDO                                                       |                            |      |     |      |     |

| $V_{5V}$                     | 5V supplier                                                  | I <sub>V5V</sub> =10mA     | 4.56 | 4.8 | 5.04 | V   |

| I <sub>5</sub> V             | 5V current limit                                             |                            | 30   |     |      | mA  |

| Vref                         | Reference voltage                                            | I <sub>REF</sub> =1mA      |      | 1.8 |      | V   |

| IREF                         | Reference current limit                                      |                            | 10   |     |      | mA  |

| IO                           |                                                              |                            |      |     |      |     |

| VHIGH_LOGIC                  | ENB, INT, GP0, GP1,<br>GP2, GP3, GP4, GP5, SCL,<br>SDA       |                            | 1.4  |     |      | V   |

| VLOW_LOGIC                   | ENB, INT, GP0, GP1,<br>GP2, GP3, GP4, GP5, SCL,<br>SDA       |                            |      |     | 0.6  | V   |

| R <sub>COMM</sub>            | COMM1/COMM2 switch on resistance                             |                            |      | 0.3 |      | ohm |

| Rcм                          | CMA/CMB switch on resistance                                 |                            |      | 0.3 |      | ohm |

| Rsink                        | SINK switch on resistance                                    |                            |      | 0.4 |      | ohm |

| Thermal Sl                   |                                                              | 1                          |      |     |      |     |

| Тотр                         | Over-temperature protection threshold                        |                            |      | 155 |      | °C  |

| THYS_OTP                     | Over-temperature protection hysteresis                       |                            |      | 30  |      | ۰C  |

<sup>[</sup>a] V5V pin has two power supply channels: VDD or VRECT

V1.0 www.icgan.com -7- lin@icgan.com

<sup>[</sup>b]  $V_{\text{RECT\_OVP1}}$  has eight settings value. The setting range is from 19.4V to 26.0V.

<sup>[</sup>c]  $V_{\text{HYS\_OVP1}}$  has two options (small/big over-voltage hysteresis level).

### 6 Register Maps

### 6.1 General Purpose Registers (Read Only)

| Address and Bit                | Default<br>Value | Default Function and Description                                                                                                      |

|--------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 0x0008 [7:0]                   | 0x00             | ADC Channel TEMP_SNS[7:0]. TEMP pin voltage sense channel.<br>[VALUE] DEC = $1023*1.8V*R_{NTC}/(R_9+R_{NTC})/2.5V$ refer to $9.7 ADC$ |

| 0x0009 [7:0]                   | 0x00             | ADC Channel VOUT_SNS[7:0]. VOUT pin voltage sense channel. Vout=22.5V*[VALUE]DEC/256DEC                                               |

| 0x000A [7:0]                   | 0x00             | ADC Channel VRECT_SNS[7:0]. VRECT pin voltage sense channel. VRECT=27.5V*[VALUE]DEC/256DEC                                            |

| 0x000B [7:0]                   | 0x00             | ADC Channel IOUT_SNS[7:0]. VOUT pin current sense channel.  IOUT=2.5A*[VALUE] DEC /256DEC                                             |

| 0x0020 [7:0] ~<br>0x0024 [7:0] | 0x00             | Reserved                                                                                                                              |

### 6.2 General Purpose Registers (Read/Write)

| Address<br>and Bit             | Default<br>Value | Default Function and Description                      |

|--------------------------------|------------------|-------------------------------------------------------|

| 0x0000 [7:0] ~<br>0x0007 [7:0] | 0x00             | Control registers, setting and control operation mode |

| 0x000C [7:0]                   | 0x00             | Reserved                                              |

| 0x000E [7:0]                   | 0x00             | Reserved                                              |

### 6.3 Start-up Mode Control Registers (Read/Write)

The following is the control register for start-up mode selection.

| Address<br>and Bit | Default<br>Value | Function and Description    |

|--------------------|------------------|-----------------------------|

| 0x000D [7:4]       | 0x0              | Writing 0x2: enable TX mode |

| 0x000D [3:0]       | 0x0              | Reserved                    |

### 6.4 Chip ID Registers (DTM Read Only)

The followings are chip ID registers which can only be read in Design Test Mode (DTM).

| Address<br>and Bit | Default<br>Value | Description                          |  |

|--------------------|------------------|--------------------------------------|--|

| 0x0096 [7:0]       | 0x19             | The second two characters of chip ID |  |

| 0x0097 [7:0]       | 0x16             | The first two characters of chip ID  |  |

V1.0 www.icgan.com -8- lin@icgan.com

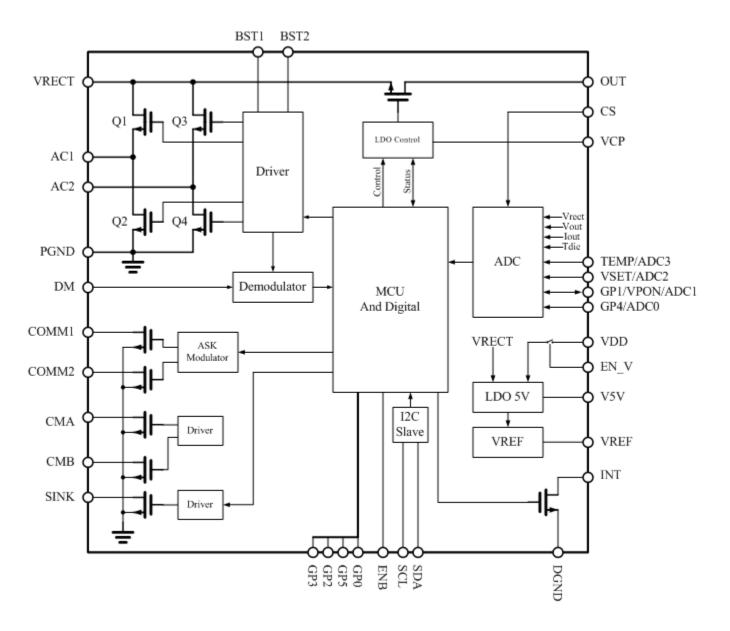

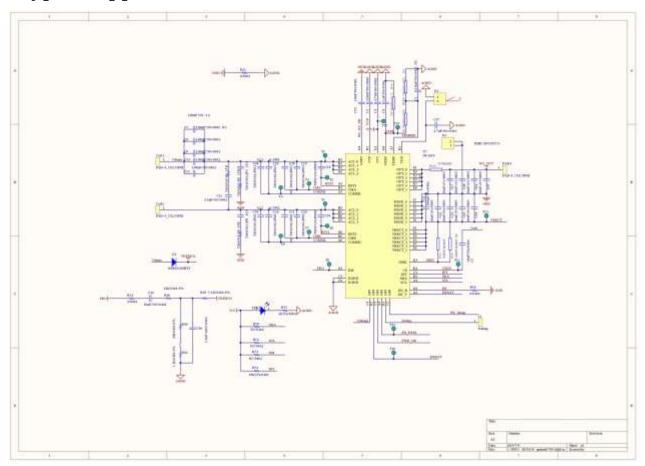

## 7 Functional Block Diagram

Figure 2. Function Block Diagram

V1.0 www.icgan.com -9- lin@icgan.com

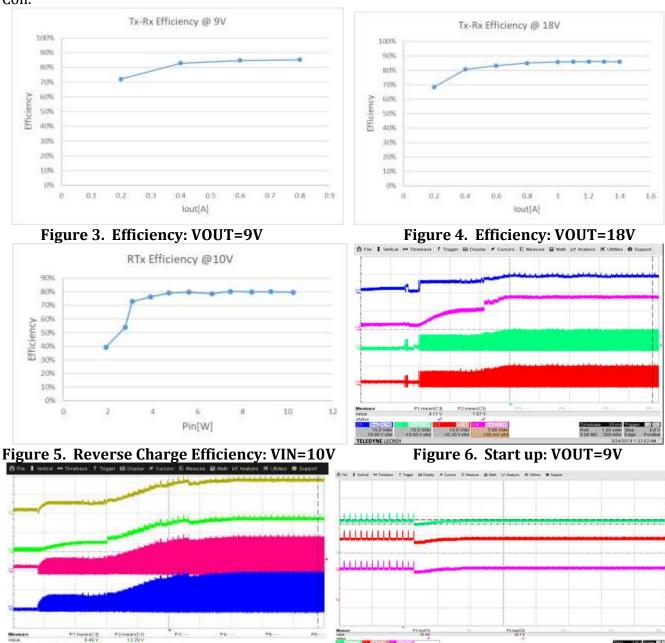

# **8 Typical Characteristics**

The following testing is using NU1020+NU1513 wireless transmitter EVM with MPA2 Tx Coil.

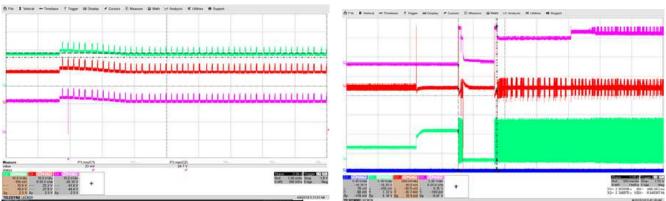

Figure 7. Start up: VOUT=18V

Figure 8. Transient Response: VOUT=18V, IOUT=0A to 0.5A

V1.0 www.icgan.com -10- lin@icgan.com

Figure 9. Transient Response: VOUT=18V, IOUT=0.5A to 0A

Figure 10. Tx mode Start up: VIN=10V

Note: (1) Figure 6~7: CH1-V<sub>RECT</sub>; CH2-AC1; CH3-Comm; CH4-Vo

- (2) Figure  $8\sim9$ : CH1-NA; CH2-Vo; CH3-  $V_{RECT}$ ; CH4-Sink

- (3) Figure 10: CH1-NA; CH2-SW; CH3- DM; CH4-  $V_{\text{RECT}}$

- (4) The typical characteristics were tested at TA = 25°C, unless otherwise noted

V1.0 www.icgan.com -11- lin@icgan.com

### 9 Application Descriptions

#### 9.1 System Overview

In a wireless power transfer system, the transmitter system generates magnetic field by feeding AC current into a transmitting coil. The magnetic field is coupled to a receiving side coil and the coupled energy is further maximized by matching the transmitter side impedance. The outputs of the resonant circuit are connected to the AC1 and AC2 pin of the IC which are the inputs to the on-chip synchronous rectifier. The rectifier output is an unregulated voltage connected to the VRECT pin of the IC. To provide a well-regulated voltage source or current source to the downstream circuit, an ultra-low dropout LDO is connected between the VRECT pin and the OUT pin.

The communication between the transmitter side (Tx) and receiver side (Rx) is needed to provide feedback on the power requirement from the receiver to the transmitter. NU1619 is equipped with bi-directional communication compliant with the WPC standard. The communication protocol can be customized for any proprietary systems. The Rx to Tx communication is implemented by turning on the COMM1 and COMM2 or CMA and CMB internal switches and inserting additional capacitance to the Rx resonant circuit. This modulation of Rx impedance can be detected on the Tx side as amplitude modulation of its coil voltage and current waveform. Tx to Rx communication is done through modulating the transmitting frequency. NU1619 is equipped with frequency measurement circuit to sense and decode the modulated frequency.

Protection is a critical requirement to wireless power receivers, especially the over-voltage protection on the VRECT pin. The coupling factor between Tx and Rx, hence the coupled energy between Tx and Rx, can change suddenly and significantly as the proximity between Rx and Tx coils is altered by end users without notice. When the coupled energy increases, the VRECT voltage can rise and potentially exceed its maximum voltage rating to cause IC damage. NU1619 incorporates comprehensive over-voltage protection against any transient conditions through the SINK pin.

### 9.2 Power Supply

When the receiving coil is placed in the magnetic field created by the transmitter analog ping, DC voltage is established on the VRECT pin through the body diode of the rectifier MOSFET initially. V5V follows VRECT voltage through an inner start up circuit. When V5V is above 3V, the 5V LDO, which provides IC internal bias voltage, is powered up to turn on internal circuit blocks, such as MCU, protection circuits and rectifier switches. In addition, the communication from Rx to Tx takes place to instruct Tx to deliver power. A capacitor of typical value of 10uF to 40uF should be placed at the VRECT pin to provide DC voltage to the IC.

When the receiving coil is removed from the magnetic field, or the transmitter is turned off, the voltage of the VRECT pin is discharged by the load connected to the OUT pin and IC operating current. If the V5V voltage drops below 2.8V, the IC enters the shutdown mode.

V5V can also be powered up with an external power supply from VDD pin, the power path is controlled by the EN\_V pin. When VDD is above 3.2V, then set EN\_V high, V5V follows VDD voltage

V1.0 www.icgan.com -12- lin@icgan.com

through an inner power path. When VDD drops below 3V or set EN\_V to Low, the VDD power path will be turn off.

#### 9.3 Synchronous Rectifier

The NU1619 has an integrated synchronous rectifier to ensure efficient AC-to-DC conversion, especially for the heavy output load. It has built in a reliable and efficient switch control algorithm to minimize the dead-time while eliminating the possibility of the shoot-through inside the rectifier.

The BST1 and BST2 pins are connected to the internal boost-strap circuit to provide supply rails to the high-side MOSFET Q1 and Q3.

#### 9.4 Output LDO

The output voltage of the LDO can be programed through I<sup>2</sup>C interface or an external resistor divider network connected to the VSET pin. The programmable voltage range is from 3.5V to 20V with 40mV step. The external resistors should be selected and the formula below:

$$R_2/(R_1+R_2) = 0.09*V_{0\_SET}/V_{REF}$$

Where R1 is between VSET and VREF, R2 is between VSET and DGND,  $V_{0\_SET}(V)$  is the targeted output voltage and  $V_{REF}(V)$  is the reference voltage.

The output current limit of the LDO can also be programed through I<sup>2</sup>C interface, the programmable current range is 0.1A to 2.2A with 20mA step.

The LDO is protected by the over-current protection. During the over-current protection, SINK switches are turned on to limit the coupled energy. And an interrupt will be triggered to MCU for more action.

LDO has a soft-start feature to prevent in-rush current caused by charging output capacitor during the startup. The soft start gradually turns on the LDO to control and limit its current.

### 9.5 Over-Voltage Protection

Since the feedback loop between Rx and Tx is inherently slow, the transmitter is unable to reduce the power output instantly when the overvoltage condition occurs on the receiver side. The delay can be in the range of tens or even hundreds of milli-seconds which is a long time enough to damage the IC. The over-voltage protection circuit engages immediately upon the occurrence of the over-voltage condition. The protection circuit will be creating a 'bleeding' resistor (One  $620\Omega$  resistors in 0805 packages is recommended) to the VRECT pin to dissipate the power through the resistor.

#### 9.6 Over-Current Protection

V1.0 www.icgan.com

NU1619 integrates a reliable over current protection circuit. Current of the LDO is sensed and compared to the over-current protection threshold (Iocp). If the current exceeds the threshold, the internal the over-current protection circuit is triggered, and LDO and PWM inputs will be turned off. The OCP threshold can be set through I<sup>2</sup>C.

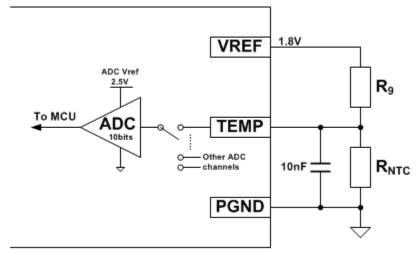

#### 9.7 ADC

NU1619 integrates an accurate 10bit ADC which takes inputs from internal signals such as VRECT voltage, output voltage and current. These signals are used to set the proper VRECT voltage through communication with the transmitter. Please refer to <u>Register Maps</u> to get more detail information.

NU1619 can monitor the external temperature through the TEMP pin, a filter capacitor and the value of 10nF is recommended connect with TEMP pin. The formula below shows the ADC value of the external temperature where the NTC is placed according to the R<sub>NTC</sub> (to DGND) and R9 (to VREF):

$$ADC_{TEMP}[VALUE] = 1023*1.8V*R_{NTC}/(R_9 + R_{NTC})/2.5V$$

Show as Figure 11, ADC<sub>TEMP</sub> is the ADC channel [VALUE] from TEMP PIN. 1.8V is the default output voltage of VREF PIN. 2.5V is the internal reference voltage of ADC.

Figure 11. External temperature ADC reference circuit.

#### 9.8 I<sup>2</sup>C, INT

NU1619 allows for the I<sup>2</sup>C communication with both SCL and SDA, see <u>Register Maps</u> for more information.

INT pin is an open-drain and LOW active pin. Connect a resistor (e.g. 5.1K) between this pin and V5V. This pin is pulled high during normal mode. Under over-current, over-voltage, short-circuit, over-temperature conditions or another interrupt, the INT pin is pulled low to indicate a fault condition. The fault mode can be read through the I<sup>2</sup>C interface.

#### 9.9 Inverter control of Tx Mode

When NU1619 operates at Tx MODE, an internal PWM generator controls the  $Q1\sim Q4$  which operate as a full bridge inverter. For a typical WPC transmitter, the AC1 and AC2 are complementary in logic and have 50% duty cycle in the frequency range of 110KHz to 205KHz. When reaching 205KHz, the duty cycle can be reduced below 50% to further limit the power output.

The PWM controller can also be independently control the AC1 and AC2 duty cycle and frequency. This allowed  $Q1 \sim Q4$  operate as a half bridge inverter

#### 9.10 Digital Demodulation

A digital demodulation circuit is integrated inside NU1619. The DM pin is used as an analog input pin. The IC detects the envelope of the peak voltage of the connecting node (Vcoil) between the resonant inductor and capacitors, decodes the voltage signals, and sends out the decoded signals to MCU.

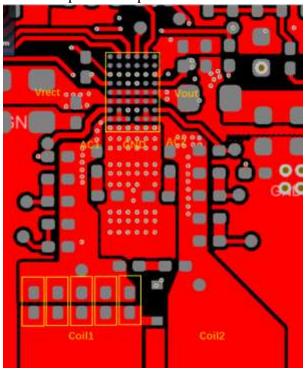

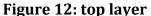

### **10 Layout Guidelines**

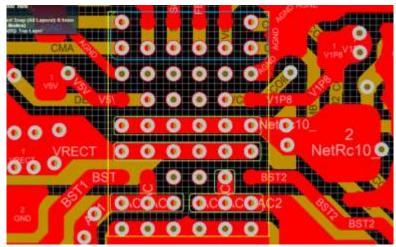

Show as Figure 12 and Figure 13, Coil connects from both sides of IC to Pins AC1 and AC2, a ground is place at GND Pin. The decoupling Capacitor of Vrect and Vout placed near by IC, to minimize the power loop of Vrect to GND and Vout to GND.

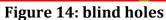

Figure 13: second layer

Show as Figure 14 and Figure 15, Power pin AC1, AC2, Vrect and Vout are connected by blind holes to top layer and the second layer, Show as green region.

Signal pin COMM1, COMM2, CMA, CMB, VCP, CS, SDA, VDD, GP4, VPON are connected by blind holes to top layer and the second layer, Show as Blue region.

V1.0 www.icgan.com -15- lin@icgan.com

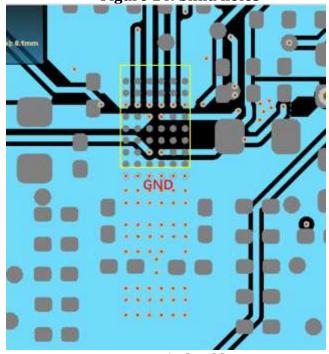

Figure 15: third layer

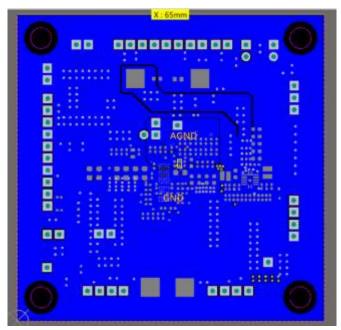

Show as Figure 16, bottom layer is Ground. There are a power GND and a signal GND, both GND are connect by a 0ohm resistor, the connect point is near Vout capacitor's negative node.

V1.0 www.icgan.com -16- lin@icgan.com

Figure 16: Bottom layer

Note: Make the resonant power routing loop as small as possible and keep away from another signal circuit.

V1.0 www.icgan.com -17- lin@icgan.com

# 11 Typical Application Circuit

# 12 Package Information

| Orderable<br>Device | Status | Packag<br>e Type | Packag<br>e<br>Drawin<br>g | Pins | Eco<br>Plan                     | Lead/Ball<br>Finish | MSL<br>Peak<br>Temp | Op Temp©   | Device<br>Marking |

|---------------------|--------|------------------|----------------------------|------|---------------------------------|---------------------|---------------------|------------|-------------------|

| NU1619WFF<br>B      | MP     | WCSP             | WFF                        | 54   | Green(R<br>oHS &<br>No<br>Sb/Br | Cu/Sn Ag<br>Cu      | Level-2             | -40 to 125 | NU1619WFF         |

V1.0 www.icgan.com -18- lin@icgan.com

### 13 Mechanical Data

| SYMBOL | ITEM             | DATA(UM)     |  |  |

|--------|------------------|--------------|--|--|

| D*E    | PACKAGE SIZE X*Y | 4040*2900±25 |  |  |

| Ф      | BALL DIAMETER    | 260±30       |  |  |

| a/b    | BALL PITCH X/Y   | 400/400      |  |  |

| N      | BALL COUNT       | 54           |  |  |

| Н      | PACKAGE HEIGHT   | 590±45       |  |  |

| H0     | BALL HEIGHT      | 195±30       |  |  |

| H1     | SI THICKNESS+PI  | 355±25       |  |  |

| H2     | DRY FILM         | 40           |  |  |

V1.0 www.icgan.com -19- lin@icgan.com