# NTE7156 Integrated Circuit DC-Coupled Vertical Deflection Circuit

#### **Description:**

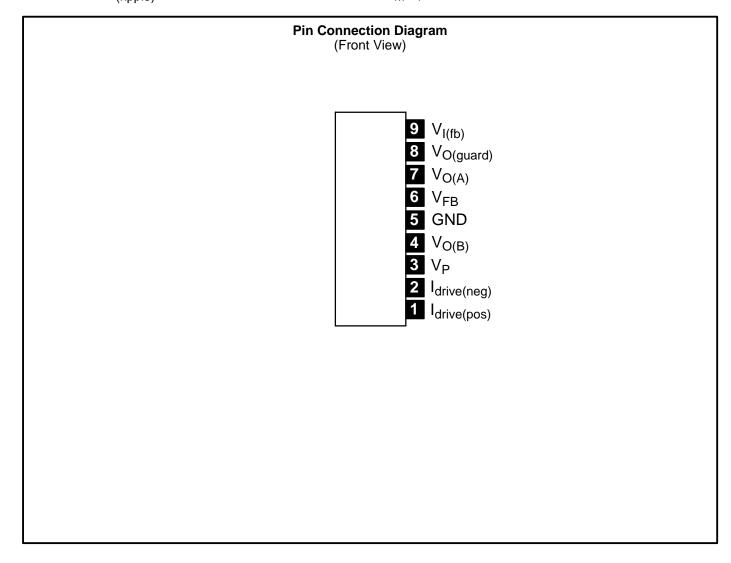

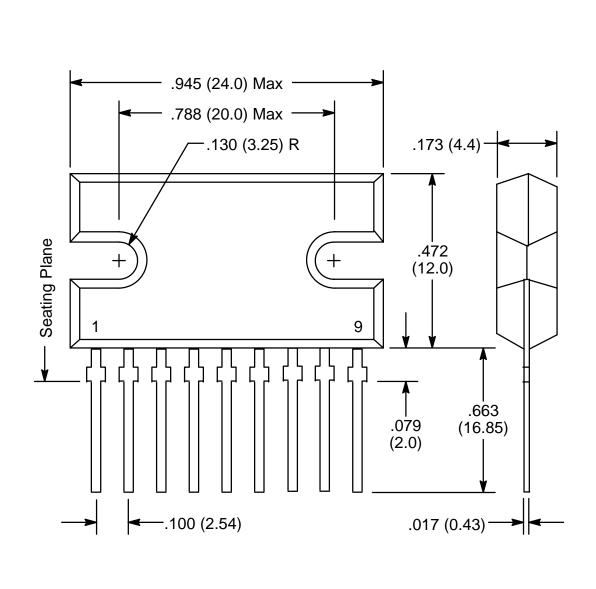

The NTE7156 is a power circuit in a 9–Lead SIP type package designed for use in 90° and 110° color deflection systems for field frequencies of 50Hz to 120Hz. This device provides a DC driven vertical deflection output circuit, operating as a highly efficient class G system.

#### Features:

- Few External Components

- Highly Efficient Fully DC-Coupled Vertical Output Bridge Circuit

- Vertical Flyback Switch

- Guard Circuit

DC Supply

- Protection Against:

- Short–Circuit of the Output Pins (7 and 4)

- Short-Circuit of the Output Pins to VP

- Temperature Protection

- High EMC Immunity Because of Common Mode Inputs

- A Guard Signal in Zoom Mode

### **Absolute Maximum Ratings:**

| DC Supply                                                         |        |

|-------------------------------------------------------------------|--------|

| Supply Voltage, V <sub>P</sub>                                    |        |

| Non-Operating                                                     | 40V    |

| Operating                                                         |        |

| Flyback Supply Voltage, V <sub>FB</sub>                           | 50V    |

| Note 1                                                            | 60V    |

| Vertical Circuit                                                  |        |

| Output Current (Peak-to-Peak Value, Note 2), I <sub>O(P-P)</sub>  | 3A     |

| Output Voltage (Pin7), V <sub>O(A)</sub>                          | 52V    |

| Output Voltage (Pin7), V <sub>O(A)</sub>                          | 62V    |

| Flyback Switch                                                    |        |

| Peak Output Current, I <sub>M</sub>                               | ±15A   |

| Thermal Data                                                      |        |

| Virtual Junction Temperature, T <sub>VJ</sub>                     | +150°C |

| Operating Ambient Temperature Range, T <sub>A</sub>               |        |

| Storage Temperature Range, T <sub>stq</sub>                       |        |

| Thermal Resistance, Virtual Junction-to-Ambient, RthVJ-C          |        |

| Thermal Resistance, Virtual Junction-to-Case, R <sub>thVJ-A</sub> |        |

| Short–Circuit Time (Note 3), t <sub>sc</sub>                      |        |

| · · · · · · · · · · · · · · · · · · ·                             |        |

- Note 1. A flyback supply voltage of > 50V up to 60V is allowed in application. A 22–nF capacititor in series with a  $22\Omega$  resistor (depending on  $I_O$  and the inductance of the coil) has to be connected between Pin7 and GND. The decoupling capacitor of  $V_{FB}$  has to be connected between Pin6 and Pin3. This supply voltage line must have a resistance of  $33\Omega$ .

- Note 2. I<sub>O</sub> maximum determined by current protection.

- Note 3. Up to  $V_P = 18V$ .

##

| Parameter                                                                                  | Symbol                | Test Conditions                                                                                     | Min            | Тур  | Max              | Unit |

|--------------------------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------|----------------|------|------------------|------|

| DC Supply                                                                                  | <u> </u>              |                                                                                                     | ı              |      |                  |      |

| Operating Supply Voltage                                                                   | V <sub>P</sub>        |                                                                                                     | 9              | _    | 25               | V    |

| Flyback Supply Voltage                                                                     | $V_{FB}$              |                                                                                                     | V <sub>P</sub> | _    | 50               | V    |

|                                                                                            |                       | Note 1                                                                                              | V <sub>P</sub> | _    | 60               | V    |

| Supply Current                                                                             | l <sub>P</sub>        | No Load, No Signal                                                                                  | _              | 30   | 55               | mA   |

| Vertical Circuit                                                                           | Į.                    |                                                                                                     | I.             | - 1  |                  |      |

| Output Voltage Swing (Scan)                                                                | V <sub>O</sub>        | $I_{diff} = 0.6mA_{(P-P)}, V_{diff} = 1.8V_{(P-P)}, I_{O} = 3A_{(P-P)}$                             | 19.8           | -    | -                | V    |

| Linearity Error                                                                            | LE                    | $I_O = 3A_{(P-P)}$ , Note 4                                                                         | _              | 1    | 3                | %    |

|                                                                                            |                       | $I_O = 50 \text{mA}_{(P-P)}$ , Note 4                                                               | _              | 1    | 3                | %    |

| Output Voltage Swing (Flyback) $V_{O(A)} - V_{O(B)}$                                       | V <sub>O</sub>        | $I_{\text{diff}} = 0.3\text{mA}, I_{\text{O}} = 1.5\text{A}$                                        | _              | 39   | -                | V    |

| Forward Voltage of the Internal<br>Efficiency Diode (V <sub>O(A)</sub> – V <sub>FB</sub> ) | $V_{DF}$              | $I_{O} = -1.5A$ , $I_{diff} = 0.3mA$                                                                | -              | -    | 1.5              | V    |

| Output Offset Current                                                                      | I <sub>OS</sub>       | $I_{diff} = 0$ , $I_{I(sb)} = 50\mu A$ to $500\mu A$                                                | _              | _    | 30               | mA   |

| Offset Voltage at the Input of the Feedback Amplifier $(V_{I(fb)} - V_{O(B)})$             | ΔV <sub>OS</sub> T    | I <sub>diff</sub> = 0                                                                               | _              | -    | 72               | μV/K |

| DC Output Voltage                                                                          | V <sub>O(A)</sub>     | I <sub>diff</sub> = 0, Note 5                                                                       | _              | 8    | -                | V    |

| Open Loop Voltage Gain (V <sub>7–4</sub> /V <sub>1–2</sub> )                               | G <sub>VO</sub>       | Note 6, Note 7                                                                                      | _              | 80   | -                | dB   |

| Open Loop Voltage Gain $(V_{7-4}/V_{9-4}, V_{1-2} = 0)$                                    |                       | Note 6                                                                                              | _              | 80   | -                | dB   |

| Voltage Ratio V <sub>1-2</sub> /V <sub>9-4</sub>                                           | V <sub>R</sub>        |                                                                                                     | -              | 0    | _                | dB   |

| Frequency Response (-3dB)                                                                  | f <sub>res</sub>      | Open Loop, Note 8                                                                                   | _              | 40   | _                | Hz   |

| Current Gain (I <sub>O</sub> /I <sub>diff</sub> )                                          | G <sub>I</sub>        |                                                                                                     | _              | 5000 | _                |      |

| Current Gain Drift as a Function of Temperature                                            | ∆G <sub>C</sub> T     |                                                                                                     | -              | -    | 10 <sup>-4</sup> | K    |

| Signal Bias Current                                                                        | I <sub>I(sb)</sub>    |                                                                                                     | 50             | 400  | 500              | μΑ   |

| Flyback Supply Current                                                                     | I <sub>FB</sub>       | During Scan                                                                                         | -              | _    | 100              | μΑ   |

| Power Supply Ripple Rejection                                                              | PSRR                  | Note 9                                                                                              | -              | 80   | _                | dB   |

| DC Input Voltage                                                                           | V <sub>I(DC)</sub>    |                                                                                                     | _              | 2.7  | _                | V    |

| Common Mode Input Voltage                                                                  | V <sub>I(CM)</sub>    | $I_{I(sb)} = 0$                                                                                     | 0              | _    | 1.6              | V    |

| Input Bias Current                                                                         | I <sub>bias</sub>     | $I_{I(sb)} = 0$                                                                                     | _              | 0.1  | 0.5              | μΑ   |

| Common Mode Output Current                                                                 | I <sub>O(CM)</sub>    | $\begin{array}{l} \Delta I_{I(sub)} = 300 \mu A_{(P-P)},  f_i = 50 Hz, \\ I_{diff} = 0 \end{array}$ | _              | 0.2  | _                | mA   |

| Guard Circuit                                                                              |                       | •                                                                                                   | _              | •    |                  |      |

| Output Current                                                                             | I <sub>O</sub>        | Not Active, V <sub>O(guard)</sub> = 0V                                                              | _              | _    | 50               | μА   |

|                                                                                            |                       | Active, V <sub>O(guard)</sub> = 3.6V                                                                | 1.0            | _    | 2.5              | mA   |

| Output Voltage on Pin8                                                                     | V <sub>O(guard)</sub> | I <sub>O</sub> = 100μA                                                                              | 4.6            | _    | 5.5              | V    |

| Allowable Voltage on Pin8                                                                  |                       | Maximum Leakage Current = 10μΑ                                                                      | _              | _    | 40               | V    |

#### Notes:

- Note 1. A flyback supply voltage of > 50V up to 60V is allowed in application. A 22–nF capacititor in series with a  $22\Omega$  resistor (depending on  $I_O$  and the inductance of the coil) has to be connected between Pin7 and GND. The decoupling capacitor of  $V_{FB}$  has to be connected between Pin6 and Pin3. This supply voltage line must have a resistance of  $33\Omega$ .

- Note 4. The linearity error is measured without S-correction and based on the same measurement principle as performed on the screen. The measuring method is as follows:

Divide the output signal I<sub>4</sub> I<sub>7</sub> (V<sub>RM</sub>) into 22 equal parts ranging from 1 to 22 inclusive. Measure the value of two succeeding parts called one block starting with part 2 and 3 (block 1) and ending with part 20 and 21 (block 10). Thus part 1 and 22 are unused. The equations for linearity error for adjacent blocks (LEAB) and linearity error for not adjacent blocks (LENAB) are given below:

$$LEAB = \ \frac{a_k - a_{(k+1)}}{a_{avg}} \ ; LEAB = \ \frac{a_{max} - a_{min}}{a_{avg}}$$

- Note 5. Referenced to V<sub>P</sub>.

- Note 6. The V values within formulae relate to voltages at or across relative pin numbers, i.e.  $V_{7-4}/V_{1-2} = voltage value across Pin7 and Pin4 divided by voltage value across Pin1 and Pin2.$

- Note 7. V<sub>9-4</sub> AC short-circuited.

- Note 8. Frequency response  $V_{7-4}/V_{9-4}$  is equal to frequency response  $V_{7-4}/V_{1-2}$ .

- Note 9. At  $V_{(ripple)} = 500 \text{mV}$  eff; measured across  $R_M$ ;  $f_i = 50 \text{Hz}$ .