# Data Sheet

NT7711

160 Output LCD Segment/Common Driver

V1.0

| Revision History                          |

|-------------------------------------------|

| Features4                                 |

| General Description                       |

| Pad Configuration                         |

| Block Diagram                             |

| Pad Descriptions                          |

| Functional Descriptions                   |

| Absolute Maximum Rating24                 |

| Electrical Characteristics24              |

| Application Circuit (for reference only)3 |

| Bonding Diagram3                          |

| Package Information38                     |

| Ordering Information 39                   |

| NOVATE DISCLOS                            |

## **Revision History**

| NT7711 Specification Revision History |                      |            |  |  |  |  |  |

|---------------------------------------|----------------------|------------|--|--|--|--|--|

| Version                               | Version Content Date |            |  |  |  |  |  |

| 1.0                                   | Original             | July. 2007 |  |  |  |  |  |

#### **Features**

(Segment mode)

■ Shift Clock frequency:

20 MHz (Max.) (VDD =  $5V\pm10\%$ ) 12 MHz (Max.) (VDD =  $2.5V\sim4.5V$ )

- Adopts a data bus system

- 4-bit/8-bit parallel input modes are selected with a mode (MD) pin

- Automatic transfer function with an enable signal

- Automatic counting function which, in the chip select mode causes the internal clock to be stopped by automatically counting 160 bits of input data.

(Common mode)

- Shift clock frequency: 4.0MHz (Max.)

- Adjust AC signal generator (without any external component)

- 2-line ~ 254 line inversion

- 2-line ~ 126 line inversion

Dual mode

- Frame inversion Single and Dual mode

■ Built-in 160-bit bi-directional shift register (divided into 80-bit x 2)

■ Available in a single mode (160-bit shift register) or in a dual mode (80-bit shift register x 2)

$- Y1 \rightarrow Y160$  Single mode  $- Y160 \rightarrow Y1$  Single mode  $- Y1 \rightarrow Y80, Y81 \rightarrow Y160$  Dual mode  $- Y160 \rightarrow Y81, Y80 \rightarrow Y1$  Dual mode

The above 4 shift directions are pin-selectable

(Both segment mode and common mode)

- Supply voltage for LCD drive: 15.0 to 36.0V

- Number of LCD driver outputs: 160

- Low output impedance

- Low power consumption

- Supply voltage for the logic system: +2.5 to +5.5V

- CMOS process

- Not designed or rated as radiation hardened

#### **General Description**

The NT7711 is a 160-bit output segment/common driver LSI suitable for driving the large-scale dot matrix LCD panels used by PDAs, personal computers and workstations. The NT7711 is good as both a segment driver and a common driver, and a low power consuming, high-precision LCD panel display can be assembled using the NT7711. In the segment mode, the data input is selected as a 4-bit parallel input mode or 8-bit parallel input mode by a mode (MD) pin. In common mode, the data input/output pins are bi-directional and the four data shift directions are pin-selectable.

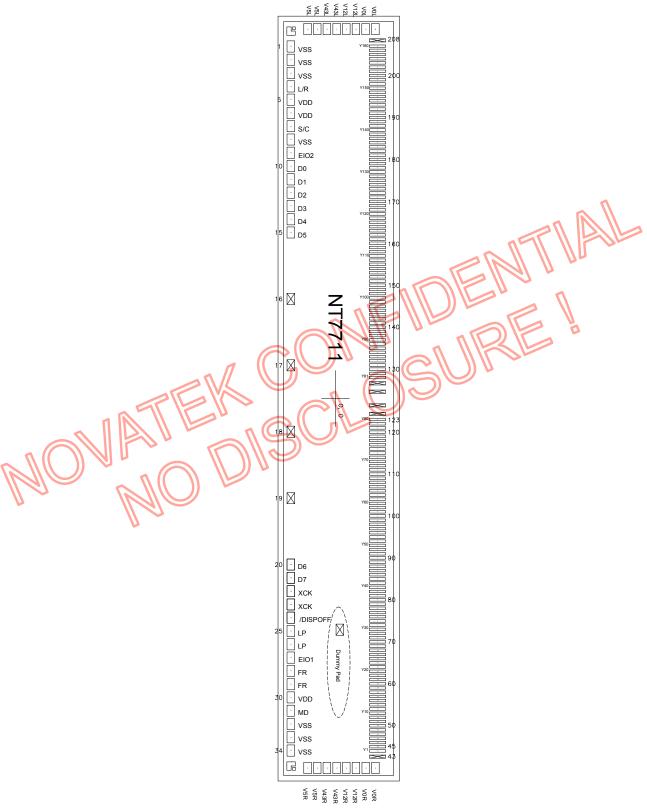

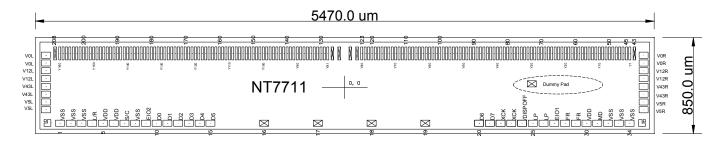

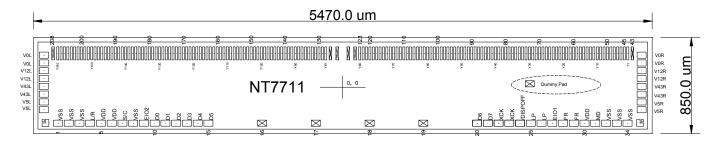

# **Pad Configuration**

2007/07/17 5 Ver 1.0

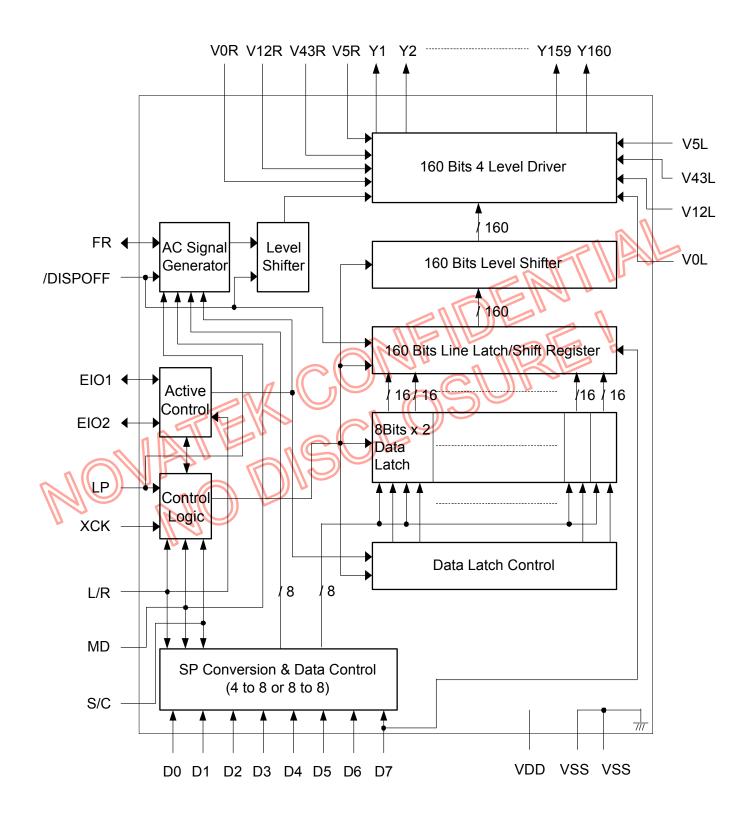

# **Block Diagram**

# **Pad Descriptions**

| Pad No.                  | Designation | I/O | Description                                                    |  |  |  |

|--------------------------|-------------|-----|----------------------------------------------------------------|--|--|--|

| 1~3                      | VSS         | Р   | Ground (0V), these pads must be connected to each other.       |  |  |  |

| 4                        | L/R         | 1   | Display data shift direction selection.                        |  |  |  |

| 5~6                      | VDD         | Р   | Power supply for the logic system (+2.5 to +5.5V).             |  |  |  |

| 7                        | S/C         | 1   | Segment mode/common mode selection.                            |  |  |  |

| 8                        | VSS         | 0   | Ground output for pad option                                   |  |  |  |

| 9                        | EIO2        | I/O | Input/output for chip selection or data of the shift register. |  |  |  |

| 10~15,20                 | D0 ~ D6     | I   | Display data input for segment mode.                           |  |  |  |

| 21                       | D7          | I   | Display data input for Segment mode/ Dual mode data input.     |  |  |  |

| 22~23                    | XCK         | I   | Display data shift clock input for segment mode.               |  |  |  |

| 24                       | /DISPOFF    | I   | Control input for deselect output level.                       |  |  |  |

| 25~26                    | LP          | I   | Latch pulse input/shift clock input for the shift register.    |  |  |  |

| 27                       | EIO1        | I/O | Input/output for chip select or data of the shift register.    |  |  |  |

| 28~29                    | FR          | I/O | AC-converting signal input/output for LCD driver waveform.     |  |  |  |

| 30                       | VDD         | 0   | Power supply output for pad option                             |  |  |  |

| 31                       | MD          | I   | Mode selection input.                                          |  |  |  |

| 32~34                    | VSS         | P   | Ground (0V), these pads must be connected to each other.       |  |  |  |

| 35~36                    | V5R         |     | Power supply for LCD driver.                                   |  |  |  |

| 37~38                    | V43R        | BII | Power supply for LCD driver.                                   |  |  |  |

| 39~40                    | V12R        | Р   | Power supply for LCD driver.                                   |  |  |  |

| 41~42                    | VOR _       | P   | Power supply for LCD driver.                                   |  |  |  |

| 44~123,<br>128~207       | Y1 - Y160   | 0   | LCD driver output.                                             |  |  |  |

| 209~210                  | VOL         | Р   | Power supply for LCD driver.                                   |  |  |  |

| 211~212                  | V12L        | Р   | Power supply for LCD driver.                                   |  |  |  |

| 213~214                  | V43L        | Р   | Power supply for LCD driver.                                   |  |  |  |

| 215~216                  | V5L         | Р   | Power supply for LCD driver.                                   |  |  |  |

| 16~19,43,<br>124~127,208 | Dummy       | х   | Must be no connection.                                         |  |  |  |

## **Functional Descriptions**

#### **Block Description**

#### **Active Control**

In the case of the segment mode, it controls the selection or deselection of the chip. Following an LP signal input, and after the select signal is input, a select signal is generated internally until 160 bits of data have been read in. Once data input has been completed, a select signal for cascade connection is output, and the chip is deselected.

In common mode, it controls the input/output data of bi-directional pins.

#### SP Conversion & Data Control

In segment mode, keep input data which are 2 clocks of XCK at 4-bit parallel mode into latch circuit, or keep input data which are 1 clock of XCK at 8-bit parallel mode into latch circuit, after that they are put on the internal data bus 8 bits at a time.

#### **Data Latch Control**

In the case of the segment mode, it selects the state of the data latch, which reads in the data bus signals. The shift direction is controlled by the control logic. For every 16 bits of data read in, the selection signal shifts one bit, based on the state of the control circuit.

#### **Data Latch**

In the case of the segment mode, it latches the data on the data bus. The latched state of each LCD driver output pin is controlled by the control logic and the data latch controlling 160 bits of data are read in 20 sets of 8 bits.

#### Line Latch / Shift Register

In the case of the segment mode, all 160 bits that have been read into the data latch are latched on to the falling edge of the LP signal and output to the level shift block simultaneously.

In the case of common mode, it shifts data from the data input pin on the falling edge of the LP signal.

## Level Shifter

The logic voltage signal is level-shifted to the LCD driver voltage level, and output to the driver block.

#### **4-Level Driver**

It drives the LCD driver output pins from the line latch/shift register data, selecting one of 4 levels (V0, V12, V43, V5) based on the S/C, FR and /DISPOFF signals.

#### **Control Logic**

It controls the operation of each block. In the case of the segment mode, when an LP signal has been input, all blocks are reset and the control logic waits for the selection signal output from the active control block. Once the selection signal has been output, operation of the data latch and data transmission are controlled, 160 bits of data are read in, and the chip is deselected.

In common mode, it controls the direction of the data shift.

#### **AC Signal Generator**

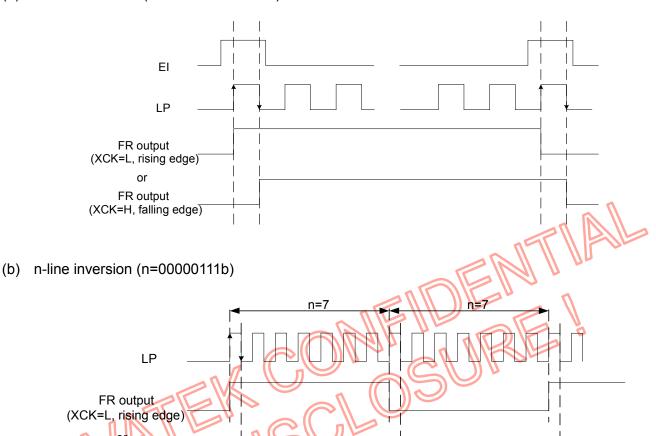

In the case of the common mode, it consists of N-line inversions and frame inversion functions. The AC signal will be transferred to output at the rising edge or the falling edge base on XCK pin setting.

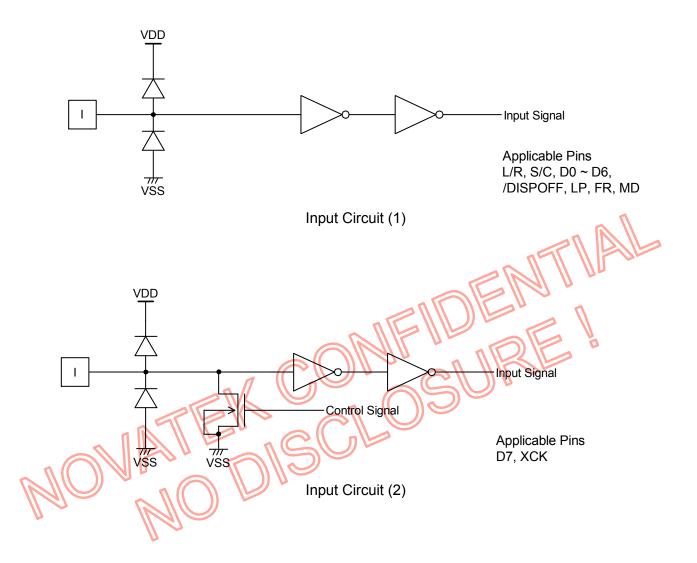

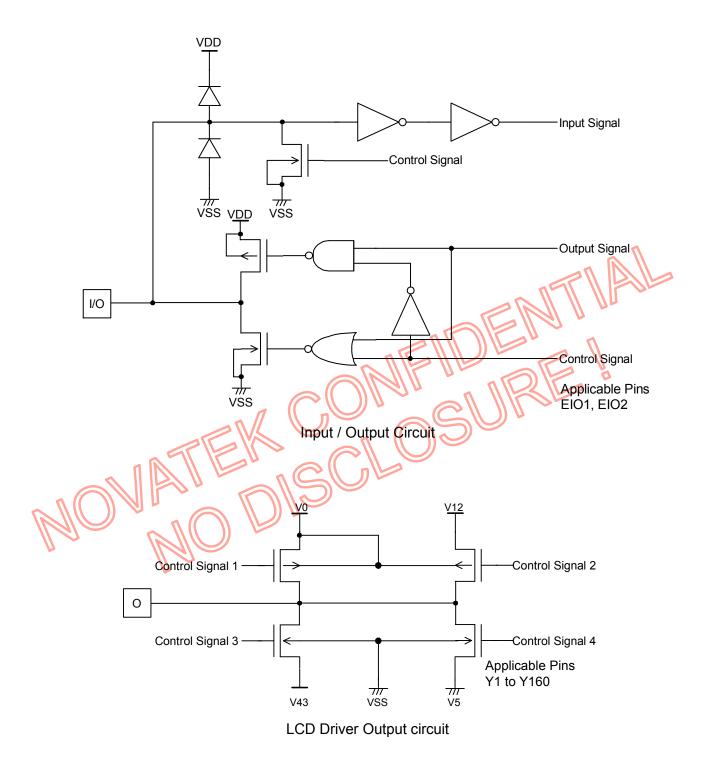

## **Input / Output Circuits**

## **Pad Function**

# Segment mode

| Symbol                                           | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD                                              | Logic system power supply pin connects to +2.5 to +5.5V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VSS                                              | Ground pin connects to 0V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| V0R, V0L<br>V12R, V12L<br>V43R, V43L<br>V5R, V5L | <ul> <li>Power supply pin for LCD driver voltage bias.</li> <li>Normally, the bias voltage used is set by a resistor divider.</li> <li>Ensure that the voltages are set such that VSS ≤ V5 &lt; V43 &lt; V12 &lt; V0.</li> <li>To further reduce the differences between the output waveforms of the LCD driver output pins Y1 to Y160, externally connect ViR and ViL (i = 0, 12, 43, 5).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                             |

| D0 ~ D7                                          | <ul> <li>Input pin for display data.</li> <li>In 4-bit parallel input mode, input data into the 4 pins D0 ~ D3. Connect D4 ~ D7 to VSS or VDD.</li> <li>In 8-bit parallel input mode, input data into the 8 pins D0 ~ D7.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| XCK                                              | Clock input pin for taking display data.  • Data is read on the falling edge of the clock pulse.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| LP                                               | Latch pulse input pin for display data.  • Data is latched on the falling edge of the clock pulse.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| L/R                                              | Direction selection pin for reading display data.  • When set to VSS level "L", data is read sequentially from Y160 to Y1.  • When set to VDD level "H", data is read sequentially from Y1 to Y160.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| VDISPOFF                                         | <ul> <li>Control input pin for output deselect level.</li> <li>The input signal is level-shifted from logic voltage level to LCD driver voltage level, and controls LCD driver circuit.</li> <li>When set to "L", the LCD driver output pins Y1 to Y160 are set to level V5.</li> <li>While /DISPOFF is set to "L", the contents of the line latch are reset, but the display data in the data latch are read regardless of the condition of /DISPOFF. When the /DISPOFF function is canceled, the driver outputs deselect level (V12 or V43), then outputs the contents of the data latch on to the next falling edge of the LP. At that time, if /DISPOFF removal time can not regulate what is shown AC characteristics, can not output the reading data correctly.</li> </ul> |

| FR                                               | <ul> <li>AC signal input for LCD driving waveform.</li> <li>The input signal is level-shifted from the logic voltage level to the driver voltage level, and controls the LCD driver circuit.</li> <li>Normally inputs a frame inversion signal.</li> <li>The LCD driver output pin's output voltage level can be set to the line latch output signal and the FR signal.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                |

| MD                                               | Mode selection pin.  • When set to VSS level "L", 4-bit parallel input mode is set.  • When set to VDD level "H", 8-bit parallel input mode is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

## Segment mode (continuous)

| Symbol     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S/C        | Segment mode / common mode selection pin.  • When set to VDD level "H", segment mode is set.  • When set to VSS level "L", common mode is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| EIO1, EIO2 | <ul> <li>Input/output pin for chip selection.</li> <li>When L/R input is at VSS level "L", EIO1 is set for output, and EIO2 is set for input.</li> <li>When L/R input is at VDD level "H", EIO1 is set for input, and EIO2 is set for output.</li> <li>During output, it is set to "H" while LP*(/XCK) is "H" and after 160-bits of data have been read, it is set to "L" for one cycle (from falling edge to falling edge of XCK), after which it returns to "H".</li> <li>During input, after the LP signal is input, the chip is selected while EI is set to "L". After 160-bits of data have been read, the chip is deselected.</li> </ul> |

| Y1 ~ Y160  | LCD driver output pins  • These correspond directly to each bit of the data latch, and one level (V0, V12, V43, or V5) is selected and the output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

## Common mode

| Symbol                                           | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD                                              | Logic system power supply pin connects to +2.5 to +5.5V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VSS                                              | Ground pin connects to 0V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| V0R, V0L<br>V12R, V12L<br>V43R, V43L<br>V5R, V5L | <ul> <li>Power supply pin for LCD driver voltage bias.</li> <li>Normally, the bias voltage used is set by a resistor divider.</li> <li>Ensure that the voltages are set such that VSS ≤ V5 &lt; V43 &lt; V12 &lt; V0.</li> <li>To further reduce the differences between the output waveforms of the LCD driver output pins Y1 to Y160, externally connect ViR and ViL (i = 0, 12, 43, 5).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                |

| EIO1                                             | <ul> <li>Bi-directional shift register shift data input/output pin.</li> <li>Is an Output pin when L/R is at VSS level "L" and an input pin when L/R is at VDD level "H".</li> <li>When EIO1 is used as an input pin, it will be pulled-down internally.</li> <li>When EIO1 is used as an output pin, it won't be pulled-down internally.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| EIO2                                             | <ul> <li>Bi-directional shift register shift data input/output pin.</li> <li>Is an Input pin when L/R is at VSS level "L" and an output pin when L/R is at VDD level "H".</li> <li>When EIO2 is used as an input pin, it will be pulled-down internally.</li> <li>When EIO2 is used as an output pin, it won't be pulled-down internally.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| LP                                               | Bi-directional shift register shift clock pulse input pin.  • Data is shifted on the falling edge of the clock pulse.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| L/R                                              | <ul> <li>Bi-directional shift register shift direction selection pin.</li> <li>Data is shifted from Y160 to Y1 when it is set to VSS level "L", and data is shifted from Y1 to Y160 when it is set to VDD level "H".</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| /DISPOFF                                         | <ul> <li>Control input pin for output deselect level.</li> <li>The input signal is level-shifted from logic voltage level to LCD driver voltage level, and controls the LCD driver circuit.</li> <li>When set to "L", the LCD driver output pins Y1 to Y160 are set to level V5.</li> <li>While /DISPOFF is set to "L", the contents of the line latch are reset, but the display data in the data latch are read regardless of the condition of /DISPOFF. When the /DISPOFF function is canceled, the driver outputs deselect level (V12 or V43), then outputs the contents of the data latch onto the next falling edge of the LP. At that time, if /DISPOFF removal time can not regulate what is shown AC characteristics, can not output the reading data correctly.</li> </ul> |

| FR                                               | <ul> <li>AC signal input for LCD driving waveform.</li> <li>The input signal is level-shifted from the logic voltage level to the driver voltage level, and controls LCD driver circuit.</li> <li>Normally inputs a frame inversion signal. The LCD driver output pin's output voltage level can be set to the line latch output signal and the FR signal.</li> <li>When AC signal generator circuit is enabled, the AC signal will be output from this pin.</li> </ul>                                                                                                                                                                                                                                                                                                              |

| MD                                               | Mode selection pin.  • When set to VSS level "L", single mode operation is selected. When set to VDD level "H", dual mode operation is selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

## Common mode (continuous)

| Symbol    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S/C       | Segment mode / common mode selection pin.  • When set to VSS level "L", common mode is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| D0~D7     | AC signal generator disable (Data bus D0~D7=00H or FFH)  • When single mode is used, connect D0~D7 to VSS or VDD, to avoid floating.  • When dual mode is used, D7 is dual mode data input pin, according to the data shift direction of the data shift register, data can be input starting from the 81 <sup>st</sup> bit. Connect D0~D6 to VSS or VDD, to avoid floating.  AC signal generator enable (Data bus D0~D7=01H to FEH)  • When single mode is used, use D0~D7 pins to set the N-Line inversion data.  • When dual mode is used, use D0~D6 pins to set the N-Line inversion data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| XCK       | AC signal generator disable (Data bus D0~D7=00H or FFH)  • Connect XCK to VSS or VDD, to avoid floating.  AC signal generator enable (Data bus D0~D7=01H to FEH)  • XCK="L": AC signal output at LP rising edge.  • XCK="H": AC signal output at LP falling edge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Y1 ~ Y160 | LCD driver output pins.  • These correspond directly to each bit of the data latch, and one level (V0, V12, V43, or V5) is selected and the output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| MO        | JATER OS VARIONS DE LA CIOSA DEL CIOSA DE LA CIOSA DEL CIOSA DE LA CIOSA DEL CIOSA DEL CIOSA DE LA CIOSA DEL CIOSA DE LA CIOSA DEL |

#### **LCD Driver Output Voltage Level**

The relationship amongst the data bus signal, AC converted signal FR and LCD driver output voltage is shown in the table below:

#### Segment Mode

| FR | Latch Data | /DISPOFF | Driver Output Voltage Level (Y1 ~ Y160) |

|----|------------|----------|-----------------------------------------|

| L  | L          | Н        | V43                                     |

| L  | Н          | Н        | V5                                      |

| Н  | L          | Н        | V12                                     |

| Н  | Н          | Н        | V0                                      |

| Х  | Х          | L        | V5                                      |

Here, VSS ≤ V5 < V43 < V12 < V0, H: VDD (+2.5 to +5.5V), L: VSS (0V), X: Don't care

#### Common Mode

| FR | Latch Data | /DISPOFF | Driver Output Voltage Level (Y1 ~ Y160) |

|----|------------|----------|-----------------------------------------|

| L  | L          | Н        | V43                                     |

| L  | Н          | Н        | VO                                      |

| Н  | L          | F        | V12                                     |

| Н  | H          |          | V5                                      |

| X  | X          | L        | V5                                      |

Here, VSS ≤ V5 < V43 < V12 < V0, H: VDD (+2.5 to +5.5V), L: VSS (0V), X: Don't care

Note: There are two kinds of power supply (logic level voltage, LCD driver voltage) for the LCD driver. Please supply regular voltage, which is assigned by specification for each power pin.

At that time "Don't care" should be fixed to "H" or "L" to avoid floating.

## Relationship between Display Data and Driver Output Pins

Segment Mode

## (a) 4-bit Parallel Mode

| MD   | L/R      | EIO1   | EIO1     | EIO1   | EIO1            | EIO1            | 1 EIO2          | Data | Number of Clock  |                  |                  |      |  |  |

|------|----------|--------|----------|--------|-----------------|-----------------|-----------------|------|------------------|------------------|------------------|------|--|--|

| IVID | L/K      |        | EIOZ     | Input  | 1 <sup>st</sup> | 2 <sup>nd</sup> | 3 <sup>rd</sup> | ~    | 38 <sup>th</sup> | 39 <sup>th</sup> | 40 <sup>th</sup> |      |  |  |

|      |          |        |          | D0     | Y157            | Y153            | Y149            | ~    | Y9               | Y5               | Y1               |      |  |  |

| LLL  | O. 45. 4 | loout  | D1       | Y158   | Y154            | Y150            | ١               | Y10  | Y6               | Y2               |                  |      |  |  |

|      | <b>L</b> | Output | it Input | D2     | Y159            | Y155            | Y151            | ٧    | Y11              | Y7               | Y3               |      |  |  |

|      |          |        |          | D3     | Y160            | Y156            | Y152            | ~    | Y12              | Y8               | Y4               |      |  |  |

|      |          |        |          | D0     | Y4              | Y8              | Y12             | ~    | Y152             | Y156             | Y160             |      |  |  |

| LH   | المورية  | Input  | loout    | Output | D1              | Y3              | Y7              | Y11  | ~                | Y151             | Y155             | Y159 |  |  |

|      | '7       | Input  | Output   | D2     | Y2              | Y6              | Y10             | ~    | Y150             | Y154             | Y158             |      |  |  |

|      |          |        | D3       | Y1     | Y5              | Y9              | ~               | Y149 | Y153             | Y157             |                  |      |  |  |

## (b) 8-bit Parallel Mode

| MD L/R EIO1 EIO2 Data Number of Clock |     |        |              |       |                 |                 |                 |     |                  |                  |                         |     |      |      |      |

|---------------------------------------|-----|--------|--------------|-------|-----------------|-----------------|-----------------|-----|------------------|------------------|-------------------------|-----|------|------|------|

| IVID                                  | L/K | LIOI   | LIOZ         | Input | 1 <sup>st</sup> | 2 <sup>nd</sup> | 3 <sup>rd</sup> |     | 18 <sup>th</sup> | 19 <sup>th</sup> | <b>20</b> <sup>th</sup> |     |      |      |      |

|                                       |     |        |              | D0    | Y153            | Y145            | Y137            | ~ < | Y17              | <b>Y</b> 9       | Y1                      |     |      |      |      |

|                                       |     |        |              | D1    | Y154            | Y146            | Y138            | ~   | Y18              | Y10              | Y2                      |     |      |      |      |

|                                       |     |        |              | D2    | Y155            | Y147            | Y139            | 1   | <b>Y</b> 19      | Y11              | Y3                      |     |      |      |      |

| Н                                     | ,   | Output | Input        | D3    | Y156            | Y148            | Y140            | ~   | Y20              | Y12              | Y4                      |     |      |      |      |

| ''                                    | -   | diput  | Iliput       | D4    | Y157            | Y149            | Y141            | ~   | Y21              | Y13              | Y5                      |     |      |      |      |

|                                       | Re  |        | 711 -        | D5    | Y158            | Y150            | Y142            | ~   | Y22              | Y14              | Y6                      |     |      |      |      |

| n = n                                 |     | ار ال  |              | D6    | Y159            | Y151            | Y143            | ~   | Y23              | Y15              | Y7                      |     |      |      |      |

|                                       |     |        |              | D     | Y160            | Y152            | Y144            | ~   | Y24              | Y16              | Y8                      |     |      |      |      |

| 11 0                                  |     | 18     |              | D0    | Y8              | Y16             | Y24             | ~   | Y144             | Y152             | Y160                    |     |      |      |      |

|                                       |     | Input  | //           | //    | //              | 11              | 9               | D1  | Y7               | Y15              | Y23                     | ~   | Y143 | Y151 | Y159 |

|                                       |     |        |              |       |                 |                 |                 |     |                  | D2               | Y6                      | Y14 | Y22  | ~    | Y142 |

| Н                                     | Н   |        | Output       | D3    | Y5              | Y13             | Y21             | ~   | Y141             | Y149             | Y157                    |     |      |      |      |

| ''                                    |     |        | Input Output | D4    | Y4              | Y12             | Y20             | ~   | Y140             | Y148             | Y156                    |     |      |      |      |

|                                       |     |        |              | D5    | Y3              | Y11             | Y19             | ~   | Y139             | Y147             | Y155                    |     |      |      |      |

|                                       |     |        |              | D6    | Y2              | Y10             | Y18             | ~   | Y138             | Y146             | Y154                    |     |      |      |      |

|                                       |     |        |              | D7    | Y1              | Y9              | Y17             | ~   | Y137             | Y145             | Y153                    |     |      |      |      |

#### Common Mode

| MD            | L/R                | Data Transfer Direction  | EIO1   | EIO2   | D7    |

|---------------|--------------------|--------------------------|--------|--------|-------|

| L<br>(Single) | L (shift to left)  | Y160 to Y1               | Output | Input  | Х     |

|               | H (shift to right) | Y1 to Y160               | Input  | Output | Х     |

| H<br>(Dual)   | L (shift to left)  | Y160 to Y81<br>Y80 to Y1 | Output | Input  | Input |

|               | H (shift to right) | Y1 to Y80<br>Y81 to Y160 | Input  | Output | Input |

Here, L: VSS (0V), H: VDD (+2.5V to +5.5V), X: Don't care

Note: "Don't care" should be fixed to "H" or "L" to avoid floating.

## AC signal Generator Function

(a) Single Mode

| FR     |    |    |       | Data Input           |           |     |               | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |          |       | Selected n-line    |  |

|--------|----|----|-------|----------------------|-----------|-----|---------------|---------------------------------------|----------|-------|--------------------|--|

| I K    | D7 | D6 | D5    | D5 D4 D3 D2 D1 D0 X0 |           | XCK | XCK inversion |                                       |          |       |                    |  |

| Input  | L  | L  | L     | 7                    | (L        |     | L             |                                       |          | 11 2. | Disable            |  |

| Output | L  | L  |       |                      |           | L   | 4             | 닢                                     | ))<br>() | Η     | Frame inversion    |  |

| Output | L  | 7  | 1     | 7                    |           | (B) | H             | )<br>ブ                                | لــ      | Η     | 2-line inversion   |  |

| Output | 4  |    | \\L\\ | Г                    |           |     | H             | Н                                     | L        | Н     | 3-line inversion   |  |

| 6      |    |    |       |                      | <u>()</u> |     | •             | . • •                                 |          | •     |                    |  |

| Output |    | H  | H     | Ŧ                    | Ŧ         | Н   | L             | Ι                                     | Ш        | Н     | 253-line inversion |  |

| Output | Н  | ¥  | H     | I                    | Η         | Н   | Н             | اــا                                  | L        | Η     | 254-line inversion |  |

| Input  | Н  | H  | 7 H   | Н                    | Н         | Н   | Н             | Н                                     | L        |       | Disable            |  |

## (b) Dual Mode

| FR     | Data Input LP↑ LP |    |    |    |    |    | LP↓ | Selected n-line |     |     |                    |  |

|--------|-------------------|----|----|----|----|----|-----|-----------------|-----|-----|--------------------|--|

| ΓN     | D7                | D6 | D5 | D4 | D3 | D2 | D1  | D0              | XCK | XCK | inversion          |  |

| Input  | *                 | L  | Ш  | L  | L  | L  | L   | L               | L   | =   | Disable            |  |

| Output | *                 | L  | Ш  | L  | L  | L  | L   | Н               | L   | Н   | Frame inversion    |  |

| Output | *                 | L  | L  | L  | L  | L  | Н   | L               | L   | Н   | 2-line inversion   |  |

| Output | *                 | L  | L  | L  | L  | L  | Н   | Н               | L   | Н   | 3-line inversion   |  |

| :      | :                 | :  | :  |    |    | :  | :   |                 | :   | :   | :                  |  |

| Output | *                 | Н  | Н  | Н  | Н  | Н  | L   | Н               | L   | Н   | 125-line inversion |  |

| Output | *                 | Н  | Н  | Н  | Н  | Н  | Н   | L               | L H |     | 126-line inversion |  |

| Input  | *                 | Н  | Н  | Н  | Н  | Н  | Н   | Н               | L   |     | Disable            |  |

Note: "\*" D7 is dual mode data input pin.

Timing waveform for AC signal generator

FR output XCK=H,falling edge)

## (a) Frame inversion (D0~D7=00000001b)

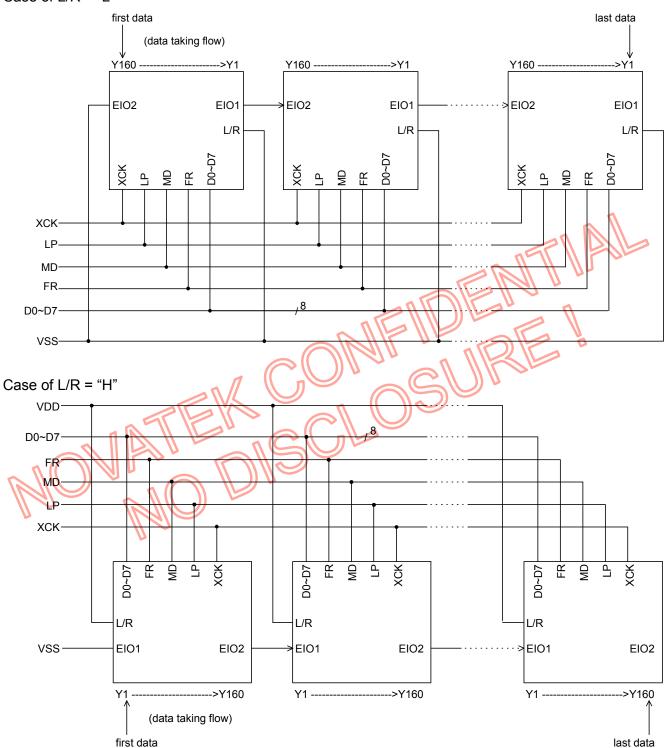

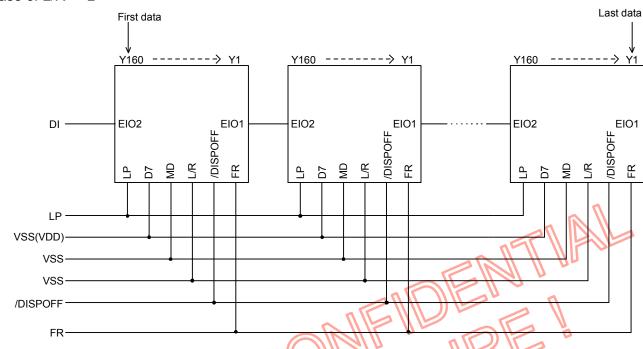

## **Connection Examples of Segment Drivers**

Case of L/R = "L"

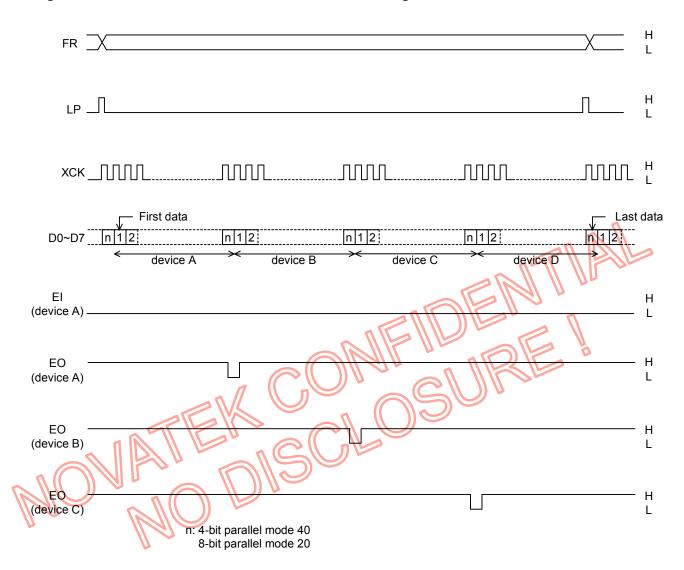

## **Timing Waveform of 4-Device Cascade Connection of Segment Drivers**

## **Connection Examples for Common Drivers**

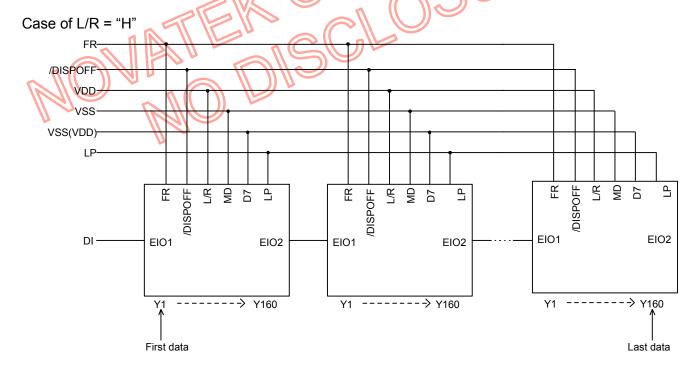

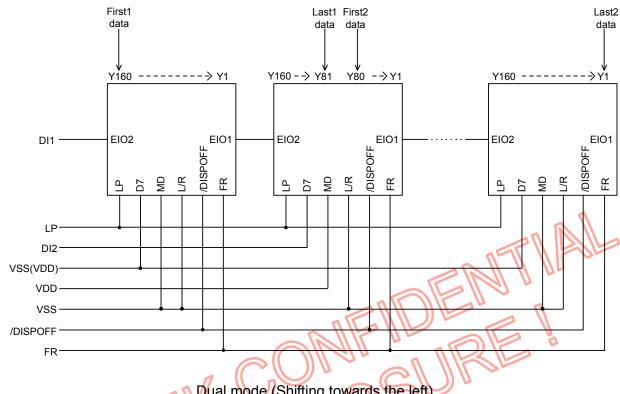

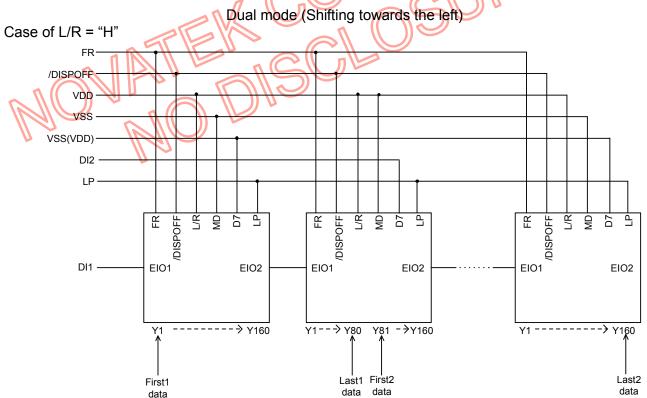

Case of L/R = "L"

Single Mode (Shifting towards the left)

Single Mode (Shifting towards the right)

#### Case of L/R = "L"

Dual mode (Shifting towards the right)

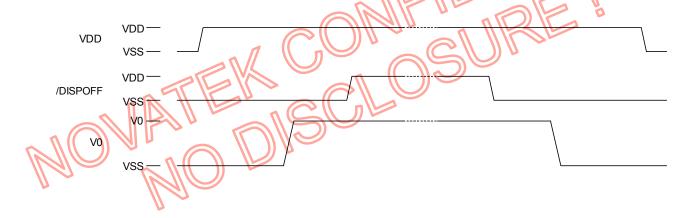

#### **Precaution**

Be careful when connecting or disconnecting the power.

This LSI has a high-voltage LCD driver, so it may be permanently damaged by a high current, which may occur, if voltage is supplied to the LCD driver power supply while the logic system power supply is floating.

The details are as follows:

- When connecting the power supply, connect the LCD driver power after connecting the logic system power. Furthermore, when disconnecting the power, disconnect the logic system power after disconnecting the LCD driver power.

- We recommend that you connect a serial resistor (50 ~ 100  $\Omega$ ) or fuse to the LCD driver power V0 of the system as a current limiting device. Also, set a suitable value for the resistor in consideration of the LCD display grade.

In addition, when connecting the logic power supply, the logic condition of the LSI inside is insecure. Therefore connect the LCD driver power supply after resetting the logic condition of this LSI inside on DISPOFF function. After that, the /DISPOFF cancels the function after the LCD driver power supply has become stable. Furthermore, when disconnecting the power, set the LCD driver output pins to level VSS on the /DISPOFF function. After that, disconnect the logic system power after disconnecting the LCD driver power.

When connecting the power supply, follow the recommended sequence shown here.

#### **Absolute Maximum Rating**

| DC Supply Voltage VDD         | 0.3V to 7.0V      |

|-------------------------------|-------------------|

| DC Supply Voltage V0          | 0.3V to +38.0V    |

| Input Voltage (Vin)           | 0.3V to VDD +0.3V |

| Operating Ambient Temperature | 30°C to +85°C     |

| Storage Temperature           | 45°C to +125°C    |

<sup>\*</sup>Comments

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to this device. These are stress ratings only. Functional operation of this device under these or any other conditions above those indicated in the operational sections of this specification is not implied or intended. Exposure to the absolute maximum rating conditions for extended periods may affect device reliability.

#### **Electrical Characteristics**

#### **DC Characteristics**

Segment Mode (VSS=V5=0V, VDD=2.5~5.5V, V0=15~36V, Ta = -30 to +85°C, unless otherwise noted)

| Symbol | Parameter                          | Min.         | Тур. | Max.         | Unit |                                                                             | Condition                |  |

|--------|------------------------------------|--------------|------|--------------|------|-----------------------------------------------------------------------------|--------------------------|--|

| VDD    | Operating Voltage                  | 2.5          | 1    | 5.5          | V    |                                                                             |                          |  |

| V0     | Operating Voltage                  | 15           |      | 36           | K    |                                                                             |                          |  |

| VIH    | Input high voltage                 | 0.8 X<br>VDD |      |              | V    | D0 ~ D7, XCK                                                                | K, LP, L/R, FR, MD, S/C, |  |

| VIL    | Input low voltage                  |              |      | 0.2 X<br>VDD | Y    | ElO1, ElO2 a                                                                | nd /DISPOFF pins         |  |

| VOH    | Output high voltage                | VDD -<br>0.4 |      | -            | V    | EIO1, EIO2 pins, IOH = -0.4mA                                               |                          |  |

| VOL    | Output low voltage                 |              | -    | +0.4         | ٧    | EIO1, EIO2 pins, IOL = +0.4mA                                               |                          |  |

| IIH    | Input leakage current 1            | ı            | ı    | +1.0         | μΑ   | D0 ~ D7, XCK, LP, L/R, FR, MD, S/C, EIO1, EIO2 and /DISPOFF pins, Vin = VDD |                          |  |

| IIL    | Input leakage current 2            | -            | -    | -1.0         | μΑ   | D0 ~ D7, XCK, LP, L/R, FR, MD, S/C, EIO1, EIO2 and /DISPOFF pins, Vin = VSS |                          |  |

| DON    | Output registance                  | -            | 1.0  | 1.5          | ΚΩ   | V0 = +36V                                                                   | Y1 ~ Y160 pins,          |  |

| RON    | Output resistance                  | -            | 1.5  | 2.0          | ΚΩ   | V0 = +30V                                                                   | ∆VON  = 0.5V             |  |

| ISB    | Stand-by current                   | -            | -    | 5.0          | μΑ   | VSS pin, Note 1                                                             |                          |  |

| IDD1   | Consumed current 1 (Non-selection) | -            | -    | 0.5          | mA   | VDD pin, Note 2                                                             |                          |  |

| IDD2   | Consumed current 2 (Selection)     | -            | -    | 1.0          | mA   | VDD pin, Note 3                                                             |                          |  |

| 10     | Consumed current                   | -            | -    | 0.5          | mA   | V0 pin, Note 4                                                              | 4                        |  |

Common Mode (VSS=V5=0V, VDD=2.5~5.5V, V0=15~36V, Ta = -30 to +85°C, unless otherwise noted)

| Symbol | Parameter                  | Min.         | Тур. | Max.         | Unit     | Condition                                                                         |

|--------|----------------------------|--------------|------|--------------|----------|-----------------------------------------------------------------------------------|

| VDD    | Operating Voltage          | 2.5          | -    | 5.5          | V        |                                                                                   |

| V0     | Operating Voltage          | 15           | 1    | 36           | ٧        |                                                                                   |

| VIH    | Input high voltage         | 0.8 X<br>VDD | -    | -            | V        | D0 ~ D7, XCK, LP, L/R, FR, MD, S/C,                                               |

| VIL    | Input low voltage          | ı            | 1    | 0.2 X<br>VDD | V        | EIO1, EIO2 and /DISPOFF pins                                                      |

| VOH    | Output high voltage        | VDD -<br>0.4 | ı    | ı            | ٧        | EIO1, EIO2, FR pins, IOH = -0.4mA                                                 |

| VOL    | Output low voltage         | 1            | 1    | +0.4         | <b>V</b> | EIO1, EIO2, FR pins, IOL = +0.4mA                                                 |

| IIH    | Input leakage<br>current 1 | -            | -    | +1.0         | μΑ       | D0 ~ D7, XCK, LP, L/R, FR, MD, S/C,<br>EIO1, EIO2 and /DISPOFF pins,<br>Vin = VDD |

| IIL    | Input leakage<br>current 2 | ı            | ı    | -1.0         | μA       | D0 ~ D7, XCK, LP, L/R, FR, MD, S/C,<br>EIO1, EIO2 and /DISPOFF pins,<br>Vin = VSS |

| IPD    | Input pull down current    | ı            |      | 100          | pΑ       | EIO1, EIO2, D7 pins                                                               |

| RON    | Output resistance          | N.           | 1.5  | 1.5          |          | V0 = +36V Y1 ~ Y160 pins,<br>$V0 = +30V$ $ \Delta VON  = 0.5V$                    |

| ISB    | Stand-by current           |              |      | 57           | μA       | VSS pin, Note 5                                                                   |

| IDD    | Consumed current 1         | (F)          |      | 80           | μΑ       | VDD pin, Note 6                                                                   |

| 10     | Consumed current 2         |              | -    | 160          | μΑ       | V0 pin, Note 6                                                                    |

#### Notes:

- 1. VDD = +5.0V, V0 = +36V, Vin = VSS

- 2. VDD = +5.0V, V0 = +36V, fXCK = 20MHz, No-load, EIO = VDD

The input data is turned over by data taking clock (4-bit parallel input mode)

- 3. VDD = +5.0V, V0 = +36V, fXCK = 20MHz, No-load. EIO = VSS The input data is turned over by data taking clock (4-bit parallel input mode)

- 4. VDD = +5.0V, V0 = +36V, fXCK = 20MHz, fLP = 41.6kHz. fFR = 80Hz, No-load The input data is turned over by data taking clock (4-bit parallel-input mode)

- 5. VDD = +5.0V, V0 = +36V, Vin = VSS

- 6. VDD = +5.0V, V0 = +36V, fLP = 41.6KHz, fFR = 80Hz, in case of 1/480 duty operation, no-load

#### **AC Characteristics**

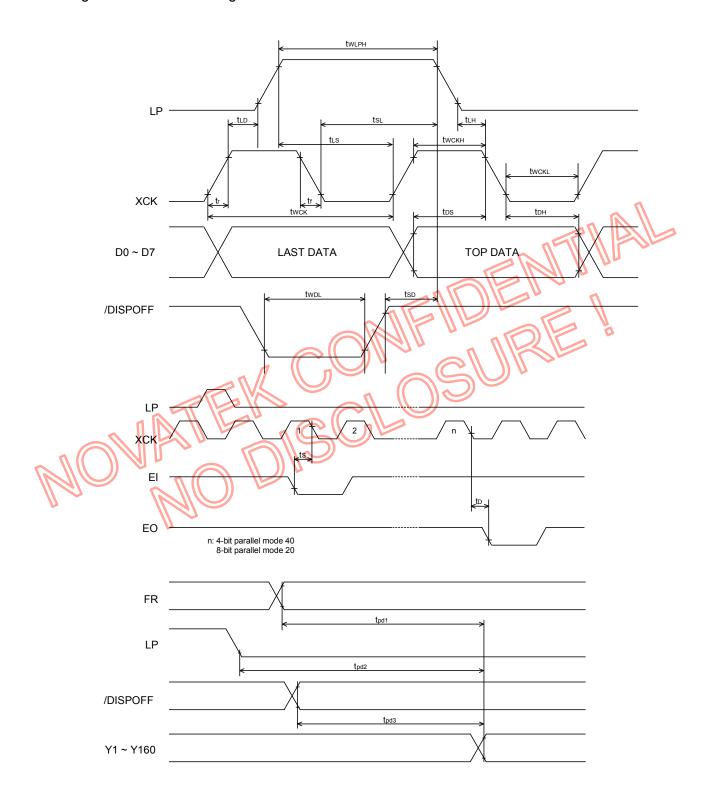

# 1. Timing Characteristics of Segment Mode

Segment Mode 1 (VSS=V5=0V, VDD=4.5~5.5V, V0=15~36V, Ta = -30~+85°C, unless otherwise noted)

| Parameter                                 | Symbol                              | Min. | Тур.  | Max. | Unit | Condition                               |

|-------------------------------------------|-------------------------------------|------|-------|------|------|-----------------------------------------|

| Shift clock period                        | twcĸ                                | 50   | -     |      | ns   | tr, tf ≤ 10ns, Note 1                   |

| Shift clock "H" pulse width               | twcкн                               | 15   | -     |      | ns   |                                         |

| Shift clock "L" pulse width               | twcĸL                               | 15   | -     |      | ns   |                                         |

| Data setup time                           | tos                                 | 10   | -     |      | ns   |                                         |

| Data hold time                            | tон                                 | 12   | -     |      | ns   |                                         |

| Latch pulse "H" pulse width               | twlph                               | 15   | -     |      | ns   |                                         |

| Shift clock rise to Latch pulse rise time | tld                                 | 0    | -     |      | ns   |                                         |

| Shift clock fall to Latch pulse fall time | tsL                                 | 30   | -     |      | ns   | 70                                      |

| Latch pulse rise to Shift clock rise time | t∟s                                 | 25   | -     |      | ns   |                                         |

| Latch pulse fall to Shift clock fall time | tьн                                 | 25   | -     |      | ns   | / // // // // // // // // // // // // / |

| Input signal rise time                    | tr                                  |      | -70 5 | 50   | ns   | Note 2                                  |

| Input signal fall time                    | t <sub>f</sub>                      | n [  |       | 50   | ns   | Note 2                                  |

| Enable setup time                         | ts                                  | 20   | / - n | . 1  | ns   |                                         |

| /DISPOFF Removal time                     | tsp                                 | 100  |       | 0    | ns   |                                         |

| /DISPOFF enable pulse width               | twoL                                | 1.2  | John  |      | μs   |                                         |

| Output delay time (1)                     | to to                               |      |       | 30   | ns   | CL=15pF                                 |

| Output delay time (2)                     | t <sub>pd1</sub> , t <sub>pd2</sub> |      | -     | 1.2  | μs   | CL=15pF                                 |

| Output delay time (3)                     | t <sub>pd3</sub>                    |      | -     | 1.2  | μs   | CL=15pF                                 |

#### Note

- 1. Take the cascade connection into consideration.

- 2. (twcк twcкн twcкL)/2 is the maximum in the case of high speed operation.

## Segment Mode 2 (VSS=V5=0V, VDD=2.5~4.5V, V0=15~36V, Ta=-30~+85°C, unless otherwise noted)

| Parameter                                 | Symbol                              | Min.   | Тур.       | Max. | Unit | Condition             |

|-------------------------------------------|-------------------------------------|--------|------------|------|------|-----------------------|

| Shift clock period                        | twcĸ                                | 82     | -          |      | ns   | tr, tf ≤ 10ns, Note 1 |

| Shift clock "H" pulse width               | twскн                               | 28     | -          |      | ns   |                       |

| Shift clock "L" pulse width               | twcĸL                               | 28     | -          |      | ns   |                       |

| Data setup time                           | tos                                 | 20     | -          |      | ns   |                       |

| Data hold time                            | tон                                 | 23     | -          |      | ns   |                       |

| Latch pulse "H" pulse width               | twlph                               | 30     | -          |      | ns   |                       |

| Shift clock rise to Latch pulse rise time | tld                                 | 0      | -          |      | ns   |                       |

| Shift clock fall to Latch pulse fall time | ts∟                                 | 65     | -          |      | ns   |                       |

| Latch pulse rise to Shift clock rise time | t∟s                                 | 30     | -          |      | ns   |                       |

| Latch pulse fall to Shift clock fall time | tьн                                 | 35     | -          |      | ns   |                       |

| Input signal rise time                    | tr                                  |        | 700        | 50   | ns   | Note 2                |

| Input signal fall time                    | t <sub>f</sub>                      | 2 11/2 |            | 50   | ns   | Note 2                |

| Enable setup time                         | ts                                  | 30     | <i>\\\</i> | 7 7  | ns   |                       |

| /DISPOFF Removal time                     | tsp                                 | 100    | <u>-</u> C |      | ns   |                       |

| /DISPOFF enable pulse width               | twoL                                | 1.2    | ) (        |      | μs   |                       |

| Output delay time (1)                     | to                                  |        | )          | 57   | ns   | CL=15pF               |

| Output delay time (2)                     | t <sub>pd1</sub> , t <sub>pd2</sub> | 7      | -          | 1.2  | μs   | CL=15pF               |

| Output delay time (3)                     | t <sub>pd3</sub>                    |        | -          | 1.2  | μs   | CL=15pF               |

# Note

- 1. Take the cascade connection into consideration.

- 2. (twcк twcкн twcкL)/2 is the maximum in the case of high speed operation.

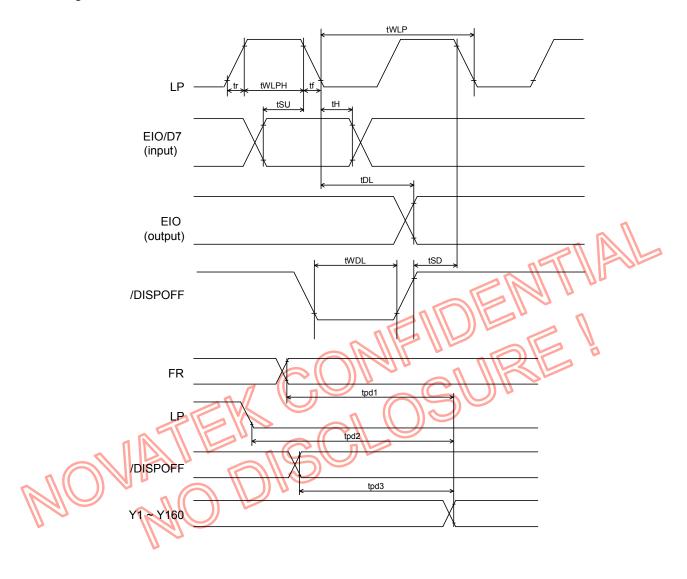

## 2. Timing Characteristics of Common Mode

Common Mode (VSS=V5=0V, VDD=2.5~5.5V, V0=15~36V, Ta=-30~+85°C, unless otherwise noted)

| Parameter                                     | Symbol                              | Min. | Тур. | Max. | Unit | Condition                              |  |  |

|-----------------------------------------------|-------------------------------------|------|------|------|------|----------------------------------------|--|--|

| Shift clock period                            | twlp                                | 250  | -    | -    | ns   | t <sub>r</sub> , t <sub>f</sub> ≤ 20ns |  |  |

| Shift clock "H" pulse width                   | twlph                               | 15   | -    | -    | ns   | VDD=5.0V±10%                           |  |  |

| Offit clock 11 pulse width                    | LWLPH                               | 30   | -    | -    | ns   | VDD=2.5~4.5V                           |  |  |

| Data setup time                               | tsu                                 | 30   | -    | -    | ns   |                                        |  |  |

| Data hole time                                | tн                                  | 50   | -    | -    | ns   |                                        |  |  |

| Input signal rise time                        | tr                                  |      | -    | 50   | ns   |                                        |  |  |

| Input signal fall time                        | t <sub>f</sub>                      |      | -    | 50   | ns   |                                        |  |  |

| /DISPOFF Removal time                         | tsp                                 | 100  | -    | -    | ns   |                                        |  |  |

| /DISPOFF enable pulse width                   | twdL                                | 1.2  | -    | -    | μs   |                                        |  |  |

| Output delay time (1)                         | to∟                                 | -    | -    | 200  | ns   | CL=15pF                                |  |  |

| Output delay time (2)                         | t <sub>pd1</sub> , t <sub>pd2</sub> | -    | -    | 1.2  | μs   | CL=15pF                                |  |  |

| Output delay time (3)                         | t <sub>pd3</sub>                    | - (  |      | 1.2  | μs   | CL=15pF                                |  |  |

| Output delay time (3)  tpd3  - 1.2 µs CL=15pF |                                     |      |      |      |      |                                        |  |  |

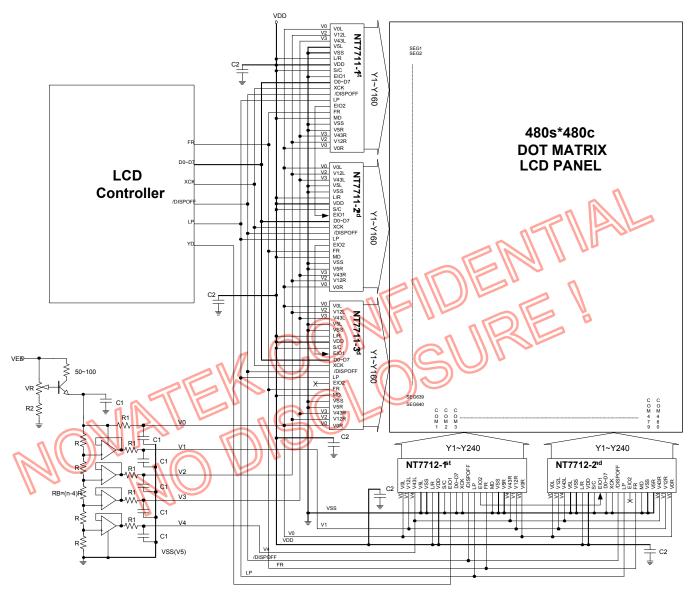

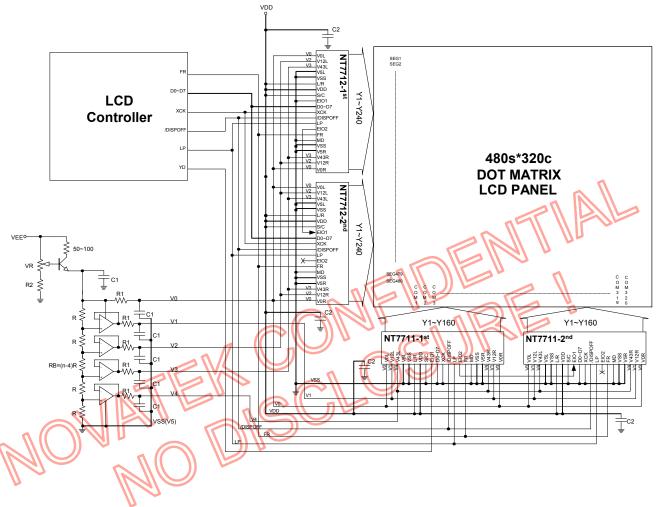

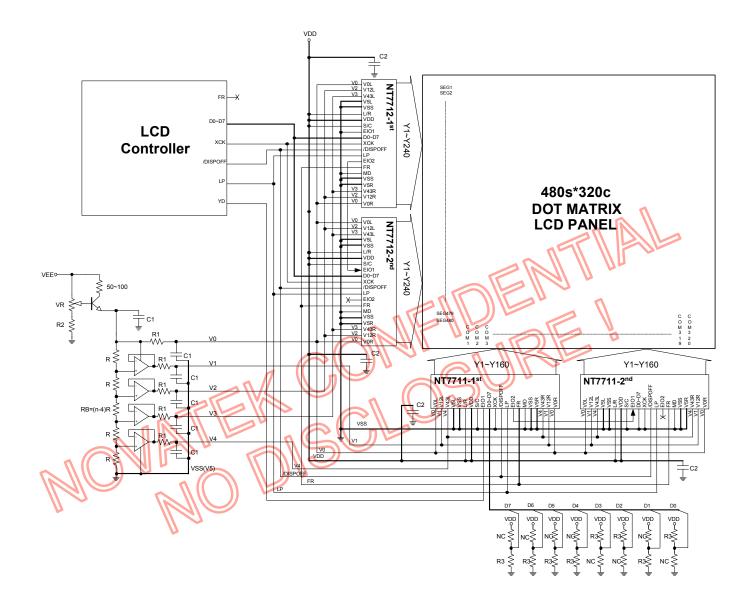

## **Application Circuit (for reference only)**

Segment Mode: (L/R=H \ 8bit mode)

#### Note

1. R=20KΩ~100KΩ

Example of RB & R:

$$\rightarrow$$

If R =20KΩ, bias=1/22, duty =1/480

$\rightarrow$  RB =(22-4)\*20KΩ

=360KΩ

- 2. VR=50KΩ, R2=22KΩ(Adjust VR & R2 to get best range and contrast)

- 3. C1=2.2~4.7 $\mu$ F/50V(depend on LCD panel size), C2=0.1 $\mu$ F/10V, R1=15 $\Omega$ .

#### Common Mode 1: (AC signal generator disable \ L/R=H \ Single mode)

#### Note

1. R=20KΩ~100KΩ

Example of RB & R:

$\rightarrow$  If R =20K $\Omega$ , bias=1/18, duty=1/320

$\rightarrow$  RB =(18-4)\*20K $\Omega$

=280KΩ

- 2. VR=50K $\Omega$ , R2=22K $\Omega$ (Adjust VR & R2 to get best range and contrast)

- 3. C1=2.2~4.7 $\mu$ F/50V(depend on LCD panel size), C2=0.1 $\mu$ F/10V, R1=15 $\Omega$ .

#### Common Mode 2: (AC signal generator enable & D0~D7=00001101:13-line inversion)

#### Note

- 1. R=20KΩ~100KΩ, R3=0Ω

- Example of RB & R:

- $\rightarrow$  If R =20K $\Omega$ , bias=1/18, duty=1/320

- $\rightarrow$  RB =(18-4)\*20KΩ =280KΩ

- 2. VR=50KΩ, R2=22KΩ(Adjust VR & R2 to get best range and contrast)

- 3. C1=2.2~4.7 $\mu$ F/50V(depend on LCD panel size), C2=0.1 $\mu$ F/10V, R1=15 $\Omega$ .

## **Application & ITO Layout Notice (for reference only)**

## **Application Notices**

- 1. To adjust the voltage of V1 and V4 you can amend the phenomena of "cross talk" (V1& V4 range of adjustment is less than 100mV, be sure V0-V1=V4-VSS after adjusting.

- 2. Add 0.1µf high frequency capacitors between VDD & V0 ~ V4 and VSS.

- 3. When OP (LP324) is used as following bias voltage, ensure OP power voltage must be 1.5V (or more) higher than output voltage.

- 4. XCK, D0~D7, LP are high frequency (Max. 20MHz) signals: pay attention to the distance between them and other signals nearby to avoid high frequency interference.

- 5. EIO1, EIO2 are enable signals for connecting chips: pay attention to the distance between them and other signals nearby to avoid interference. The distance of connection between two chips is the shorter the better.

## ITO Layout Notice (It is for application of COG type)

- 1. We suggest that the LCD panel is made of glass whose ITO resistor is under  $15\Omega$ /square. ITO will be better if it is straight. Its resistor value is the smaller the better.

- Among interface Pins, first ensure ITO resistor values of VDD, VSS and V0 ~ V4 are less than values we suggest as shown below:

• ITO resistance value of power pins.