# **NMH1000**

### **Magnetic switch**

Rev. 3 — 18 October 2023

Product data sheet

### 1 General description

The NMH1000 is a hall effect magnetic field switch. The switch is most sensitive to a vertical field passing through the top-to-bottom surfaces, orthogonal to the plane of the application printed circuit board. The switch operates at low voltage, low current, low output data rate, and is a small physical size.

Processing of input consists of functional blocks such as a configurable state machine, analog-to-voltage conversion of the input, and comparison to generate the bi-state output, arranged in linear succession.

### 2 Features and benefits

- Threshold selection 3-state hardware pin.

- Threshold selection data bit(s) in an I<sup>2</sup>C accessible register.

- Sample rate selection 3-state hardware pin.

- Sample rate selection data bit(s) in an I<sup>2</sup>C accessible register.

- Mode selection hardware pin to select between standalone or I<sup>2</sup>C serial interface.

- Mode selection data bit(s) in an I<sup>2</sup>C accessible register.

- Two types of output indicate the absence of a magnetic field as compared to an internally set threshold:

- Binary state hardware pin.

- Binary state data bit(s), configurable as assert-high or assert-low, in an I<sup>2</sup>C accessible register.

# 3 Applications

- **Electronic system wake-up:** Detecting the proximity vs. lack of proximity to an included magnet when the electronics are removed from its delivery packaging, to wake up the electronics.

- Laptop lid open / closed: Detecting the proximity vs. lack of proximity to a magnet mounted to laptop lid, to trigger a status change, for example turn on / off the display.

- **Door or window open / closed:** Detecting the proximity vs. lack of proximity to a magnet mounted to a door, lid, or window, to trigger a status change, for example an alarm.

# 4 Ordering information

Table 1. Ordering information

| Type number | Package |                                                                                                      |           |  |  |  |

|-------------|---------|------------------------------------------------------------------------------------------------------|-----------|--|--|--|

|             | Name    | Description                                                                                          | Version   |  |  |  |

| NMH1000     | VSON    | Very thin small outline package, no leads, 6 terminals, 0.5 mm pitch, 1.4 mm x 1.4 mm x 0.85 mm body | SOT2078-1 |  |  |  |

**Magnetic switch**

Refer to AN1902<sup>[1]</sup> for additional information regarding use-case design and manufacturing recommendations.

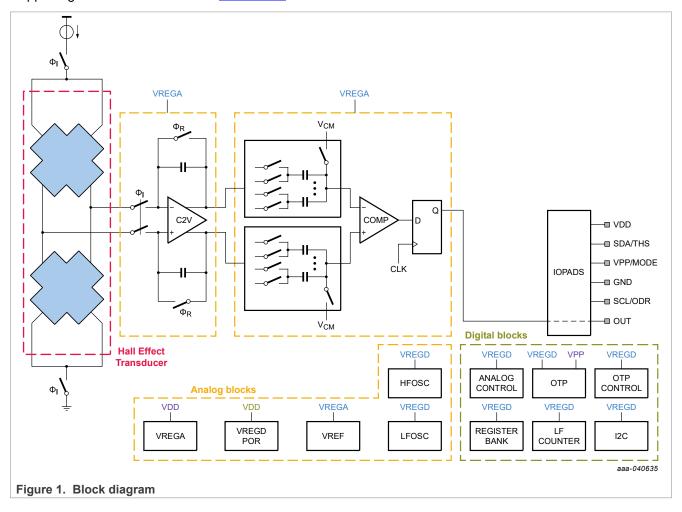

# 5 Block diagram

The device consists of a monolithic die holding a Hall effect transducer, conversion, and comparison chain. Supporting blocks are described in <u>Section 5.1</u>.

**Magnetic switch**

### 5.1 Block descriptions

• Hall effect: A transducer which generates a small charge which is proportional to the proximal magnetic flux density.

#### VREGA block:

- C2V: Converts the Hall effect charge to a voltage, which is stored onto the capacitor across the amplifier.

- **Comparator:** Compares the voltage generated by the C2V with the pre-defined threshold voltage, then determines the state of the output Q, either Asserted or Cleared.

#### · Analog blocks:

- HF and LF Oscillator: Configurable frequency (f<sub>HFO</sub> and f<sub>LFO</sub>) RC-Relaxation oscillators with independent trim bits for trimming.

- Regulators and references: Regulators to step down the external supply for analog and digital circuits.

Bandgap reference and current reference for biasing all analog module.

### · Digital blocks:

- **Analog control block:** Control signal generation for regulators and references, C2V, oscillators, comparator, for example, based on different operational modes.

- **OTP:** A 16 x 8 bit array, it requires external V<sub>PPTM</sub> for programming.

- OTP controller block: Provides read and write control for OTP. All control signals needed by OTP are generated by this module.

- Register bank: Provides the registers where users can write configurations or read status values.

- LF counter: Counts the specific time depending on the sample rate (ODR) set by the user.

- I<sup>2</sup>C and test register block: Includes the address decode logic and interrupt functions.

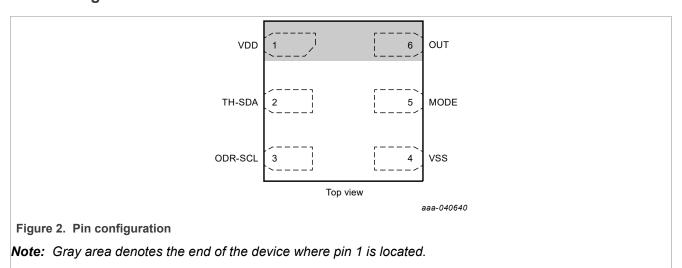

## 6 Pinning information

#### 6.1 Pinning

#### 6.2 Pin description

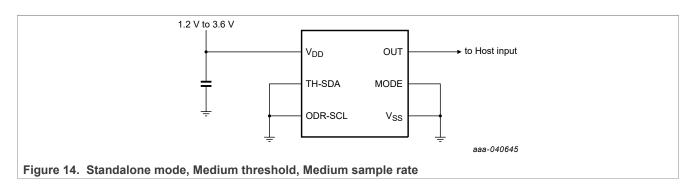

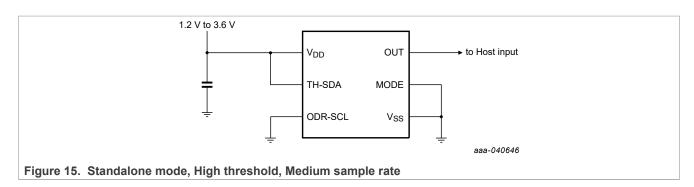

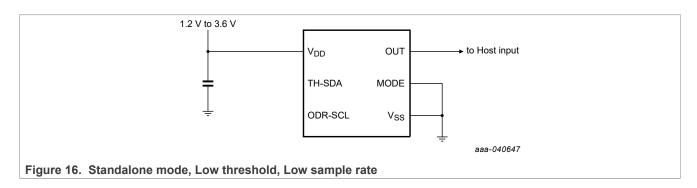

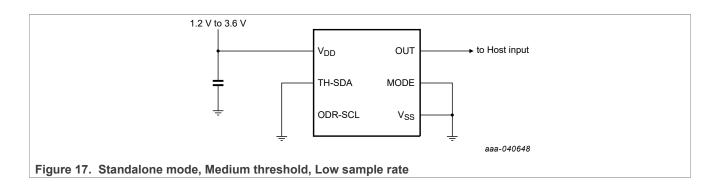

Package and pin assignments support the options of magnetic field threshold and sample rate selections, based on the voltage applied to the MODE pin, upon appropriate voltage applied to the  $V_{DD}$  pin, relative to the  $V_{SS}$  pin.

NMH1000

**Magnetic switch**

Table 2. Pin description

| Symbol                 | Pin | Туре   | Description                                                                            |  |  |

|------------------------|-----|--------|----------------------------------------------------------------------------------------|--|--|

| $V_{DD}$               | 1   | Supply | Main supply voltage                                                                    |  |  |

| TH-SDA <sup>[1]</sup>  | 2   | I/O    | Standalone mode: Threshold I <sup>2</sup> C user mode: I <sup>2</sup> C serial data    |  |  |

| ODR-SCL <sup>[2]</sup> | 3   | I      | Standalone mode: Sample rate I <sup>2</sup> C user mode: I <sup>2</sup> C serial clock |  |  |

| V <sub>SS</sub>        | 4   | Ground | Main ground                                                                            |  |  |

| MODE <sup>[3]</sup>    | 5   | I      | Selects between Standalone or I <sup>2</sup> C modes.                                  |  |  |

| OUT <sup>[4]</sup>     | 6   | 0      | Standalone mode: Output indicating absence of field                                    |  |  |

- Three states: low state for medium threshold  $B_O$ -M, open circuit for low threshold  $B_O$ -L, or high state for high threshold  $B_O$ -H, relative to  $V_{SS}$  Three states: low state for medium sample rate  $f_{ODR}$ -M, open circuit for low sample rate  $f_{ODR}$ -L, or high state for high sample rate  $f_{ODR}$ -H, relative to  $V_{SS}$  Two states: low state for standalone, high state for l^C User Mode, relative to  $V_{SS}$  Two states: default assert for magnet not present, clear for magnet present, relative to  $V_{SS}$ [1] [2] [3] [4]

### 6.3 Orientation

The device adheres to the convention of north magnetic field represented by positive/North polarity, orthogonal to the plane of the package body top surface and the arrows depict increasing strengths.

Figure 3. Magnetic field vs. package orientation

**Magnetic switch**

# 7 Functional description

### 7.1 Operating modes

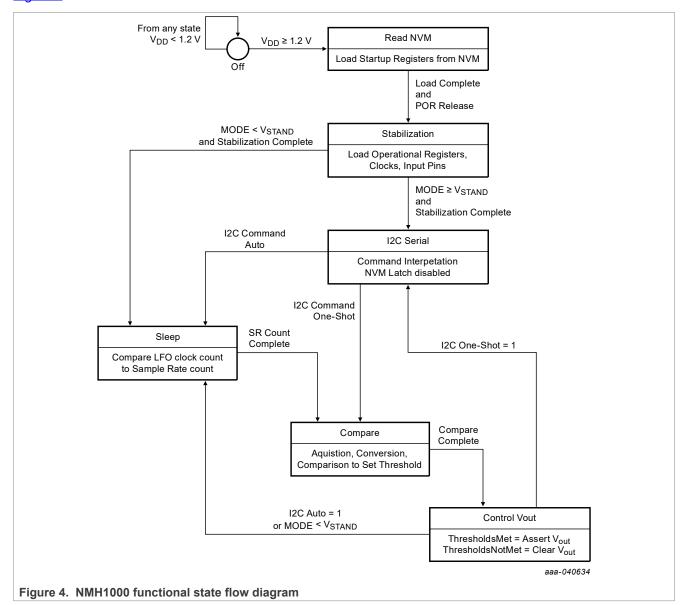

#### 7.1.1 Functional states

Figure 4 illustrates the functional states that the device transitions between.

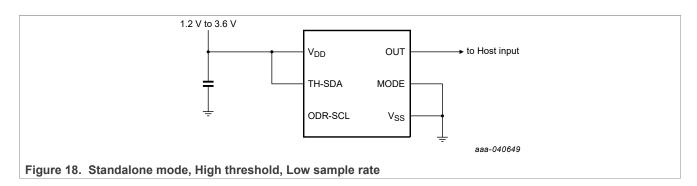

## 7.1.2 Interface Operational Modes

The NMH1000 operates under one of two modes when appropriately configured as described in the following sections:

- I<sup>2</sup>C user mode.

- Standalone mode.

NMH1000

All information provided in this document is subject to legal disclaimers.

**Magnetic switch**

Entry into each of the two user modes is initiated by the voltage existing at the MODE pin at the time of the  $V_{DD}$  pin rising above  $V_{DDMIN}$ , and followed by a read of NVM Start-up register(s), both relative to the  $V_{SS}$  pin:

- MODE < V<sub>STAND</sub> results in the device entering standalone mode and forcing OPMODE to 0.

- MODE ≥ V<sub>STAND</sub> results in the device entering I<sup>2</sup>C user mode and forcing OPMODE to 1.

Transition from  $I^2C$  user mode to standalone mode is initiated by the host writing I2C\_DIS to 1, which results in OPMODE being forced to 0.

**Note:** The device reloads the NVM into operating registers after  $t_{RLDS}$  seconds from final power application, needing a duration of  $t_{RLDC}$ .

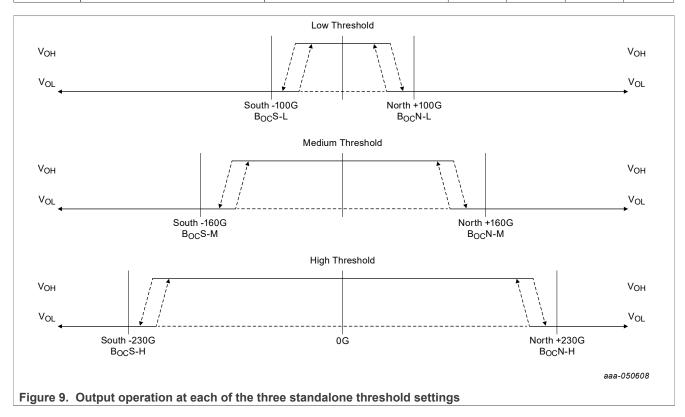

### 7.2 Threshold configurations

#### 7.2.1 Fixed thresholds

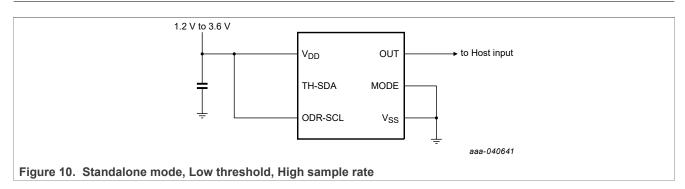

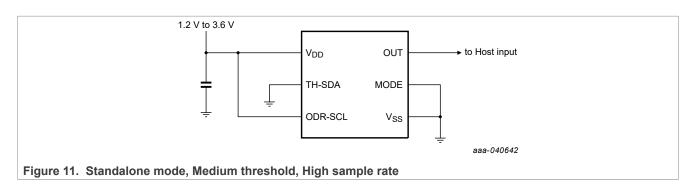

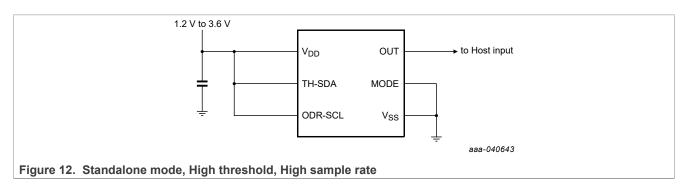

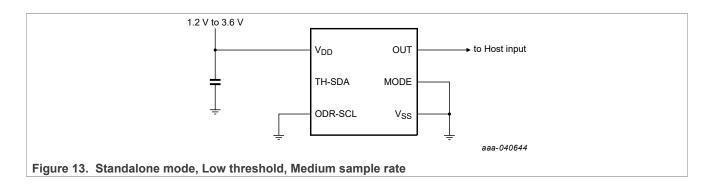

In standalone mode, fixed thresholds with fixed hysteresis are selected by voltage applied to  $V_{TH}$  pin relative to  $V_{SS}$  pin.

### 7.2.1.1 Fixed threshold selection via V<sub>TH</sub> pin voltage

Table 3. Fixed threshold selection

| V <sub>TH</sub>                          | Threshold <sup>[1]</sup> |

|------------------------------------------|--------------------------|

| V <sub>TH</sub> < V <sub>BO</sub> -L     | Medium magnetic field    |

| $V_{BO}$ -L $\leq V_{TH} \leq V_{BO}$ -H | Low magnetic field       |

| V <sub>TH</sub> > V <sub>BO</sub> -H     | High magnetic field      |

<sup>[1]</sup> See <u>Table 27</u>.

#### 7.2.2 User-defined threshold

In I<sup>2</sup>C mode, user-defined output assert threshold without hysteresis is selected by write to register bits, in units of  $B\Delta$  in G/LSB:

Table 4. User-defined assert thresholds

| USER_ASSERT_THRESH[7:3] | Assert Threshold <sup>[1]</sup> - B <sub>OA</sub>    |

|-------------------------|------------------------------------------------------|

| 0 0 0 0 0               | 0 G                                                  |

| 0 0 0 0 1               | Lowest in-range magnetic field to assert the output  |

| 11111                   | Highest in-range magnetic field to assert the output |

<sup>[1]</sup> See to Section 10.6 "I2C user mode, output assertion"

In I<sup>2</sup>C mode, user-defined output clear threshold without hysteresis is selected by write to register bits, in units of B $\Delta$  in G/LSB:

Table 5. User-defined output clear thresholds

| USER_CLEAR_THRESH[7:3] | Clear Threshold <sup>[1]</sup> - B <sub>OC</sub>    |

|------------------------|-----------------------------------------------------|

| 0 0 0 0 0              | 0 G                                                 |

| 0 0 0 0 1              | Lowest in-range magnetic field to clear the output  |

| 11111                  | Highest in-range magnetic field to clear the output |

NMH1000

All information provided in this document is subject to legal disclaimers.

**Magnetic switch**

#### [1] See to Section 10.7 "I2C user mode, output clear"

**Note:** If the USER\_ASSERT\_THRESH and USER\_CLEAR\_THRESH are set too close in value to each other, the intended hysteresis may cause the output to change states at unintended magnetic field strengths, or may cause the output to not change states at intended magnetic field strengths.

Be aware of the minimum hysteresis noted in Table 32.

### 7.3 Sample rate configurations

### 7.3.1 Fixed sample rates

In standalone mode, the sample rate is the selected voltage applied to V<sub>ODR</sub> pin relative to V<sub>SS</sub> pin.

### 7.3.1.1 Sample rate selection via V<sub>ODR</sub> pin voltage

Table 6. Sample rate selection

| V <sub>ODR</sub>                        | Sample Rate <sup>[1]</sup> |

|-----------------------------------------|----------------------------|

| V <sub>ODR</sub> < V <sub>fODR-L</sub>  | f <sub>ODR</sub> -M        |

| $V_{fODR-L} \le V_{ODR} \le V_{fODR-H}$ | f <sub>ODR</sub> -L        |

| V <sub>ODR</sub> > V <sub>fODR-H</sub>  | f <sub>ODR</sub> -H        |

<sup>[1]</sup> See Section 10.2 "Clocks and rates".

### 7.3.2 User-defined sample rate

In I<sup>2</sup>C mode, the user-defined sample rate is selected by a write to register bits:

Table 7. I<sup>2</sup>C mode user-defined sample rate

| USER_ODR[2:0] | Sample Rate              |

|---------------|--------------------------|

| 0 0 0         | f <sub>ODR</sub> -L      |

| 0 0 1         | 5 x f <sub>ODR</sub> -L  |

| 0 1 0         | f <sub>ODR</sub> -M      |

| 0 1 1         | 5 x f <sub>ODR</sub> -M  |

| 100           | f <sub>ODR</sub> -H      |

| 1 0 1         | 5 x f <sub>ODR</sub> -H  |

| 110           | 10 x f <sub>ODR</sub> -H |

| 1 1 1         | config. error            |

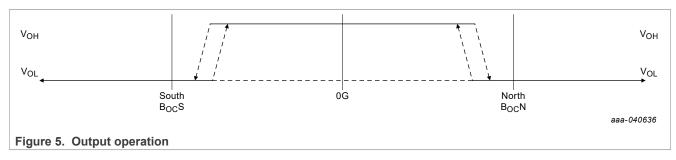

### 7.4 Output control function description

### 7.4.1 Output hysteresis

Hysteresis is implemented as the magnetic field difference between the output being cleared versus the output being asserted.

- In Standalone mode, the hysteresis is a fixed difference.

- In I<sup>2</sup>C mode with the selection of one of the three fixed thresholds, the hysteresis is a fixed difference, equal to the Standalone mode hysteresis.

NMH1000

All information provided in this document is subject to legal disclaimers.

**Magnetic switch**

• In I<sup>2</sup>C mode with customer selected thresholds, the hysteresis is the result of the customer choices of output Clear threshold versus output Assert threshold.

#### 7.4.2 Control Output State

#### 7.4.2.1 Standalone mode output assert / clear states

In Standalone mode, the OUT pin asserts to high state upon the completion of the comparison stage, and the magnetic field is lower than the selected threshold Low, Medium, or High, minus the hysteresis.

In Standalone mode, the OUT pin is cleared to low state upon completion of the comparison stage, and the magnetic field is higher than the selected threshold Low, Medium, or High.

### 7.4.2.2 User-defined output assert / clear states

In I<sup>2</sup>C mode, the OUT pin and OUT-B register bit asserted and cleared states are selectable via the V\_POL register bit.

Table 8. User-defined output assert and clear states

| V_POL | OUT pin assert / clear state                |

|-------|---------------------------------------------|

| 0     | OUT pin Assert = high / OUT pin Clear = low |

| 1     | OUT pin Assert = low / OUT pin Clear = high |

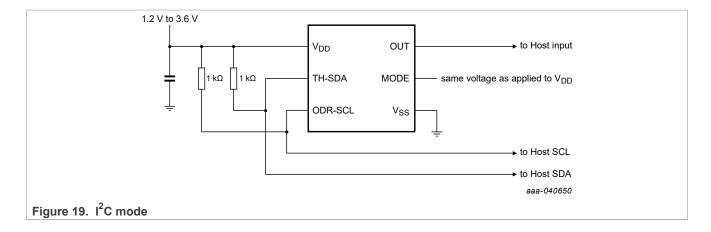

# 7.5 I<sup>2</sup>C serial data function description

# 7.5.1 I<sup>2</sup>C pin functions

Two signals support the I<sup>2</sup>C-bus:

- · Serial Clock Line SCL.

- · Serial Data line SDA.

SCL is input and used for clocking the data into or out from the SDA data line.

SDA is bidirectional and used for sending and receiving the data.

When the bus is free, both the lines idle high.

The I<sup>2</sup>C interface is compliant to the standard mode (100 kHz).

SDA and SCL both expect external pull-up resistors connected to V<sub>DD</sub>.

• 1 kΩ minimum, board capacitance 20 pF maximum.

NMH1000

All information provided in this document is subject to legal disclaimers.

**Magnetic switch**

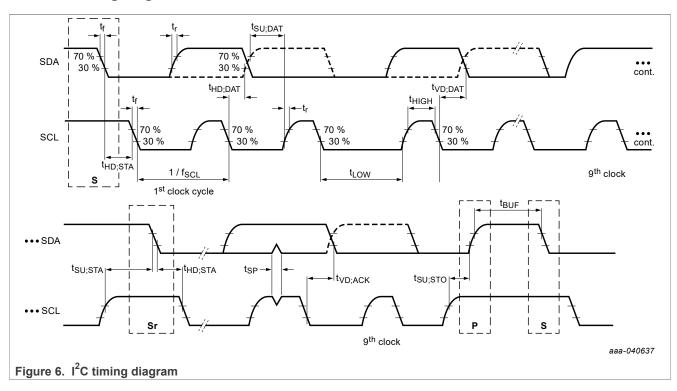

## 7.5.2 I<sup>2</sup>C timing diagram

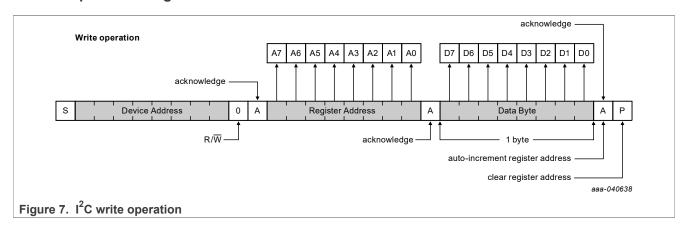

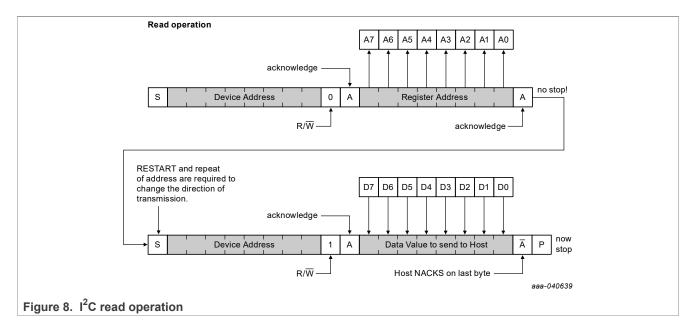

## 7.5.3 I<sup>2</sup>C operation

The I<sup>2</sup>C transaction on the bus is initiated through a start condition (START) signal. START signal is defined as a HIGH to LOW transition on the SDA line while the SCL line is held HIGH. After START is transmitted by the host, the bus is considered busy. The next byte of data transmitted after START contains the device address in the first seven bits, and the eighth bit indicates whether the host is receiving data from the device or transmitting data to the device. When an address is sent, each device in the system compares the first seven bits after a start condition with its address. If they match, the device considers itself addressed by the host. The ninth clock pulse, following the device address byte (and each subsequent byte) is the acknowledge (ACK). The transmitter must release the SDA line during the ACK period. The receiver must then pull the data line low for it to remain stable low during the high period of the acknowledge clock period.

The number of bytes per transfer is unlimited because the internal addressing wraps after \$6D to \$00, continuing to \$6D again, then to \$00, and so forth. The wrapping applies to both write transfers and read transfers. Note that usable addresses stop at \$09, therefore a host may expect random values between \$0A to \$6D. If the host is unable to receive another complete byte of data until it has performed some other function, the host can hold the SCL line low, forcing the transmitter into a wait state. Data transfer continues only when the host is ready for another byte and releases the clock line.

A stop condition (STOP) is defined as a low to high transition on the SDA line while the SCL line is high. Data transfer is terminated by a STOP.

A host may also issue a RESTART during a data transfer. The device expects RESTARTs to randomly read from specific registers.

The bus logic of the device resets on receipt of a START, or RESTART condition. The device anticipates the sending of a device address, even if these START conditions are not positioned or follow proper format.

The device accepts the first bit of an address after each START, or RESTART condition.

NMH1000

All information provided in this document is subject to legal disclaimers

**Magnetic switch**

The device detects when the SDA line is held low, and in such cases, releases the SDA line when the host issue no more than nine cycles of the SCL line.

The device determines the value in the NVM  $I^2C$  address register. If the value is not \$00, the device uses this address during  $I^2C$  transactions. If the address register is \$00, the address defaults to \$60. The reset value of the  $I^2C$  address register is also \$60.

## 7.5.4 I<sup>2</sup>C protocol diagram

### 7.6 Register map

### 7.6.1 Register overview

Table 9. Register map overview

| Address | Name          | Description                              | AO or S <sup>[1]</sup> | Bit 7  | Bit 6 | Bit 5 | Bit 4   | Bit 3  | Bit 2        | Bit 1        | Bit 0 |

|---------|---------------|------------------------------------------|------------------------|--------|-------|-------|---------|--------|--------------|--------------|-------|

| \$00    | <u>STATUS</u> | Status reporting of modes and selections | S                      | OUTPUT | MDO   | MDR   | _       | OPMODE | _            | RST_<br>STAT | OUT_B |

| \$01    | CONTROL_REG1  | Control of Operations                    | s                      | _      | _     | V_POL | I2C_DIS | AUTO   | ONE_<br>SHOT | _            | RST   |

NMH1000

All information provided in this document is subject to legal disclaimers.

**Magnetic switch**

Table 9. Register map overview...continued

| Address | Name                   | Description                                                         | AO or S <sup>[1]</sup>                      | Bit 7                            | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2    | Bit 1 | Bit 0 |

|---------|------------------------|---------------------------------------------------------------------|---------------------------------------------|----------------------------------|-------|-------|-------|---------|----------|-------|-------|

| \$02    | _                      | Reserved                                                            | _                                           | _                                | _     | _     | _     | _       | _        | _     | _     |

| \$03    | OUT_M_REG              | Report of Magnetic Strength                                         | eport of Magnetic Strength S MAG_DATA [7:2] |                                  |       |       |       |         | _        | _     |       |

| \$04    | USER_ASSERT_<br>THRESH | User selectable output Assert threshold, N or S                     | AO USER_ASSERT_THRESH [7:3] Reserved        |                                  |       |       |       |         | Reserved |       |       |

| \$05    | USER_CLEAR_<br>THRESH  | User selectable output Clear threshold, N or S                      | AO                                          | USER_CLEAR_THRESH [7:3] Reserved |       |       |       |         |          |       |       |

| \$06    | USER_ODR               | User selectable sleep sample output data rates                      | AO                                          | USER_OI                          |       |       |       | ER_ODR[ | 2:0]     |       |       |

| \$07    | _                      | Reserved                                                            | _                                           |                                  |       | _     | _     | _       |          |       |       |

| \$08    | WHO_AM_I               | I <sup>2</sup> C Configured Identifier                              | s                                           | WHO_AM_I [7:0]                   |       |       |       |         |          |       |       |

| \$09    | I2C_ADDR               | I <sup>2</sup> C Configured Address -<br>default after reset = \$60 | s                                           | — ADDR [6:0]                     |       |       |       |         |          |       |       |

<sup>[1]</sup> AO - Always On, S - Switched

### 7.6.2 Register details

### 7.6.2.1 Status reporting of modes and selections (STATUS) (\$00h)

Table 10. STATUS – Status reporting of modes and selections (address \$00h) bit allocation

| Bit    | 7      | 6   | 5   | 4 | 3      | 2 | 1        | 0     |

|--------|--------|-----|-----|---|--------|---|----------|-------|

| Symbol | OUTPUT | MDO | MDR | _ | OPMODE | _ | RST_STAT | OUT_B |

| Reset  | 0      | 1   | 1   | _ | 1      | _ | 1        | х     |

| Access | R/W    | R/W | R/W | _ | R/W    | _ | R/W      | R/W   |

Table 11. STATUS - Status reporting of modes and selections (address \$00h) bit descriptions

| Bit | Symbol | Access | Value | Description                                                                                                                                                                                                                                                                                                    |

|-----|--------|--------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | OUTPUT | R/W    |       | $V_{out}$ control block state. This bit follows the state of the OUT pin in either case of $V\_POL = 0$ or 1.                                                                                                                                                                                                  |

|     |        |        | 0     | The state of VOUT is driven to low; Result of Reset.                                                                                                                                                                                                                                                           |

|     |        |        | 1     | The state of VOUT is driven to high.                                                                                                                                                                                                                                                                           |

| 6   | MDO    | R/W    |       | Magnetic data overwrite indicates the validity of the value in register \$03. After asserting to 1, the MDO bit retains this value after the register \$03 returns to the range of \$00 to \$1F, until a read operation is performed on register \$00. The MDO reasserts if the register \$03 is again > \$1F. |

|     |        |        | 0     | Register \$03 value is within the range \$00 to \$1F.                                                                                                                                                                                                                                                          |

|     |        |        | 1     | Register \$03 value is >\$1F indicates out-of-range or fault; Result of reset.                                                                                                                                                                                                                                 |

| 5   | MDR    | R/W    |       | Magnetic data ready indicates the value in register \$03 is available for read operation. After asserting to 1, the MDR bit retains this value after the register \$03 becomes available, until a read operation is performed on register \$00. The MDR reasserts if the register \$03 is again not available. |

|     |        |        | 0     | \$03 data available.                                                                                                                                                                                                                                                                                           |

|     |        |        | 1     | \$03 data not available; Result of reset.                                                                                                                                                                                                                                                                      |

**Magnetic switch**

Table 11. STATUS - Status reporting of modes and selections (address \$00h) bit descriptions...continued

| Bit | Symbol   | Access | Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|----------|--------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | OPMODE   | R/W    |       | The read-only OPMODE indicates the mode of the internal state-machine.                                                                                                                                                                                                                                                                                                                                                      |

|     |          |        | 0     | Indicates VPP < VSTAND and the device in standalone mode indicating a state machine fault, since the registers are only accessible in the I <sup>2</sup> C mode.                                                                                                                                                                                                                                                            |

|     |          |        | 1     | Indicates VPP ≥ VSTAND and the device in I <sup>2</sup> C user mode.                                                                                                                                                                                                                                                                                                                                                        |

| 1   | RST_STAT | R/W    |       | Reset status indicates the state-machine reset sequence. RST_STAT set to 1 as the device enters POR or soft reset. This bit is cleared to 0 upon reading the register \$00. After asserting to 1, the RST_STAT bit retains this value after the exit of POR or soft rest, until a read operation is performed on register \$00. The RST_STAT reasserts if POR or soft reset is entered.                                     |

|     |          |        | 0     | Reset sequence complete and read operation performed on register \$00.                                                                                                                                                                                                                                                                                                                                                      |

|     |          |        | 1     | Reset sequence not complete; Result of reset.                                                                                                                                                                                                                                                                                                                                                                               |

| 0   | OUT_B    | R/W    |       | Output buffer indicates a latched state of the OUT pin after a transition from either Asserted to Clear or Clear to Asserted. After asserting to 1, or clearing to 0, the OUT_B bit retains this value until a read operation is performed on register \$00. This bit is intended to allow the user or tester to check for a transition while the actual OUT pin or OUTPUT bit may have changed state again between checks. |

|     |          |        | 0     | OUT cleared on previous cycle.                                                                                                                                                                                                                                                                                                                                                                                              |

|     |          |        | 1     | OUT asserted on previous cycle.                                                                                                                                                                                                                                                                                                                                                                                             |

## 7.6.2.2 Control of operations (CONTROL\_Reg1) (\$01h)

Table 12. CONTROL Reg1 - Control of operations(address \$01h) bit allocation

|        |   | 3 |       | - (     | ,    | _        |   |     |

|--------|---|---|-------|---------|------|----------|---|-----|

| Bit    | 7 | 6 | 5     | 4       | 3    | 2        | 1 | 0   |

| Symbol | _ | _ | V_POL | I2C_DIS | AUTO | ONE_SHOT | _ | RST |

| Reset  | _ | _ | 0     | 0       | 0    | 0        | _ | 0   |

| Access | _ | _ | R/W   | R/W     | R/W  | R/W      | _ | R/W |

Table 13. CONTROL\_Reg1 - Control of operations (address \$01h) bit description

| Bit | Symbol | Access | Value | Description                                                                                                  |

|-----|--------|--------|-------|--------------------------------------------------------------------------------------------------------------|

| 5   | V_POL  | R/W    |       | V_POL provides control of the user-defined OUT pin and resultant OUT_B register bit assert / clear polarity. |

|     |        |        | 0     | Assert = out pin high, Clear = out pin low; Result of reset.                                                 |

|     |        |        | 1     | Assert = out pin low, Clear = out pn high.                                                                   |

Magnetic switch

Table 13. CONTROL\_Reg1 - Control of operations (address \$01h) bit description...continued

| Bit | Symbol   | Access | Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|----------|--------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | I2C_DIS  | R/W    |       | I2C_DIS provides control of the operating mode "on-the-fly" after the device exits POR or Soft Reset. I2C_DIS allows the user to force the device into standalone mode from the I <sup>2</sup> C mode.  Note: Writing 1 to I2C_DIS is a one-time-only operation. Bringing the device into I <sup>2</sup> C mode from standalone requires a full power cycle and release of POR.  Note: MAG_DATA retains its last value, and is updated upon next write to ONE_SHOT. |

|     |          |        | 0     | Write to 0 has no effect; Read of 0 indicates I <sup>2</sup> C mode; Result of reset.                                                                                                                                                                                                                                                                                                                                                                               |

|     |          |        | 1     | Write to 1 forces the device from I <sup>2</sup> C mode to standalone mode; Read of 1 indicates a state machine fault, since the registers are only accessible in the I <sup>2</sup> C mode.                                                                                                                                                                                                                                                                        |

| 3   | 3 AUTO   | R/W    |       | AUTO provides control of the state machine to enter a sequential autonomous mode cycling from sleep to compare to Vout control, then back to sleep, for example. The sequence is halted when the AUTO is written to 0.                                                                                                                                                                                                                                              |

|     |          |        | 0     | Write to 0 halts or prevents autonomous mode; Read of 0 indicates that autonomous mode is not active; Result of reset.                                                                                                                                                                                                                                                                                                                                              |

|     |          |        | 1     | Write to 1 starts the autonomous mode; Read of 1 indicates that autonomous mode is active.                                                                                                                                                                                                                                                                                                                                                                          |

| 2   | ONE_SHOT | R/W    |       | ONE_SHOT provides control of the state machine to trigger a single sequence of compare to Vout control, then halt. The bit clears upon the sequence being completed.                                                                                                                                                                                                                                                                                                |

|     |          |        | 0     | Write to 0 has no effect; Read of 0 indicates One-Shot is not active; Result of reset.                                                                                                                                                                                                                                                                                                                                                                              |

|     |          |        | 1     | Write to 1 triggers a one-shot sequence; Read of 1 has no effect.                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |          |        |       | <b>Note:</b> The BUSY bit indicates that the sequence is underway or not completed. <b>Note:</b> MAG_DATA retains its last value, and is updated upon next write to ONE_SHOT.                                                                                                                                                                                                                                                                                       |

| 0   | RST      | R/W    |       | RST provides I <sup>2</sup> C access to force an internal device soft reset:                                                                                                                                                                                                                                                                                                                                                                                        |

|     |          |        | 0     | No reset is forced.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |          |        | 1     | Internal device reset is forced.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

## 7.6.2.3 Magnetic strength report (OUT\_M\_REG) (\$03h)

Table 14. OUT\_M\_REG – Magnetic strength report (address \$03h) bit allocation

| Bit    | 7   | 6                       | 5   | 4   | 3   | 2   | 1 | 0 |

|--------|-----|-------------------------|-----|-----|-----|-----|---|---|

| Symbol |     | MAG_DATA [7:2] reserved |     |     |     |     |   |   |

| Reset  | 0   | 0                       | 0   | 0   | 0   | 0   | 0 | 0 |

| Access | R/W | R/W                     | R/W | R/W | R/W | R/W | _ | _ |

**Magnetic switch**

Table 15. OUT\_M\_REG - Magnetic strength report (address \$03h) bit description

| Bit    | Symbol   | Access | Value | Description                                                                                 |

|--------|----------|--------|-------|---------------------------------------------------------------------------------------------|

| 7 to 2 | MAG_DATA | R/W    |       | MAG_DATA[7:2] indicates a relative magnetic field strength in units of B $\Delta$ in G/LSB. |

|        |          |        | \$00  | 0 G; Result of reset.                                                                       |

|        |          |        | \$01  | Lowest in-range magnetic field strength.                                                    |

|        |          |        | \$1F  | Highest in-range magnetic field strength.                                                   |

### 7.6.2.4 User selectable output, assert threshold, N or S (USER\_ASSERT\_THRESH) (\$04h)

Table 16. USER\_ASSERT\_THRESH – User selectable output, assert threshold, N or S (address \$04h) bit allocation

| Bit    | 7   | 6      | 5          | 4        | 3   | 2   | 1   | 0   |

|--------|-----|--------|------------|----------|-----|-----|-----|-----|

| Symbol |     | USER_A | SSERT_THRE | Reserved |     |     |     |     |

| Reset  | 0   | 0      | 0          | 0        | 0   | _   | _   | _   |

| Access | R/W | R/W    | R/W        | R/W      | R/W | R/W | R/W | R/W |

Table 17. USER\_ASSERT\_THRESH – User selectable output, assert threshold, N or S (address \$04h) bit description

| Bit    | Symbol                     | Access | Value | Description                                                                                                                                                                                     |

|--------|----------------------------|--------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 to 3 | USER_<br>ASSERT_<br>THRESH | R/W    |       | In I <sup>2</sup> C mode, USER_ASSERT_THRESH[7:3] provides the capability for the user to override the fixed threshold controlling the output assert condition, in units of $B\Delta$ in G/LSB. |

|        |                            |        |       | <b>Note:</b> Hysteresis is controlled by appropriate user settings for both USER_ASSERT_THRESH and USER_CLEAR_THRESH registers.                                                                 |

|        |                            |        | \$00  | 0 G; Result of reset.                                                                                                                                                                           |

|        |                            |        | \$01  | Lowest in-range magnetic field to assert the output.                                                                                                                                            |

|        |                            |        | \$1F  | Highest in-range magnetic field to assert the output.                                                                                                                                           |

### 7.6.2.5 User selectable output, clear threshold, N or S (USER\_CLEAR\_THRESH) (\$05h)

Table 18. USER\_CLEAR\_THRESH – User selectable output, clear threshold, N or S (address \$05h) bit allocation

| Bit    | 7   | 6      | 5          | 4        | 3   | 2   | 1   | 0   |

|--------|-----|--------|------------|----------|-----|-----|-----|-----|

| Symbol |     | USER_0 | CLEAR_THRE | Reserved |     |     |     |     |

| Reset  | 0   | 0      | 0          | 0        | 0   | _   | _   | _   |

| Access | R/W | R/W    | R/W        | R/W      | R/W | R/W | R/W | R/W |

**Magnetic switch**

Table 19. USER\_CLEAR\_THRESH – User selectable output, clear threshold, N or S (address \$05h) bit description

| Bit    | Symbol                    | Access | Value | Description                                                                                                                                                                                    |

|--------|---------------------------|--------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 to 3 | USER_<br>CLEAR_<br>THRESH | R/W    |       | In I <sup>2</sup> C mode, USER_CLEAR_THRESH[7:3] provides the capability for the user to override the fixed threshold controlling the output clear condition, in units of B $\Delta$ in G/LSB. |

|        |                           |        |       | <b>Note:</b> Hysteresis is controlled by appropriate user settings for both USER_ASSERT_THRESH and USER_CLEAR_THRESH registers.                                                                |

|        |                           |        | \$00  | 0 G; Result of reset.                                                                                                                                                                          |

|        |                           |        | \$01  | Lowest in-range magnetic field to clear the output.                                                                                                                                            |

|        |                           |        | \$1F  | Highest in-range magnetic field to clear the output.                                                                                                                                           |

### 7.6.2.6 User selectable sleep sample output data rates (USER\_ODR) (\$06h)

Table 20. USER ODR - User selectable sleep sample output data rates (address \$06h) bit allocation

| Bit    | 7 | 6 | 5 | 4 | 3 | 2         | 1    | 0   |

|--------|---|---|---|---|---|-----------|------|-----|

| Symbol | _ | _ | _ | _ | _ | USER_ODR[ | 2:0] |     |

| Reset  | _ | _ | _ | _ | _ | 0         | 0    | 0   |

| Access | _ | _ | _ | _ | _ | R/W       | R/W  | R/W |

Table 21. USER\_ODR - User selectable sleep sample output data rates (address \$06h) bit description

| Bit    | Symbol   | Access | Value | Description                                                                                                                                                   |

|--------|----------|--------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 to 0 | USER_ODR | R/W    |       | In I <sup>2</sup> C mode, USER_ODR[2:0] provides the capability for the user to override the fixed sample rate controlling the sleep-compare-Vout cycle time. |

|        |          |        | 000   | Low sample rate selected.                                                                                                                                     |

|        |          |        | 0 0 1 | 5 x Low sample rate selected.                                                                                                                                 |

|        |          |        | 0 1 0 | Medium sample rate selected.                                                                                                                                  |

|        |          |        | 0 1 1 | 5 x Medium sample rate selected.                                                                                                                              |

|        |          |        | 100   | High sample rate selected.                                                                                                                                    |

|        |          |        | 101   | 5 x High sample rate selected.                                                                                                                                |

|        |          |        | 110   | 10 x High sample rate selected.                                                                                                                               |

|        |          |        | 111   | Configuration error.                                                                                                                                          |

# 7.6.2.7 I<sup>2</sup>C configured identifier (WHO\_AM\_I) (\$08h)

Table 22. WHO\_AM\_I - I<sup>2</sup>C configured identifier (address \$08h) bit allocation

| Bit    | 7   | 6              | 5   | 4   | 3   | 2   | 1   | 0   |  |

|--------|-----|----------------|-----|-----|-----|-----|-----|-----|--|

| Symbol |     | WHO_AM_I [7:0] |     |     |     |     |     |     |  |

| Reset  | 0   | 0              | 0   | 0   | 0   | 0   | 0   | 1   |  |

| Access | R/W | R/W            | R/W | R/W | R/W | R/W | R/W | R/W |  |

NMH1000

**Magnetic switch**

Table 23. WHO\_AM\_I - I<sup>2</sup>C configured identifier (address \$08h) bit description

| Bit    | Symbol   | Access | Value           | Description                                                                                                                                               |

|--------|----------|--------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 to 0 | WHO_AM_I | R/W    |                 | WHO_AM_I[7:0] provides the device identification register. The value is programmed in the NVM at final test. Each variation has its own unique device ID. |

|        |          |        | \$00            | WHO_AM_I error condition.                                                                                                                                 |

|        |          |        | \$01            | Generic open market default value.                                                                                                                        |

|        |          |        | \$02 to<br>\$FE | Customer defined unique values.                                                                                                                           |

|        |          |        | \$FF            | WHO_AM_I not programmed.                                                                                                                                  |

# 7.6.2.8 I<sup>2</sup>C configured identifier (I2C\_ADDR) (\$09h)

Table 24. I2C\_ADDR - I<sup>2</sup>C configured identifier (address \$09h) bit allocation

| Bit    | 7 | 6   | 5              | 4   | 3   | 2   | 1   | 0   |  |

|--------|---|-----|----------------|-----|-----|-----|-----|-----|--|

| Symbol | _ |     | I2C_ADDR [6:0] |     |     |     |     |     |  |

| Reset  | _ | 1   | 1              | 0   | 0   | 0   | 0   | 0   |  |

| Access | _ | R/W | R/W            | R/W | R/W | R/W | R/W | R/W |  |

# Table 25. I2C\_ADDR - I<sup>2</sup>C configured identifier (address \$09h) bit description

|        |          |        | 9     | intinor (address worn) bit description                                                                                                                                                                                                                                          |

|--------|----------|--------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit    | Symbol   | Access | Value | Description                                                                                                                                                                                                                                                                     |

| 6 to 0 | I2C_ADDR | R/W    |       | I2C_ADDR[6:0] is register mapped and loaded by default value \$60 at boot time. After that, users may write any non-zero value to it. This non-zero value is used until the device is reset. If the device is reset, the same default value of \$60 is reloaded and used again. |

|        |          |        |       | \$60 = default loaded at exit of reset.                                                                                                                                                                                                                                         |

|        |          |        |       | \$00 = lowest address value.                                                                                                                                                                                                                                                    |

|        |          |        |       | \$7F = highest address value.                                                                                                                                                                                                                                                   |

# 8 Limiting values

Table 26. Limiting values

| Symbol             | Description                                                                           | Condition                                                                                           | Min                   | Тур | Max                       | Unit         |

|--------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------|-----|---------------------------|--------------|

| $B_G$              | Magnetic field                                                                        | $T_A \text{ Min} \le T_A \le T_A \text{ Max}, V_{DD} \text{ Min} \le V_{DD} \le V_{DD} \text{ Max}$ | _                     | _   | Not<br>limited            | G<br>(Gauss) |

| V <sub>SUP</sub>   | V <sub>DD</sub> to V <sub>SS</sub> range                                              | $T_A \text{ Min} \le T_A \le T_A \text{ Max}, V_{DD} \text{ Min} \le V_{DD} \le V_{DD} \text{ Max}$ | -0.3                  | _   | 3.6                       | V            |

| V <sub>IO</sub>    | IO pin voltage, each pin vs $V_{DD}$ / $V_{SS}$                                       | $T_A Min \le T_A \le T_A Max$                                                                       | V <sub>SS</sub> – 0.3 | _   | V <sub>SUP</sub><br>+ 0.3 | V            |

| I <sub>IO</sub>    | IO pin current, each pin vs $V_{DD}$ / $V_{SS}$                                       | $T_A \text{ Min} \le T_A \le T_A \text{ Max}, V_{DD} \text{ Min} \le V_{DD} \le V_{DD} \text{ Max}$ | -10                   | _   | 10                        | mA           |

| I <sub>SUBIO</sub> | Substrate current injection, all IO pins, current from pin to V <sub>SS</sub> – 0.3 V | $T_A \text{ Min} \le T_A \le T_A \text{ Max, VDD Min}$<br>$\le \text{VDD} \le \text{VDD Max}$       | _                     | 100 | _                         | mA           |

NMH1000

All information provided in this document is subject to legal disclaimers.

Magnetic switch

Table 26. Limiting values...continued

| Symbol              | Description                                                                                    | Condition                                                                                           | Min   | Тур | Max  | Unit |

|---------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------|-----|------|------|

| I <sub>LATCH</sub>  | Latch-up current, current to/from pin to V <sub>DD</sub> /V <sub>DDA</sub> + 0.3 V             | $T_A \text{ Min} \le T_A \le T_A \text{ Max}, V_{DD} \text{ Min} \le V_{DD} \le V_{DD} \text{ Max}$ | -100  | _   | 100  | mA   |

| ESD <sub>HBM</sub>  | Electrostatic discharge, Human<br>Body Model (HBM) all pins                                    | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 1.5 V                                                     | -2000 | _   | 2000 | V    |

| ESD <sub>CDM</sub>  | Electrostatic discharge, Charged Device Model (CDM) all pins                                   | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 1.5 V                                                     | -500  | _   | 500  | V    |

| EOS <sub>EMIR</sub> | Conducted immunity DPI, until OUT unintentionally changes state or I <sup>2</sup> C corruption | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 1.5 V                                                     | _     | 30  | _    | dBm  |

| T <sub>STG</sub>    | Unpowered storage temperature range                                                            | _                                                                                                   | -40   | _   | 150  | °C   |

# 9 Recommended operating conditions

Table 27. Operating conditions

| Symbol             | Description                                                                       | Condition                                                                                           | Min                   | Тур                   | Max                      | Unit |

|--------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------|-----------------------|--------------------------|------|

| Transition         | ns                                                                                |                                                                                                     |                       |                       |                          |      |

| t <sub>OP</sub>    | Power-on initialization                                                           | From V <sub>DD</sub> > 1.2 V to Operation Ready; 25 °C and 1.5 V.                                   | _                     | 4.8                   | 5.1                      | ms   |

| t <sub>BOC-A</sub> | Cleared state to Asserted state phase delay                                       | $T_A \text{ Min} \le T_A \le T_A \text{ Max}, V_{DD} \text{ Min} \le V_{DD} \le V_{DD} \text{ Max}$ | _                     | 100                   | _                        | μs   |

| Voltages           | -                                                                                 |                                                                                                     |                       |                       |                          |      |

| $V_{DD}$           | Operating voltage range where Min = $V_{DD}$ Min, Typ = 1.5 V, Max = $V_{DD}$ Max | $T_A Min \le T_A \le T_A Max$                                                                       | 1.2                   | 1.5                   | V <sub>SUP</sub>         | V    |

| V <sub>STAND</sub> | MODE pin voltage - Standalone mode                                                | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 1.5 V                                                     | V <sub>SS</sub> – 0.3 | _                     | 0.3 x V <sub>DD</sub>    | V    |

| V <sub>STAND</sub> | Mode pin voltage - I <sup>2</sup> C mode                                          | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 1.5 V                                                     | 0.7 x V <sub>DD</sub> | _                     | V <sub>DD</sub><br>+ 0.3 | V    |

| $V_{TH}$           | TH-SDA pin - Standalone mode,<br>Low threshold                                    | TA Min ≤ TA ≤ TA Max, VDD Min<br>≤ VDD ≤ VDD Max                                                    | 0.4 x V <sub>DD</sub> | 0.5 x V <sub>DD</sub> | 0.6 x V <sub>DD</sub>    | V    |

| V <sub>TH</sub>    | TH-SDA pin - Standalone mode,<br>Medium threshold                                 | TA Min ≤ TA ≤ TA Max, VDD Min<br>≤ VDD ≤ VDD Max                                                    | _                     | _                     | 0.3 x V <sub>DD</sub>    | V    |

| $V_{TH}$           | TH-SDA pin - Standalone mode,<br>High threshold                                   | TA Min ≤ TA ≤ TA Max, VDD Min<br>≤ VDD ≤ VDD Max                                                    | 0.7 x V <sub>DD</sub> | _                     | _                        | V    |

| V <sub>ODR</sub>   | ODR-SCL pin - Standalone mode, Low sample rate                                    | TA Min ≤ TA ≤ TA Max, VDD Min<br>≤ VDD ≤ VDD Max                                                    | 0.4 x V <sub>DD</sub> | 0.5 x V <sub>DD</sub> | 0.6 x V <sub>DD</sub>    | V    |

| V <sub>ODR</sub>   | ODR-SCL pin - Standalone mode, Medium sample rate                                 | TA Min ≤ TA ≤ TA Max, VDD Min<br>≤ VDD ≤ VDD Max                                                    | _                     | _                     | 0.3 x V <sub>DD</sub>    | V    |

| V <sub>ODR</sub>   | ODR-SCL pin - Standalone mode, High sample rate                                   | TA Min ≤ TA ≤ TA Max, VDD Min<br>≤ VDD ≤ VDD Max                                                    | 0.7 x V <sub>DD</sub> | _                     | _                        | V    |

Magnetic switch

Table 27. Operating conditions...continued

| Symbol         | Description                                                                                       | Condition                                                   | Min    | Тур | Max | Unit |

|----------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------|-----|-----|------|

| Temperatu      | res                                                                                               |                                                             |        |     |     |      |

| T <sub>A</sub> | Operating temperature range where Min = T <sub>A</sub> Min, Typ = 25 °C, Max = T <sub>A</sub> Max | V <sub>DD</sub> Min ≤ V <sub>DD</sub> ≤ V <sub>DD</sub> Max | –40 °C | 25  | +85 | °C   |

### 10 Characteristics

# 10.1 Supply currents

Table 28. Supply currents

| Symbol                | Description                                        | Condition                                                                                                                                                     | Min | Тур   | Max | Unit |

|-----------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|------|

| I <sub>DDS-LODR</sub> | Supply current, Low ODR                            | Typical value is calculated by a time-weighted average of the consumption during the measurement and sleeping phases while in the Low ODR stand-alone mode.   | _   | 47.5  | 187 | nA   |

| I <sub>DDS-MODR</sub> | Supply current, Medium ODR                         | Typical value is calculated by a time-weighted average of the consumption during the measurement and sleeping phases while in the Medium ODR stand-alone mode | _   | 72.2  | 234 | nA   |

| I <sub>DDS-HODR</sub> | Supply current, High ODR                           | Typical value is calculated by a time-weighted average of the consumption during the measurement and sleeping phases while in the High ODR stand-alone mode.  | _   | 319.6 | 760 | nA   |

| I <sub>DDS-S</sub>    | Supply current, Sleep mode                         | Typ = 25 °C, $V_{DD}$ = 1.5 V Max = $T_A$ Min to $T_A$ Max and $V_{DD}$ Min to $V_{DD}$ Max                                                                   | _   | 42    | 300 | nA   |

| I <sub>DDS-M</sub>    | Supply current, measurement                        | Typ = 25 °C, $V_{DD}$ = 1.5 V Max = $T_A$ Min to $T_A$ Max and $V_{DD}$ Min to $V_{DD}$ Max                                                                   | _   | 580   | 650 | μА   |

| I <sub>DDS-2</sub>    | Supply current, I <sup>2</sup> C command/ response | Typ = 25 °C, 1.5 V, Max = $T_A$ Min $\leq T_A \leq T_A$ Max, $V_{DD}$ Min $\leq V_{DD} \leq V_{DD}$ Max                                                       | _   | 35    | 45  | μА   |

### 10.2 Clocks and rates

Table 29. Clocks and rates

| Symbol           | Description               | Condition                                                                                           | Min | Тур | Max | Unit |

|------------------|---------------------------|-----------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| f <sub>LFO</sub> | Low frequency oscillator  | $T_A \text{ Min} \le T_A \le T_A \text{ Max}, V_{DD} \text{ Min} \le V_{DD} \le V_{DD} \text{ Max}$ | 2.8 | 3.2 | 3.5 | kHz  |

| f <sub>HFO</sub> | High frequency oscillator | $T_A \text{ Min} \le T_A \le T_A \text{ Max}, V_{DD} \text{ Min} \le V_{DD} \le V_{DD} \text{ Max}$ | 1.7 | 2   | 2.3 | MHz  |

NMH1000

All information provided in this document is subject to legal disclaimers.

Magnetic switch

Table 29. Clocks and rates...continued

| Symbol             | Description                  | Condition                                                                                           | Min | Тур | Max | Unit |

|--------------------|------------------------------|-----------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| f <sub>SCL</sub>   | I <sup>2</sup> C input clock | $T_A \text{ Min} \le T_A \le T_A \text{ Max}, V_{DD} \text{ Min} \le V_{DD} \le V_{DD} \text{ Max}$ | _   | _   | 1   | MHz  |

| f <sub>ODR-H</sub> | Sample rate - High           | $T_A \text{ Min} \le T_A \le T_A \text{ Max}, V_{DD} \text{ Min} \le V_{DD} \le V_{DD} \text{ Max}$ | _   | 10  | _   | Hz   |

| f <sub>ODR-M</sub> | Sample rate - Medium         | $T_A \text{ Min} \le T_A \le T_A \text{ Max}, V_{DD} \text{ Min} \le V_{DD} \le V_{DD} \text{ Max}$ | _   | 1   | _   | Hz   |

| f <sub>ODR-L</sub> | Sample rate - Low            | $T_A \text{ Min} \le T_A \le T_A \text{ Max}, V_{DD} \text{ Min} \le V_{DD} \le V_{DD} \text{ Max}$ | _   | 0.1 | _   | Hz   |

# 10.3 I<sup>2</sup>C pin thresholds

Table 30. I<sup>2</sup>C pin thresholds

| Symbol           | Description                       | Condition                                                                                                                  | Min                   | Тур | Max                      | Unit |

|------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------|-----|--------------------------|------|

| V <sub>IH</sub>  | Digital high-level input voltage  | $T_A \text{ Min} \le T_A \le T_A \text{ Max}, V_{DD} \text{ Min} \le V_{DD} \le V_{DD} \text{ Max at } I_{IH} \text{ max}$ | 0.7 x V <sub>DD</sub> | _   | V <sub>DD</sub><br>+ 0.3 | V    |

| V <sub>IL</sub>  | Digital low-level input voltage   | $T_A Min \le T_A \le T_A Max, V_{DD} Min \le V_{DD} \le V_{DD} Max at I_{IL} Max$                                          | V <sub>SS</sub> – 0.3 | _   | 0.3 x V <sub>DD</sub>    | V    |

| V <sub>OH</sub>  | Digital high-level output voltage | $T_A Min \le T_A \le T_A Max, V_{DD} Min \le V_{DD} \le V_{DD} Max at I_{OH} Max$                                          | V <sub>DD</sub> – 0.3 | _   | _                        | V    |

| V <sub>OL</sub>  | Digital low-level output voltage  | $T_A Min \le T_A \le T_A Max, V_{DD} Min \le V_{DD} \le V_{DD} Max at I_{OL} Max$                                          | _                     | _   | V <sub>SS</sub> + 0.3    | V    |

| I <sub>pin</sub> | Digital pin current               | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 1.5 V                                                                            |                       | _   | ±10                      | mA   |

## 10.4 Serial data timing characteristics

Table 31. Serial data timing characteristics

| Symbol                              | Description                                                      | Condition                                                                                            | Min | Тур | Max | Unit |

|-------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Св                                  | Board capacitive load SDA, SCL                                   | $T_A \text{ Min} \le T_A \le T_A \text{ Max}, V_{DD} \text{ Min} \le V_{DD} \le V_{DD} \text{ Max}$  | _   | _   | 1   | μF   |

| t <sub>BUF</sub>                    | Bus free time, between stop and start                            | $T_A \text{ Min} \le T_A \le T_A \text{ Max}, V_{DD} \text{ Min} \le V_{DD} \le V_{DD} \text{ Max}$  | 4.7 | _   | _   | μs   |

| t <sub>HD</sub> to t <sub>STA</sub> | Restart hold, after this period the first clock may be generated | $T_A \text{ Min} \le T_A \le T_A \text{ Max}, V_{DD} \text{ Min} \le V_{DD} \le V_{DD} \text{ Max}$  | 4.0 | _   | _   | μs   |

| t <sub>SU</sub> to t <sub>STA</sub> | Restart setup                                                    | $T_A \text{ Min} \le T_A \le T_A \text{ Max, } V_{DD} \text{ Min} \le V_{DD} \le V_{DD} \text{ Max}$ | 4.7 | _   | _   | μs   |

| t <sub>SU</sub> to t <sub>STO</sub> | Stop setup                                                       | $T_A \text{ Min} \le T_A \le T_A \text{ Max, } V_{DD} \text{ Min} \le V_{DD} \le V_{DD} \text{ Max}$ | 4.0 | _   | _   | μs   |

| t <sub>HD</sub> to t <sub>DAT</sub> | SDA hold                                                         | $T_A \text{ Min} \le T_A \le T_A \text{ Max}, V_{DD} \text{ Min} \le V_{DD} \le V_{DD} \text{ Max}$  | 300 | _   | _   | ns   |

| t <sub>SU</sub> to t <sub>DAT</sub> | SDA setup                                                        | $T_A \text{ Min} \le T_A \le T_A \text{ Max}, V_{DD} \text{ Min} \le V_{DD} \le V_{DD} \text{ Max}$  | 250 | _   | _   | ns   |

| t <sub>LOW</sub>                    | SCL low                                                          | $T_A \text{ Min} \le T_A \le T_A \text{ Max}, V_{DD} \text{ Min} \le V_{DD} \le V_{DD} \text{ Max}$  | 4.7 | _   | _   | μs   |

**Magnetic switch**

Table 31. Serial data timing characteristics...continued

| Symbol            | Description      | Condition                                                                                           | Min | Тур | Max  | Unit |

|-------------------|------------------|-----------------------------------------------------------------------------------------------------|-----|-----|------|------|

| t <sub>HIGH</sub> | SCL high         | $T_A \text{ Min} \le T_A \le T_A \text{ Max}, V_{DD} \text{ Min} \le V_{DD} \le V_{DD} \text{ Max}$ | 4.0 | _   | _    | μs   |

| t <sub>r</sub>    | SDA and SCL rise | $T_A \text{ Min} \le T_A \le T_A \text{ Max}, V_{DD} \text{ Min} \le V_{DD} \le V_{DD} \text{ Max}$ | _   | _   | 1000 | ns   |

| t <sub>f</sub>    | SDA and SCL fall | $T_A \text{ Min} \le T_A \le T_A \text{ Max}, V_{DD} \text{ Min} \le V_{DD} \le V_{DD} \text{ Max}$ | _   | _   | 300  | ns   |

## 10.5 Magnetic field characteristics

Table 32. Magnetic field characteristics

| Symbol             | Description                          | Condition                                       | Min | Тур  | Max  | Unit  |

|--------------------|--------------------------------------|-------------------------------------------------|-----|------|------|-------|

| Transfer F         | unction                              |                                                 |     |      |      |       |

| ВΔ                 | Sensitivity                          | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 1.5 V | _   | 1.75 | _    | G/LSB |

| B <sub>off</sub>   | Offset                               | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 1.5 V | _   | 0    | _    | G     |

| Bhyst              | Assert - Clear hysteresisa           | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 1.5 V | 20  | _    | _    | G     |

| BOC <sub>x-L</sub> | OUT pin transition, Low threshold    | T <sub>A</sub> - 25 °C, V <sub>DD</sub> = 1.5 v | _   | _    | ±100 | G     |

| BOC <sub>x-M</sub> | OUT pin transition, Medium threshold | T <sub>A</sub> - 25 °C, V <sub>DD</sub> = 1.5 v | _   | _    | ±160 | G     |

| BOC <sub>x-H</sub> | OUT pin transition, High threshold   | T <sub>A</sub> - 25 °C, V <sub>DD</sub> = 1.5 v | _   | _    | ±230 | G     |

**Magnetic switch**

# 10.6 I<sup>2</sup>C user mode, output assertion

Table 33. I<sup>2</sup>C user mode, recommended lowest USER\_ASSERT\_THRESH [7:3] output assertion

| Symbol               | Description                                 | Condition                                                           | Min | Тур    | Max | Unit |

|----------------------|---------------------------------------------|---------------------------------------------------------------------|-----|--------|-----|------|

| B <sub>OA</sub> -I2C | Output assertion, magnetic field collapsing | $T_A Min \le T_A \le T_A Max, V_{DD} Min \le V_{DD} \le V_{DD} Max$ | _   | < 0x10 | _   | hex  |

# 10.7 I<sup>2</sup>C user mode, output clear

Table 34. I<sup>2</sup>C user mode, recommended highest USER\_CLEAR\_THRESH [7:3] output clear

| Symbol               | Description                             | Condition                                                                                            | Min | Тур    | Max | Unit |

|----------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------|-----|--------|-----|------|

| B <sub>OC</sub> -I2C | Output clear, magnetic field increasing | $T_A \text{ Min} \le T_A \le T_A \text{ Max, } V_{DD} \text{ Min} \le V_{DD} \le V_{DD} \text{ Max}$ | _   | > 0xF0 | _   | hex  |

# 11 Application information

NMH1000

All information provided in this document is subject to legal disclaimers.

**Magnetic switch**

**Magnetic switch**

**Magnetic switch**

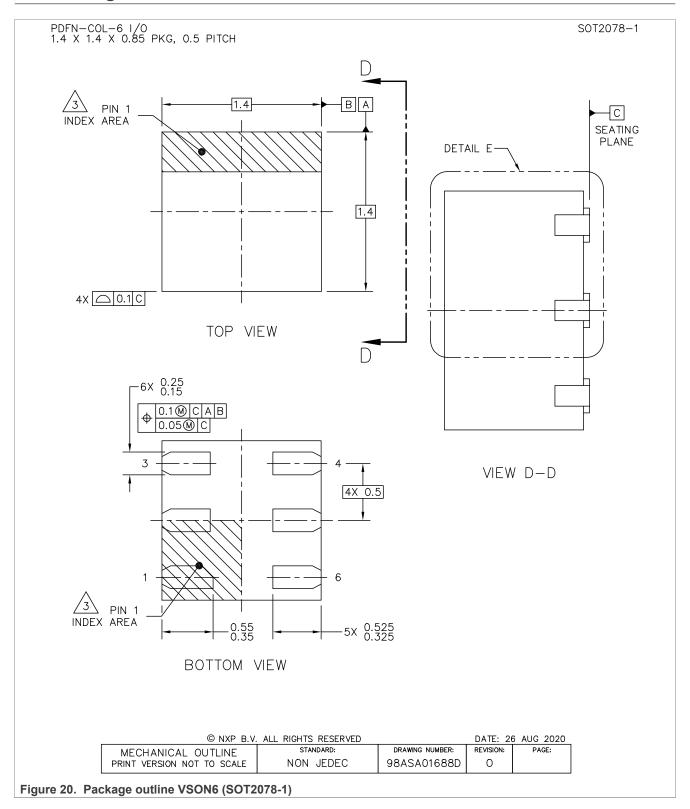

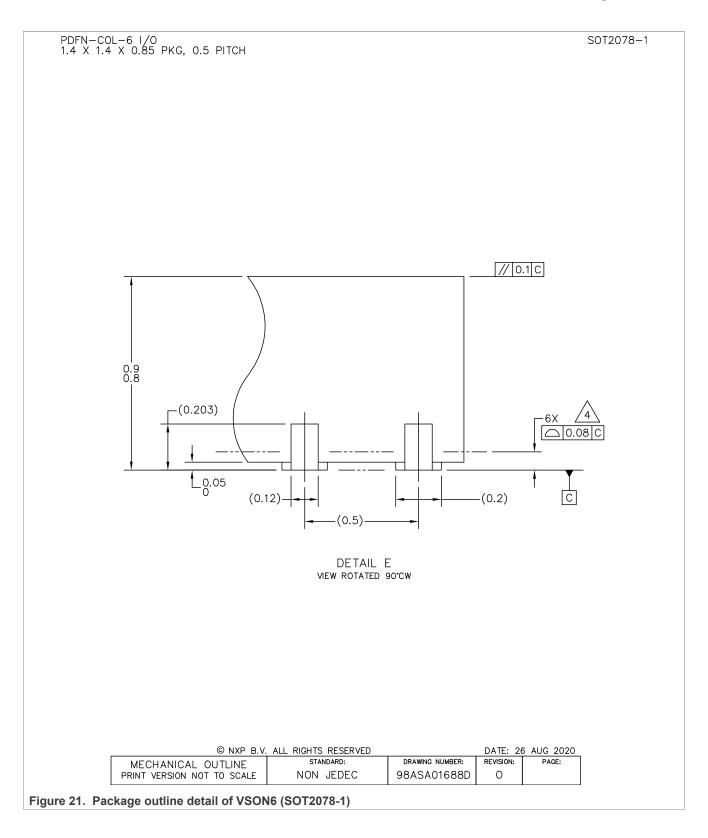

# 12 Package outline

**Magnetic switch**

**Magnetic switch**

PDFN-COL-6 I/O 1.4 X 1.4 X 0.85 PKG, 0.5 PITCH

SOT2078-1

#### NOTES:

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

3.

PIN 1 FEATURE SHAPE, SIZE AND LOCATION MAY VARY.

COPLANARITY APPLIES TO LEADS.

5. MIN. METAL GAP SHOULD BE 0.15 MM.

|   | © NXP B.V.                 | ALL RIGHTS RESERVED |                 | DATE: 26  | 6 AUG 2020 |

|---|----------------------------|---------------------|-----------------|-----------|------------|

|   | MECHANICAL OUTLINE         | STANDARD:           | DRAWING NUMBER: | REVISION: | PAGE:      |

| ı | PRINT VERSION NOT TO SCALE | NON JEDEC           | 98ASA01688D     | 0         |            |

Figure 22. Package outline note VSON6 (SOT2078-1)

**Magnetic switch**

# 13 Soldering information

NMH1000

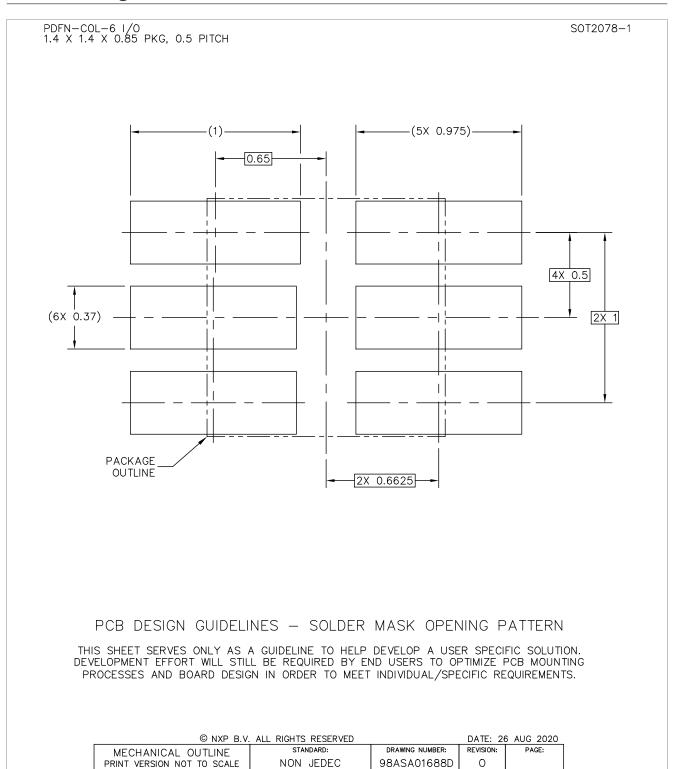

Figure 23. Reflow soldering footprint part 1 for VSON6 (SOT2078-1)

**Magnetic switch**

| © NXP B.V.                 | ALL RIGHTS RESERVED |                 | DATE: 26  | 6 AUG 2020 |

|----------------------------|---------------------|-----------------|-----------|------------|

| MECHANICAL OUTLINE         | STANDARD:           | DRAWING NUMBER: | REVISION: | PAGE:      |

| PRINT VERSION NOT TO SCALE | NON JEDEC           | 98ASA01688D     | 0         |            |

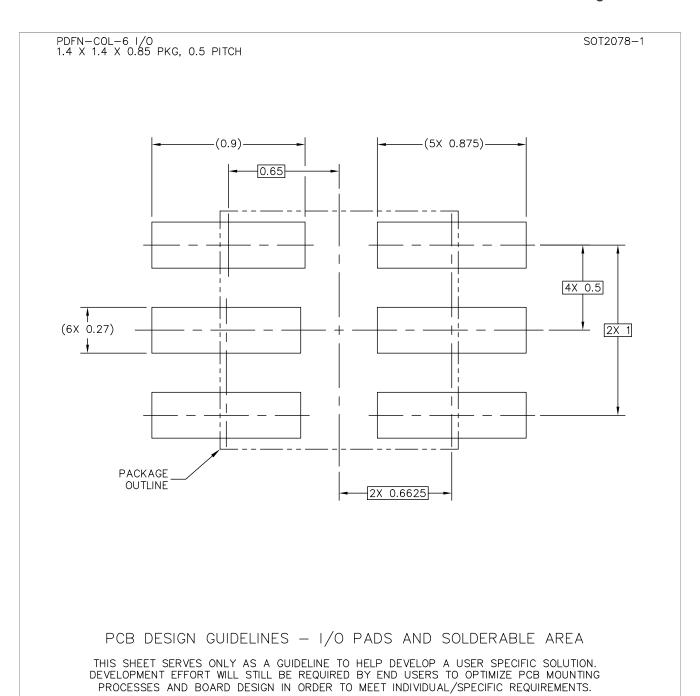

Figure 24. Reflow soldering footprint part 2 for VSON6 (SOT2078-1)

**Magnetic switch**

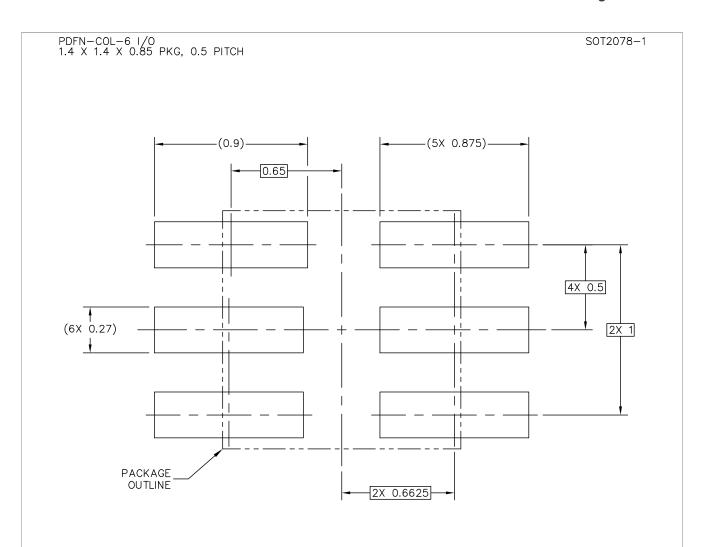

RECOMMENDED STENCIL THICKNESS 0.1

### PCB DESIGN GUIDELINES - SOLDER PASTE STENCIL

THIS SHEET SERVES ONLY AS A GUIDELINE TO HELP DEVELOP A USER SPECIFIC SOLUTION. DEVELOPMENT EFFORT WILL STILL BE REQUIRED BY END USERS TO OPTIMIZE PCB MOUNTING PROCESSES AND BOARD DESIGN IN ORDER TO MEET INDIVIDUAL/SPECIFIC REQUIREMENTS.

|   | © NXP B.V.                 | ALL RIGHTS RESERVED |                 | DATE: 26  | 6 AUG 2020 |

|---|----------------------------|---------------------|-----------------|-----------|------------|

| Г | MECHANICAL OUTLINE         | STANDARD:           | DRAWING NUMBER: | REVISION: | PAGE:      |

|   | PRINT VERSION NOT TO SCALE | NON JEDEC           | 98ASA01688D     | 0         |            |

Figure 25. Reflow soldering footprint part 3 for VSON6 (SOT2078-1)

**Magnetic switch**

## 14 References

[1] AN1902 — Assembly guidelines for QFN (quad flat no-lead) and SON (small outline no-lead) packages <a href="https://www.nxp.com/docs/en/application-note/AN1902.pdf">https://www.nxp.com/docs/en/application-note/AN1902.pdf</a>

# 15 Revision history

Table 35. Revision history