## Frequency Synthesiser (I<sup>2</sup>C BUS Programmable)

## Advance Information

DS2429 - 3.2 September 1994

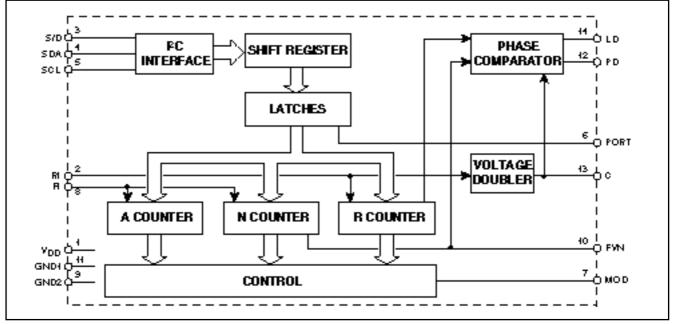

The NJ88C33 is a synthesiser circuit fabricated on Zarlink Semiconductor's 1.4 micron CMOS process, assuring very high performance. It is I<sup>2</sup>C compatible and can also be programmed at up to 5MHz. It contains a 16-bit R counter, a 12-bit N counter and a 7-bit A counter.

A digital phase comparator gives improved loop stability with current source outputs to reduce loop components. A voltage doubler is provided for the loop driver to improve control voltage range to the VCO when operating at low supply voltages.

## FEATURES

- Easy to Use

- Low Power Consumption (15mW)

- Single Supply 2.5V to 5.5V

- Digital Phase Comparator with Current Source Outputs

- Serial (I<sup>2</sup>C Compatible) Programming, 5MHz max

- Channel Loading in 8µs

- 150MHz Input Frequency Without Prescaler at 4.5V (52MHz at 2.7V)

- Standby Modes

- Use of Two-Modulus Prescaler is Possible

#### **APPLICATIONS**

- Cordless Telephones (CT2, DECT)

- Cellular Telephones (GSM, PCN, ETACS)

- Hand Held Marine Radios

- Sonarbuoys

- Video Clock generators

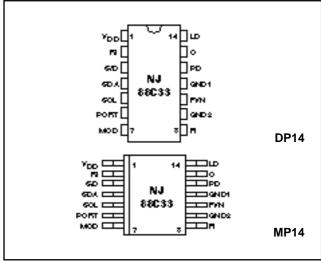

Fig.1 Pin connections (not to scale) - top views

#### ABSOLUTE MAXIMUM RATINGS

| Supply voltage, V <sub>DD</sub>            | -0.3V to 7V                   |

|--------------------------------------------|-------------------------------|

| Input voltage, V <sub>IM1</sub>            | -0.3 to V <sub>DD</sub> +0.3V |

| Output voltage on pin 13, V <sub>IM2</sub> | -V <sub>DD</sub> to 0V        |

| Storage temperature, T <sub>stg</sub>      | -55°C to +125°C               |

#### **ORDERING INFORMATION**

NJ88C33 MA DP (Industrial - Plastic DIL package) NJ88C33 MA MP (Industrial - Miniature Plastic DIL package)

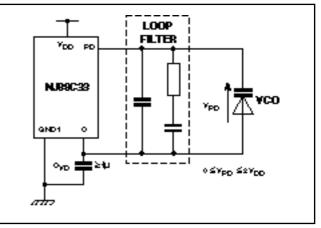

Fig.2 Simplified block diagram of NJ88C33

## **PIN DESIGNATIONS**

| Pin<br>No. | Pin<br>Name     | Description                                                                                                                                                                                                                                                                                                                                 |

|------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | V <sub>DD</sub> | Supply voltage (normally 5V or 3V).                                                                                                                                                                                                                                                                                                         |

| 2          | RI              | Reference frequency input from an accurate source, normally a crystal oscillator. The input is normally an AC coupled sinewave but may be a DC coupled square wave.                                                                                                                                                                         |

| 3          | S/D             | Single/dual modulus operating mode selection input. Single modulus operation is selected by driving the pin low. 'High' selects dual modulus mode.                                                                                                                                                                                          |

| 4          | SDA             | I <sup>2</sup> C bus data input pin. It is also an open-drain output for generating I <sup>2</sup> C bus acknowledge pulses.                                                                                                                                                                                                                |

| 5          | SCL             | I <sup>2</sup> C bus clock input. It can be clocked at up to 5MHz.                                                                                                                                                                                                                                                                          |

| 6          | PORT            | Output control pin, which can be programmed via the I <sup>2</sup> C bus. It can be connected to the S/D pin to select single or dual modulus mode under bus control.                                                                                                                                                                       |

| 7          | MOD             | Modulus control pin. It is high in single modulus mode but switches in dual modulus operation. In dual modulus mode, MOD remains low during operation of the A counter until A=0; MOD then remains high until N=0, when both counters are reloaded. It can be programmed via the I <sup>2</sup> C bus as an open-drain or push-pull output. |

| 8          | FI              | Frequency input from a VCO or prescaler. The input is normally an AC coupled sinewave but may be a DC coupled square wave.                                                                                                                                                                                                                  |

| 9          | GND2            | Dedicated ground for the FI input buffer. It should be connected to the VCO ground or the prescaler ground, if used. Any noise on this pin will affect the performance of the VCO loop.                                                                                                                                                     |

| 10         | FVN             | Open-drain output from the N counter.                                                                                                                                                                                                                                                                                                       |

| 11         | GND1            | Ground supply pin (global).                                                                                                                                                                                                                                                                                                                 |

| 12         | PD              | Tristate current output from the phase detector. The polarity of the output can be programmed via the $I^2C$ bus.                                                                                                                                                                                                                           |

| 13         | С               | Voltage doubler output. The operation of the doubler can be controlled via the I2C bus. In applications where the voltage doubler is switched off, this pin should be connected to GND1; a reservior capacitor should be connected from this pin to GND1 for applications where it is switched on.                                          |

| 14         | LD              | Open-drain lock detect output - requires integration if used.                                                                                                                                                                                                                                                                               |

## **OPERATING RANGE**

## Test conditions (unless otherwise stated):

PLL locked, RI = 10MHz

| Characteristic                                          | Symbol                    |            | Value |            | Unit   | Conditions                                                                                           |

|---------------------------------------------------------|---------------------------|------------|-------|------------|--------|------------------------------------------------------------------------------------------------------|

| Characteristic                                          | Symbol                    | Min.       | Тур.  | Max.       | Unit   | Conditions                                                                                           |

| Supply voltage<br>Ambient temperature<br>Supply current | $V_{_{DD}} \\ T_{_{amb}}$ | 2.5<br>-40 | 5     | 5.5<br>+85 | ∨<br>℃ |                                                                                                      |

| Single modulus                                          | I <sub>DD</sub>           |            | 2.1   | 3.0        | mA     | FI = 50MHz, $V_{FI}$ = 150mVrms, N,R > 1000 without voltage doubler, $V_{DD}$ = 5V, $T_{amb}$ = 25°C |

| Dual modulus                                            | I <sub>DD</sub>           |            | 2     | 3.0        | mA     | FI = 10MHz, $V_{FI}$ = 500mVrms, N,R > 1000 without voltage doubler, $V_{DD}$ = 5V, $T_{amb}$ = 25°C |

| Standby mode                                            | I <sub>DD</sub>           |            |       | 1          | μA     | FI = 50MHz, $V_{FI}$ = 150mVrms, preamp off, divider off, $V_{DD}$ = 5V, $T_{amb}$ = 25°C            |

| Standby mode                                            | I <sub>DD</sub>           |            | 1.0   | 1.5        | mA     | FI = 50MHz, $V_{FI}$ = 150mVrms, preamp on, divider off,<br>$V_{DD}$ = 5V, $T_{amb}$ = 25°C          |

## **ELECTRICAL CHARACTERISTICS**

These characteristics are guaranteed over the following conditions (unless otherwise stated):

$V_{DD}$  = 4.5V to 5.5V,  $T_{amb}$  = -40°C to +85°C INPUT SIGNALS

| Characteristic                                                                                                  | Symbol                                                 |                    | Value |                                                   | Unit                  | Conditions                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------|-------|---------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Characteristic                                                                                                  | Symbol                                                 | Min.               | Тур.  | Max.                                              | Unit                  | Conditions                                                                                                                    |

| Input Signals SDA,<br>SCL, S/D<br>Input voltage high<br>Input voltage low<br>Input capacitance<br>Input current | V⊪<br>V∟<br>C₁<br>I <sub>N</sub>                       | 0.7V <sub>DD</sub> |       | V <sub>DD</sub><br>0.3V <sub>DD</sub><br>10<br>10 | V<br>V<br>pF<br>μA    | $V_{IN} = V_{DD} = 5.5V$                                                                                                      |

| Input signal RI<br>Input frequency<br>Input voltage<br>Input capacitance<br>Input current                       | f<br>V<br>Irms<br>C<br>I<br>I <sub>IN</sub>            | 100                |       | 52<br>10<br>10                                    | MHz<br>mV<br>pF<br>μA | Sinewave input<br>Note 1, 2<br>$V_{IN} = V_{DD} = 5.5V$                                                                       |

| Input signal FI<br>Input frequency<br>Input voltage<br>Input capacitance<br>Input current                       | f<br>V<br>Irms<br>C<br>I<br>I <sub>IN</sub>            | 50                 |       | 52<br>10<br>10                                    | MHz<br>mV<br>pF<br>μA | Dual modulus operation<br>Sinewave input<br>Note 1, 2<br>$V_{IN} = V_{DD} = 5.5V$                                             |

| Input signal FI<br>Input frequency<br>Input voltage                                                             | f <sub>max</sub><br>V<br>Irms<br>VIrms<br>V            | 30<br>100<br>200   |       | 150                                               | MHz<br>mV<br>mV<br>mV | Single modulus operation<br>Sinewave input<br>FI = 0-70MHz Note 1, 2<br>FI = 70-120MHz Note 1, 2<br>FI = 120-150MHz Note 1, 2 |

| Input capacitance<br>Input current                                                                              | V <sub>Irms</sub><br>C <sub>I</sub><br>I <sub>IN</sub> |                    |       | 10<br>10                                          | pF<br>μA              | $V_{IN} = V_{DD} = 5.5V$                                                                                                      |

Note.1Lowest noise floor achieved at 10dB above this level with I<sup>2</sup>C bus operating. The source impedance should be less than 2k .

Note.2DC coupled input amplitude  $V_{IRMS} > 0.8V_{DD}$ .

## **OUTPUT SIGNALS**

| Observationistic                                                                  | Symbol                              |                                | Value                                |                                  | l Init               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|-----------------------------------------------------------------------------------|-------------------------------------|--------------------------------|--------------------------------------|----------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Characteristic                                                                    | Symbol                              | Min.                           | Тур.                                 | Max.                             | Unit                 | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Output Signals SDA, LD<br>Output voltage low                                      | V <sub>ol</sub>                     |                                |                                      | 0.4                              | V                    | Open drain, I <sub>OL</sub> = 3mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

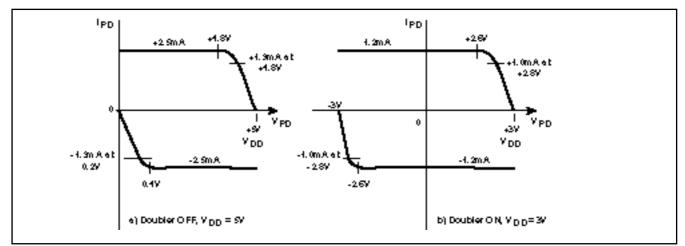

| Output Signal PD<br>High current mode (see Fig.4)<br>Low current mode<br>Tristate | I HU<br>I HD<br>I LU<br>I LD<br>I Z | 1.9<br>-1.9<br>0.475<br>-0.475 | 2.5<br>-2.5<br>0.625<br>-0.625<br>50 | 3.1<br>-3.1<br>0.775<br>-0.775   | mA<br>mA<br>mA<br>nA | $\begin{array}{l} C_{\text{L}} = 400 \text{pF}, \text{ tristate output} \\ 0 < V_{\text{PD}} < 4.5, V_{\text{DD}} = 5\text{V}, \text{T} = 25^{\circ}\text{C} \text{ Note 1} \\ 0.4 < V_{\text{PD}} < 5, V_{\text{DD}} = 5\text{V}, \text{T} = 25^{\circ}\text{C} \text{ Note 1} \\ 0 < V_{\text{PD}} < 4.6, V_{\text{DD}} = 5\text{V}, \text{T} = 25^{\circ}\text{C} \text{ Note 1} \\ 0.4 < V_{\text{PD}} < 5, V_{\text{DD}} = 5\text{V}, \text{T} = 25^{\circ}\text{C} \text{ Note 1} \\ \text{T}_{\text{amb}} = -25^{\circ}\text{C} \text{ to } +60^{\circ}\text{C} \end{array}$ |  |  |  |  |

| Output Signal FVN<br>Output voltage low<br>Output low pulse width                 | V <sub>ol</sub><br>t <sub>wL</sub>  |                                |                                      | 0.4<br>1/Fl                      | V                    | Open drain output<br>$I_{OL} = 1mA$<br>$C_L = 30pF$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| Output Signals MOD, PORT<br>Output voltage high<br>Output voltage low             | V <sub>OH</sub><br>V <sub>OL</sub>  | V <sub>DD</sub> -0.4           |                                      | 0.4                              | V<br>V               | Push-pull output<br>IOH = $0.5$ mA<br>I <sub>OL</sub> = $0.5$ mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Output Signal LD<br>Output voltage low<br>Output low pulse width                  | V <sub>ol</sub><br>t <sub>wL</sub>  |                                | 10                                   | 0.4<br>1/FVN<br>1/f <sub>c</sub> | V<br>ns              | Open drain output<br>$I_{OL} = 3mA, C_L = 30pF$<br>Loop locked<br>Loop not locked<br>FVN = FI/N<br>$f_C = RI/R$                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

Note.1Temperature coefficient for current is typically -0.7%/°C

Fig. 4 Typical output signal PD, high current mode

## VOLTAGE DOUBLER V<sub>DD</sub>

ЗV

| Characteristic                 | Symbol                           |                                      | Value | 9                                                  | Unit   | Conditions                                        |  |  |

|--------------------------------|----------------------------------|--------------------------------------|-------|----------------------------------------------------|--------|---------------------------------------------------|--|--|

| Characteristic                 | Symbol                           | Min.                                 | Тур.  | Max.                                               | Onit   | Conditions                                        |  |  |

| Output Pin C<br>Output voltage | V <sub>c</sub><br>V <sub>c</sub> | -V <sub>DD</sub><br>-V <sub>DD</sub> |       | -V <sub>DD</sub> + 0.8V<br>-V <sub>DD</sub> + 1.5V | V<br>V |                                                   |  |  |

| Current Consumption            | I <sub>D</sub>                   |                                      |       | 100                                                | μA     | $f_{VD} = 2MHz, \ I_{OC} = 0\mu A, \ V_{DD} = 3V$ |  |  |

#### TIMING INFORMATION

| Characteristic                                                                               | Symbol                                                                   |             | Value |                         | Unit                             | O an differen                                                                                                                                                               |

|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------|-------|-------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Characteristic                                                                               | Symbol                                                                   | Min.        | Тур.  | Max.                    | Onit                             | Conditions                                                                                                                                                                  |

| Input Signal RI<br>Input frequency<br>Input frequency<br>Rise time<br>Fall time<br>Slew rate | f <sub>max</sub><br>f <sub>max</sub><br>t <sub>R</sub><br>t <sub>F</sub> | 0<br>0<br>3 |       | 52<br>10<br>1.5<br>1.5  | MHz<br>MHz<br>μs<br>V/μs         | $V_{DD} = 2.7V$                                                                                                                                                             |

| Input Signal FI<br>Input frequency<br>Input frequency<br>Rise time<br>Fall time<br>Slew rate | f <sub>max</sub><br>f <sub>max</sub><br>t <sub>R</sub><br>t <sub>F</sub> | 0<br>0<br>3 |       | 52<br>20<br>1.5<br>1.5  | MHz<br>MHz<br>μs<br>V/μs         | Dual modulus<br>$V_{DD} = 2.7V$                                                                                                                                             |

| Input Signal FI<br>Input frequency<br>Input frequency<br>Rise time<br>Fall time<br>Slew rate | f <sub>max</sub><br>f <sub>max</sub><br>t <sub>R</sub><br>t <sub>F</sub> | 0<br>0<br>3 |       | 150<br>52<br>1.5<br>1.5 | MHz<br>MHz<br>μs<br>V/μs<br>V/μs | Single modulus<br>V <sub>DD</sub> = 2.7V                                                                                                                                    |

| Output Signal PORT<br>Rise time<br>Fall time                                                 | t <sub>R</sub><br>t <sub>F</sub>                                         |             |       | 1<br>1                  | μs<br>μs                         | $C_L = 30pF$<br>$C_L = 30pF$                                                                                                                                                |

| Output Signal FVN<br>Fall time                                                               | t <sub>F</sub>                                                           |             | 20    |                         | ns                               | C <sub>L</sub> = 30pF                                                                                                                                                       |

| Output Signal MOD<br>Rise time<br>Fall time<br>Delay time (L H)<br>Delay time (H L)          | t <sub>R</sub><br>t <sub>F</sub><br>t <sub>DLH</sub><br>t <sub>DHL</sub> |             |       | 10<br>10<br>15<br>15    | ns<br>ns<br>ns<br>ns             | $\begin{array}{l} C_L = 30 p F \\ Measured from +Ve edge of FI \\ C_L = 30 p F \\ Measured from +Ve edge of FI \end{array}$ |

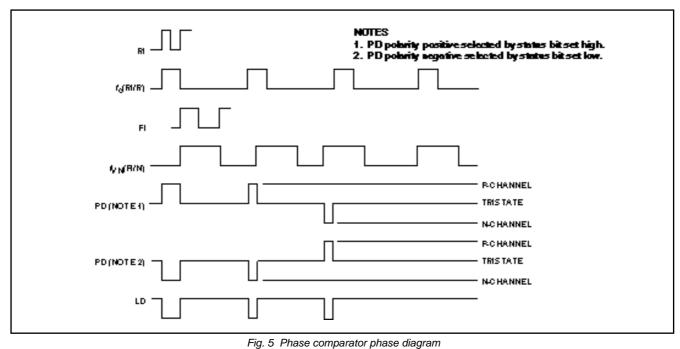

#### PHASE COMPARATOR

The phase comparator produces current pulses of duration equal to the difference in phase between the comparison frequency (fc=RI/R), and  $f_{_{VN}}$ , the divided-down VCO frequency (FI/N).

When status bit 4 is set high the positive polarity mode of the output PD is selected. When fc leads  $f_{VN}$  the PD output goes high; when  $f_{VN}$  leads fc it goes low. Similarly, selecting the negative polarity mode of PD by programming bit 4 of the status register low causes PD to have the inverse polarity. The loop filter integrates the current pulses to produce a voltage drive to the VCO.

No pulses are produced when locked. The lock detect output, LD, produces a logic '0' pulse equal to the phase difference between  $\rm f_c$  and  $\rm f_{\rm VN}.$

When the phase difference between fc and  $f_{vN}$  is too small to be resolved by the phase detector then no current pulses are produced. In this region the loop does not reduce the close-in noise on the VCO output. This can be overcome using a very high value resistor to leak a few nanoAmps of current from the filter and keep the loop on the edge of the region.

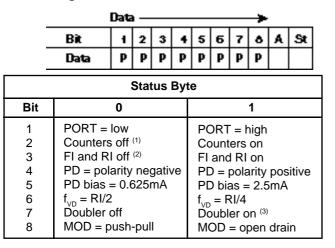

PROGRAMMING

#### **Transmission Protocol**

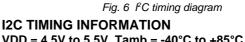

I<sup>2</sup>C programming messages consist of an address byte followed by a sub-address byte followed by 1, 2 or 3 bytes of data. Bit 7 of the address byte must match the setting of the S/D pin for the address to be recognised. This allows for separate addressing of two NJ88C33 synthesisers on the same bus. The sub-address should be set to select the correct registers to be programmed and should be followed by the appropriate number of data bytes. Registers are not programmed until the complete message protocol has been checked.

Each message should commence with a START condition and end with a STOP condition unless followed immediately by another transfer, when the STOP condition may be omitted.

Data is transferred from the shift register to the latches on a STOP condition or by a second START condition.

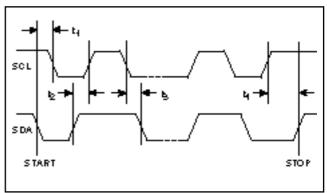

A START condition is indicated by a falling edge on the Serial Data line, SDA, when the Serial Clock line. SCL, is high.

A rising edge on SDA when SCL is high indicates a STOP condition as shown in Fig.6.

Data on SDA is clocked into the NJ88C33 on the rising edge of SCL. The NJ88C33 acknowledges each byte transferred to it by pulling the SDA line low for one cycle of SCL after the last bit has been received.

| VDD = 4.5V to 5.5V, Tame | 1 = -40 C        | 10 +05 | 0    |     |

|--------------------------|------------------|--------|------|-----|

| Parameter                | Symbol           | Va     | Unit |     |

|                          | • • • • • •      | Min.   | Max. | •   |

| Serial clock frequency   | f <sub>scl</sub> |        | 5    | MHz |

| SCL hold after START     | t,               | 200    |      | ns  |

| Data set-up time         | t <sub>2</sub>   | 20     |      | ns  |

| Data hold after SCL low  | t <sub>3</sub>   | 0      |      | ns  |

| SCL set-up before STOP   | t <sub>4</sub>   | 20     |      | ns  |

#### Address and Sub-Address Formats

The correct addressing sequence for the NJ88C33 is shown below. The START condition is followed by the address byte, the acknowledge from the NJ88C33, the subaddress byte, another acknowledge then the associated data. The correct values for each address and sub-address are listed, together with the message selection options.

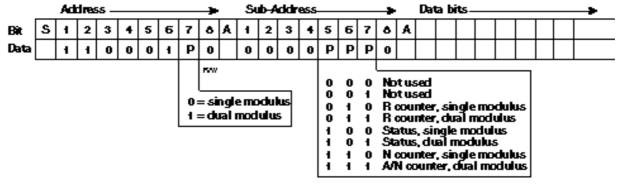

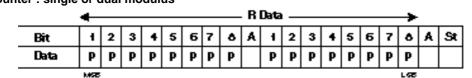

#### **Data Formats**

Each of the data formats should be preceded contiguously by the addressing sequence given above.

R counter : single or dual modulus

Status : single or dual modulus

#### NOTES

In this standby mode the counters are disabled but the voltage doubler and I<sup>2</sup>C interface can both function.

In this standby mode the FI and RI preamplifiers are disabled, which stops the counters and the voltage doubler. The I<sup>2</sup>C interface still operates.

3. The voltage doubler should only be used when  $V_{_{DD}}$  3.0V

#### N counter : single modulus

|      |   |   | 🖌 🔤 N Data |   |   |      |   |   |   |   |   |   | – N Data —————————————————————————————————— |   |   |   |     |   |    |  |  |

|------|---|---|------------|---|---|------|---|---|---|---|---|---|---------------------------------------------|---|---|---|-----|---|----|--|--|

| Bit  | 1 | 2 | 3          | 4 | 5 | 6    | 7 | 8 | A | 1 | 2 | 3 | 4                                           | 5 | 6 | 7 | ð   | A | St |  |  |

| Data | X | x | x          | x | Р | P    | P | Р |   | Р | P | P | P                                           | P | P | P | Р   |   |    |  |  |

|      |   |   |            |   |   | N#SE |   |   |   |   |   |   |                                             |   |   |   | LGE |   |    |  |  |

#### A/N counters : dual modulus

|      |   |   |   |   |   | •    |   |   | A | Data | ) |   | •   | •    |   |   |   |   | N D | bta | _ |   |   |   |   | •   |   |    |

|------|---|---|---|---|---|------|---|---|---|------|---|---|-----|------|---|---|---|---|-----|-----|---|---|---|---|---|-----|---|----|

| Bit  | 1 | 2 | 3 | 4 | 5 | 6    | 7 | ٥ | A | 1    | 2 | 3 | 4   | 5    | 6 | 7 | ٥ | A | 1   | 2   | 3 | 4 | 5 | 6 | 7 | ٥   | A | St |

| Data | x | x | x | X | Р | P    | P | Р |   | P    | Р | P | Р   | P    | P | P | Р |   | P   | P   | Р | Р | P | P | P | P   |   |    |

|      |   |   |   |   |   | MISE | : |   |   |      |   |   | LGE | N458 |   |   |   |   |     |     |   |   |   |   |   | LGE |   |    |

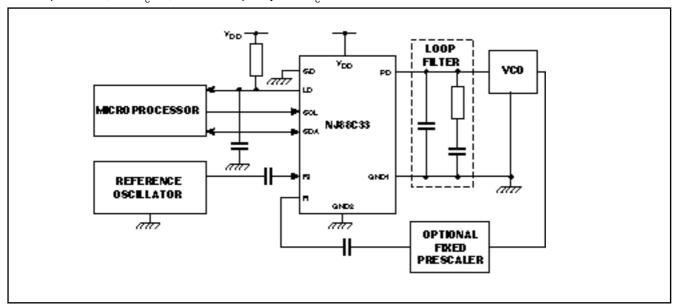

#### APPLICATION CIRCUITS Single Modulus

In this mode, the NJ88C33 synthesiser can be used with or without a fixed modulus prescaler. The R counter is programmed with a value to produce a comparison frequency fc. When the N counter is changed by 1 the loop is no longer in lock and the phase detector output produces current pulses to bring the loop back into lock. These pulses are integrated by the loop filter to produce the VCO voltage drive. When the VCO loop is locked,  $Fl/N=f_c$  i.e., the VCO frequency is N x f<sub>c</sub>. Using a prescaler with a division ratio P, the smallest VCO output frequency step is  $Pf_c$  and the VCO frequency is  $PNf_c$ . If a low pass filter is connected to the lock detect output as

shown and sampled by the microprocessor, the proximity of the synthesiser loop to lock can be evaluated.

The A counter is not used in this mode.

Fig. 7 Single modulus application

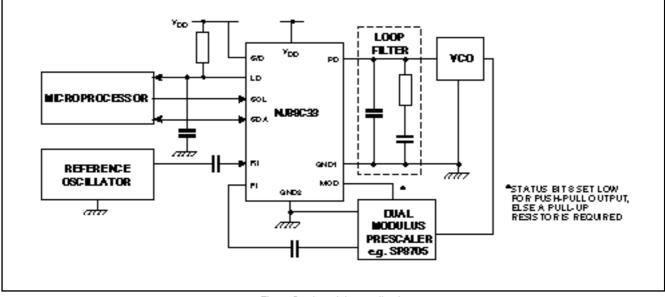

#### **Dual Modulus**

This mode allows much higher frequencies to be used in conjunction with a prescaler but maintains the step size, fc. In this mode, a dual modulus prescaler (with ratios P and P + 1) must be used with the NJ88C33. The A counter controls the MOD output, which is used to select the division ratio of the prescaler.

When the A counter is non-zero, the MOD output is low and goes high when the A counter has counted down to zero. MOD remains high until the N counter reaches zero, when both counters are re-loaded. Thus, the prescaler divides by P for N-A cycles and by P + 1 for A cycles of FI. The VCO frequency is given by  $PNf_c + Af_c$ .

Note that programming A = 0 produces a count of 128 cycles.

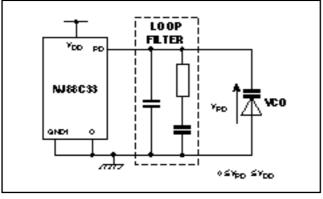

#### VCO Driving Without Voltage Doubler

To switch off the voltage doubler, bit 7 of the status register is programmed low. This will reduce current consumption and minimise noise. The voltage doubler output C should be connected to GND1 as connection to GND2 would induce noise in the VCO loop.

Fig. 9 Driving a VCO without voltage doubler

#### **Further Applications Information**

A stand-alone programmer card and an evaluation board are available for evaluating the NJ88C33. The programmer card allows two sets of variables to be programmed into both the divider and status registers during alternate programming cycles, at either the standard I<sup>2</sup>C bus rate of 100kHz or at 2MHz.

Initialisation is with either a manual push-button or by an external logic level pulse; a synchronisation output is provided to allow a quick assessment of 'step' and 'settle' responses to be made.

#### VCO Driving With Voltage Doubler

The voltage doubler is switched on by setting bit 7 of the status register high. It is recommended that a reservoir capacitor of at least  $1\mu$ F be connected from C to GND1.

The voltage doubler is designed to boost VCO drive in low voltage applications.

Fig. 10 Driving a VCO using the voltage doubler

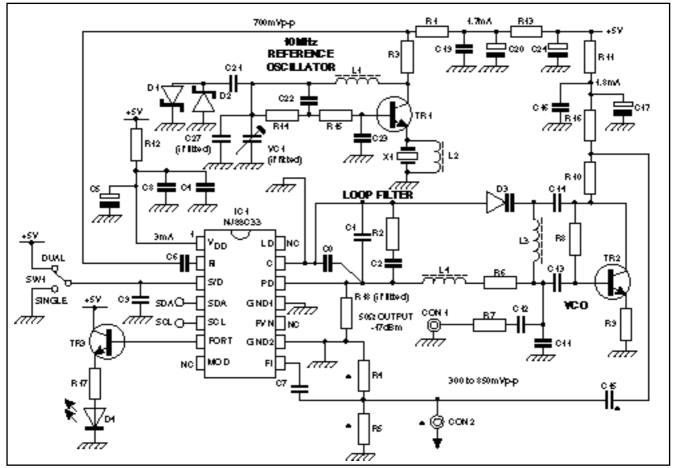

The NJ88C33 evaluation board (Fig. 11) dernonstrates the preferred layout technique - providing a reference oscillator, a 60 to 80MHz VCO and a simple loop filter to complete a minimal frequency synthesiser loop. The two units allow analysis of different loop variables as well as the selection of comparison frequencies for fast frequencyhopping loops.

Application Note: AN94, *'Using* the NJ88C33 *PLL Synthesiser'* explains the design equations and demonstrates the use of the device, and is available from your local Zarlink Semiconductor customer service centre.

Fig. 11 Typical applications circuit

\* Insert C15, delete R4 and R5 if CON2 is to be used to monitor the VCO. Delete C15 insert R4 and R5 if CON is to provide an external source, otherwise short C15 and delete R4, R5 and CON2.

#### **COMPONENT LIST FOR FIG. 11**

|                                        | Сар                                                                                     | acito                                  | rs                                                                                                       | Re                               | sistors                                      |                      | Inductors                                                          | Miscellaneous                           |                                                                                                  |  |  |  |

|----------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------------------------|----------------------|--------------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|

| C0<br>C1<br>C2<br>C4<br>C5<br>C6<br>C7 | 1nF 10%<br>100nF 10%<br>1μF Tant.<br>10nF 10%<br>22μF/35V Elect.<br>10nF 10%<br>1nF 10% | C19<br>C20<br>C21<br>C22<br>C23<br>C24 | 22μF/35V Elect.<br>10nF 10%<br>22μF/35V Elect.<br>10nF 10%<br>10nF 10%<br>22pF 5% NPO<br>22μF/35V Elect. | R2<br>R3<br>R4<br>R5<br>R6<br>R7 | 270<br>470<br>330<br>100<br>100<br>1k<br>120 | L1<br>L2<br>L3<br>L4 | 15μΗ 10%<br>220μΗ 10%<br>180nΗ 20%<br>470μΗ 10%<br><b>Diodes</b>   | IC1<br>X1<br>SW1<br>CON1<br>CON2<br>PCB | NJ88C33<br>10.00MHz 5ppm series<br>Miniature slide switch<br>SMC socket<br>SMC socket<br>C33ISS2 |  |  |  |

| C8<br>C9<br>C11<br>C12<br>C13          | 1nF 10%<br>1nF 10%<br>150pF 5% NPO<br>1nF 10%<br>1nF 10%                                | VC1                                    | 22pF 5% NPO<br>3p5-22p                                                                                   | R8<br>R9<br>R10<br>R11<br>R12    | 27k<br>Link<br>1k<br>10<br>10                | D1<br>D2<br>D3<br>D4 | 1N6263 Schottky<br>1N6263 Schottky<br>BBY40 varicap<br>5mm red LED |                                         |                                                                                                  |  |  |  |

| C14                                    | 2p7 ± 0.5pF NPO                                                                         |                                        |                                                                                                          | R13                              | 10                                           |                      | Transistors                                                        |                                         |                                                                                                  |  |  |  |

| C15<br>C16                             | 10nF 10%<br>10nF 10%                                                                    |                                        |                                                                                                          | R14<br>R15<br>R16<br>R17<br>R18  | 22k<br>2.7k<br>330R<br>100<br>33M            | TR1<br>TR2<br>TR3    | BFS17 RF NPN<br>BFS17 RF NPN<br>2N3904 Switching                   |                                         |                                                                                                  |  |  |  |

NOTES

1. With the exception of electrolytics, all capacitors are surface mount types.

2. All resistors are 0.25W, ±2%.

3. C0, C1, C2, C11, C12, C13 and C14 must be low leakage types.

4. R18 may be required to optimise VCO close in noise performance.

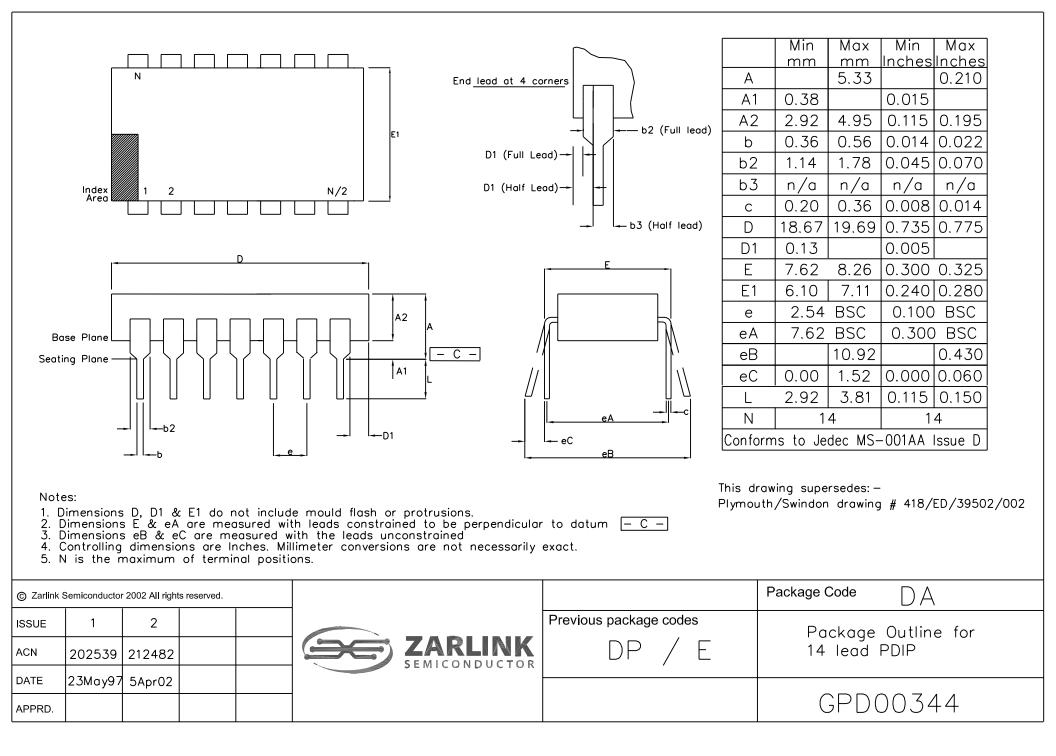

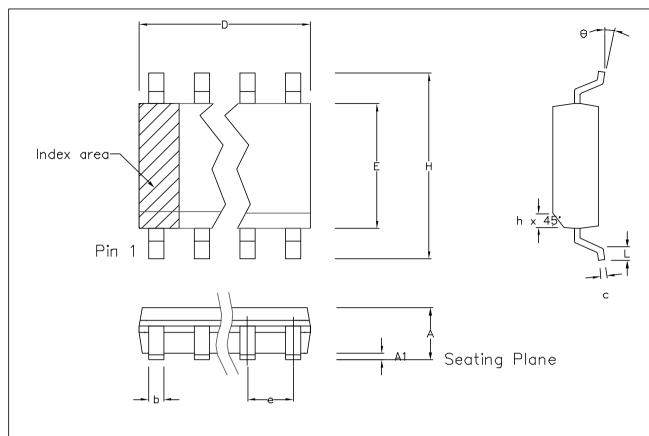

|                                   | Min                     | Max   | Min   | Max   |  |  |  |  |  |  |  |  |

|-----------------------------------|-------------------------|-------|-------|-------|--|--|--|--|--|--|--|--|

|                                   | mm                      | mm    | inch  | inch  |  |  |  |  |  |  |  |  |

| A                                 | 1.35                    | 1.75  | 0.053 | 0.069 |  |  |  |  |  |  |  |  |

| A1                                | 0.10                    | 0.010 |       |       |  |  |  |  |  |  |  |  |

| D                                 | D 8.55 8.75 0.337 0.344 |       |       |       |  |  |  |  |  |  |  |  |

| <u> </u>                          | 5.80                    | 6.20  | 0.228 | 0.244 |  |  |  |  |  |  |  |  |

| E                                 | 3.80                    | 4.00  | 0.150 | 0.157 |  |  |  |  |  |  |  |  |

| L                                 | 0.40                    | 1.27  | 0.016 | 0.050 |  |  |  |  |  |  |  |  |

| е                                 | 1.27                    | BSC   | 0.050 | BSC   |  |  |  |  |  |  |  |  |

| b                                 | 0.33                    | 0.51  | 0.013 | 0.020 |  |  |  |  |  |  |  |  |

| С                                 | 0.19                    | 0.25  | 0.008 | 0.010 |  |  |  |  |  |  |  |  |

| 0                                 | ٥°                      | රී    | °()   | 8°    |  |  |  |  |  |  |  |  |

| h                                 | 0.25                    | 0.50  | 0.010 | 0.020 |  |  |  |  |  |  |  |  |

|                                   | Pin Features            |       |       |       |  |  |  |  |  |  |  |  |

| N 14 14                           |                         |       |       |       |  |  |  |  |  |  |  |  |

| Conforms to JEDEC MS-012AB Iss. C |                         |       |       |       |  |  |  |  |  |  |  |  |

## Notes:

- 1. The chamfer on the body is optional. If not present, a visual index feature, e.g. a dot, must be located within the cross-hatched area.

- 2. Controlling dimensions are in inches.

- 3. Dimension D do not include mould flash, protusion or gate burrs. These shall not exceed 0.006" per side.

- 4. Dimension E1 do not include inter-lead flash or protusion. These shall not exceed 0.010" per side.

- 5. Dimension b does not include dambar protusion / intrusion. Allowable dambar protusion shall be 0.004" total in excess of b dimension.

| © Zarlink | Semiconducto | or 2003 All right | s reserved. |        |         |  |                          | Package Code           |                                     |

|-----------|--------------|-------------------|-------------|--------|---------|--|--------------------------|------------------------|-------------------------------------|

| ISSUE     | 6            | 2                 | 3           | 4      | 5       |  | ZARLINK<br>SEMICONDUCTOR | Previous package codes | Package Outline for                 |

| ACN       | 214220       | 201937            | 202596      | 203707 | 212430  |  |                          | MP / S                 | 14 lead SOIC<br>(0.150" Body Width) |

| DATE      | 7Apr03       | 27Feb97           | 12Jun97     | 9Dec97 | 25Mar02 |  |                          |                        |                                     |

| APPRD.    |              |                   |             |        |         |  |                          |                        | GPD00011                            |

# For more information about all Zarlink products visit our Web Site at

## www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's I<sup>2</sup>C components conveys a licence under the Philips I<sup>2</sup>C Patent rights to use these components in and I<sup>2</sup>C System, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright Zarlink Semiconductor Inc. All Rights Reserved.

TECHNICAL DOCUMENTATION - NOT FOR RESALE