# **NID1100**

1.5 V to 5.5 V, 1 A, ideal diode with forward voltage blocking Rev. 2 — 17 March 2025 Product data sheet

## 1. General description

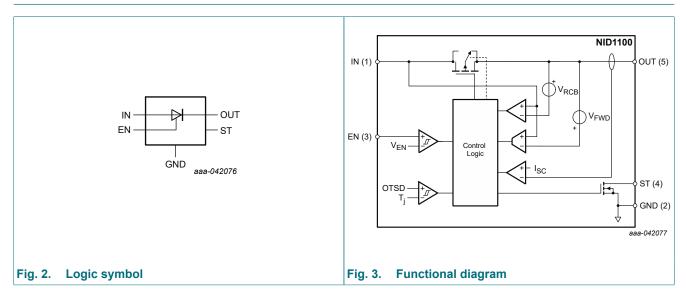

The NID1100 is a low forward-voltage drop ideal diode with forward and reverse voltage blocking. It can be used to replace rectifiers in low voltage systems unable to tolerate the high voltage drops of conventional Schottky diodes. The device operates over an input voltage range of 1.5 V to 5.5 V and can support up to 1 A continuous current. They can also be used in dual supply systems in an OR-ing configuration to switch the load seamlessly from one supply to the next.

The EN pin determines the operation mode of the NID1100. When EN is low, the NID1100 blocks voltages in both forward and reverse directions. When the enable input goes high, and the input voltage is higher than the output voltage, the NID1100 starts up in controlled manner limiting the inrush current. Once inrush is complete, the device regulates the voltage between the IN and OUT pins resulting in a forward voltage drop,  $V_{FWD}$ , approximately an order of magnitude smaller than similarly rated Schottky diodes. If at any time, the OUT voltage becomes higher than IN voltage, the NID1100 stops conducting with very low leakage currents.

NID1100 also includes short circuit current limiting and over temperature shut down to provide robust protection against load fault conditions. The opendrain ST pin can be used to monitor the status of the NID1100. The ST pin pulls low when the device is disabled, in reverse voltage blocking state or in over temperature shut down.

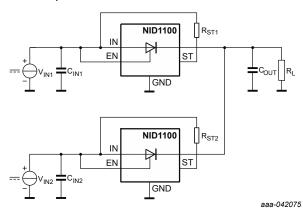

A variety of power OR-ing configurations are supported for system flexibility:

- Two, or more, NID1100 devices

- NID1100s and conventional Schottky diodes

- NID1100 and an external PMOS

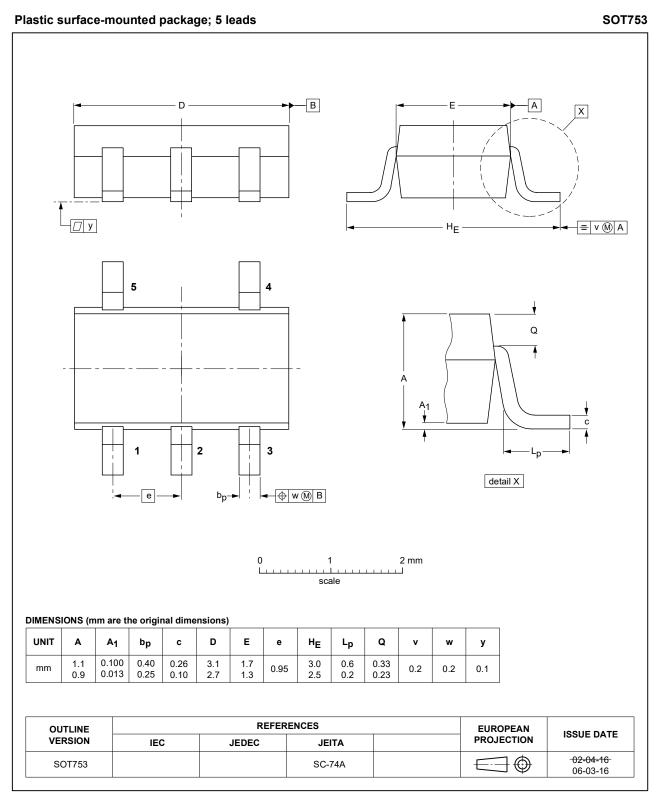

The NID1100 is available in a standard SOT753 (SC-74A) package and is characterized for operation over a junction temperature range of -40 °C to 125 °C.

## 2. Features and benefits

- Input voltage range of 1.5 V to 5.5 V

- Low forward drop voltage: V<sub>FWD</sub> = 120 mV (typ. at 3.6 V input and 1 A load current)

- Reverse voltage blocking always

- Low leakage current when reverse biased

- Forward voltage blocking when disabled

- Low quiescent current

- Enhanced load transient response

- · Controlled rise time at start-up

- Over temperature protection

- Short circuit protection

- SOT753 (SC-74A) 5 pins plastic surface-mounted package

- Specified over T<sub>i</sub>= -40 °C to +125 °C

## 3. Applications

- IoT systems

- · Gas meters, smart meters

- CO Detectors

- Battery backup systems

- USB powered devices

Fig. 1. Simplified application

## 4. Ordering information

| Table 1. Ordering information |                     |        |                                          |               |  |  |  |

|-------------------------------|---------------------|--------|------------------------------------------|---------------|--|--|--|

| Type number                   | Type number Package |        |                                          |               |  |  |  |

|                               | Temperature range   | Name   | Description                              | Version       |  |  |  |

| NID1100GV                     | -40 °C to +125 °C   | SC-74A | plastic surface-mounted package; 5 leads | <u>SOT753</u> |  |  |  |

## 5. Marking

| Table 2. Marking code |              |  |  |  |

|-----------------------|--------------|--|--|--|

| Type number           | Marking code |  |  |  |

| NID1100GV             | u2           |  |  |  |

## 6. Functional diagram

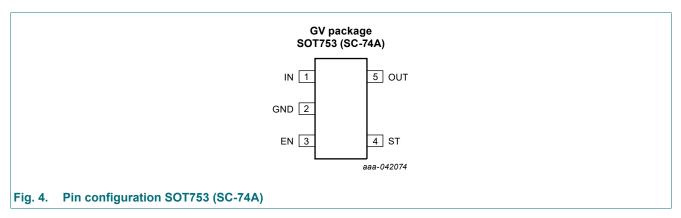

# 7. Pin configuration and description

## 7.1. Pin configuration

NID1100

## 7.2. Pin description

| Symbol | Pin | I/O | Description                                                                                                                                                                                                          |  |  |

|--------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| IN     | 1   | 1   | "Anode" connection of the ideal diode. Connect to a power supply. Bypass with a low ESR capacitance of at least 0.1 $\mu\text{F}.$                                                                                   |  |  |

| GND    | 2   | GND | Ground (0 V)                                                                                                                                                                                                         |  |  |

| EN     | 3   | I   | Active high enable input to the IC. Connect to IN to permanently enable th device. Connect to GND to disable. Connect EN to an I/O to control it. Do leave this pin floating.                                        |  |  |

| ST     | 4   | 0   | Active Low status output. Pulls low during when device is disabled, in reverse voltage blocking state or in over temperature shut down. Pull up with a resistor to IN. Leave floating or connect to GND if not used. |  |  |

| OUT    | 5   | 0   | "Cathode" connection of the ideal diode. Connect to the load. Bypass with a low ESR capacitance of at least 0.33 $\mu F_{\rm c}$                                                                                     |  |  |

## 8. Specifications

## 8.1. Limiting values

### Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).

| Symbol           | Parameter                   | Conditions | Min  | Max | Unit |

|------------------|-----------------------------|------------|------|-----|------|

| V <sub>IN</sub>  | input voltage               |            | -0.3 | 6   | V    |

| V <sub>OUT</sub> | output voltage              |            | -0.3 | 6   | V    |

| V <sub>EN</sub>  | EN pin voltage              |            | -0.3 | 6   | V    |

| V <sub>ST</sub>  | ST pin voltage              |            | -0.3 | 6   | V    |

| I <sub>ST</sub>  | max current into status pin |            | -    | 1   | mA   |

| Tj               | junction temperature        |            | -40  | 125 | °C   |

| T <sub>stg</sub> | storage temperature         |            | -65  | 150 | °C   |

## 8.2. ESD ratings

#### Table 5. ESD ratings

| Symbol           | Parameter               | Conditions                            | Value | Unit |

|------------------|-------------------------|---------------------------------------|-------|------|

| V.               | electrostatic discharge | HBM: ANSI/ESDA/JEDEC JS-001 class 2   | ±2000 | V    |

| V <sub>ESD</sub> | electrostatic discharge | CDM: ANSI/ESDA/JEDEC JS-002 class C2a | ±500  | V    |

nent feedback

## 8.3. Recommended operating conditions

### Table 6. Recommended operating conditions

Voltages are referenced to GND (ground = 0 V).

| Symbol                                            | Parameter                     | Conditions                                            | Min | Мах | Unit |

|---------------------------------------------------|-------------------------------|-------------------------------------------------------|-----|-----|------|

| V <sub>IN</sub>                                   | input voltage                 |                                                       | 1.5 | 5.5 | V    |

| V <sub>OUT</sub>                                  | output Voltage                |                                                       | 0   | 5.5 | V    |

| I <sub>OUT</sub> max continuous output<br>current |                               | >2.0 V input                                          | -   | 1   | А    |

|                                                   |                               | 1.6 V to 1.9 V                                        |     | 0.5 | А    |

|                                                   |                               | 1.5 V                                                 |     | 50  | mA   |

| I <sub>OUT,SW</sub>                               | maximum pulsed switch current | ≤120 ms, 2% duty-cycle, V <sub>IN</sub> = 3.3 V/5.0 V | -   | 1.5 | A    |

| V <sub>EN</sub>                                   | EN Pin voltage                |                                                       | 0   | 5.5 | V    |

| I <sub>ST</sub>                                   | current into ST pin           |                                                       | 0   | 0.5 | mA   |

| C <sub>OUT</sub>                                  | total capacitance at OUT      | including derating and tolerances                     | 0.3 | 100 | μF   |

## 8.4. Thermal information

### Table 7. Thermal information

Thermal resistance according to JEDEC51-5 and -7

| Symbol           | Parameter                                  | SOT753 | Unit |

|------------------|--------------------------------------------|--------|------|

| R <sub>OJA</sub> | junction-to-ambient thermal resistance     | 206    | °C/W |

| $\Psi_{JT}$      | junction-to-top characterization parameter | 111    | °C/W |

ent feedb

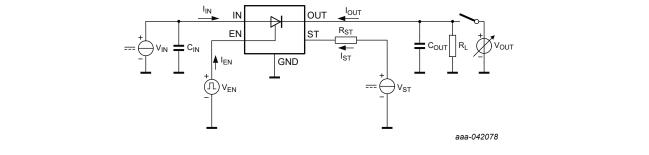

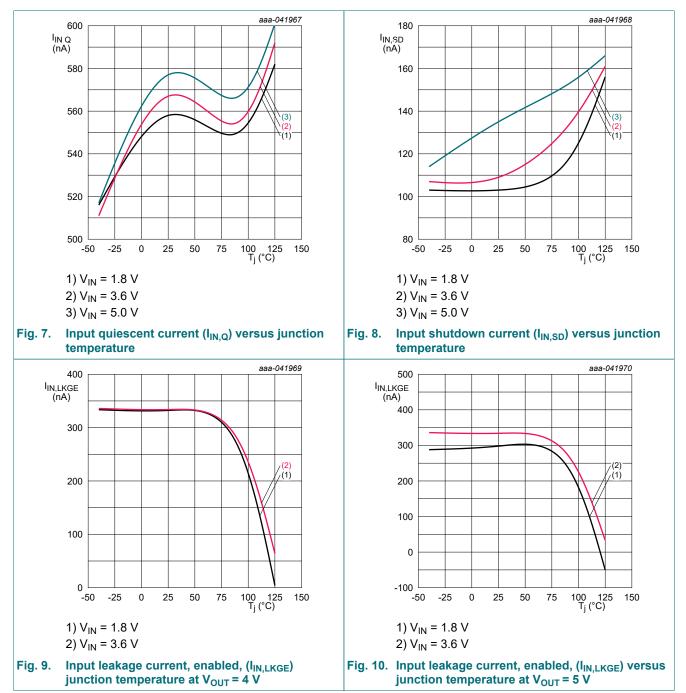

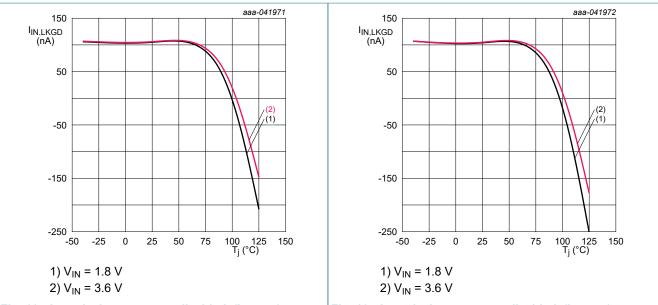

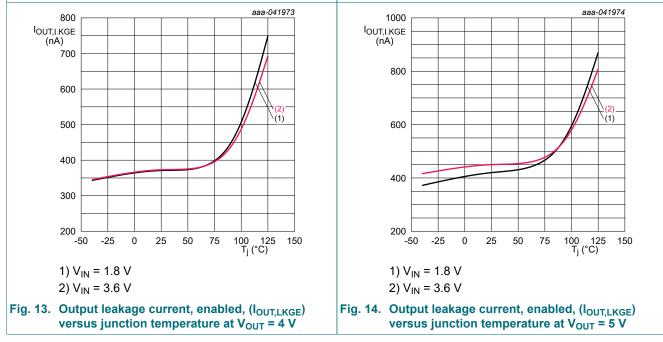

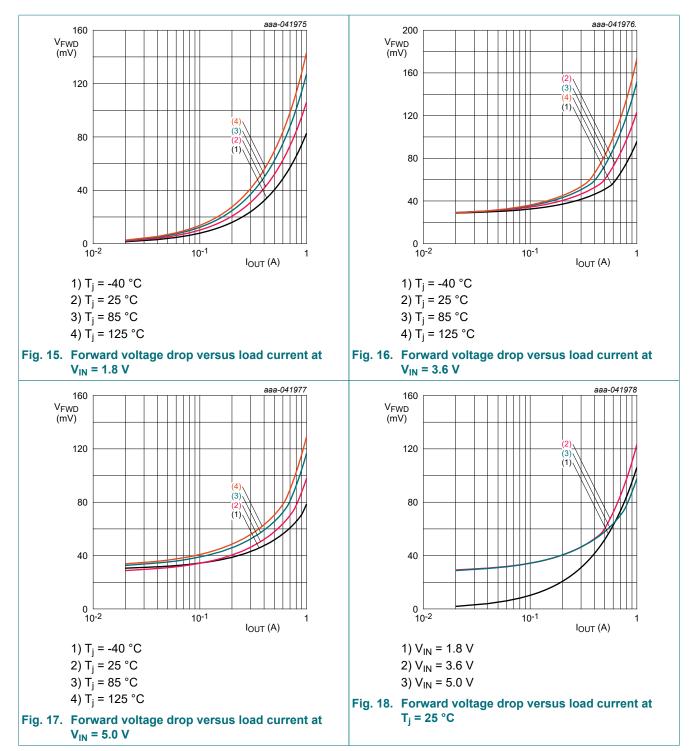

## 8.5. Electrical characteristics

#### Table 8. Static characteristics

$V_{IN}$  = 3.6 V,  $V_{EN}$  = 3.6 V,  $R_{ST}$  = 36.5 k $\Omega$  pull-up resistor to 3.6 V,  $C_{OUT}$  = 0.33  $\mu$ F unless otherwise specified.

| Symbol                | Parameter                                               | Conditions                                                     |     | T <sub>j</sub> = | 40 °C to +1 | Unit |    |

|-----------------------|---------------------------------------------------------|----------------------------------------------------------------|-----|------------------|-------------|------|----|

|                       |                                                         |                                                                |     | Min              | Typ[1]      | Max  |    |

| Input                 |                                                         |                                                                |     |                  |             |      |    |

| I <sub>IN,Q</sub>     | input quiescent current                                 | V <sub>EN</sub> = V <sub>IN</sub>                              |     | -                | 562         | 725  | nA |

| I <sub>IN,SD</sub>    | input shutdown current                                  | EN = LO                                                        |     | -                | 108         | 250  | nA |

| Pass FET              |                                                         | 1                                                              |     |                  | - <b>-</b>  |      |    |

| V <sub>FWD</sub>      | forward voltage drop                                    | V <sub>IN</sub> = 1.5 V; I <sub>O</sub> = 50 mA                |     | -                | 55          | 97   | mV |

|                       |                                                         | V <sub>IN</sub> = 3.6 V; I <sub>O</sub> = 100 mA               |     | -                | 36          | 75   |    |

|                       |                                                         | V <sub>IN</sub> = 3.6 V; I <sub>O</sub> = 500 mA               | [2] | -                | 62          | 100  | mV |

|                       |                                                         | V <sub>IN</sub> = 3.6 V; I <sub>O</sub> = 1000 mA              | [2] | -                | 119         | 180  | mV |

|                       |                                                         | V <sub>IN</sub> = 5.5 V; I <sub>O</sub> = 100 mA               |     | -                | 40          | 70   | mV |

| Reverse (             | Current Blocking                                        |                                                                |     |                  | 1           |      |    |

| V <sub>RCBA</sub>     | RCB activation voltage                                  | V <sub>OUT</sub> - V <sub>IN</sub> ; ST pin goes from HI to LO |     | -                | 31          | -    | mV |

| V <sub>RCBD</sub>     | RCB deactivation voltage                                | $V_{IN}$ - $V_{OUT}$ ; ST pin goes from LO to HI               |     | -                | 41          | -    | mV |

| I <sub>IN,LKGE</sub>  | leakage current into IN,                                | V <sub>OUT</sub> = 4 V                                         | [2] | -220             | 331         | 615  | nA |

| enabled               |                                                         | V <sub>OUT</sub> = 5 V                                         |     | -220             | 332         | 615  | nA |

| I <sub>OUT,LKGE</sub> | I <sub>OUT,LKGE</sub> leakage current into OUT, enabled | V <sub>OUT</sub> = 4 V                                         | [2] | -200             | 372         | 1200 | nA |

| OU I,ENOL             |                                                         | V <sub>OUT</sub> = 5 V                                         |     | -200             | 449         | 1200 | nA |

| I <sub>IN,LKGD</sub>  | leakage current into IN,                                | V <sub>OUT</sub> = 4 V; EN = LO                                | [2] | -500             | -           | 500  | nA |

|                       | disabled                                                | V <sub>OUT</sub> = 5 V; EN = LO                                |     | -500             | -           | 500  | nA |

| Enable ip             | ut                                                      |                                                                |     |                  | 1           |      |    |

| V <sub>EN,HI</sub>    | enable high threshold                                   | ST goes LO to HI                                               |     | 1.2              | -           | -    | V  |

| V <sub>EN,LO</sub>    | enable low threshold                                    | ST goes HI to LO                                               |     | -                | -           | 0.4  | V  |

| V <sub>EN,HYS</sub>   | enable hysteresis                                       |                                                                |     | -                | 45          | -    | mV |

| I <sub>EN,HI</sub>    | enable input current                                    | V <sub>EN</sub> = 3.6 V                                        |     | -                | -           | 50   | nA |

| Status pir            | n                                                       | 1                                                              |     |                  |             |      |    |

| V <sub>OL,ST</sub>    | status low threshold                                    | ST pin sinking 100 μA                                          |     | -                | -           | 0.3  | V  |

| I <sub>LKG,ST</sub>   | status pin leakage current                              | EN = 3.6 V                                                     |     | -75              | -           | 75   | nA |

| Short Circ            | cuit Protection                                         |                                                                |     |                  | ı           |      | _  |

| I <sub>LIM</sub>      | over current limit                                      | R <sub>L</sub> = 100 mΩ                                        |     | -                | 2.8         | -    | А  |

| Over Tem              | perature Shutdown                                       |                                                                |     |                  | ı           |      | _  |

| T <sub>OTSD</sub>     | overtemperature shut down                               | T <sub>j</sub> rising                                          | [2] | 170              | 175         | -    | °C |

| T <sub>OTHYS</sub>    | over temperature<br>hysteresis                          | T <sub>j</sub> falling                                         | [2] | -                | 35          | -    | °C |

|                       | 1                                                       | I                                                              |     |                  | 1           |      |    |

[1]

All typical values are measured at  $T_{amb}$  = 25 °C. Not tested in production. Obtained by characterization. [2]

nent feedback

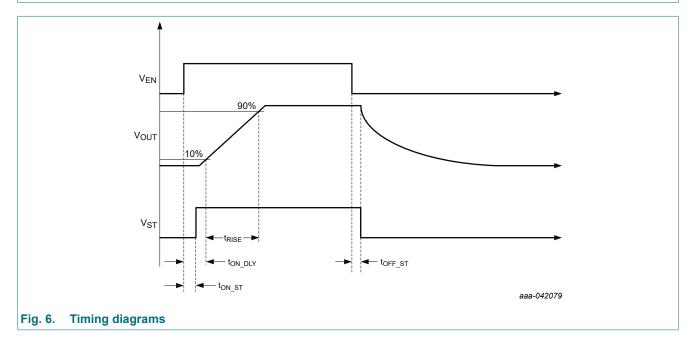

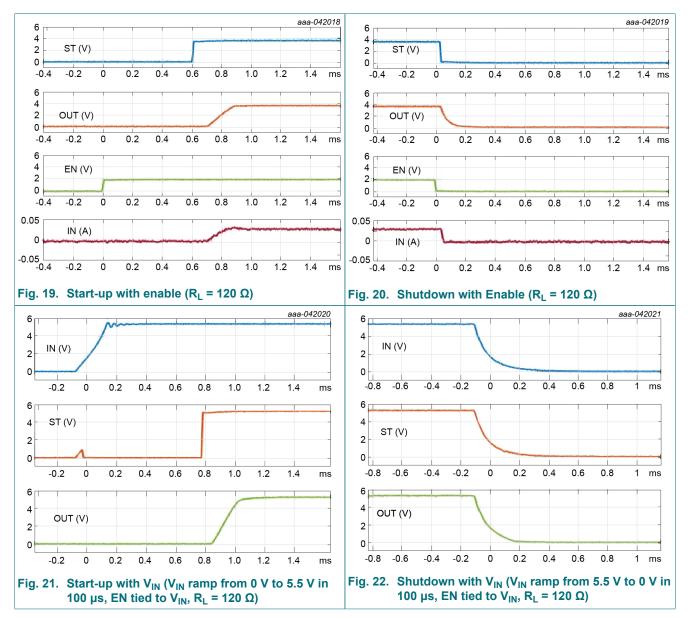

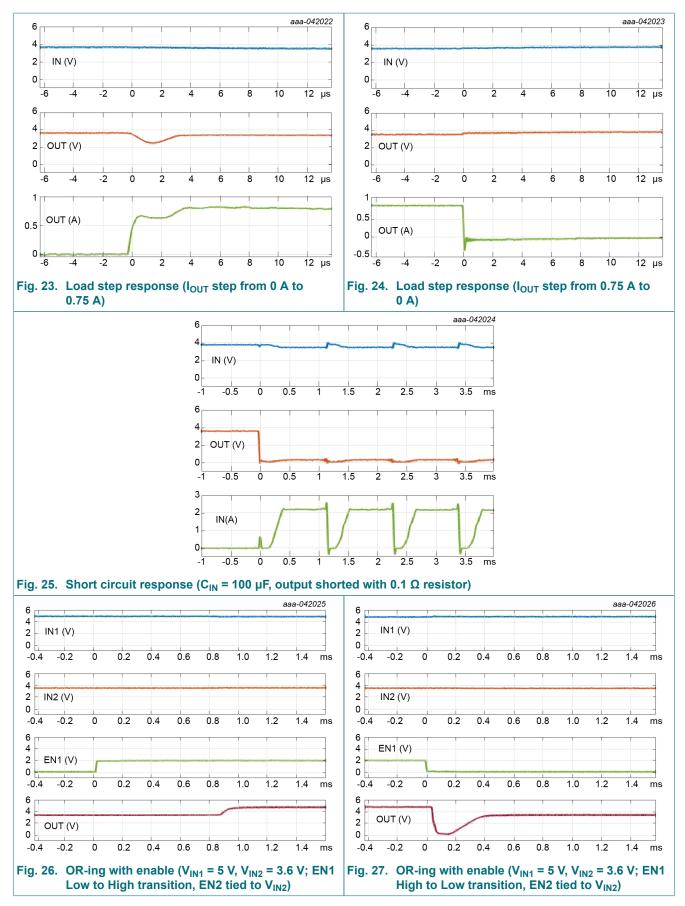

## 8.6. Dynamic characteristics

### Table 9. Dynamic characteristics

$V_{IN}$  = 3.6 V,  $R_{ST}$  = 36.5 k $\Omega$  pull-up resistor to 3.6 V,  $C_{OUT}$ = 1  $\mu$ F,  $R_L$  = open unless otherwise specified.

| Symbol              | Parameter                     | Conditions                                                           |     | T <sub>j</sub> = 25 °C |     | ;   | Unit |

|---------------------|-------------------------------|----------------------------------------------------------------------|-----|------------------------|-----|-----|------|

|                     |                               |                                                                      |     | Min                    | Тур | Max |      |

| t <sub>ON,ST</sub>  | status ON delay time          | EN = LO to HI step to ST = LO to HI step                             | [1] | -                      | 600 | -   | μs   |

| t <sub>OFF,ST</sub> | status OFF delay time         | EN = HI to LO step to ST = HI to LO step                             | [1] | -                      | 45  | -   | μs   |

| t <sub>ON,DLY</sub> | turn-On delay time            | $V_{EN}$ = LO to HI step to $V_{OUT}$ = 10 %                         |     | -                      | 756 | -   | μs   |

| t <sub>RISE</sub>   | rise time                     | V <sub>OUT</sub> = 10 % to V <sub>OUT</sub> = 90%                    |     | -                      | 100 | -   | μs   |

| t <sub>RCB</sub>    | reverse current blocking time | $V_{OUT} = V_{IN}$ -100 mV to $V_{IN}$ +100mV step to $I_{IN}$ <1 mA | [1] | -                      | 8   | -   | μs   |

| t <sub>LIM</sub>    | current limit response time   | OUT shorted with 100 m $\Omega$ to $I_{OUT}$ within 10% of $I_{LIM}$ | [1] | -                      | 115 | -   | μs   |

#### [1] Not tested in production. Obtained by characterization.

### Fig. 5. Test circuit

## 8.7. Typical characteristics graphs

NID1100

7 / 26

## NID1100

### 1.5 V to 5.5 V, 1 A, ideal diode with forward voltage blocking

## NID1100

#### 1.5 V to 5.5 V, 1 A, ideal diode with forward voltage blocking

© Nexperia B.V. 2025. All rights reserved

## 8.8. Typical characteristics graphs

nent feedback

NID1100 Submit document feedt All information provided in this document is subject to legal disclaimers.

© Nexperia B.V. 2025. All rights reserved

# NID1100

### 1.5 V to 5.5 V, 1 A, ideal diode with forward voltage blocking

nent feedback

## 9. Functional Description

### 9.1. Overview

NID1100 is a low voltage ideal diode capable of blocking voltages in either direction. It has integrated protection features like Inrush Current Limit, Reverse Voltage Blocking, and Over Temperature Protection. It comes in a small 5-pin SOT753 (SC-74A) package.

### 9.2. Startup

The device starts when the voltage at either IN or OUT pins reach 1.5 V. Until then, there is insufficient voltage to power up the internal circuitry.

When  $V_{IN}$  exceeds 1.5 V (and  $V_{OUT} < V_{IN}$ ), the device enters Power-On-Reset (POR). In this situation, the switch is held OFF and the body diode is oriented such that the anode is at OUT and cathode is at IN. If EN pin goes high, the IC starts charging the output capacitor with an internally controlled slew rate. Once the capacitor is fully charged, the internal FET's gate is controlled by a transconductance amplifier to maintain a constant difference between  $V_{IN}$  and  $V_{OUT}$  to emulate a diode. If EN is pulled low at any time, the FET is turned OFF.

## 9.3. Functional modes

<u>Table 10</u> summaries the various functional modes of the NID1100 and the status of the diode and the ST pin in each mode.

| Functional mode          | EN pin | ST pin | Power device state                            |  |  |

|--------------------------|--------|--------|-----------------------------------------------|--|--|

| OFF                      | LOW    | LOW    | Forward blocking                              |  |  |

| ON                       | HIGH   | High-Z | Forward conduction regulated V <sub>FWD</sub> |  |  |

| Reverse current blocking | Х      | LOW    | Reverse blocking                              |  |  |

| Output short             | HIGH   | High-Z | Forward conduction regulated IOUT             |  |  |

| Thermal fault            | HIGH   | LOW    | Reverse blocking                              |  |  |

Table 10. Device functional modes ( $V_{IN} \ge 1.5 V$ )

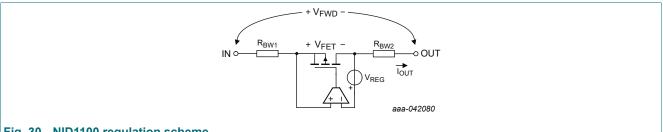

The forward drop of the NID1100 depends on the input voltage and load current. Fig. 30 shows the internal block diagram of the NID1100 in forward regulation mode. Based on this figure, the drop seen between the IN and OUT pins ( $V_{FWD}$ ) is given by the equation

$$V_{FWD} = I_{OUT} \times (R_{BW1} + R_{BW2}) + V_{FET}$$

where I<sub>OUT</sub> is the load current, R<sub>BW1</sub> and R<sub>BW2</sub> are the bond wire impedances and V<sub>FET</sub> is the voltage drop across the FET.

#### Fig. 30. NID1100 regulation scheme

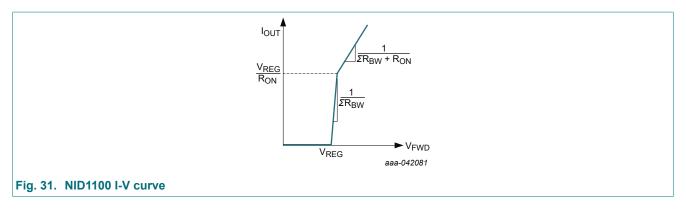

The voltage drop across the FET is regulated to V<sub>REG</sub> until the load current increases to a point where

$$I_{OUT} = \frac{V_{REG}}{R_{ON}}$$

Where R<sub>ON</sub> is the resistance of the FET.

The overall variation of the forward voltage incorporating all these effects is shown in Fig. 31.

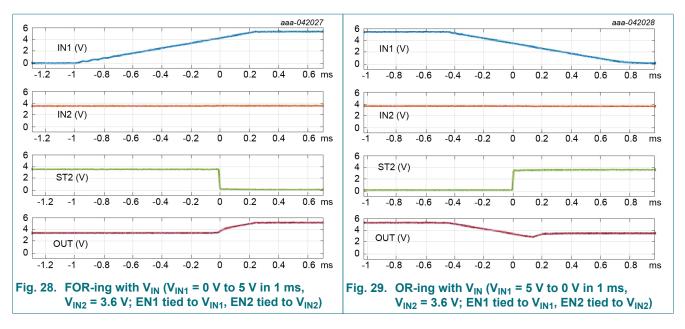

### 9.4. Reverse current blocking

Reverse Current Blocking (RCB) protection is always active, regardless of the state of EN. This protects the power supply from having to sink currents.

Two scenarios can activate the reverse current blocking functional mode.

- · Output voltage starts rising and exceeds the input voltage (eg: OR-ing with two different voltage levels)

- Input voltage starts falling and goes below the output voltage (eg: loss of input power)

In either case, the NID1100 tries to maintain the forward drop between  $V_{IN}$  and  $V_{OUT}$ . As the  $V_{IN}$ - $V_{OUT}$  differential starts reducing, the transconductance amplifier modulates the gate of the FET to increase its resistance to maintain the  $V_{IN} - V_{OUT}$  differential. Once  $V_{IN} \le V_{OUT}$ , the transconductance amplifier turns off the pass transistor and prevents reverse currents. An internal comparator detects when  $V_{IN} \le V_{OUT}$  -  $V_{RCBA}$  and flips the body diode polarity to ensure that the diode remains reverse biased.

When  $V_{IN}$  starts rising (or  $V_{OUT}$  starts falling) and  $V_{IN}$  exceeds  $V_{OUT} + V_{RCBD}$ , the diode polarity is flipped such that the anode is at IN and the pass FET starts conducting.

In case of an extremely fast transition from forward conduction to reverse bias, the comparator also acts to turn off the pass transistor before the transconductance amplifier has a chance to react.

## 9.5. Output overload and temperature protection

Unlike conventional diodes and other ideal diodes, the NID1100 is also protected from output short circuit and over temperature conditions. This is due to its unique feature of being able to block voltages in either direction.

When the output current exceeds  $I_{LIM}$ , the NID1100 limits the current through the device to  $I_{LIM}$ . It will stay in this current regulation mode until the output overload condition disappears or the junction temperature of the part exceeds  $T_{OTSD}$ .

Once an over temperature condition is detected, the NID1100 turns of the pass transistor. Once the NID1100 cools down such that  $T_i < T_{OTSD} - T_{HYS}$ , the part attempts restart in an inrush controlled manner.

NID1100

## **10.** Application information

**Note:** Application implementation information in the following sections is not part of the Nexperia component specification. Nexperia's device users are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

The NID1100 ideal diode is a versatile device suitable for high side power switching, protecting against reverse current conditions, OR-ing and simple power multiplexing. The following sections provide application examples to aid the design of products using NID1100.

## 10.1. Startup

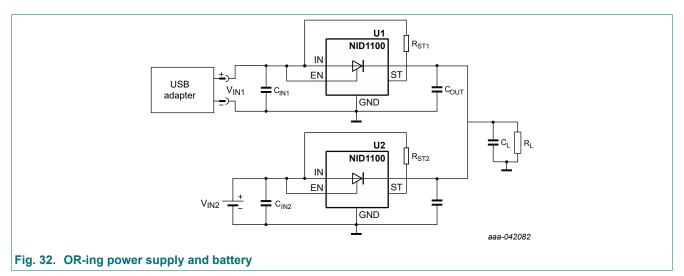

#### 10.1.1. n+1 OR-ing using ideal diodes

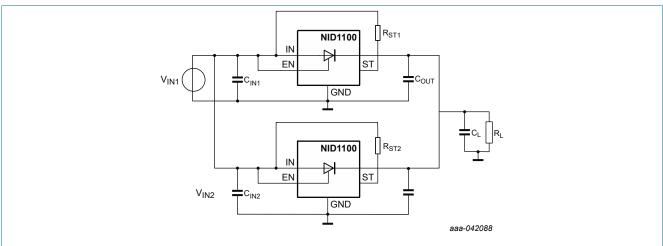

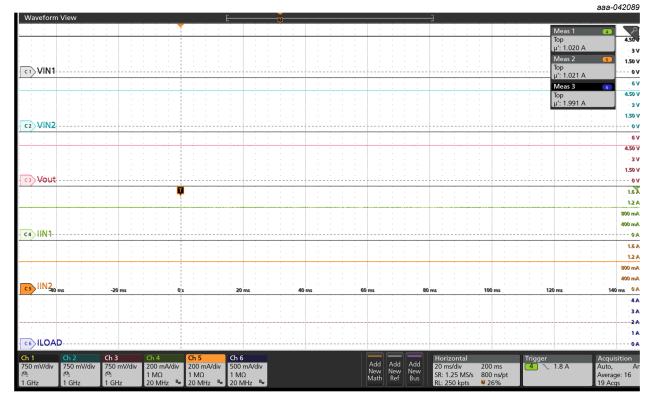

There is no specific limitation to the number of NID1100 ideal diodes used for power OR-ing. The example below illustrates a common two power supply scenario with smooth transitions between supplies.

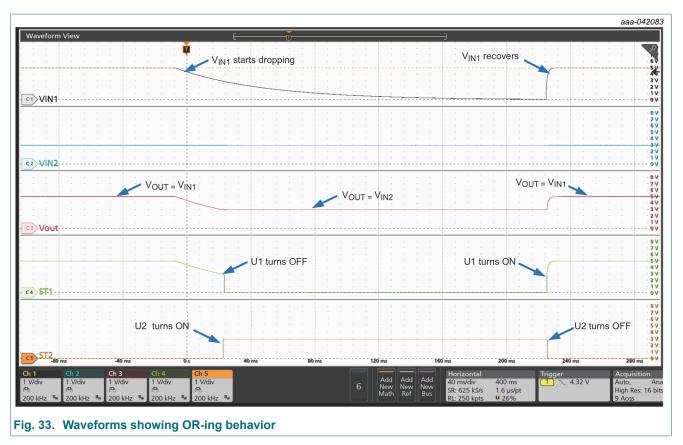

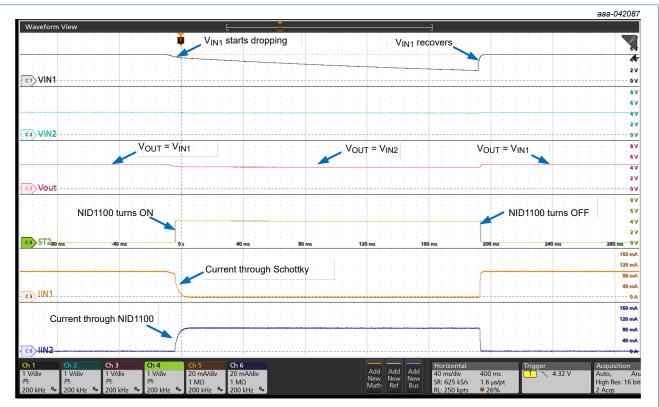

Some devices operate from a fixed power supply such as a standard 5 V USB port output in normal conditions but must quickly transition to a 3 V battery backup when the power supply is disabled or unplugged. Using two NID1100 devices in a power OR-ing configuration, the downstream load remains uninterrupted when either the DC supply or the backup battery are disconnected.

The scope capture shows the output voltage ( $V_{OUT}$ ) being initially powered by  $V_{IN1}$  at 5 V. When  $V_{IN1}$  is removed,  $V_{IN2}$  at 3.0 V powers  $V_{OUT}$ . When  $V_{IN1}$  is reconnected,  $V_{OUT}$  is once again powered by  $V_{IN1}$ . The ST pins of the NID1100's transition to indicate which ideal diode is supplying the load.

### 10.1.2. OR-ing similar supply voltages

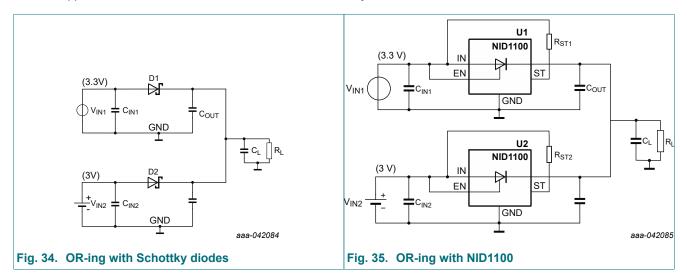

Some applications may require the OR-ing of supplies with similar voltages (eg: Fig. 34 and Fig. 35). In these examples, the primary DC supply is 3.3 V with a 3 V battery backup. Consider the scenario where  $V_{IN1}$ , which is initially supplying the load, is removed and subsequently restored.

In case of the OR-ing scenario with Schottky diodes, as the two supplies differ by only 300 mV, when  $V_{IN1}$  is restored, there may not be enough forward voltage,  $V_F$ , across the diode in the  $V_{IN1}$  path to forward bias it. Thus,  $V_{IN2}$  will continue to deliver power to the load until the battery voltage depletes sufficiently wasting energy in the backup source.

In case of the OR-ing scenario with NID1100s, when  $V_{IN1}$  is restored, the reverse current blocking deactivation threshold,  $V_{RCBD}$ , is easily exceeded allowing the 3.3 V supply to carry the full load. As the OUT is approximately 300 mV above  $V_{IN2}$ , the 3 V supplied NID1100 becomes reverse biased and the battery drain is minimized.

NID1100

© Nexperia B.V. 2025. All rights reserved

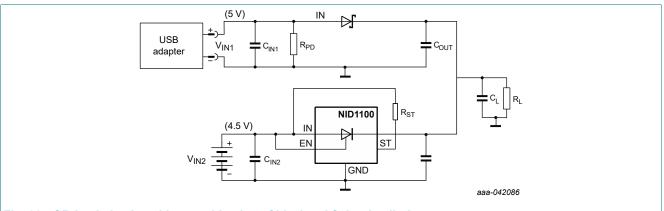

### 10.1.3. n+1 OR-ing using ideal and conventional diodes

When voltage drops and electrical losses of one of two power sources is not of concern, a combination of ideal diodes and conventional diodes can be implemented as shown in Fig. 36. In this example the AC-DC adapter is the primary power source supplying 5 V to the system with three alkaline cells providing a 4.5 V backup. As stated in Section 8.5, consideration should be given to the V<sub>F</sub> rating of the Schottky diode as well as worst case tolerances of the supply voltages to ensure seamless transitions.

A resistor,  $R_{PD}$ , connected to ground in the Schottky diode path is recommended to prevent diode reverse leakage during blocking conditions from charging  $C_{IN1}$  and raising  $V_{IN1}$ .

Fig. 37. Waveforms showing OR-ing behavior with a combination of ideal and Schottky diode (PMEG4010)

### 10.1.4. Paralleling NID1100 for thermal and sustained high current considerations

As with using any power semiconductor component, thermal ratings must be observed to maintain device reliability. Refer to the <u>Section 8.4</u> table. System thermal analysis should be performed to ensure the device junction temperature, T<sub>J</sub>, remains below 125 °C under all operating conditions. If analysis shows that using a single NID1100 would cause a thermal violation, two NID1100s can be paralleled to share the load current and lower internal power dissipation as shown in <u>Fig. 38</u>. Fig. 39 shows two NID1100's supporting a combined 2 A load current with 1 A current flowing in each NID1100.

#### Fig. 38. Paralleling two NID1100 ideal diodes for high current

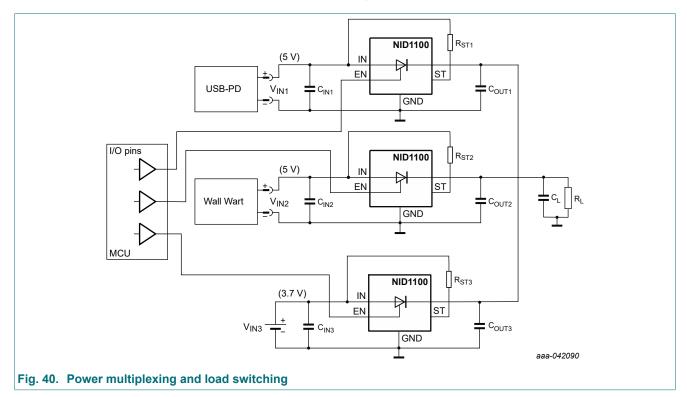

## 10.1.5. Power multiplexing and load switching

Because the NID1100 has forward voltage blocking, it is possible to use a single device as a high side load switch with short circuit protection or multiple devices for power multiplexing. Fig. 40 depicts an application example that can be used to switch between an USB-PD source, a wall wart and a Li-ion battery.

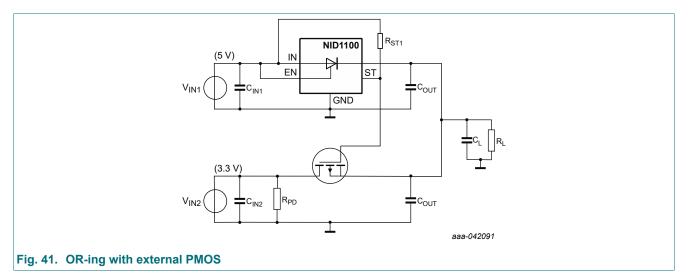

#### 10.1.6. OR-ing with discrete MOSFET

In this application, the EN pin of the NID1100 is always connected to  $V_{IN1}$  "enabling" the device. When both the 5 V and 3.3 V supplies are present, OUT is initially 5 V and the ST pin is high-Z with the  $R_{ST1}$  resistor pulled up to  $V_{IN1}$ , keeping the gate of the external PFET high.

- If V<sub>IN1</sub> is quickly removed, the ST pin output will transition low, enhancing the external PMOS. The load is then supplied from V<sub>IN2</sub>.

- If V<sub>IN1</sub> is a slowly discharging battery, OUT will transition from being supplied by the NID1100 OUT pin to being supplied by the external PMOS when V<sub>IN1</sub> decreases below V<sub>IN2</sub> by V<sub>FWD(ext\_PMOS)</sub>.

- Conversely, if V<sub>IN1</sub> is slowly recharged, OUT will be supplied from the PMOS until V<sub>IN1</sub> + V<sub>REG</sub> ≥ V<sub>IN2</sub> + V<sub>RDSON(ext PMOS)</sub>

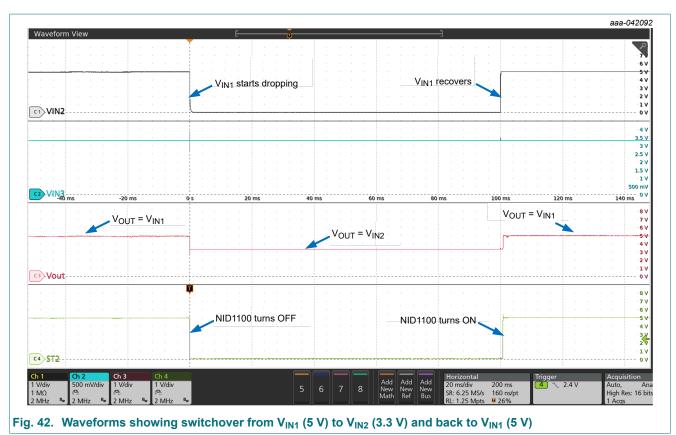

**Note:** The supply to the NID1100 ( $V_{IN1}$ ) should be the higher of the two supplies when both  $V_{IN1}$  and  $V_{IN2}$  are present. Fig. 42 shows the switchover performance between  $V_{IN1}$  and  $V_{IN2}$ . A resistor,  $R_{PD}$ , to ground is recommended to prevent any reverse leakage from charging the 3.3 V  $C_{IN2}$  capacitor and raising the  $V_{IN2}$  voltage in the event the 3.3 V supply is disconnected.

### 10.2. Thermal characteristics and power dissipation

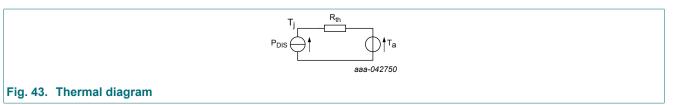

The junction temperature of a semiconductor device is determined by the internal power dissipation and its capacity to dissipate heat to the surrounding environment. The electronic equivalent is shown in Fig. 43.

From the diagram, the formula for calculating the junction temperature can be derived as follows:

$$T_j = P_{DIS} \times R_{th} + T_{amb}$$

Where  $T_j$  is the junction temperature,  $P_{DIS}$  is the power dissipation,  $R_{th}$  is the thermal resistance, and  $T_{amb}$  is the ambient temperature.

The internal power dissipation is given by:

$$P_{DIS} = I_{OUT} \times (V_{IN} - V_{OUT})$$

Where  $I_{OUT}$  is the output current,  $V_{IN}$  is the input voltage, and  $V_{OUT}$  is the output voltage.

It is a characteristic of semiconductor devices that power losses increase with rising temperatures. Operating the device above the specified maximum junction temperature of 125°C can lead to thermal runaway due to these increased losses, thereby reducing the device's lifespan or triggering thermal protection.

The aforementioned equations can be used to estimate the junction temperature for a given application. To verify the actual junction temperature, the specified  $\Psi_{JT}$  value can be used in conjunction with the measured top package temperature:

$$T_j = \Psi_{JT} \times P_{DIS} + T_{TOP}$$

where  $T_{TOP}$  is the top surface temperature of the package.

NID1100

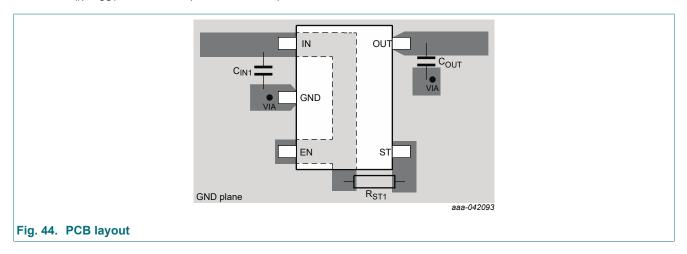

## 10.3. PCB Layout

For best performance, all traces must be as short as possible. To be most effective, the input and output capacitors must be placed close to the device to minimize the effects that parasitic trace inductances may have on normal operation. Using wide traces for  $V_{IN}$ ,  $V_{OUT}$  and GND helps minimize the parasitic electrical events.

# 11. Package outline

Fig. 45. Package outline SOT753 (SC-74A)

NID1100

## 12. Abbreviations

| Table 11. Abbreviatio | Table 11. Abbreviations                           |  |  |  |  |

|-----------------------|---------------------------------------------------|--|--|--|--|

| Acronym               | Description                                       |  |  |  |  |

| CDM                   | Charged Device Model                              |  |  |  |  |

| ESD                   | ElectroStatic Discharge                           |  |  |  |  |

| FET                   | Field-Effect Transistor                           |  |  |  |  |

| НВМ                   | Human Body Model                                  |  |  |  |  |

| IEC                   | International Electrotechnical Commission         |  |  |  |  |

| JEDEC                 | Joint Electron Device Engineering Council         |  |  |  |  |

| MOSFET                | Metal-Oxide Semiconductor Field-Effect Transistor |  |  |  |  |

| PCB                   | Printed Circuit Board                             |  |  |  |  |

| PMOS                  | P-channel Metal-Oxide Semiconductor               |  |  |  |  |

# 13. Revision history

| Document ID    | Release date                                                                                                                                                | Data sheet status  | Change notice | Supersedes  |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------|-------------|--|

| NID1100 v.2    | 20250317                                                                                                                                                    | Product data sheet | -             | NID1100 v.1 |  |

| Modifications: | <ul> <li><u>Section 9.3</u>: Typo corrected in equation.</li> <li><u>Fig. 40</u> moved to <u>Section 10.1.5</u> and <u>Section 10.2</u> updated.</li> </ul> |                    |               |             |  |

| NID1100 v.1    | 20250120                                                                                                                                                    | Product data sheet | -             | -           |  |

## 14. Legal information

#### Data sheet status

| Document status<br>[1][2]         | Product<br>status [3] | Definition                                                                                  |

|-----------------------------------|-----------------------|---------------------------------------------------------------------------------------------|

| Objective [short]<br>data sheet   | Development           | This document contains data from<br>the objective specification for<br>product development. |

| Preliminary [short]<br>data sheet | Qualification         | This document contains data from the preliminary specification.                             |

| Product [short]<br>data sheet     | Production            | This document contains the product specification.                                           |

Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions".

- [3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the internet at <u>https://www.nexperia.com</u>.

#### **Definitions**

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. Nexperia does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local Nexperia sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

**Product specification** — The information and data provided in a Product data sheet shall define the specification of the product as agreed between Nexperia and its customer, unless Nexperia and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the Nexperia product is deemed to offer functions and qualities beyond those described in the Product data sheet.

#### **Disclaimers**

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, Nexperia does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. Nexperia takes no responsibility for the content in this document if provided by an information source outside of Nexperia.

In no event shall Nexperia be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, Nexperia's aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of Nexperia.

**Right to make changes** — Nexperia reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — Nexperia products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an Nexperia product can reasonably be expected to result in personal

injury, death or severe property or environmental damage. Nexperia and its suppliers accept no liability for inclusion and/or use of Nexperia products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Quick reference data** — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. Nexperia makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using Nexperia products, and Nexperia accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the Nexperia product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

Nexperia does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using Nexperia products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). Nexperia does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — Nexperia products are sold subject to the general terms and conditions of commercial sale, as published at <u>http://www.nexperia.com/profile/terms</u>, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. Nexperia hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of Nexperia products by customer.

No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Non-automotive qualified products — Unless this data sheet expressly states that this specific Nexperia product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. Nexperia accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without Nexperia's warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond Nexperia's specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies Nexperia for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond Nexperia's standard warranty and Nexperia's product specifications.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

#### Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

All information provided in this document is subject to legal disclaimers.

© Nexperia B.V. 2025. All rights reserved

## Contents

| 1. General description                                 | 1    |

|--------------------------------------------------------|------|

| 2. Features and benefits                               | 1    |

| 3. Applications                                        | 1    |

| 4. Ordering information                                | 2    |

| 5. Marking                                             | 2    |

| 6. Functional diagram                                  | 2    |

| 7. Pin configuration and description                   | 2    |

| 7.1. Pin configuration                                 | 2    |

| 7.2. Pin description                                   | 3    |

| 8. Specifications                                      | 3    |

| 8.1. Limiting values                                   | 3    |

| 8.2. ESD ratings                                       | 3    |

| 8.3. Recommended operating conditions                  | 4    |

| 8.4. Thermal information                               | 4    |

| 8.5. Electrical characteristics                        | 5    |

| 8.6. Dynamic characteristics                           | 6    |

| 8.7. Typical characteristics graphs                    | 7    |

| 8.8. Typical characteristics graphs                    | 10   |

| 9. Functional Description                              | . 13 |

| 9.1. Overview                                          | . 13 |

| 9.2. Startup                                           | . 13 |

| 9.3. Functional modes                                  | . 13 |

| 9.4. Reverse current blocking                          | . 14 |

| 9.5. Output overload and temperature protection        | . 14 |

| 10. Application information                            | . 15 |

| 10.1. Startup                                          | . 15 |

| 10.1.1. n+1 OR-ing using ideal diodes                  | . 15 |

| 10.1.2. OR-ing similar supply voltages                 | . 16 |

| 10.1.3. n+1 OR-ing using ideal and conventional diodes | 17   |

| 10.1.4. Paralleling NID1100 for thermal and sustained  |      |

| high current considerations                            |      |

| 10.1.5. Power multiplexing and load switching          |      |

| 10.1.6. OR-ing with discrete MOSFET                    |      |

| 10.2. Thermal characteristics and power dissipation    | . 21 |

| 10.3. PCB Layout                                       |      |

| 11. Package outline                                    |      |

| 12. Abbreviations                                      |      |

| 13. Revision history                                   |      |

| 14. Legal information                                  | 25   |

|                                                        |      |

#### © Nexperia B.V. 2025. All rights reserved

For more information, please visit: http://www.nexperia.com For sales office addresses, please send an email to: salesaddresses@nexperia.com Date of release: 17 March 2025

ent feedback