# onsemi

# NCV84160

The NCV84160 is a fully protected single channel high side driver that can be used to switch a wide variety of loads, such as bulbs, solenoids, and other actuators. The device incorporates advanced protection features such as active inrush current management, over-temperature shutdown with automatic restart and an overvoltage active clamp. A dedicated Current Sense pin provides precision analog current monitoring of the output as well as fault indication of short to  $V_D$ , short circuit to ground and ON and OFF state open load detection. An active high Current Sense Disable pin allows all diagnostic and current sense features to be disabled.

#### Features

- Short Circuit Protection with Inrush Current Management

- CMOS (3 V / 5 V) Compatible Control Input

- Very Low Standby Current

- Very Low Current Sense Leakage

- Proportional Load Current Sense

- Current Sense Disable

- Off State Open Load Detection

- Output Short to V<sub>D</sub> Detection

- Overload and Short to Ground Indication

- Thermal Shutdown with Automatic Restart

- Undervoltage Shutdown

- Integrated Clamp for Inductive Switching

- Loss of Ground and Loss of V<sub>D</sub> Protection

- ESD Protection

- Reverse Battery Protection

- AEC-Q100 Qualified

- This is a Pb–Free Device

#### **Typical Applications**

- Switch a Variety of Resistive, Inductive and Capacitive Loads

- Can Replace Electromechanical Relays and Discrete Circuits

- Automotive / Industrial

#### FEATURE SUMMARY

| Max Supply Voltage                            | VD                  | 41        | V  |

|-----------------------------------------------|---------------------|-----------|----|

| Operating Voltage Range                       | VD                  | 4.5 to 28 | V  |

| R <sub>DSon</sub> (max) T <sub>J</sub> = 25°C | R <sub>ON</sub>     | 160       | mΩ |

| Output Current Limit (typical)                | I <sub>LIM</sub>    | 12        | А  |

| OFF-state Supply Current (typical)            | I <sub>D(off)</sub> | 0.01      | μΑ |

8 1 50IC-8

CASE 751 STYLE 11

(Note: Microdot may be in either location)

#### **ORDERING INFORMATION**

| Device       | Package             | Shipping <sup>†</sup> |

|--------------|---------------------|-----------------------|

| NCV84160DR2G | SOIC-8<br>(Pb-Free) | 2500 / Tape &<br>Reel |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

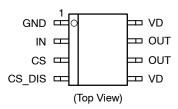

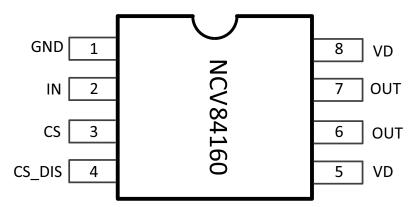

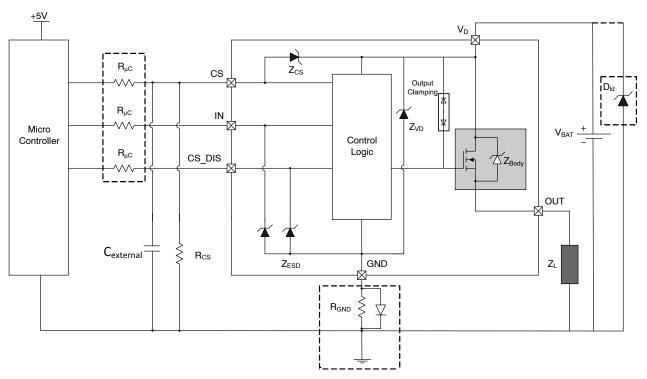

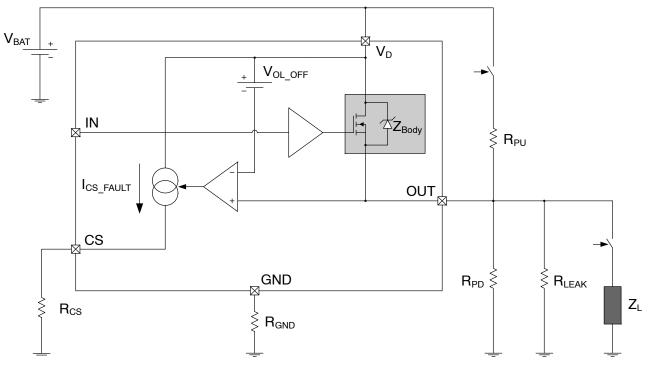

## **Block Diagram & Pin Configuration**

GND

Figure 1. Block Diagram

#### Table 1. SO8 PACKAGE PIN DESCRIPTION

| Pin # | Symbol | Description                       |

|-------|--------|-----------------------------------|

| 1     | GND    | Ground                            |

| 2     | IN     | Logic Level Input                 |

| 3     | CS     | Analog Current Sense Output       |

| 4     | CS_DIS | Active High Current Sense Disable |

| 5     | VD     | Supply Voltage                    |

| 6     | OUT    | Output                            |

| 7     | OUT    | Output                            |

| 8     | VD     | Supply Voltage                    |

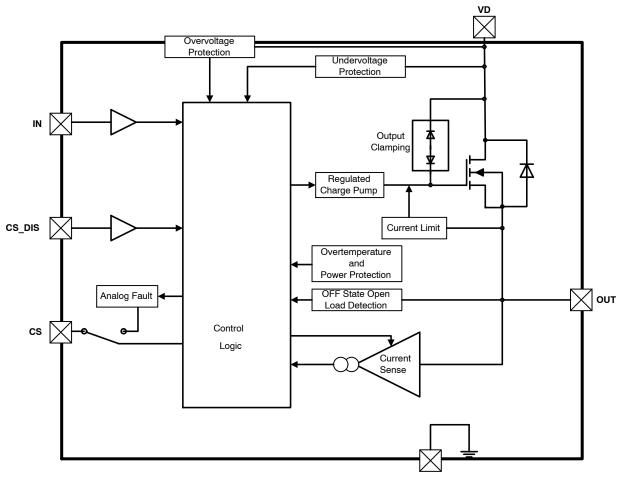

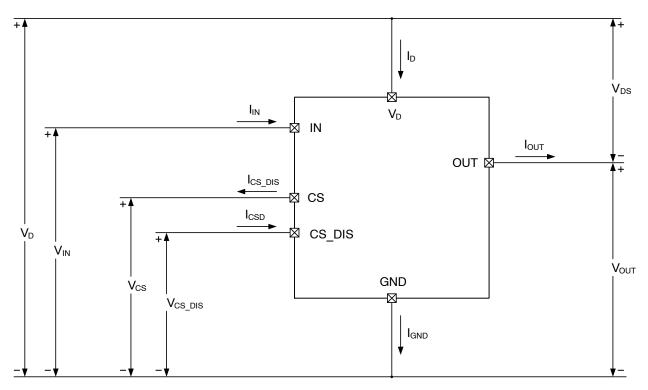

Figure 2. Voltage and Current Conventions

| Table 2. Connection suggestions for unused and or unconnected pins |

|--------------------------------------------------------------------|

|--------------------------------------------------------------------|

| Connection | Input                          | Output      | Current Sense                 | Current Sense Enable           |

|------------|--------------------------------|-------------|-------------------------------|--------------------------------|

| Floating   | Х                              | Х           | Not Allowed                   | Х                              |

| To Ground  | Through 10 k $\Omega$ resistor | Not Allowed | Through 1 k $\Omega$ Resistor | Through 10 k $\Omega$ resistor |

Figure 3. Pin Configuration (top view)

#### **ELECTRICAL SPECIFICATIONS**

#### **Table 3. MAXIMUM RATINGS**

|                                                                                                                                                                                 |                      |                              | Value              |                                  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------------------|--------------------|----------------------------------|--|

| Rating                                                                                                                                                                          | Symbol               | Min                          | Max                | Unit                             |  |

| DC Supply Voltage                                                                                                                                                               | V <sub>D</sub>       | -0.3                         | 41                 | V                                |  |

| Peak Transient Input Voltage<br>(Load Dump 46 V, V <sub>D</sub> = 14 V, ISO16750-2: 2012 Test B)                                                                                | V <sub>peak</sub>    |                              | 48                 | V                                |  |

| Input Voltage                                                                                                                                                                   | V <sub>IN</sub>      | -10                          | 10                 | V                                |  |

| Input Current                                                                                                                                                                   | I <sub>IN</sub>      | -5                           | 5                  | mA                               |  |

| Reverse Ground Pin Current                                                                                                                                                      | I <sub>GND</sub>     |                              | -200               | mA                               |  |

| Output Current (Note 2)                                                                                                                                                         | I <sub>OUT</sub>     | -6                           | Internally Limited | А                                |  |

| CS Current                                                                                                                                                                      | I <sub>CS</sub>      |                              | 200                | mA                               |  |

| CS Voltage                                                                                                                                                                      | V <sub>CS</sub>      | V <sub>D</sub> -41           | V <sub>D</sub>     | V                                |  |

| CS_DIS Voltage                                                                                                                                                                  | V <sub>CS_DIS</sub>  | -10                          | 10                 | V                                |  |

| CS_DIS Current                                                                                                                                                                  | I <sub>CS_DIS</sub>  | -5                           | 5                  | mA                               |  |

| Power Dissipation $T_c = 25^{\circ}C$ (Note 4)                                                                                                                                  | P <sub>tot</sub>     |                              | 1.49               | W                                |  |

| Electrostatic Discharge<br>(HBM Model 100 pF / 1500 Ω)<br>Input<br>Current Sense<br>Current Sense Enable<br>Output<br>V <sub>D</sub><br>Charge Device Model<br>CDM-AEC-Q100-011 | V <sub>ESD</sub>     | 4<br>3<br>4<br>3<br>3<br>750 |                    | DC<br>kV<br>kV<br>kV<br>kV<br>kV |  |

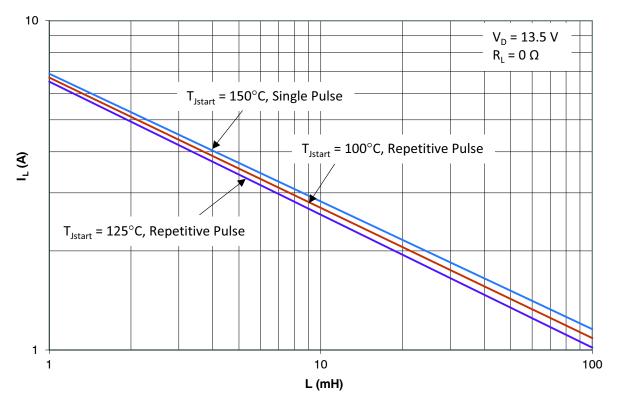

| Single Pulse Inductive Load Switching Energy (Note 1) (L = 8 mH, $V_{bat}$ = 13.5 V; I <sub>L</sub> = 3.08 A, T <sub>J_Start</sub> = 150°C)                                     | E <sub>AS</sub>      |                              | 53.71              | mJ                               |  |

| Operating Junction Temperature                                                                                                                                                  | TJ                   | -40                          | +150               | °C                               |  |

| Storage Temperature                                                                                                                                                             | T <sub>storage</sub> | -55                          | +150               | °C                               |  |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected. 1. Not subjected to production testing

2. Reverse Output current has to be limited by the load to stay within absolute maximum ratings and thermal performance.

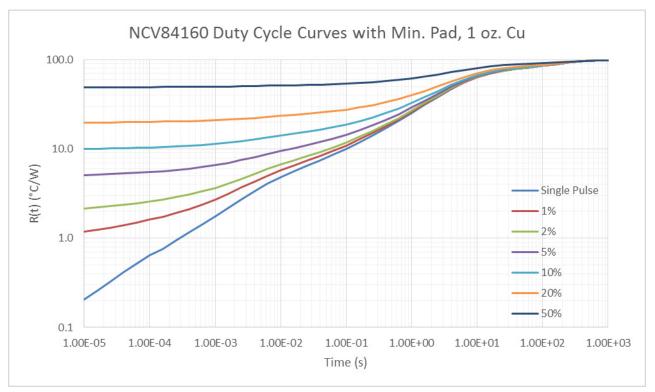

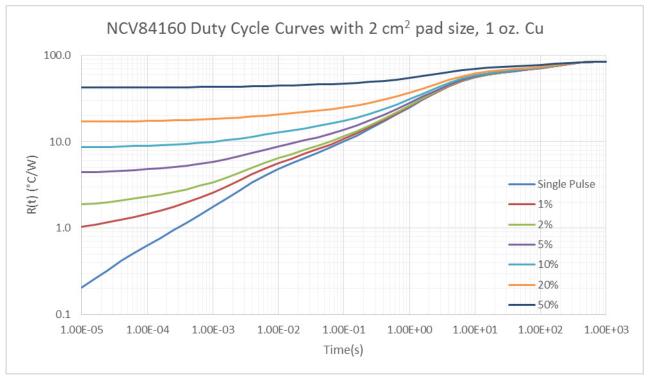

#### **Table 4. THERMAL RESISTANCE RATINGS**

| Parameter                                        | Symbol                               | Max. Value | Units |

|--------------------------------------------------|--------------------------------------|------------|-------|

| Thermal Resistance                               | 6                                    | 20         | °C/W  |

| Junction-to-Lead<br>Junction-to-Ambient (Note 3) | R <sub>θJL</sub><br>R <sub>θJA</sub> | 32<br>98   |       |

| Junction-to-Ambient (Note 4)                     | $R_{\theta JA}$                      | 84         |       |

Min. pad size, 1 oz. Cu with backside plane covered with 1 oz. Cu (backside plane not electrically connected).

2 cm<sup>2</sup> pad size, 1 oz. Cu with backside plane covered with 1 oz. Cu (backside plane not electrically connected).

#### **ELECTRICAL CHARACTERISTICS** (8 $\leq$ V<sub>D</sub> $\leq$ 28 V; -40°C < T<sub>J</sub> < 150°C unless otherwise specified)

### Table 5. POWER

|                                     |                      |                                                                                 | Value |      |     |      |

|-------------------------------------|----------------------|---------------------------------------------------------------------------------|-------|------|-----|------|

| Rating                              | Symbol               | Conditions                                                                      | Min   | Тур  | Max | Unit |

| Operating Supply Voltage            | V <sub>D</sub>       |                                                                                 | 4.5   | -    | 28  | V    |

| Undervoltage Shutdown               | V <sub>UV</sub>      |                                                                                 |       | 3.5  | 4.5 | V    |

| Undervoltage Shutdown<br>Hysteresis | V <sub>UV_HYST</sub> |                                                                                 |       | 0.5  |     | V    |

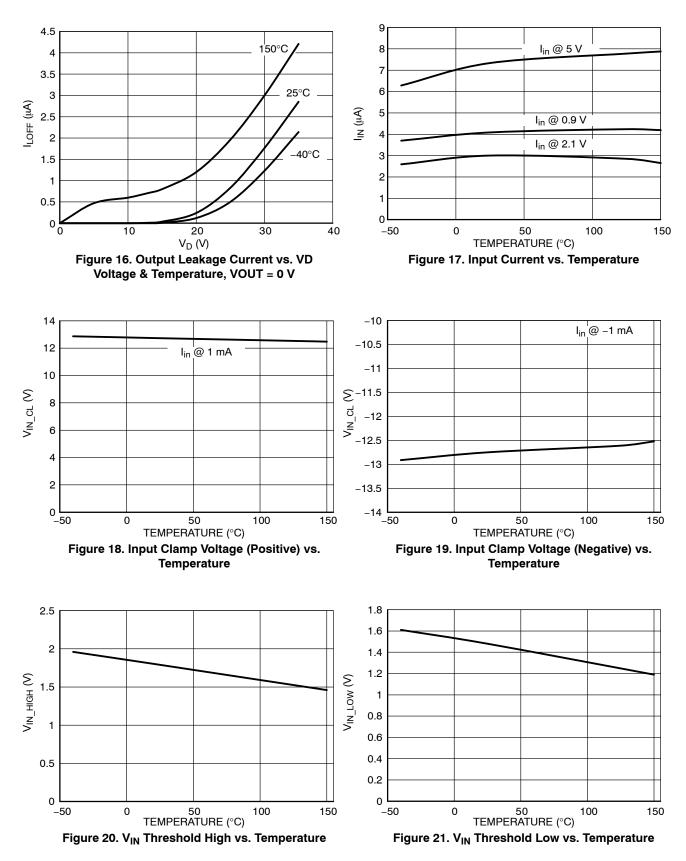

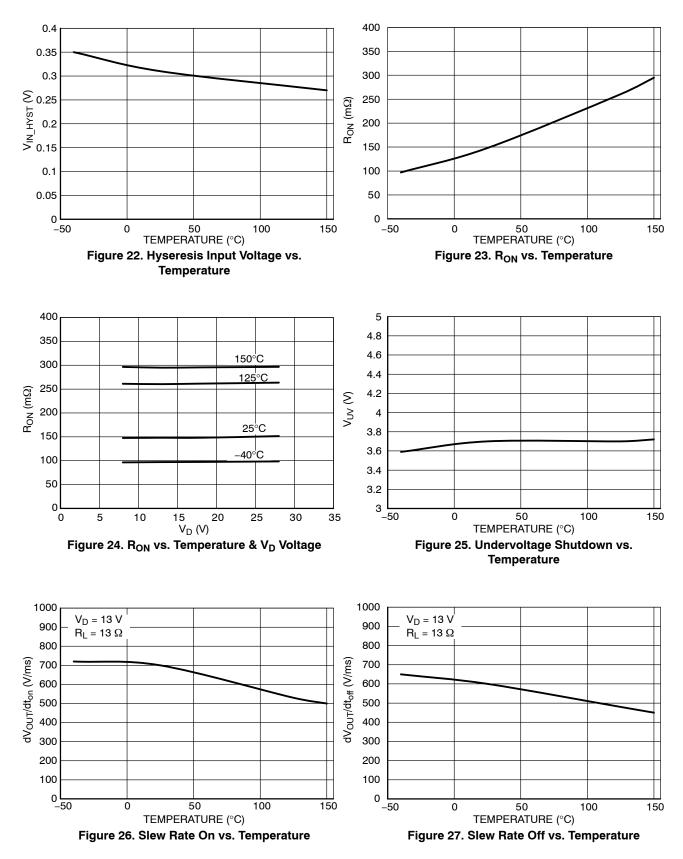

| On Resistance                       | R <sub>ON</sub>      | I <sub>OUT</sub> = 1 A, T <sub>J</sub> = 25°C                                   |       |      | 160 | mΩ   |

|                                     |                      | I <sub>OUT</sub> = 1 A, T <sub>J</sub> = 150°C                                  |       |      | 320 |      |

|                                     |                      | $I_{OUT} = 1 \text{ A}, V_D = 5 \text{ V}, T_J = 25^{\circ}\text{C}$            |       |      | 210 |      |

| Supply Current (Note 5)             | ۱ <sub>D</sub>       | OFF-state: $V_D$ = 13 V,<br>$V_{IN}$ = $V_{OUT}$ = 0 V, $T_J$ = 25°C            |       | 0.01 | 0.5 | μΑ   |

|                                     |                      | ON-state: $V_D = 13 V$ ,<br>$V_{IN} = 5 V$ , $I_{OUT} = 0 A$                    |       | 1.9  | 3.5 | mA   |

| Output Leakage Current              | I <sub>L(OFF)</sub>  | $V_{IN} = V_{OUT} = 0$ V, $V_D = 13$ V, $T_J = 25^{\circ}C$                     |       |      | 0.5 | μΑ   |

|                                     |                      | $V_{IN} = V_{OUT} = 0 \text{ V}, V_D = 13 \text{ V}, T_J = 125^{\circ}\text{C}$ |       |      | 0.5 |      |

5. Includes PowerMOS leakage current.

# Table 6. LOGIC INPUTS (V\_D = 13.5 V; -40°C < T\_J < 150°C)

|                           |                          |                             |     | Value |     |      |

|---------------------------|--------------------------|-----------------------------|-----|-------|-----|------|

| Rating                    | Symbol                   | Conditions                  | Min | Тур   | Max | Unit |

| Input Voltage – Low       | V <sub>IN_LOW</sub>      |                             |     |       | 0.9 | V    |

| Input Current – Low       | I <sub>IN_LOW</sub>      | V <sub>IN</sub> = 0.9 V     | 1   |       |     | μA   |

| Input Voltage – High      | V <sub>IN_HIGH</sub>     |                             | 2.1 |       |     | V    |

| Input Current – High      | I <sub>IN_HIGH</sub>     | V <sub>IN</sub> = 2.2 V     |     |       | 10  | μΑ   |

| Input Hysteresis Voltage  | V <sub>IN_HYST</sub>     |                             | 0.2 |       |     | V    |

| Input Clamp Voltage       | V <sub>IN_CL</sub>       | I <sub>IN</sub> = 1 mA      | 12  | 13    | 14  | V    |

|                           |                          | I <sub>IN</sub> = -1 mA     | -14 | -13   | -12 |      |

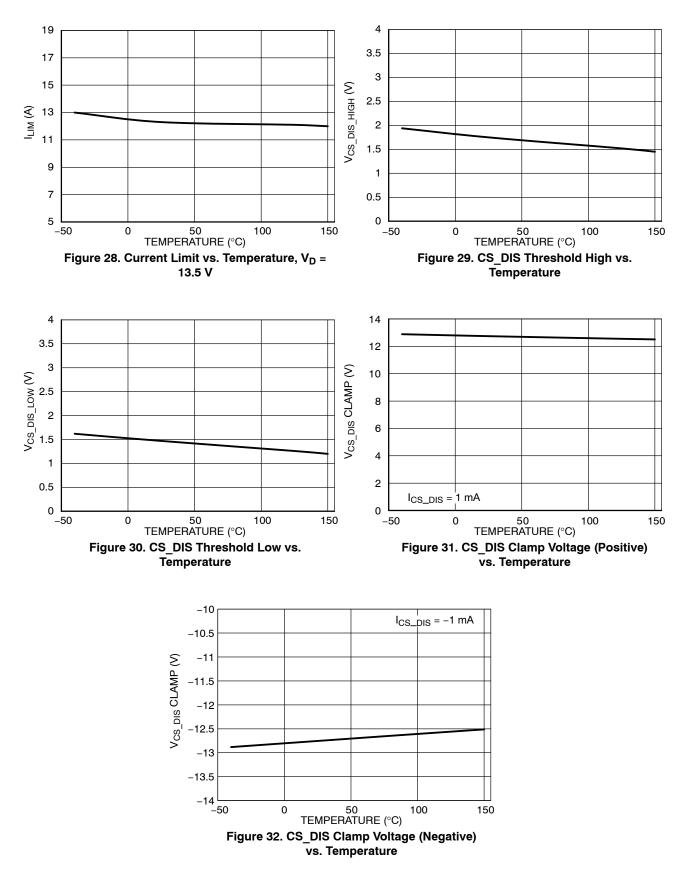

| CS_DIS Voltage - Low      | V <sub>CS_DIS_LOW</sub>  |                             |     |       | 0.9 | V    |

| CS_DIS Current – Low      | ICS_DIS_LOW              | $V_{CS_{DIS}} = 0.9 V$      | 1   |       |     | μΑ   |

| CS_DIS Voltage - High     | V <sub>CS_DIS_HIGH</sub> |                             | 2.1 |       |     | V    |

| CS_DIS Current – High     | I <sub>CS_DIS_HIGH</sub> | $V_{CS_{DIS}} = 2.2 V$      |     |       | 10  | μA   |

| CS_DIS Hysteresis Voltage | V <sub>CS_DIS_HYST</sub> |                             | 0.2 |       |     | V    |

| CS_DIS Clamp Voltage      | V <sub>CS_DIS_CL</sub>   | I <sub>CS_DIS</sub> = 1 mA  | 12  | 13    | 14  | V    |

|                           |                          | I <sub>CS_DIS</sub> = -1 mA | -14 | -13   | -12 |      |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

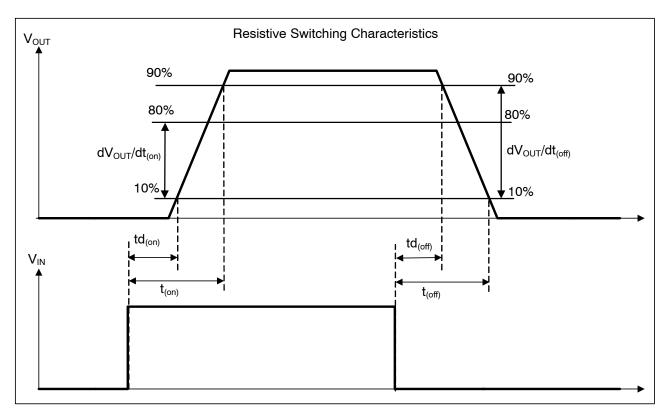

## Table 7. SWITCHING CHARACTERISTICS (T\_J = 25°C)

|                                  |                                      |                                                                                   | Value |      |     |      |

|----------------------------------|--------------------------------------|-----------------------------------------------------------------------------------|-------|------|-----|------|

| Rating                           | Symbol                               | Conditions                                                                        | Min   | Тур  | Max | Unit |

| Turn-On Delay Time               | t <sub>d_on</sub>                    | to 10% V_OUT, V_D = 13 V, R_L = 13 $\Omega$                                       |       | 10   |     | μs   |

| Turn-Off Delay Time              | t <sub>d_off</sub>                   | to 90% V_OUT, V_D = 13 V, R_L = 13 $\Omega$                                       |       | 10   |     | μs   |

| Slew Rate On                     | dV <sub>OUT</sub> /dt <sub>on</sub>  | 10% to 80% V <sub>OUT</sub> , V <sub>D</sub> = 13 V, R <sub>L</sub> = 13 $\Omega$ |       | 0.7  |     | V/μs |

| Slew Rate Off                    | dV <sub>OUT</sub> /dt <sub>off</sub> | 90% to 10% V <sub>OUT</sub> , V <sub>D</sub> = 13 V, R <sub>L</sub> = 13 $\Omega$ |       | 0.7  |     | V/μs |

| Turn-On Switching Loss (Note 6)  | Eon                                  | $V_{D}$ = 13 V, $R_{L}$ = 13 $\Omega$                                             |       | 0.04 |     | mJ   |

| Turn–Off Switching Loss (Note 6) | E <sub>off</sub>                     | $V_{D}$ = 13 V, $R_{L}$ = 13 $\Omega$                                             |       | 0.04 |     | mJ   |

6. Not subjected to production testing

#### **Table 8. OUTPUT DIODE CHARACTERISTICS**

|                 |                |                                                                                                                                   | Value |     |     |      |

|-----------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------|-------|-----|-----|------|

| Rating          | Symbol         | Conditions                                                                                                                        | Min   | Тур | Max | Unit |

| Forward Voltage | V <sub>F</sub> | $I_{OUT} = -1 \text{ A},  \text{T}_{\text{J}} = 150^{\circ}\text{C},  \text{V}_{\text{F}} = \text{V}_{OUT} - \text{V}_{\text{D}}$ |       |     | 0.7 | V    |

#### Table 9. PROTECTION FUNCTIONS (Note 8)

|                                                                |                        |                                                                            | Value                |                      |                     |      |

|----------------------------------------------------------------|------------------------|----------------------------------------------------------------------------|----------------------|----------------------|---------------------|------|

| Rating                                                         | Symbol                 | Conditions                                                                 | Min                  | Тур                  | Max                 | Unit |

| Temperature Shutdown (Note 7)                                  | T <sub>SD</sub>        |                                                                            | 150                  | 175                  | 200                 | °C   |

| Temperature Shutdown Hysteresis $(T_{SD} - T_R)$ (Note 7)      | T <sub>SD_HYST</sub>   |                                                                            |                      | 7                    |                     | °C   |

| Reset Temperature (Note 7)                                     | Τ <sub>R</sub>         |                                                                            | T <sub>R_CS</sub> +1 | T <sub>R_CS</sub> +5 |                     | °C   |

| Thermal Reset of CS_FAULT<br>(Note 7)                          | T <sub>R_CS</sub>      |                                                                            | 135                  |                      |                     | °C   |

| DC Output Current Limit                                        | I <sub>LIM_H</sub>     | V <sub>D</sub> = 13 V                                                      | 6                    | 12                   | 18                  | А    |

|                                                                |                        | 5 V < V <sub>D</sub> < 28 V                                                |                      |                      | 18                  | А    |

| Short Circuit Current Limit during<br>Thermal Cycling (Note 7) | ILIM_L                 | V <sub>D</sub> = 13 V<br>T <sub>R</sub> < T <sub>J</sub> < T <sub>SD</sub> |                      | 6.5                  |                     | A    |

| Switch Off Output Clamp Voltage                                | V <sub>OUT_CLAMP</sub> | I <sub>OUT</sub> = 1 A, V <sub>IN</sub> = 0 V, L = 20 mH                   | V <sub>D</sub> – 41  | V <sub>D</sub> – 45  | V <sub>D</sub> – 52 | V    |

| Overvoltage Protection                                         | V <sub>OV</sub>        | V <sub>IN</sub> = 0 V, I <sub>D</sub> = 20 mA                              | 41                   | 45                   | 52                  | V    |

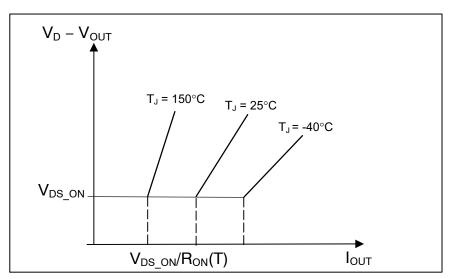

| Output Voltage Drop Limitation                                 | V <sub>DS_ON</sub>     | $I_{OUT}=0.025~A,~-40^\circ C \leq T_J \leq 150^\circ C$                   |                      | 25                   |                     | mV   |

Not subjected to production testing.

To ensure long term reliability during overload or short circuit conditions, protection and related diagnostic signals must be used together with a fitting hardware & software strategy. If the device operates under abnormal conditions, this hardware & software solution must limit the duration and number of activation cycles.

|                                                          |                       |                                                                      | Value |     |     |      |

|----------------------------------------------------------|-----------------------|----------------------------------------------------------------------|-------|-----|-----|------|

| Rating                                                   | Symbol                | Conditions                                                           | Min   | Тур | Max | Unit |

| Open-load Off-State Detection<br>Threshold               | V <sub>OL</sub>       | V <sub>IN</sub> = 0 V                                                | 2     | -   | 4   | V    |

| Open-load On-State Detection<br>Threshold                | I <sub>OL</sub>       | $V_{IN}$ = 5 V, $I_{CS}$ = 5 $\mu$ A                                 | 0.5   |     | 5   | mA   |

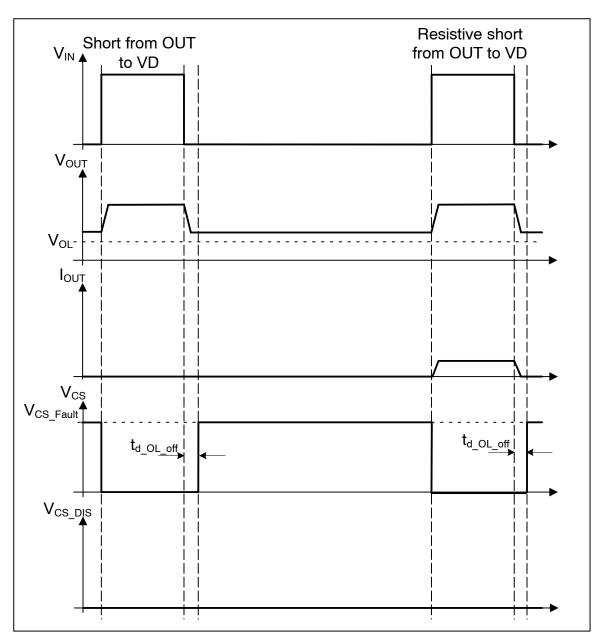

| Open-load Detection Delay at<br>Turn-Off                 | <sup>t</sup> d_OL_off |                                                                      | 100   |     | 800 | μs   |

| Off-State Output Current                                 | I <sub>OLOFF1</sub>   | V <sub>IN</sub> = 0 V, V <sub>OUT</sub> = V <sub>OL</sub>            | -3    |     | 3   | μΑ   |

| Output rising edge to CS rising<br>edge during open-load | t <sub>D_OL</sub>     | $V_{OUT}$ = 4 V, $V_{IN}$ = 0 V,<br>$V_{CS}$ = 90% of $V_{CS}$ _HIGH |       |     | 20  | μs   |

# Table 10. OPEN–LOAD DETECTION (8 $\leq$ V\_D $\leq$ 18 V)

# Table 11. CURRENT SENSE CHARACTERISTICS (8 $\leq$ V\_D $\leq$ 18 V)

|                                                               |                         |                                                                                                                                                                                            | Value |     |     |                                       |

|---------------------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-----|---------------------------------------|

| Rating                                                        | Symbol                  | Conditions                                                                                                                                                                                 | min   | typ | max | Unit                                  |

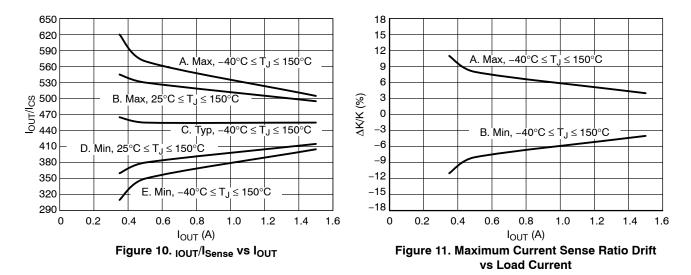

| Current Sense Ratio                                           | K <sub>0</sub>          | K <sub>0</sub> $I_{OUT} = 0.025 \text{ A}, V_{CS} = 0.5 \text{ V}, T_{J} = -40^{\circ}\text{C} \text{ to } 150^{\circ}\text{C}$                                                            |       | 490 | 760 | I <sub>OUT</sub><br>/ I <sub>CS</sub> |

| Current Sense Ratio                                           | K <sub>1</sub>          | $I_{OUT} = 0.35 \text{ A}, V_{CS} = 0.5 \text{ V}, T_{J} = -40^{\circ}\text{C} \text{ to } 150^{\circ}\text{C}$                                                                            | 310   | 465 | 620 |                                       |

|                                                               |                         | I <sub>OUT</sub> = 0.35 A, V <sub>CS</sub> = 0.5 V,<br>T <sub>J</sub> = 25°C to 150°C                                                                                                      | 360   | 465 | 545 |                                       |

| Current Sense Ratio Drift (Note 9)                            | $\Delta K_1 / K_1$      | I <sub>OUT</sub> = 0.35 A, V <sub>CS</sub> = 0.5 V,<br>T <sub>J</sub> = −40°C to 150°C                                                                                                     | -11   |     | 11  | %                                     |

| Current Sense Ratio                                           | K <sub>2</sub>          | I <sub>OUT</sub> = 0.5 A, V <sub>CS</sub> = 4 V,<br>T <sub>J</sub> = −40°C to 150°C                                                                                                        | 350   | 455 | 570 |                                       |

|                                                               |                         | I <sub>OUT</sub> = 0.5 A, V <sub>CS</sub> = 4 V,<br>T <sub>J</sub> = 25°C to 150°C                                                                                                         | 380   | 455 | 530 |                                       |

| Current Sense Ratio Drift (Note 9)                            | $\Delta K_2 / K_2$      | $I_{OUT} = 0.5 \text{ A}, \text{ T}_{\text{J}} = -40^{\circ}\text{C} \text{ to } 150^{\circ}\text{C}$                                                                                      | -8    |     | 8   | %                                     |

| Current Sense Ratio                                           | K <sub>3</sub>          | l <sub>OUT</sub> = 1.5 A, V <sub>CS</sub> = 4 V,<br>T <sub>J</sub> = −40°C to 150°C                                                                                                        | 405   | 455 | 505 |                                       |

|                                                               |                         | I <sub>OUT</sub> = 1.5 A, V <sub>CS</sub> = 4 V,<br>T <sub>J</sub> = 25°C to 150°C                                                                                                         | 415   | 455 | 495 |                                       |

| Current Sense Ratio Drift (Note 9)                            | $\Delta K_3 / K_3$      | $I_{OUT}$ = 1.5 A, $T_{J}$ = -40°C to 150°C                                                                                                                                                | -4    |     | 4   | %                                     |

| Current Sense Leakage Current                                 | CS <sub>Ilkg</sub>      | $I_{OUT} = 0 \text{ A}, \text{ V}_{CS} = 0 \text{ V}$<br>$V_{CS}_{DIS} = 5 \text{ V}, \text{ V}_{IN} = 0 \text{ V}$<br>$T_{J} = -40^{\circ}\text{C} \text{ to } 150^{\circ}\text{C}$       |       |     | 1   | μΑ                                    |

|                                                               |                         | $I_{OUT} = 0 \text{ A}, \text{ V}_{CS} = 0 \text{ V}$<br>$V_{CS} \text{ DIS} = 0 \text{ V}, \text{ V}_{IN} = 5 \text{ V}$<br>$T_{J} = -40^{\circ}\text{C} \text{ to } 150^{\circ}\text{C}$ |       |     | 2   |                                       |

|                                                               |                         | $I_{OUT} = 1 \text{ A}, V_{CS} = 0 \text{ V}$<br>$V_{CS} \text{ DIS} = 5 \text{ V}, V_{IN} = 5 \text{ V}$<br>$T_J = -40^{\circ}\text{C}$ to $150^{\circ}\text{C}$                          |       |     | 1   |                                       |

| CS Max Voltage                                                | CS <sub>Max</sub>       | R <sub>CS</sub> = 10 KΩ, I <sub>OUT</sub> = 1 A                                                                                                                                            | 5     |     |     | V                                     |

| Current Sense Voltage in Fault Con-<br>dition (Note 10)       | V <sub>CS_FAULT</sub>   | $V_D$ = 13 V, $R_{CS}$ = 3.9 k $\Omega$                                                                                                                                                    |       | 8   |     | V                                     |

| Current Sense Current in Fault Con-<br>dition (Note 10)       | ICS_FAULT               | V <sub>D</sub> = 13 V, V <sub>CS</sub> = 5 V                                                                                                                                               |       | 10  |     | mA                                    |

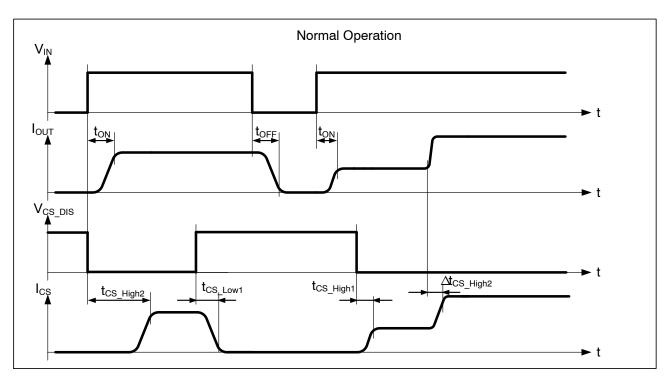

| CS_DIS Low to CS High Delay Time                              | <sup>t</sup> CS_HIGH1   | V <sub>CS</sub> < 4 V, 0.025 A < I <sub>OUT</sub> < 1.5 A<br>I <sub>CS</sub> = 90% of I <sub>CS</sub> Max                                                                                  |       | 40  | 100 | μs                                    |

| CS_DIS High to CS Low Delay Time                              | <sup>t</sup> CS_LOW1    | V <sub>CS</sub> < 4 V, 0.025 A < I <sub>OUT</sub> < 1.5 A<br>I <sub>CS</sub> = 10% of I <sub>CS</sub> Max                                                                                  |       | 5   | 20  | μs                                    |

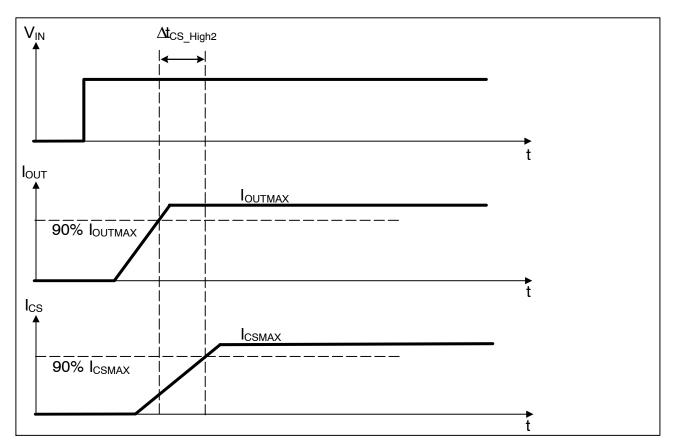

| $V_{IN}$ High to CS High Delay Time                           | t <sub>CS_HIGH2</sub>   | V <sub>CS</sub> < 4 V, 0.025 A < I <sub>OUT</sub> < 1.5 A<br>I <sub>CS</sub> = 90% of I <sub>CS</sub> Max                                                                                  |       | 30  | 160 | μs                                    |

| $V_{IN}$ Low to CS Low Delay Time                             | t <sub>CS_LOW2</sub>    | V <sub>CS</sub> < 4 V, 0.025 A < I <sub>OUT</sub> < 1.5 A<br>I <sub>CS</sub> = 10% of I <sub>CS</sub> Max                                                                                  |       | 80  | 250 | μs                                    |

| Delay Time I <sub>D</sub> Rising Edge to Rising<br>Edge of CS | $\Delta t_{CS}_{HIGH2}$ | $V_{CS}$ < 4 V, $I_{CS}$ = 90% of $I_{CS}$ Max,<br>$I_{OUT}$ = 90% of $I_{OUTmax}$ , $I_{OUTmax}$ = 1.5 A                                                                                  |       |     | 110 | μS                                    |

9. Not subjected to production testing.

10. The following fault conditions are: Overtemperature, Power Limitation, and OFF State Open–Load Detection.

### Table 12. TRUTH TABLE

| Conditions              | Input  | Output                                                      | CS (V <sub>CS_DIS</sub> = 0 V) (Note 11)                      |

|-------------------------|--------|-------------------------------------------------------------|---------------------------------------------------------------|

| Normal Operation        | L<br>H | L<br>H                                                      | 0<br>I <sub>CS</sub> = I <sub>OUT</sub> /K <sub>NOMINAL</sub> |

| Over-temperature        | L<br>H | L                                                           | 0<br>V <sub>CS_FAULT</sub>                                    |

| Under-voltage           | L<br>H | L                                                           | 0<br>0                                                        |

| Overload                | H<br>H | H (no active current mgmt)<br>Cycling (active current mgmt) | $I_{CS} = I_{OUT}/K_{NOMINAL}$<br>$V_{CS}FAULT$               |

| Short circuit to Ground | L<br>H | L                                                           | 0<br>Vcs_fault                                                |

| OFF State Open-Load     | L      | н                                                           | V <sub>CS_FAULT</sub>                                         |

11. If the V<sub>CS\_DIS</sub> is high, the Current Sense output is at a high impedance, its potential depends on leakage currents and external circuitry.

### ELECTRICAL CHARACTERISTICS WAVEFORMS AND GRAPHS

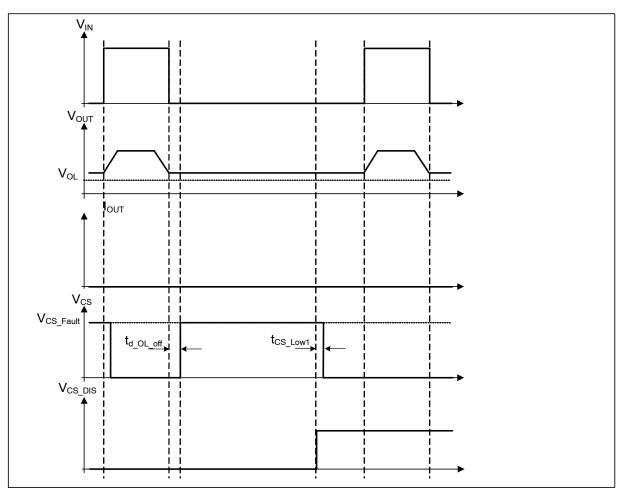

# Figure 4. Switching Characteristics

Figure 5. Normal Operation with Current Sense Timing Characteristics

Figure 6. Delay Response from Rising Edge of  $I_{OUT}$  and Rising Edge of CS (for CS\_EN = 5V)

Figure 7. OFF-State Open-Load Flag Delay Timing

Figure 8. Off-State Open-Load with added external components

Figure 9. Voltage Drop Limitation for VDS\_ON

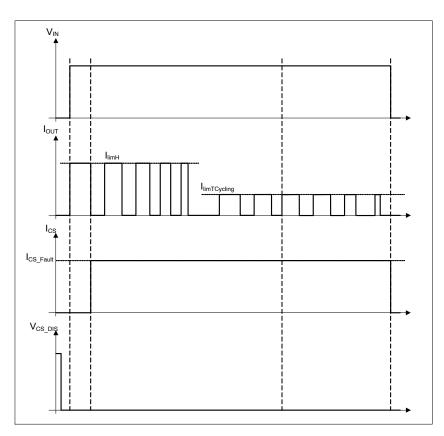

Figure 14. Discontinuous Overload or Short to GND

Figure 15. Short Circuit from OUT to VD

# ISO 7637-2: 2011(E) PULSE TEST RESULTS

| ISO<br>7637-2:2011 | Test Seve                                                                                                                                                                                                                                                           | rity Levels                           |                                                 |                               |                          |  |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------------------------|-------------------------------|--------------------------|--|

| Test Pulse         | Ш                                                                                                                                                                                                                                                                   | IV                                    | Delays and Impedance                            | # of Pulses or Test Time      | Pulse / Burst rep. time  |  |

| 1                  | -112                                                                                                                                                                                                                                                                | -150                                  | 2 ms, 10 Ω                                      | 500 pulses                    | 0.5 s                    |  |

| 2a                 | 55                                                                                                                                                                                                                                                                  | 112                                   | 0.05 ms, 2 $\Omega$                             | 500 pulses                    | 0.5 s                    |  |

| 3a                 | -165                                                                                                                                                                                                                                                                | -220                                  | 0.1 us, 50 Ω                                    | 1 h                           | 100 ms                   |  |

| 3b                 | 112                                                                                                                                                                                                                                                                 | 150                                   | 0.1 us, 50 Ω                                    | 1 h                           | 100 ms                   |  |

| ISO<br>7637-2:2011 | Test nesults                                                                                                                                                                                                                                                        |                                       |                                                 |                               |                          |  |

| Test Pulse         | III                                                                                                                                                                                                                                                                 | IV                                    |                                                 |                               |                          |  |

| 1                  |                                                                                                                                                                                                                                                                     | А                                     |                                                 |                               |                          |  |

| 2a                 | A                                                                                                                                                                                                                                                                   | E                                     |                                                 |                               |                          |  |

| 3a                 |                                                                                                                                                                                                                                                                     | А                                     |                                                 |                               |                          |  |

| 3b                 |                                                                                                                                                                                                                                                                     | A                                     |                                                 |                               |                          |  |

| Class              |                                                                                                                                                                                                                                                                     |                                       | Functional                                      | Status                        |                          |  |

| А                  | All functions of a device perform as designed during and after exposure to disturbance.                                                                                                                                                                             |                                       |                                                 |                               |                          |  |

| В                  | All functions of a device perform as designed during exposure. However, one or more of them can go beyond speci-<br>fied tolerance. All functions return automatically to within normal limits after exposure is removed. Memory functions<br>shall remain class A. |                                       |                                                 |                               |                          |  |

| С                  | One or more functions of a device do not perform as designed during exposure but return automatically to normal operation after exposure is removed.                                                                                                                |                                       |                                                 |                               |                          |  |

| D                  | One or more functions of a device do not perform as designed during exposure and do not return to normal operation until exposure is removed and the device is reset by simple "operator/use" action.                                                               |                                       |                                                 |                               |                          |  |

| E                  |                                                                                                                                                                                                                                                                     | nctions of a devi<br>n without replac | ce do not perform as designe<br>ing the device. | d during and after exposure a | nd cannot be returned to |  |

#### **Application Information**

Figure 33. Application Schematic

#### Loss of Ground Protection

When device or ECU ground connection is lost and load is still connected to ground, the device will turn the output OFF. In loss of ground state, the output stage is held OFF independent of the state of the input. Input resistors are recommended between the device and microcontroller.

#### **Reverse Battery Protection**

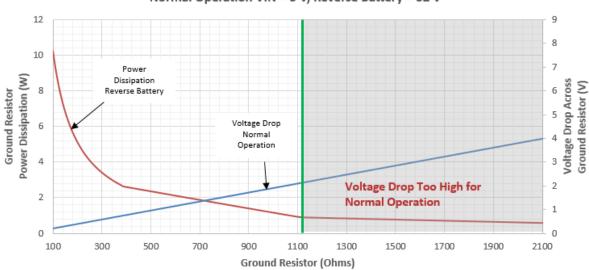

Solution 1: Resistor in the GND line only (no parallel Diode) The following calculations are true for any type of load.

In the case for no diode in parallel with  $R_{GND}$ , the calculations below explain how to size the resistor.

Consider the following parameters:  $-I_{GND}$  Maximum = 200 mA for up to  $-V_D = 32$  V.

Where  $-I_{GND}$  is the DC reverse current through the GND pin and  $-V_D$  is the DC reverse battery voltage.

$$-I_{GND} = \frac{-V_D}{R_{GND}}$$

(eq. 1)

Since this resistor can be used amongst multiple High–Side devices, please take note the sum of the maximum active GND currents ( $I_{GND(On)max}$ ) for each device when sizing the resistor. Please note that if the microprocessor GND is not shared by the device GND, then  $R_{GND}$  produces a shift of ( $I_{GND(On)max} * R_{GND}$ ) in the input thresholds and CS output values. If the calculated power dissipation leads to too large of a resistor size or several devices have to share the same resistor, please look at the second solution for Reverse Battery Protection. Refer to the figure below for selecting the proper  $R_{GND}$ .

NCV84160 Reverse Battery Considerations Normal Operation VIN = 5 V, Reverse Battery = 32 V

Figure 34. Reverse Battery R<sub>GND</sub> Considerations

# Solution 2: Diode (DGND) in parallel with RGND in the ground line.

A resistor value of  $R_{GND} = 1$  kOhm should be selected and placed in parallel to  $D_{GND}$  if the device drives an inductive load. The diode ( $D_{GND}$ ) provides a ~600–700 mV shift in the input threshold and current sense values if the micro controller ground is not common to the device ground. This shift will not vary even in the case of multiple high–side devices using the same resistor/diode network.

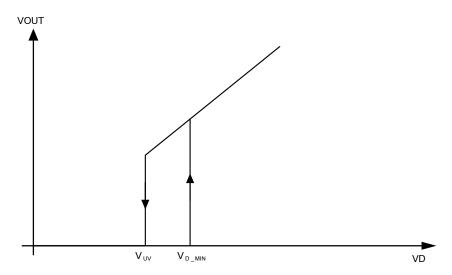

#### **Undervoltage Protection**

The device has two under-voltage threshold levels,  $V_{D\_MIN}$  and  $V_{UV}$ . Switching function (ON/OFF) requires supply voltage to be at least  $V_{D\_MIN}$ . The device features a lower supply threshold  $V_{UV}$ , above which the output can remain in ON state. While all protection functions are guaranteed when the switch is ON, diagnostic functions are operational only within nominal supply voltage range  $V_{D}$ .

Figure 35. Undervoltage Behavior

#### **Overvoltage Protection**

The NCV84160 has two Zener diodes ZV<sub>D</sub> and ZCS, which provide integrated overvoltage protection. ZV<sub>D</sub> protects the logic block by clamping the voltage between supply pin V<sub>D</sub> and ground pin GND to VZV<sub>D</sub>. ZCS limits voltage at current sense pin CS to  $V_D - VZCS$ . The output power MOSFET's output clamping diodes provide protection by clamping the voltage across the MOSFET (between V<sub>D</sub> pin and OUT pin) to VCLAMP. During overvoltage protection, current flowing through ZV<sub>D</sub>, ZCS and the output clamp must be limited. Load impedance ZL limits the current in the body diode ZBody. In order to limit the current in  $ZV_D$  a resistor, RGND (150  $\Omega$ ), is required in the GND path. External resistors RCS and RSENSE limit the current flowing through ZCS and out of the CS pin into the micro-controller I/O pin. With RGND, the GND pin voltage is elevated to V<sub>D</sub> - VZV<sub>D</sub> when the supply voltage V<sub>D</sub> rises above VZV<sub>D</sub>. ESD diodes ZESD pull up the voltage at logic pins IN, CS Dis close to the GND pin voltage  $V_D$  – VZV<sub>D</sub>. External resistors RIN, and RCS DIS are required to limit the current flowing out of the logic pins into the micro-controller I/O pins. During overvoltage exposure, the device transitions into a self-protection state, with automatic recovery after the supply voltage comes back to the normal operating range. The specified parameters as well as short circuit robustness and energy capability cannot be guaranteed during overvoltage exposure.

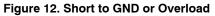

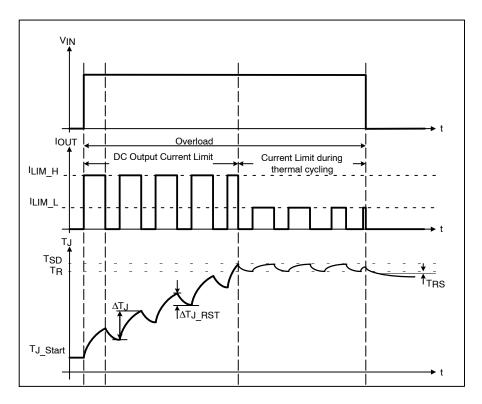

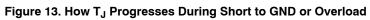

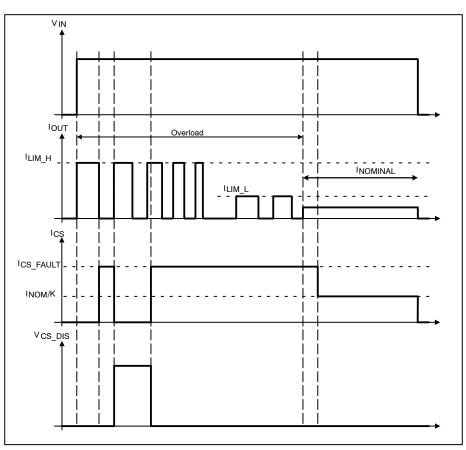

#### **Overload Protection**

Current limitation as well as over-temperature shutdown mechanisms are integrated into the NCV84160 to provide protection from overload conditions such as bulb inrush or short to ground.

#### **Current Limitation**

In case of overload, the NCV84160 limits the current in the output power MOSFET to a safe value. Due to high power dissipation during current limitation, the device's junction temperature increases rapidly. In order to protect the device, the output driver is shut down by one of the two over-temperature protection mechanisms. The output current limitation level is dependent on the drain-to-source voltage of the power MOSFET. If the input remains active during the shutdown, the output power MOSFET will automatically be re-activated after a minimum OFF time or when the junction temperature returns to a safe level.

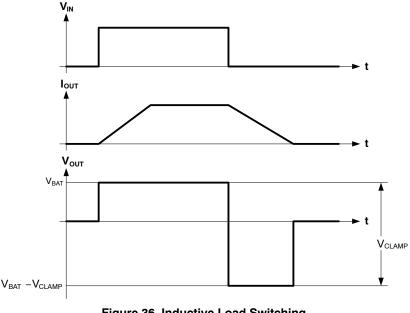

#### **Output Clamping with Inductive Load Switch Off:**

The output voltage  $V_{OUT}$  drops below GND potential when switching off inductive loads. This is because the inductance develops a negative voltage across the load in response to a decaying current. The integrated clamp of the device clamps the negative output voltage to a certain level relative to the supply voltage  $V_{BAT}$ . During output clamping with inductive load switch off, the energy stored in the inductance is rapidly dissipated in the device resulting in high power dissipation. This is a stressful condition for the device and the maximum energy allowed for a given load inductance should not be exceeded in any application.

Figure 36. Inductive Load Switching

Figure 37. Maximum Switch–Off Current vs. Load Inductance, V\_D = 13.5 V; R\_L = 0  $\Omega$

#### **Open Load Detection in OFF State**

Open load diagnosis in the OFF-state can be performed by activating an external resistive pull-up path (RPU) to VBAT. To calculate the pull-up resistance, external leakage currents (designed pull-down resistance, humidity-induced leakage etc) as well as the open load threshold voltage VOL have to be taken into account.

Figure 38. Off State Open Load Detection Circuit

#### **Current Sense in PWM Mode**

While operating in PWM mode, the current sense functionality can be used, but the timing of the input signal and the response time of the current sense need to be considered. When operating in PWM mode, the following performance is to be expected. The CS\_DIS pin should be left low to eliminate any unnecessary delay time to the circuit. When  $V_{IN}$  switches from low to high, there will be

a typical delay (tCS\_High2) before the current sense responds. Once this timing delay has passed, the rise time of the current sense output ( $\Delta tCS_High2$ ) also needs to be considered. When V<sub>IN</sub> switches from high to low a delay time (tCS\_Low1) needs to be considered. As long as these timing delays are allowed, the current sense pin can be operated in PWM mode.

#### PACKAGE AND PCB THERMAL DATA (Note 1)

Figure 39. Junction to Ambient Transient Thermal Impedance (Min. Pad Cu Area)

Figure 40. Junction to Ambient Transient Thermal Impedance (2 cm<sup>2</sup> Cu Area)

1. PCB FR4 Area = 4.8 cm x 4.8 cm, PCB Thickness = 1.6 mm, backside plane covered with 1 oz. Cu (backside plane not electrically connected)

# onsemí

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

## STYLES ON PAGE 2

| DOCUMENT NUMBER:                                                                     | 98ASB42564B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

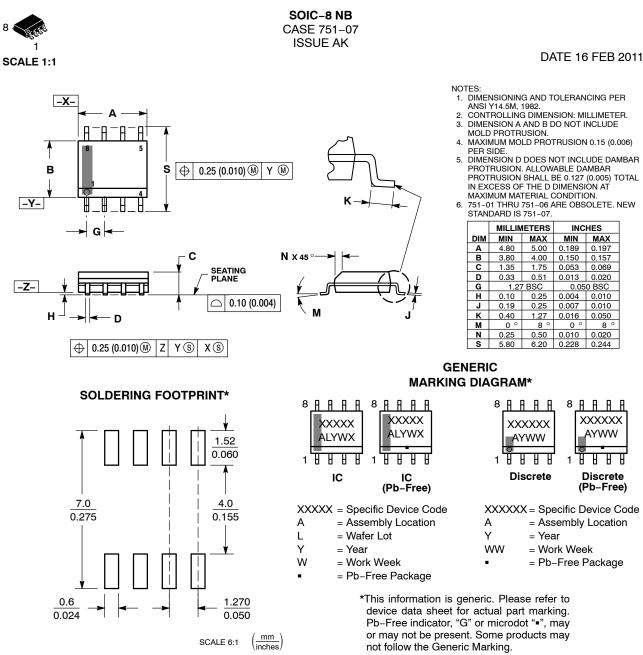

| DESCRIPTION:                                                                         | SOIC-8 NB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                     | PAGE 1 OF 2 |  |  |  |

| the right to make changes without furth<br>purpose, nor does <b>onsemi</b> assume ar | onsemi and ONSEMI. are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others. |                                                                                                                                                                                     |             |  |  |  |

#### SOIC-8 NB CASE 751-07 **ISSUE AK**

STYLE 1: PIN 1. EMITTER COLLECTOR 2. 3. COLLECTOR 4. EMITTER 5. EMITTER BASE 6. 7 BASE EMITTER 8. STYLE 5: PIN 1. DRAIN 2. DRAIN 3. DRAIN DRAIN 4. GATE 5. 6. GATE SOURCE 7. 8. SOURCE STYLE 9: PIN 1. EMITTER, COMMON COLLECTOR, DIE #1 COLLECTOR, DIE #2 2. З. EMITTER, COMMON 4. 5. EMITTER, COMMON 6 BASE. DIE #2 BASE, DIE #1 7. 8. EMITTER, COMMON STYLE 13: PIN 1. N.C. 2. SOURCE 3 GATE 4. 5. DRAIN 6. DRAIN DRAIN 7. DRAIN 8. STYLE 17: PIN 1. VCC 2. V2OUT V10UT З. TXE 4. 5. RXE 6. VFF 7. GND 8. ACC STYLE 21: PIN 1. CATHODE 1 2. CATHODE 2 3 CATHODE 3 CATHODE 4 4. 5. CATHODE 5 6. COMMON ANODE COMMON ANODE 7. 8. CATHODE 6 STYLE 25: PIN 1. VIN 2 N/C REXT З. 4. GND 5. IOUT IOUT 6. IOUT 7. 8. IOUT STYLE 29: BASE, DIE #1 PIN 1. 2 EMITTER, #1 BASE, #2 З. EMITTER, #2 4. 5 COLLECTOR, #2 COLLECTOR, #2 6.

STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 COLLECTOR, #2 3. 4 COLLECTOR, #2 BASE, #2 5. EMITTER, #2 6. 7 BASE #1 EMITTER, #1 8. STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN SOURCE 4. SOURCE 5. 6. GATE GATE 7. 8. SOURCE STYLE 10: GROUND PIN 1. BIAS 1 OUTPUT 2. З. GROUND 4. 5. GROUND 6 BIAS 2 INPUT 7. 8. GROUND STYLE 14: PIN 1. N-SOURCE 2. N-GATE 3 P-SOURCE P-GATE 4. P-DRAIN 5 6. P-DRAIN N-DRAIN 7. N-DRAIN 8. STYLE 18: PIN 1. ANODE ANODE 2. SOURCE 3. GATE 4. 5. DRAIN 6 DRAIN CATHODE 7. CATHODE 8. STYLE 22 PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC 3 COMMON CATHODE/VCC 4. I/O LINE 3 COMMON ANODE/GND 5. 6. I/O LINE 4 7. I/O LINE 5 8. COMMON ANODE/GND STYLE 26: PIN 1. GND 2 dv/dt З. ENABLE 4. ILIMIT 5. SOURCE SOURCE 6. SOURCE 7. 8. VCC STYLE 30: DRAIN 1 PIN 1. DRAIN 1 2 GATE 2 З. SOURCE 2 4 SOURCE 1/DRAIN 2 SOURCE 1/DRAIN 2 5.

6.

7.

8 GATE 1

SOURCE 1/DRAIN 2

STYLE 3: PIN 1. DRAIN, DIE #1 DRAIN, #1 2. DRAIN, #2 З. DRAIN, #2 4. GATE, #2 5. SOURCE, #2 6. 7 GATE #1 8. SOURCE, #1 STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS THIRD STAGE SOURCE GROUND З. 4. 5. DRAIN 6. GATE 3 SECOND STAGE Vd 7. FIRST STAGE Vd 8. STYLE 11: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. З. GATE 2 4. 5. DRAIN 2 6. DRAIN 2 DRAIN 1 7. 8. DRAIN 1 STYLE 15: PIN 1. ANODE 1 2. ANODE 1 ANODE 1 3 ANODE 1 4. 5. CATHODE, COMMON CATHODE, COMMON CATHODE, COMMON 6. 7. CATHODE, COMMON 8. STYLE 19: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. 3. GATE 2 4. 5. DRAIN 2 6. MIRROR 2 7. DRAIN 1 MIRROR 1 8. STYLE 23: PIN 1. LINE 1 IN COMMON ANODE/GND COMMON ANODE/GND 2. 3 LINE 2 IN 4. LINE 2 OUT 5. COMMON ANODE/GND COMMON ANODE/GND 6. 7. 8. LINE 1 OUT STYLE 27: PIN 1. ILIMIT OVI O 2 UVLO З. 4. INPUT+ 5. 6. SOURCE SOURCE SOURCE 7. 8 DRAIN

#### DATE 16 FEB 2011

STYLE 4: PIN 1. 2. ANODE ANODE ANODE З. 4. ANODE ANODE 5. 6. ANODE 7 ANODE COMMON CATHODE 8. STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 З. BASE #2 COLLECTOR, #2 4. COLLECTOR, #2 5. 6. EMITTER, #2 EMITTER, #1 7. 8. COLLECTOR, #1 STYLE 12: PIN 1. SOURCE SOURCE 2. 3. GATE 4. 5. DRAIN 6 DRAIN DRAIN 7. 8. DRAIN STYLE 16 EMITTER, DIE #1 PIN 1. 2. BASE, DIE #1 EMITTER, DIE #2 3 BASE, DIE #2 4. 5. COLLECTOR, DIE #2 6. COLLECTOR, DIE #2 COLLECTOR, DIE #1 7. COLLECTOR, DIE #1 8. STYLE 20: PIN 1. SOURCE (N) GATE (N) SOURCE (P) 2. 3. 4. GATE (P) 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 24: PIN 1. BASE EMITTER 2. 3 COLLECTOR/ANODE COLLECTOR/ANODE 4. 5. CATHODE 6. CATHODE COLLECTOR/ANODE 7. 8. COLLECTOR/ANODE STYLE 28: PIN 1. SW\_TO\_GND 2. DASIC OFF DASIC\_SW\_DET З. 4. GND 5. 6. V MON VBULK 7. VBULK 8 VIN

| DOCUMENT NUMBER: | 98ASB42564B Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |             |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|--|--|

| DESCRIPTION:     | SOIC-8 NB                                                                                                                                                                                       |  | PAGE 2 OF 2 |  |  |

|                  |                                                                                                                                                                                                 |  |             |  |  |

onsem and of isor in are trademarks or semiconductor compension instructions, the do onsem or its subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced stat purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

7.

8

COLLECTOR, #1

COLLECTOR, #1

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent\_Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com

ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at <u>www.onsemi.com/support/sales</u>