# www.Dat**NCP5393A**

# Product Preview 2/3/4-Phase Controller for CPU Applications

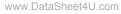

The NCP5393A is a multiphase synchronous buck regulator controller designed to power the Core and Northbridge of an AMD microprocessor. The controller has a user configurable two, three, or four phase regulator for the Core and an independent single phase regulator to power the microprocessor Northbridge. The NCP5393A incorporates differential voltage sensing, differential phase current sensing, optional load–line voltage positioning, and programmable  $V_{DD}$  and  $V_{DDNB}$  offsets to provide accurately regulated power parallel– and serial–VID AMD processors. Dual–edge multiphase modulation provides the fastest initial response to dynamic load events. This reduces system cost by requiring less bulk and ceramic output capacitance to meet transient regulation specifications.

High performance operational error amplifiers are provided to simplify compensation of the  $V_{DD}$  and  $V_{DDNB}$  regulators. Dynamic Reference Injection further simplifies loop compensation by eliminating the need to compromise between response to load transients and response to VID code changes.

### Features

- Meets AMD's Hybrid VR Specifications

- Up to Four V<sub>DD</sub> Phases

- Single-Phase V<sub>DDNB</sub> Controller

- Dual-Edge PWM for Fastest Initial Response to Transient Loading

- High Performance Operational Error Amplifiers

- Internal Soft Start and Slew Rate Limiting

- Dynamic Reference Injection (Patent #US07057381)

- DAC Range from 12.5 mV to 1.55 V

- $\pm 0.5\%$  DAC Accuracy fro 0.8 V to 1.55 V

- V<sub>DD</sub> and V<sub>DD</sub> Offset Ranges 0 mV 800 mV

- True Differential Remote Voltage Sense Amplifiers

- Phase-to-Phase I<sub>DD</sub> Current Balancing

- Differential Current Sense Amplifiers for Each Phase of Each Output

- "Lossless" Inductor Current Sensing for V<sub>DD</sub> and V<sub>DDNB</sub> Outputs

- Supports Load Lines (Droop) for V<sub>DD</sub> and V<sub>DDNB</sub> Outputs

- Oscillator Range of 100 kHz 1 MHz

- Tracking Over Voltage Protection

- Output Inductor DCR–Based Over Current Protection for  $V_{DD}$  and  $V_{DDNB}$  Outputs

- Guaranteed Startup into Precharged Loads

- Temperature Range: 0°C to 70°C

- This is a Pb–Free Device

## Applications

- Desktop Processors

- Server Processors

- High-End Notebook PCs

This document contains information on a product under development. ON Semiconductor reserves the right to change or discontinue this product without notice.

# **ON Semiconductor®**

http://onsemi.com

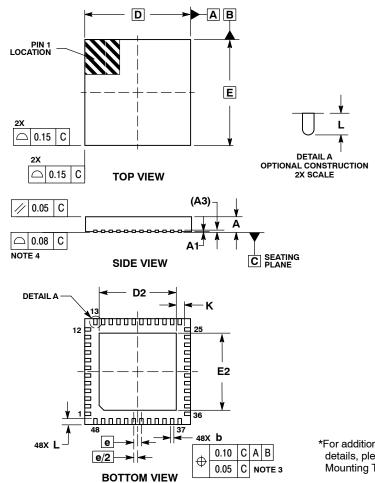

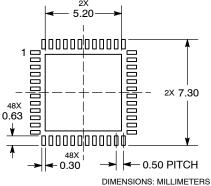

#### **ORDERING INFORMATION**

| Device        | Package            | Shipping <sup>†</sup> |

|---------------|--------------------|-----------------------|

| NCP5393AMNR2G | QFN48<br>(Pb–Free) | 2500 / Tape & Reel    |

+ For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

www.DataSheet4U.com

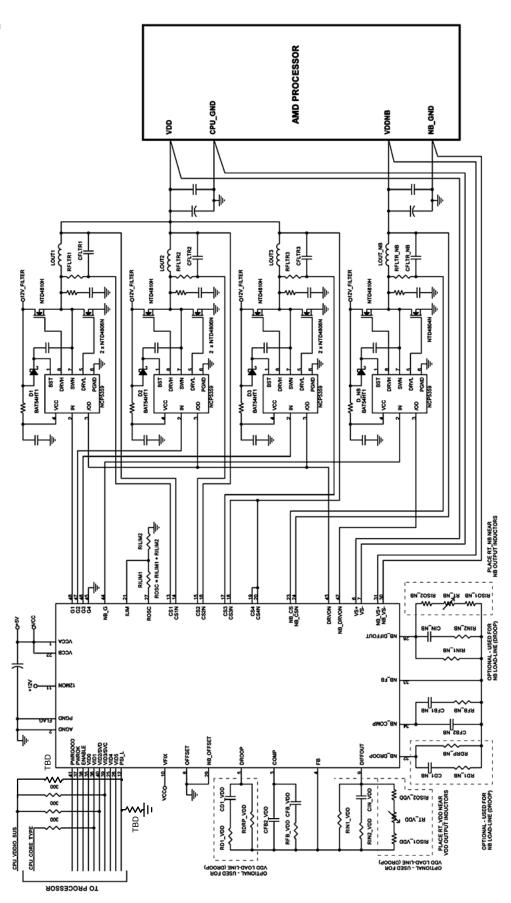

Figure 3. NCP5393A Configured for 3 + 1 Phases, with Optional Droop

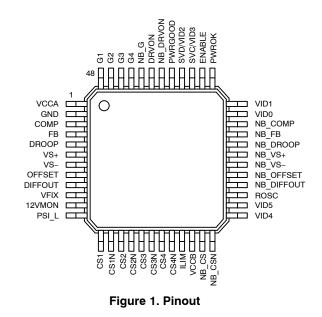

#### www.Data NCP5393A PIN DESCRIPTIONS

| Pin No. | Symbol     | Description                                                                                                                                                                                                                         |

|---------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | VCCA       | 5 V supply pin for the NCP5393A. The V <sub>CC</sub> bypassing capacitance must be connected between this pin and GND (preferably returned to the package flag).                                                                    |

| 2       | GND        | Small-signal power supply return. This pin should be tied directly to the package flag (exposed pad).                                                                                                                               |

| 3       | COMP       | Output of the voltage error amplifier for the V <sub>DD</sub> regulator.                                                                                                                                                            |

| 4       | FB         | Voltage error amplifier inverting input for the V <sub>DD</sub> regulator.                                                                                                                                                          |

| 5       | DROOP      | Voltage output signal proportional to total current drawn from the V <sub>DD</sub> regulator. Used when load line operation ("droop") is desired.                                                                                   |

| 6       | VS+        | Non-inverting input to the differential remote sense amplifier for the V <sub>DD</sub> regulator.                                                                                                                                   |

| 7       | VS-        | Inverting input to the differential remote sense amplifier for the V <sub>DD</sub> regulator.                                                                                                                                       |

| 8       | OFFSET     | Input for offset voltage to be added to the $V_{DD}$ DAC's output voltage. Ground this pin for zero $V_{DD}$ offset.                                                                                                                |

| 9       | DIFFOUT    | Output of the differential remote sense amplifier for the V <sub>DD</sub> regulator.                                                                                                                                                |

| 10      | VFIX       | When pulled low, this pin causes the levels on the SVC (VID3) and SVD (VID2) pins to be decoded as a two-bit DAC code, which controls the V <sub>DD</sub> and VDDNB outputs. Internally pulled high by 5 $\mu$ A to V <sub>CC</sub> |

| 11      | 12VMON     | UVLO monitor input for the 12 V power rail.                                                                                                                                                                                         |

| 12      | PSI_L      | Determines number of phases operating in PSI_L mode. Phase shed count is locked upon ENABLE assertion. After soft-start, becomes power saving control in PVID mode. Low = phase shed operation, High = normal operation.            |

| 13      | CS1        | Non-inverting input to current sense amplifier #1 for the $V_{\mbox{DD}}$ regulator. See Table: "Pin Connections vs. Phase Count"                                                                                                   |

| 14      | CS1N       | Inverting input to current sense amplifier #1 for the V <sub>DD</sub> regulator. See Table: "Pin Connections vs. Phase Count"                                                                                                       |

| 15      | CS2        | Non-inverting input to current sense amplifier #2 for the V <sub>DD</sub> regulator. See Table: "Pin Connections vs. Phase Count"                                                                                                   |

| 16      | CS2N       | Inverting input to current sense amplifier #2 for the V <sub>DD</sub> regulator. See Table: "Pin Connections vs. Phase Count"                                                                                                       |

| 17      | CS3        | Non-inverting input to current sense amplifier #3 for the V <sub>DD</sub> regulator. See Table: "Pin Connections vs. Phase Count"                                                                                                   |

| 18      | CS3N       | Inverting input to current sense amplifier #3 for the V <sub>DD</sub> regulator. See Table: "Pin Connections vs. Phase Count"                                                                                                       |

| 19      | CS4        | Non-inverting input to current sense amplifier #4 for the V <sub>DD</sub> regulator. See Table: "Pin Connections vs. Phase Count"                                                                                                   |

| 20      | CS4N       | Inverting input to current sense amplifier #4 for the V <sub>DD</sub> regulator. See Table: "Pin Connections vs. Phase Count"                                                                                                       |

| 21      | ILIM       | Overcurrent shutdown threshold for $V_{DD}$ and VDDNB. A resistor divider from ROSC to GND is typically used to develop an appropriate voltage on ILIM.                                                                             |

| 22      | VCCB       | 5 V supply pin. Tie this pin to VCCA (Pin 1).                                                                                                                                                                                       |

| 23      | NB_CS      | Non-inverting input to the current sense amplifier for the VDDNB regulator                                                                                                                                                          |

| 24      | NB_CSN     | Inverting input to the current sense amplifier for the VDDNB regulator                                                                                                                                                              |

| 25      | VID4       | Parallel Voltage ID DAC Input 4. Not used in SVI mode.                                                                                                                                                                              |

| 26      | VID5       | Parallel Voltage ID DAC Input 5. Not used in SVI mode.                                                                                                                                                                              |

| 27      | ROSC       | A resistance from this pin to ground programs the $V_{DD}$ and VDDNB oscillator frequencies. This pin supplies a trimmed output voltage of 2 V.                                                                                     |

| 28      | NB_DIFFOUT | Output of the differential remote sense amplifier for the VDDNB regulator.                                                                                                                                                          |

| 29      | NB_OFFSET  | Input for offset voltage to be added to the VDDNB DAC's output voltage. Ground this pin for zero VDDNB offset.                                                                                                                      |

| 30      | NB_VS-     | Inverting input to the differential remote sense amplifier for the VDDNB regulator.                                                                                                                                                 |

| 31      | NB_VS+     | Non-inverting input to the differential remote sense amplifier for the VDDNB regulator.                                                                                                                                             |

#### www.Data NCP5393A PIN DESCRIPTIONS

| Pin No. | Symbol   | Description                                                                                                                             |

|---------|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 32      | NB_DROOP | Voltage output signal proportional to total current drawn from the VDDNB regulator. Used when load line operation ("droop") is desired. |

| 33      | NB_FB    | Voltage error amplifier inverting input for the V <sub>DDNB</sub> regulator.                                                            |

| 34      | NB_COMP  | Output of the voltage error amplifier for the V <sub>DDNB</sub> regulator.                                                              |

| 35      | VID0     | Parallel Voltage ID DAC Input 0. Not used in SVI mode.                                                                                  |

| 36      | VID1     | Parallel Voltage ID DAC Input 1. Also used for PVI or SVI mode selection.                                                               |

| 37      | PWROK    | System power supplies status input. Used in SVI mode only.                                                                              |

| 38      | ENABLE   | High = Run, Low = Standby/Reset.                                                                                                        |

| 39      | VID3/SVC | Parallel Voltage ID DAC Input 1. Also used in SVI mode.                                                                                 |

| 40      | VID2/SVD | Parallel Voltage ID DAC Input 1. Also used in SVI mode.                                                                                 |

| 41      | PWRGOOD  | Open drain output. High indicates that the active output(s) are within specification. Internally pulled high by 5 $\mu A$ to $V_{CC}$   |

| 42      | NB_DRVON | Bidirectional Gate Drive Enable to the gate driver for the V <sub>DDNB</sub> regulator.                                                 |

| 43      | DRVON    | Bidirectional Gate Drive Enable to gate drivers for the V <sub>DD</sub> regulator.                                                      |

| 44      | NB_G     | PWM output to the V <sub>DDNB</sub> gate driver.                                                                                        |

| 45      | G4       | PWM output #4. See Table: "Pin Connections vs. Phase Count"                                                                             |

| 46      | G3       | PWM output #3. See Table: "Pin Connections vs. Phase Count"                                                                             |

| 47      | G2       | PWM output #2. See Table: "Pin Connections vs. Phase Count"                                                                             |

| 48      | G1       | PWM output #1. See Table: "Pin Connections vs. Phase Count"                                                                             |

| FLAG    | PGND     | High-current power supply return via metal pad (flag) underneath package. The package flag should be tied directly to Pin 2.            |

## **PIN CONNECTIONS VS. PHASE COUNT**

| Number of<br>Phases | G4      | G3      | G2      | G1      | CS4 &<br>CS4N      | CS3 &<br>CS3N | CS2 &<br>CS2N      | CS1 &<br>CS1N |

|---------------------|---------|---------|---------|---------|--------------------|---------------|--------------------|---------------|

| 4                   | Phase 4 | Phase 3 | Phase 2 | Phase 1 | Phase 4 CS         | Phase 3 CS    | Phase 2 CS         | Phase 1 CS    |

|                     | Out     | Out     | Out     | Out     | Input              | Input         | Input              | Input         |

| 3                   | Tie to  | Phase 3 | Phase 2 | Phase 1 | Tie to GND         | Phase 3 CS    | Phase 2 CS         | Phase 1 CS    |

|                     | GND     | Out     | Out     | Out     | or V <sub>DD</sub> | Input         | Input              | Input         |

| 2                   | Tie to  | Phase 2 | Tie to  | Phase 1 | Tie to GND         | Phase 2 CS    | Tie to GND         | Phase 1 CS    |

|                     | GND     | Out     | GND     | Out     | or V <sub>DD</sub> | input         | or V <sub>DD</sub> | Input         |

#### www.Data ABSOLUTE MAXIMUM RATINGS **ELECTRICAL INFORMATION**

| Pin Symbol          | V <sub>MAX</sub> | V <sub>MIN</sub> | ISOURCE | I <sub>SINK</sub> |

|---------------------|------------------|------------------|---------|-------------------|

| 12VMON              | 13.2 V           | –0.3 V           | N/A     | <b>50</b> μA      |

| VCC                 | 7.0 V            | –0.3 V           | N/A     | 10 mA             |

| COMP, NB_COMP       | 5.5 V            | –0.3 V           | 10 mA   | 10 mA             |

| DROOP, NB_DROOP     | 5.5 V            | –0.3 V           | 5 mA    | 5 mA              |

| DIFFOUT, NB_DIFFOUT | 5.5 V            | –0.3 V           | 20 mA   | 20 mA             |

| DRVON, NB_DRVON     | 5.5 V            | –0.3 V           | 5 mA    | 10 mA             |

| PWRGOOD             | 5.5 V            | –0.3 V           | N/A     | 20 mA             |

| VS+, NB_VS+         | 3 V              | –0.3 V           | 1 mA    | 1 mA              |

| VS-, NB_VS-         | 0.3 V            | –0.3 V           | 1 mA    | 1 mA              |

| ROSC                | 5.5 V            | –0.3 V           | 1 mA    | N/A               |

| All Other Pins      | 5.5 V            | –0.3 V           | N/A     | N/A               |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

NOTE: All signals are referenced to GND unless noted otherwise.

#### THERMAL INFORMATION

| Rating                                        | Symbol           | Value       | Unit |

|-----------------------------------------------|------------------|-------------|------|

| Thermal Characteristic, QFN Package (Note 1)  | $R_{\theta JA}$  | 30.5        | °C/W |

| Operating Junction Temperature Range (Note 2) | TJ               | 0 to 125    | °C   |

| Operating Ambient Temperature Range           | T <sub>A</sub>   | 0 to 70     | °C   |

| Maximum Storage Temperature Range             | T <sub>STG</sub> | –55 to +150 | °C   |

| Moisture Sensitivity Level, QFN Package       | MSL              | 1           |      |

\* The maximum package power dissipation must be observed. 1. JESD 51–5 (1S2P Direct–Attach Method) with 0 LFM.

2. JESD 51-7 (1S2P Direct-Attach Method) with 0 LFM.

| Parameter                                                  | Test Conditions                                                                                                                                                                                                                                      | Min              | Тур         | Max           | Un            |

|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------|---------------|---------------|

| ERROR AMPLIFIERS (VDD & VDDNB)                             | )                                                                                                                                                                                                                                                    | •                | I.          |               |               |

| Input Bias Current                                         |                                                                                                                                                                                                                                                      | -200             | -           | 200           | nA            |

| Input Offset Voltage (Note 3)                              | V+ = V- = 1.3V                                                                                                                                                                                                                                       | -1.0             | -           | 1.0           | m∖            |

| Open Loop DC Gain                                          | $C_L$ = 60 pF to GND, $R_L$ = 10 k $\Omega$ to GND                                                                                                                                                                                                   | -                | 80          | -             | dB            |

| Open Loop Unity Gain Bandwidth                             | $C_L = 60 \text{ pF to GND}, R_L = 10 \text{ k}\Omega \text{ to GND}$                                                                                                                                                                                | -                | 15          | -             | MH            |

| Open Loop Phase Margin                                     | $C_L = 60 \text{ pF to GND}, R_L = 10 \text{ k}\Omega \text{ to GND}$                                                                                                                                                                                | -                | 70          | -             | deg           |

| Slew Rate                                                  | $\begin{array}{l} \Delta V_{IN} = 100 \text{ mV}, \text{AV} = -10 \text{ V/V}, \\ 1.5 \text{ V} < V_{COMP} < 2.5 \text{ V}, \\ C_L = 60 \text{ pF}, \text{ DC Loading} = \pm 125 \ \mu\text{A} \end{array}$                                          | _                | 5           | _             | V/µ           |

| Maximum Output Voltage                                     | 10 mV of Overdrive, I <sub>SOURCE</sub> = 2.0 mA                                                                                                                                                                                                     | 3.5              | _           | -             | V             |

| Minimum Output Voltage                                     | 10 mV of Overdrive, I <sub>SINK</sub> = 2.0 mA                                                                                                                                                                                                       | -                | -           | 1.0           | V             |

| Output Source Current (Note 3)                             | 10 mV of Overdrive, V <sub>OUT</sub> = 3.5 V                                                                                                                                                                                                         | -                | 2           | -             | mA            |

| Output Sink Current (Note 3)                               | 10 mV of Overdrive, V <sub>OUT</sub> = 1.0 V                                                                                                                                                                                                         | -                | 2           | -             | mA            |

| DIFFERENTIAL SUMMING AMPLIFI                               | ERS (V <sub>DD</sub> & V <sub>DDNB</sub> )                                                                                                                                                                                                           |                  |             |               |               |

| VS- Input Bias Current                                     | VS- Voltage at 0 V                                                                                                                                                                                                                                   |                  | 33          |               | μA            |

| VS+ Input Resistance                                       | DRVON = Low                                                                                                                                                                                                                                          |                  | 1.0         |               | kΩ            |

|                                                            | DRVON = High                                                                                                                                                                                                                                         |                  | 7           |               |               |

| VS+ Input Bias Voltage                                     | DRVON = Low                                                                                                                                                                                                                                          |                  | 0.37        |               | V             |

|                                                            | DRVON = High                                                                                                                                                                                                                                         |                  | 0.05        |               |               |

| VS+ Input Voltage Range (Note 3)                           |                                                                                                                                                                                                                                                      | -0.3             | -           | 3.0           | V             |

| VS- Input Voltage Range (Note 3)                           |                                                                                                                                                                                                                                                      | -0.3             | _           | 0.3           | V             |

| -3dB Bandwidth (Note 3)                                    | $C_L$ = 80 pF to GND, $R_L$ = 10 k $\Omega$ to GND                                                                                                                                                                                                   |                  | 15          |               | MH            |

| DC gain, VS+ to DIFFOUT                                    | VS+ to VS- = 0.5 V to 2.35 V                                                                                                                                                                                                                         | 0.982            | 1.0         | 1.022         | V/\           |

| DAC Accuracy (Measured at VS+)                             | $\begin{array}{l} \mbox{Closed Loop Measurement, Error Amplifier Inside the} \\ \mbox{Loop.} \\ 1.0125 \ V \leq \ VDAC \ \leq \ 1.5500 \ V \\ 0.8000 \ V \leq \ VDAC \ \leq \ 1.0000 \ V \\ 12.5 \ mV \ \leq \ VDAC \ \leq \ 0.8000 \ V \end{array}$ | -0.5<br>-5<br>-8 | -<br>-<br>- | 0.5<br>5<br>8 | %<br>m\<br>m\ |

| Slew Rate                                                  | $\Delta V_{IN}$ = 100 mV, $\Delta V_{OUT}$ = 1.3 V–1.2 V                                                                                                                                                                                             |                  | 10          |               | V/µ           |

| Maximum Output Voltage                                     | I <sub>SOURCE</sub> = 2 mA                                                                                                                                                                                                                           | 2.0              |             |               | V             |

| Minimum Output Voltage                                     | I <sub>SINK</sub> = 2 mA                                                                                                                                                                                                                             |                  |             | 0.5           | V             |

| Output source current (Note 3)                             | V <sub>OUT</sub> = 3 V                                                                                                                                                                                                                               |                  | 2.0         |               | mA            |

| Output sink current (Note 3)                               | V <sub>OUT</sub> = 0.5 V                                                                                                                                                                                                                             |                  | 2.0         |               | mA            |

| DROOP AMPLIFIERS (VDD & VDDNB)                             | )                                                                                                                                                                                                                                                    |                  | 1           |               |               |

| Gain from Current Sense Input to<br>Droop Amplifier Output | 0 mV < (CSx – CSxN) < 60 mV                                                                                                                                                                                                                          | 5.7              | 6.0         | 6.3           | V/\           |

| Droop Amplifier DC Output Voltage                          | CSx = CSxN = 1.3 V                                                                                                                                                                                                                                   |                  | 1.3         |               | V             |

| Slew Rate                                                  | $C_L$ = 20 pF to GND, $R_L$ = 1 k $\Omega$ to GND                                                                                                                                                                                                    | -                | 5.0         | -             | V/µ           |

| Maximum Output Voltage                                     | I <sub>SOURCE</sub> = 4.0 mA                                                                                                                                                                                                                         | 3.0              | -           | -             | V             |

| Minimum Output Voltage                                     | I <sub>SINK</sub> = 1.0 mA                                                                                                                                                                                                                           | -                | -           | 1.0           | V             |

| Output Source Current (Note 3)                             | V <sub>OUT</sub> = 3.0 V                                                                                                                                                                                                                             | -                | 4.0         | -             | m/            |

| Output Sink Current (Note 3)                               | V <sub>OUT</sub> = 1.0 V                                                                                                                                                                                                                             |                  | 1.0         | _             | m/            |

www.Data ELECTRICAL CHARACTERISTICS (Unless otherwise stated: 0°C≤T<sub>A</sub>≤70°C; 4.75 V≤V<sub>CC</sub>≤5.25 V; All DAC Codes; C<sub>VCC</sub> = 0.1 µF)

3. Guaranteed by design. Not production tested.

| Parameter                                            | Test Conditions                                                                                  | Min               | Тур         | Max               | U   |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------|-------------|-------------------|-----|

| CURRENT SENSE AMPLIFIERS (VDI                        | ) & V <sub>DDNB</sub> )                                                                          |                   | •           |                   |     |

| Input Bias Current                                   | CSx = CSxN = 1.4 V                                                                               | -50               | _           | 50                | n   |

| Common Mode Input Voltage Range                      |                                                                                                  | -0.3              | -           | 2.6               | \   |

| Differential Mode Input Voltage<br>Range (Note 3)    |                                                                                                  | -120              | -           | 120               | m   |

| Input Offset Voltage (Note 3)                        | CSx = CSxN = 1.00 V                                                                              | -1.0              | -           | 1.0               | m   |

| Gain from Current Sense Input to<br>PWM Comparator   | 0 mV < (CSx – CSxN) < 60 mV                                                                      | 5.0               | 6.0         | 7.0               | V/  |

| INTERNAL OFFSET VOLTAGE                              | ·                                                                                                |                   |             |                   | •   |

| Voltage at Error Amplifier Non-In-<br>verting Inputs |                                                                                                  | -                 | 1.3         | -                 | \   |

| DRVON & NB_DRVON                                     |                                                                                                  |                   |             |                   |     |

| Output Voltage (High)                                | Sourcing 500 μA                                                                                  | 3.0               | -           | -                 | \   |

| Output Voltage (Low)                                 | Sinking 500 μA                                                                                   | -                 | -           | 0.7               | \   |

| Delay Time                                           | Propagation Delays                                                                               | -                 | 10          | -                 | n   |

| Active Internal Pull-up Resistance                   | Sourcing 500 μA                                                                                  | -                 | 2.0         | -                 | k   |

| Active Internal Pull-down Resistance                 | Sinking 500 μA                                                                                   | -                 | 150         | -                 | 2   |

| Rise Time                                            | $C_L$ (PCB) = 20 pF, $\Delta V_{OUT}$ = 10% to 90%                                               | -                 | 130         | -                 | n   |

| Fall Time                                            | $C_{L}$ (PCB) = 20 pF, $\Delta V_{OUT}$ = 10% to 90%                                             | _                 | 15          | -                 | n   |

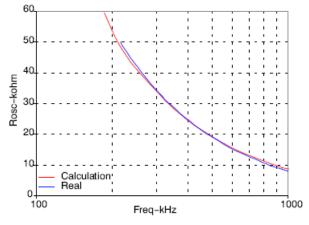

| V <sub>DD</sub> PWM OSCILLATOR                       |                                                                                                  | 1                 | 1           |                   |     |

| Switching Frequency Range                            |                                                                                                  | 100               | -           | 900               | k⊦  |

| Switching Frequency Accuracy<br>2- or 4-phase        | ROSC = 49.9 kΩ<br>ROSC = 24.9 kΩ<br>ROSC = 10 kΩ                                                 | 196<br>380<br>803 | -<br>-<br>- | 226<br>420<br>981 | k⊦  |

| Switching Frequency Accuracy<br>3-phase              | ROSC = 49.9 kΩ<br>ROSC = 24.9 kΩ<br>ROSC = 10 kΩ                                                 | 196<br>380<br>803 | -<br>-<br>- | 226<br>420<br>981 | kŀ  |

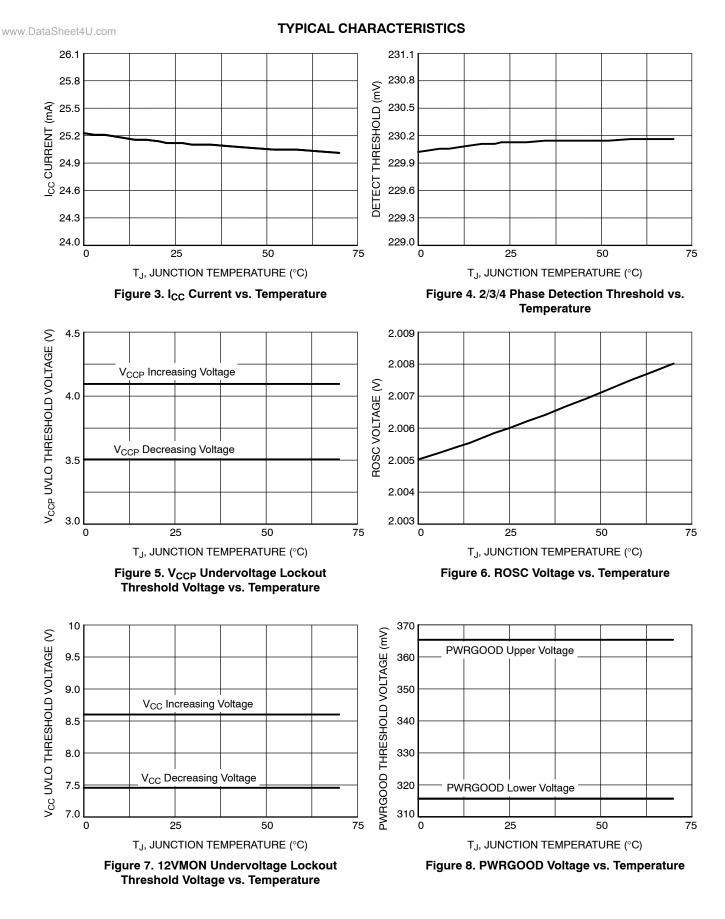

| ROSC Output Voltage                                  | 10 μA ≤ IROSC ≤ 200 μA                                                                           | 1.94              | 2.0         | 2.06              | \   |

| V <sub>DDNB</sub> PWM OSCILLATOR                     | 1                                                                                                |                   |             |                   |     |

| Switching Frequency                                  |                                                                                                  | -                 | 1.25        | -                 | x f |

| PWM COMPARATORS (V <sub>DD</sub> & V <sub>DDNB</sub> | 3)                                                                                               | 1                 | 1           |                   |     |

| Minimum Pulse Width (Note 3)                         | F <sub>SW</sub> = 800 kHz                                                                        | -                 | 30          | -                 | n   |

| Propagation Delay (Note 3)                           | ±20 mV of Overdrive                                                                              | -                 | 10          | -                 | n   |

| Magnitude of the PWM Ramp                            |                                                                                                  | -                 | 1.0         | -                 | \   |

| 0% Duty Cycle                                        | COMP Voltage at which the PWM Outputs Remain LOW                                                 | -                 | 0.2         | -                 | ١   |

| 100% Duty Cycle                                      | COMP Voltage at which the PWM Outputs Remain HIGH                                                | -                 | 1.2         | -                 | ۱.  |

| PWM Phase Angle Error                                | Between Adjacent Phases                                                                          | -15               |             | +15               | 0   |

| PWRGOOD OUTPUT                                       |                                                                                                  |                   |             |                   | -   |

| PWRGOOD Output Voltage (Low)                         | I <sub>PGD</sub> = 5 mA                                                                          | -                 | -           | 0.4               | \   |

| PWRGOOD Rise Time                                    | External Pullup of 1 k $\Omega$ to 5 V C <sub>TOTAL</sub> = 45 pF, $\Delta V_{OUT}$ = 10% to 90% | -                 | 125         | -                 | n   |

| PWRGOOD High-State Leakage                           | V <sub>PWRGOOD</sub> = 5.25 V                                                                    | _                 | _           | 1                 | μ   |

3. Guaranteed by design. Not production tested.

| Parameter                                          | Test Conditions                                                                                                 | Min     | Тур  | Max             | Unit |

|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|---------|------|-----------------|------|

| PWRGOOD OUTPUT                                     |                                                                                                                 |         | •    | •               |      |

| PWRGOOD Upper Threshold                            | V <sub>OUT</sub> Increasing, DAC = 1.3 V (Wrt DAC)                                                              | -       | 300  | -               | mV   |

| PWRGOOD Lower Threshold                            | V <sub>OUT</sub> Decreasing, DAC = 1.3 V                                                                        | -       | 350  | -               | mV   |

| PWM OUTPUTS (V <sub>DD</sub> & V <sub>DDNB</sub> ) | 1                                                                                                               | 1       |      |                 |      |

| Output Voltage (High)                              | Sourcing 500 μA                                                                                                 | 3.0     | -    | V <sub>CC</sub> | V    |

| Output Voltage (Mid)                               | $R_L = 4 k\Omega$ to GND                                                                                        | 1.3     | 1.5  | 1.7             | V    |

| Output Voltage (Low)                               | Sinking 500 μA                                                                                                  | _       | _    | 0.15            | V    |

| Rise and Fall Times                                | C <sub>L</sub> = 50 pF, 0.7 V to 3.0 V or 3.0 V to 0.7 V                                                        | _       | 15   | _               | ns   |

| Tri-State Output Leakage                           | Gx = 2.5 V (x = 1–4 or NB)                                                                                      | -1.5    | _    | 1.5             | μA   |

| Output Impedance – HIGH or LOW<br>State            | Resistance to V <sub>CC</sub> or GND                                                                            | -       | 50   | -               | Ω    |

| VDD REGULATOR 2/3/4 PHASE DET                      | FECTION                                                                                                         |         |      |                 |      |

| Gate Pin Source Current                            |                                                                                                                 | -       | 80   | -               | μA   |

| Gate Pin Threshold Voltage                         |                                                                                                                 | _       | 250  | -               | mV   |

| Phase Detect Timer                                 |                                                                                                                 | _       | 20   | _               | μs   |

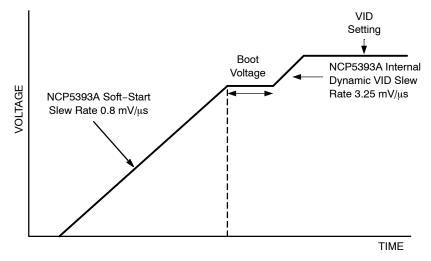

| SLEW RATE LIMITERS                                 |                                                                                                                 |         |      |                 |      |

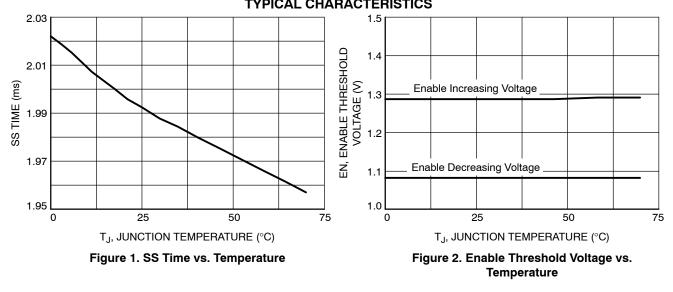

| Soft-Start Slew Rate                               | In Any Mode During Soft-Start                                                                                   | 0.64    | 0.8  | 0.96            | mV/μ |

| Slew Rate Limit                                    | In Any Mode after Soft–Start Completes                                                                          | _       | 3.25 | _               | mV/μ |

| VID INPUTS (Note: In SVI Mode, VID)                | 2] = Bidirectional "SVD' Line and VID[3] = "SVC" Clock Inp                                                      | ut)     |      |                 | .,   |

| VID Input Voltage (High)                           | VHIGH                                                                                                           | 0.9     | _    | -               | V    |

| VID Input Voltage (Low)                            | V <sub>LOW</sub>                                                                                                | _       | _    | 0.6             | V    |

| VID Hysteresis                                     | V <sub>HIGH</sub> – V <sub>LOW</sub> or V <sub>LOW</sub> – V <sub>HIGH</sub>                                    | _       | 100  | _               | mV   |

| Input Pulldown Current                             | V <sub>IN</sub> = 0.6 V – 1.9 V                                                                                 | _       | 15   | _               | μA   |

| SVD Output Voltage (Low)                           | In SVI Mode, I <sub>SINK</sub> = 5 mA                                                                           | 0       | _    | 0.25            | V    |

| ENABLE INPUT                                       |                                                                                                                 |         |      |                 |      |

| ENABLE Input Voltage (High)                        | V <sub>HIGH</sub>                                                                                               | 2.0     | _    | _               | V    |

| ENABLE Input Voltage (Low)                         | V <sub>LOW</sub>                                                                                                | _       | _    | 0.8             | V    |

| Enable Hysteresis                                  | Low – High or High – Low                                                                                        | _       | 200  | -               | mV   |

| Enable Input Pull-Up Current                       | Internal Pullup to V <sub>CC</sub>                                                                              | _       | 15   | -               | μA   |

| VFIXEN INPUT (Active-Low Input)                    |                                                                                                                 |         |      |                 |      |

| VFIXEN Input Voltage (High)                        | VHIGH                                                                                                           | 0.9     | _    | -               | V    |

| VFIXEN Input Voltage (Low)                         | VLOW                                                                                                            | _       | _    | 0.6             | V    |

| VFIXEN Hysteresis                                  | Low – High or High – Low                                                                                        |         | 100  |                 | mV   |

| VFIXEN Input Pull-Up Current                       | Internal Pullup to V <sub>CC</sub>                                                                              | _       | 15   | _               | μA   |

| • •                                                | nd Control, Active Low) (This pin is used in PVI mode on                                                        | <br> v) |      |                 |      |

| PSI_L Phase Shed Count                             | Before Enable Assertion, No Phase Shedding while<br>PSI_L Active. All Phases Operate in Diode Emulation<br>Mode | -       | -    | 0.6             | V    |

| PSI_L Phase Shed Count                             | Before ENABLE Assertion, Phase Shed to 2 Phases                                                                 | 0.9     | -    | 1.1             | V    |

| PSI_L Phase Shed Count                             | Before ENABLE Assertion, Phase Shed to 1 Phase                                                                  | 1.3     | -    | -               | V    |

| PSI_L Input Voltage (High)                         | After Soft-Start, V <sub>HIGH</sub>                                                                             | 0.9     | -    | -               | V    |

| PSI_L Input Voltage (Low)                          | After Soft-Start, V <sub>LOW</sub>                                                                              | _       | _    | 0.6             | V    |

3. Guaranteed by design. Not production tested.

| 2 $1$ $1$ $1$ $1$ $1$ $1$ $1$ $1$ $1$ $1$ | L CHARACTERISTICS (Unless otherwise stated: $0^{\circ}C \le T_A \le 70^{\circ}C$ ; 4.75 V $\le V_{CC} \le 5.25$ V; All DAC Codes; $C_{VCC} = 0.1 \mu$ F) |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                            | Test Conditions                                                                                                                                                                                    | Min                       | Тур                       | Max                       | Unit |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------|---------------------------|------|

| PSI_L (Power Saving Phase Shed a                     | and Control, Active Low) (This pin is used in PVI mode on                                                                                                                                          | ly)                       |                           |                           |      |

| PSI_L Hysteresis                                     | After Soft-Start, V <sub>HIGH</sub> - V <sub>LOW</sub> or V <sub>LOW</sub> - V <sub>HIGH</sub>                                                                                                     |                           | 100                       |                           | mV   |

| CURRENT LIMIT                                        | ·                                                                                                                                                                                                  |                           |                           |                           |      |

| Current Sense Amp to ILIM Gain                       | 20 mV < (CSx – CSxN) < 60 mV (CS inputs tied)                                                                                                                                                      | 5.7                       | 6.0                       | 6.3                       | V/V  |

| ILIM Pin Input Bias Current                          |                                                                                                                                                                                                    | -                         | -                         | 0.5                       | μA   |

| ILIM Pin Working Voltage Range<br>(Note 3)           |                                                                                                                                                                                                    | 0.2                       | _                         | 2.0                       | V    |

| ILIM Offset Voltage                                  | Offset extrapolated to CSx-CSxN = 0 V, and referred to the ILIM pin                                                                                                                                | -                         | 30                        | _                         | mV   |

| Delay                                                |                                                                                                                                                                                                    | -                         | 600                       | -                         | ns   |

| VDDNB Current Limit Coefficient                      | = N x V <sub>NBILIM</sub> /V <sub>ILIM</sub> , where N = number of VDD phases, and V <sub>NBILIM</sub> is the equivalent voltage threshold for NB Current Limit resulting from V <sub>ILIM</sub> . |                           | 1.0                       |                           | V    |

| OFFSET INPUTS (V <sub>DD</sub> & V <sub>DDNB</sub> ) | -                                                                                                                                                                                                  |                           |                           | •                         |      |

| Output Offset Voltage Above VDAC                     |                                                                                                                                                                                                    | 0                         | _                         | 800                       | mV   |

| OUTPUT OVERVOLTAGE PROTEC                            | TION (V <sub>DD</sub> & V <sub>DDNB</sub> )                                                                                                                                                        |                           |                           |                           |      |

| Over Voltage Threshold                               | In normal operation, with no VID changes                                                                                                                                                           | V <sub>DAC</sub><br>+ 220 | V <sub>DAC</sub><br>+ 235 | V <sub>DAC</sub><br>+ 250 | mV   |

| VCCA UNDERVOLTAGE PROTECT                            | ION                                                                                                                                                                                                | •                         | •                         | •                         |      |

| VCCA UVLO Start Threshold                            |                                                                                                                                                                                                    | 4.0                       | 4.25                      | 4.5                       | V    |

| VCCA UVLO Stop Threshold                             |                                                                                                                                                                                                    | 3.8                       | 4.05                      | 4.3                       | V    |

| VCCA UVLO Hysteresis                                 |                                                                                                                                                                                                    |                           | 200                       |                           | mV   |

| INPUT SUPPLY CURRENT                                 | ·                                                                                                                                                                                                  |                           |                           |                           |      |

| VCC Operating Current                                | ENABLE held Low, No PWM operation                                                                                                                                                                  | -                         | 25                        | 35                        | mA   |

| 12VMON                                               | ·                                                                                                                                                                                                  |                           |                           |                           |      |

| 12VMON (High Threshold)                              |                                                                                                                                                                                                    | 8                         | 8.5                       | 9                         | V    |

| 12VMON (Low Threshold)                               |                                                                                                                                                                                                    | 7                         | 7.5                       | 8                         | V    |

| 12VMON Hysteresis                                    | Low – High or High – Low                                                                                                                                                                           | 1                         | 1.0                       |                           | V    |

#### www.DatEunctional Description

#### General

NCP5393A is a universal CPU hybrid power Controller compatible with both Parallel VID interface (PVI) and Serial VID interface (SVI) protocols for AMD Processors. The Controller implements a single-phase control architecture to provide the Northbridge (NB) voltage on the same chip. For the CORE section, programmable 2– to–4 phase featuring Dual–Edge multiphase architecture is implemented. It embeds two independent controllers for CPU CORE and the integrated NB, each one with its set of protections.

The NCP5393A incorporates differential voltage sensing, differential phase current sensing, optional load-line voltage positioning, and programmable VDD and VDDNB offsets to provide accurately regulated power parallel- and serial-VID AMD processors. Dual-edge multiphase modulation provides the fastest initial response to dynamic load events.

NCP5393A also supports V\_FIX mode for board debug and testing. In this particular configuration the SVI bus is used as a static bus configuring four operative voltages (through SVC and SVD) for both the sections and ignoring any serial–VID command.

NCP5393A is able to detect which kind of CPU is connected and configures itself to work as a Single–Plane PVI controller or Dual–Plane SVI controller.

#### **Remote Output Sensing Amplifier (RSA)**

A true differential amplifier allows the NCP5393A to measure V<sub>core</sub> voltage feedback with respect to the V<sub>core</sub> ground reference point by connecting the V<sub>core</sub> reference point to VSP, and the V<sub>core</sub> ground reference point to VSN. This configuration keeps ground potential differences between the local controller ground and the V<sub>core</sub> ground reference point from affecting regulation of V<sub>core</sub> between V<sub>core</sub> and V<sub>core</sub> ground reference points. The RSA also subtracts the DAC (minus VID offset) voltage, thereby producing an unamplified output error voltage at the DIFFOUT pin. This output also has a 1.3 V bias voltage as the floating ground to allow both positive and negative error voltages.

#### Precision Programmable DAC

A precision programmable DAC is provided and system trimmed. This DAC has 0.5% accuracy over the entire operating temperature range of the part. The NCP5393A is a Hybrid controller which supports both a six bit parallel VID interface (PVI) and a seven bit serial VID interface (SVI). The NCP5393A allows manufacturers to build a motherboard that will accommodate either parallel or serial VID processors in the same socket.

#### High Performance Voltage Error Amplifier

The error amplifier is designed to provide high slew rate and bandwidth. Although not required when operating as the controller of a voltage regulator, a capacitor from COMP to VFB is required for stable unity gain test configurations.

#### Gate Driver Outputs and 2/3/4 Phase Operation

The part can be configured to run in 2–, 3–, or 4–phase mode. In 2–phase mode, phases 1 and 3 should be used to drive the external gate drivers, G2 and G4 must be grounded. In 3–phase mode, gate output G4 must be grounded. In 4–phase mode all 4 gate outputs are used as shown in the 4–phase Applications Schematic. The Current Sense inputs of unused channels should be connected to GND or to  $V_{DD}$ . Please refer to table "PIN CONNECTIONS vs. PHASE COUNTS" for details.

# Differential Current Sense Amplifiers and Summing Amplifier

Four differential amplifiers are provided to sense the output current of each phase. The inputs of each current sense amplifier must be connected across the current sensing element of the phase controlled by the corresponding gate output (G1, G2, G3, or G4). If a phase is unused, the differential inputs to that phase's current sense amplifier must be shorted together and connected to the GND or to  $V_{DD}$ .

The current signals sensed from inductor DCR are fed into a summing amplifier to have a summed-up output. The outputs of current sense amplifiers control three functions. First, the summing current signal of all phases will go through DROOP amplifier and join the voltage feedback loop for output voltage positioning. Second, the output signal from DROOP amplifier also goes to ILIM amplifier to monitor the output current limit. Finally, the individual phase current contributes to the current balance of all phases by offsetting their ramp signals of PWM comparators.

#### **Oscillator and Triangle Wave Generator**

The controller embeds a programmable precision dual-Oscillator: one section is used for the CORE and it is a multiphase programmable oscillator managing equal phase-shift among all phases and the other section is used for the NB section. The oscillator's frequency is programmed by the resistance connected from the ROSC pin to ground. The user will usually form this resistance from two resistors in order to create a voltage divider that uses the ROSC output voltage as the reference for creating the current limit setpoint voltage. The oscillator frequency range is 100 kHz per phase to 1.0 MHz per phase. The oscillator generates up to 4 symmetrical triangle waveforms with amplitude between 1.3 V and 2.3 V. The triangle waves have a phase delay between them such that for 2-, 3- and 4-phase operation the PWM outputs are separated by 180, 120, and 90 angular degrees, respectively.

When the NB phase is enabled, in order to ensure that the VDDNB oscillator does not accidentally lock to the VDD oscillator, the VDDNB oscillator will free-run at a frequency which is nominally 1.25 ratio of  $f_{VDD}$ .

## www.DatCPU\_Support

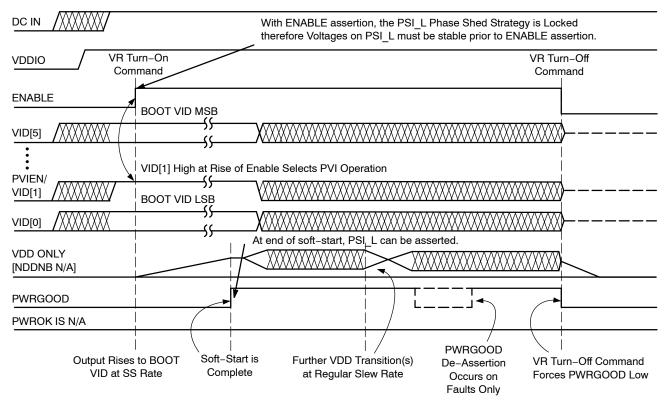

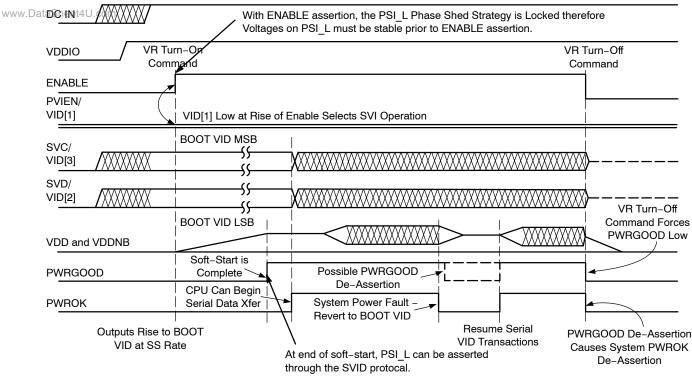

NCP5393A is able to detect the CPU it is going to supply and configure itself to PVI or SVI mode. When in PVI mode, to address the CORE section the NCP5393A uses VID[5:0]. When in SVI mode NCP5393A uses VID2 and VID3 alone for SVC and SVD information respectively. Whether the controller is controlled by the serial or parallel interface is determined by sampling the VID1 line at the time that the voltage regulator enable line is asserted; if the VID1 line is high when Enable is asserted, the voltage regulator starts in PVI mode, otherwise the voltage regulator starts in SVI mode.

#### **PVI – Parallel Interface**

PVI is a 6-bit wide parallel interface to address the CORE Section reference. NB is kept in HiZ mode. Parallel mode operation is depicted in Figure 9. Voltage identifications for the 6bit AMD mode is given in Table 2.

The normal PVI startup sequence for the NCP5393A is as follows:

- 5 V is applied to the VCCA and VCCB pins to power the NCP5393A and 12 V is applied to 12VMON.

- The NCP5393A samples the load on the G4 and G2 pins. If these pins are tied to ground the operating mode will be altered from four phase mode, to three phase, or two phase operation.

- The system power sequence logic asserts the NCP5393A ENABLE pin:

- The NCP5393A will sample the VID1 line to determine whether to start in SVI or PVI mode.

PVID mode is determined when VID1 = High.

- The NCP5393A samples the voltage on the PSI\_L pin in order to determine the desired operating configuration during power saving mode.

- The Boot VID is captured from decoding the voltages on the VID[0:5].

- The NCP5393A V<sub>DD</sub> regulator will soft-start and ramp to the initial Boot VID. The VDDNB regulator remains off (high-Z output).

- PWRGOOD is asserted by the NCP5393A.

- PWROK is not used in PVID mode.

- The NCP5393A will accept new VID codes on the parallel VID interface (See Table 2). See Figure 9 for details.

#### Table 1. Metal VID/BOOT VID

|     |     | Output Voltage      |

|-----|-----|---------------------|

| SVC | SVD | Pre-PWROK Metal VID |

| 0   | 0   | 1.1 V               |

| 0   | 1   | 1.0 V               |

| 1   | 0   | 0.9 V               |

| 1   | 1   | 0.8 V               |

Figure 9. Power Up Sequences in Parallel Mode Operation

| SVID[5:0] | V <sub>OUT</sub> (V) |

|-----------|----------------------|-----------|----------------------|-----------|----------------------|-----------|----------------------|

| 00_0000   | 1.5500               | 01_0000   | 1.1500               | 10_0000   | 0.7625               | 11_0000   | 0.5625               |

| 00_0001   | 1.5250               | 01_0001   | 1.1250               | 10_0001   | 0.7500               | 11_0001   | 0.5500               |

| 00_0010   | 1.5000               | 01_0010   | 1.1000               | 10_0010   | 0.7375               | 11_0010   | 0.5375               |

| 00_0011   | 1.4750               | 01_0011   | 1.0750               | 10_0011   | 0.7250               | 11_0011   | 0.5250               |

| 00_0100   | 1.4500               | 01_0100   | 1.0500               | 10_0100   | 0.7125               | 11_0100   | 0.5125               |

| 00_0101   | 1.4250               | 01_0101   | 1.0250               | 10_0101   | 0.7000               | 11_0101   | 0.5000               |

| 00_0110   | 1.4000               | 01_0110   | 1.0000               | 10_0110   | 0.6875               | 11_0110   | 0.4875               |

| 00_0111   | 1.3750               | 01_0111   | 0.9750               | 10_0111   | 0.6750               | 11_0111   | 0.4750               |

| 00_1000   | 1.3500               | 01_1000   | 0.9500               | 10_1000   | 0.6625               | 11_1000   | 0.4625               |

| 00_1001   | 1.3250               | 01_1001   | 0.9250               | 10_1001   | 0.6500               | 11_1001   | 0.4500               |

| 00_1010   | 1.3000               | 01_1010   | 0.9000               | 10_1010   | 0.6325               | 11_1010   | 0.4375               |

| 00_1011   | 1.2750               | 01_1011   | 0.8750               | 10_1011   | 0.6250               | 11_1011   | 0.4250               |

| 00_1100   | 1.2500               | 01_1100   | 0.8500               | 10_1100   | 0.6125               | 11_1100   | 0.4125               |

| 00_1101   | 1.2250               | 10_1101   | 0.8250               | 10_1101   | 0.6000               | 11_1101   | 0.4000               |

| 00_1110   | 1.2000               | 01_1110   | 0.8000               | 10_1110   | 0.5875               | 11_1110   | 0.3875               |

| 00_1111   | 1.1750               | 01_1111   | 0.7750               | 10_1111   | 0.5750               | 11_1111   | 0.3750               |

#### www.Data Table 2. SIX-BIT PARALLEL VID CODES in PVI Modes

#### SVI – Serial Interface

SVI is a two wire, Clock and Data, bus that connects a single master (CPU) to one NCP5393A. The master initiates and terminates SVI transactions and drives the clock, SVC, and the data SVD, during a transaction. The slave receives the SVI transactions and acts accordingly. SVI wire protocol is based on fast-mode I2C.

PWROK is properitery of the SVI protocol and is considered at start-up. The SVI mode operation is explained in Figure 10. The VID codes from the decoded SVI value are given in Table 3.

The normal SVI startup sequence for the NCP5393A is as follows:

- 5 V is applied to the VCCA and VCCB pins to power the NCP5393A and 12 V is applied to 12VMON.

- The NCP5393A samples the load on the G4 and G2 pins. If these pins are tied to ground the operating mode will be altered from four phase mode, to three phase, or two phase operation.

- The system power sequence logic asserts the NCP5393A ENABLE pin:

- The NCP5393A will sample the VID1 line to determine whether to start in SVI or PVI mode. SVID mode is determined when VID1 = Low.

- The NCP5393A samples the voltage on the PSI\_L pin in order to determine the desired operating configuration during power saving mode.

- The Boot VID is captured from decoding the voltages on the VID3/SVC and VID2/SVD pins per Table 1 and stored.

- The NCP5393A will start the VDD and VDDNB regulators. Both regulators will soft start and ramp to the Boot VID Voltage (See Table 1).

- The NCP5393A asserts PWRGOOD.

- The system asserts PWROK The system processor will hold the boot VID voltage for at least 10us after PWROK signal is asserted

- Now the NCP5393A can accept new SVID codes on the serial VID interface (See Table 3).

- If the system should de-assert PWROK, then the NCP5393A will reset the Core and Northbridge VIDs and regulate at the Boot VID voltage.

## www.DataTable 3. SEVEN-BIT SERIAL VID CODES for SVI Mode

| SVID[6:0] | V <sub>OUT</sub> (V) |

|-----------|----------------------|-----------|----------------------|-----------|----------------------|-----------|----------------------|

| 000_0000  | 1.5500               | 010_0000  | 1.1500               | 100_0000  | 0.7500               | 110_0000  | 0.3500               |

| 000_0001  | 1.5375               | 010_0001  | 1.1375               | 100_0001  | 0.7375               | 110_0001  | 0.3375               |

| 000_0010  | 1.5250               | 010_0010  | 1.1250               | 100_0010  | 0.7250               | 110_0010  | 0.3250               |

| 000_0011  | 1.5125               | 010_0011  | 1.1125               | 100_0011  | 0.7125               | 110_0011  | 0.3125               |

| 000_0100  | 1.5000               | 010_0100  | 1.1000               | 100_0100  | 0.7000               | 110_0100  | 0.3000               |

| 000_0101  | 1.4875               | 010_0101  | 1.0875               | 100_0101  | 0.6875               | 110_0101  | 0.2875               |

| 000_0110  | 1.4750               | 010_0110  | 1.0750               | 100_0110  | 0.6750               | 110_0110  | 0.2750               |

| 000_0111  | 1.4625               | 010_0111  | 1.0625               | 100_0111  | 0.6625               | 110_0111  | 0.2625               |

| 000_1000  | 1.4500               | 010_1000  | 1.0500               | 100_1000  | 0.6500               | 110_1000  | 0.2500               |

| 000_1001  | 1.4375               | 010_1001  | 1.0375               | 100_1001  | 0.6325               | 110_1001  | 0.2375               |

| 000_1010  | 1.4250               | 010_1010  | 1.0250               | 100_1010  | 0.6250               | 110_1010  | 0.2250               |

| 000_1011  | 1.4125               | 010_1011  | 1.0125               | 100_1011  | 0.6125               | 110_1011  | 0.2125               |

| 000_1100  | 1.4000               | 010_1100  | 1.0000               | 100_1100  | 0.6000               | 110_1100  | 0.2000               |

| 000_1101  | 1.3875               | 010_1101  | 0.9875               | 100_1101  | 0.5875               | 110_1101  | 0.1875               |

| 000_1110  | 1.3750               | 010_1110  | 0.9750               | 100_1110  | 0.5750               | 110_1110  | 0.1750               |

| 000_1111  | 1.3625               | 010_1111  | 0.9625               | 100_1111  | 0.5625               | 110_1111  | 0.1625               |

| 001_0000  | 1.3500               | 011_0000  | 0.9500               | 101_0000  | 0.5500               | 111_0000  | 0.1500               |

| 001_0001  | 1.3375               | 011_0001  | 0.9375               | 101_0001  | 0.5375               | 111_0001  | 0.1375               |

| 001_0010  | 1.3250               | 011_0010  | 0.9250               | 101_0010  | 0.5250               | 111_0010  | 0.1250               |

| 001_0011  | 1.3125               | 011_0011  | 0.9125               | 101_0011  | 0.5125               | 111_0011  | 0.1125               |

| 001_0100  | 1.3000               | 011_0100  | 0.9000               | 101_0100  | 0.5000               | 111_0100  | 0.1000               |

| 001_0101  | 1.2875               | 011_0101  | 0.8875               | 101_0101  | 0.4875               | 111_0101  | 0.0875               |

| 001_0110  | 1.2750               | 011_0110  | 0.8750               | 101_0110  | 0.4750               | 111_0110  | 0.0750               |

| 001_0111  | 1.2625               | 011_0111  | 0.8625               | 101_0111  | 0.4625               | 111_0111  | 0.0625               |

| 001_1000  | 1.2500               | 011_1000  | 0.8500               | 101_1000  | 0.4500               | 111_1000  | 0.0500               |

| 001_1001  | 1.2375               | 011_1001  | 0.8375               | 101_1001  | 0.4375               | 111_1001  | 0.0375               |

| 001_1010  | 1.2250               | 011_1010  | 0.8250               | 101_1010  | 0.4250               | 111_1010  | 0.0250               |

| 001_1011  | 1.2125               | 011_1011  | 0.8125               | 101_1011  | 0.4125               | 111_1011  | 0.0125               |

| 001_1100  | 1.2000               | 011_1100  | 0.8000               | 101_1100  | 0.4000               | 111_1100  | OFF                  |

| 001_1101  | 1.1875               | 011_1101  | 0.7875               | 110_1101  | 0.3875               | 111_1101  | OFF                  |

| 001_1110  | 1.1750               | 011_1110  | 0.7750               | 101_1110  | 0.3750               | 111_1110  | OFF                  |

| 001_1111  | 1.1625               | 011_1111  | 0.7625               | 101_1111  | 0.3625               | 111_1111  | OFF                  |

Figure 10. Power–Up Sequence in Serial Mode Operation

## Hardware Jumper Override – V\_FIX

VFIX is an active low pin and when it is pulled low, the controller enters V\_FIX mode. The voltage regulator can be powered when an external SVI bus master is not present. When in VFIX mode, all of the voltage regulator's output voltages will be governed by the information shown in Table 4, regardless of the state of PWROK. VFIX mode is for debug only. If VFIX mode is necessary for processor bring–up, VFIXEN, SVC, and SVD should be connected with jumpers to either ground or VDDIO through suitable pull–up resistors. SVC and SVD are considered as static VID and the output voltage will change according to their status.

| SVC | SVD | V <sub>OUT</sub> (V) |

|-----|-----|----------------------|

| 0   | 0   | 1.4                  |

| 0   | 1   | 1.2                  |

| 1   | 0   | 1.0                  |

| 1   | 1   | 0.8                  |

The normal VFIXEN startup sequence for the NCP5393A is as follows:

- 5 V is applied to the VCCA and VCCB pins to power the NCP5393A and 12 V is applied to 12VMON.

- The NCP5393A samples the load on the G4 and G2 pins. If these pins are tied to ground the operating mode will be altered from four phase mode, to three phase, or two phase operation.

- The system power sequence logic asserts the NCP5393A ENABLE pin:

- The NCP5393A will sample the VID1 line to determine whether to start in SVI or PVI mode.

- The NCP5393A samples the voltage on the PSI\_L pin in order to determine the desired operating configuration during power saving mode.

- The Boot VID is dependent on SVI or PVI mode startup.

- The NCP593A V<sub>DD</sub> regulator (and VDDNB if in SVID mode) will soft-start and ramp to the initial Boot VID.

- VFIXEN mode is entered once VFIXEN is asserted and the V<sub>DD</sub> and VDDNB regulators will regulate to the VFIXEN VID.

- VFIXEN VID is captured from decoding the voltages on the VID3/SVC and VID2/SVD pins per Table 4.

- If VFIXEN is asserted prior to the VID controller reaching the Boot VID, the VID controller will move to the VFIXEN VID.

- If VFIXEN is de-asserted, the evice PORs. This occurs independent of ENABLE.

#### **PWROK De-Assertion**

Anytime PWROK de-asserts while EN is asserted, the controller uses the previously stored *BOOT VID* and regulates all planes to that level performing an on-the-Fly transition to that level. PWRGOOD remains asserted in this process.