# Advance Information

# Primary Side Combination Resonant and PFC Controllers

The NCP1901 is a combination of PFC and half-bridge resonant controllers optimized for off-line adapter applications. This device includes all the features needed to implement a highly efficient and small form factor adapter. It integrates a critical conduction mode (CrM) power factor correction (PFC) controller and a half-bridge controller with a built-in 600 V driver. The half-bridge stage operates at a fixed frequency. Regulation is achieved by adjusting the PFC stage output voltage.

This device includes an enable input on the PFC feedback pin, open feedback loop protection and PFC overvoltage and undervoltage detectors. Other features included in the NCP1901 are a 600 V startup circuit and an adjustable frequency oscillator. The controllers are properly sequenced, simplifying system design.

#### **Features**

- Adjustable Half-Bridge Frequency up to 75 kHz

- Open Feedback Loop Protection

- CrM Power Factor Correction Controller

- PFC Undervoltage Detector

- PFC Overvoltage Detector

- Half-Bridge Controller with 600 V High Side Gate Drive

- State Machine Ensures Proper Turn-on and Turn-off of Half-Bridge Stage

- Enable Input on the PFC Feedback Pin Disables Controllers and Reduces Power

- Controllers are Properly Sequenced for Fault Free Operation

- Internal 600 V Startup Circuit

- This is a Pb-Free Device

## **Typical Applications**

- High Efficiency Notebook Adapter

- Solid State Lighting

This document contains information on a new product. Specifications and information herein are subject to change without notice.

## ON Semiconductor®

http://onsemi.com

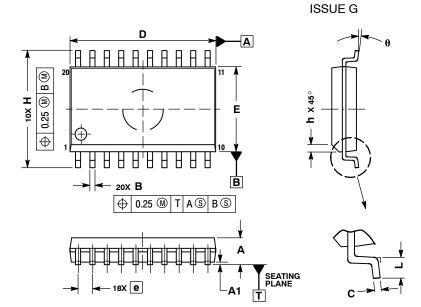

SO-20 WB DW SUFFIX CASE 751D

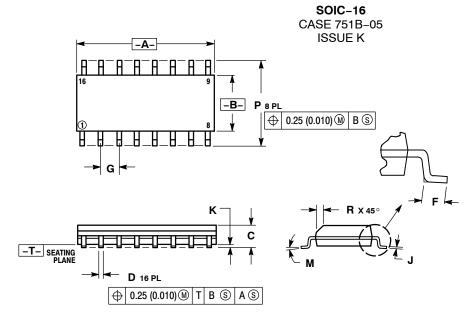

SOIC-16 D SUFFIX CASE 751B

## MARKING DIAGRAM

NCP1901 = Specific Device Code

= Assembly Location

WL = Wafer Lot Y or YY = Year WW = Work Week G = Pb-Free Package

## **ORDERING INFORMATION**

| Device       | Package               | Shipping <sup>†</sup> |

|--------------|-----------------------|-----------------------|

| NCP1901DR2G  | SOIC-16<br>(Pb-Free)  | 2500/Tape & Reel      |

| NCP1901DWR2G | SO-20 WB<br>(Pb-Free) | 1000/Tape & Reel      |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

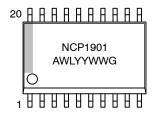

Figure 1. Pin Connections

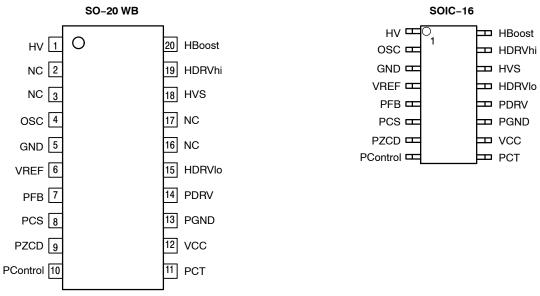

Figure 2. Functional Block Diagram

## **Table 1. PIN FUNCTION DESCRIPTION**

| 20 Pin | 16 Pin | Name     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | 1      | HV       | This is the input of the high voltage startup regulator and connects directly to the bulk voltage. A constant current source supplies current from this pin to the V <sub>CC</sub> capacitor, eliminating the need for an external startup resistor. The charge current is 7.5 mA (typical).                                                                                                                                                                                              |

| 4      | 2      | OSC      | A capacitor on this pin adjusts the frequency of the internal oscillator. The oscillator sets the frequency of the half-bridge controller. The half-bridge operates at half the oscillator frequency.                                                                                                                                                                                                                                                                                     |

| 5      | 3      | GND      | Analog ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6      | 4      | VREF     | Reference voltage. The capacitor on this pin decouples the internal reference. A 0.1 $\mu$ F capacitor needs to be connected between this pin and ground.                                                                                                                                                                                                                                                                                                                                 |

| 7      | 5      | PFB      | PFC voltage feedback input. The voltage on this pin is compared to a 2.5 V reference (typical) to regulate the PFC output voltage. The voltage on this pin is also used to detect PFC undervoltage and overvoltage conditions.                                                                                                                                                                                                                                                            |

| 8      | 6      | PCS      | PFC regulator current sense input. A voltage ramp proportional to the PFC switch current is applied to this pin. The current sense threshold, V <sub>PCS(ILIM)</sub> , is typically 0.84 V. A 110 ns (typical) leading edge blanking circuit filters the current sense signal at the start of each cycle.                                                                                                                                                                                 |

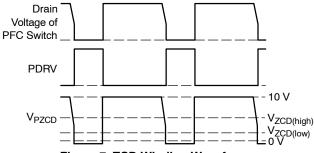

| 9      | 7      | PZCD     | PFC inductor zero current detector. The inductor current is monitored using an auxiliary winding on the PFC inductor. The PFC drive signal is enabled during a high to low transition on the PZCD pin. A series resistor limits the current into the PZCD pin.                                                                                                                                                                                                                            |

| 10     | 8      | PControl | PFC control voltage. This pin connects to the output of the PFC error amplifier. The error amplifier is a transconductance amplifier. A compensation network between this pin and grounds sets the PFC loop bandwidth. The PFC control voltage is compared to a level shifted version of V <sub>PCT</sub> to control the PFC duty ratio.                                                                                                                                                  |

| 11     | 9      | PCT      | PFC on time control capacitor. A 270 $\mu$ A (typical) current source charges a capacitor connected between this pin and ground. Once the level shifted PCT voltage reaches $V_{PControl}$ , the PFC drive signal is disabled and the PCT capacitor is discharged.                                                                                                                                                                                                                        |

| 12     | 10     | VCC      | Positive input supply. This pin connects to an external capacitor for energy storage. An internal current source supplies current from HV to this pin. Once the $V_{\rm CC}$ voltage reaches $V_{\rm CC(on)}$ (15.3 V typical), the current source turns off and the controller is enabled. The current source turns on once $V_{\rm CC}$ falls to $V_{\rm CC(off)}$ (9.3 V typical). During normal operation, power is supplied to the IC via this pin by means of an auxiliary winding. |

| 13     | 11     | PGND     | Ground connection for PDRV and HDRVIo. Tie to the power stage return with a short trace.                                                                                                                                                                                                                                                                                                                                                                                                  |

| 14     | 12     | PDRV     | PFC switch gate drive control signal. The source and sink drive capability is limited to 60 $\Omega$ and 15 $\Omega$ (typical), respectively. A discrete driver may be needed to drive the external MOSFET.                                                                                                                                                                                                                                                                               |

| 15     | 13     | HDRVIo   | Half-bridge low side switch gate drive control signal. The source and sink drive capability is limited to 75 $\Omega$ and 15 $\Omega$ (typical), respectively. A discrete driver may be needed to drive the half bridge switch.                                                                                                                                                                                                                                                           |

| 18     | 14     | HVS      | Half-bridge high side driver source connection. This pin connects directly to the bridge terminal and can float up to 600 V.                                                                                                                                                                                                                                                                                                                                                              |

| 19     | 15     | HDRVhi   | Half–bridge high side switch gate drive control signal. The source and sink drive capability is limited to 75 $\Omega$ and 15 $\Omega$ (typical), respectively. The supply terminals of the high side driver connect to the HBoost and HVS pins.                                                                                                                                                                                                                                          |

| 20     | 16     | HBoost   | Supply voltage of the high side gate driver. A charge pump generates a bootstrap voltage floating on top of the HVS voltage. A diode between the VCC and HBoost pins provides a charge path. The bootstrap voltage is V <sub>CC</sub> minus a diode drop.                                                                                                                                                                                                                                 |

Table 2. MAXIMUM RATINGS (Notes 1 and 2)

| Rating                                                                                                                                               | Symbol                      | Value                   | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------------|------|

| High Voltage Input Voltage                                                                                                                           | V <sub>HV</sub>             | -0.3 to 600             | V    |

| High Voltage Input Current                                                                                                                           | I <sub>HV</sub>             | 10                      | mA   |

| Supply Input Voltage                                                                                                                                 | V <sub>CC</sub>             | -0.3 to 20              | V    |

| Supply Input Current                                                                                                                                 | Icc                         | 10                      | mA   |

| Oscillator Input Voltage                                                                                                                             | Vosc                        | -0.3 to 10              | V    |

| Oscillator Input Current                                                                                                                             | losc                        | 10                      | mA   |

| Bandgap Reference Decoupling Output Voltage                                                                                                          | V <sub>REF</sub>            | -0.3 to 9               | V    |

| Bandgap Reference Decoupling Output Current                                                                                                          | I <sub>REF</sub>            | 10                      | mA   |

| PFC Feedback Voltage Input Voltage                                                                                                                   | $V_{PFB}$                   | -0.3 to 10              | V    |

| PFC Feedback Voltage Input Current                                                                                                                   | I <sub>PFB</sub>            | 10                      | mA   |

| PFC Current Sense Input Voltage                                                                                                                      | V <sub>PCS</sub>            | -0.3 to 10              | V    |

| PFC Current Sense Input Current                                                                                                                      | I <sub>PCS</sub>            | 10                      | mA   |

| PFC Zero Current Detection Input Voltage                                                                                                             | V <sub>PZCD</sub>           | -0.3 to 10              | V    |

| PFC Zero Current Detection Input Current                                                                                                             | I <sub>PZCD</sub>           | 10                      | mA   |

| PFC Control Input Voltage                                                                                                                            | V <sub>PControl</sub>       | -0.3 to 10              | V    |

| PFC Control Input Current                                                                                                                            | I <sub>PControl</sub>       | 1.2                     | mA   |

| PFC On Time Control Input Voltage                                                                                                                    | V <sub>PCT</sub>            | -0.3 to 10              | V    |

| PFC On Time Control Input Current                                                                                                                    | I <sub>PCT</sub>            | 9                       | mA   |

| PFC Drive Signal Voltage                                                                                                                             | V <sub>PDRV</sub>           | -0.3 to V <sub>CC</sub> | V    |

| PFC Drive Signal Current                                                                                                                             | I <sub>PDRV</sub>           | 100                     | mA   |

| Half-Bridge Low Side Driver Input Voltage                                                                                                            | $V_{HDRVlo}$                | –0.3 to $V_{CC}$        | V    |

| Half-Bridge Low Side Driver Input Current                                                                                                            | I <sub>HDRVIo</sub>         | 100                     | mA   |

| Half-Bridge High Side Driver Source Connection Input Voltage                                                                                         | V <sub>HVS</sub>            | -1.0 to 600             | V    |

| Half-Bridge High Side Driver Source Connection Input Current                                                                                         | I <sub>HVS</sub>            | 100                     | mA   |

| Half-Bridge High Side Driver Input Voltage                                                                                                           | $V_{HDRVhi}$                | -1.3 to 600             | V    |

| Half-Bridge High Side Driver Input Current                                                                                                           | I <sub>HDRVhi</sub>         | 100                     | mA   |

| Half-Bridge High Side Driver Charge Pump Input Voltage                                                                                               | V <sub>HBoost</sub>         | -0.3 to 600             | V    |

| Half-Bridge High Side Driver Charge Pump Input Current                                                                                               | I <sub>HBoost</sub>         | 100                     | mA   |

| High Side Boost Circuit Supply Voltage (between HBoost and HVS pins)                                                                                 | V <sub>HBoost(supply)</sub> | –0.3 to $V_{CC}$        | V    |

| High Side Boost Circuit Supply Voltage (between HBoost and HVS pins)                                                                                 | I <sub>HBoost(supply)</sub> | 100                     | mA   |

| Half-Bridge High Side Driver Source Connection Slew Rate                                                                                             | dV <sub>HVS</sub> /dt       | TBD                     | V/ns |

| Operating Junction Temperature                                                                                                                       | T <sub>J</sub>              | -40 to 150              | °C   |

| Storage Temperature Range                                                                                                                            | T <sub>stg</sub>            | -60 to 150              | °C   |

| Power Dissipation (T <sub>A</sub> = 25°C, 1 Oz Cu, 0.155 Sq Inch, Printed Circuit Copper Clad) D Suffix, Plastic Package Case 751B–05 (SOIC–16)      | P <sub>D</sub>              | 0.95                    | W    |

| Thermal Resistance, Junction to Ambient<br>(1 Oz Cu, 0.155 Sq Inch, Printed Circuit Copper Clad)<br>D Suffix, Plastic Package Case 751B-05 (SOIC-16) | R <sub>θJA</sub>            | 130                     | °C/W |

| D Suffix, Plastic Package Case 751B-05 (SOIC-16)                                                                                                     |                             |                         | L    |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

device reliability.

This device(s) contains ESD protection and exceeds the following tests:

Pins 1, 14, 15 and 16 rated to the maximum voltage of the part, or 600 V.

All Other Pins: Human Body Model 1500 V per JEDEC Standard JESD22–A114E.

Machine Model 150 V per JEDEC Standard JESD22–A115–A.

<sup>2.</sup> This device contains Latch–Up protection and exceeds  $\pm$  100 mA per JEDEC Standard JESD78.

| Characteristics                                                                     | Conditions                                                                                                   | Symbol                                                           | Min                 | Тур                 | Max                  | Unit |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|---------------------|---------------------|----------------------|------|

| STARTUP AND SUPPLY CIRCUITS                                                         |                                                                                                              |                                                                  | -1                  |                     |                      | ·    |

| Supply Voltage Startup Threshold Minimum Enable Threshold Minimum Operating Voltage | V <sub>CC</sub> Increasing<br>V <sub>CC</sub> Decreasing<br>V <sub>CC</sub> Decreasing                       | V <sub>CC(on)</sub> V <sub>CC(enable)</sub> V <sub>CC(off)</sub> | 14.3<br>13.6<br>8.5 | 15.3<br>14.6<br>9.3 | 16.3<br>15.6<br>10.0 | V    |

| Supply Current Device Disabled/Fault Device Switching                               | V <sub>PFB</sub> = V <sub>PUVP(low)</sub><br>(Note 4)                                                        | Icc <sub>1</sub><br>Icc <sub>2</sub>                             | 1.0<br>1.5          | 1.4<br>2.4          | 2.0<br>3.0           | mA   |

| Startup Current                                                                     | $V_{CC} = V_{CC (on)} - 0.2 V,$<br>$V_{HV} = 50 V$                                                           | I <sub>start</sub>                                               | 3.0                 | 7.5                 | 10.5                 | mA   |

| Startup Circuit Off-State Leakage Current                                           | V <sub>HV</sub> = 600 V,<br>V <sub>CC</sub> = V <sub>CC (on)</sub> + 0.2 V                                   | I <sub>HV(off)</sub>                                             | -                   | 15                  | 50                   | μΑ   |

| BANDGAP REFERENCE                                                                   |                                                                                                              | •                                                                |                     |                     | •                    | •    |

| Reference Voltage                                                                   | C <sub>REF</sub> = 0.1 μF                                                                                    | V <sub>REF</sub>                                                 | 6.605               | 7.000               | 7.295                | V    |

| OSCILLATOR                                                                          |                                                                                                              |                                                                  |                     |                     |                      |      |

| Half-Bridge Clock Frequency                                                         | V <sub>HVS</sub> = 50 V                                                                                      | f <sub>clock</sub>                                               | 13.5                | 15.5                | 16.5                 | kHz  |

| Maximum Half-Bridge Clock Frequency                                                 | C <sub>OSC</sub> = open                                                                                      | f <sub>clock(MAX)</sub>                                          | 75                  | -                   | -                    | kHz  |

| PFC ERROR AMPLIFIER                                                                 |                                                                                                              |                                                                  |                     |                     |                      |      |

| PFC Feedback Voltage Reference                                                      | 0°C < T <sub>J</sub> < 125°C<br>−40°C < T <sub>J</sub> < 125°C                                               | V <sub>PREF</sub>                                                | 2.42<br>2.40        | 2.50                | 2.58<br>2.60         | V    |

| PFC Feedback Voltage Reference<br>Regulation with Line                              | V <sub>CC(on)</sub> + 0.2 V < V <sub>CC</sub> < 20 V                                                         | V <sub>PREF(line)</sub>                                          | -15                 | =                   | 15                   | mV   |

| Error Amplifier Drive Capability Sink Source                                        | V <sub>PControl</sub> = 4 V, V <sub>PFB</sub> = 5 V<br>V <sub>PControl</sub> = 4 V, V <sub>PFB</sub> = 0.5 V | I <sub>EA(SNK)</sub><br>I <sub>EA(SRC)</sub>                     | 60<br>-60           | 80<br>-80           | -<br>-               | μΑ   |

| Open Loop Error Amplifier<br>Transconductance                                       | V <sub>PControl</sub> = 4 V,<br>V <sub>PFB</sub> = 2.4 V and 2.6 V                                           | Gm                                                               | 60                  | 95                  | _                    | μS   |

| Feedback Input Pulldown Current Source                                              | V <sub>PFB</sub> = 3 V                                                                                       | I <sub>PFB</sub>                                                 | 0.5                 | 1.2                 | 1.5                  | μΑ   |

| Error Amplifier Maximum Output Voltage                                              | I <sub>PControl</sub> = 10 μA                                                                                | V <sub>EA(OH)</sub>                                              | 5.30                | 5.65                | 6.00                 | V    |

| Error Amplifier Minimum Output Voltage                                              | I <sub>PControl</sub> = -10 μA                                                                               | V <sub>EA(OL)</sub>                                              | 2.10                | 2.25                | 2.40                 | V    |

| Error Amplifier Output Voltage Range                                                | V <sub>EA(OH)</sub> – V <sub>EA(OL)</sub>                                                                    | $\Delta V_{EA}$                                                  | 3.1                 | 3.4                 | 3.7                  | V    |

<sup>3.</sup> Resistor/capacitor parallel combination (39 pF  $\parallel$  20 k $\Omega$ ) between drive pin and driver supply and between xDRVxx and GND pins.

| Characteristics                                                                                     | Conditions                                                                | Symbol                                               | Min                        | Тур                        | Max                        | Unit |

|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------|----------------------------|----------------------------|----------------------------|------|

| PFC CURRENT SENSE                                                                                   |                                                                           |                                                      |                            | •                          |                            |      |

| Current Sense Threshold Voltage                                                                     |                                                                           | V <sub>PCS(ILIM)</sub>                               | 0.78                       | 0.84                       | 0.92                       | V    |

| Current Sense Input Bias Current                                                                    | V <sub>PCS</sub> = 2 V                                                    | I <sub>PCS</sub>                                     | -1                         | 0                          | 1                          | μА   |

| Leading Edge Blanking Duration                                                                      |                                                                           | t <sub>PCS(LEB)</sub>                                | 40                         | 110                        | 200                        | ns   |

| Propagation Delay                                                                                   | V <sub>PCS</sub> = V <sub>PCS(ILIM)</sub> + 1 V                           | t <sub>PCS(delay)</sub>                              | _                          | 90                         | 250                        | ns   |

| PFC ZERO CURRENT DETECTION                                                                          |                                                                           |                                                      | 1                          |                            | 1                          |      |

| ZCD Threshold Voltage                                                                               | V <sub>PZCD</sub> increasing<br>V <sub>PZCD</sub> decreasing              | V <sub>ZCD(high)</sub>                               | 1.9<br>1.3                 | 2.1<br>1.5                 | 2.3<br>1.7                 | V    |

| ZCD Voltage Hysteresis                                                                              |                                                                           | V <sub>ZCD(HYS)</sub>                                | 400                        | 600                        | 800                        | mV   |

| ZCD Input Bias Current                                                                              | V <sub>PZCD</sub> = 1 V<br>V <sub>PZCD</sub> = 5 V                        | I <sub>PZCD(bias1)</sub><br>I <sub>PZCD(bias2)</sub> | -1<br>-1                   | -<br>-                     | 1<br>1                     | μΑ   |

| PFC MAXIMUM OFF TIME                                                                                |                                                                           |                                                      |                            |                            |                            |      |

| Maximum Off Time                                                                                    |                                                                           | t <sub>PFC(off)</sub>                                | 50                         | 180                        | 350                        | μs   |

| PFC ON TIME RAMP GENERATOR                                                                          |                                                                           |                                                      |                            |                            |                            |      |

| ON time Capacitor Charge Current                                                                    | V <sub>PCT</sub> = 0 V                                                    | I <sub>PCT(C)</sub>                                  | 220                        | 270                        | 300                        | μΑ   |

| On Time Capacitor Discharge Time                                                                    | C <sub>PCT</sub> = 1 nF,<br>V <sub>PCT</sub> = 2.4 V to 0.6 V             | t <sub>PCT(D)</sub>                                  | -                          | 70                         | 300                        | ns   |

| ON Time Capacitor Peak Voltage                                                                      |                                                                           | V <sub>PCT(peak)</sub>                               | 2.6                        | 3.0                        | 3.4                        | V    |

| Minimum Duty Ratio                                                                                  | V <sub>PFB</sub> = 3.0 V, V <sub>PZCD</sub> = 0 V                         | D <sub>PMIN</sub>                                    | 0                          | _                          | _                          | %    |

| Maximum On Time Detect Delay                                                                        | V <sub>PCT</sub> = V <sub>PCT(peak)</sub> + 1 V                           | t <sub>PCT(delay)</sub>                              | _                          | 250                        | 375                        | ns   |

| Voltage Delta between PControl Voltage<br>Needed to Generate PDRV Pulses and<br>V <sub>EA(OL)</sub> | ΔV <sub>EA</sub> - V <sub>PCT(peak)</sub>                                 | V <sub>PCT(offset)</sub>                             | 250                        | 400                        | 550                        | mV   |

| PFC OVERVOLTAGE and UNDERVOLTAGE                                                                    | <u> </u>                                                                  |                                                      |                            |                            |                            |      |

| Overvoltage Detector Threshold Voltage                                                              | Midpoint between high and low threshold, V <sub>PControl</sub> = 4 V      | V <sub>POVP</sub>                                    | 1.03*<br>V <sub>PREF</sub> | 1.05*<br>V <sub>PREF</sub> | 1.07*<br>V <sub>PREF</sub> | V    |

| Overvoltage Comparator Hysteresis                                                                   | Between increasing and decreasing thresholds, V <sub>PControl</sub> = 4 V | V <sub>POVP(HYS)</sub>                               | 5                          | 30                         | 60                         | mV   |

| Propagation Delay                                                                                   | V <sub>PFB</sub> = V <sub>PREF</sub> + 1 V                                | t <sub>POVP(delay)</sub>                             | _                          | 400                        | 800                        | ns   |

| Undervoltage Detector Threshold Voltage                                                             | V <sub>PFB</sub> increasing<br>V <sub>PFB</sub> decreasing                | V <sub>PUVP(high)</sub><br>V <sub>PUVP(low)</sub>    | -<br>175                   | 290<br>230                 | 350<br>-                   | mV   |

| Undervoltage Comparator Hysteresis                                                                  | V <sub>PFB</sub> increasing                                               | V <sub>PUVP(HYS)</sub>                               | 20                         | 60                         | 100                        | mV   |

| PFC DRIVER                                                                                          |                                                                           |                                                      |                            |                            |                            |      |

| PFC Driver Rise Time                                                                                | 10% to 90% (Note 4)                                                       | t <sub>PDRV(rise)</sub>                              | _                          | 18                         | _                          | ns   |

| PFC Driver Fall Time                                                                                | 90% to 10% (Note 4)                                                       | t <sub>PDRV(fall)</sub>                              | _                          | 9                          | -                          | ns   |

| PFC Driver High State Voltage                                                                       | I <sub>PDRV</sub> = -8 mA                                                 | V <sub>PDRV(OH)</sub>                                | 14.00                      | 14.55                      | -                          | V    |

| PFC Driver Low State Voltage                                                                        | I <sub>PDRV</sub> = 8 mA                                                  | V <sub>PDRV(OL)</sub>                                | -                          | 0.12                       | 0.50                       | V    |

PFC Driver Low State Voltage  $I_{PDRV} = 8 \text{ mA}$   $V_{PDRV(OL)}$  - 0.12 0.50 4. Resistor/capacitor parallel combination (39 pF || 20 k $\Omega$ ) between PDRV and driver supply and between PDRV and GND pins.

$\begin{tabular}{ll} \textbf{Table 5. ELECTRICAL CHARACTERISTICS} & (V_{HV} = \text{open}, V_{PFB} = 2.4 \text{ V}, V_{PCS} = 0 \text{ V}, V_{PZCD} = 5 \text{ V}, V_{PControl} = \text{open}, V_{CC} = 15 \text{ V}, V_{PDRV} = \text{open}, V_{HDRVlo} = 15 \text{ V}, C_{OSC} = 2200 \text{ pF}, C_{VREF} = 0.1 \text{ } \mu\text{F}, C_{PCT} = 1000 \text{ pF}, \text{ for typical values}, T_J = 25^{\circ}\text{C}, \text{ for min/max values}, T_J \text{ is } -40^{\circ}\text{C to } 125^{\circ}\text{C}, \text{ unless otherwise noted}) \\ \end{tabular}$

| Characteristics                                                | Conditions                                                                      | Symbol                    | Min  | Тур  | Max | Unit |  |

|----------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------|------|------|-----|------|--|

| HALF BRIDGE HIGH SIDE DRIVER                                   |                                                                                 |                           |      |      |     |      |  |

| Half-Bridge High Side Driver Rise Time                         | 10% to 90% (Note 5)                                                             | t <sub>HDRVhi(rise)</sub> | -    | 18   | =   | ns   |  |

| Half-Bridge High Side Driver Fall Time                         | 90% to 10% (Note 5)                                                             | t <sub>HDRVhi(fall)</sub> | =    | 9    | =   | ns   |  |

| High State Voltage                                             | I <sub>HDRVhi</sub> = -4 mA                                                     | V <sub>HDRVhi(OH)</sub>   | 14.0 | 14.7 | =   | V    |  |

| Low State Voltage                                              | I <sub>HDRVhi</sub> = 4 mA                                                      | V <sub>HDRVhi(OL)</sub>   | _    | 0.06 | 0.5 | V    |  |

| High Side Driver Duty Ratio                                    | 10 to 90% to 10% transitions,<br>V <sub>HSVS</sub> = 50 V (Note 5)              | D <sub>HDRVhiMAX</sub>    | 44   | 48   | 50  | %    |  |

| Boost Supply Undervoltage Threshold                            |                                                                                 | V <sub>HBoost(UVLO)</sub> | 4    | 6.1  | 8.0 | V    |  |

| Boost Current Consumption                                      | HDRVhi switching,<br>between HDRVhi and HVS (Note 5)                            | I <sub>CC(Boost)</sub>    | _    | 0.1  | 0.5 | mA   |  |

| HVS Leakage Current                                            | T <sub>J</sub> = 25°C, V <sub>HVS</sub> = 600 V,<br>V <sub>HBoost</sub> = 600 V | I <sub>HVS(off)</sub>     | -    | 0.1  | 1   | μΑ   |  |

| HALF BRIDGE LOW SIDE DRIVER                                    |                                                                                 |                           |      |      |     |      |  |

| Half-Bridge Low Side Driver Rise Time                          | 10% to 90% (Note 5)                                                             | t <sub>HDRVIo(rise)</sub> | =    | 18   | =   | ns   |  |

| Half-Bridge Low Side Driver Fall Time                          | 90% to 10% (Note 5)                                                             | t <sub>HDRVhi(fall)</sub> | _    | 9    | _   | ns   |  |

| Half-Bridge Low Side Driver High State<br>Voltage              | I <sub>HDRVIo</sub> = -4 mA                                                     | V <sub>HDRVIo(OH)</sub>   | 14   | 14.7 | _   | V    |  |

| Half-Bridge Low Side Driver Low State Voltage                  | I <sub>HDRVIo</sub> = 4 mA                                                      | V <sub>HDRVIo(OL)</sub>   | =    | 0.06 | 0.5 | V    |  |

| Half-Bridge Low Side Driver Duty Ratio                         | 10 to 90% to 10% transitions<br>(Note 5)                                        | D <sub>HDRVIoMAX</sub>    | 44   | 48   | 50  | %    |  |

| CROSSOVER DEAD TIME                                            | <u>'</u>                                                                        |                           |      |      | ı   |      |  |

| Delay from HDRVIo high to low to HDRVhi low to high transition | V <sub>HVS</sub> = 50 V                                                         | t <sub>HDRVhi(h-l)</sub>  | 500  | 785  | 950 | ns   |  |

| Delay from HDRVhi high to low to HDRVlo low to high transition | V <sub>HVS</sub> = 50 V                                                         | t <sub>HDRVhi(h-l)</sub>  | 500  | 785  | 950 | ns   |  |

<sup>5.</sup> Resistor/capacitor parallel combination (39 pF || 20 kΩ) between drive pin and driver supply and between xDRVxx and GND pins.

#### **DETAILED OPERATING DESCRIPTION**

#### Introduction

The NCP1901 is a combination of PFC and half-bridge resonant controllers optimized for off-line adapter applications. This device includes all the features needed to implement a highly efficient and small form factor adapter. It integrates a critical conduction mode (CrM) power factor correction (PFC) controller and half-bridge controller with a built-in 600 V driver. The half-bridge stage operates at a fixed frequency. Regulation is achieved by adjusting the PFC stage output voltage.

This device includes an enable input, open feedback loop protection and PFC overvoltage and undervoltage detectors. Other features included in the NCP1901 are a 600 V startup circuit and an adjustable frequency oscillator. The controllers are properly sequenced, simplifying system design.

#### Supply Sequencing

The PFC controller is enabled once  $V_{CC}$  reaches  $V_{CC(on)}$  and the PFB voltage exceeds  $V_{UVP(high)}$ , typically 290 mV. Once the PFC controller is enabled the PControl pin begins to charge. Once the control voltage exceeds  $V_{EA(OL)}$  the first PFC drive pulse is observed. The half–bridge driver is enabled once the first PFC drive pulse is generated. This ensures a monotonic output voltage rise as the input voltage to the half bridge stage is regulated.

The controller will not start in the event that  $V_{CC}$  falls below  $V_{CC(MIN)}$  before PFB goes above  $V_{UVP(high)}$ . This ensures there is enough time to start the controller before  $V_{CC}$  reaches  $V_{CC(off)}$ .

## **Output Voltage Regulation**

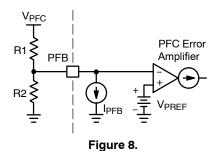

The half-bridge stage operates at a fixed frequency. Output voltage regulation is achieved by adjusting the half-bridge input voltage (PFC output voltage). The PFC output voltage is sensed using a resistor divider. The mid point of the resistor divider connects to the PFB pin. Subtracting current out of the feedback resistor divider increases the PFC output voltage and thus regulation is achieved.

## **High Voltage Startup Circuit**

The NCP1901 internal startup regulator eliminates the need for external startup components. In addition, this regulator increases the efficiency of the supply as it uses no power when in the normal mode of operation, but instead uses power supplied by an auxiliary winding. The startup regulator consists of a constant current source that supplies current from the high voltage line ( $V_{in}$ ) to the supply capacitor on the  $V_{CC}$  pin ( $C_{CC}$ ). The startup current ( $I_{start}$ ) is typically 7.5 mA. The startup circuit is rated at a maximum voltage of 600 V.

Once  $C_{CC}$  is charged to 15.3 V ( $V_{CC(on)}$ ), the startup regulator is disabled and the PFC controller is enabled if the PFB voltage exceeds  $V_{PUVP(high)}$ . The startup regulator

remains disabled until the lower supply threshold,  $V_{\rm CC(off)}$ , (typically 9.3 V) is reached. Once reached, the drive outputs are disabled and the startup current source is enabled. Once the outputs are disabled, the bias current of the NCP1901 is reduced, allowing  $V_{\rm CC}$  to charge back up.

The supply capacitor provides power to the controller while operating in the power up or self-bias mode. During the converter power up,  $C_{CC}$  must be sized such that a  $V_{CC}$  voltage greater than  $V_{CC(off)}$  is maintained while the auxiliary supply voltage is building up. Otherwise,  $V_{CC}$  will collapse and the controller will turn off. The IC bias current and gate charge load at the drive outputs must be considered to correctly size  $C_{CC}$ . The increase in current consumption due to external gate charge is calculated using Equation 1.

$$I_{CC(\text{gate charge})} = f \cdot Q_G$$

(eq. 1)

where, f is the operating frequency and  $Q_G$  is the gate charge of the external MOSFETs.

#### **Main Oscillator**

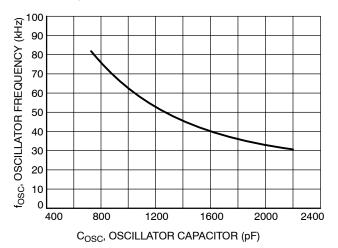

The oscillator frequency is set by the oscillator capacitor,  $C_{OSC}$ , on the OSC pin. The oscillator operates at a fixed 80% duty ratio. A current source charges  $C_{OSC}$  to its peak voltage, typically 5 V. Once the peak voltage is reached, the charge current is disabled and  $C_{OSC}$  is discharged down to 3 V by another current source. The charge and discharge currents are typically 173 and 692  $\mu$ A, respectively. The oscillator frequency vs oscillator capacitance graph is shown in Figure 3.

Figure 3. Oscillator Frequency vs. Oscillator Capacitor

An internal clock signal is generated dividing by two the oscillator frequency. This clock signal is used to control the half-bridge controller. The half-bridge duty ratio is limited to 50%. The PFC is not synchronized to the oscillator as it operates in CrM.

#### Voltage Reference

The internal voltage reference,  $V_{REF}$ , is brought out of the controller to ease compensation requirements. The reference voltage is typically 7.0 V. A 0.1  $\mu F$  is required for stability. The reference should not be loaded with external circuitry.

## **PFC Regulator**

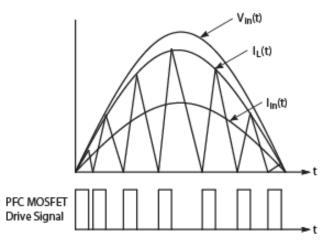

The PFC stage operates in critical conduction mode (CrM). In CrM, the PFC inductor current,  $I_{L(t)}$ , reaches zero at the end of the switch cycle as shown in Figure 4. As seen in Figure 4, the average input current,  $I_{in(t)}$ , is in phase with the ac line voltage,  $V_{in(t)}$ .

Figure 4. Inductor Current in CrM

High power factor is achieved in CrM by maintaining a constant on time  $(t_{on})$  for a given RMS input voltage  $(V_{ac(RMS)})$  and load conditions. Equation 2 shows the relationship between on time and system operating conditions.

$$t_{on} = \frac{2 \cdot P_{out} \cdot L}{\eta \cdot V_{ac(RMS)}^{2}}$$

(eq. 2)

where,  $P_{out}$  is the output power, L is the PFC inductor inductance and  $\eta$  is the system efficiency.

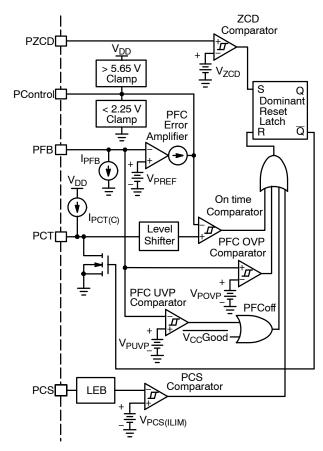

#### **On Time Control**

The NCP1901 controls the on time by charging an external timing capacitor on the PCT pin,  $C_T$ , with a constant current source,  $I_{PCT(C)}$ . The  $C_T$  ramp is then compared to the control voltage,  $V_{PControl}$ . The control voltage is constant for a given RMS line voltage and output load, satisfying Equation 2. A voltage offset,  $V_{PCT(offset)}$ , is added to the  $C_T$  ramp to account for the control voltage range. The block diagram of the constant on time section is shown in Figure 5.

Figure 5. Constant On Time Control Block Diagram

The PControl voltage is internally clamped between 2.25 V and 5.65 V. An offset voltage greater than the minimum PControl clamp voltage is added to the  $C_T$  ramp prior to comparing it to the control voltage signal. This allows the PFC stage to stop the drive pulses (0% duty ratio) and regulate at light loads. The delta between the Pcontrol voltage needed to generate a PDRV pulse and the minimum PControl Clamp voltage is  $V_{PCT(offset)}$ .

The timing capacitor is discharged and held low once the  $C_T$  ramp voltage plus offset reaches  $V_{PControl}$ . The PFC drive pulse terminates once the  $C_T$  voltage reaches its peak voltage threshold,  $V_{PCT(peak)}$ . A new cycle starts once the inductor current reaches zero detected by a transition on the ZCD pin or the maximum off has been reached.

The timing capacitor is sized such that the  $C_T$  ramp peak voltage is reached at low line and full load. In this operating mode  $V_{PControl}$  is at its maximum. Equation 3 is used to calculate the on time for a given  $C_T$ .

$$t_{on(MAX)} = \frac{C_T \cdot V_{PCT(MAX)}}{I_{PCT(C)}}$$

(eq. 3)

Substituting t<sub>on</sub> in Equation 2 with Equation 3 and rearranging Equation 4 provides a maximum value for C<sub>T</sub>.

$$C_T \ge \frac{2 \cdot P_{out} \cdot L \cdot I_{PCT(C)}}{\eta \cdot V_{ac(RMS)}^2 \cdot V_{PCT(MAX)}}$$

(eq. 4)

where,  $V_{PCT(MAX)}$ , is the maximum PCT voltage, typically 3.0 V.

#### **Off Time Control**

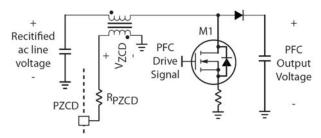

The PFC off time varies with the instantaneous line voltage and it is adjusted every cycle to allow the inductor current to reach zero before the next switch cycle begins. The inductor is demagnetized once its current reaches zero. Once the inductor is demagnetized the drain voltage of the PFC switch begins to drop. The inductor demagnetization is detected by sensing the voltage across the inductor using an auxiliary winding. This winding is commonly known as a zero crossing detector (ZCD) winding. This winding provides a scaled version of the inductor voltage. Figure 6 shows the ZCD winding arrangement.

Figure 6. ZCD Winding Implementation

A negative voltage appears on the ZCD winding while the PFC switch is on. The PZCD voltage is positive while the PFC switch is off and current is flowing through the inductor. The PZCD voltage drops to and rings around zero volts once the inductor is demagnetized. Once a negative transition is detected in the PZCD pin the next switch cycle commences. A positive transition (corresponding to the PFC switch turn off) arms the ZCD detector to prevent false triggering. The arming of the ZCD detector is typically 2.1 V (V<sub>PZCD</sub> increasing) and the triggering is typically 1.5 V (V<sub>PZCD</sub> decreasing).

The PZCD pin is internally clamped to 10 V with a zener diode. A resistor in series with the ZCD pin is required to limit the current into the PZCD pin. The zener diode prevents the voltage from exceeding the 10 V clamp or going below ground. Figure 7 shows typical ZCD waveforms.

Figure 7. ZCD Winding Waveforms

During startup there are no ZCD transitions to enable the PFC switch. A watchdog timer enables the PFC controller if no switch pulses are detected for a period of 180 µs (typical). The watchdog is also useful while operating at light load because the amplitude of the ZCD signal may be very small to cross the ZCD thresholds. The watchdog

timer is reset at the beginning of a PFC drive pulse and in a PFC undervoltage fault.

## **PFC Compensation**

A transconductance error amplifier regulates the PFC output voltage,  $V_{PFC}$ , by comparing the PFC feedback signal to an internal 2.5 V reference. As shown in Figure 28 a resistor divider from the PFC output voltage consisting of R1 and R2 generates the PFC feedback signal.

The feedback signal is applied to the amplifier inverting input. The internal 2.5 V reference,  $V_{PREF}$ , is applied to the amplifier non–inverting input. The reference is trimmed during manufacturing to achieve an accuracy of  $\pm 3.2\%$ . Figure 5 shows the PFC error amplifier and sensing network. Equation 5 is used to calculate the values of the PFC feedback network.

$$V_{PFC} = V_{PREF} \cdot \frac{R_1 + R_2}{R_2} + I_{PFB} \cdot R_1 \quad \text{(eq. 5)}$$

A transconductance amplifier has a voltage–to–current gain, gm. That is, the output current is controlled by the differential input voltage. The NCP1901 amplifier has a typical gm of 95  $\mu$ S. The PControl pin provides access to the amplifier output for compensation. The compensation network is ground referenced allowing the PFC feedback signal to be used to detect an overvoltage condition.

The compensation network on the PControl pin is selected to filter the bulk voltage ripple such that a constant control voltage is maintained across the ac line cycle. A capacitor between the PControl pin and ground sets a pole. A pole at or below 20 Hz is enough to filter the ripple voltage for a 50 and 60 Hz system. The low frequency pole, fp, of the system is calculated using Equation 6.

$$f_{\rm p} = \frac{{\rm gm}}{2\pi{\rm C}_{\rm PControl}}$$

(eq. 6)

where, C<sub>PControl</sub> is the capacitor on the PControl pin to ground.

A key feature to using a transconductance type amplifier, is that the input is allowed to move independently with respect to the output, since the compensation capacitor is connected to ground. This allows dual usage of the feedback pin by the error amplifier and by the overvoltage comparator.

#### **PFC Undervoltage**

The NCP1901 safely disables the controller if the PFB pin is left open. An undervoltage detector disables the controller if the voltage on the PFB pin is below  $V_{PUVP(low)}$ , typically 0.23 V. A 1.2  $\mu$ A (typical) pull down current source,  $I_{PFB}$ , ensures  $V_{PFB}$  falls below  $V_{PUVP(low)}$  if the PFB pin is floating. The PFB pull down current source affects the PFC output voltage regulation setpoint.

#### **PFC Overvoltage**

An overvoltage detector monitors the PFC feedback voltage and disables the PFC driver if the PFC output voltage is greater than 5% of its nominal value. PFC drive pulses are suppressed until the overvoltage condition is removed. The overvoltage detector tolerance is better than  $\pm 2\%$  across the operating temperature voltage range. The overvoltage comparator hysteresis is typically 30 mV (1.2%).

#### **PFC Overcurrent**

The PFC current is monitored by means of an overcurrent detector. The PCS pin provides access to the overcurrent detector. The PFC drive pulse is terminated if the voltage on the PCS pin exceeds the overcurrent threshold,  $V_{PCS(ILIM)}$ . This comparison is done on a cycle by cycle basis. The overcurrent threshold is typically 0.84 V.

The current sense signal is prone to leading edge spikes caused by the power switch transitions. The NCP1901 has leading edge blanking circuitry that blocks out the first 110 ns (typical) of each current pulse.

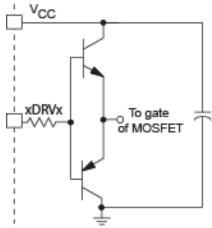

#### **PFC Driver**

The PFC driver source and sink impedances are typically 60 and 15  $\Omega$ , respectively. Depending on the external MOSFET gate charge requirements, an external driver may be needed to drive the PFC power switch. A driver as the one shown in Figure 9 can be easily implemented.

Figure 9. External Driver

## Half-Bridge Driver

The half-bridge stage operates at a fixed 50% duty ratio. The oscillator frequency is divided by two before it is applied to the half-bridge controller.

The half-bridge controller has a low side driver, HDRVIo, and a 600 V high side driver, HDRVhi. The built in high voltage driver eliminates the need for an external transformer or dedicated driver. A built-in delay between each drive transition eliminates the risk of cross conduction. The delay is typically 785 ns. The typical duty ratio of each half-bridge driver is 48%.

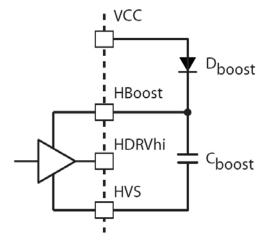

The high side driver is connected between the HBoost and the HVS pins as shown in Figure 10.

Figure 10. Half-bridge High Side Driver

A boost circuit comprised of  $D_{boost}$  and  $C_{boost}$  generates the supply voltage for the high side driver. Once HDRVlo turns on, the HVS pin is effectively grounded through the external power switch. This allows  $C_{boost}$  to charge to  $V_{CC}$ . Once HDRVlo turns off, HVS floats high and  $D_{boost}$  is reversed biased. An undervoltage detector monitors the HBoost voltage. Once the HBoost voltage is greater than  $V_{Boost(UV)}$ , typically, 6.1 V, the high side driver is enabled. The low side driver generally starts before the high side driver because the boost voltage is generated by the low side driver switch transitions.

The half-bridge low side driver source and sink impedances are typically 75 and 15  $\Omega$ , respectively. The half-bridge high side driver source and sink impedances are typically 75 and 15  $\Omega$ , respectively. Depending on the external MOSFETs gate charge requirements, an external driver may be needed to drive the low and high side power switches.

## **Analog and Power Ground**

The NCP1901 has an analog ground, GND, and a power ground, PGND, terminal. GND is used for analog connections such as VREF and OSC. PGND is used for high current connections such as the gate drivers. It is recommended to have independent analog and power ground planes and connect them at a single point, preferably at the ground terminal of the system. This will prevent high current flowing on PGND from injecting noise in GND. The PGND connection should be as short and wide as possible to reduce inductance—induced spikes.

## **PACKAGE DIMENSIONS**

## **SO-20 WB** CASE 751D-05

- NOTES:

1. DIMENSIONS ARE IN MILLIMETERS.

2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 1994.

3. DIMENSIONS D AND E DO NOT INCLUDE MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.

5. DIMENSION B DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE PROTRUSION SHALL BE 0.13 TOTAL IN EXCESS OF B DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIMETERS |       |  |  |

|-----|-------------|-------|--|--|

| DIM | MIN         | MAX   |  |  |

| Α   | 2.35        | 2.65  |  |  |

| A1  | 0.10        | 0.25  |  |  |

| В   | 0.35        | 0.49  |  |  |

| С   | 0.23        | 0.32  |  |  |

| D   | 12.65       | 12.95 |  |  |

| E   | 7.40        | 7.60  |  |  |

| е   | 1.27        | BSC   |  |  |

| Н   | 10.05       | 10.55 |  |  |

| h   | 0.25        | 0.75  |  |  |

| L   | 0.50        | 0.90  |  |  |

| θ   | 0° 7°       |       |  |  |

#### PACKAGE DIMENSIONS

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

- CONTROLLING DIMENSION: MILLIMETER.

DIMENSIONS A AND B DO NOT INCLUDE MOLD

- DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.

MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER

- 4. MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE

- 5. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIN | IETERS   | INC   | HES   |

|-----|--------|----------|-------|-------|

| DIM | MIN    | MAX      | MIN   | MAX   |

| Α   | 9.80   | 10.00    | 0.386 | 0.393 |

| В   | 3.80   | 4.00     | 0.150 | 0.157 |

| С   | 1.35   | 1.75     | 0.054 | 0.068 |

| D   | 0.35   | 0.49     | 0.014 | 0.019 |

| F   | 0.40   | 1.25     | 0.016 | 0.049 |

| G   | 1.27   | 1.27 BSC |       | BSC   |

| J   | 0.19   | 0.25     | 0.008 | 0.009 |

| K   | 0.10   | 0.25     | 0.004 | 0.009 |

| M   | 0 °    | 7°       | 0°    | 7°    |

| P   | 5.80   | 6.20     | 0.229 | 0.244 |

| R   | 0.25   | 0.50     | 0.010 | 0.019 |

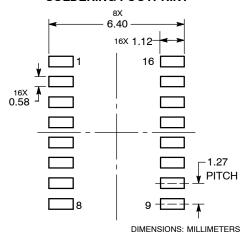

#### **SOLDERING FOOTPRINT**

The products described herein (NCP1901) may be covered by one or more of the following U.S. patents: 6,373,734. There may be other patents pending.

ON Semiconductor and the registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and exasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada

Fax: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81–3–5773–3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your loca Sales Representative