# NBM5100A-Q100; NBM5100B-Q100

Coin cell battery life booster with adaptive power optimization

Rev. 2 — 10 April 2025

## Product data sheet

# 1. General description

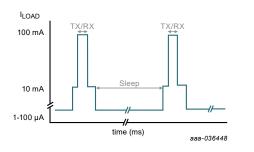

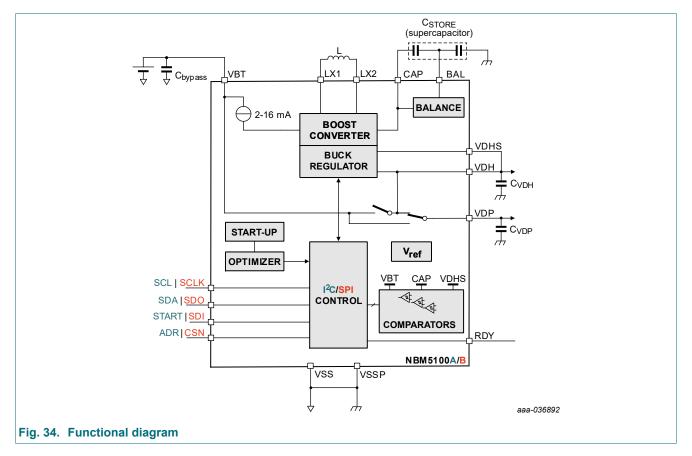

The NBM5100A/B-Q100 is a battery energy management device designed to maximize usable capacity from non-rechargeable, primary batteries when used in low-voltage, low-power applications requiring burst current loads. The devices overcome voltage drop and battery life limitations associated with extracting high pulse currents (Fig. 1) from lithium primary batteries such as 3.6 V lithium thionyl chloride (Li-SOCl<sub>2</sub>), which are commonly used in wireless, low-power loT sensor applications.

The NBM5100A/B-Q100 contains two stages of high efficiency DC-DC conversion and an intelligent learning algorithm. The first stage DC-DC conversion transfers energy from the lithium battery at a low constant current to a capacitive storage element. Once charged, a second DC-DC conversion cycle utilizes this stored energy to supply a regulated voltage with high pulse load current capability on the VDH output pin. The battery is never directly subjected to large load pulse currents, resulting in a longer, more predictable battery lifetime.

The proprietary learning algorithm monitors the energy used during repetitive load pulse cycles and optimizes first stage DC-DC conversion to minimize the residual charge in the storage capacitor.

A serial interface allows a microcontroller to change default configuration settings and read-back system information.

#### Table 1. Related devices

| Type number   | Bus<br>interface | Auto<br>start | Pulse<br>I <sub>LOAD</sub> |

|---------------|------------------|---------------|----------------------------|

| NBM5100A-Q100 | I²C              | Yes           | ≥ 150 mA                   |

| NBM5100B-Q100 | SPI              | No            | ≥ 150 mA                   |

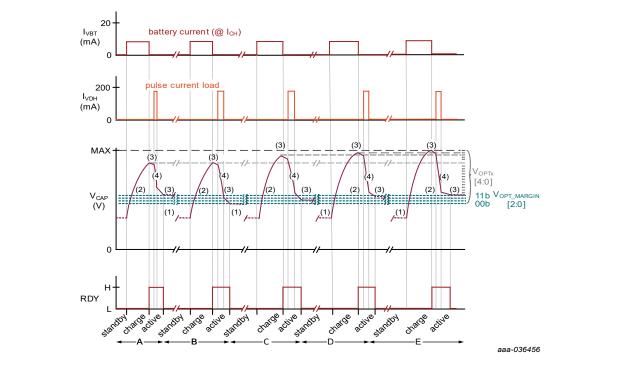

Fig. 1. IoT pulsed load profile

# 2. Features and benefits

- Automotive product qualification in accordance with AEC-Q100 (Grade 3)

- Specified from -40 °C to +85 °C

- Programmable constant battery load current: 2 mA to 16 mA

- Protection against battery voltage dips (Brown-out)

- Pulse output current: > 150 mA

- Low ripple regulated programmable output voltage, VDH: 1.8 V to 3.6 V

- Ultra-low standby current: 20 nA (typ)

- Peak conversion efficiency up to 93% with adaptive optimization

- Integrated fuel gauge

- Integrated capacitor voltage balancing circuit

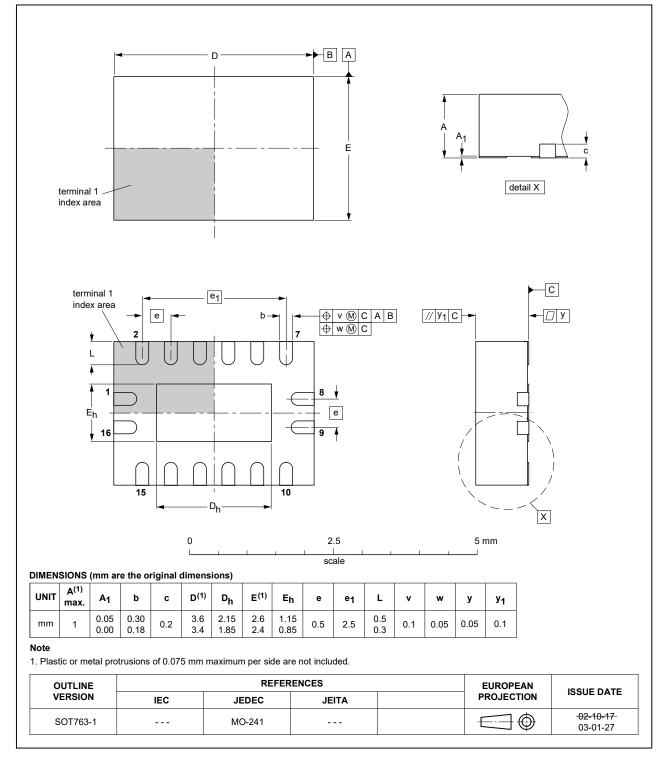

- Small 16 pin lead-free package (SOT763-1/DHVQFN16; 2.5 mm × 3.5 mm × 0.85 mm) with side wettable flanks

# 3. Applications

- Battery powered wireless microcontroller applications (IoT): Bluetooth<sup>®</sup>, LoRaWAN<sup>®</sup>, Sigfox<sup>™</sup>, LTE-M, NB-IoT, Zigbee, etc.

- **Industrial:** temperature, occupancy, e-metering, electronic shelf label, asset tracking, irrigation monitoring

- Automotive: tire pressure monitors (TPMS), key fobs

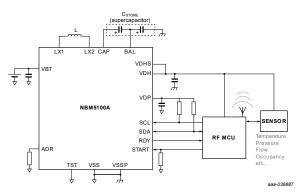

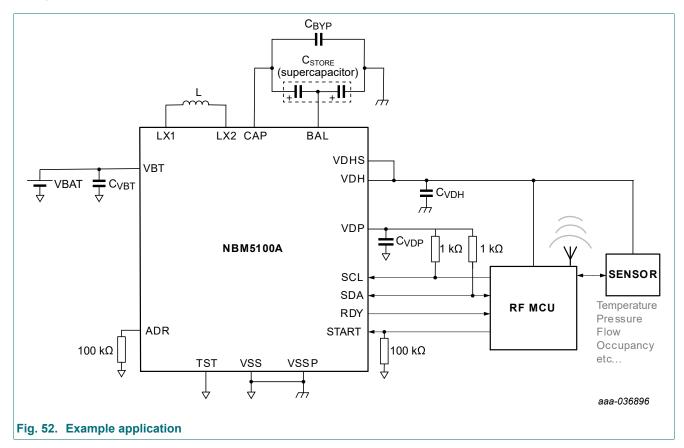

Fig. 2. Simplified Application

# ne<mark>x</mark>peria

# 4. Ordering information

| Table 2. Ordering information       Type number     Package |                   |      |                                                                                                                                      |                 |  |

|-------------------------------------------------------------|-------------------|------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|

|                                                             | Temperature range | Name | Description                                                                                                                          | Version         |  |

| NBM5100ABQ-Q100<br>NBM5100BBQ-Q100                          |                   |      | plastic dual in-line compatible thermal enhanced<br>very thin quad flat package; no leads; 16 terminals;<br>body 2.5 × 3.5 × 0.85 mm | <u>SOT763-1</u> |  |

# 5. Marking

| Table 3. Marking codes |              |  |

|------------------------|--------------|--|

| Type number            | Marking code |  |

| NBM5100ABQ-Q100        | M5100A       |  |

| NBM5100BBQ-Q100        | M5100B       |  |

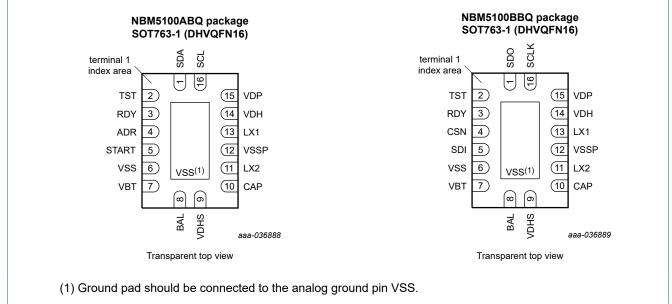

# 6. Pin configuration and description

# 6.1. Pin configuration

## Fig. 3. Pin configuration SOT763-1 (DHVQFN16)

# 6.2. Pin description

### Table 4. Pin description

|     | Symbol                                                     |               |                                                    |                                                                                                                                         |  |  |

|-----|------------------------------------------------------------|---------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin | NBM5100A-Q100                                              | NBM5100B-Q100 | I/O                                                | Description                                                                                                                             |  |  |

| 1   | SDA                                                        | SDO           | I (A) O (B)                                        | serial data I/O (I <sup>2</sup> C) / serial data out MISO (SPI)                                                                         |  |  |

| 2   | Т                                                          | ST            | I                                                  | factory test only, tie to VSS                                                                                                           |  |  |

| 3   | RI                                                         | ΟY            | 0                                                  | status output                                                                                                                           |  |  |

| 4   | ADR                                                        | CSN           | I                                                  | address pin (I <sup>2</sup> C) / chip select (SPI; active LOW)                                                                          |  |  |

| 5   | START                                                      | SDI           | l                                                  | start pin (active high) [1] / serial data in MOSI (SPI)                                                                                 |  |  |

| 6   | V                                                          | SS            | PWR                                                | analog ground, should be connected to VSSP on PCB                                                                                       |  |  |

| 7   | VBT PWR input supply to the IC (typically from a battery). |               | input supply to the IC (typically from a battery). |                                                                                                                                         |  |  |

| 8   | B                                                          | AL            | I/O                                                | capacitor balancing input/output                                                                                                        |  |  |

| 9   | VD                                                         | HS            | I                                                  | sense input                                                                                                                             |  |  |

| 10  | C                                                          | ٩P            | PWR                                                | storage capacitor                                                                                                                       |  |  |

| 11  | Ľ                                                          | X2            | -                                                  | inductor connection 2                                                                                                                   |  |  |

| 12  | VS                                                         | SP            | PWR                                                | power (switching) ground, should be connected to VSS on PCB                                                                             |  |  |

| 13  | L                                                          | X1            | -                                                  | inductor connection 1                                                                                                                   |  |  |

| 14  | VI                                                         | ЭН            | 0                                                  | regulated supply output (see output configuration)                                                                                      |  |  |

| 15  | VI                                                         | OP            | 0                                                  | permanent supply output (see output configuration)                                                                                      |  |  |

| 16  | SCL SCLK                                                   |               | I                                                  | serial clock input SCL (I <sup>2</sup> C); SCLK (SPI)                                                                                   |  |  |

| -   | Pad                                                        |               | -                                                  | this is not a supply pin; should be soldered to PCB and connected to VSS externally; used to heat-sink the device to the circuit board. |  |  |

[1] Connect to VSS with a pull-down resistor when not actively driving.

NBM5100\_Q100 Submit document feed

# 7. Specifications

## 7.1. Limiting values

#### Table 5. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).

| Symbol           | Parameter               | Conditions                                                                           | Min  | Max                   | Unit |

|------------------|-------------------------|--------------------------------------------------------------------------------------|------|-----------------------|------|

| V <sub>VBT</sub> | supply voltage pin VBT  |                                                                                      | -0.3 | 6.0                   | V    |

| VI               | input voltage           | VDHS<br>NBM5100A-Q100: ADR, START, SCL, SDA<br>NBM5100B-Q100: CSN, SDI, SDO and SCLK | -0.3 | V <sub>VDP</sub> +0.3 | V    |

| Vo               | output voltage          | BAL, VDH and VDP                                                                     | -0.3 | 6.0                   | V    |

| V <sub>CAP</sub> | storage voltage pin CAP |                                                                                      | -0.3 | 6.0                   | V    |

| I <sub>O</sub>   | output current          | VDH, LX1, LX2 and CAP                                                                | -    | 500                   | mA   |

| T <sub>amb</sub> | ambient temperature     |                                                                                      | -40  | +85                   | °C   |

| T <sub>stg</sub> | storage temperature     |                                                                                      | -65  | +150                  | °C   |

# 7.2. ESD ratings

#### Table 6. ESD ratings

|      |                                      |                                       | Value  | Unit |

|------|--------------------------------------|---------------------------------------|--------|------|

| V    | /ESD electrostatic discharge voltage | HBM: ANSI/ESDA/JEDEC JS-001 Class 2   | ± 2000 | V    |

| ✓ESD |                                      | CDM: ANSI/ESDA/JEDEC JS-002 Class C2a | ± 500  | V    |

# 7.3. Thermal information

#### Table 7. Thermal information

Thermal resistance according to JEDEC51-5 and -7

| Symbol                | Parameter                                  | SOT763-1 | Unit |

|-----------------------|--------------------------------------------|----------|------|

| R <sub>OJA</sub>      | junction-to-ambient thermal resistance     | 82       | K/W  |

| R <sub>OJC(TOP)</sub> | junction-to-case (top) thermal resistance  | 50       | K/W  |

| $\Psi_{JT}$           | junction-to-top characterization parameter | 7        | K/W  |

# 7.4. Recommended operating conditions

#### Table 8. Recommended operating conditions

Voltages are referenced to GND (ground = 0 V).

| Symbol           | Parameter            | Conditions                                                                       | Min | Max              | Unit |

|------------------|----------------------|----------------------------------------------------------------------------------|-----|------------------|------|

| V <sub>VBT</sub> | supply voltage       | VBT pin                                                                          | 2.4 | 3.6              | V    |

| V <sub>I/O</sub> | input/output voltage | RDY<br>NBM5100A-Q100: SCL, SDA, START, ADR<br>NBM5100B-Q100: CSN, SDI, SDO, SCLK | 0   | V <sub>VDP</sub> | V    |

| I <sub>O</sub>   | output current       | VDP pin (Standby state)                                                          | 0   | 5                | mA   |

| lo               | output current       | VDH pin (Active state)                                                           | 0   | 150              | mA   |

# 7.5. Recommended components

#### Table 9. Recommended components

Nominal component values, not including tolerance or derating factors. [1]

| Symbol           | Parameter                      | Min   | Nom    | Мах | Unit |

|------------------|--------------------------------|-------|--------|-----|------|

| C <sub>VBT</sub> | capacitance on VBT             | 1     | 2      |     | μF   |

| C <sub>VDP</sub> | capacitance on VDP             | 1     | 2      | -   | μF   |

| C <sub>VDH</sub> | capacitance on VDH             | 47    | -      | -   | μF   |

| C <sub>CAP</sub> | energy storage capacitance     | 0.047 | -      | 470 | mF   |

| L [2]            | inductance between LX1 and LX2 |       | 15 [3] | -   | μH   |

[1] Nominal component values shown - does not include derating factors.

[2] Ensure inductor saturation current,  $I_{SAT}$ , rating > 1 A.

[3] Assume ± 20% tolerance.

# 7.6. Electrical characteristics

#### Table 10. Static characteristics

At recommended operating conditions; voltages are referenced to GND (ground = 0 V); typical values are at 25°C (unless otherwise noted).

| $V_{VBT} = 3.0 V: C_{VBT} = 1 \mu F: C_{VDP}$ | = 1 иF: С <sub>VDH</sub> = 47 иF: L = | 15 μH; unless otherwise specified. |

|-----------------------------------------------|---------------------------------------|------------------------------------|

|                                               |                                       |                                    |

| Symbol             | Parameter                 | Conditions                                                                                     | T <sub>amb</sub> | = -40 °C to + | -85 °C | Unit |

|--------------------|---------------------------|------------------------------------------------------------------------------------------------|------------------|---------------|--------|------|

|                    |                           |                                                                                                | Min              | Тур           | Max    |      |

| Input              |                           | 1                                                                                              |                  |               |        | _    |

| V <sub>POR</sub>   | power on reset            | Device starting voltage for operation at battery<br>insert<br>T <sub>amb</sub> = -40 °C        | 1.3              | -             | 2.7    | V    |

| V <sub>POR</sub>   | power on reset            | Device starting voltage for operation at battery<br>insert<br>25 °C ≤ T <sub>amb</sub> ≤ 85 °C | 1.3              | -             | 2.3    | V    |

| ٤ <sub>V</sub>     | absolute<br>voltage error | $V_{\text{FIX}}, V_{\text{CAP}(\text{max})}, V_{\text{SET}}, \text{ and } V_{\text{EW}}$       | -                | -             | 5      | %    |

| Capacito           | r charge current          | from VBT pin                                                                                   |                  |               |        |      |

| I <sub>CH</sub>    | charge current            | Charge state, <u>ich</u> = 000b                                                                | 1.4              | 2.0           | 2.6    | mA   |

|                    |                           | Charge state, <u>ich</u> = 001b                                                                | 2.8              | 4.0           | 5.2    | mA   |

|                    |                           | Charge state, <u>ich</u> = 010b                                                                | 5.6              | 8.0           | 10.4   | mA   |

|                    |                           | Charge state, <u>ich</u> = 011b                                                                | 11.2             | 16            | 20.75  | mA   |

|                    |                           | Charge state, <u>ich</u> = 100b (V <sub>CAP</sub> > V <sub>VBT</sub> )                         | 35               | 50            | 85     | mA   |

| EFF <sub>ch</sub>  | converter<br>efficiency   | Conversion efficiency (Charge state)                                                           | -                | 80            | -      | %    |

| Supply c           | urrent from VBT           | pin                                                                                            |                  |               |        |      |

| I <sub>Q_STB</sub> | quiescent<br>current      | Standby state                                                                                  | -                | 20            | -      | nA   |

| I <sub>Q_CM</sub>  | quiescent<br>current      | Continuous mode, C <sub>STORE</sub> charged                                                    | -                | 1.8           | -      | μA   |

| I <sub>Q_ACT</sub> | quiescent<br>current      | Active state, I <sub>LOAD</sub> = 10 mA                                                        | -                | 0.4           | -      | mA   |

| Symbol                     | Parameter               | Conditions                                                                                                          | T <sub>amb</sub> | = −40 °C to +    | •85 °C | Unit |

|----------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------|------------------|------------------|--------|------|

|                            |                         | -                                                                                                                   | Min              | Тур              | Max    |      |

| VDH outp                   | ut                      | ·                                                                                                                   |                  | -                |        |      |

| Vo                         | output voltage          | Active state, I <sub>VDH</sub> > 1 mA                                                                               | -                | V <sub>SET</sub> | -      | V    |

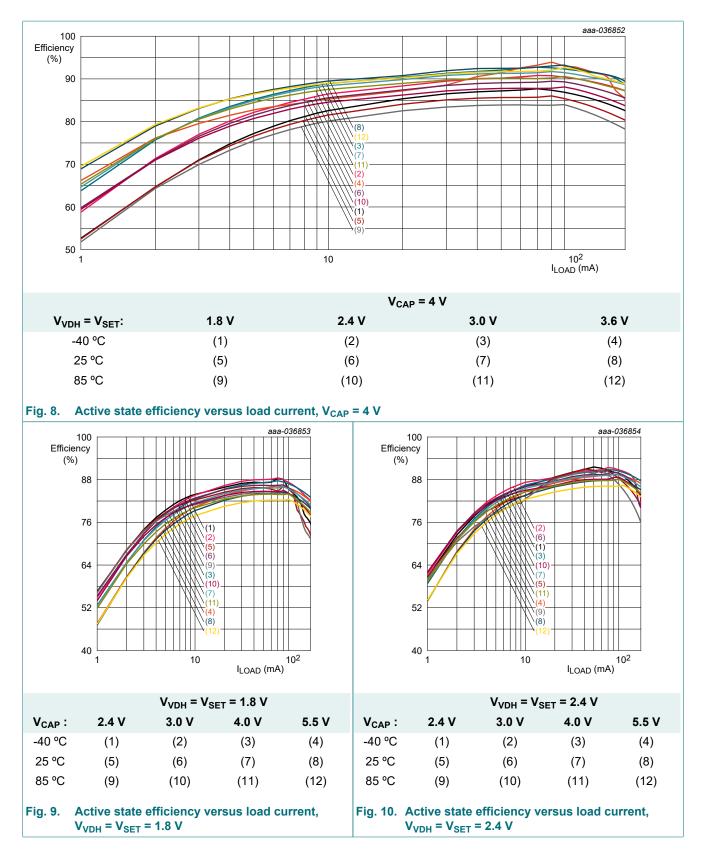

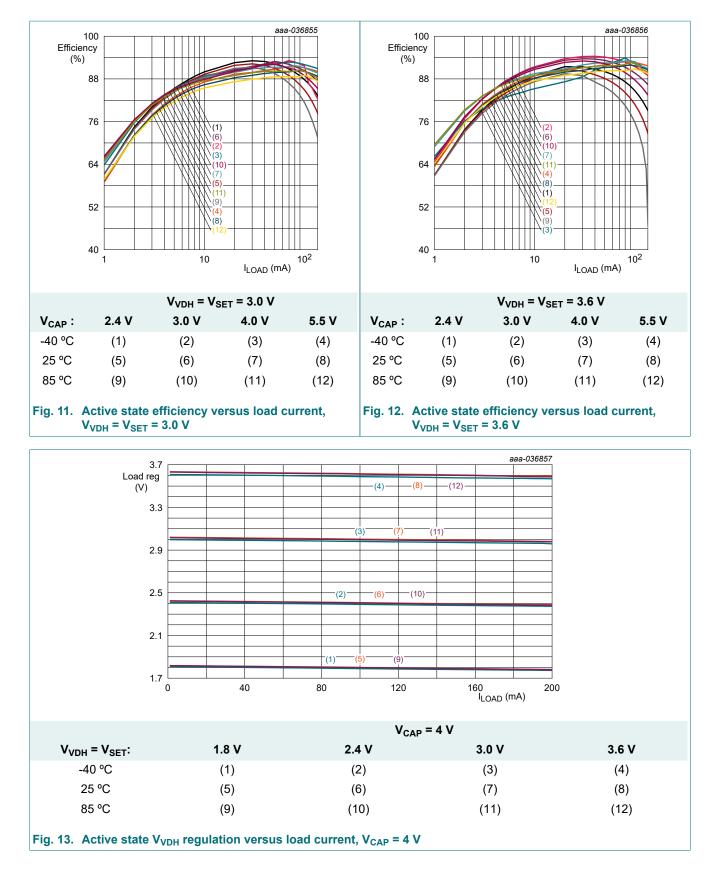

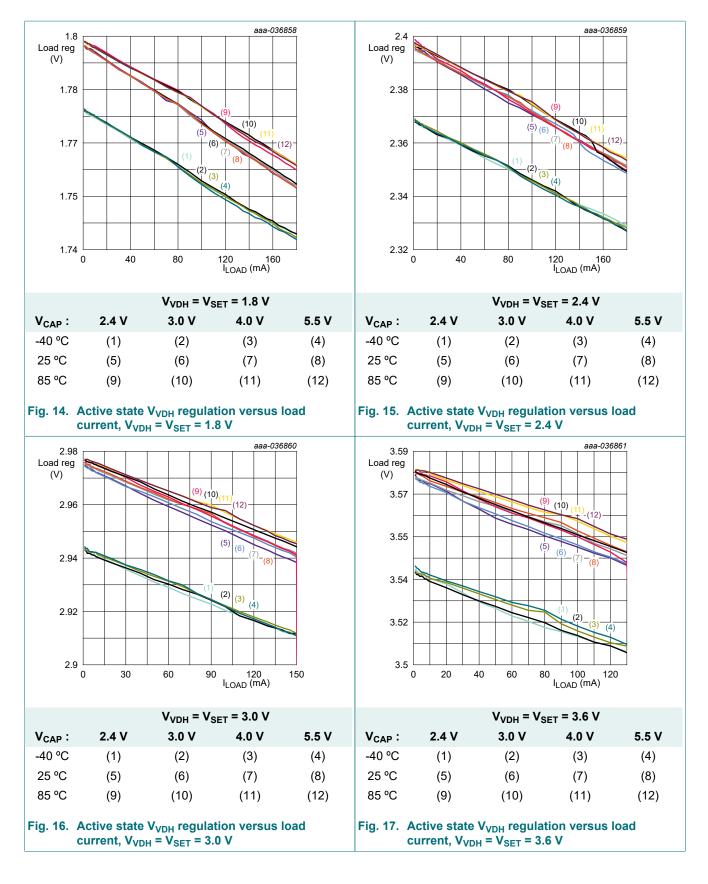

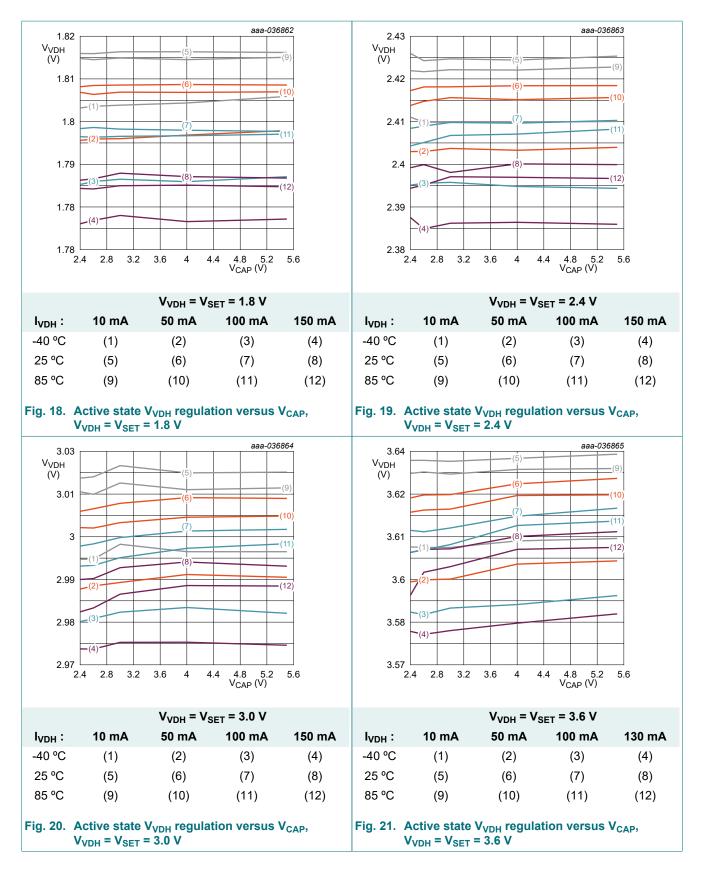

| $\Delta V_{DH(\Delta IO)}$ | VDH load regulation     | see <u>Fig. 13</u>                                                                                                  | -                | ± 1              | -      | %    |

| EFF <sub>ACT</sub>         | converter<br>efficiency | Active state                                                                                                        | -                | 90               | -      | %    |

| R <sub>VDP</sub>           | output<br>resistance    | pin VDP                                                                                                             | -                | 20               | 30     | Ω    |

| Balance c                  | urrent                  |                                                                                                                     |                  | -                |        |      |

|                            |                         | at $V_{CAP}$ = 5 V. Values scale with $V_{CAP}$ voltage.<br>on positive or negative offset of $V_{BAL}$ compared to |                  |                  |        |      |

| I <sub>BAL</sub>           | balance                 | <i>bal_mode</i> = 00b                                                                                               | 0.3              | 1.1              | 1.9    | mA   |

|                            | current                 | <i>bal_mode</i> = 01b                                                                                               | 1.2              | 2.2              | 3.5    | mA   |

|                            |                         | <i>bal_mode</i> = 10b                                                                                               | 1.6              | 3.0              | 4.3    | mA   |

|                            |                         | <i>bal_mode</i> = 11b                                                                                               | 2.9              | 4.7              | 6.8    | mA   |

| No load d                  | etection                | · !                                                                                                                 |                  |                  |        |      |

No load detection is active in the Auto mode only. It set the device into standby state when the load current is below the threshold  $I_{NL}$  for longer than  $T_{NL}$ .

The detected load detection current is the sum of currents in the VDP and VDH outputs.

| I <sub>NL</sub> | current<br>threshold | No load Current threshold | - | 100 | - | μA |

|-----------------|----------------------|---------------------------|---|-----|---|----|

| T <sub>NL</sub> | detection time       | No load Detection time    | - | 20  | - | ms |

#### Table 11. Logic inputs/outputs (SDA/SDO), RDY, (ADR/CSN), (START/SDI) and (SCL/SCLK) pins

At recommended operating conditions; voltages are referenced to GND (ground = 0 V); typical values are at 25°C (unless otherwise noted).

$V_{VBT}$  = 3.0 V;  $C_{VBT}$  = 1  $\mu$ F;  $C_{VDP}$  = 1  $\mu$ F;  $C_{VDH}$  = 47  $\mu$ F; L = 15  $\mu$ H; unless otherwise specified.

| Symbol          | Parameter                    | T <sub>amb</sub>           | = −40 °C to +          | 85 °C | Unit                   |    |

|-----------------|------------------------------|----------------------------|------------------------|-------|------------------------|----|

|                 |                              |                            | Min                    | Тур   | Max                    |    |

| I <sub>I</sub>  | input current                |                            | -                      | 0     | -                      | μA |

| V <sub>IL</sub> | LOW-level<br>input voltage   |                            | -                      | -     | 0.3 x V <sub>VDP</sub> | V  |

| V <sub>IH</sub> | HIGH-level<br>input voltage  |                            | 0.7 x V <sub>VDP</sub> | -     | -                      | V  |

| V <sub>H</sub>  | hysteresis<br>voltage        |                            | 0.16V x <sub>VDP</sub> | -     | -                      | V  |

| V <sub>OL</sub> | LOW-level output voltage     | I <sub>OL</sub> = 3 mA     | -                      | -     | 0.2 x V <sub>VDP</sub> | V  |

| V <sub>OH</sub> | HIGH-level<br>output voltage | I <sub>OH</sub> = 2 mA [1] | 0.7 x V <sub>VDP</sub> | -     | -                      | V  |

[1] For NBM5100A-Q100 open drain output at SDA pin excluded.

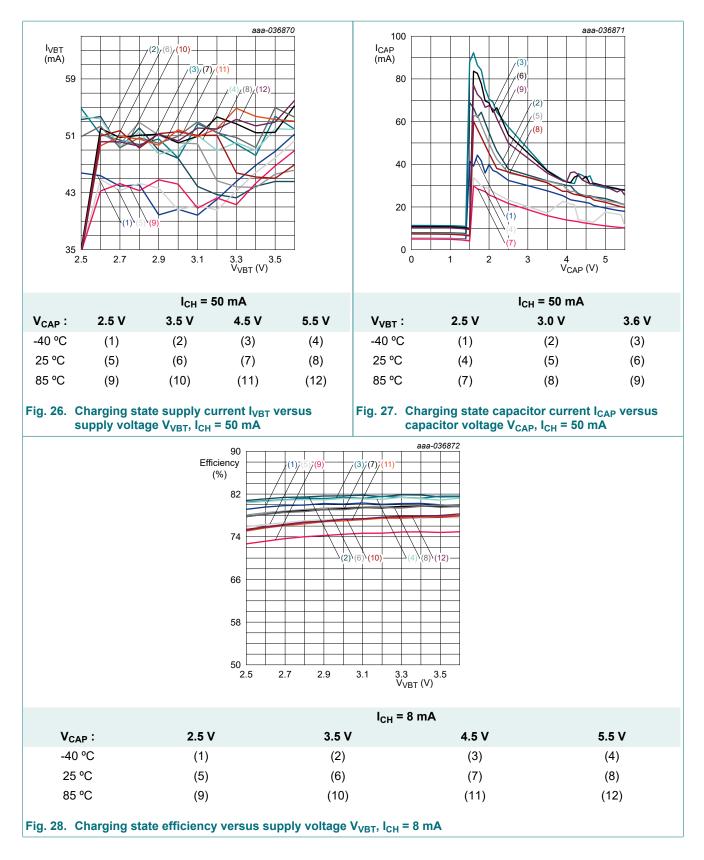

# 7.7. Dynamic characteristics

Table 12. Timing requirements and switching characteristics of logic inputs/outputs I<sup>2</sup>C (NBM5100A-Q100, SDA and SCL pins

At recommended operating conditions; voltages are referenced to GND (ground = 0 V); typical values are at 25°C (unless otherwise noted).

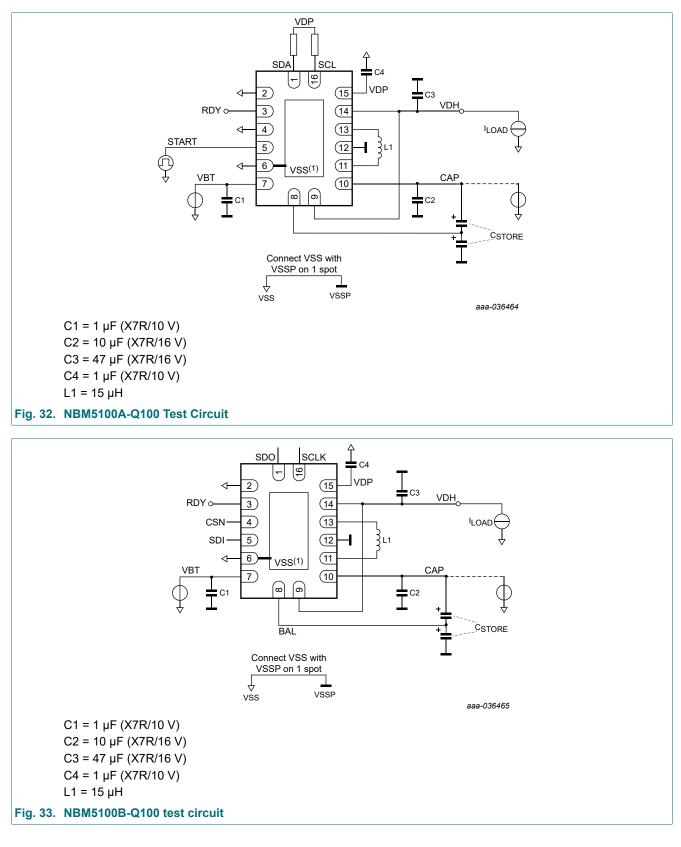

$V_{VBT}$  = 2.4 V to 3.6 V;  $C_{VBT}$  = 1  $\mu$ F;  $C_{VDP}$  = 1  $\mu$ F;  $C_{VDH}$  = 47  $\mu$ F; L = 15  $\mu$ H. At recommended operating conditions; voltages are referenced to GND (ground = 0 V); for waveforms see Fig. 29; for test circuit see Fig. 32.

| Symbol              | Parameter                  | Conditions                                    | T <sub>amb</sub> = | T <sub>amb</sub> = -40 °C to +85 °C |     |     |  |

|---------------------|----------------------------|-----------------------------------------------|--------------------|-------------------------------------|-----|-----|--|

|                     |                            |                                               | Min                | Тур                                 | Max |     |  |

| Timing re           | quirements                 |                                               |                    |                                     |     |     |  |

| f <sub>clk</sub>    | clock frequency            | SCL                                           | -                  | -                                   | 1   | MHz |  |

| t <sub>low</sub>    | low time                   | SCL                                           | 500                | -                                   | -   | ns  |  |

| t <sub>high</sub>   | high time                  | SCL                                           | 260                | -                                   | -   | ns  |  |

| t <sub>su;sta</sub> | set-up time                | START; for repeated START condition           | 260                | -                                   | -   | ns  |  |

| t <sub>h;sta</sub>  | hold time                  | START; for repeated START condition           | 260                | -                                   | -   | ns  |  |

| t <sub>su;sto</sub> | set-up time                | STOP; for STOP condition                      | 260                | -                                   | -   | ns  |  |

| t <sub>buf</sub>    | bus free time              | between STOP and START                        | 500                | -                                   | -   | ns  |  |

| t <sub>su;dat</sub> | set-up time                | SDA                                           | 50                 | -                                   | -   | ns  |  |

| t <sub>h;dat</sub>  | hold time                  | SDA                                           | 0                  | -                                   | -   | ns  |  |

| t <sub>r</sub>      | rise time                  | SCL                                           | -                  | -                                   | 120 | ns  |  |

| t <sub>r</sub>      | rise time                  | SDA                                           | -                  | -                                   | 120 | ns  |  |

| t <sub>f</sub>      | fall time                  | SCL                                           | -                  | -                                   | 120 | ns  |  |

| t <sub>f</sub>      | fall time                  | SDA                                           | -                  | -                                   | 120 | ns  |  |

| Switching           | characteristics            |                                               |                    |                                     |     |     |  |

| t <sub>vd_dat</sub> | valid time, data           | SDA; in Tx mode                               | -                  | -                                   | 450 | ns  |  |

| t <sub>vd_ack</sub> | valid time,<br>acknowledge | SDA; in Tx mode                               | -                  | -                                   | 450 | ns  |  |

| t <sub>of</sub>     | output fall time           | in Tx mode, C <sub>L</sub> = 10 pF, 70% - 30% | -                  | -                                   | 120 | ns  |  |

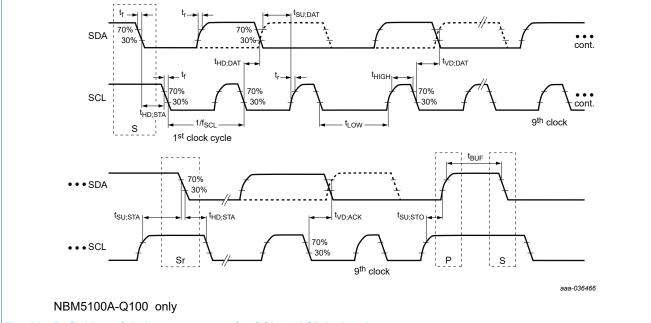

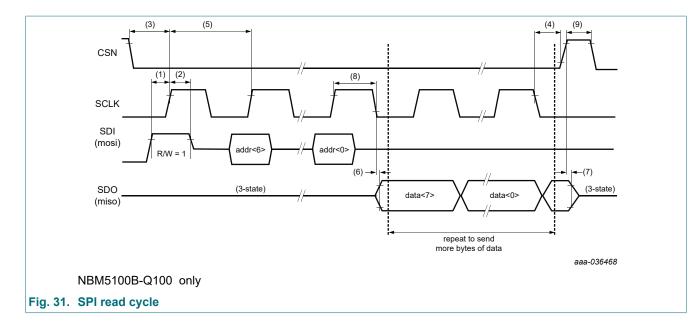

# Table 13. Timing requirements and switching characteristics of logic inputs/outputs SPI (NBM5100B-Q100, SDO, CSN, SDI and SCLK pins

At recommended operating conditions; voltages are referenced to GND (ground = 0 V); typical values are at 25°C (unless otherwise noted).

| Symbol            | Parameter       | Conditions                                                                                  | T <sub>amb</sub> = | = -40 °C to | +85 °C   | Unit |

|-------------------|-----------------|---------------------------------------------------------------------------------------------|--------------------|-------------|----------|------|

|                   |                 |                                                                                             | Min                | Тур         | Max      |      |

| Timing re         | quirements      |                                                                                             |                    |             |          |      |

| f <sub>clk</sub>  | clock frequency | SCLK                                                                                        | -                  | -           | 4        | MHz  |

| t <sub>clk</sub>  | period time     | SCLK; see <u>Fig. 30<sup>(5)</sup> and Fig. 31<sup>(5)</sup></u>                            | 250                | -           | -        | ns   |

| t <sub>CSH</sub>  | reset time      | CSN; see <u>Fig. 30<sup>(6)</sup> and Fig. 31<sup>(9)</sup></u>                             | 200                | -           | -        | ns   |

| t <sub>low</sub>  | low time        | SCLK                                                                                        | 100                | -           | -        | ns   |

| t <sub>high</sub> | high time       | SCLK                                                                                        | 100                | -           | -        | ns   |

| t <sub>su</sub>   | setup time      | CSN; see <u>Fig. 30<sup>(3)</sup></u> and <u>Fig. 31<sup>(3)</sup></u>                      | 100                | -           | -        | ns   |

| t <sub>h</sub>    | hold time       | CSN; see <u>Fig. 30<sup>(4)</sup></u> and <u>Fig. 31<sup>(4)</sup></u>                      | 0                  | -           | -        | ns   |

| t <sub>su</sub>   | setup time      | SDI; see <u>Fig. 30<sup>(1)</sup> and Fig. 31<sup>(1)</sup></u>                             | 10                 | -           | -        | ns   |

| t <sub>h</sub>    | hold time       | SDI; see <u>Fig. 30<sup>(2)</sup> and Fig. 31<sup>(2)</sup></u>                             | 20                 | -           | -        | ns   |

| Switching         | characteristics |                                                                                             | <b>I</b>           |             | <u> </u> |      |

| t <sub>dav</sub>  | valid time      | SDO; after neg clock edge, incl 3-state/<br>active delay; see <u>Fig. 31</u> <sup>(6)</sup> | -                  | -           | 100      | ns   |

| t <sub>rel</sub>  | release time    | SDO; after CSN transition to high; see <u>Fig. 31</u> <sup>(7)</sup>                        | -                  | -           | 100      | ns   |

| t <sub>f</sub>    | fall time       | SDO; C <sub>L</sub> = 10 pF, 70% - 30%                                                      | -                  | -           | 10       | ns   |

| t <sub>r</sub>    | rise time       | SDO; C <sub>L</sub> = 10 pF, 30% - 70%                                                      | -                  | -           | 10       | ns   |

#### Table 14. Switching characteristics of RDY output

At recommended operating conditions; voltages are referenced to GND (ground = 0 V); typical values are at 25°C (unless otherwise noted).

$V_{VBT} = V_{VDP} = 2.4 \text{ V to } 3.6 \text{ V}; C_{VBT} = 1 \ \mu\text{F}; C_{VDP} = 1 \ \mu\text{F}; C_{VDH} = 47 \ \mu\text{F}; L = 15 \ \mu\text{H}.$  At recommended operating conditions; voltages are referenced to GND (ground = 0 V); for test circuit see Fig. 32 and Fig. 33.

| Symbol             | Parameter      | Conditions                             | T <sub>amb</sub> = -40 °C to +85 °C |     | Unit |    |

|--------------------|----------------|----------------------------------------|-------------------------------------|-----|------|----|

|                    |                |                                        | Min                                 | Тур | Мах  |    |

| t <sub>r</sub>     | rise time      | RDY; C <sub>L</sub> = 10 pF, 30% - 70% | -                                   | -   | 10   | ns |

| t <sub>f</sub>     | fall time      | RDY; C <sub>L</sub> = 10 pF, 70% - 30% | -                                   | -   | 10   | ns |

| t <sub>W(EW)</sub> | EW pulse width | RDY; Early Warning active              | 2.6                                 | -   | 6.5  | μs |

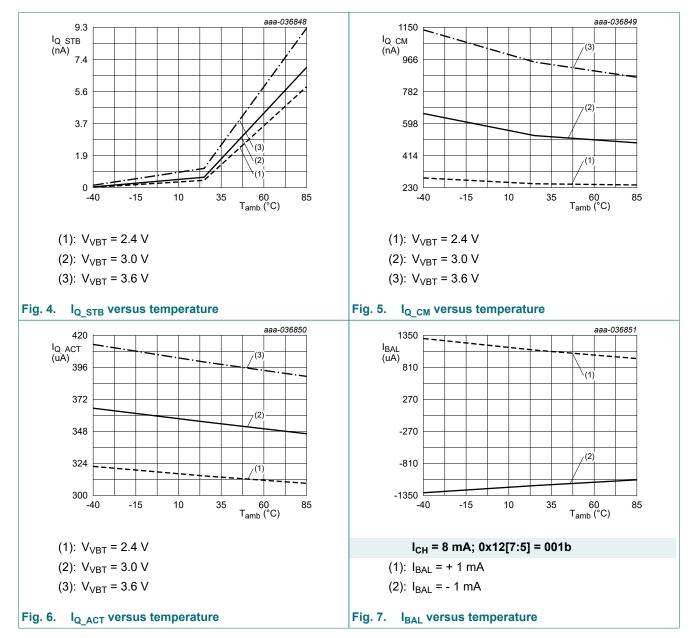

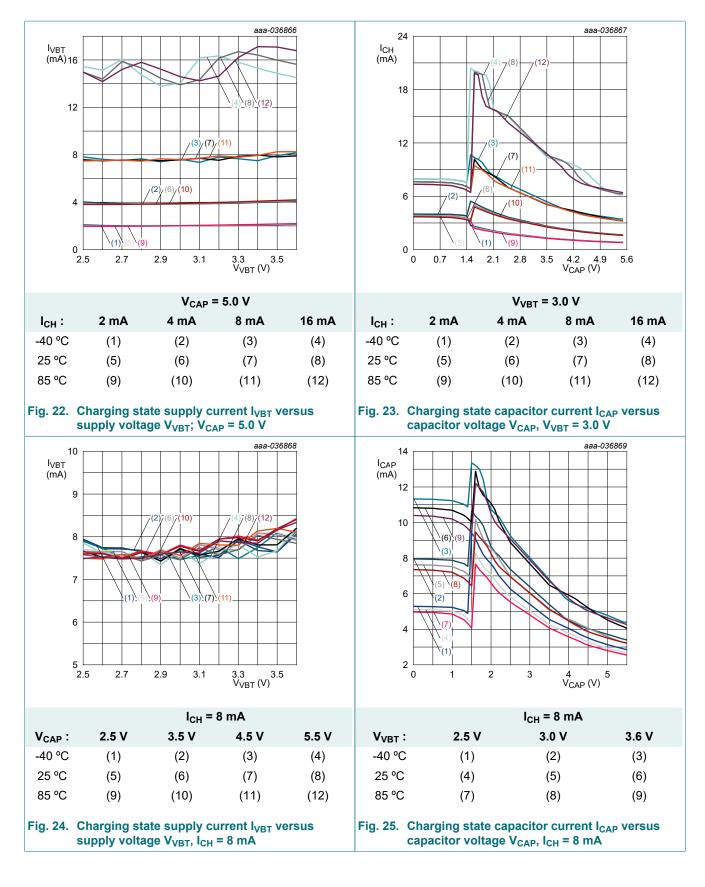

# 7.8. Typical characteristics

At recommended operating conditions; voltages are referenced to GND (ground = 0 V); typical values are at 25°C (unless otherwise noted).

# 7.9. Timing diagrams

# 7.10. Test circuits

# 8. Detailed description

## 8.1. Functional diagram

# 8.2. Overview

The NBM5100A/B-Q100 is a battery energy management device designed to maximize usable capacity from non-rechargeable, primary batteries when used in low-voltage, low-power applications requiring burst current loads.

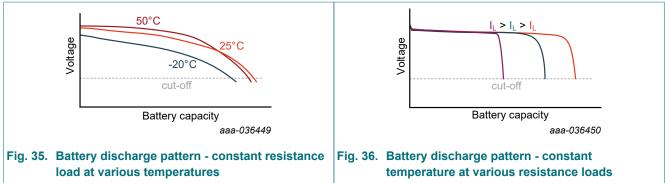

Battery capacity, expressed as milliampere-hours (mAh) is the amount of current withdrawn from a cell multiplied times the number of hours the cell can deliver the current to a specific end-point voltage, often referred to as the cut-off voltage. Cell capacity varies in response to the applied load and temperature. The shape of the curve depends upon battery construction and chemistry. Primary battery data sheets provide characteristic curves to aid the system designer in estimating the life of the cell under load and temperature conditions. Illustrative, hypothetical characteristic curves are shown in <u>Table 15</u>. Fig. 35 highlights the effect of temperature on primary cell capacity and <u>Fig. 36</u> shows the result of increasing constant current loading on capacity. The diagrams illustrate how usable battery capacity is adversely affected by both its operating environment and operating condition.

#### Table 15. Example primary battery characteristics

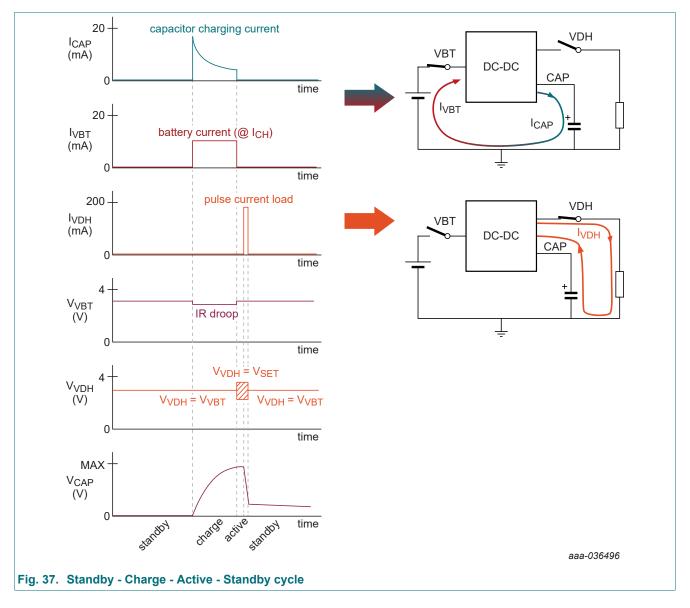

The NBM5100A/B-Q100 uses two stages of high efficiency DC-DC conversion to buffer the battery from high current, short duration load transients. The first stage conversion, or charge cycle, is initiated in advance of a period of heavy load current. During the charge cycle, energy is transferred from the battery to an external storage capacitor at constant current from the battery. Once charged, the second stage of DC-DC conversion, or active cycle, transfers energy from the storage capacitor to a fixed voltage output capable of supplying high load current. The peak current drawn from the battery remains very low during the charge cycle and is minimal in the active cycle decreasing the repetitive stress on the battery and maximizing the usable capacity. When not operating in charge or active state, the NBM5100A/B enters a low quiescent current standby state. An intelligent learning algorithm monitors the load pulse characteristics and optimizes energy transfer to the capacitor.

NBM5100\_Q100

All information provided in this document is subject to legal disclaimers

© Nexperia B.V. 2025. All rights reserved

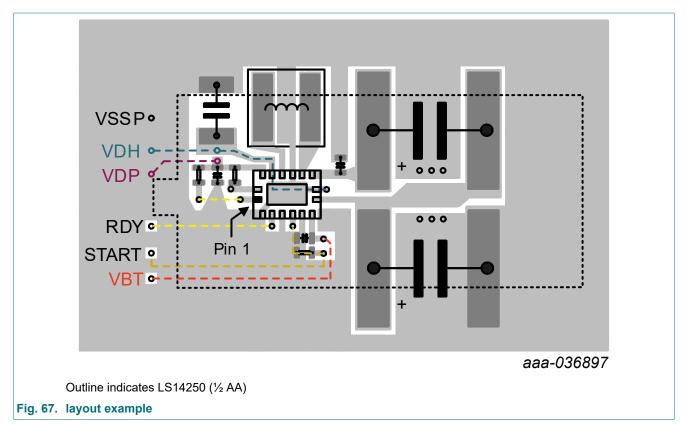

The NBM5100A/B-Q100 is ideal for applications supplied from non-rechargeable, primary cell batteries with high internal impedance. Common examples include: lithium metal primary batteries such as 3V lithium manganese dioxide (LiMnO<sub>2</sub> - example "CR 2032 coin cell"), 3.6 V lithium thionyl chloride (Li-SOCl<sub>2</sub> - example "LS 14250" ½ AA), and emerging paper printed types. Lithium metal batteries are commonly selected for low-voltage, low-power electronics due to their superior energy density (Wh/kg) and long storage life. A comparison of lithium batteries is shown in <u>Table 16</u>. The 2 × "AA" alkaline column is included for reference.

#### Table 16. Basic primary cell battery comparison

|                            | LiMnO <sub>2</sub><br>CR 2032 | Li-SOCI <sub>2</sub><br>LS 14250 (½ AA) | 2 × "AA"<br>Alkaline                   |

|----------------------------|-------------------------------|-----------------------------------------|----------------------------------------|

| open circuit voltage (BoL) | 3 V                           | 3.6 V                                   | 3 V                                    |

| energy density             | 280 Wh/kg                     | 500 Wh/kg                               | 200 Wh/kg                              |

| capacity                   | 240 mAh (0.2 mA)              | 1200 mAh (0.5 mA)                       | ~ 4000 mAh (@ 250 mA)<br>(2 × 2000mAh) |

| cut-off voltage            | 2 V                           | 2 V                                     | 1.6 V<br>(2 × 0.8 V)                   |

| shelf life                 | 10+ years                     | 10+ years                               | 5-7 years                              |

| operating temperature      | -30 to 60°C                   | -55 to 85⁰C                             | 0 to 60°C                              |

| internal resistance [1]    | 10 Ω (BoL)<br>70 Ω (EoL)      | 10 Ω (BoL)<br>70 Ω (EoL)                | < 1 Ω (over lifetime)                  |

[1] BoL: Beginning of life

EoL: End of life

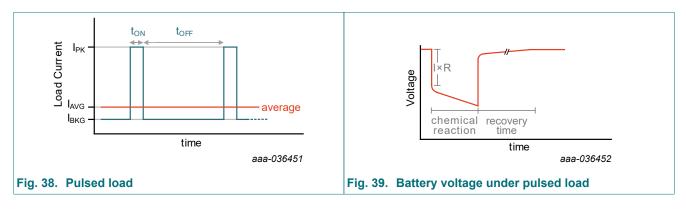

Many battery powered electronic loads do not operate with a constant current drain from the primary cell, rather are made of short periods of relatively high current followed by much longer periods of very low current. The resulting average current is very low, often only a few 10s of  $\mu$ A. It is complicated to accurately estimate the effect variable loading on battery capacity, but important to realize the usable capacity will be lower than the average indicates as the chemical reaction rate needed to support a load pulse of t<sub>ON</sub> is higher than that required in the t<sub>OFF</sub> condition scales non-linearly.

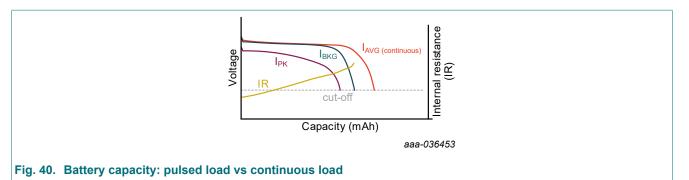

Fig. 38 depicts a pulsed load having a peak current  $I_{PK}$  and a background (continuous) current drain of  $I_{BKG}$ . During the load pulse, the battery voltage droops for two reasons Fig. 39: 1) I × R drop due to the pulsed current and 2) the chemical reaction rate in response to the load step. When the  $I_{PK}$  is released and the battery loading returns to  $I_{BKG}$ , the battery voltage returns close to its value before the load pulse was applied. Over time and repetitive pulses, battery chemicals are depleted and the starting and recovery voltages decrease.

<u>Fig. 40</u> compares a <u>continuous</u> current drain,  $I_{AVG}$  equal to the duty cycle average of  $I_{PK}$  and  $I_{BKG}$  to the piecewise components of  $I_{PK}$  and  $I_{BKG}$  to illustrate battery capacity under pulsed conditions are not equivalent to a steady-state current drain of an average equivalent load. Maximum battery life is achieved when the battery is exposed to low DC current, ideally < 10 mA.

NBM5100\_Q100

## 8.3. Operating modes

The NBM5100-Q100 has three operating modes:

- 1. Continuous mode

- 2. On-demand mode

- 3. Auto mode (NBM5100A-Q100 only)

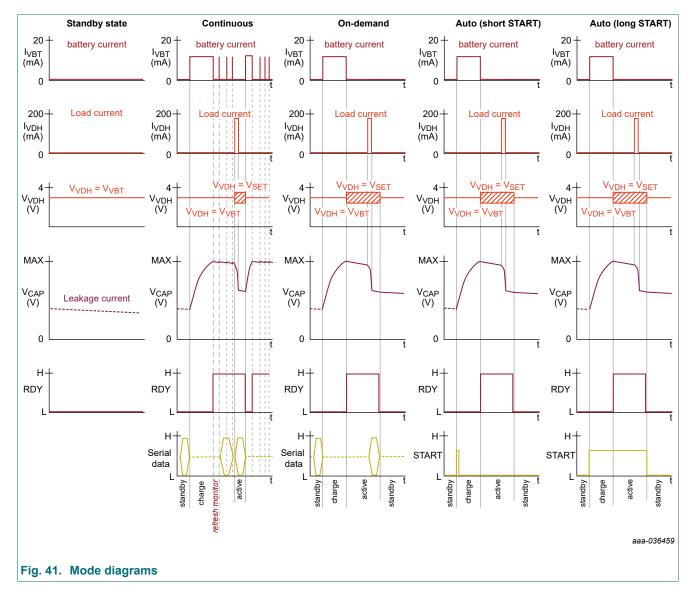

When the NBM5100A/B-Q100 is in one of the three operating modes, the device may transition between different <u>States of operation</u>: Standby, Charge, or Active. The Standby state is not an Operating mode, but is represented in <u>Fig. 41</u> for clarity of device behavior while <u>not</u> in one of the three operating modes.

#### 8.3.1. Mode overview

#### **Mode Controls**

| Register 8<br>0x08<br>(write) | Code (bin) | Function | Remark                                                       |

|-------------------------------|------------|----------|--------------------------------------------------------------|

| bit [0] <i>eod</i>            | 0          | off      | -                                                            |

| (enable On-demand)            | 1          | on       | -                                                            |

| bit [1] <i>ecm</i>            | 0          | off      | -                                                            |

| (enable Continuous mode)      | 1          | on       | -                                                            |

| bit [2] <i>act</i>            | 0          | off      | -                                                            |

| (force Active state)          | 1          | on       | force active                                                 |

| bit [3] <i>rstpf</i>          | 0          | -        | -                                                            |

| (reset optimizer)             | 1          | reset    | reset optimizer result of active profile<br><u>prof[5:0]</u> |

| Register 11 (write)           |            |          |                                                              |

| bit [7] automode              | 0          | off      | default for NBM5100B-Q100 version [1]                        |

|                               | 1          | on       | default for NBM5100A-Q100 version                            |

[1] NBM5100B-Q100 cannot be written to 1.

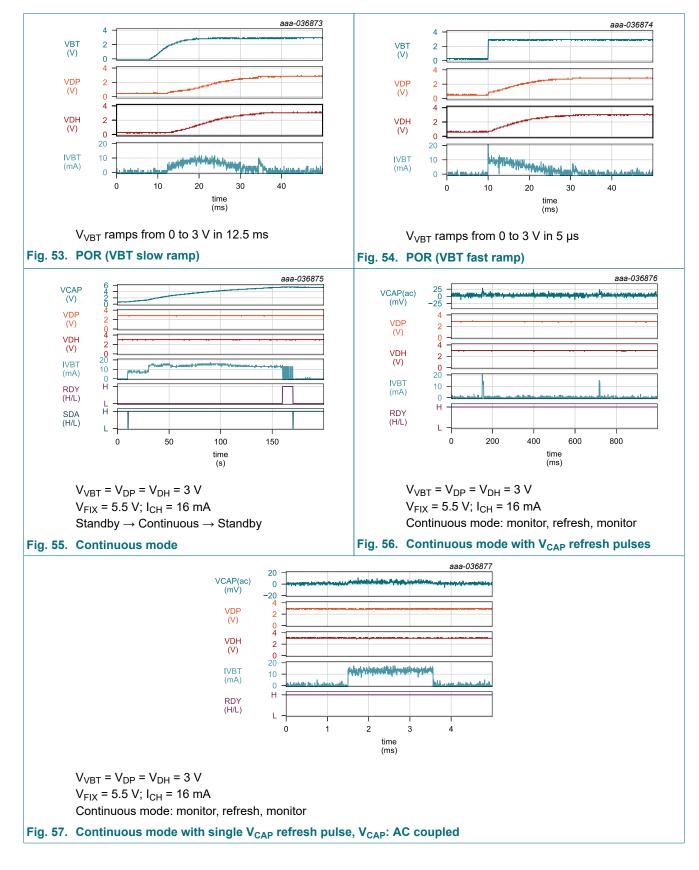

#### 8.3.2. Continuous mode

Continuous mode is intended for applications requiring instant pulse load capability. It is initiated by setting the ECM bit 0x08[1] (see <u>Mode controls</u>). In Continuous mode, the external storage capacitor is charged and the DC-DC converter is idled. The CAP pin voltage is "monitored," and if the capacitor voltage,  $V_{CAP}$  as indicated in <u>vcap</u> drops below the end of charge  $V_{FIX}$  as programmed in <u>vfix</u> the DC-DC is automatically enabled to "refresh" the capacitor to the target  $V_{FIX}$  voltage. When an Active command is received then the stored energy in the capacitor is immediately available at full power as a regulated supply voltage at pin VDH. The storage capacitor will get recharged automatically after the device has delivered its energy pulse to the load. The RDY signal indicates when the storage capacitor has been charged or recharged to  $V_{FIX}$ . Active state and recharging can be toggled as needed. The device returns to Standby mode by resetting both the ECM and ACT bits.

#### 8.3.3. On-demand mode

On-demand mode is initiated by setting *eod* bit 0x08[0] (see <u>Mode controls</u>). This mode is intended to maximize battery lifetime in low duty cycle applications where the system is in sleep-mode most of the time. In this mode the energy is first extracted from the battery and stored in a capacitor (C<sub>store</sub>) connected to the CAP pin. The stored energy is then made available at full power as a regulated supply voltage at pin VDH. The RDY output indicates when the output VDH is ready to deliver power. On-demand mode is ended by resetting the *eod* and *act* bits.

#### 8.3.4. Auto mode (NBM5100A-Q100 only)

Auto mode utilizes the START pin to set and reset the *eod* bit without requiring the serial bus. One cycle is initiated by a rising edge on the START pin. When charging is finished the Active state will begin automatically and the RDY pin will go high to confirm that the VDH pin is regulating to  $V_{SET}$  and ready to deliver full power. The Auto mode can be enabled or disabled by the *automode* bit 0x0B[7]. To prevent unintended Auto mode triggering due to a floating input condition, the START pin should be connected to VSS via a pull-down resistor. The pull-down resistor should be sized appropriately for the  $I_{OH}$  of the external microcontroller driving the pin.

In Auto mode, there are two ways to define the end of the Active state:

Short pulse on START: From standby mode, a short pulse (≥ 10 µs) is applied on the START pin. A charge cycle initiates followed by automatic transition to Active state. A short START pulse is defined as the time the START pin is driven high until Active state is reached at the conclusion of the Charge state. 10 µs ≤ t<sub>START(short)</sub> ≤ time<sub>(Charge state ends)</sub> as indicated

by the <u>rdy</u> bit or the <u>RDY pin</u>. The Active state automatically ends when the combined VDP and VDH load current is below  $I_{NL}$  for approximately  $T_{NL}$ .

2. Long pulse on START: From standby mode, the START pin is driven high and maintained high until the Active cycle begins as indicated by a high transition on the RDY pin. The Active state is ended when the START pin is driven low. When a long START pulse is initiated, the START pin should be maintained high until the high current load pulse on VDH is concluded.

Note: in case the START pin is set low during the charge state, this will be interpreted as a short pulse.

At power-on, the default settings of the NBM5100A-Q100 are:

- Auto mode is ON (see <u>Mode controls</u>)

- V<sub>SET</sub> = 3.0 V

- I<sub>ch</sub> = 8 mA

- Profile number = 1 (Optimization is active for profile 1)

When other settings are required, a serial bus command is required to change the default settings.

The NBM5100A-Q100 can be switched between Continuous mode, On-demand mode and Auto mode at any time.

## 8.4. Feature description

#### 8.4.1. Chip control

Refer to <u>functional diagram</u>. The chip control consists of the device <u>state machine</u>; <u>serial bus interface</u>; status, configuration and control <u>registers</u>; the <u>optimizer</u> engine, <u>capacitor balance</u>; and <u>fuel gauge</u> functions. It enables and disables peripheral analog blocks as required to execute the <u>state machine</u>.

#### 8.4.1.1. Serial bus

The NBM5100A/B-Q100 is controlled using a serial bus interface. Reading or writing of settings may be performed approximately 20 ms after power-on reset is cleared and device start-up completed. Initiating communication while the device is in startup may result in register errors. Internal registers allow control of the Standby-Charge-Active cycling process (On-demand mode) or the Charge-Active cycling process (Continuous mode), reading of device status indications, and adjustment of device operating parameters.

#### 8.4.1.1.1. NBM5100A-Q100 I<sup>2</sup>C interface

The NBM5100A-Q100 is protocol compatible to Fast Mode Plus I<sup>2</sup>C interface (1 MHz). The NBM5100A-Q100 is a slave device and has two programmable slave addresses. Each I<sup>2</sup>C transaction requires a register address followed by one or more data bytes. The register address is auto-incremented after each data-byte.

For reading data, the selection of the register address and the reading of the data must occur in one single transaction. Switching from write to read mode (or vice versa) must be done with a repeated Start condition. Register selection is always cleared after a STOP (P) command. If no register is selected while reading, the status register will appear as the first data byte.

| S SLAVE ADDRESS W A DAT                  | TA (REG ADDR = N) | A DATA (       | N) A P   |                            |            |

|------------------------------------------|-------------------|----------------|----------|----------------------------|------------|

| Multiple byte write to register (N +     | 1)                |                |          |                            |            |

| S SLAVE ADDRESS W A DAT                  | TA (REG ADDR = N) | A DATA (       | N) A     | DATA (N + 1) A P           | ]          |

| Multiple read from register (M) and      | (M + 1)           |                |          |                            |            |

| S SLAVE ADDRESS W A DATA                 | (REG ADDR = M) A  | Sr SLAVE ADDI  | RESS R A | DATA (M) A DATA (M +       | • 1) A P   |

| Multiple read of registers (0 - 2)       |                   |                |          |                            |            |

| S SLAVE ADDRESS R A                      | DATA (0) A C      | DATA (1) A     | DATA (2) | AP                         |            |

|                                          |                   |                |          |                            |            |

|                                          |                   |                |          |                            |            |

| Legend                                   |                   |                |          |                            |            |

| Legend<br>From Master to Battery Booster | S Start condition | WWrite bit (0) | Acknowle | dge bit                    |            |

| _                                        | S Start condition | WWrite bit (0) |          | dge bit<br>Start condition |            |

| From Master to Battery Booster           |                   |                |          | Start condition            | aaa-036470 |

| From Master to Battery Booster           |                   |                |          | Start condition            | aaa-036470 |

NBM5100\_Q100

Two I<sup>2</sup>C slave addresses are available for the NBM5100A :

#### Table 18. I<sup>2</sup>C addresses

| ADR pin | I <sup>2</sup> C Slave address |

|---------|--------------------------------|

| 0       | 0x2E (010 1110 R/Wn)           |

| 1       | 0x2F (010 1111 R/Wn)           |

#### 8.4.1.1.2. NBM5100B-Q100 Serial Peripheral Interface (SPI)

The NBM5100B-Q100 supports bidirectional communication with a master system controller (MCU) via a 4-wire SPI mode 0 compatible serial communication interface. It is a transmit/receive slave-only interface. The master device initiates data transfers on the bus and must generate the Clock (SCLK) and Chip Select Not (CSN) signals. The data input is SDI (MOSI), and the data output is SDO (MISO). Each transmission starts with the falling edge of CSN and ends with the rising edge. During a transmission, commands and data are controlled by SCLK and CSN according to the following rules:

- Commands and data are shifted MSB first, LSB last.

- Input bit is sampled at the rising edge of SCLK.

- In read mode, data bits are shifted out at the falling edge of SCLK. After the device has been selected with the falling

edge of CSN, the first byte defines data direction and register address. MSB = 1 for Read, or MSB = 0 for Write, followed

by 7-bits for the address in the register space.

- The rising edge of CSN ends all data transfer, terminating any previous command and clears the address pointers.

- If an invalid command is received, no data is shifted out of the circuit until the falling edge of CSN. This reinitializes the serial communication.

- Data that is written to the NBM5100B-Q100 immediately follows the first address byte.

- Data that is read from the device at the rising edge of SCLK immediately follows the last bit of the address byte.

- Maximum SCLK clock frequency is 4 MHz (500 Kbyte/s)

- An SPI command can be followed by multiple data bytes within one transmission. The register address pointer is autoincremented.

- SPI mode 0 means that the parameters Clock Polarity (CPOL) and the Clock Phase (CPHA) are both 0.

#### 8.4.1.1.3. Device register overview

Refer to the <u>register map</u>. Short description of the registers and their functions follows. Additional details can be found in the respective feature sections.

**setx** registers [0x09:0x0D] configure the active mode regulated output voltage <u>vset[3:0]</u> (V<sub>DH</sub>); the charge state target voltage <u>vfix[3:0]</u>, V<sub>FIX</sub> and maximum voltage for the storage capacitor <u>vcapmax</u> (V<sub>CAP(MAX)</sub>); the capacitor charging current <u>ich[2:0]</u> (I<sub>CH</sub>); low voltage monitor thresholds for battery <u>vmin[2:0]</u> (V<sub>MIN</sub>), and capacitor early warning <u>vew[3:0]</u> (V<sub>EW</sub>); enable/disable the internal power path switch between V<sub>DP</sub> and V<sub>DH</sub> <u>vdhhiz</u>; enable/disable auto mode <u>automode</u>; adjust the voltage margin of the optimizer function <u>opt\_marg[1:0]</u>; and enable/disable balance pin operation <u>enbal</u> and balance current <u>bal\_mode[1:0]</u>.

<u>status</u> register [0x00] provides indication the capacitor is charged and is the device is ready (<u>rdy</u>) to support a high current load on the  $V_{DH}$  pin. The <u>RDY</u> output pin reflects the present status of the <u>rdy</u> bit without requiring serial bus data transactions. Monitor alarms for low battery,  $V_{MIN}$ , (<u>lowbat</u>); low capacitor voltage,  $V_{EW}$ , early warning (<u>ew</u>) and low output voltage in the Active state,  $V_{DH}$  (<u>alarm</u>) provide a view of device and system conditions.

<u>command</u> register [0x08] is used to set the device operating modes: enable On-demand, enable Continuous, and Active. The MSBs of [0x08] and LSBs of [0x07] are used to set the optimizer profile number <u>prof[5:0]</u> (1d to 63d). Each profile setting can be used optimize the energy transfer of one unique repetitive load condition (see <u>Section 8.4.5</u>). The least significant bits of the optimizer profile setting are deliberately located in the command register to facilitate a single write transaction for the first 14 settings (1d to 14d).

<u>vcap</u> register [0x05] is utilized in the charge and active states to provide near real-time indication of storage capacitor voltage. The registers are not updated in the standby state. The <u>vchend</u> register is a translated digital mapping of the target  $V_{CAP}$  voltage obtained from <u>vfix[3:0]</u> in [0x08] when the <u>prof[5:0]</u> bits are all reset [0h], or <u>voptx[3:0]</u> hidden registers used by the optimizer to set the target capacitor charging voltage threshold associated with each profile.

<u>chengy</u> registers [0x01:0x04] provide indication of the charge removed from the battery following one enable On-demand or upon completion of a Continuous mode cycle. The registers are reset before the charging cycle begins and should be read and accumulated by an external microcontroller while the device is in the active or standby state.

#### 8.4.1.2. The ready (RDY) output signal and rdy bit

The RDY signal is driven high indicating that the NBM5100A/B-Q100 is ready to provide full power to its load. It can serve as an interrupt signal to a connected microcontroller. Its behavior is different (see below) in On-demand mode than it is in Continuous mode. The <u>rdy</u> bit in 0x00[0] follows the RDY signal.

#### **RDY in On-demand mode**

The RDY signal will go high when the capacitor charge level is reached, and the VDH output voltage is regulating to VSET.

The RDY signal will go low if:

- The eod bit is reset (see <u>Mode controls</u>) or

- The storage capacitor is depleted.

If Early Warning is activated and the voltage at the storage capacitor drops below  $V_{EW}$  (see <u>capacitor early warning voltage</u>), then the RDY signal will pulse low for t<sub>EW</sub>, then resume high state until one of the above On-demand mode conditions is met.

#### **RDY in Continuous mode**

The RDY signal will go high when the voltage at pin CAP has reached V<sub>FIX</sub>.

The RDY signal will go low if:

- The act bit is reset (see <u>Mode controls</u>) or

- The storage capacitor is depleted.

If Early Warning is activated and the voltage at the storage capacitor drops below  $V_{EW}$  (see <u>capacitor early warning voltage</u>), then the RDY signal will pulse low for t<sub>EW</sub>, then resume high state until one of the above Continuous mode conditions is met.

#### 8.4.2. States of operation

The NBM5100A/B-Q100 has four main states of operation as shown in Table 19.

| Operating state                 | Continuous mode                                                                         |     | On-demand mode                                                                                                                                                                            |                                        | Auto mode                                                                                        |                   |

|---------------------------------|-----------------------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------|-------------------|

| Battery insertion<br>Startup    | <ul> <li>(1) ecm bit set</li> <li>(2) act bit set</li> <li>(3) act bit reset</li> </ul> | 110 | <ul> <li>(1) eod bit set</li> <li>(2) Charge ready</li> <li>(occurs autonomously)</li> <li>(4) eod bit reset</li> </ul>                                                                   | 001<br><b>101</b><br>000               | <ul> <li>(1) 10 μs start pulse</li> <li>(2) Charge ready</li> <li>(4) no_load current</li> </ul> | 001<br>101<br>000 |

| Standby<br>(1)<br>Charge        | from Charge or Active<br>return to Standby:<br>(4) Reset <i>ecm</i> and <i>act</i>      | 000 | <ol> <li>eod bit set</li> <li>Force active</li> <li>(before Charge ready)</li> <li>Continue charge</li> <li>Charge ready</li> <li>Coccurs autonomously)</li> <li>EOD bit reset</li> </ol> | 001<br>101<br>001<br><b>101</b><br>000 | 17 -                                                                                             | 001<br>101<br>000 |

| (2) (3)<br>Active<br>aaa-036463 | either controlled through logic.                                                        |     | ralue of the bits ( <i>act</i> ; <i>ecm</i> ; e<br>al bus command, or ( <b>in bo</b> l                                                                                                    |                                        |                                                                                                  |                   |

#### 8.4.2.1. Startup state

When a battery or other voltage source is sensed at the VBT pin and the sensed voltage is higher than V<sub>POR</sub> level, internal power switches connect VBT and outputs VDP and VDH (See <u>POR VBT fast ramp</u>). Approximately 20 ms after start-up, the Standby state is entered.

NBM5100\_Q100

**Note:** The <u>register map</u> indicates the default state of all bits at startup. Reading or writing to the serial bus during the Startup state may cause corruption of the non-volatile memory. Serial bus transactions should not be initiated until approximately 20 ms after  $V_{VBT} > V_{POR}$  when the device has entered the Standby state.

#### 8.4.2.2. Standby state

The Standby state is a low power operating condition where the quiescent current consumption is almost negligible; the serial port is active and ready to receive commands; and the VBT to VDP switch is enabled.

In the Standby state, the device is inactive. The supply current drawn from the battery is very low,  $I_{Q\_STB}$  and the device is waiting for a serial bus command or START command (NBM5100A-Q100). While the device is in Standby state, device settings can be programmed. For example: <u>maximum storage voltage</u>,  $V_{CAP(MAX)}$ ; the <u>charging current</u>,  $I_{CH}$ ; and the active mode VDH <u>output voltage</u>,  $V_{SET}$ .

The VBT to VDH switch is enabled at POR by default. Alternatively, for a high-impedance VDH output in the Standby and Charge states, set  $\underline{vdhhiz} = 1$  (see  $\underline{VDH}$ ).

The register settings are retained while supply voltage at VBT input is not interrupted.

The RDY output and *rdy* register bit is low in Standby state.

The chip will exit Standby and enter the Charge state by:

- the setting of <u>eod</u> (Enable On-demand) bit, or

- setting the <u>ecm</u> (Enable Continuous Mode) bit, or

- activation with the <u>START</u> pin (NBM5100A-Q100) with <u>automode</u> = 1.

#### 8.4.2.3. Charge state

The DC-DC <u>boost converter</u> is enabled with VBT as the input and CAP as the output. The external storage capacitor is charged from VBT using constant current,  $I_{CH}$ , as set by the *ich[3:0]* bits in 0x0A[7:5]. The *ich* bits provide 4 normal charging current settings and one high current (emergency) level. Using the lowest  $I_{CH}$  setting maximizes battery life at the expense of a long charging time.

In the Charge state, if  $V_{VBT}$  drops below the programmed VBT input minimum threshold,  $V_{MIN}$  as set by the <u>vmin[2:0]</u> bits in 0x0A[2:0], the NBM5100A/B-Q100 pauses charging until VBT recovers above  $V_{MIN}$  at which point charging resumes. If VBT remains below the  $V_{MIN}$  threshold for more than 16 µs, the <u>lowbat</u> alarm status bit will be set to indicate the battery may be nearing end of life.

<u>vmin[2:0]</u> is an aid for maintaining a minimum battery voltage. Battery voltage drop could be caused by multiple factors including, current consumed by other functions in the application connected directly to the battery, end of battery life, a low operating temperature or the formation of a passivation layer inside the battery (in case of Li-Thionyl batteries).

While above V<sub>MIN</sub>, charging continues until the "End-of-charge" voltage is reached.

- Fixed (optimizer disabled): The "End-of-charge" voltage as set by <u>vfix (optimizer profile = 0)</u>

- Optimizer (enabled): The "End-of-charge" voltage as set by voptx (hidden register location) as controlled by the optimizer (optimizer profile ≠ 0)

The <u>vcapmax</u> bit in 0x0C[4] defines,  $V_{CAP(MAX)}$ , the maximum storage capacitor voltage allowed during the Charge state. For safety reasons the value  $V_{CAP(MAX)}$  will never be exceeded even if a higher fixed End-of-charge voltage is programmed.

The progress of charging the storage capacitor can be monitored by reading the vcap status register 0x05[4:0].

In On-demand mode, the device will automatically enter Active state after reaching the End-of-charge voltage.

In Continuous mode the device will stay in Charge state and the charge level of the capacitor will be maintained at the programmed level. This will compensate for any leakage from the storage capacitor. This charge maintenance uses minimal power from the battery.

#### 8.4.2.4. Emergency charge state

The normal charge currents ich[3:0] = 0h, 1h, 2h, or 3h are intended to limit the battery current for optimal efficiency and battery lifetime. The lower the charge current, the longer the time to charge the storage capacitor. In cases where a shorter charge time prevails above battery lifetime, the emergency charge mode (ich[3:0] = 4h) is available. In emergency charge mode, the battery current is increased to 50 mA (typical). <u>wmin[2:0]</u> continues to function as described in <u>Charge state</u>.

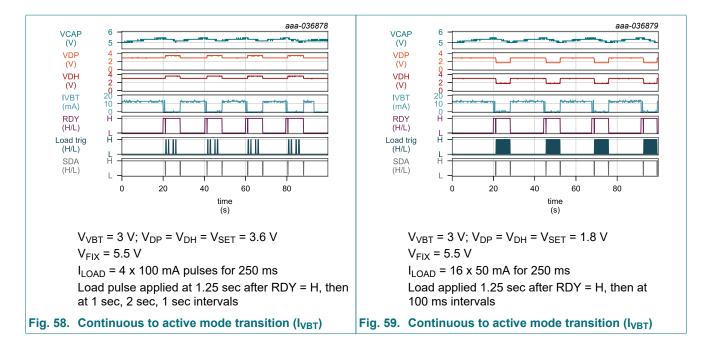

#### 8.4.2.5. Active state

In the Active state both the VDP and VDH outputs are supplied from the integrated switching regulator using the storage capacitor as its energy source. In this state the current consumed by the NBM5100A/B-Q100 from the battery is very low,  $I_{Q,ACT}$ . The output voltage (VDP and VDH) is determined by the value programmed in the *set1* register using the <u>vset[3:0]</u> (V<sub>SET</sub>) bits.

<u>On-demand mode</u>: The Active state is entered automatically after charging has been completed. The Active state can also be initiated prior to completion of the charge cycle (force active) by setting the <u>act</u> bit high. Active state ends by resetting the <u>eod</u> bit and returns to the Standby state.

**Continuous mode:** The Active state is entered at any time by setting the <u>act</u> bit. Active state ends by resetting the <u>act</u> bit and returns to the Charge state. Resetting the <u>ecm</u> and <u>act</u> bits returns the device to Standby.

#### 8.4.2.6. Capacitor input voltage Early Warning alarm

In the Active state the storage capacitor is the energy source for the DC-DC converter. As the capacitor is discharged by the load its voltage drops. A programmable early warning alarm is available to alert the system when  $V_{CAP}$  drops below the  $V_{EW}$  threshold set by the <u>vew[3:0]</u> bits indicating a limited amount of energy is remains in the capacitor. The <u>eew</u> bit enables or disables the alarm indication. The condition of the alarm is indicated by the <u>ew</u> bit in the status register 0x00[6]. When the <u>ew</u> bit goes high, the <u>RDY</u> pin pulses low for t<sub>EW</sub> providing two mechanisms for the system to receive an indication the alarm has triggered. The power on default state for <u>eew</u> is disabled.

#### 8.4.2.7. VDH output voltage alarm

In the Active state, if the load current exceeds the capability of the regulator, the VDH voltage may drop below the programmed target voltage,  $V_{SET}$  triggering the VDH alarm. The condition of the alarm is indicated by the <u>alarm</u> bit in the status register 0x00[5]. When the <u>alarm</u> bit is set, the RDY pin is driven low providing dual mechanisms for the system to receive the indication. If the load current is reduced, VDH may recover to  $V_{SET}$  before the Active state concludes; however, the <u>alarm</u> bit and RDY pin low indications will not reset until the next Charge state is initiated.

The maximum load current depends on the operating point of the DC-DC converter in the Active state: capacitor voltage (input supply to the DC-DC); the programmed VDH voltage  $V_{SET}$  (output of the DC-DC); external components ratings and tolerances; and the ambient temperature. Some typical characteristics are given in <u>Application curves</u>.

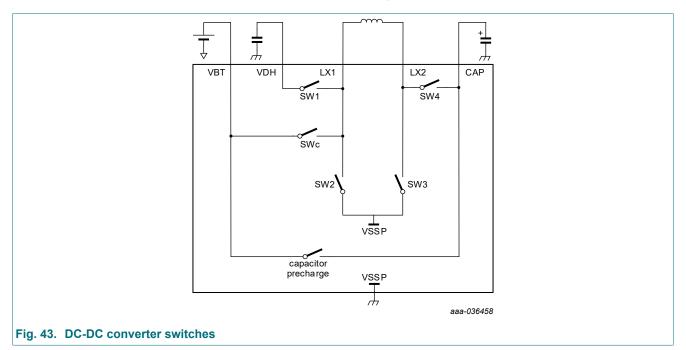

## 8.4.3. DC-DC converter

The NBM5100-Q100 integrates a variation of a classical peak-current mode control "4-switch buck-boost" with a fixed frequency of 1 MHz. The DC/DC converter operates with discontinuous conduction mode for light loads and transitions to continuous conduction mode as the load current increases. Refer to Fig. 43.

In the charge state when  $V_{CAP}$  < 1.6 V, the storage capacitor is initially charged at low current via the capacitor precharge switch.

In the Charge state when  $V_{CAP} > 1.6$  V, the DC-DC converter operates in boost mode to draw constant programmed charging current ( $I_{CH}$ ) from the battery and charge the energy storage capacitor connect to the CAP pin.

The charging transition threshold can be seen in the <u>typical characteristics</u> section of the datasheet in the charging state capacitor current  $I_{CAP}$  versus capacitor voltage,  $V_{CAP}$  plots.

#### Boost mode (Charge)

- Primary phase: SWc and SW3 are ON

- Secondary phase: SW2 and SW4 are ON

In the Active state, the dc/dc converter uses the energy available in the storage capacitor to deliver a regulated output ( $V_{SET}$ ) on the  $V_{DH}$  pin capable of supporting pulsed current loads.

#### Buck mode (Active)

- Primary phase: SW1 and SW4 are ON

- Secondary phase: SW1 and SW3 are ON

#### Boost mode (Active)

- Primary phase: SW2 and SW4 are ON

- Secondary phase: SW1 and SW4 are ON

## 8.4.4. VDP and VDH output configuration

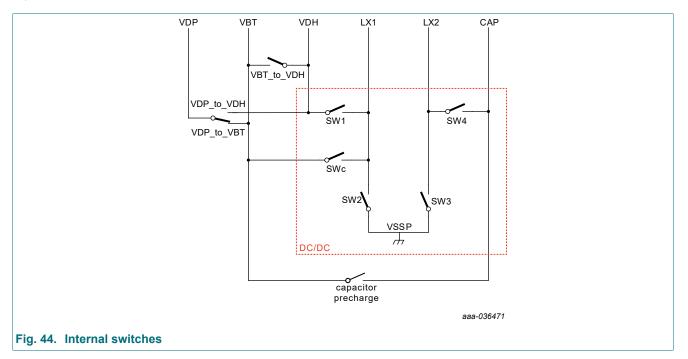

Fig. 44 provides a simplified representation of the internal power switches within the NBM5100A/B-Q100 devices.

#### 8.4.4.1. VDP

VDP is a 'permanent' supply output pin. It is internally connected to VBT in the Standby and Charge states via the VDP\_to\_VBT switch. In the active state, VDP connects to VDH via the VDP\_to\_VDH switch. It provides power to 'always on' system loads (e.g. host microcontroller core and I/O). Due to the variable range of output voltages between VBT and the regulated VDH, care should be taken to ensure loads connected to the VDP pin will not be subjected unintended overvoltage or under-voltage conditions.

The VDP pin should be connected to a bypass capacitor. See <u>Recommended components</u>.

#### 8.4.4.2. VDH

The <u>vdhhiz</u> bit 0x0A[4] is 0b upon entry into the Standby state following POR, connecting VBT to VDH. Unless the <u>vdhhiz</u> is set via the serial interface, VDH pin remains internally connected to VBT in all <u>states of operation</u> except the Active state.

In the Active state, VDH supplies a regulated output voltage according to <u>vset[3:0]</u> in 0x09[3:0]. <u>Table 20</u> summarizes the device default switch connections.

| State   | VDP            | VDH                             | Diagram                              |

|---------|----------------|---------------------------------|--------------------------------------|

| Standby | Connect to VBT | Connect to VBT                  |                                      |

| Charge  | Connect to VBT | Connect to VBT                  | Fig. 45. Standby and charge          |

| Active  | Connect to VDH | Connect to DC-DC output<br>vset | VBT<br>VBT<br>VBT<br>Fig. 46. Active |

If the <u>vdhhiz</u> bit 0x0A[4] is set via the serial interface, the VDH output becomes high impedance if the device is not in the Active state as indicated in <u>Table 21</u>. The high impedance configuration is useful in cases where it is preferable to switch off a load (e.g. a sensor) connected to the VDH pin. When the high impedance <u>vdhhiz</u> mode is not required, all loads can be supplied from the VDH pin simplifying system configuration. When high impedance mode is enabled, the host microcontroller should be supplied from the VDP pin or directly from the battery.

#### Table 21. VDP and VDH operation, *vdhhiz* 0x0A[4] = 1 (high-Z operation)

| State   | VDP            | VDH                                    | Diagram                          |

|---------|----------------|----------------------------------------|----------------------------------|

| Standby | Connect to VBT | Hi-Z                                   |                                  |

| Charge  | Connect to VBT | Hi-Z                                   | Fig. 47. Standby and charge      |

| Active  | Connect to VDH | Connect to DC-DC output<br><i>vset</i> | VBT VDH<br>VBT VDH<br>aaa-036687 |

In more complex RF microcontroller applications with multiple input voltage pins, the VDP output can be connected to the core and I/O functions supply inputs, while the VDH output is connected to the high current RF power supply input.

The VDH pin should be connected to a bypass capacitor after accounting for derating characteristics to achieve the minimum capacitance indicated in the <u>Recommended components</u> table.

#### 8.4.4.3. Setting VDH output voltage, V<sub>SET</sub> (Active state)

Upon completion of a Charge state, the device transitions to the Active state at which time VDH becomes a regulated voltage output denoted as  $V_{SET}$  as configured in <u>vset[3:0]</u> in 0x09[3:0]. Unless overwritten via the serial bus, the default  $V_{SET}$  voltage is 3.0 V.

For some applications it may be beneficial to change  $V_{SET}$  during the Active state. For example, an RF microcontroller in a sensor application needs to transmit several data packets to a remote receiver. The initial data packet is transmitted at maximum power likely requiring a  $V_{SET}$  voltage of 3.6 V. After receiving an acknowledgement of a successful link with receiver, the RF microcontroller may determine a lower transmit power is sufficient and decrease the  $V_{SET}$  voltage dynamically to 3 V for duration of this transmit/receive period.

#### 8.4.5. Adaptive power optimization

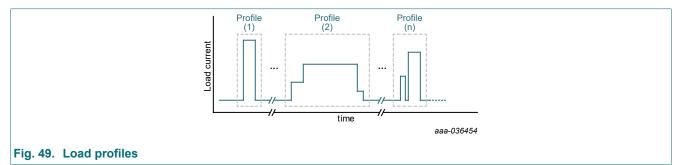

The NBM5100A/B-Q100 applies a proprietary learning algorithm to adaptively determine and optimize the amount of energy to be transferred from the battery and stored in the capacitor. This optimization engine can learn up to 63 load profiles. Each learned profile is retained in a reserved register location used by the optimization engine.

Each optimizer setting is used to store one load profile. Each stored load profile should be reasonably consistent and repetitive in energy requirements.

If *prof[5:0]* = 0h, the optimizer is <u>disabled</u> and the storage capacitor is charged according to the <u>vfix[3:0]</u> registers.

The optimizer engine works by measuring the residual energy level in the storage capacitor after each load pulse and predicts the optimized energy level to charge the storage capacitor for the next pulse.

Optimizer profile 1 and 'extra safe' optimization margin are enabled by default after the device POR threshold is cleared. Assigning a different profile, *prof[5:0]* in 0x07, 0x08, or altering the optimization margin, *opt\_margin* in 0x0D, is performed via the serial bus.

The optimizer margin voltages in <u>opt\_marg[1:0]</u> correspond approximately to the first four  $V_{OPTx}$  levels and is analogous to the first four  $V_{FIX}$  levels.

#### 8.4.5.1. Optimizer initialization and downward increment

Each optimizer profile setting learns the repetitive energy requirement of the assigned load. The number of repeated load pulses needed to reach an optimized level will vary depending upon the energy consumed. Reserved register locations maintain the target capacitor charging voltages for each profile,  $V_{OPTx}$ .  $V_{OPTx}$  is analogous to the user programmable  $V_{FIX}$  setting (optimizer profile = 0), the exception being the optimizer engine automatically increments  $V_{OPTx}$  during the initial learning phase and in response to changes in the load profile.

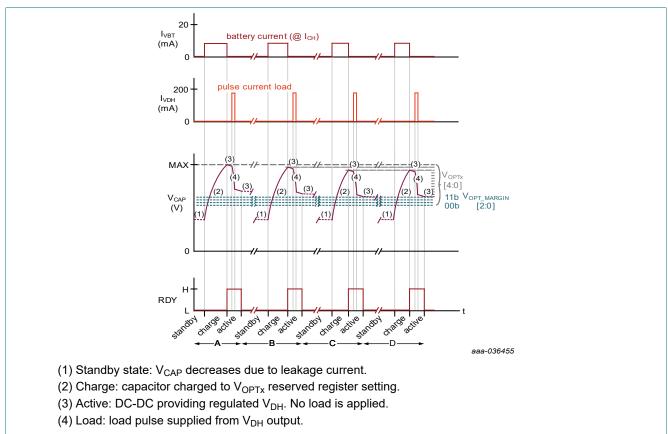

At the start of the optimization process,  $V_{OPTx}$  is set to  $V_{CAP(MAX)}$  according to the <u>vcapmax</u> setting. When On-demand is initiated via register write or START pin (NBM5100A-Q100), the capacitor charges to  $V_{CAP(MAX)}$ . When charging is complete, the NBM5100A/B-Q100 initiates an ACTIVE cycle during which the load is applied. At the conclusion of the Active cycle the capacitor voltage is compared to the  $V_{OPT}$  <u>MARGIN</u>, <u>opt\_marg[1:0]</u>, threshold.

- If  $V_{CAP} > V_{OPT MARGIN}$ , the *voptx* register is decremented one setting.

- If  $V_{CAP} < V_{OPT MARGIN}$ , the *voptx* register is incremented by at least one setting.

Fig. 50 is an example of an optimizer initialization sequence. The initialization sequence occurs after device power on, or if the optimizer profile is reset, by selecting a profile number using and writing 1b to <u>rstpf</u> 0x08[3].

Initial conditions for initialization example:

- 1. Device powered and POR cleared (battery insertion).

- 2. vcapmax 0x0C[4] = 1b.

- 3. V<sub>CAP</sub> at zero or holding residual charge.

- **4.**  $V_{OPT MARGIN} 0x0D[1:0] = 11b$  (default)

- 5. prof = 1b (default)

Fig. 50. Optimizer profile initialization and down increment

#### Table 22. Optimizer profile initialization and down increment

| · · ·                                              |                                                     |                                                    |                                                                           |

|----------------------------------------------------|-----------------------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------|

| Α                                                  | В                                                   | С                                                  | D                                                                         |

| V <sub>OPTx</sub> = V <sub>CAP(MAX)</sub> [15d]    | V <sub>OPTx</sub> = [14d]                           | V <sub>OPTx</sub> = [13d]                          | V <sub>OPTx</sub> = [13d]                                                 |

| (1) Standby.                                       |                                                     |                                                    |                                                                           |

| (2) On-demand cycle initiated: Charging.           |                                                     |                                                    |                                                                           |